# BUS ADAPTOR PRODUCTS CHASSIS PRODUCTS

Q22bus-VME Adaptor Model 432

IBM PC/AT

SUN SBus

**APPLE NuBus**

**MULTIBUS I**

CABLING

-SOLID

CONDUCTOR

-FIBER

OPTICS

DEC Q-BUS

IBM PS/2 MCA

**VMEbus**

**MIX BOARD**

**MULTIBUS II**

BIT3

COMPUTER CORPORATION

8120 Penn Avenue South Minneapolis, Minnesota 55431-1393 (612) 881-6955 FAX (612) 881-9674

#### DISCLAIMER

Please read and abide by the following paragraphs. Questions and comments should be directed to Bit 3 at the address below.

Bit 3 Computer Corporation does not authorize the use of its components in life support applications where failure or malfunction of the component may result in injury or death. In accordance with Bit 3's terms and conditions of sale, the user of Bit 3 components in any and all life support applications assumes all risks arising out of such use and further agrees to indemnify and hold Bit 3 harmless against any and all claims of whatsoever kind or nature (including claims of culpable conduct [strict liability, negligence or breach of warranty] on the part of Bit 3) for all costs of defending any such claims.

Bit 3 does not authorize the use of its components in nuclear control and process applications where failure or malfunction of the component may result in radioactive releases, explosions, environmental damage/contamination, personal injury or death. In accordance with Bit 3's terms and conditions of sale, the user of Bit 3 components in any and all nuclear applications assumes all risks arising out of such use and further agrees to indemnify and hold Bit 3 harmless against any and all claims of whatsoever kind or nature (including claims of culpable conduct [strict liability, negligence or breach of warranty] on the part of Bit 3) for all costs of defending any such claims.

Bit 3 makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Bit 3 assumes no responsibility for any errors that may appear in this document. The information in this document is subject to change without notice.

Bit 3 Computer Corporation 8120 Penn Avenue South Minneapolis, MN 55431-1393

#### NOTE:

DEC, Q-bus, MicroVAX and VMS are trademarks of Digital Equipment Corporation.

Revision 1.3 6/89 pub. no. 82602145

# TABLE OF CONTENTS

| INTRODUCTION                                        | 04          |

|-----------------------------------------------------|-------------|

| INSTALLATION                                        | 06          |

| INSTALLING THE ADAPTOR CARDS                        | 07          |

| INSTALLING THE VME CARD                             | 07          |

| INSTALLING THE Q22 CARD                             | 08          |

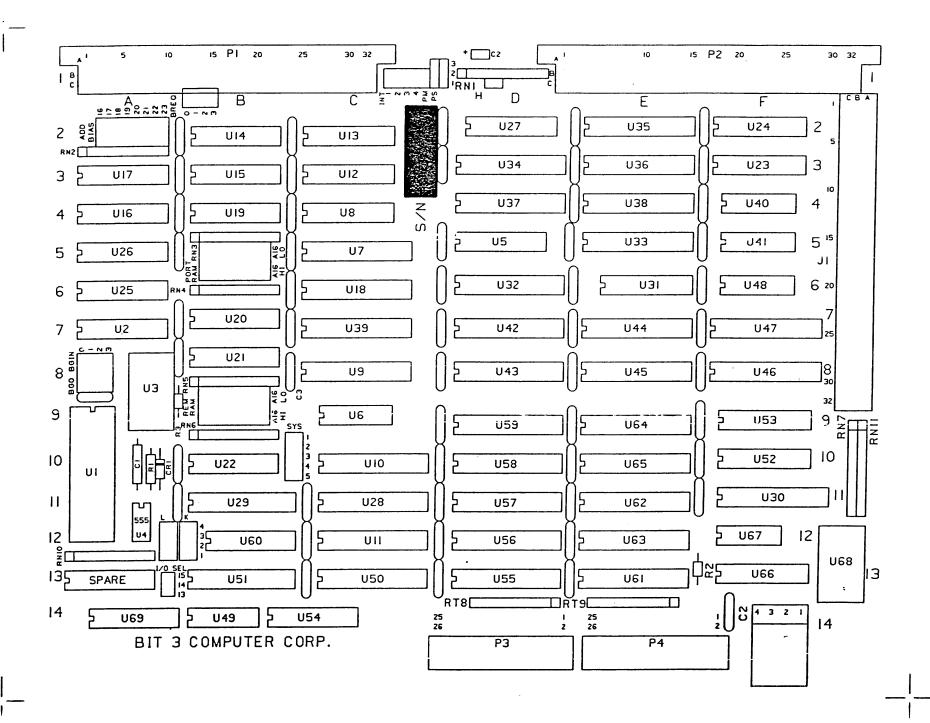

| VME CARD OUTLINE                                    | 09          |

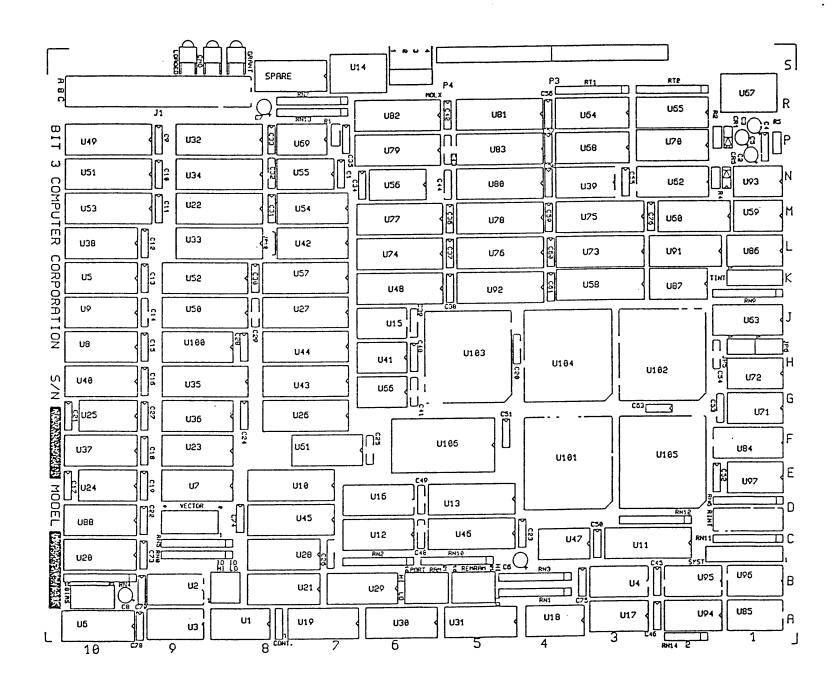

| Q22 CARD OUTLINE                                    | 10          |

| MEMORY MAPPING                                      | 11          |

| SETTING THE ADAPTOR CARD JUMPERS                    | 13          |

| THE VME ADAPTOR CARD JUMPERS                        | 14          |

| THE SYS JUMPERS                                     | 14          |

| INTERRUPT JUMPERS (INT)                             | 17          |

| BACKPANEL INTERRUPTS                                | 17          |

| PROGRAMMED INTERRUPTS                               | 18          |

| INTERFACE ERROR INTERRUPT                           | 19          |

| THE VME ADAPTOR REM RAM HI and REM RAM LO JUMPERS   | 20          |

| THE VME ADAPTOR ADDRESS BIAS JUMPERS (ADD BIAS)     | 23          |

| THE VME ADAPTOR DUAL PORT RAM JUMPER SETTINGS       | 24          |

| THE VME ADAPTOR PORT RAM HI and PORT RAM LO JUMPERS | 25          |

| SETTING THE VME I/O ADDRESS RANGE                   | 28          |

| THE VME ADAPTOR I/O SEL JUMPERS                     | 28          |

| OTHER VME ADAPTOR JUMPERS                           | 29          |

| VME ADAPTOR CARD FACTORY JUMPER SETTINGS            | 29          |

| THE 432 ADAPTOR Q22 CARD JUMPERS                    | 30          |

| ADDITIONAL Q22bus INTERRUPT JUMPERS                 | 32          |

| INTERFACE ERROR INTERRUPT                           | 34          |

| DMA DONE INTERRUPT                                  | 34          |

| QBUS C/D ROW BUS GRANT AND INTERRUPT CONTINUNITY    | 36          |

| USE OF THE Q-bus GRANT CONTINUNITY CARD             | 37          |

| THE Q22 CARD REM RAM HI and REM RAM LO JUMPERS      | 38          |

| THE ADDRESS BIAS JUMPERS                            | 40          |

| THE Q22 ADAPTOR CARD I/O SELECT JUMPERS             | 41          |

| THE PORT RAM HI and LO ADDRESS JUMPERS              | 42          |

| OTHER Q22 ADAPTOR JUMPERS                           | 45          |

| Q22 ADAPTOR CARD FACTORY JUMPER SETTINGS            | 45          |

| FUNCTIONAL USE OF THE ADAPTOR                       | 46          |

| THE Q22 ADAPTOR CARD DMA CONTROL REGISTERS          | 46          |

| NODE CONTROL REGISTERS                              | 49          |

| VME ADAPTOR CARD LOCAL NODE REGISTERS               | 50          |

| THE LOCAL NODE VME COMMAND REGISTER                 | 51          |

| THE LOCAL NODE VME STATUS REGISTER                  | 51          |

| €VME ADAPTOR CARD REMOTE NODE REGISTERS             | <b>→</b> 52 |

| THE VME CARD REMOTE NODE COMMAND REGISTER           | 53          |

| THE VME CARD REMOTE NODE STATUS REGISTER            | <b>/</b> 54 |

| VME ADDRESS PAGE REGISTER                           | 55          |

| VME ADDRESS MODIFIER REGISTER                       | 55          |

| THE IACK READ REGISTER                              | 56          |

| Q22bus ADAPTOR CARD LOCAL NODE REGISTERS            | <b>-</b> 57 |

| THE Q22bus LOCAL NODE COMMAND REGISTER              | 57          |

| THE Q22bus LOCAL NODE STATUS REGISTER               | 5 <i>7</i>  |

| THE Q22bus COMMAND REGISTER EXTENSION               | 58          |

| HANDSHAKE MODE DATA                                 | 50          |

| Q22bus LOCAL NODE STATUS REGISTER      | 60 ن |

|----------------------------------------|------|

| LADDRESS PAGE REGISTER                 | 60   |

| Q22 ADAPTOR CARD REMOTE NODE REGISTERS | 61   |

| Q22 CARD REMOTE NODE COMMAND REGISTER  | 62   |

| ADDRESS PAGE REGISTER                  | 64   |

| Q22 PAGE CONTROL REGISTER              | 65   |

| Q22 REMOTE NODE STATUS REGISTER        | 66   |

| THE IACK READ REGISTER                 | 66   |

| BYTE, WORD, and LONGWORD ADDRESSING    | 67   |

| THE SETUP PROGRAM                      | 67   |

| TESTING THE ADAPTOR                    |      |

| ACCESS TIMES BETWEEN SYSTEMS           | 68   |

|                                        | 68   |

| VME ADAPTOR CARD FRONT PANEL CONNECTOR | 69   |

| Q22bus ADAPTOR CARD LEDS               | 69   |

| POWER REQUIREMENTS                     | 69   |

| ENVIRONMENTAL                          | 69   |

|                                        |      |

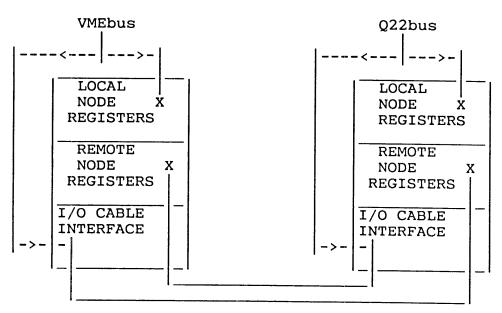

#### INTRODUCTION

The Bit 3 Model 432 Q22 - VME ADAPTOR permits the interconnection of a Q22 system and a VMEbus system. The two systems can be configured in a TRANSMITTER/RECEIVER relationship or in a TRANSMITTER/TRANSMITTER relationship. A processor on the TRANSMITTER system can appear as a bus master processor on the system. The memory windowing technique used interconnect the two systems enables a bus master processor communicate with memory or I/O on the other system without interim software drivers. Memory windowing maps memory addresses from the destination system's address space onto the host system's address space. The window size is jumper selectable and can range from 65 Kbytes to 16 Mbytes. A processor performing random access reads or writes to any address within the window in its address space has the read or write translated by the ADAPTOR into a read or write on the destination system. Hardware interrupts can be exchanged between the two systems.

The 432 Q22 - VME ADAPTOR consists of two printed circuit cards -- one for the VME card cage and one for the Q22 card cage.

Optional dual port RAM is available in the form of a daughter board that plugs into one of the two cards. The dual port RAM appears as a common memory to both systems. It is a convenient memory for electronic mail box or other applications where a processor needs to read or write to a common memory without using the other system's bus to access memory.

Multiple Q22 and VMEbus systems can be connected together in a star, daisy chain or combination star/daisy chain configuration. Other Bit 3 bus adaptor products permit MULTIBUS I and IBM PC/AT systems to be included in the configuration.

The ADAPTOR enables a bus master processor on the host system to directly address memory in the destination system as though it were local memory.

There are five ways to communicate between the two systems.

First, communication between the two systems can be via random access memory reads or writes. There is no need to pass data through intermediate software drivers. A processor in the host system can even execute code from memory on the destination system. This technique provides an easy to use, very flexible interface with low overhead. The high speed interconnect permits random access 16-bit read/writes to the destination system at speeds comparable to read/write speeds on bus memory cards on the host system. The user can establish the resulting host and destination address ranges in 24-bit VMEbus address space or in 22 bit Q-bus address space with BIAS jumpers.

Once the jumpers have been set up, the adaptor can be used as a bridge, invisible to the system software, between the two buses.

The system software does not have to check status of the adaptor card or execute any kind of setup program to initialize the adaptors. There are, however, additional features, (such as status on the interface) that are available if the applications system software is programmed to use them.

Up to 16 Mbytes of VMEbus memory can be assessed from the Q-bus. Up to 4 Mbytes of Q-bus memory can be accessed from the VMEbus.

A second method of communication is via 65 Kbyte paging.

A 65 Kbyte window in the Q-bus address space is coupled with an eight-bit programmable register. The address referenced within the window provides the lower sixteen address bits and the I/O register provides the upper eight bits of the 24-bit VMEbus address. The Q-bus system can then access up to 16 MBytes of memory in the VMEbus system by paging in 65K byte increments. The VMEbus system can access 4 Mbytes of Q-bus address space using 65 Kbyte to 1 Mbyte pages. A six-bit programmable register is used to provide the upper six bits of the Q-bus address.

A third method of communications is via block mode memory to memory DMA transfers. The Q-bus adaptor has a DMA controller that can be instructed to move up to 128 Kbytes of data between memory on the Q-bus and memory on the VMEbus. The DMA data rate is between 500 Kbytes and 700 Kbytes per second.

A fourth method of communication between the host and destination system is via I/O. Q22 I/O on the destination system can be directly addressed by a processor on the host VME system as host system I/O. VME host system short I/O reads or writes within the VMEbus I/O window are translated by the ADAPTOR into Q22 I/O reads or writes. Conversely, Q22 I/O reads or writes within the Q22 I/O space window are translated into VMEbus short I/O reads or writes.

A fifth method of communication between the two systems is via optional Dual Port Memory. Dual Port Memory is available in 32K, 128K, or 1 Mbyte sizes. It is a low profile daughter card that plugs into one of the ADAPTOR cards. This option provides a memory or DMA buffer available for use by both systems, and can save the cost of purchasing additional memory cards. Use of the dual port RAM can conserve bus bandwidth since neither system ties up the other system's bus when it reads or writes to the dual port RAM. The dual port RAM can be mapped into unused space on both systems with independent address jumpers on both boards.

An important feature of the Bit 3 Q22 - VME ADAPTOR is that it is not a simple repeater-type connection which links the timing of both buses together so that activity on either bus slows down the other bus. Instead, the Bit 3 model 432 ADAPTOR permits each bus to operate asynchronously and independently of the other. The two buses are linked only when a memory or I/O reference is made to an address in the window that translates to a reference on the other system.

Byte and word swapping (to adjust for the difference in addressing conventions between DEC and MOTOROLA type microprocessors) is supported by both jumper selection and command bit selection.

Interrupts on the VMEbus (IRQ1, IRQ2, IRQ3, or IRQ4) can be passed to the Q-bus. The VMEbus interrupt can be mapped into any of the four Q22 interrupt levels. Conversely, if there is no processor card in the Q22 system, any one of the four Q22 interrupts can be passed to one of the aforementioned VMEbus interrupts. It is also possible to pass interrupts between the two systems under program control. Either system can generate an interrupt acknowledge cycle on the other system. Interrupts are configured with jumpers.

If there is no system controller in the VMEbus application, the VME card can be configured with jumpers to drive the VME SYSCLK and to act as a single level bus arbiter on level 3. Also, if there is no processor card on the Q-bus, the Q22 card can be configured with jumpers to provide bus arbitration and to support interrupt acknowledgment. Additional system controller type cards are not needed.

Normally, one of the Bit 3 ADAPTOR cards is set with a jumper to allow its host bus to become a transmitter on the destination system. The companion receiver ADAPTOR card in the destination chassis is jumpered to accept commands from the host system but not to attempt reads and writes back to the host bus. Both cards, however, can be jumpered to permit them to become transmitters to the other bus.

The interface between the two cards is parity checked on address, control, and data lines.

I/O cables of eight feet, twenty-five feet, and fifty feet are available. A long line differential driver module is also available to extend cable distances to 300 feet.

Support software for MicroVMS users is available from Bit 3.

#### INSTALLATION

The Adaptor package contains the following items:

\* A VME printed circuit card Model 432-202

\* A Q22 printed circuit card Model 432-201

\* This Manual Model 432-901

\* An I/O cable to connect the two cards (purchased separately)

# \* A warranty card

Take time now to fill out and mail the warranty card. Your name will then be placed on our mailing list to receive update information on the Adaptor and other Bit 3 products.

#### INSTALLING THE ADAPTOR CARDS

It is necessary to study the rest of this manual to understand how to set the jumpers on the adaptor cards. Once the jumpers have been configured, the cards can be installed in their respective card cages by following the instructions below.

#### INSTALLING THE VME CARD

If a VME ADAPTOR card is to be the only bus master in the VME system, and hence the bus arbiter, it is necessary (per VME convention) to place the card in slot 1. Otherwise, the adaptor cards can be placed in any unused VME card slot. The two cable connectors mate with the I/O cable provided. The cable connectors are mechanically keyed as well as labeled to insure that they will not be connected upside down or backwards. Match the label on the connector to the label on the VME card bracket. The connectors fit tightly to provide a solid electrical and mechanical connection. (When removing the connectors use the pull tabs - don't pull on the wire.) A wire connected to the cable shield and terminated with a terminal lug is provided on each end of the cable.

The VMEbus has a bus priority scheme that permits bus masters to use other cards on the VMEbus. Before the VME adaptor card can talk to other VME cards in the same chassis, it must first gain A VMEbus functional module called the BUS control of the bus. ARBITER grants VME cards permission to use the VMEbus. arbiter is sometimes located on a separate system controller Other times it is integrated into a processor card. is beyond the scope of this manual to describe VMEbus arbitration but it is essential that the user understand how it works. VMEbus Specification Manual rev C.1, available from VITA (VMEbus International Trade Association) 10229 N. Scottsdale RD., Suite E, Scottsdale, Az. 85253, describes the VMEbus and the bus arbiter in detail. Experience shows that a common problem users encounter is an inability to communicate with other VME cards because the bus arbiter has been incorrectly configured.

The adaptor can be configured with jumpers to work with an already-installed system controller board containing a bus arbiter. If necessary, the adaptor can provide the system controller function of driving the system clock and can be a single level bus arbiter on level 3. In single level bus arbitration mode, the adaptor is the highest priority bus master. It will respond to bus requests on level 3 from other masters and activate the level 3 bus grant line when the Bit 3 adaptor does

not need the VMEbus. The adaptor operates in RWD (release when done) mode.

The dual port RAM option does not require an extra card slot on the VMEbus.

#### INSTALLING THE Q22 CARD

The Q22 card may be installed in any unoccupied quad slot in the Q22 card cage. It is necessary that the Q22 card receive bus grant and interrupt continuity. If there are unoccupied card slots in the chassis, it may be necessary to add bus grant continuity cards in the unused slots.

The MicroVAX chassis reserves the first three slots of an eight-slot backplane (and the first four slots of a twelve-slot backplane) for processor and memory cards. These slots are called Q/CD-type; the C- and D-connectors of these slots do not wire through the standard Q-bus signals. The remaining slots are for general use and are called Q/Q-type; the C- and D- connectors duplicate the standard Q-bus signals on the A- and B- connectors.

The BIT 3 Q-bus board is factory-jumpered to be installed in one of the general-use Q/Q slots in the backplane. If the user chooses to install the board in a Q/CD slot, the CONT jumpers at location A8 should be removed. (See page 36.)

If a dual port RAM card is installed on the Q22 card, the Q22 card may occupy two Q-bus card slots. A bus grant continuity card is provided with the dual port RAM card to insure that bus grant continuity to other cards in the Q-bus is maintained. (See page 37.)

The two cable connectors mate with the I/O cable provided. Match the label on the cable connector to the label above the connector on the Q22 card. The connectors are keyed so that the cables cannot be connected incorrectly. Connect the cable shield wire lug to the computer chassis.

#### MEMORY MAPPING

The 432 adaptor works by mapping a portion of memory address space in the second chassis into memory address space on the first (host) chassis. The memory in the second chassis appears to the first chassis as though it was logically present in the first chassis and behaves as it would if the memory were located on a memory card in the first chassis. It is also possible to map a portion of memory space from the first chassis into memory space on the second chassis (transmit/transmit mode). With this hardware mechanism it is possible for a Q-bus processor to directly read and write to memory or I/O devices located on a VMEbus or for a VMEbus processor to directly read and write to memory or I/O devices on the Q-bus.

In Q-bus to VMEbus operations, the Q-bus processor can address both 24 bit VME memory space and short 16-bit VME memory space. The address modifier code presented to the VMEbus can be either the default values sent from the Q-bus adaptor card or it can be a value loaded into a register on the VME adaptor card from the Q-bus processor.

In VMEbus to Q-bus operations, a VME processor can address both normal Q22 address space and I/O page address space.

The absolute address of the memory window in one chassis might not be the same absolute address location that you want to get at in the other chassis. The 432 adaptor provides a means to reposition the window to a different location in the destination bus.

Once the jumpers have been set up, the adaptor can be used as a bridge, invisible to the system software, between the two buses. The system software does not have to status the adaptor card or execute any kind of setup program to initialize the adaptors. There are, however, several additional features built into the adaptor cards that can be useful if the system software is set up to take advantage of them. For example, parity on all transfers between buses is checked and any parity errors are recorded in an adaptor status bit. There is a "page mode" of operation which can be used under program control to access memory outside of the jumpered window boundaries, and the adaptor can be set up to use an address modifier from a programmable register instead of using the address modifier code presented with the memory address. Q-bus to VMEbus applications, there is a memory-to-memory block mode DMA capability that will move up to 128 Kbytes of data back and forth between the two systems. Also, a "reset bus" command can be sent from one chassis to the other chassis. information is presented in the section on functional programming of the adaptor.

The data path between the two buses is 16 bits wide and the address path is 24 bits wide. Both byte (8-bit) and word (16-bit) data paths are supported. Byte swapping, sometimes required because of the addressing differences in MOTOROLA and DEC

microprocessors, is supported.

The optional dual port RAM card supports full 32-bit longword data transfers (from the VMEbus to the dual port RAM card only) as well as word and byte transfers.

Before setting the jumpers, take a minute to consider your system architecture.

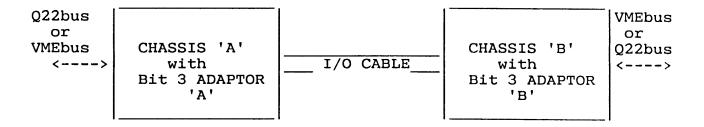

FIGURE 1 NOMENCLATURE

If a device in chassis 'A' performs reads or writes to memory or I/O on chassis 'B' but devices in chassis 'B' never perform reads or writes to memory or I/O cards inside chassis 'A', then, for the purposes of this manual, chassis 'A' is designated as the TRANSMIT (or host) chassis and chassis 'B' is designated as the RECEIVE (or destination) chassis. Jumpers in the SYS jumper block on each adaptor card configure an adaptor as either a transmit device or a receive device. In the above example, adaptor 'A' would be jumpered as a transmit adaptor and adaptor 'B' would be jumpered as a receive adaptor. Except for interrupts, the transmit adaptor has exclusive rights to use the I/O cable interface connecting the two adaptor cards. In this case, the optional dual port RAM card would be installed on the receive adaptor since, if the dual port RAM card was installed on the transmit card, it could not be accessed by the receive card (because the receive card cannot use the I/O cable for reads and writes). In any adaptor pair configuration, only one of the two adaptors can contain the optional dual port RAM memory card.

If devices in chassis 'A' sometimes perform reads or writes to chassis 'B' and devices in chassis 'B' sometimes perform reads or writes to chassis 'A', then both adaptors must be jumpered as transmitters. Either chassis can then control the other chassis. In this configuration, it is possible for a cable interference situation to develop if chassis 'A' tries to use the interface cable to talk to chassis 'B' at the same time that chassis 'B' tries to use the interface cable to talk to chassis 'A'. Hardware is not present to arbitrate this situation. If the flow of data between the two systems is sequenced such that both adaptors do not talk to the other chassis at the same time, then both adaptors can be jumpered as transmitters with no concern for

cable interference since it could not arise. A typical example would be a processor in chassis 'A' instructing a disk controller on chassis 'B' to read a file and DMA the file to memory in chassis 'A'. The processor in chassis 'A' would become a transmitter on chassis 'B' long enough to issue the command to the disk controller instructing it to do the operation and interrupt upon completion. The processor on chassis 'A' would then not use the adaptor interface until it had received the completion interrupt. Meanwhile, the disk controller in chassis 'B' would read the file and DMA transfer it into memory in chassis 'A' by becoming a transmitter over the adaptor interface. Cable interference cannot occur in this situation since the operation is sequenced such that both sides will not try to use the interface at the same time. Also, if communication between the two buses is through the dual port RAM, cable interference cannot occur since the dual port RAM interface is hardware If, on the other hand, communication between the arbitrated. systems is across the adaptor cable on each chassis and if it is bi-directional and asynchronous, cable interference could occur. The situation can be covered by a software semaphore in a number of ways. Consider the following sequence:

Chassis 'B' wants to get to a device in chassis 'A' but chassis 'A' is more frequently a transmitter to chassis 'B'.

The processor in Chassis 'B' does a local I/O write to its adaptor card, setting the PT interrupt flip-flop which sends an interrupt to chassis 'A'.

A processor in chassis 'A' detects the interrupt and does a read-modify-write operation (using a MOTOROLA TAS or DEC BBSSI/BBCCI type of indivisible instruction) to a semaphore flag in local chassis 'A' memory. If another 'A' bus co-processor has not reserved the adaptor to communicate with the 'B' bus, it sets the semaphore flag to indicate "don't use chassis 'B'" and then does an I/O write to the adaptor in chassis 'B' which clears the PT interrupt flip-flop.

The processor in chassis 'B' sees that its interrupt flag bit is reset by doing a local adaptor I/O status read. It is then free to use the adaptor interface to talk on chassis 'A' as long as it wants. When it is finished with chassis 'A', the processor in chassis 'A' clears the "don't use chassis 'B' semaphore flag" in memory on chassis 'A'.

If cable interference results from trying to communicate over the interface cable in both directions simultaneously, the data will probably be lost. Adaptor interface parity errors and interface timeouts will occur.

# SETTING THE ADAPTOR CARD JUMPERS

The customary designation for active low VMEbus signals is to follow the signal name with an asterisk (\*). This convention is

followed in this manual.

Jumpers are actually installed as shown here.

#### THE VME ADAPTOR CARD JUMPERS

The adaptor operating modes and memory mapping windows on each card are set by the user via jumpers to configure the cards for the applications system requirements. The VME adaptor card contains the following categories of jumpers:

- 1. System configuration jumpers -- SYS.

- The bus arbitration jumpers (VME CARD ONLY) -- BGIN, BGO, BREQ.

- 3. The interrupt select jumpers -- INT.

- 4. The address and range of the memory window through which memory in the Q22 chassis is viewed -- REM RAM LO and REM RAM HI.

- 5. The destination memory address and range jumpers for transfers from the Q22bus to the VMEbus -- ADD BIAS.

- 6. The VME I/O range select jumpers -- I/O SEL.

- 7. The VME address and range of the dual port RAM -- PORT RAM HI and PORT RAM LO.

#### THE SYS JUMPERS

There is some configuration information that you need to know about your VMEbus system.

First, determine if the Bit 3 VME adaptor card is the only bus master in the VMEbus chassis. One of the bus master cards in a VME chassis must provide clocking for the rest of the cards in the system. The Bit 3 adaptor can drive the SYSCLK signal if you choose, but it should only be set to do so if some other card is not already sourcing the signal. The adaptor card will not work if there is no SYSCLK.

Locate the SYS jumper block at location B/C 10 on the VME board.

NOTE: The jumpers shown in place are the factory jumper settings.

- o##o 1 jumper if the address modifier register is not used \*

- jumper if this card is a TRANSMITTER \*\* 0 02

- o o 3 there should never be a jumper on these pins

- jumper if you want Bit 3 card to drive SYSCLK

- o--o 4 o o 5 there should never be a jumper on these pins

- If this jumper is "ON", the address modifier presented to the VMEbus chassis holding this card comes from the default address modifier code/sent from the Q22 adaptor card in the other chassis. If the jumper is removed, the address modifier comes from the address modifier register located on the VME adaptor card.

- \*\* The term "TRANSMITTER" here means transmitter card, which sends commands to the receiver card. It does not mean that the card is necessarily a VMEbus master.

Second, determine which bus priority scheme is being used to grant the bus masters permission to use the VMEbus. several choices. Now might be a good time to review the subject by re-reading the VMEbus specification manual.

If there is a bus arbiter in the VMEbus system, the VME adaptor card can be configured to use any of the four bus request/ bus grant levels. If there is no bus arbiter in the VMEbus system, the VME adaptor card can be set to become a single level arbiter on level 3.

Locate the bus grant out and bus grant in (BGO/BGIN) jumper block at location A8 on the VME board. Also locate the bus request (BREQ) jumper block at location B2.

CAUTION -- VME card cages have jumpers to connect these daisychained bus arbitration signals and the interrupt acknowledge signal around unused card locations. Make sure that these jumpers are removed for the card slot that the Bit 3 adaptor is plugged into.

I hie pag. 55 onderaan.

If the Bit 3 adaptor is to be the bus arbiter, configure the jumpers as follows:

If there is another VME bus arbiter and the Bit 3 adaptor is to be configured to use level 3, set the jumpers as follows:

| BG | O BG  | IN |   | BREQ  |

|----|-------|----|---|-------|

| 0  | 00    | 0  | 0 | 0 0 0 |

| 0  | 00    | 0  | 1 | 100   |

| 0  | 00    | 0  | 2 | 200   |

| 0- | -0 0- | -0 | 3 | 3 00  |

|    |       | 0  |   |       |

If there is another VME bus arbiter and the Bit 3 adaptor is to be configured to use level 2, set the jumpers as follows:

| BG | O E  | BGIN |   | H | 3R | ΕÇ | ) |

|----|------|------|---|---|----|----|---|

| 0  | 00   | 0    | 0 | 0 | 0  | ,  | 0 |

| 0  | 00   | 0    | 1 | 1 | 0  |    | 0 |

| 0- | -o c | 00   | 2 | 2 | 0  |    | 0 |

| 0  | 00   | 0    | 3 | 3 | 0  |    | 0 |

|    |      | 0    |   |   |    |    |   |

If there is another VME bus arbiter and the Bit 3 adaptor is to be configured to use level 1, set the jumpers as follows:

| BG | 0  | BG1 | ΙN |   | I | 3R | REÇ   | ) |

|----|----|-----|----|---|---|----|-------|---|

| 0  | 0  | 0   | 0  | 0 | 0 | С  | )     | 0 |

| 0- | -0 | 0   | -0 | 1 | 1 | С  | ) — — | 0 |

| 0  | 0  | 0   | 0  | 2 | 2 | С  | )     | 0 |

| 0  | 0  | 0   | 0  | 3 | 3 | С  | )     | 0 |

|    |    |     | 0  |   |   |    |       |   |

If there is another VME bus arbiter and the Bit 3 adaptor is to be configured to use level 0, set the jumpers as follows:

| ВG | O BO  | NIE |   | E | BRE | Q  |

|----|-------|-----|---|---|-----|----|

| 0- | -0 0- | 0   | 0 | 0 | 0-  | -0 |

| 0  | 00    | 0   | 1 | 1 | 0   | 0  |

| 0  | 00    | 0   | 2 | 2 | 0   | 0  |

| 0  | 00    | 0   | 3 | 3 | 0   | 0  |

|    |       | _   |   |   |     |    |

#### INTERRUPT JUMPERS (INT)

Locate the block of interrupt jumpers (INT) at location C1 on the VME adaptor card. This set of jumpers permits selection of VMEbus interrupt signals to connect between the VMEbus and the Q22bus.

```

INT

Cable Int 1

100

VME Interrupt IRQ1*

200

Cable Int 2

VME Interrupt IRQ2*

Cable Int 3

300

VME Interrupt IRQ3*

Cable Int 4

4 o o

VME Interrupt IRQ4*

PM o

PS 0--0 0

o--o o<---- interface error interrupt pin

```

Up to four interrupt lines can be connected between the two buses.

There are also three categories of interrupts. The categories are:

- (1) Interrupts that are present on the VMEbus backpanel. Interrupt lines IRQ4\*, IRQ3\*, IRQ2\*, or IRQ1\* can be passed to the Q22bus.

- (2) Programmed interrupts.

- (3) An interface error interrupt.

#### BACKPANEL INTERRUPTS

Any of the four interrupts IRQ1-IRQ4 on the VMEbus (category 1 above) can be passed to the Q22bus. If the Q22bus adaptor card is connecting interrupts from the Q22bus to the VME adaptor card, then that cable interrupt line cannot be used at the same time to send a VME interrupt back to the Q22bus.

The INT jumper block selects the source of the interrupt lines that can be exchanged. If interrupts of category 1 above are to be sent to the Q22bus, then just put a jumper across one of the IRQ 1-4 lines on the VME adaptor card. On the Q22 adaptor card, make sure that there are no jumpers on the corresponding cable interrupt line pin (in the TINT Q22 card jumper block). If an interrupt is being sent from the Q22bus to the VMEbus, remove the associated INT jumper from the corresponding cable interrupt pin on the VME adaptor card.

#### PROGRAMMED INTERRUPTS

In addition to interconnecting "raw" backpanel interrupts between the two systems, there are two types of programmed interrupts that can be exchanged: PT interrupts and PR interrupts.

The term PT stands for programmed interrupt to the transmitter adaptor. This programmed interrupt does not require the local adaptor to use the read/write resources of the interface cable to send a programmed interrupt to the other bus (the four cable interrupts can always be sent between the two buses and are not considered to be in the same category as reads and writes).

PT interrupts work as follows:

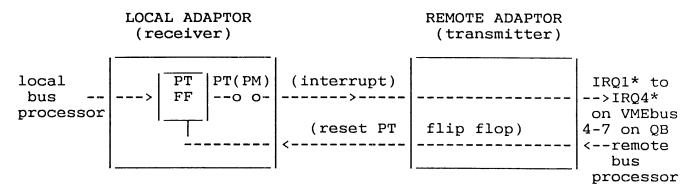

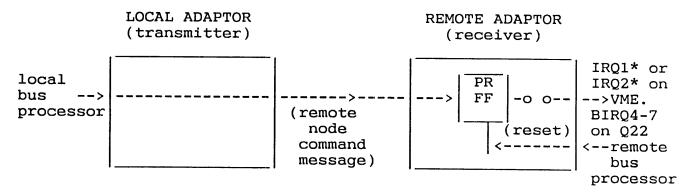

FIGURE 2 PT INTERRUPT

The pin at location PM in the interrupt jumper block area is a "O" when the PT flip flop in interrupt category 2 described above is active. This interrupt can be sent to the Q22bus over one of the four cable interrupt lines. The cable interrupt line selected to carry this PT interrupt back to the Q22bus adaptor cannot also be used to send a VMEbus IRQ line back to the Q22bus. Pin PM can be jumpered or wire wrapped to any of the four adaptor cable interrupt lines.

The programming sequence is:

- A processor in the receiver chassis writes to the receiver adaptor card local node command register and sets the PT interrupt flip-flop on the receiver adaptor card in its chassis.

- 2. The PT interrupt flip-flop on the receiver adaptor card is jumpered to a line in the INT jumper block on the receiver adaptor which sends the PT interrupt back to the remote transmit chassis.

- 3. When the transmitter adaptor bus processor detects the PT interrupt, it clears the PT flip-flop by doing a remote write over the interface cable to the remote node command register on the receiver adaptor card.

The term PR stands for programmed interrupt to receive adaptor. This type of programmed interrupt does not require the receive adaptor to use the interface cable to reset a programmed interrupt from the transmit bus.

PR interrupts work as follows:

FIGURE 3 PR INTERRUPT

The programming sequence is:

- A processor in the transmitter chassis writes over the interface cable to the receiver adaptor and sets the PR interrupt flip-flop on the receiver adaptor card.

- 2. The PR interrupt on the receiver adaptor card is jumpered to an interrupt line on the receiver bus backplane.

- 3. When the receiver bus processor detects the PR interrupt, it clears it by doing a local write to the adaptor card (the receiver card) in its chassis.

Pin 3 in the PS row of pins in the interrupt jumper block area is a "0" when the PR flip-flop in interrupt category 2 described above is being received by the VME adaptor card. This interrupt can be presented to the VMEbus as either IRQ1\* or IRQ2\*. To have the interrupt appear as IRQ1\*, remove the jumper from pins 1 and 2 of the PS row of pins and place it on pins 2 and 3 of the same row. To have the interrupt appear as IRQ2\*, remove the jumper from pins 1 and 2 of the bottom row of pins (the row containing the interface error interrupt pin) and wire wrap a wire from pin 2 in the same row to pin 3 in the PS row. If either IRQ1\* or IRQ2\* is used to present another type of interrupt to the VMEbus, the same interrupt line cannot also be used for the PR interrupt.

#### INTERFACE ERROR INTERRUPT

Interrupt category 3 described above (interface error interrupt) is presented to the VMEbus as either IRQ1\* or IRQ2\*. The

interface error interrupt pin is active when any of the two status error bits (timeout or parity error) are a "1". It is cleared with a "reset status errors" command and is not automatically cleared by a VME interrupt acknowledge. The interface error interrupt and status bit are meaningful if the adaptor card initiates communication over the interface cable to the other adaptor.

To have the interrupt appear as IRQ2\*, remove the jumper from pins 1 and 2 of the bottom row of pins (the row containing the interface error interrupt pin) and place it on pins 2 and 3 of the same row. To have the interrupt appear as IRQ1\*, remove the jumper from pins 1 and 2 of the PS row of pins and wire wrap a wire from the interface error interrupt pin to pin 2 in the PR row. If either IRQ1\* or IRQ2\* is used to present the interface error interrupt to the VMEbus, the same cable interrupt line cannot also be used to receive an interrupt from the Q22bus.

The following example shows a program generated interrupt from a VME processor card being sent to the Q22bus on VME level IRQ4\* and IRQ2\* backpanel interrupt being sent to the Q22 adaptor on VME level IRQ2\*. The Q-bus interrupt level that it activates is selected by jumpers on the Q22 adaptor card.

| in |

|----|

|    |

| i  |

EXAMPLE SETTING

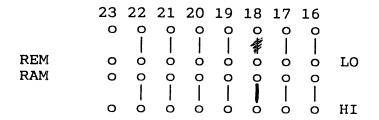

# THE VME ADAPTOR REM RAM HI and REM RAM LO JUMPERS

Locate the REM RAM HI and LO jumper block at location  $\ensuremath{\mathsf{B8}}$  on the VME adaptor card.

The REM RAM LO and HI (for remote bus RAM) jumper settings select the starting address and the address range that a VMEbus master will reference in its address space on the VMEbus when it wants to read from or write to the Q22bus. The REM RAM LO jumper block sets the starting VME address and the REM RAM HI selects the ending address. If the address range is translated to a different address range on the Q22bus (via the BIAS jumper settings on the Q22bus card), the VMEbus starting address should be an integral address multiple of the range selected, starting from address zero on the VMEbus. For example, if a 128 Kbyte

range is selected, the VME starting address should be set to a 128K boundary counting up from address zero on the VMEbus. The maximum possible setting for the range is 16 Mbytes, but a range greater than 4 Mbytes would not be useful since 4 Mbytes is the maximum range on the Q22bus. There cannot be any other VMEbus RAM in the same chassis at the addresses assigned for REMOTE BUS RAM since then there would then be two memories addressed at the same time and neither one could work properly.

Set the REM BUS RAM LO jumpers to the starting address of the first two digits of the 6 digit hex VME 24 bit address for the block of memory that you want mapped to the Q22bus. Assume that the remaining four digits of the hexidecimal address are all zeros. Set the REMOTE RAM HI jumpers to the first address after the end of the block of memory to be mapped to the Q22bus.

VMEbus address space equal to or greater than the REM RAM LO setting and less than the REM RAM HI setting is mapped to the Q22bus. If you do not want to use the REM BUS RAM function, set the REM RAM HI jumpers to a value less than the REM RAM LO value.

A jumper forms a logic "0" when it is installed (ON in the tables). It forms a logical "1" when it is removed (OFF in the tables).

The bit significance of the pins is shown below:

The jumpers are shown for the factory setting of 800000 for the LO address and 840000 for the HI address. With this setting any VMEbus memory reference using an address modifier of 39, 3A, 3D, or 3E and an address in the 256K range from 800000 through 83FFFF will be mapped to the Q22bus.

# REMOTE BUS RAM FIRST DIGIT VALUE

| 2 | A23                               | A22                                      | A21                                             | A20                                       | VME REMOTE BUS RAM ADDRESS 1st DIGIT |  |

|---|-----------------------------------|------------------------------------------|-------------------------------------------------|-------------------------------------------|--------------------------------------|--|

|   | ON ON ON ON ON ON OFF OFF OFF OFF | ON ON ON OFF OFF OFF ON ON ON OFF OFF OF | ON OFF ON OFF ON ON OFF ON OFF ON OFF ON ON OFF | ON OFF ON OFF ON OFF ON OFF ON OFF ON OFF | 0 hex 1 2 3 4 5 6 7 8 9 A B C D E    |  |

|   |                                   |                                          |                                                 |                                           | RAM SECOND DIGIT VALUE               |  |

| 2 | A19                               | A18                                      | A17                                             | A16                                       | VME REMOTE BUS RAM ADDRESS 2nd DIGIT |  |

|   | ON ON ON ON ON ON OFF OFF OFF     | ON ON ON OFF OFF OFF ON ON ON ON OFF OFF | ON OFF ON OFF ON ON OFF ON OFF ON OFF           | ON OFF ON OFF ON OFF ON OFF ON OFF ON OFF | O hex 1 2 3 4 5 6 7 8 9 A B C D E    |  |

E F

OFF OFF OFF ON OFF OFF

When a bus master in the Q22bus chassis wants to reference memory in the VMEbus chassis, it does so by addressing within a window in Q22bus address space. The window is selected by the REM BUS RAM jumper settings on the Q22bus adaptor card. This address is convenient for the processor in the Q22bus chassis, but it may not be at the address that it wants to use in the VMEbus chassis.

The ADD BIAS jumpers permit you to offset the Q22bus address into a different address in VMEbus address space.

Be careful not to set the memory mapping jumpers such that a memory address from the first chassis that addresses in the second chassis would map through the second chassis and try to reappear again in the first chassis. This would cause an adaptor conflict and would not work.

NOTE: You can also use the adaptor cards in page mode where the upper eight VME address bits are supplied by an 8-bit address page register on the VME card. See FUNCTIONAL USE OF THE ADAPTOR.

When the Q22bus adaptor card addresses VMEbus RAM in the chassis containing the VME adaptor card, the lower sixteen Q22bus address lines are passed on "as is" to the VMEbus backpanel. This establishes the minimum contiguous block of VME addresses as 65 Kbytes in VMEbus memory. You can position this 65 Kbyte block anywhere in VMEbus address space so long as the VMEbus target address starts on a 65K boundary (from address zero). The jumpers give you three choices for the remaining eight higher VMEbus address lines:

- 1. You can set the destination VMEbus address bit to a "ZERO".

- 2. You can set the destination VMEbus address bit to a "ONE".

- 3. You can extend the VMEbus address range by connecting more Q22bus address bits to the VMEbus address.

The VME adaptor card is set at the factory to map a 256K VME address range from the Q22bus to start at address zero on the VMEbus. If you want to re-position the destination address in VMEbus memory so that it starts at an address other than zero, or if you want to map a larger or smaller block of memory to the VMEbus, you will have to change the jumpers.

If you connect Q22bus address line 16 to VMEbus address line A16, you can address a 128K VMEbus block. Subsequently connecting A17, A18, A19, A20, and A21 from the Q22bus to address lines A17, A18, A19, A20, and A21 on the VME card permits extending the

range to 256K, 512K, 1MEG, 2MEG, and 4MEG.

Once the range has been established, the remaining higher VMEbus address bits must be jumpered to ground or left open to establish the starting address.

A bit left in the open position (i.e., not jumpered to ground or connected to a Q22bus address line) appears as a "ONE" bit in the VMEbus address.

A bit jumpered to one of the ground pins appears as a "ZERO" in the VMEbus address.

|                                        |             | ADD    |             |

|----------------------------------------|-------------|--------|-------------|

|                                        |             | BIAS   |             |

|                                        | Q22bus A16  | 0440-0 | VMEbus A16  |

|                                        | Q22bus A17  | 0440-0 | VMEbus A17  |

|                                        | Q22bus A18  | 0440-0 | VMEbus A18  |

|                                        | Q22bus A19  | 0440-0 | VMEbus A19  |

|                                        | Q22bus A20  | 0440-0 | VMEbus A20  |

|                                        | Q22bus A21  | 0440-0 | VMEbus A21  |

|                                        | not defined | 0 00   | VMEbus A22  |

|                                        | not defined | 0 00   | VMEbus A23  |

| source address bits from the Q22bus    |             |        | GND PINS    |

|                                        |             | -      | <del></del> |

| destination address to VMEbus backpane |             |        |             |

#### VME ADD BIAS JUMPER BLOCK AT LOCATION A2

NOTE: the jumper positions shown are for the factory jumper settings with the same address appearing on the VMEbus as is selected with the REM RAM jumpers on the Q-bus adaptor card.

The middle row of pins connect through a non-inverting buffer to drive the VMEbus address lines A16-A23. The right row of pins (by the address numbers) are all connected to ground. The left row of pins are the address bits received from the Q22bus chassis.

## VME ADAPTOR DUAL PORT RAM JUMPER SETTINGS

The dual port RAM is an optional memory piggy back board that attaches to one of the adaptor cards. Only one dual port RAM card can be used at a time with the pair of adaptor cards. The RAM card should be added to the adaptor board which is normally a receiver, since the bus which holds the card can then directly access the dual port RAM without using the interface cable connecting the two adaptor cards. This leaves the interface cable free for use by the other chassis to access the dual port RAM or

to access devices on the bus holding the adaptor without concern for a possible cable interference situation. The VME adaptor still uses only one VME card slot after adding the dual port RAM card.

The dual port RAM looks to both systems as simply more RAM memory. The address of the dual port RAM is set by jumpers on both adaptor cards. The card can be set to respond to an address range in the VME system and to a different address range in the Q22bus system. The dual port RAM responds to VMEbus address modifier codes 39, 3A, 3D, or 3E.

The dual port RAM offers several advantages. First, there are some types of I/O cards that do not have on-board RAM but need some RAM, such as a DMA buffer, to perform their function. that case, the dual port RAM can save the cost of purchasing another memory card. Second, a bus master can access the dual port RAM without using the other bus. This permits operation when reading and writing to the dual port RAM than is possible when reading and writing directly to the other bus, since a bus arbitration cycle to gain access to the other bus is not necessary. Third, use of the dual port RAM can conserve bus bandwidth since neither system ties up the other bus when it reads and writes to the dual port RAM. The dual port RAM can also be used as a common memory for interchange of information between processors in a multiprocessor environment. Fourth, as mentioned previously, adding the dual port RAM does not use another VMEbus slot. Unless the card-to-card spacing in the Q22bus card cage is 8/10 in., the dual port RAM card will require two card slots when it is mounted in the Q22bus card cage. Bit 3 has short bus grant continuity cards to be used if the dual port RAM card is mounted on the Q22 card.

Both systems can access the memory concurrently. The adaptor card housing the dual port RAM card arbitrates conflicts that occur if both systems try to use the memory at the same instant.

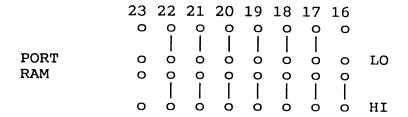

#### THE VME ADAPTOR PORT RAM HI and PORT RAM LO JUMPERS

Locate the PORT RAM HI and LO jumper block at location B5 on the VME adaptor card.

The PORT RAM LO and HI jumper settings select the starting address and the address range that a VME bus master in the VME chassis will reference when it wants to read or write to the dual port RAM. The PORT RAM LO jumper block sets the starting VME address and the PORT RAM HI selects the ending address. The minimum range is 65 Kbytes and the maximum range is 16 Mbytes. Set the range to match the size of your dual port memory. If the dual port memory is less than 65 Kbytes, set the range to 65K. There cannot be any other VMEbus RAM at the addresses assigned for dual port RAM since then there would then be two memories addressed at the same time and neither one could work properly.

Set the PORT RAM LO jumpers to the starting address of the first two digits of the six-digit hex VME 24-bit address for the block of memory that you want mapped to the dual port RAM. Assume that the remaining four digits of the hexidecimal address are all zeros. Set the PORT RAM HI jumpers to the first address after the end of the block of memory to be mapped to the dual port RAM.

VMEbus address space equal to or greater than the PORT RAM LO setting and less than the PORT RAM HI setting is mapped to the dual port RAM. If you do not want to use the dual port RAM function, set the PORT RAM HI jumpers to a value less than the PORT RAM LO value.

A jumper forms a logic "0" when it is installed (ON in the tables). It forms a logical "1" when it is removed (OFF in the tables).

The bit significance of the pins is shown below:

The jumpers are shown for the factory setting of 810000 for the LO address and 800000 for the HI address. With this setting the dual port RAM function is disabled since the HI value is less than the LO value.

# PORT RAM FIRST DIGIT VALUE

| A23                            | A22                                         | A21                                          | A20                                    | VME PORT RAM ADDRESS 1st DIGIT                                   |

|--------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------|------------------------------------------------------------------|

| A23 ON ON ON ON ON OFF OFF OFF | A22 ON ON ON OFF OFF ON ON ON OFF ON ON OFF | A21 ON OFF ON OFF ON OFF ON OFF ON OFF ON ON | A20 ON OFF ON OFF ON OFF ON OFF ON OFF | VME PORT RAM ADDRESS 1st DIGIT  O hex  1 2 3 4 5 6 7 8 9 A B C D |

| OFF<br>OFF                     | OFF<br>OFF                                  | OFF<br>OFF                                   | ON<br>OFF                              | E<br>F                                                           |

# PORT RAM SECOND DIGIT VALUE

| A19                        | A18                          | A17                          | A16                  | VME PORT RAM ADDRESS 2nd DIGIT |

|----------------------------|------------------------------|------------------------------|----------------------|--------------------------------|

| ON<br>ON<br>ON<br>ON<br>ON | ON<br>ON<br>ON<br>OFF<br>OFF | ON<br>ON<br>OFF<br>OFF<br>ON | ON OFF ON OFF ON OFF | 0 hex<br>1<br>2<br>3<br>4<br>5 |

| ON                         | OFF                          | OFF                          | ON                   | 6                              |

| ON                         | OFF                          | OFF                          | OFF                  | 7                              |

| OFF                        | ON                           | ON                           | ON                   | 8                              |

| OFF                        | ON                           | ON                           | OFF                  | 9                              |

| OFF                        | ON                           | OFF                          | ON                   | Α                              |

| OFF                        | ON                           | OFF                          | OFF                  | В                              |

| OFF                        | OFF                          | ON                           | ON                   | С                              |

| OFF                        | OFF                          | ON                           | OFF                  | D                              |

| OFF                        | OFF                          | OFF                          | ON                   | E                              |

| OFF                        | OFF                          | OFF                          | OFF                  | F                              |

# SETTING THE VME I/O ADDRESS RANGE

The "short address modifier codes" 29 and 2D are often used to identify a sixteen bit I/O address space on the VMEbus. Address modifier 29 is defined as short non-privileged access and address modifier 2D is defined as short Supervisory Access. There are two types of I/O operations that can be directed to the VME adaptor card from a VMEbus processor. First, there are the optional I/O commands that permit extended control of the adaptor through adaptor register reads and writes. Second, I/O reads and writes can be mapped through the adaptors to become I/O reads and writes on the Q22bus. The I/O SEL jumper block at location A/B 13 selects the I/O address range in VMEbus short I/O address space used for these two functions.

The 65 Kbyte I/O address range is divided into seven eight-Kbyte ranges, depending on the setting of the I/O SEL jumpers. A read or write within the selected 8K range with an address modifier code of 29 is passed to the Q22bus adaptor, where it becomes an I/O read or write at the same 8K address offset in the I/O page on the Q22bus system. A read or write within the selected 8K range with an address modifier code of 2D does not appear on the Q22bus chassis, but instead controls registers on the adaptor cards.

# THE VME ADAPTOR I/O SELECT JUMPERS

Locate the I/O SEL jumper block at location A/B 13. This jumper block sets the I/O addresses of the VME adaptor card. VMEbus processor cards can perform I/O operations to the adaptor card to read status or control adaptor registers (see FUNCTIONAL USE OF THE ADAPTOR). Also, the VME chassis can perform I/O reads and writes on the Q22bus chassis. If your application does not use these features, it is possible to disable both functions by removing all of the jumpers from the I/O SEL jumper block.

|   | I/O | SEL  |     |     |          |

|---|-----|------|-----|-----|----------|

|   | 0   | o 15 |     |     |          |

| — | 0   | o 14 | VME | I/O | disabled |

|   | 0   | 0 13 |     |     |          |

With no jumpers on, the card will not respond to the short address modifier codes and the I/O feature is disabled.

I/O SEL o--o 15 o--o 14 VME I/O address is 2000-3FFF o o 13

NOTE: This 2000-3FFF range is the factory setting.

I/O SEL o--o 15 VME I/O address is 4000-5FFF o o 14 o--o 13 I/O SEL o--o 15 o o 14 VME I/O address is 6000-7FFF o o 13 I/O SEL o o 15 0--0 14 VME I/O address is 8000-9FFF o--o 13 I/O SEL o o 15 o--o 14 VME I/O address is A000-BFFF o o 13 I/O SEL 0 0 15 VME I/O address is COOO-DFFF 0 0 14 o--o 13

# OTHER VME ADAPTOR JUMPERS

The remaining jumpers on the VME adaptor at locations A/B 12 and D1 are preset at the factory and are not to be changed by the user.

# VME ADAPTOR CARD FACTORY JUMPER SETTINGS

VMEbus REMOTE RAM ADDRESS (to Q-bus) 800000 - 840000

VMEbus ADDRESS OF PORT RAM disabled

VMEbus RAM BIAS JUMPERS 4 Mbytes, same adr as Q-bus

VMEbus ADAPTOR VMEbus I/O ADDRESS 2000-3FFF, AM = 29 or 2D

VMEbus INTERRUPT JUMPERS none

LEVEL 3 ARBITER

DRIVES SYSCLK

RECEIVER MODE

USES DEFAULT ADDRESS MODIFIERS FROM Q22bus ADAPTOR

#### THE 432 ADAPTOR Q22bus CARD JUMPERS (Q22bus CARD)

To properly set the jumpers on the Q22bus card, there is some configuration information that you must know about your Q22bus system.

Determine if there is a Q-bus processor card in your Q-bus chassis (the MicroVAX II processor acts like a Q-bus processor card). If there is no Q-bus processor card, the Bit 3 Q22bus adaptor can be jumpered to provide the bus arbitration and interrupt acknowledge functions normally provided by the Q-bus processor. When used in this mode (processor mode), the Q22bus adaptor must be placed in Q-bus card slot 1. The Q22bus adaptor does not have bus terminators which are sometimes provided by the Q-bus processor card. When using the card in processor mode, use a backplane that has terminator resistors or install a Q22 terminator resistor card in one of the card slots.

Usually there will be a Q-bus processor card in the Q-bus system, so it will not be necessary to use the Bit 3 Q22 card in processor mode. In that case, the Q22 adaptor can be installed in any quad card slot. It is necessary that the Q22 adaptor receive the bus grant and interrupt acknowledge signals from the processor card, so be sure that you have continuity cards in any unused card locations between the processor card and the Q22 adaptor card.

Locate the SYST jumper block at location C1 on the Q22bus board.

```

1

jumper if the card is used in processor mode

0

О

there should never be a jumper on these pins

0 0

0--0

there should always be a jumper on these pins

jumper if the card is used in processor mode

0 0

jumper if this card is a "transmitter" **

0---0

0 0

Q-bus interrupt level select 0 ***

Q-bus interrupt level select 1 ***

0--0

0 0

jumper to word swap on VMEbus to Q-bus transfers *

0 0

jumper to byte swap on VMEbus to Q-bus transfers *

jumper to word swap on Q-bus to VMEbus transfers *

0 0

0

jumper to byte swap on Q-bus to VMEbus transfers *

T

S

Y

S

```

<sup>\*</sup> See the section on byte and word swapping

<sup>\*\*</sup> The term "TRANSMITTER" means transmitter card, which sends commands to the RECEIVER card. It does not mean that the card is necessarily a Q22bus bus master.

<sup>\*\*\*</sup> This pair of jumpers selects which Q-bus interrupt level will

be activated when the Q22 adaptor card sends an interrupt to the Q-bus. The factory default setting is Q-bus interrupt level 5. The levels are selected per the following table:

## Q-bus interrupt level 4 (BIRQ4)

Level 0 jumper o--o JUMPER ON Level 1 jumper o--o JUMPER ON

# Q-bus interrupt level 5 (BIRQ5)

Level 0 jumper o o JUMPER OFF Level 1 jumper o--o JUMPER ON

## Q-bus interrupt level 6 (BIRQ6)

Level 0 jumper o--o JUMPER ON Level 1 jumper o o JUMPER OFF

# Q-bus interrupt level 7 (BIRQ7)

Level 0 jumper o o JUMPER OFF Level 1 jumper o o JUMPER OFF

# ADDITIONAL Q22bus INTERRUPT JUMPERS (Q22bus CARD)

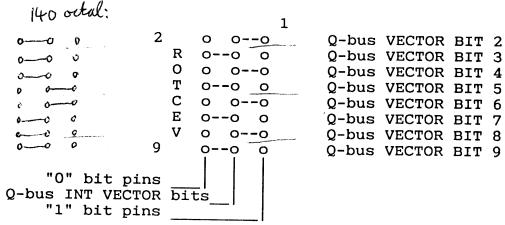

Locate the block of jumpers (VECTOR) at location D9 on the Q22bus card. This set of jumpers selects the interrupt vector transmitted on the Q-bus when the Q-bus processor acknowledges an interrupt from the Q22bus adaptor card.

Q-bus vector bits "0" and "1" are always zero. To make a vector bit a "0", place a jumper between the middle row pin for that bit and the corresponding "0" bit pin. To make a vector bit a "1", place a jumper between the middle row pin for that bit and the corresponding "1" bit pin.

The interrupt vector jumpers are shown for the factory default setting of Hex 154 (524 octal).

Locate the block of jumpers at location D1 on the Q22 adaptor card. This block is labeled RINT and is used for jumpering interrupts received from the VMEbus into Q-bus interrupts.

There are seven possible sources of interrupts from the Q22 adaptor card to the Q-bus. They are: (1) interface error interrupt, (2) DMA done interrupt, (3) the PR interrupt, programmed interrupt to receiver card, and (4) any one of the four possible interrupts sent from the VME adaptor card over the cable interrupt lines 1-4. An inactive to active transition of any of these interrupt sources can be captured by the Q22 adaptor card and will cause a Q-bus interrupt (BIRQ4, BIRQ5, BIRQ6, or BIRQ7, depending on the level jumpers in the SYST jumper block).

The Q-bus interrupt handler can determine the actual interrupt source by reading bits 9,10, and 11 in the CSR status register after the Q-bus interrupt acknowledge. The interrupt sources are priority encoded as follows:

| PRIORITY LEVEL | INTERRUPT TYPE | CSR STATUS CODE |

|----------------|----------------|-----------------|

|                |                | BITS 11 10 9    |

| 0 (highest)    | PR O           | 0 0 0           |

| 1              | PR 1           | 0 0 1           |

| 2              | PR 2           | 0 1 0           |

| 3              | EXT INT 3 (DMA | DONE) 0 1 1     |

| 4              | EXT INT 4      | 1 0 0           |

| 5              | EXT INT 5      | 1 0 1           |

| 6              | EXT INT 6      | 1 1 0           |

| 7 (lowest)     | EXT INT 7      | 1 1 1           |

The PR interrupt does not have to be jumpered. It is hardwired to priority levels 0, 1, and 2. It is set when a VMEbus processor sets the PR flip-flop by writing a "1" to bit 5 in the Q22bus remote node command register. Along with setting the PR bit, the VMEbus processor must also set control bits 0 and 1 in the same register. If bit 0 is set, the PR interrupt flip-flop is interpreted as PR 1. If bit 1 is set, the PR interrupt is interpreted as PR 2. If neither bit 0 or bit 1 is set, the PR interrupt is interpreted as PR 0. After acknowledging the PR interrupt, the Q-bus processor can clear the PR flip-flop to inform the VMEbus processor that the requested Q-bus task has been completed. Note that only a "0" to "1" transition of the PR flip-flop will cause a Q-bus interrupt, so it is necessary for either the Q-bus processor or the VMEbus processor to clear it before it can cause another PR interrupt by setting it again.

The external interrupt sources are selected by jumpering or wire wrapping to the adjacent pins in the RINT jumper block that are possible sources for interrupts. Each interrupt is detected by the <u>inactive-to-active transition</u> of the interrupt source. If more than one interrupt source is active, the highest priority interrupt source will be acknowledged first, and the CSR status register will reflect the status for that source, but the Q-bus interrupt will remain active. When the interrupt is acknowledged a second time, the CSR status register will reflect the status for the next highest interrupt source. This will continue until all active interrupt sources have been acknowledged.

```

ERR INT

DMA DONE

NOT USED

NOT USED

O O EXT INT 3

NOT USED

O O EXT INT 5

Cable Int LINE 4

Cable Int LINE 3

Cable Int LINE 2

Cable Int LINE 1

NOT USED

O RINT

```

# INTERFACE ERROR INTERRUPT

The ERR INT pin, interface error interrupt, is a "0" when any of the three status error bits (timeout, parity error, or BERR) are a "1". It is cleared with a "reset status error" command. Interface errors are only meaningful if the Q22bus adaptor card is the master and uses the I/O cable to send commands to the VME adaptor card. The ERR INT pin can be wire wrapped to any of the five external interrupt lines.

#### DMA DONE INTERRUPT

The DMA DONE interrupt pin is active if the interrupt enable DMA CSR bit is set and a block mode DMA operation has terminated, either successfully or unsuccessfully. It is cleared by a write to the Q22 adaptor card CSR register. The BIT 3 DMA DRIVER software for MicroVAX II applications expects to see the DMA DONE interrupt wired to external interrupt 3, as installed by the factory.

The other pins in the RINT jumper block are not used in the 432 adaptor configuration but are used in other adaptor applications that require this same Q22bus circuit card.

Locate the block of interrupt jumpers (TINT) at location K1 on the Q22bus card. This set of jumpers permits selection of Q22bus interrupt signals to send to the VMEbus.

```

NOT USED

O O NOT USED

NOT USED

O O NOT USED

PT INT

O O NOT USED

NOT USED

o o TO Cable Interrupt 4

FROM QBUS BIRQ7

o o TO Cable Interrupt 3

FROM QBUS BIRQ6 o o TO Cable Interrupt 2

FROM QBUS BIRQ5 o o TO Cable Interrupt 1

o o NOT USED

FROM QBUS BIRQ4

Т

N

I

Т

```

Up to four interrupt lines are available to send interrupts from the Q-bus to the VMEbus. The four lines can be jumpered or wire wrapped to Q22bus interrupt source lines to select which Q22bus interrupts are sent to the VMEbus.

There are three types of interrupts that can be exchanged. See the section on VME adaptor card interrupt jumpers for a description of the three types of interrupts.

The TINT jumper block selects the sources of the three interrupt types.

Interrupts of type 1 (backpanel interrupts) are unique in that none of the four Q-bus interrupt lines BIRQ4-7 can be sent to the VMEbus if there is a Q-bus processor card in the Q-bus chassis. This is because the Q-bus processor card will acknowledge all interrupts on the Q-bus. Also, the Q-bus interrupt lines are encoded so that there is not a unique Q-bus interrupt line for each Q-bus interrupt. These interrupts should only be wired back to the VMEbus if the Q22 adaptor is being used in processor mode (see the section on the Q22 SYST jumper block). To send one of these four interrupt lines back to the VMEbus, wire wrap the Q-bus interrupt pin to one of the four interrupt lines that transmit to the VMEbus. Remove any jumpers that might be on the corresponding interrupt line pins on the VME adaptor card.

The pin at location PT in the interrupt jumper block area is a "O" when the PT interrupt flip-flop on the Q22bus adaptor card (type 2, programmed interrupts) has been set by a processor in the Q22bus chassis. This interrupt can be sent to the VMEbus over one of the four INT lines. The INT line selected to carry this interrupt to the VMEbus cannot also be used to send a Q22bus backpanel interrupt to the VMEbus. Pin PT can be wire wrapped to any of the four interrupt lines that carry interrupts back to the VMEbus.

The following example shows Q22bus interrupt 7 sent to the VMEbus IRQ3 as well as a program generated interrupt (PT) from a Q22bus processor card sent to the VMEbus on line 4.

```

NOT USED

0 0

NOT USED

NOT USED

O O NOT USED

PT INT

o o NOT USED

NOT USED

o to Cable Interrupt 4

FROM QBUS BIRQ7

o--o TO Cable Interrupt 3

FROM QBUS BIRQ6 o o TO Cable Interrupt 2 FROM QBUS BIRQ5 o o TO Cable Interrupt 1

FROM QBUS BIRQ4

O O NOT USED

T

N

I

Т

```

#### EXAMPLE SETTING

# THE QBUS C/D ROW BUS GRANT AND INTERRUPT ACKNOWLEDGE CONTINUITY JUMPERS

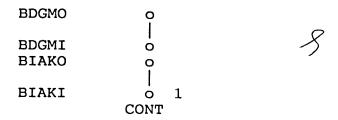

Locate the CONT jumper block at location A8 on the Q22bus adaptor card. These two jumpers insure bus grant and interrupt acknowledge continuity for "downstream" cards on the C/D connectors of Q/Q type backplane slots. If the Q-bus backplane slot is a Q/CD-type, the jumpers should be removed. Either both jumpers are on or both jumpers are off. The factory setting is to have these jumpers installed.

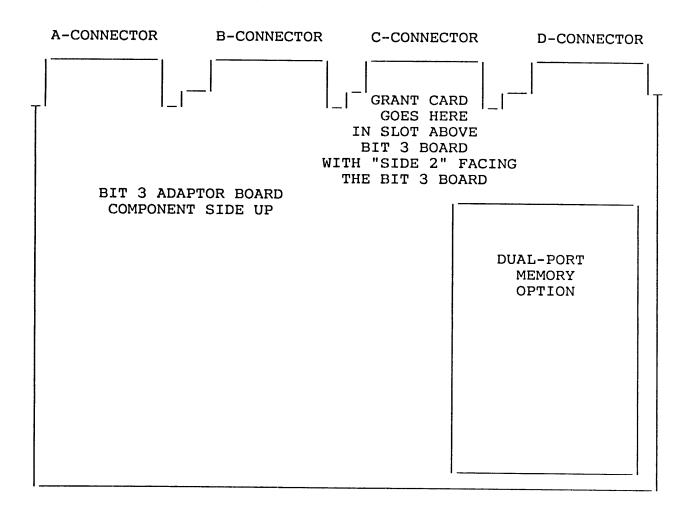

The BIT 3 Q-bus grant continuity card (model 400-801) is a short version of a standard DEC grant card, to be used with BIT 3 Q-bus adaptor boards with the Dual-Port memory option installed. The BIT 3 board requires the space of two Q-bus slots with the dual-port memory installed, and the short grant card allows passage of the bus grant (BDMGI/BDMGO) and interrupt acknowledge (BIAKI/BIAKO) signals on the C-connector of a Q/Q-type backplane slot. The grant card is not required on the C-connector of Q/CD-type backplane slots.

The A-connector and B-connector space in the slot above the BIT 3 board can be filled with a normal-size grant card or any normal dual-height Q-bus card.

# THE Q22bus CARD REM RAM HI and REM RAM LO JUMPERS

Locate the REM RAM HI and LO jumper block at location  ${\tt B5}$  on the Q22bus adaptor card.

The REM RAM LO and HI (for remote bus RAM) jumper settings select the starting address and the address range that a Q22bus master will reference in its address space on the Q22bus when it wants to read or write to the VMEbus. The REM RAM LO jumper block sets the starting Q22bus address and the REM RAM HI selects the ending address. If the range is translated to a different address range on the VMEbus, the starting address should be an integral address multiple of the range selected, starting from address zero. For example, if a 128 Kbyte range is selected, the starting address should be set to a 128K boundary counting up from address zero. The maximum range is 4 megabytes. There cannot be any other Q22bus RAM in the same chassis at the addresses assigned for REM BUS RAM, since there would then be two memories addressed at the same time and neither could work properly.

Q-bus address space in this manual is described using hexidecimal notation. An address in the 4 megabyte address range on the Q22bus can be described as a value between 000000 and 3FFFFF Hex.

Set the REM BUS RAM LO jumpers to the starting address of the first two digits of the 6-digit hex Q22bus 22-bit memory address for the block of memory to be mapped to the VMEbus. Assume that the remaining four digits of the hexidecimal address are all zeros. Set the REMOTE RAM HI jumpers to the first address after the end of the block of memory to be mapped to the VMEbus.

Q22bus address space equal to or greater than the REM RAM LO setting and less than the REM RAM HI setting is mapped to the VMEbus. If you do not want to use the REM BUS RAM function, set the REM RAM HI jumpers to a value less than the REM RAM LO value.

A jumper forms a logic "0" when it is installed (ON in the tables). It forms a logical "1" when it is removed (OFF in the tables).

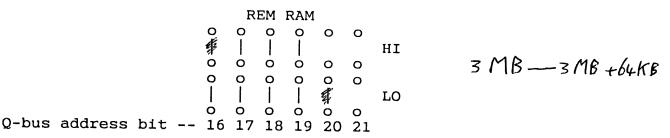

The bit significance of the pins is shown below:

The jumpers are shown for the factory setting of 200000 for the LO address and 300000 for the HI address. With this setting any Q22bus memory reference in the 1 megabyte range from 200000 through 2FFFFF will be mapped to the VMEbus.

# REMOTE BUS RAM FIRST DIGIT VALUE

| A21                    | A20                    | Q22bus | REMOTE | BUS           | RAM | ADDRESS | 1st | DIGIT |

|------------------------|------------------------|--------|--------|---------------|-----|---------|-----|-------|

| ON<br>ON<br>OFF<br>OFF | ON<br>OFF<br>ON<br>OFF |        |        | 0 h<br>1<br>2 | ех  |         |     |       |

# REMOTE BUS RAM SECOND DIGIT VALUE

| A19 | A18 | A17 | A16 | Q22bus REMOTE BUS RAM | ADDRESS 2nd DIGIT |

|-----|-----|-----|-----|-----------------------|-------------------|

| ON  | ON  | ON  | ON  | 0 5                   |                   |

| ON  | ON  | ON  | OFF | 0 hex                 |                   |

| ON  | ON  | OFF | ON  | 2                     |                   |

| ON  | ON  | OFF | OFF | 3                     |                   |

| ON  | OFF | ON  | ON  | 4                     |                   |

| ON  | OFF | ON  | OFF | 5                     |                   |

| ON  | OFF | OFF | ON  | 6                     |                   |

| ON  | OFF | OFF | OFF | 7                     |                   |

| OFF | ON  | ON  | ON  | 8                     |                   |

| OFF | ON  | ON  | OFF | 9                     |                   |

| OFF | ON  | OFF | ON  | Ä                     |                   |

| OFF | ON  | OFF | OFF | В                     |                   |

| OFF | OFF | ON  | ON  | Č                     |                   |

| OFF | OFF | ON  | OFF | D                     |                   |

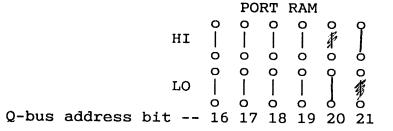

| OFF | OFF | OFF | ON  | E                     |                   |

| OFF | OFF | OFF | OFF | F                     |                   |

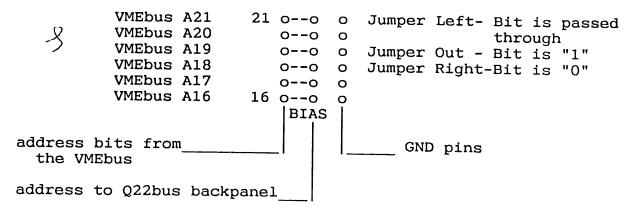

## THE ADDRESS BIAS JUMPERS (BIAS) AT LOCATION B10 (Q22bus CARD)

When a VMEbus processor directly addresses memory in the Q22bus chassis, it does so by using an area in VME address space (REMOTE BUS RAM jumpers on the VME adaptor card) that you have selected. This address is convenient for the VMEbus, but might not be the same as the absolute address that the VME processor wants to use in Q22bus address space.

The ADD BIAS jumpers permit you to offset the VMEbus address into a different address in Q22bus address space.

Be careful not to set the memory mapping jumpers such that a memory address from the first chassis that addresses in the second chassis would map through the second chassis and try to reappear again in the first chassis. This would cause an adaptor conflict and would not work.

NOTE: You can also use the card in page mode where the upper six Q22bus address bits are supplied by an address page register on the Q22bus card. See FUNCTIONAL USE OF THE ADAPTOR.

When the VME device addresses Q22bus RAM, the lower sixteen VMEbus address lines are passed on "as is" to the Q22bus backpanel. This establishes the minimum contiguous block of VMEbus addresses as 65 Kbytes in Q22bus memory. (16 address bits = 65K). You can position this 65K block anywhere in Q22bus address space so long as the Q22bus target address starts on a 65K boundary (from address zero). The jumpers give you three choices for the remaining six high-order Q22bus address lines:

- 1. You can set the Q22bus address bit to a "ZERO".

- 2. You can set the Q22bus address bit to a "ONE".

- 3. You can extend the Q22bus address range by passing more VMEbus address bits to the Q22bus address.

The Q22bus adaptor card is set at the factory to map to the same addresses on the Q-bus as are used on the VMEbus (VME address bits 22 and 23 are stripped off). If you want to re-position the address in Q22bus memory so that it starts at another address, you will have to change the jumpers.

If you connect VME address line A16 to Q22bus address line A16 you can address a 128K Q22bus block. Subsequently connecting VMEbus A17, A18, A19, A20, and A21 to Q22bus ADDRESS lines A17, A18, A19, A20, and A21 permits extending the range to 256K, 512K, 1MEG, 2MEG, and 4MEG.

Once the range has been established, the remaining higher Q22bus address bits must be jumpered to ground or left open to establish the starting address.

A bit left in the open position (i.e., not jumpered to ground or connected to a VMEbus address line) appears as a "ONE" bit in the Q22bus address.

A bit jumpered to one of the ground pins appears as a "zero" in the Q22bus address.

BIAS JUMPER BLOCK AT LOCATION B10

Note: The jumper positions shown are for factory jumper settings with all addresses from the VMEbus wired directly through to the same Q-bus addresses.

The middle row of pins connect through an inverting buffer to drive the Q22bus address lines A16-A21. The right row of pins are all connected to ground. The left row of pins are the adress bits received from the VMEbus.

## THE Q22bus ADAPTOR CARD I/O SELECT JUMPERS

Locate the I/O jumper block at location B9. This jumper block is used to set the start address of the adaptor card in the I/O page. It is used when the Q-bus processor card wants to communicate with the 432 adaptor I/O registers. It is also used to map Q22bus I/O reads and writes into short I/O address space memory reads and writes on the VMEbus.

The Q-bus adaptor uses a minimum of 32 bytes in the I/O page. The first sixteen bytes are used to control the block mode DMA function. The next sixteen bytes are used for miscellaneous bus-to-bus communication control registers -- eight to communicate with the Q-bus adaptor card registers and the next eight to communicate with the VME adaptor card registers.

If the I/O HI address is set higher than the I/O LO address, then Q22bus I/O reads and writes to I/O page address space above I/O LO + 32 and less than the I/O HI jumper setting are converted into short I/O memory reads and writes on the VMEbus at the same

16-bit address on the VMEbus. The address modifier code presented to the VMEbus is 29.

The REMOTE I/O PAGE address range can be increased in 512 byte increments by setting the I/O HI jumper to a higher I/O page address than the I/O LO jumper.