Burroughs 3

# B 1700 Systems Micro Implementation Language (MIL)

REFERENCE MANUAL

PRICED ITEM

Burroughs 3

# B 1700 Systems Micro Implementation Language (MIL)

REFERENCE MANUAL

Copyright © 1977, Burroughs Corporation, Detroit, Michigan 48232

PRICED ITEM

Burroughs believes that the software described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, can be accepted for any consequences arising out of the use of this material, including loss of profit, indirect, special, or consequential damages. There are no warranties which extend beyond the program specification.

The Customer should exercise care to assure that use of the software will be in full compliance with laws, rules, and regulations of the jurisdictions with respect to which it is used.

The information contained herein is subject to change. Revisions may be issued from time to time to advise of changes and/or additions.

# TABLE OF CONTENTS

| Section |                                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | Page        |

|---------|------------------------------------|---------|---|---|---|-----|-----|-----|---|---|-----|---|---|---|---|---|---|---|---|-------------|

|         | INTRODUCTION                       |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | ix          |

|         | Background                         |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | ix          |

|         | Related Documents                  |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | ix          |

| 1       | MICROPROGRAMMING CONCE             | РТС     |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 1-1         |

| 1       | General                            |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 1-1         |

|         | Micro-Instructions                 |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 1-1         |

|         |                                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 1-1         |

|         | Defined Field Concepts             |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 1-1         |

|         | Interpretation of the Virtual Lang | uage    | • | • | • | •   | . : | •   | • | • | • • | • | • | • | • | • | • | ٠ | • | 1-2         |

| 2       | SYNTAX DIAGRAMS                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-1         |

|         | Forward Arrows                     |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-1         |

|         | End of Statement                   |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-1         |

|         | Continuation                       |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-2         |

|         | Keywords                           |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-2         |

|         | Variables                          |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 2-2         |

| 2       | BASIC COMPONENTS OF MIL            |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-1         |

| 3       |                                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   |             |

|         | General                            |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-1         |

|         | Identifiers                        |         | • | • | • | •   |     | •   | • | • |     | • | • | • | • | • | • | • | • | 3-2         |

|         | Labels                             | • , • • | • | • | • | •   |     | •   | • | • |     | • | • | • |   | • | • | • | • | 3-3         |

|         | Card Terminators                   |         |   |   | • |     |     |     |   | • |     | • | • | • |   | • | • | • |   | 3-4         |

|         | Numbers                            |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-5         |

|         | Bit Strings                        |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-5         |

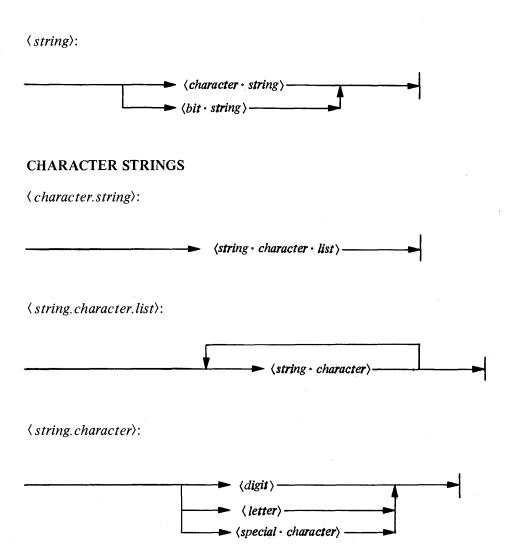

|         | Character Strings                  |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-7         |

|         | Literals                           |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 3-8         |

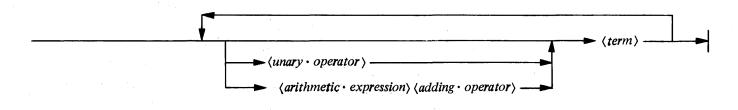

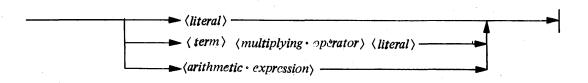

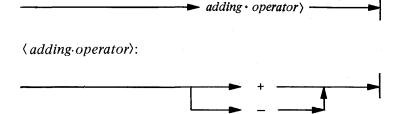

|         | Arithmetic Expressions             |         |   |   |   | •   |     |     |   |   |     |   |   |   |   | • | • | • |   | 3-9         |

| 4       | STRUCTURE OF A MIL PROGR           | AM .    |   |   |   |     |     |     |   |   |     |   |   |   | • |   |   |   |   | 4-1         |

| 5       | SEGMENTATION                       |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 5-1         |

| 3       | Introduction                       |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 5-1         |

|         | Label Addresses                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 5-1         |

|         | Segment Statement                  |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 5-2         |

|         | Code Segment Statement             |         | • | • | • | . • |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 5-2<br>5-3  |

|         | Code.Segment Statement             |         | • | • | • | •   |     | ٠   | • | • | • • | ٠ | • | • | • | • | • | • | • | 5-5         |

|         | Compiler - Generated Code          |         | • | • | ٠ | •   | • • | •   | • | • | • • | • | • | • | • | • | • | • | • | 5-5<br>5-5  |

|         | Main Code Block                    | • • • • | • | • | • | •   | • • | ٠   | • | • |     | • | • | • | • | • | • | • | • |             |

|         | External Code Block                |         | • | • | • | •   | • • | . • | • | • | • • | • | • | • | • | • | • | ٠ | ٠ | 5-6         |

| 6       | DECLARATIONS                       |         |   |   |   | •   |     |     |   |   |     |   |   |   |   |   |   |   |   | 6-1         |

| -       | Data Types                         |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 6-1         |

|         | Declare Statement                  |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 6-1         |

|         | Non-Structured Declarations        |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   | 6-2         |

|         | Structured Declarations            |         |   |   |   |     |     |     |   |   |     |   | - | • | · | Ċ |   |   |   | 6-4         |

|         | Declare Examples                   |         | • | • | • | •   |     | •   | • |   |     | • | • |   |   |   |   |   |   | 6-6         |

|         | Introduction                       |         | • | • | • | •   |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 6-6         |

|         | Non-Remap Items                    |         | • | • | • | •   |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 6-6         |

|         | Remap Items                        |         | • | • | • | •   |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 6-8         |

|         | General                            |         | • | • | • | •   |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 6-8         |

|         | Reverse                            |         | • | • | • | •   |     | •   | • | • | • • | • | • | • | • | • | • | • | • | 6-10        |

|         | 1000150                            |         | • | • | • | •   |     | •   | • | • |     | • | • | • | • | • | • | • | • | 0-10<br>::: |

|         |                                    |         |   |   |   |     |     |     |   |   |     |   |   |   |   |   |   |   |   |             |

| Section | Page                                               |

|---------|----------------------------------------------------|

| 7       | REGISTERS AND SCRATCHPAD                           |

|         | General                                            |

|         | Register Groups                                    |

|         | Alphabetical Listing of Registers and Key Concepts |

|         | Active Registers                                   |

|         | X and Y Registers                                  |

|         | Field (F) Register                                 |

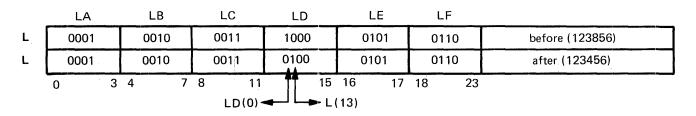

|         | Local (L) Register                                 |

|         | Transform (T) Register                             |

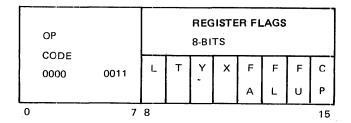

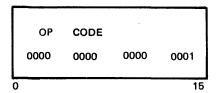

|         | Micro-Instruction (M) Register                     |

|         | Base (BR) and Limit (LR) Registers                 |

|         | Address (A) Register                               |

|         | Address (A) Register                               |

|         |                                                    |

|         |                                                    |

|         |                                                    |

|         | Control (C) Register                               |

|         | Combinatorial Logic or Functional Box              |

|         | Result Registers                                   |

|         | XORY Result Register                               |

|         | XANY Result Register                               |

|         | XEOY Result Register                               |

|         | CMPX Result Register                               |

|         | CMPY Result Register                               |

|         | MSKX Result Register                               |

|         | MSKY Result Register                               |

|         | SUM Result Register                                |

|         | Difference (DIFF) Result Register                  |

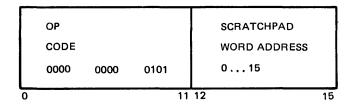

|         | Scratchpad                                         |

|         | Scratchpad Words - 24 Bits Each                    |

|         | Double Scratchpad Words - 48 Bits Each             |

|         | Constant Registers                                 |

|         | Maximum Main Memory (MAXS) Register                |

|         | Maximum Control Memory (MAXM) Register             |

|         | NULL Register                                      |

|         | Input/Output Registers                             |

|         | Console.Switches                                   |

|         | Console Cassette Tape Input (U) Register           |

|         | Command (CMND) Register                            |

|         | Data Register                                      |

|         | Condition Registers                                |

|         | Introduction                                       |

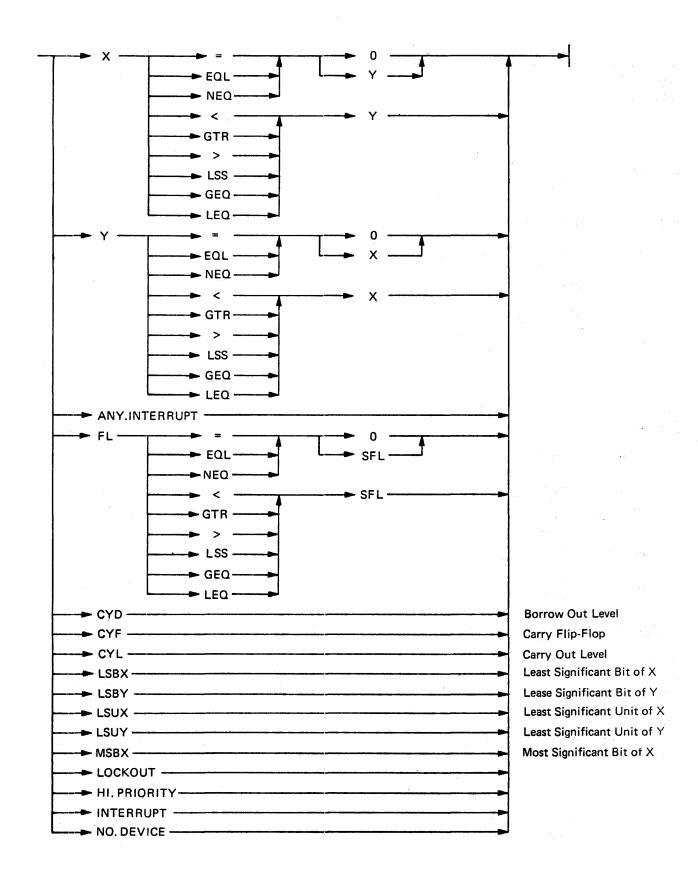

|         | Binary Conditions (BICN) Register                  |

|         |                                                    |

|         | , , , <u>,</u>                                     |

|         | XY States (XYST) Register                          |

|         | Any.Interrupt Bit                                  |

|         | Console Interrupt (CC(3))                          |

|         | Main Memory Read Parity Error Interrupt (CD(0))    |

|         | Main Memory Address Out-of-Bounds Override (CD(1)) |

| Sec | tion |                                                    | Page             |

|-----|------|----------------------------------------------------|------------------|

|     | 7    | REGISTERS AND SCRATCHPAD (Cont)                    |                  |

|     | •    | Read Address Out-of-Bounds Interrupt (CD(2))       | 7-13             |

|     |      | Write/Swap Address Out-of-Bounds Interrupt (CD(3)) |                  |

|     |      | Field Length Conditions (FLCN) Register            | 7-13             |

|     |      | Interment Conditions (INCN) Projector              | 7-13             |

|     |      | Interrupt Conditions (INCN) Register               | . /-13<br>7.14   |

|     |      | Register Designations and Areas of Application     | . 7-14<br>. 7-14 |

|     |      | Organization of Fields and Subfields               | , /-14           |

|     | 8    | MIL STATEMENTS                                     | 8-1              |

|     |      | Index to Statements                                | . 8-1            |

|     |      | ADD Scratchpad                                     | 8-2              |

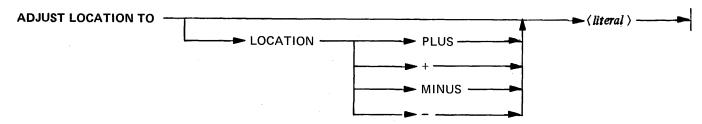

|     |      | ADJUST                                             | 8-3              |

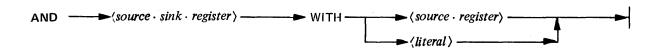

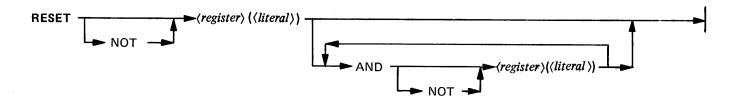

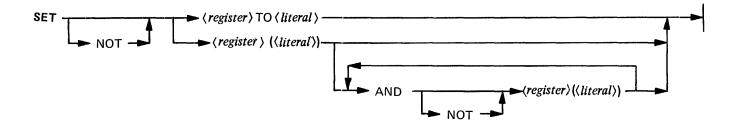

|     |      | AND                                                | 8-4              |

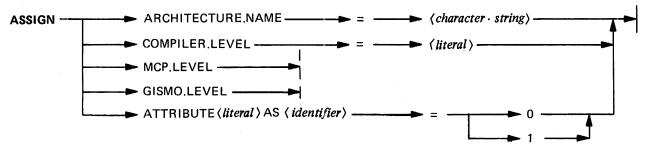

|     |      | ASSIGN                                             |                  |

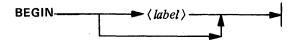

|     |      | BEGIN                                              |                  |

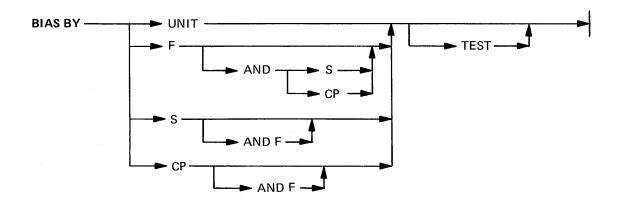

|     |      | BIAS                                               |                  |

|     |      | BRANCH.EXTERNAL                                    |                  |

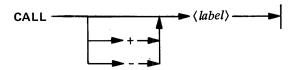

|     |      | CALL                                               |                  |

|     |      | CALL.EXTERNAL                                      |                  |

|     |      |                                                    |                  |

|     |      |                                                    |                  |

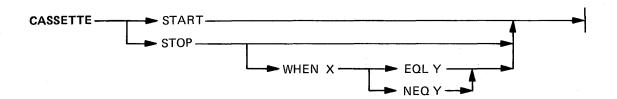

|     |      | CASSETTE                                           |                  |

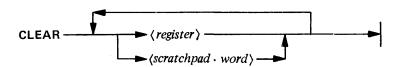

|     |      | CLEAR                                              |                  |

|     |      | CODE.SEGMENT                                       |                  |

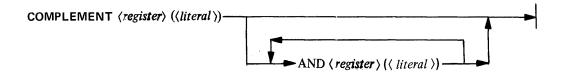

|     |      | COMPLEMENT                                         |                  |

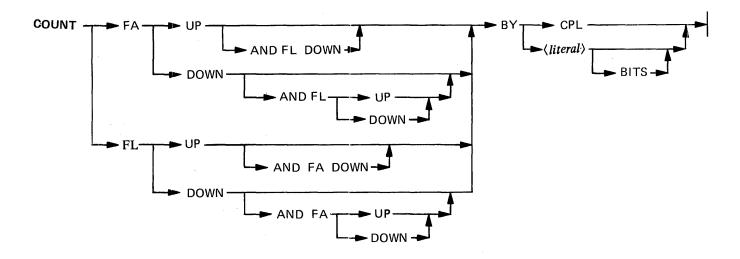

|     |      | COUNT                                              |                  |

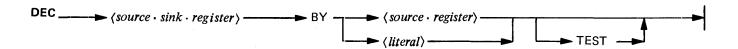

|     |      | <u>DEC</u>                                         |                  |

|     |      | DEFINE                                             |                  |

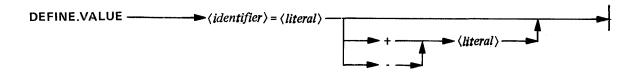

|     |      | DEFINE.VALUE                                       |                  |

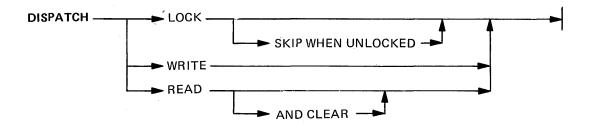

|     |      | DISPATCH                                           |                  |

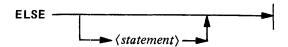

|     |      | ELSE                                               |                  |

|     |      | EMIT.RETURN.TO.EXTERNAL                            | . 8-29           |

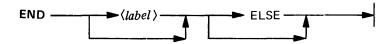

|     |      | END                                                | . 8-30           |

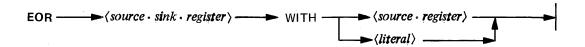

|     |      | EOR                                                | . 8-31           |

|     |      | EXIT                                               | 8-33             |

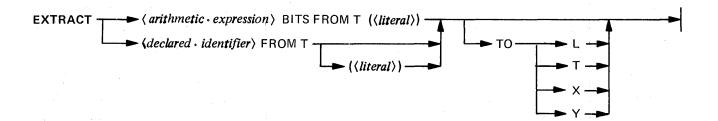

|     |      | EXTRACT                                            | 8-34             |

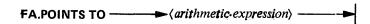

|     |      | FA.POINTS                                          | 8-36             |

|     |      | FINI                                               | . 8-37           |

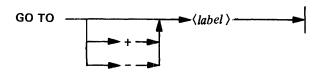

|     |      | GO TO                                              | 0.00             |

|     |      | HALT                                               |                  |

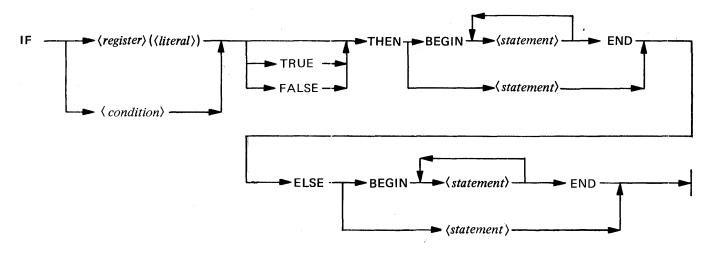

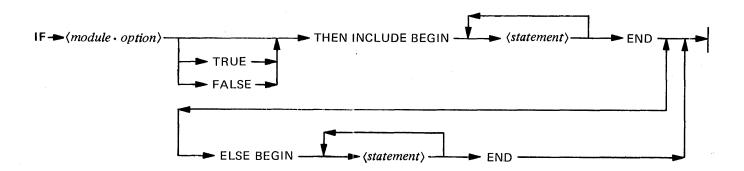

|     |      | IF                                                 |                  |

|     |      |                                                    |                  |

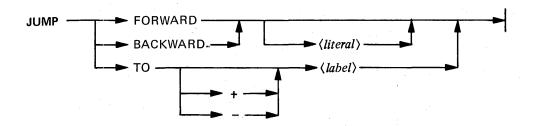

|     |      | JUMP                                               | - 4 <b>-</b>     |

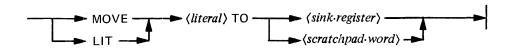

|     |      | LIT                                                | -                |

|     |      |                                                    |                  |

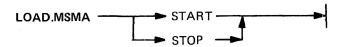

|     |      | LOAD MSMA                                          |                  |

|     |      | LOAD MSMA                                          |                  |

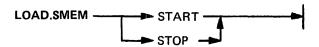

|     |      | LOAD.SMEM                                          |                  |

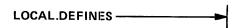

|     |      | LOCAL DEFINES                                      |                  |

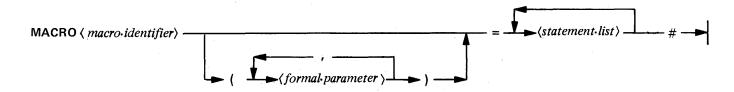

|     |      | MACRO DECLARATION                                  | . 8-55           |

| Section     | +                                                |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | Page |

|-------------|--------------------------------------------------|------------|-----|---|---|---|---|---|---|---|-----|---|---|---|---|---|---|---|---|----|-----|------|

| 8           | MIL STATEMENTS (Cont)                            |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

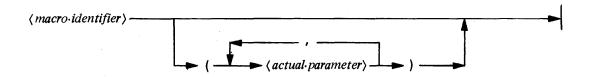

|             | MACRO REFERENCE                                  |            |     |   |   |   |   | • |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-57 |

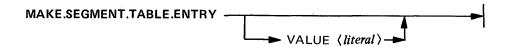

|             | MAKE.SEGMENT.TABLE.EN                            | <b>NTR</b> | ĽΥ  |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-59 |

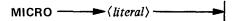

|             | MICRO                                            |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

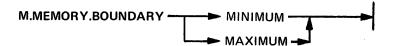

|             | M.MEMORY.BOUNDARY.                               |            |     | - |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-61 |

|             | MONITOR                                          |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

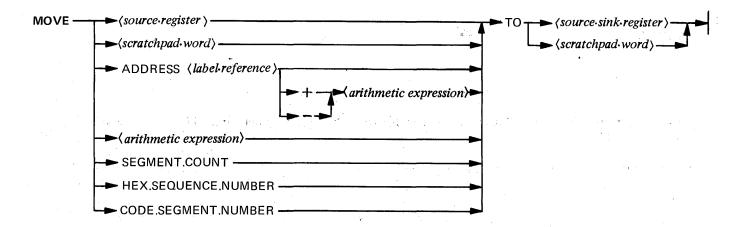

|             | MOVE                                             |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | NOP                                              |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 0    |

|             | NORMALIZE                                        |            |     | - |   | - | - |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

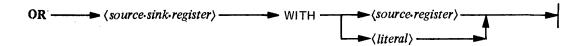

|             | OR                                               |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 0 (- |

|             | OVERLAY                                          |            |     | - | - | - | - |   | - | - |     |   |   |   |   |   |   |   |   |    |     | 0 10 |

|             | PAGE                                             |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 0.70 |

|             | POINT                                            |            | -   | - | - | - | - | - | - | - |     |   |   |   |   |   |   |   |   |    |     | 4    |

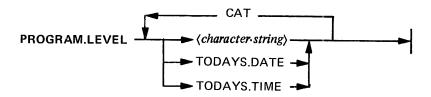

|             | PROGRAM.LEVEL                                    |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-72 |

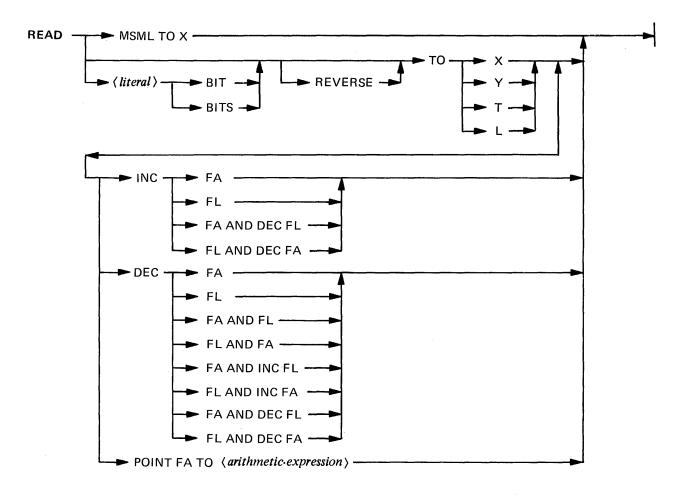

|             | READ                                             |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-73 |

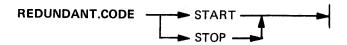

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 8-75 |

|             | RESERVE.SPACE                                    |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   | •  |     | 8-76 |

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   | •. |     | ~ `  |

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 0 70 |

|             | , , , , , , , ,                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    | •   | 8-79 |

|             | SEGMENT                                          |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             |                                                  | •          |     | • | • | • | • | • | • | • |     | • | • | • | • | • | • | • | • | •  |     |      |

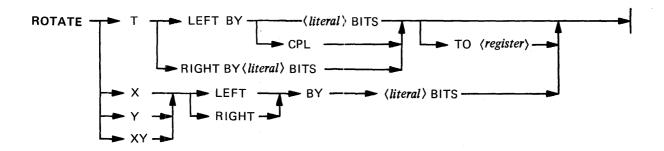

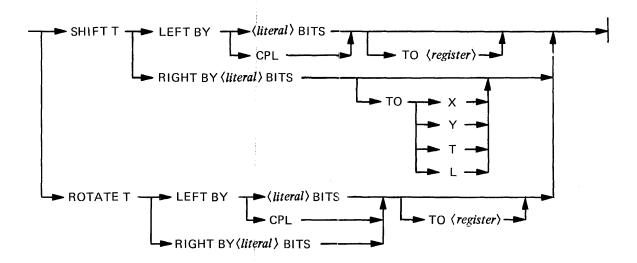

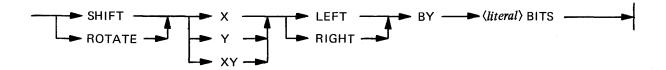

|             | SHIFT/ROTATE X/Y/YX SKIP                         |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    | • • | 8-85 |

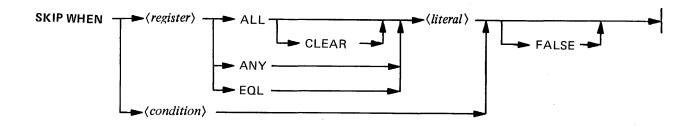

|             | SKIP                                             | •          |     | • | • | • | • | • | • | • | •   | • | • | • | • | • | • | • | • | •  |     | 8-87 |

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    | • • | 8-88 |

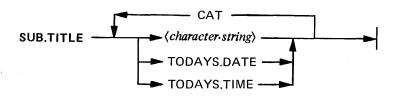

|             | STORE SUB.TITLE                                  | •          |     | • | • | • | • | • | • | • |     | • | • | • |   | • | • | • | • | •  |     | 8-89 |

|             | SUBTRACT SCRATCHPAD                              | •          |     | • | • | • | • | • | • | • |     | • | • | • | • | • | • | • | • | •  |     | 8-90 |

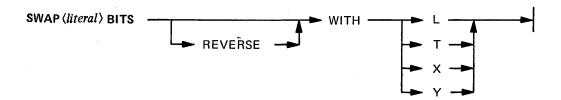

|             | SWAP                                             |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   | • | •  |     | 8-91 |

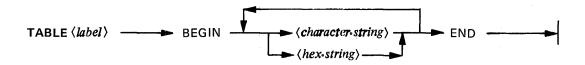

|             | TABLE                                            |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   | •  |     |      |

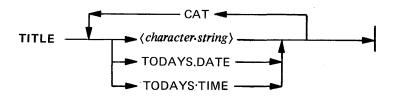

|             | TITLE                                            |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | TRANSFER.CONTROL                                 | •          | • • | ٠ | • | • | • | • | • | • | • • | • | • | ٠ | • | • | • | • | • | •  |     |      |

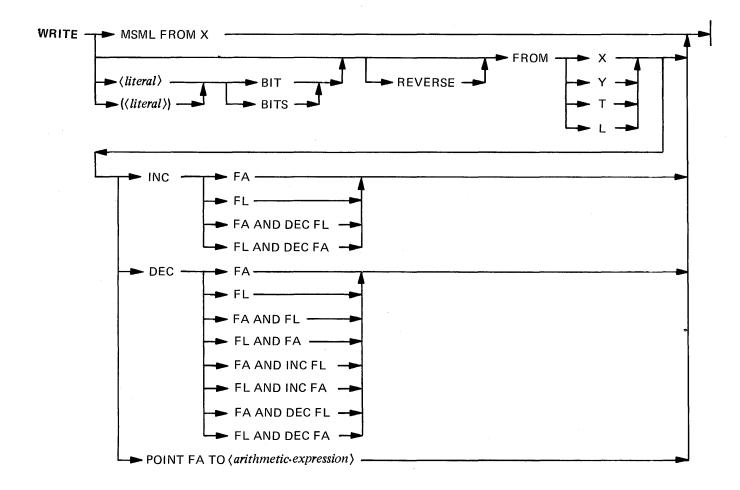

|             | WRITE                                            |            |     | - | - | - | • | - | - | - |     | - | - | - |   |   |   |   |   |    |     |      |

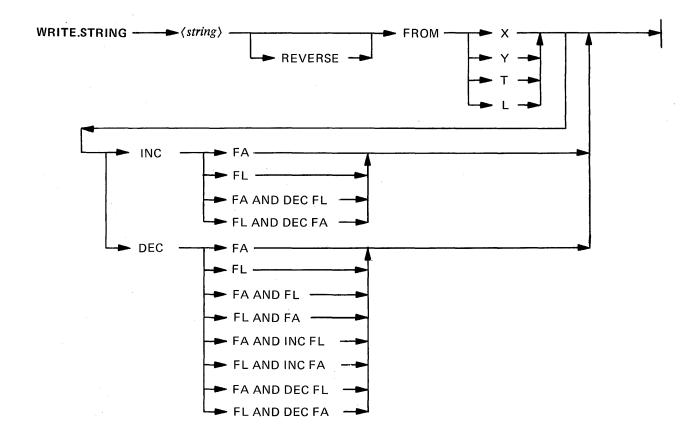

|             | WRITE.STRING                                     |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | XCH                                              | •          |     | • | • | • | • | • | • | • |     | • | • | • | • | • | • | • | • | •  |     | 0.77 |

| 9           | PROGRAMMING TECHNIQU                             | IEC        |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | 9-1  |

| 9           |                                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | Virtual-Langauge Definitions Source Image Format |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | _                                                |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | Program Example                                  | •          |     | • | • | • | • | • | • | • |     | • | • | • | • | • | • | • | • | •  | •   | 9-1  |

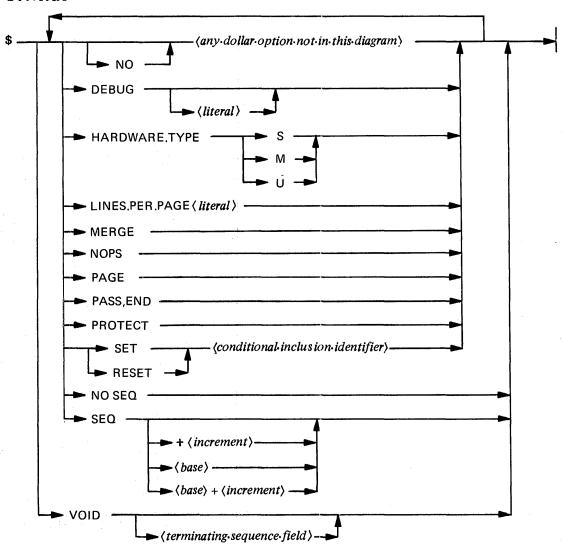

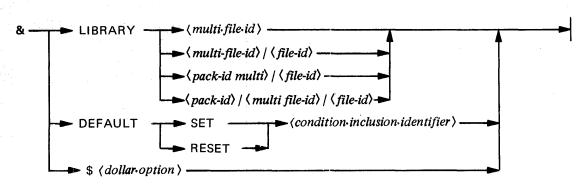

| Appendix A  | MIL COMPILER OPERATI                             | ION        | I   |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     | A-1  |

| 1 pponuix A | Control Cards                                    |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | General                                          |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | Dollar Cards                                     |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

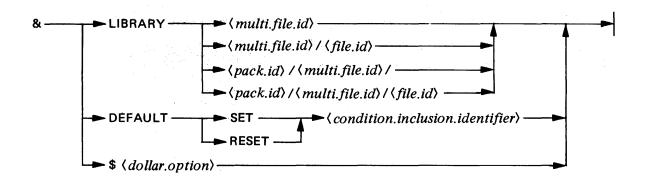

|             | Ampersand Cards                                  |            |     |   |   |   |   |   |   |   |     |   |   |   |   |   |   |   |   |    |     |      |

|             | MIL Compiler Files                               | •          |     | • | • | • | • | • | • | • |     | • | • | • | • | • | • | • | • | •  | •   | A-6  |

| Appendix B | HARDWARE INSTRUCTION FORMATS AND TABLES | B-1         |

|------------|-----------------------------------------|-------------|

|            | B 1700 Hardware Tables                  | B-1         |

|            | B 1700 Hardware Instruction Formats     | B-5         |

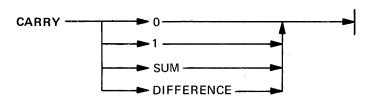

|            | Blas                                    | B-5         |

|            | Bias                                    | B-5         |

|            | Bit lest Branch Irue                    | B-6         |

|            | Branch                                  | B-6         |

|            | Call                                    | B-′         |

|            | Cassette Control                        | B-          |

|            | Clear Registers                         | B-8         |

|            | Count FA/FL                             | B-8         |

|            | Dispatch                                | B-9         |

|            | Extract From T                          | B-10        |

|            | Four-Bit Manipulate                     | B-10        |

|            | Halt                                    | B-1         |

|            | Load F From Doublepad Word              | B-1         |

|            | Monitor                                 | B-12        |

|            | Move 8-Bit Literal                      | B-12        |

|            | Move 24-Bit Literal                     | B-1.        |

|            | No Operation                            | B-13        |

|            | Normalize X                             | B-13        |

|            | Overlay Control Memory                  | B-14        |

|            | Read/Write Memory                       | B-14        |

|            | Read/Write MSM                          | B-1:        |

|            | Register Move                           | B-16        |

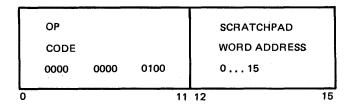

|            | Scratchnad Move                         | B-1'        |

|            | Register Move                           | B-1'        |

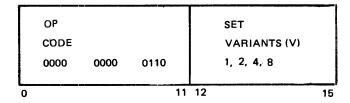

|            | Set CYF                                 | B-18        |

|            | Shift/Rotate T Left                     | B-18        |

|            | Shift/Rotate XY Left/Right              | B-19        |

|            | Shift/Rotate X/Y Left/Right             | B-20        |

|            | Silit/ Rotate A/ 1 Lett/ Right          | B-20        |

|            | Skip When                               | B-20        |

|            | Store F Into Doublepad Word             |             |

|            | Swap F with Doublepad Word              | B-22        |

|            | Swap Memory                             | B-22        |

|            | Transfer Control                        | B-23        |

|            | Micro-Instruction Timing                | B-24        |

|            | B 1710 Notes                            | B-2:        |

|            | B 1720 Notes                            | B-2:        |

| Appendix C | RESERVED WORDS AND SYMBOLS              | <b>C</b> -3 |

| Index      |                                         | <b>I_</b> 1 |

# LIST OF TABLES

| Table |                        |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | Page |

|-------|------------------------|------|---|--|--|--|--|--|---|--|--|--|---|--|--|--|------|

| 8-1   | AND Truth Table .      |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | 8-4  |

| 8-2   | EOR Truth Table .      |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  |      |

| 8-3   | OR Truth Table         |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | 8-67 |

| 8-4   | String Definitions .   |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | 8-97 |

| B-1   | Register Addressing    |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | B-1  |

| B-2   | Condition Registers    |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  | B-2  |

| B-3   | Microinstructions .    |      |   |  |  |  |  |  |   |  |  |  | • |  |  |  | B-3  |

| B-4   | Variant Field Definiti |      |   |  |  |  |  |  |   |  |  |  |   |  |  |  |      |

| B-5   | Micro-Instruction Tin  | ning | 3 |  |  |  |  |  | • |  |  |  |   |  |  |  | B-24 |

# INTRODUCTION

# **BACKGROUND**

The Burroughs Micro Implementation Language (MIL) is a symbolic coding technique that makes available all the capabilities of the B 1700 Processor. The MIL compiler's machine language output is ready for execution directly upon the hardware. The user, however, must be prepared to programmatically control the total environment including bootstrap loading, interrupt servicing, and potential machine malfunctioning (e.g., parity error detection).

To use MIL properly and efficiently, the programmer must have an extensive knowledge of the available registers and their capabilities. This manual describes the registers, the syntax and the semantics of the MIL language and may be used to write programs without prior knowledge of the system.

# RELATED DOCUMENTS

A description of the Input/Output subsystem and the I/O descriptors as well as more detailed information about the registers can be found in the B 1700 Systems Reference Manual (form 1057155).

### 1. MICROPROGRAMMING CONCEPTS

### GENERAL

Microprogramming is a method for programming a computer hardware architecture. The microprogrammer is concerned with machine registers which were formerly the domain of the hardware systems designer. Strings of micro-instructions manipulate those internal registers to present an outward appearance of system hardware which is more functional for problem-oriented programming. In most machines now in the market place, read-only memories (ROM's) contain microprograms which convert the unique internal environment of several different processors into a standard assembly language. Once created, the microprograms are unalterable and may contain compromises in efficiency because of a limited hardware instruction set.

The Burroughs B 1700 system makes use of the latest technology to implement a writable control memory and has several microprograms, each optimized for the functions it will perform. The virtual system architectures chosen have been those of the standard (such as COBOL and FORTRAN), problem-oriented, compiler languages. Other microprogrammers may choose architectures and create languages optimized for other purposes.

### **MICRO-INSTRUCTIONS**

A micro-instruction is the smallest programmable operation within the system. Each micro-instruction is fetched from memory and decoded in the (micro) register to be directly executed by the hardware.

### **DEFINED FIELD CONCEPTS**

A defined field concept allows bit-level data addressing with lengths from 1 to 65,535 bits. There are no visible boundaries or "best" container size for any information contained in main memory. Virtual machine instruction strings (the B 1700 analog of machine object code) and their data may thus be densely packed into meaningful fields, saving considerable memory space. The programming problem of packing and unpacking data fields across hardware container boundaries is completely resolved, saving much programming effort and processor time. The microprogram fetches groups of bits in meaningful field sizes from anywhere in main memory as needed.

Special hardware, called a Field Isolation Unit, has been implemented to achieve bit addressability and variable length fields and to automatically increment addresses. This allows maximum flexibility in defining data fields and resolves the problem of packing and unpacking data fields across hardware container boundaries.

# INTERPRETATION OF THE VIRTUAL LANGUAGE

The traditional approach to supporting a higher-level language is to translate the source statements as written by the programmer into another language either directly recognized by the hardware, (e.g., machine object code) or easily translatable into the machine object code (e.g., an assembly language). An alternate technique is the interpretive execution for each source statement with a logically equivalent routine in some lower-level language. A microprogrammed system offers the opportunity to combine the best of both methods. The source statements in the higher-level language are translated into a virtual system code by a compilation process. This system code, also called S-code or S-language, very closely resembles the original source language. Micro-instruction routines then interpretively execute each virtual language statement. The results are:

- a. Faster compilation,

- b. System architecture, as expressed in the set of microroutines, which is optimized to the source language,

- c. Reduction in the processor time required to perform the logical equivalent of each source statement,

- d. Reduction in the memory space required to encode each source language operation.

A set of microprogrammed routines is called an interpreter and effectively creates a virtual system architecture for the source language being executed. That is, when the COBOL interpreter is executing, the system is effectively a COBOL machine. When the FORTRAN interpreter is executing, the system is a FORTRAN machine, and so on for any other S-language defined.

# 2. SYNTAX DIAGRAMS

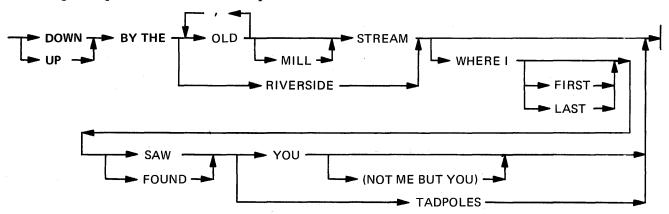

The principal means of describing MIL syntax is through the syntax diagram, commonly known as "rail-road" notation. The basic conventions are discussed below.

# FORWARD ARROWS

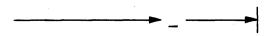

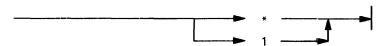

Any path traced along the directional flow of the arrows will produce a syntactically valid command. The following example illustrates the technique:

Valid syntax generated from this diagram could be:

DOWN BY THE OLD MILL STREAM

UP BY THE OLD, OLD STREAM

DOWN BY THE RIVERSIDE WHERE I FOUND TADPOLES

DOWN BY THE OLD STREAM WHERE I FIRST SAW YOU (NOT ME BUT YOU)

UP BY THE RIVERSIDE WHERE I LAST FOUND YOU

The bridge over OLD, unless otherwise specified, can be crossed any number of times.

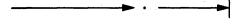

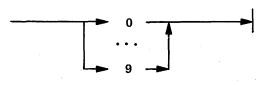

# **END OF STATEMENT**

The completion of a statement is indicated by the following convention:

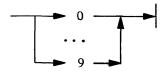

# **CONTINUATION**

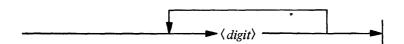

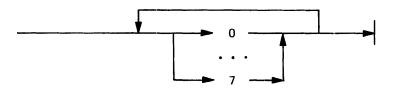

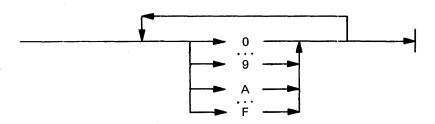

The following convention indicates that any number from 0 through 9 is syntactically valid:

# **KEYWORDS**

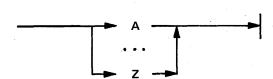

Upper-case letters indicate keywords which must literally appear in MIL statements.

# **VARIABLES**

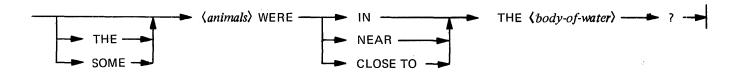

Lower-case letters, words, and phrases within angle brackets indicate syntactic variables which require information to be supplied by the programmer. The following example illustrates the technique:

Valid syntax generated from this diagram might be:

THE TADPOLES WERE IN THE STREAM? COWS WERE CLOSE TO THE POND? SOME BIRDS WERE NEAR THE OCEAN?

# 3. BASIC COMPONENTS OF MIL

# **GENERAL**

$\langle point \rangle$ :

To understand MIL grammar the user should be familiar with the following basic elements of the MIL language.

⟨underscore⟩:

$\langle digit \rangle$ :

⟨letter⟩:

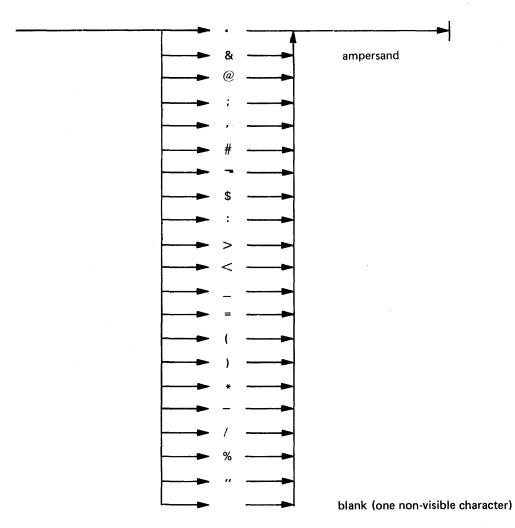

# $\label{eq:special.characters} \ \langle \ special.characters \rangle :$

# **IDENTIFIERS**

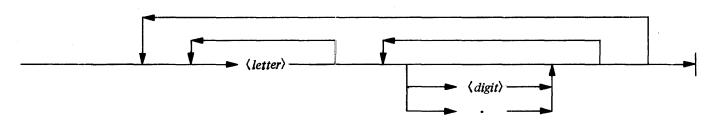

# ⟨identifier⟩:

# **RESTRICTIONS**

- 1. An \(\(\delta\) identifier\(\rangle\) must begin with a \(\left\) letter\(\rangle\).

- 2. An \(\langle identifier \rangle\) may not contain blanks.

- 3. Reserved words may not be used as (identifiers). (See Appendix C: Reserved Words and Symbols.)

- 4. An (identifier) is limited to a maximum of 63 characters: only the first 25 characters are used in uniqueness detection.

# Examples

TEST.NAME.1 T.123.Q ABC LOOP...12

# **LABELS**

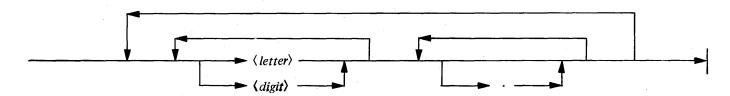

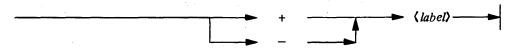

⟨ label⟩:

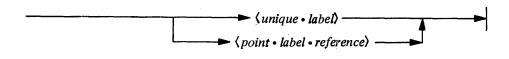

⟨unique.label⟩:

⟨point.label.declaration⟩:

⟨point.label.reference⟩:

# ⟨label.reference⟩:

⟨label.declaration⟩:

⟨ Labels⟩s may be declared by: (1) starting the ⟨ label⟩ anywhere in columns 1 through 5 of a source image, or (2) starting the ⟨ label⟩ immediately after the reserved words TABLE, SEGMENT, or CODE.SEGMENT. (See also Segmentation: Label addresses.)

# RESTRICTIONS

- 1. A  $\langle label \rangle$  must begin with a  $\langle letter \rangle$  or a  $\langle digit \rangle$

- 2. A (label) may not contain blanks.

- 3. A \(\lambda\) is limited to a maximum of 63 characters: only the first 25 characters are used in uniqueness detection.

- 4. \(\langle Unique Label\rangle\)s may be declared only once.

- 5. \(\langle Point Label \rangle \)s may or may not be unique.

# Examples

.A.POINT.LABEL REGULAR.LABEL LOOP BEGINNING.OF.TEST.1

# **CARD TERMINATORS**

⟨ card.terminator⟩:

# RESTRICTION

A percent sign (%) is treated as any other string character if it is contained within a \( \character string \)\). However, in all other cases, a \( \% \) will cause the scanning of the current source image to terminate.

# **NUMBERS**

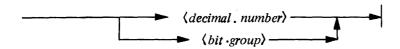

$\langle number \rangle$ :

⟨decimal·number⟩:

# **BIT STRINGS**

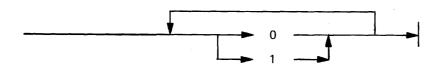

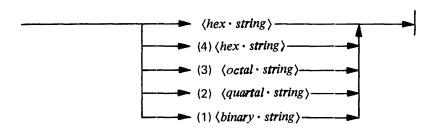

⟨binary·string⟩:

⟨quartal·string⟩:

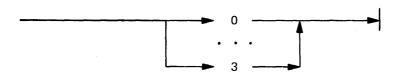

# ⟨octal·string⟩:

# ⟨ hex·string⟩:

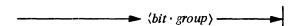

# ⟨bit.group⟩:

# ⟨bit·string⟩:

# RESTRICTION

If no bit mode is specified (i.e., the indicator digit in parentheses is omitted), then "hex" is assumed.

# **Examples**

- "\*\* THIS IS AN EXAMPLE OF A CHARACTER STRING"

- " ROW THE BOAT GENTLY . . . "

# RESTRICTION

The quotation mark (") cannot be specified as a \( \string \character \). As an alternative, the programmer can specify a \( \lambda \text{hex string} \rangle \) instead of a \( \lambda \text{character.string} \rangle \).

**LITERALS** ⟨literal⟩: **►** ⟨numbe**r**⟩ − - ⟨declare · special⟩ -► ⟨declared · identifier⟩ -⟨ declare special⟩: ► DATA.LENGTH \(\langle declared \cdot identifier \rangle -\) LENGTH BETWEEN ENTRIES ((array · identifier)) -⟨ declared identifier⟩: ► ⟨simple · identifier⟩ – **►** ⟨array · identifier⟩ — ⟨array identifier⟩: → ⟨simple · identifier⟩ → ⟨array · index⟩ →  $\langle array \cdot index \rangle$ :

DATA LENGTH (\(\langle declared \cdot identifier \rangle\) will supply the specified or computed length in bits of the indicated \(\langle \text{declared identifier} \rangle.\) For an \(\langle \text{array identifier} \rangle,\) the length will be the length of one of the items in the array, not the length of the entire array.

(number) -

LENGTH BETWEEN ENTRIES ((array identifier)) will supply the bit difference between the beginning of one item in the specified array and the next item in the array. Note that in the case of structured arrays (See Structured Declarations) this will not always be the same as DATA LENGTH (array identifier).

# **Examples:**

1587

"STRING"

DATA LENGTH (AN ITEM)

ARRAY ELEMENT (7)

# **ARITHMETIC EXPRESSIONS**

$\langle arithmetic \cdot expression \rangle$ :

⟨ term⟩:

⟨unary operator⟩:

# ⟨multiplying operator⟩:

(Arithmetic expression)s yield numerical values by combining (literal)s in accordance with specified operations. The operators +, -, \*, and / have the conventional mathematical meanings of addition, subtraction, multiplication, and division, respectively.

The sequence in which operations are performed is determined by the precedence of the operators involved. The order of precedence is:

When operators have the same order of precedence, the sequence of operation is determined by the order of their appearance, from left to right. Parentheses can be used in normal mathematical fashion to override the usual order of precedence.

Parenthesized expressions are treated as  $\langle term \rangle$ s, i.e., they are evaluated by themselves and the resulting value is subsequently combined with the other elements of the  $\langle arithmetic expression \rangle$ . Thus the normal precedence of operators may be overridden by careful placement of parentheses.

# 4. STRUCTURE OF A MIL PROGRAM

There are two parts or sections to a MIL program: the declarations and the body. The declarations should contain:

- a. A comment description of the function of the MIL program.

- b. Any global data structures (DECLARES). Note that "global" refers to use throughout the program; local refers to use restricted to a part of the program.

- c. Any global DEFINEs.

- d. Any MACRO definitions.

The body follows the declarations and will contain all code-producing statements. The statements should be logically grouped in labeled BEGIN . . . END blocks. Each BEGIN . . . END block may contain its own local data structures, LOCAL.DEFINES or labels. The last statement of the body should be FINI.

The following is a basic outline of a MIL program using the above general rules. For specific details on assembly coding forms and program examples refer to: Programming Techniques.

Declarations

% descriptive comment DECLARES DEFINES MACROS

LABEL.A

BEGIN A

(code for A)

END A

BEGIN B

(code for B)

END B

**FINI**

Body

### 5. SEGMENTATION

### INTRODUCTION

Segmentation in MIL is a multi-faceted and somewhat complicated subject. Because MIL is the language of the B 1700's, and because it is used for many different purposes (Diagnostics, Emulators, Interpreters, I/O Drivers, MCP Kernels, etc.), it must attempt to satisfy the needs of a wide range of users. Segmentation plays a particularly important role on the B 1700 because of the READ/WRITE access capability of the hierarchical memory structure (M-Memory, S-Memory, Disk).

# LABEL ADDRESSES

To begin the discussion on segmentation, we must first identify the label types pertaining to address assignment. They are:  $\langle regular.label \rangle$  and  $\langle physical.label \rangle$ . (These should not be confused with the two types of label representation: $\langle unique.label \rangle$  and  $\langle point.label \rangle$ . See Basic Components Of MIL: Labels.) The types are based on how the labels are declared which in turn determines how the address of the label is to be assigned.

A \(\lambda \lambda \lambda bel\) which is declared by starting it in column 1-5 of a source image is always a \(\lambda \text{regular.label}\).

A \(\lambda \lambda \lambda \lambda \lambda \lambda \text{label}\rangle\) which is declared by starting it immediately after the reserved words TABLE, SEGMENT, or CODE.SEGMENT is always a \(\lambda \text{physical.label}\rangle\).

A  $\langle regular, label \rangle$  is always given the current  $\langle segment, code, address \rangle$  when the  $\langle label \rangle$  is declared.

A  $\langle physical, label \rangle$  is always given the current  $\langle physical, code, address \rangle$  when the  $\langle label \rangle$  is declared.

The (segment.code.address) is updated by 16 as each micro-instruction is generated and can be changed to a new value by the appearance of a SEGMENT or CODE.SEGMENT statement.

The (physical code address) is also updated by 16 as each micro-instruction is generated and can be changed to a new value by the appearance of an ADJUST LOCATION statement. (See MIL Statements: ADJUST).

Both the  $\langle physical.code.address \rangle$  and the  $\langle segment.code.address \rangle$  are initialized to 0 (zero) when a compilation begins.

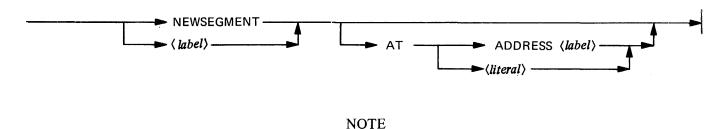

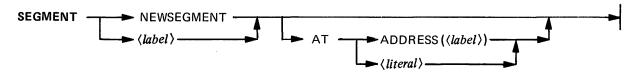

### SEGMENT STATEMENT

# Syntax.

The  $\langle literal \rangle$  must be MOD 16, meaning the last four bits must be @ (1) 0000 @.

### **Semantics**

Through the use of the SEGMENT statement, the user has the means to divide his/her MIL program into several parts such as a single  $\langle primary.code.block \rangle$  and one or more  $\langle segment.block \rangle$  (s). The  $\langle primary.code.block \rangle$  should provide one or more areas suitable for containing the individual  $\langle segment.block \rangle$  (s). These areas are designated by declaring one or more  $\langle regular.label \rangle$ (s) somewhere within the  $\langle primary.code.block \rangle$ . Quite often there will be only one designated area for  $\langle segment.block \rangle$ (s), and it will begin at the end of the  $\langle primary.code.block \rangle$ .

The purpose of the SEGMENT statement is to inform the compiler exactly where the  $\langle segment.block \rangle$  will be (relative to the  $\langle primary.code.block \rangle$ ) when its code is executed. In this way the compiler can generate the correct branch/call displacements whenever a statement in the  $\langle primary.code.block \rangle$  branches to or calls a routine in one of the  $\langle segment.block \rangle$ (s). In the same way, a statement in one of the  $\langle segment.block \rangle$ (s) may branch to or call a routine in either the  $\langle primary.code.block \rangle$  or in any of the  $\langle segment.block \rangle$ (s). (See MIL Statements: EMIT.RETURN.TO.EXTERNAL, CALL.EXTERNAL, BRANCH. EXTERNAL.)

All code is assumed to be in the \( \) primary.code.block\\ until the first SEGMENT statement is encountered. From this point one, all code is assumed to be in that segment until the next SEGMENT statement is encountered, and so on.

The SEGMENT statement may also be used to specify logical breaks within a continuous stream of code. In this case, only the name of the segment needs to be specified since the code addresses are to continue linearly. The entire program and all of the (segment.block)(s) are given entries in the segment dictionaries as part of the parameter blocks associated with a MIL code file. From these dictionary entries and from the segment name-to-number correspondence table the addresses and lengths of each segment are available and can be used to do sophisticated static binding prior to execution of the code. (See MIL Statements: MAKE.SEGMENT, TABLE.ENTRY).

# CODE.SEGMENT STATEMENT

### **Syntax**

### Semantics

Another form of segmentation in MIL is used when a microprogram is running with the MCP, or under MCP control. All of the interpreters as well as GISMO are examples of this situation. With this mechanism, a microprogrammer is able to specify which portions of the program are to reside on disk until they are actually needed for execution. This provides the programmer with the same facility normally only found in higher level languages.

In order to use this facility, the programmer must follow certain rules and remember some restrictions. First, some definitions:

(main.code.block): all code generated until the first CODE.SEGMENT statement is

encountered; this may encompass the \( \text{primary.code.block} \) and

one or more  $\langle segment.block \rangle$ (s).

⟨external.code.block⟩: all code generated between a given CODE.SEGMENT statement

and the next CODE.SEGMENT statement, or the end of the

program, whichever comes first.

(main.code.base): the M-Memory bit address of the first micro-instruction in the

$\langle main.code.block \rangle$ . If no part of the  $\langle main.code.block \rangle$  resides

in M-Memory, then the \( \text{main.code.base} \) should be 0.

If the processor is an S-Memory processor, then the (main.code.base) should be the memory address of the first micro-instruction in the

program. (See MIL Statements: MAIN.CODE.BASE.)

(mbr,topm): a 24-bit bucket containing the MBR value for the (main.code.block).

In addition, since the MBR value is always a MOD 16 number, the low

order 4 bits of \( mbr, topm \) should be the TOPM value of the

$\langle main.code.block \rangle$ .

The microprogrammer must provide the following items in a program:

a. A define for MAIN.CODE.BASE to indicate the Scratchpad word containing (main.code.base).

# Example:

DEFINE MAIN.CODE.BASE = \$14B#

b. A define for MBR.TOPM to indicate the Scratchpad word containing (mbr.topm).

# Example:

DEFINE MBR. TOPM = S15A

# NOTE

The above defines must be included in the \( \text{main.code.} \)

block\( \) and must not be defined within some LOCAL.

DEFINE scope. In addition, the two Scratchpad locations must be initialized by the interpreter when it is given control from GISMO.

c. A routine labeled GO.TO.EXTERNAL.SEGMENT to interrogate the interpreter dictionary and generate a communicate (if necessary) to guarantee that the requested \( \lambda external.code.segment \) is present in S-Memory. In addition, it must perform the initial transfer to the \( \lambda external.code.segment \).

# Example:

```

GO.TO.EXTERNAL.SEGMENT

% T CONTAINS SEGMENT NUMBER

% L CONTAINS BIT DISPLACEMENT WITHIN SEGMENT

SHIFT T LEFT BY 6 BITS TO X

% T * 64

SHIFT T LEFT BY 4 BITS TO Y

% T * 16

MOVE SUM TO FA

% T * 80

ADD ADDR.INTERP.SEG.DICT TO FA

READ 2 BITS TO X

IF LSUX THEN

% THE SEGMENT IS PRESENT

BEGIN PRESENT

COUNT FA UP BY 32

READ 24 BITS TO X

% SEGMENT BASE ADDRESS

IF SUBSET THEN INCLUDE % FOR S-MEMORY PROCESSORS

BEGIN

MOVE L TO Y

MOVE SUM TO A

END ELSE

BEGIN

MOVE 0 TO TAS

% NECESSARY FOR

% M-MEMORY SYSTEM

MOVE L TO T

% NEW A AND TOPM VALUE

MOVE X TO L

% NEW MBR VALUE

TRANSFER.CONTROL

END

END PRESENT

MOVE T TO L

MOVE 58 TO T

% COMMUNICATE NO.FOR

% NON PRESENT SEGMENT

SHIFT T LEFT BY 16 BITS

SET L(0)

% ONE LEVEL SEG DICT.

GO TO GIVE.UP.CONTROL.

% SAVE STATE AND XFER TO

% MCP VIA GISMO

```

### **NOTES**

- a. The initial "T" and "L" values are supplied by the compiler prior to entering the above routine.

- b. Other registers may be destroyed depending on how the routine is written.

- c. The routine must push a 0 (zero) onto the A stack for the M-Memory Processor. This is necessary so that an exit within an \( \langle external.code.block \rangle \) can be trapped into a routine that will transfer control back to the \( \langle main.code.block \rangle \). This also implies that parameters may not be passed via the A stack when initially transferring to an \( \langle external.code.block \rangle \).

The compiler will provide all other routines necessary to effect the transfer to and from  $\langle external.code.block\rangle(s)$ .

The only kind of transfers allowed are calls and branches from the \( \text{main.code.block} \) to an \( \text{external.code.} \) block\( \) and from an \( \text{external.code.block} \) to the \( \text{main.code.block} \). Transfers between \( \text{external.code.} \) block\( \text{o} \) are not allowed. In addition, such calls and branches must be syntactically separated from calls and branches with the same \( \text{code.block} \). Instead of CALL, the command CALL EXTERNAL must be used. Instead of GO TO, the command BRANCH.EXTERNAL must be used. (See MIL statements: EMIT. RETURN.TO.EXTERNAL, CALL.EXTERNAL and BRANCH.EXTERNAL.)

# Compiler - Generated Code

Following is the code the compiler generates when CODE.SEGMENTs are used. (All \( label \) s used in the examples are shown for clarity only: the compiler has its own internal representation for the labels.)

# MAIN CODE BLOCK

a. For each different \( \lambda label \rangle \) occurring after a CALL.EXTERNAL or BRANCH.EXTERNAL statement in the \( \lambda main.code.block \rangle \), the compiler will divert the call or branch to the following code which is generated at the end of, and part of, the \( \lambda main.code.block \rangle : \)

MOVE ADDRESS (label) TO L MOVE (label.segment.number) TO T GO TO GO.TO.EXTERNAL.SEGMENT

b. If the program executes on an M-Memory Processor (B 1726), the following code will be emitted in the main.code.block:

EXIT.TO.EXTERNAL

MOVE TAS TO L

MOVE TAS TO T

MOVE LF TO TF

MOVE 0 TO LF

TRANSFER.CONTROL

# EXTERNAL CODE BLOCK

a. If the program executes on an M-Memory Processor (B 1726), the following code will be emitted at the beginning of every (external.code.block):

MOVE TAS TO T

LEAVE.EXTERNAL.SEGMENT

MOVE MBR TOPM TO L

MOVE LF TO T

SET LF TO 0

TRANSFER.CONTROL

- b. For each different \( \lambda \lambda block \rangle \) occurring after a CALL.EXTERNAL or BRANCH.EXTERNAL statement in the \( \lambda \) external code \( block \rangle \), the compiler will divert the call or branch to the following code which is generated at the end of, and part of, the \( \lambda \) external \( code \) \( block \rangle \):

- 1. If the program executes on an S-Memory PRocessor (B 1712 B 1714) the following code is generated:

MOVE ADDRESS (( label)) TO X GO TO SUBSET.BRANCH.TO.MAIN

2. If the program executes on an M-Memory Processor (B 1726) the following code is generated for each different \( \lambda \lambda bel \rangle \) in a BRANCH.EXTERNAL statement:

MOVE ADDRESS (\(\lambda abel\rangle\) TO X GO TO BRANCH.TO.MAIN

3. If the program executes on an M-Memory Processor (B 1726) the following code is generated for each different \( label \) in a CALL.EXTERNAL statement:

MOVE ADDRESS (⟨label⟩) TO X GO TO CALL.TO.MAIN

- c. At the end of every (external.code.block) the following code is emitted.

- 1. For S-Memory Processor (B 1712 B 1714):

SUBSET.BRANCH.TO.MAIN

MOVE MAIN.CODE.BASE TO Y

MOVE SUM TO A

2. For M-Memory Processors (B 1726):

BRANCH.TO.MAIN

MOVE TAS TO NULL

MOVE MAIN.CODE.BASE TO Y

MOVE SUM TO T

GO TO LEAVE.EXTERNAL.SEGMENT

CALL.TO.MAIN

MOVE MAIN.CODE.BASE TO Y

MOVE SUM TO T

MOVE MBR TO L

MOVE TOPM TO LF

MOVE L TO TAS

MOVE ADDRESS (EXIT.TO.EXTERNAL) TO X

MOVE SUM TO TAS

GO TO LEAVE.EXTERNAL.SEGMENT

# **NOTES**

- a. When branching from the \( \text{main.code.block} \) to an \( \text{external.code.block} \) the T and L registers are used, plus whatever registers the GO.TO.EXTERNAL.SEGMENT routine uses.

- b. When calling or branching to a routine in the (main.code.block), the X and Y registers are used: This means that they cannot also be used for passing parameters. In addition CP should be equal to 24, otherwise the transfer may not take place correctly.

Also, on an M-Memory Processor, the T and L registers, as well as the A stack are used. Thus, a good rule of thumb is to avoid using X, Y, T, L, and TAS when passing parameters to/from the  $\langle main.code.block \rangle$  and  $\langle external.code.block \rangle$ (s).

c. The code for S-Memory Processors is different than the code for M-Memory Processors. Thus, CODE.SEGMENTS cannot be used if the program is to execute interchangeably on either the B 1710 or B 1720 Series processors. (See Appendix A: \$ NO EXTERNAL).

# 6. DECLARATIONS

### **DATA TYPES**

Three main types of data fields may be declared in MIL:

- 1. BIT

- 2. CHARACTER

- 3. FIXED

A bit field consists of a number of bits specified by a number in parentheses following the reserved word BIT.

A character field consists of a number of 8-bit characters specified by a number in parenthesis following the reserved word CHARACTER.

A FIXED data field is the same as a BIT (24) field but is allowed in order to keep declare syntax consistent with SDL.

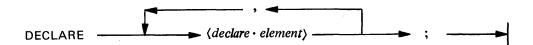

# **DECLARE STATEMENT**

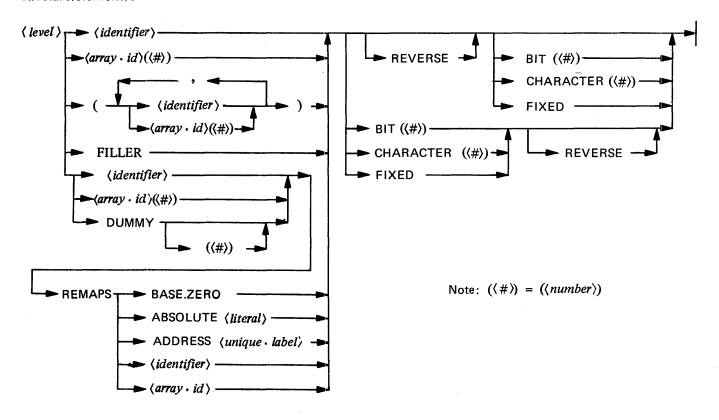

# **Syntax**

# **Semantics**

The DECLARE statement specifies the addresses and characteristics of contents of memory storage areas.

The maximum number of data elements (including fillers, dummys, and implicit fillers) allowed in one structure is 50. Any attempt to declare more will cause a table overflow error to be detected at compile time.

An  $\langle array \rangle$  may have a maximum of 65535 elements, each being a maximum of 65535 bits (8191 characters).

The two types of \( \declare.elements \rangle \) are discussed separately below.

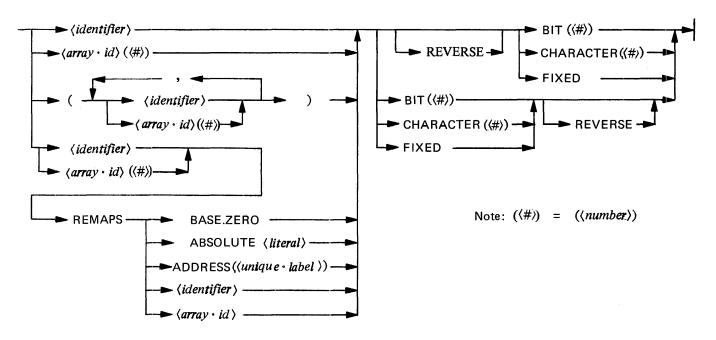

# Non-Structured Declarations

\ declare.element\:

Data may be declared as simple, having one occurrence, or as subscripted, having as many occurrences as specified by the  $\langle array \ bound \rangle$ . In the latter case, array subscripts are considered to range from zero to  $\langle array \ bound \rangle$ -1.

BIT, CHARACTER or FIXED specifies the type of data in the field and the field size.

REVERSE specifies that an item or a structure is to be accessed in a reverse manner or in a reverse direction from some base. The easiest way to remember what is happening is to realize that the compiler will simply compute the address of a declared (*identifier*) normally, and then, if reverse is specified, subtract the (*identifier*)'s length from the address to get the starting address of the (*identifier*).

As the syntax indicates, different data fields having the same format may be declared collectively inside parenthesis ( ).

The following example illustrates the various options available in this type of \( \) declaration statement \( \).

# Example

```

DECLARE

PRIDE

COVETOUSNESS

GLUTTONY

(LUST, ENVY, ANGER (5))

SLOTH (20)

WRATH (5)

FIXED

CHARACTER (10),

BIT (40),

BIT (10),

FIXED,

CHARACTER (6);

```

#### where

PRIDE is a 24-bit numeric field;

COVETOUSNESS is a 10-byte character field;

GLUTTONY is a 40-bit field;

LUST and ENVY are each 10-bit fields, as is each of the five elements comprising ANGER;

SLOTH occurs twenty times, each element being a 24-bit numeric field;

WRATH is a six-byte character field occurring five times.

Data fields may be re-formatted by the use of the REMAPS option. Remapping is subject to the same general rules discussed above. The following example best illustrates its use:

B FIXED, C BIT (50), BB REMAPS B CHARACTER (3), CC (2) REMAPS C FIXED;

Note that CC specifies 48-bits (or 2 elements, 24-bits each). The last two bits will be considered as an implied filler by the compiler. A field may not be remapped larger than its original size.

There is no limit on the number of times a field may be remapped. A field which has remapped another may itself be remapped. The remap option specifies that the \( identifier \) on the left side of the reserved word REMAPS will have the same starting address as the \( identifier \) on the right side.

A data field may be remapped to BASE.ZERO which will give the field a relative address of zero. For example:

DECLARE Q REMAPS BASE.ZERO BIT (7);

This device is used as a free-standing declaration since it does not remap a previously declared data item.

#### **Structured Declarations**

(declare.element):

MIL allows the structuring of data where a field may be subdivided into a number of sub-fields, each of which has its own \( \langle identifier \rangle \). The whole structure is organized in a hierarchical form, where the most general declaration is a \( \langle level \rangle 01 \) (or 1). No declaration may be on a \( \langle level \rangle \) greater than 99. A subdivided field is called a Group Item, and a field not subdivided is known as an Elementary Item.

The type and length of data need not be specified on the group level. All Elementary Items must indicate type and length; the compiler will assume type bit and add the lengths of the components to determine the length of the Group Item. Note that the length of the Group Item is the sum of the lengths of its Elementary Items.

In the following example, both A.A and C.C are considered Group Items; A.A has a total length of 90 bits, and C.C is 50 bits in length.

#### Example

Fillers may be used to designate certain Elementary Items which the program does not reference. If the filler is the last item in a structure, it may be omitted; the compiler will consider the Group Item to have an implied filler. A filler may never be used as a Group Item.

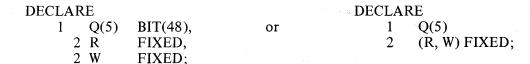

If the 01 level group item is an  $\langle array \rangle$ , it is mapped as a contiguous area in memory. However, subdivisions of this  $\langle array \rangle$  are not contiguous as shown in the example structure below:

## Example

If a Group Item is an  $\langle array \rangle$ , an  $\langle array \ specification \rangle$  may not appear in any subordinate item; that is, only one-dimensional  $\langle array \rangle$ s are allowed. An  $\langle array \ specification \rangle$  is implied for all subordinate items.

If a Group Item is declared with the REVERSE option, then REVERSE is also implied for all subordinate items in that group. Specification of the REVERSE option for subordinate items would be redundant.

Structured data may be remapped in the same manner as non-structured data. In addition, structured data may be remapped with a dummy group identifier. The purpose of this construct is to allow the user to remap data items without having to declare another Group Item which describes the same area in memory. Thus in the following example:

#### Example

YAK might be remapped as:

| DECLARE     |     |           | DEC | CLARE | 3     |        |     |           |

|-------------|-----|-----------|-----|-------|-------|--------|-----|-----------|

| 1 AA REMAPS | YAK | BIT(100), |     | 1     | DUMMY | REMAPS | YAK | BIT(100), |

| 2 CC        |     | BIT(30),  | or  | 2     | CC    |        |     | BIT(30),  |

| 2 DD        |     | BIT(70);  |     | 2     | DD    |        |     | BIT(70);  |

Both YAK and AA refer to the same area in memory: hence AA is redundant.

If a remapped item contains the REVERSE option, then REVERSE is also implied for the remapping item.

The user should note the distinction between DUMMY and FILLER. DUMMY is used in conjunction with REMAPS to eliminate the necessity of declaring a redundant Group Item. FILLER is used if one desires to skip over a part of the structure.

The following restrictions apply to the use of DUMMY REMAPS:

- 1. DUMMY may only be used with \(\(\text{remap declarations}\)\).

- 2. All restrictions applying to REMAPS apply to DUMMY REMAPS.

- 3. DUMMY must not remap another DUMMY.

- 4. DUMMY Group Items must have at least one non-filler component.

#### DECLARE EXAMPLES

#### Introduction

Let us illustrate by example exactly how declarations might be used in a MIL program, and note the associated relevant points.

The DECLARE statement in MIL is one which allows the user to logically assign names to physical or relative memory address in a structured manner. This facility allows one to construct data structures in a format that is simple to understand and easy to change when the occasion arises.

## Non-Remap Items

The MIL compiler maintains a variable which is initialized to 0. When an item is declared, it is assigned the current value of this variable and the variable is incremented by the bit length of the declared item.

#### Example

| DECLARE               |          |

|-----------------------|----------|

| DISPATCH.REGISTER     | BIT(24), |

| GLOP1                 | BIT(48), |

| ADDR.GISMO            | BIT(24), |

| LOCN.MAKE.MCP.BE.HERE | BIT(36), |

| GLOP2                 | BIT(29), |

| ADDR.MCP.LIMIT        | FIXED:   |

Note that the DECLARE statement is completely free form, must begin with the world "DECLARE", must end in a ";", and that each element must be separated from its predecessor with a ",".

Each element thus declared is used exactly as a (literal) and most often represents a memory address.

## Example

```

MOVE ADDR.GISMO TO FA

READ 24 BITS TO X

```

This would assign the literal 72 (= 24+48 = ADDR.GISMO) to register FA and would cause the contents of memory at address 72 to be read into register X.

Should the compiler encounter another DECLARE, it will merely start assigning addresses where it left off previously.

## Example

```

DECLARE

GLOP3

BIT(10)

CHAR.SAVE.AREA

CHARACTER(8);

```

GLOP3 above would be assigned the value of the aforementioned address-counting variable, in this instance 185.

DECLARE elements may also be structured such that some names overlap pieces of memory described by other names.

## Example

| <b>DECLARE</b> |     |                    |          |

|----------------|-----|--------------------|----------|

| 1              |     | TRACE.BITS         | BIT(27), |

| 5              |     | FILLER             | BIT(15), |

| 5              |     | TB.FLAGS           | BIT(1),  |

| 5              |     | TB.TYPE            | BIT(4),  |

|                | 8 . | FILLER             | BIT(1),  |

|                | 8   | TB.STORES.ONLY     | BIT(1),  |

|                | 8   | TB.BRANCHES        | BIT(1),  |

|                | 8   | TB.THE.REST        | BIT(1),  |

| 5              |     | TB.GET.SPACE.TYPE, |          |

|                | 99  | (TB.STORES.ONLY,   |          |

|                |     | TB.BRANCHES,       |          |

|                |     | TB.REMAINDER)      | BIT(1);  |

This example illustrates the following points:

- 1. The address picks up where the previous DECLARE leaves off. This is not true, however, where the previous item or structure is a "remap item". The compiler's internal variable used for default address assignment is maintained and incremented only for non-remap items or structures.

- 2. DECLAREs may be structured such that some fields are denoted as being contained within other fields.

- 3. "FILLER" can be used in structures as often as necessary to increment the address-counting variable past an area of memory which the programmer does not intend to reference by a symbolic name.

- 4. Items with the same type and length can be put into a list surrounded by parentheses, with the type and length specified only once at the end.

- 5. The length of an item need not be specified if it has sub-items whose lengths can be determined.

#### **NOTE**

Structures must begin with an "01" level identifier. Substructures may then have any level from 02 to 99 inclusive, with the substructure always having higher level numbers than the superstructure.

#### Remap Items

DECLARE

#### **GENERAL**

It is possible to temporarily suspend the mechanism which causes addresses to be assigned based on where the last DECLARE left of by using remaps structures.

For example, if we wish to declare a "template", where the declared addresses are added to some base prior to actual use, we would do the following:

#### 1 SYSTEM.DESCRIPTOR REMAPS BASE.ZERO, 2 SY.MEDIA BIT(2), 2 SY.LOCK BIT(1), 2 (SY.IN.PROCESS, SY.INITIAL, SY.FILE) BIT(1), 2 FILLER BIT(10),

- 2 FILLER BIT(10), 2 SY.TYPE BIT(4), 2 SY.ADDRESS BIT(36),

- 3 FILLER BIT(12), % PORT AND CHANNEL

- 3 SY.CORE BIT(24), 2 SY.LENGTH BIT(24);

One might use the above structure as follows:

```

DEFINE SYS.DESC.BASE = S14A#

%

MOVE SY.TYPE TO FA

ADD SYS.DESC.BASE TO FA

READ DATA.LENGTH (SY.TYPE) BITS TO X

```

Note the use of a new reserved word, "DATA.LENGTH". This construct allows one to use the length of a declared item without having to define it elsewhere.

The remap structures that are permitted are:

- 1. REMAPS BASE.ZERO

- 2. REMAPS ABSOLUTE (literal)

- 3. REMAPS ADDRESS (\(\langle unique.label \rangle \)

- 4. REMAPS (identifier)

- 5. REMAPS (array.identifier)

If one knew the absolute address of some data structure in memory, the following could be done:

#### DECLARE

- 1 SAVE.AREA REMAPS ABSOLUTE 1024,

- 2 SA.FIRST.ITEM FIXED,

- 2 SA.SECOND.ITEM CHARACTER(200),

- 2 SA.THIRD.ITEM BIT(256);

The following technique could be used when a \( \lambda \) denoting the start of a table of constants was present in a program:

#### **DECLARE**

- 1 TRACE.TABLE(10) REMAPS ADDRESS (TRACE.MNEMONICS),

- 2 ADDR.TRACE.NAME CHARACTER (4);%

```

TRACE.MNEMONICS

TABLE

BEGIN

"LA

"ALA"

"STN"

"STD"

"LIT"

"ILA"

"STO"

"CASE"

"IFTH"

"IFEL"

END

MOVE ADDR.TRACE.NAME (2) TO FA

READ 24 BITS TO X INC FA

READ 8 BITS TO Y

```

Note the use of  $\langle array \rangle$  in the above example. If the programmer does not know the index to use at compile time, the following could be done:

```

DEFINE TRACE.INDEX = SOB

%

MOVE TRACE.INDEX TO X

MOVE LENGTH.BETWEEN.ENTRIES (TRACE.TABLE) TO Y

CALL MULTIPLY.X.Y

% AND SO FORTH

%

MULTIPLY.X.Y

% MULTIPLICATION CODE

EXIT

```

The above examples have shown, among other things, two of the "specials" that are included in MIL syntax to augment usage of DECLAREd items. They are:

```

DATA.LENGTH (\langle declared identifier \rangle)

LENGTH.BETWEEN.ENTRIES (\langle array identifier \rangle)

```

Note that when  $\langle array \rangle$  names are used with the specials, the subscript is not included; it is syntactically invalid to do so.

Another type of remaps is one that remaps a previously declared structure. In this case, the addresses of the remap structure will begin at the address of the remapped structure.

## Example

#### **DECLARE**

1 SAVE.AREA.CHARS REMAPS SA.SECOND.ITEM

2 SA.NAME CHARACTER(30),

3 (SA.PACK.ID,

SA.FAMILY.NAME,

SA.OFFSPRING NAME) CHARACTER(10),

SA.OWNER.NAME CHARACTER(14):%

% THE RIGHTMOST 156 CHARACTERS OF SA.SECOND.ITEM ARE NOT REMAPPED HERE

#### **REVERSE**

"REVERSE" is an attribute that may be applied to a remapping simple item or structure. The presence of this reserved work causes the address associated with a \( \declared \) identifier \( \) to be the normally-calculated address minus its declared length.

For example, suppose a programmer wishes to specify a structure that describes the top memory and wants to list the (identifier)s from the top of memory downward. The following could be done:

| DECLARE |   |                         |                   |

|---------|---|-------------------------|-------------------|

| 1       |   | TOP.OF.MEMORY REMAPS B. | ASE.ZERO REVERSE, |

| 2       |   | FILLER                  | BIT(32),          |

| 2       |   | ADDR.INTERRUPT.QUEUE    | BIT(553),         |

| 2       |   | ADDR.SAVED.A.STACK      | BIT(240),         |

| 2       |   | ADDR.GISMO.WORK.SPACE   | BIT(384),         |

| 2       |   | ADDR.TEMP.FIB           | BIT(920),         |

| 2       |   | ADDR.TRACE.SPACE        | BIT(2232),        |

|         | 3 | ADDR.TRACE.CODE         | BIT(24);          |

These (identifier)s could then be used in MIL statements as follows:

MOVE ADDR.INTERRUPT.QUEUE TO Y EXTRACT ADDR.TRACE.CODE FROM T TO X

#### 7. REGISTERS AND SCRATCHPAD

#### **GENERAL**

This section is intended only as a brief overview of the registers within the processor. It is assumed that the reader is familiar with the contents of the B 1700 Systems Reference Manual (form 1057155). (See also Appendix B in this manual).

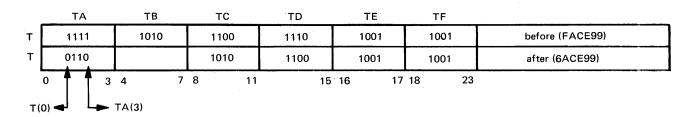

#### **NOTE**

The most-significant (left-most) bit in any register is identified in the MIL syntax as bit 0 (zero), the next most-significant as bit 1, etc. This is particularly advantageous in a bit-addressable machine since, for software purposes, it is often desirable to think of a register as being an extension of main memory. It should be noted that this convention is at variance with the hardware bit numbering convention where, generally, all bits are numbered right to left, 0 through N. This difference has particular significance when any bit data is to be OR'ed into the M register at run time.

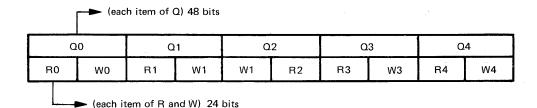

## **REGISTER GROUPS**

The registers briefly described in this section are divided into the following logical groups:

Active registers Result registers Scratchpads Constant registers Input/Output registers Condition registers

- \* MSMA, TOPM, MBR and the low order 3 bits of CD are not physically present in the S-Memory Precessor. When addressed as a source they will yield a binary value of zero. When addressed as a sink (destination) the data is lost.

- \*\* CPU, a 2-bit subregister of CP, is not addressable as a source or a sink.

## RESULT REGISTERS

# SOURCE SUM CMPX CMPY XANY XEOY MSKX MSKY OXRY DIFF

#### SCRATCHPAD

| Source & Sink   |

|-----------------|

| S0A<br><br>S15A |

| S0B<br><br>S15B |

Single Scratchpad

|   | Source & Sink |

|---|---------------|

|   | ) S0          |

|   | ••            |

| 1 | S15           |

Double Scratchpad

#### CONSTANT REGISTERS

| Source       |  |

|--------------|--|

| MAXS<br>MAXM |  |

## INPUT/OUTPUT REGISTERS

| Source | Sink | Source & Sink |

|--------|------|---------------|

| U      | CMND | DATA          |

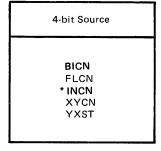

#### CONDITION REGISTERS

\* INCN is not physically present on the S-Memory Processor. When addressed as a source it yields a binary value of 0. When addressed as a sink (destination) the data is lost.

# ALPHABETICAL LISTING OF REGISTERS AND KEY CONCEPTS

| <u>Name</u>         | Length<br><u>In Bits</u> | Source<br>Sink | <u>Note</u>                                                                 |

|---------------------|--------------------------|----------------|-----------------------------------------------------------------------------|

| A                   | *                        | so & sk        | Control Memory Micro-instruction Address<br>* 24 (1726), 19 (S-1), 20 (S-2) |

| BICN                | 4                        | source         | boolean conditions                                                          |

| BR                  | 24                       | so & sk        | Base Register or low address<br>S-Memory protection                         |

| C                   | 24                       | ***            | Control; not addressable as a unit                                          |

| CA                  | 4                        | so & sk        | subfield of C; general purpose                                              |

| СВ                  | 4                        | so & sk        | subfield of C; general purpose                                              |

| CC                  | 4                        | so & sk        | subfield of C; interrupts and flags                                         |

| CD                  | 4                        | so & sk        | subfield of C; interrupts and flags                                         |

| CMND                | 24                       | sink           | I/O Command Register                                                        |

| CMPX                | 24                       | source         | Result: complement of X; masked by CPL                                      |

| CMPY                | 24                       | source         | Result: complement of Y; masked by CPL                                      |

| Console<br>Switches | 24                       | source         | the 24 toggle switches located on the Console front panel                   |

| Control<br>Memory   | 16-bit<br>words          | so & sk        | Location of micro-instructions on M-Memory Processor                        |

| CP                  | 8                        | so & sk        | Control Parallel; subfield of C                                             |

| CPL                 | 5                        | so & sk        | Control Parallel Length; subfield of CP                                     |

| CPU                 | 2                        |                | Control Parallel Unit; subfield of CP                                       |

| CYD                 | 1                        |                | Carry Difference or carry of borrow                                         |

| CYF                 | 1                        |                | Carry Flip-Flop; subfield of CP                                             |

| CYL                 | 1                        |                | Carry Level or carry of sum; masked by CPL                                  |

| DATA                | 24                       | so & sk        | I/O Data Register                                                           |

| DIFF                | 24                       | source         | result of $X-(Y+CYF)$ ; masked by CPL                                       |