# B 1900 SERIES CENTRAL SYSTEM

TECHNICAL MANUAL VOLUME 1:

# OPERATION and MAINTENANCE

# Burroughs 3

### FIELD ENGINEERING

FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under special License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

| •  | OPERATION                          |   |

|----|------------------------------------|---|

| 2  | INSTALLATION                       |   |

| 3  | DOCUMENTATION<br>AND<br>COMPONENTS |   |

| 4  | MAINTENANCE<br>TECHNIQUES          |   |

| 5  |                                    |   |

| 6  |                                    |   |

| 7  |                                    |   |

| 8  |                                    |   |

| 9  |                                    |   |

| 10 |                                    |   |

| A  |                                    |   |

| В  |                                    | _ |

| C  |                                    |   |

**FUNCTION**

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

### LIST OF EFFECTIVE PAGES

| Page          | Issue    |

|---------------|----------|

| Title         | Original |

| ii            | Original |

| iii           | Original |

| iv            | Blank    |

| v thru xi     | Original |

| xii           | Blank '  |

| 1-1 thru 1-71 | Original |

| 1-72          | Blank    |

| 2-1 thru 2-8  | Original |

| 3-1 thru 3-4  | Original |

| 4-1 thru 4-13 | Original |

| 4-14          | Blank    |

### TABLE OF CONTENTS

| Section | Title                                         |    |       |    |     |     |   |   |   |   |     |     |     | Page |

|---------|-----------------------------------------------|----|-------|----|-----|-----|---|---|---|---|-----|-----|-----|------|

| 1       | FUNCTION AND OPERATION                        |    |       |    |     |     |   |   |   |   |     |     |     | 1-1  |

| •       | Introduction                                  |    |       |    |     |     |   |   |   |   |     |     | •   | 1-1  |

|         | System Description                            |    |       |    |     |     |   |   |   |   |     | •   | . • | 1-1  |

|         | Features and Ontions                          |    |       |    |     | •   |   |   |   |   |     |     |     | 1-2  |

|         | Subsystems                                    |    |       |    |     |     |   |   |   |   |     |     |     | 1-3  |

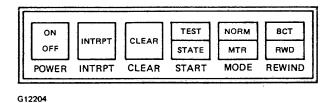

|         | Control Panels                                |    |       |    |     |     |   |   |   |   |     |     |     | 1-5  |

|         | Operator Control Panel                        |    |       |    |     |     |   |   |   |   |     |     |     | 1-5  |

|         | POWER Push Button, ON/OFF Indicator           |    |       |    |     |     |   |   |   |   |     |     |     | 1-5  |

|         | INTRPT Push Button/Indicator                  |    |       |    |     |     |   |   |   |   |     |     |     | 1-5  |

|         | CLEAR Push Button                             |    |       |    |     |     |   |   |   |   |     |     |     | 1-5  |

|         | START Push Button, TEST STATE Indicator       | ·  |       |    |     |     | _ |   |   |   |     | •   |     | 1-5  |

|         | MODE Push Button, NORMAL/MTR Indicator        | •  | • •   | •  | •   | Ī   |   |   |   |   |     |     |     | 1-6  |

|         | BOT/RWD Push Button and Indicator             | •  | • •   | •  | •   | •   | Ī | • |   |   |     |     |     | 1-6  |

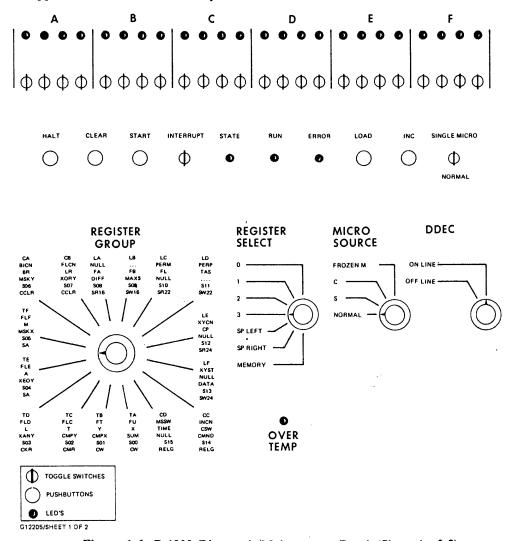

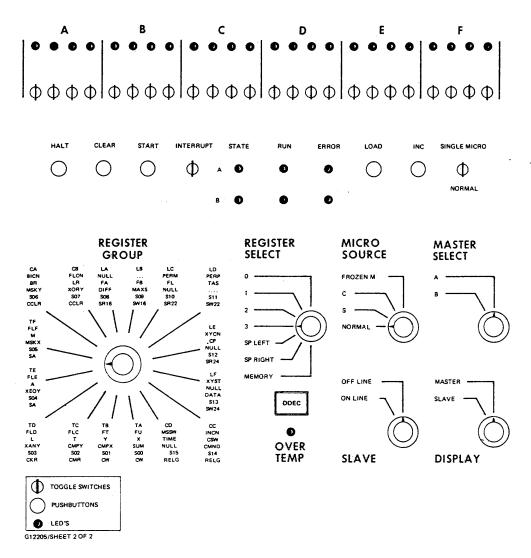

|         | Diagnostic/Maintenance Panel                  | •  |       | •  | • • | •   | • | • |   | • |     |     |     | 1-6  |

|         | Diagnostic/Maintenance Panel                  | •  | • •   | •  |     | •   | • | • | • | • | •   | •   | •   | 1-7  |

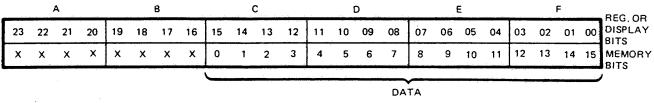

|         | Console Lamps                                 | •  | • •   | •  |     | •   | • | • | • | • | • • | •   | •   | 1-7  |

|         | Console Switches                              |    |       |    |     |     |   |   |   |   |     |     |     | 1-8  |

|         | HALT Push Button                              | •  |       | •  |     | •   | • | • | • | • | •   | •   | •   | 1-8  |

|         | CLEAR Push Button, START Push Button .        | •  | • •   | •  |     | •   | • | • | • | • | •   | •   | •   | 1-8  |

|         | INTERRUPT Switch                              | •  |       | •  |     | •   | ٠ | • | • | • | •   | •   | •   | 1-8  |

|         | STATE Indicator                               | •  | • •   | •  |     | •   | • | • | • | • | •   | •   | •   | 1-8  |

|         | RUN Indicator                                 | •  |       | ٠  |     | :•  | • | ٠ | • | • | • - | •   | •   | 1-8  |

|         | ERROR Indicator                               |    |       | •  |     | •   | ٠ | • | • | • | •   | •   | •   | 1-8  |

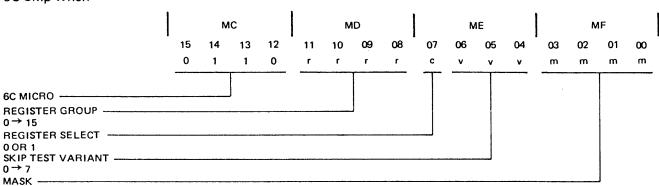

|         | REGISTER GROUP and REGISTER SELECT            | Sw | ritch | es |     | •   | • | • | • | • | •   | • • | •   |      |

|         | LOAD Push Button                              | •  |       | •  |     | •   | • | • | • | • | •   | •   | •   | 1-10 |

|         | INC (Increment) Push Button                   | •  |       | •  |     | •   | • | • | • | • | •   |     | •   | 1-12 |

|         | SINGLE MICRO/NORMAL Switch                    | •  |       | •  |     | •   | ٠ | • | • | • | •   | • • | •   | 1-12 |

|         | MICRO SOURCE Switch                           |    |       | •  |     | •   | • | • | • | • | •   |     | •   | 1-12 |

|         | DDEC Switch Indicator                         |    |       |    |     | •   | • |   | • | • | •   | • • | ٠   | 1-12 |

|         | OVER TEMP Indicator                           |    |       |    |     |     | • |   |   | • | •   |     | •   | 1-12 |

|         | Switches for Two-Processor Systems            |    |       |    |     |     |   | • | • |   | •   |     | •   | 1-12 |

|         | Console Uses in Central System Operation      |    |       |    |     |     |   | • |   |   | •   |     | •   | 1-13 |

|         | Operator Panel: Basic Functions               |    |       |    |     |     | • | • | • | • | •   |     | •   | 1-13 |

|         | Diagnostic/Maintenance Panel; Basic Functions |    |       |    |     |     |   |   |   | • |     |     | •   | 1-13 |

|         | Displaying a Register                         |    |       |    |     |     |   | ٠ |   | • |     |     | •   | 1-14 |

|         | Loading a Register                            |    |       |    |     |     |   |   |   |   |     |     | •   | 1-14 |

|         | Displaying S-Memory                           |    |       |    |     |     |   |   |   |   |     |     |     | 1-14 |

|         | Writing into an S-Memory Location             |    |       |    |     |     |   |   |   |   |     |     |     | 1-15 |

|         | Displaying a Cache Location                   |    |       |    |     |     |   |   |   |   |     |     |     | 1-15 |

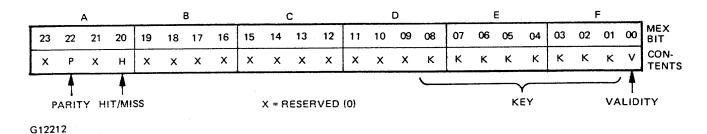

|         | Displaying a Cache Key                        |    |       |    |     |     |   |   |   |   |     |     |     | 1-17 |

|         | Writing into a Cache Micro and Key Location   | on |       |    |     |     |   |   |   |   |     |     |     | 1-17 |

|         | Processor                                     |    |       |    |     |     |   |   |   |   |     |     |     | 1-17 |

|         | Functional Layout                             |    |       |    |     |     |   |   |   |   |     |     |     | 1-18 |

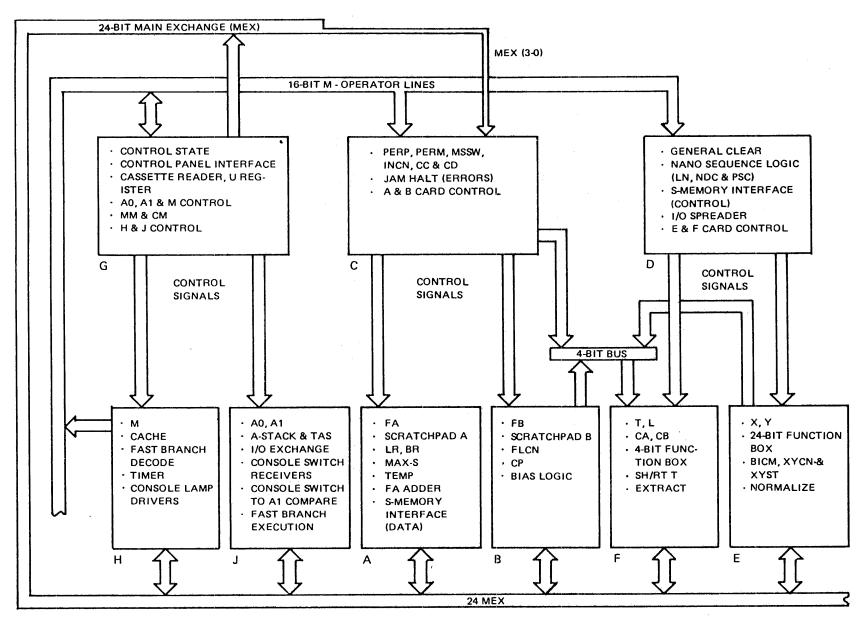

|         | Processor Block Diagram                       | •  |       | •  |     | . • | • | • |   |   |     |     |     | 1-18 |

|         | Card Group 1 (G, H, J)                        | •  |       | •  | •   | •   | • | • |   |   |     |     |     | 1-20 |

|         | Card Group 1 (G, H, J)                        | •  | • •   | •  | •   |     | • | • | • |   | -   |     |     | 1-21 |

|         | Card Group 2 (C, A, B)                        | •  |       | •  | •   | • • | • | • | • |   |     |     |     | 1-22 |

|         | System Clock (Card K)                         | •  |       | •  | •   |     | • | • | • | • | •   |     | •   | 1-22 |

|         | System Clock (Card K)                         | •  |       | •  | •   |     | • | • | • | • | •   |     | •   |      |

| Section | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1       | FUNCTION AND OPERATION (Cont)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

|         | Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 22 |

|         | General-Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-22 |

|         | L Register (Including LA, LB, LC, LD, LE, and LF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-23 |

|         | T Register (Including TA, TB, TC, TD, TE, and TF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-23 |

|         | X Register, Y Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-23 |

|         | TAS (Top Of A-Stack) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-24 |

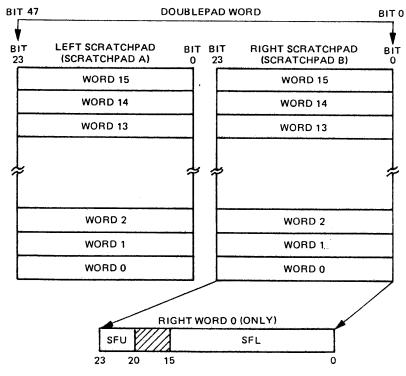

|         | A-Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-24 |

|         | Addressing and Execution Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-24 |

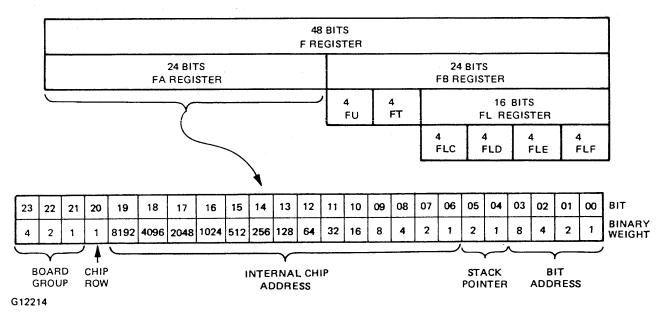

|         | FA (Field Address) Pagister                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-24 |

|         | FA (Field Address) Register FB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-24 |

|         | FB Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-24 |

|         | BR (Base Register) and LR (Limit Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-25 |

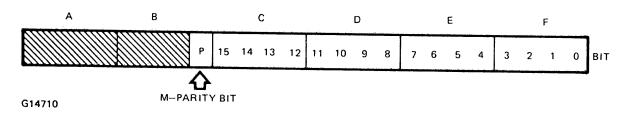

|         | M (Microinstruction) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-26 |

|         | U Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-26 |

|         | A (Address) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-26 |

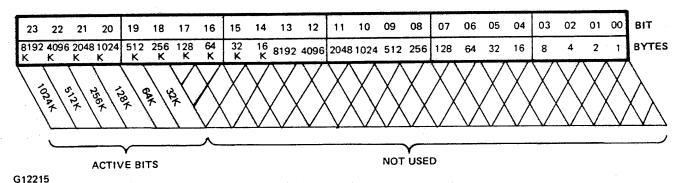

|         | MAXS (Maximum S-Memory Size) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-27 |

|         | Arithmetic and Logical Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-27 |

|         | SUM Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-27 |

|         | DIFF (Difference) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-27 |

|         | AANI, AURY and XEUY (Boolean Functions)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-28 |

|         | CMPX (Complement of X), CMPY (Complement of Y)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-28 |

|         | MSKX (Mask of X), MSKY (Mask of Y) Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1-28 |

|         | BICN (Binary Conditions) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1-28 |

|         | XYCN (XY Conditions) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-29 |

|         | XYST (XY States) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-29 |

|         | Interrupt and Processor Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-30 |

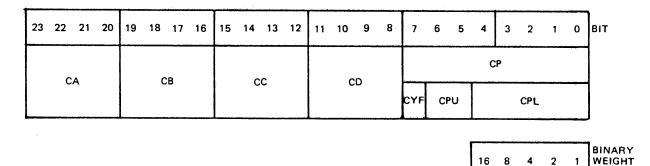

|         | C Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1-30 |

|         | CA AND CB Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1-30 |

|         | CC Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-30 |

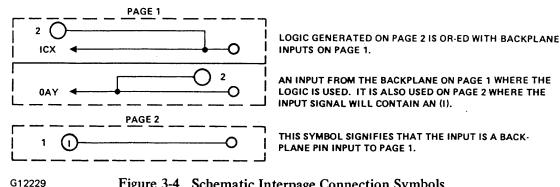

|         | CD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-31 |