## **B 1900 SYSTEM**

TECHNICAL MANUAL VOLUME 3:

# THEORY OF OPERATION

# Burroughs 3

#### FIELD ENGINEERING

FIELD ENGINEERING PROPRIETARY DATA

The information contained in this document is proprietary to Burroughs Corporation. The information or this document is not to be reproduced, shown, or disclosed outside Burroughs Corporation without written permission of the Patent Division.

This material is furnished for Burroughs Field Engineering Personnel, and is not furnished to customers except under special License Agreement.

THIS DOCUMENT IS THE PROPERTY OF AND SHALL BE RETURNED TO BURROUGHS CORPORATION, BURROUGHS PLACE, DETROIT, MICHIGAN 48232.

|     | <u> </u>                                            |

|-----|-----------------------------------------------------|

| 2   | CIRCUIT COPERATIONAL DETAIL                         |

| 3 * | CIRCUIT<br>OPERATIONAL<br>DETAIL<br>B 1900 S-MEMORY |

| 4   | CIRCUIT<br>OPERATIONAL<br>DETAIL<br>HOST ADAPTER-3  |

| 5   |                                                     |

| 6   |                                                     |

| 7   |                                                     |

| 8   |                                                     |

| 9   |                                                     |

| 10  |                                                     |

| Α   | GLOSSARY<br>OF<br>TERMS                             |

BASIC PRINCIPLES

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO-West.

### LIST OF EFFECTIVE PAGES

| Page                                                                          | Issue                                                                                                       | Page                                                                                                          | Issue                                                                               |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Page  Title ii iii iv v thru xi xii 1-1 1-2 2-1 thru 2-21 2-22 2-23 thru 2-27 | Issue Original Original Original Blank Original Blank Original Blank Original Blank Original Blank Original | 2-30<br>2-31<br>2-32<br>2-33 thru 2-60<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5 thru 3-11<br>3-12<br>3-13 thru 3-46 | Blank Original Blank Original Original Blank Original Blank Original Blank Original |

| 2-28<br>2-29                                                                  | Blank<br>Original                                                                                           | 4-1 thru 4-33<br>4-34<br>A-1 thru A-16                                                                        | Original<br>Blank<br>Original                                                       |

## **TABLE OF CONTENTS**

| Section | Title                                       | Page |

|---------|---------------------------------------------|------|

| 1       | BASIC PRINCIPLES                            | 1-1  |

| 2       | CIRCUIT OPERATIONAL DETAIL                  | 2-1  |

| 2       | Introduction                                | 2-1  |

|         | Console Interface Logic                     | 2-1  |

|         | Operator Panel                              | 2-1  |

|         | TEST STATE Indicator                        | 2-2  |

|         | MODE Push Button, NORMAL/MTR Indicators     | 2-2  |

|         | BOT/RWD Push Button/Indicator               | 2-2  |

|         | Diagnostic/Maintenance Panel                | 2-2  |

|         |                                             | 2-4  |

|         |                                             | 2-4  |

|         | Console Switches                            | 2-5  |

|         | REGISTER GROUP and REGISTER SELECT Switches | 2-6  |

|         | HALT Push Button                            | 2-6  |

|         | STATE Indicator                             | 2-6  |

|         | RUN Indicator                               | 2-6  |

|         | ERROR Indicator                             | 2-10 |

|         | LOAD Push Button                            | 2-10 |

|         | INC (Increment) Push Button                 | 2-12 |

|         | SINGLE MICRO/NORMAL Switch                  | 2-12 |

|         | MICRO SOURCE Switch                         | 2-14 |

|         | Over Temperature Indicator                  | 2-13 |

|         | DDEC Switch                                 |      |

|         | Switches for Two-Processor Systems          | 2-16 |

|         | MASTER SELECT Switch                        | 2-16 |

|         | SLAVE Switch                                | 2-16 |

|         | DISPLAY Switch                              | 2-16 |

|         | Duplicate Console Functions                 | 2-16 |

|         | CLEAR Push Button                           | 2-16 |

|         | START Push Button                           | 2-17 |

|         | INTERRUPT Switch                            | 2-17 |

|         | System Clock                                | 2-17 |

|         | Processor Clocks                            | 2-19 |

|         | Cache Memory Clocks                         | 2-19 |

|         | Memory Base Unit Clocks                     | 2-19 |

|         | System Clocks                               | 2-20 |

|         | I/O Clocks                                  | 2-20 |

|         | Main Exchange                               | 2-23 |

|         | Processor Card Functions                    | 2-23 |

|         | Card Group G, H, J                          | 2-26 |

|         | Card G                                      | 2-26 |

|         | Fetch Structure                             | 2-29 |

|         | Decode Structure                            | 2-29 |

|         | Nano Generation Logic                       | 2-33 |

|         | Nano Sequence Logic                         | 2-33 |

|         | U Register                                  | 2-33 |

|         | Card H                                      | 2-33 |

|         | Cache Memory                                | 2-33 |

|         | Cache Memory Organization                   | 2-36 |

|         | Implementation                              | 2-38 |

|         | implementation                              |      |

## **TABLE OF CONTENTS (Cont)**

| Section | Title                             |                                       | Page          |

|---------|-----------------------------------|---------------------------------------|---------------|

| 2       | CIRCUIT OPERATIONAL DETAIL (Cont) |                                       |               |

|         | Validity                          |                                       | 2-39          |

|         | Parity                            |                                       | 2-39          |

|         | Cache Key Readout                 |                                       | 2-39          |

|         | M Register                        |                                       | 2-39          |

|         | Time                              |                                       | 2-40          |

|         | Card J                            |                                       | 2-40          |

|         | A Register                        |                                       | 2-40          |

|         | A-Stack and TAS Register          |                                       | 2-42          |

|         | Pushing                           |                                       | 2-43          |

|         | ropping                           |                                       | 2-43          |

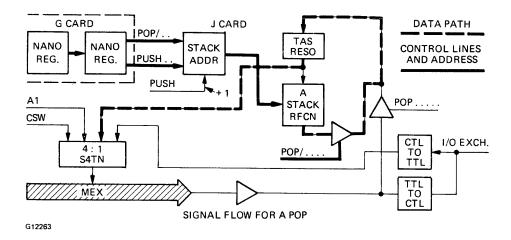

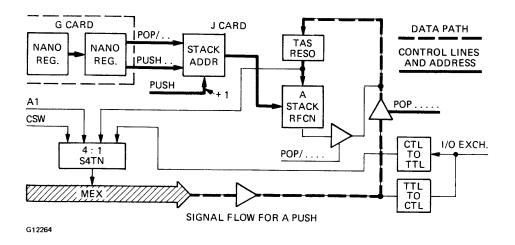

|         | Logic and Signal Flows            |                                       | 2-43          |

|         | I/O Interface                     |                                       | 2-46          |

|         | Data Register                     |                                       | 2-46          |

|         | Command Register                  |                                       | 2-46          |

|         | Console Switch Register           |                                       | 2-46          |

|         | Cald Gloup C, A, B                |                                       | 2-46          |

|         |                                   |                                       | 2-47          |

|         | Register Source/Sink Control      |                                       | 2-47          |

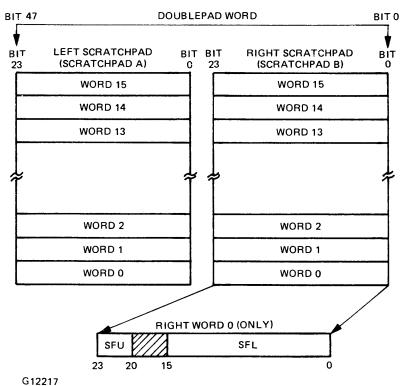

|         | Scratchpad                        |                                       | 2-49          |

|         | CC and CD Registers               |                                       | 2-50          |

|         | CC Register                       |                                       | 2-50          |

|         | CD Register                       |                                       | 2-50          |

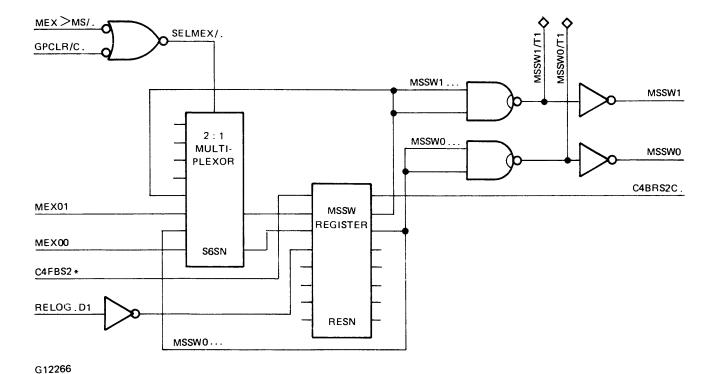

|         | MSSW Register                     |                                       | 2-51          |

|         | INCN Register                     |                                       | 2-52          |

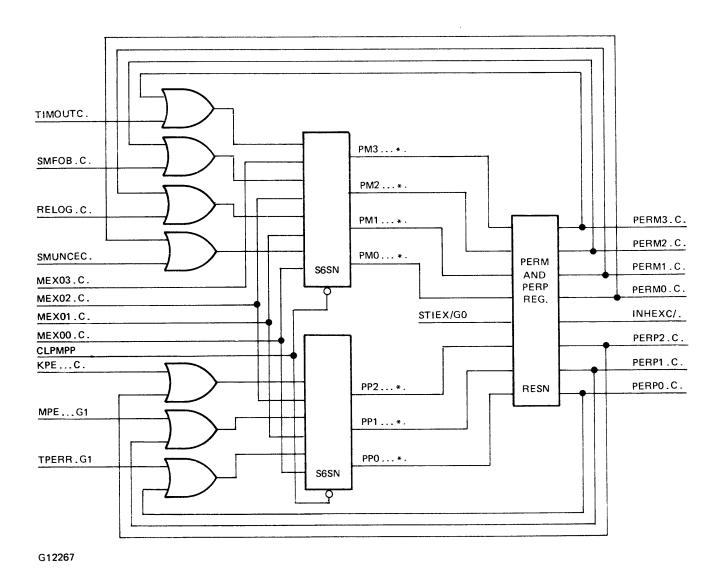

|         | PERM Register                     |                                       | 2-52          |

|         | PERP Register                     |                                       | 2-54          |

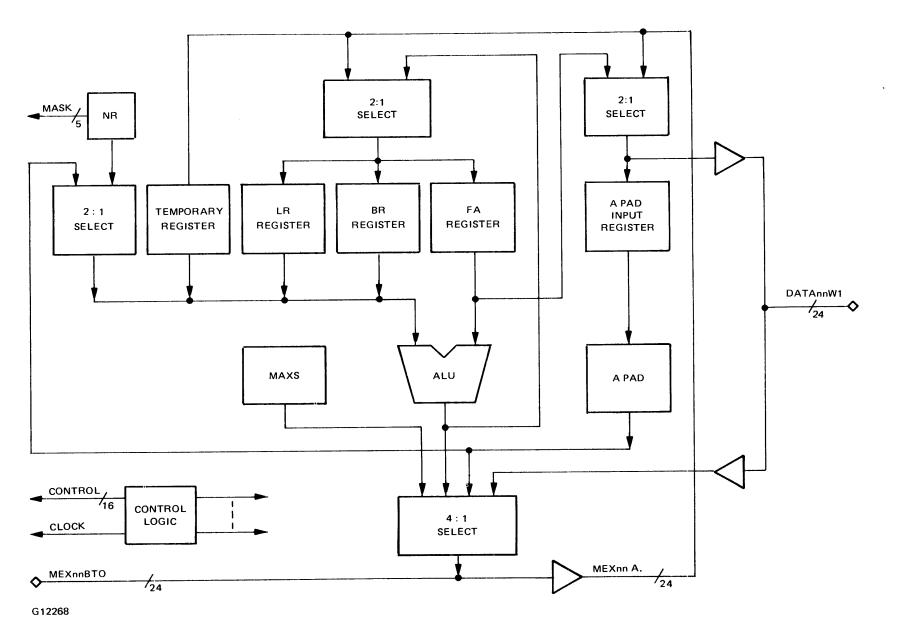

|         | Card A Functions                  |                                       | 2-54          |

|         | BR and LR Registers               |                                       | 2-54          |

|         | ra Kegister                       |                                       | 2-56          |

|         | MAXS Register                     |                                       | 2-57          |

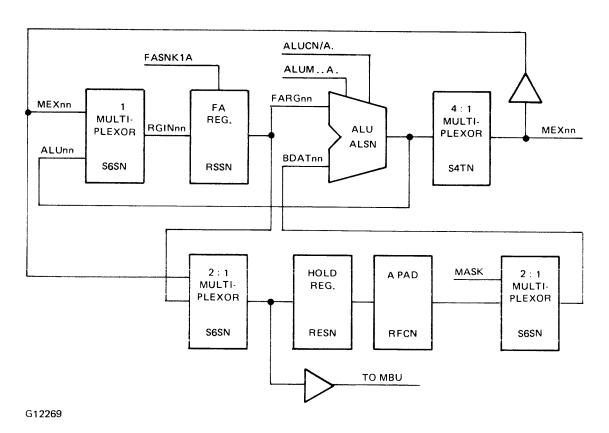

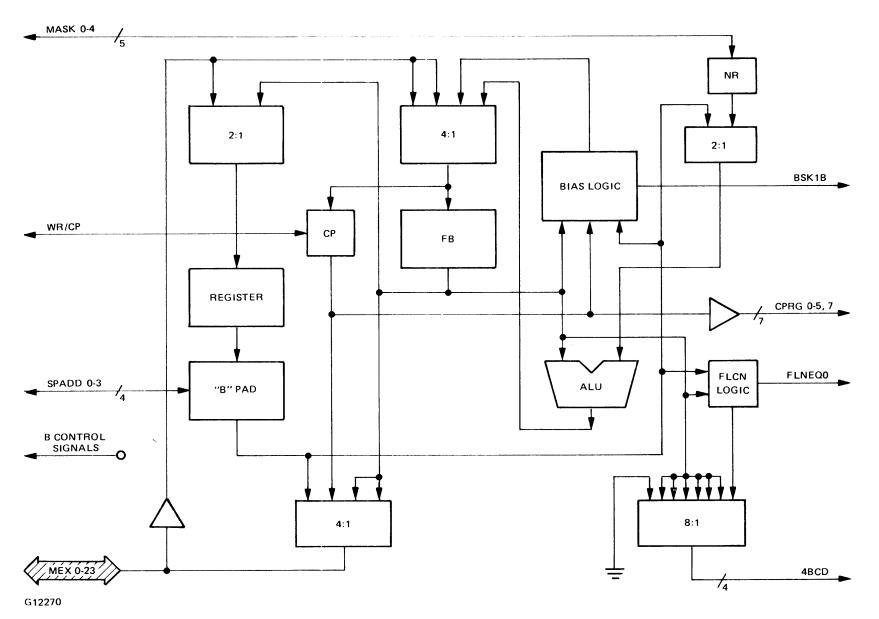

|         | Card B Functions                  |                                       | 2-57          |

|         | FB Register                       |                                       | 2-57          |

|         | FLCN Register                     |                                       | 2-59          |

|         | CP Register                       |                                       | 2-59          |

|         | Card Group D, E, F                |                                       | 2-59          |

|         | Card D                            |                                       | 2-60          |

|         | 4-Bit Data Source/Sink            |                                       | 2-60          |

|         | Null Register                     |                                       | 2-60          |

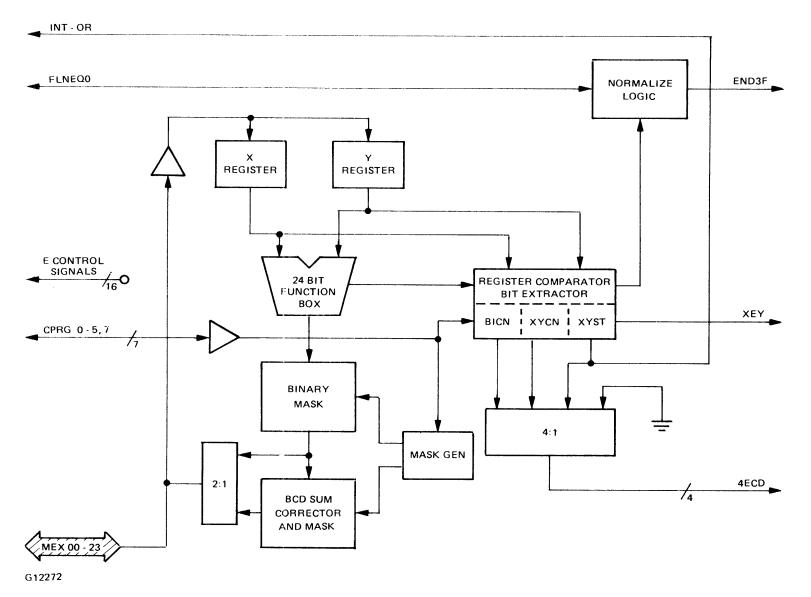

|         | Card E                            |                                       | 2-60          |

|         |                                   |                                       | 2-60          |

|         | 24-Bit Function Box               |                                       | 2-63          |

|         | Card F                            | · · · · · · · · · · · · · · · · · · · | 2-63          |

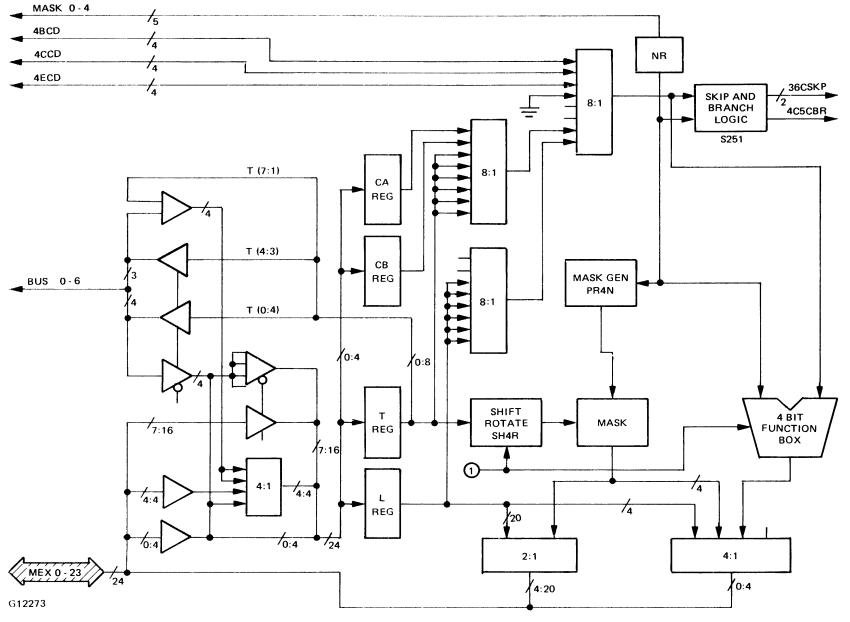

|         | T Register                        | · · · · · · · · · · · · · · · · · · · | 2-65          |

|         | L Register                        |                                       | 2-65          |

|         | G                                 |                                       | 2-65          |

|         | 4-Bit Function Box                | · · · · · · · · · · · · · · · · · · · | 2-65<br>2-66  |

|         |                                   |                                       | 4 <b>-0</b> 0 |

## **TABLE OF CONTENTS (Cont)**

| Section | Title                                        | Page         |

|---------|----------------------------------------------|--------------|

| •       | CIRCUIT OPERATIONAL DETAIL - B 1900 S-MEMORY | 3-1          |

| 3       | Introduction                                 | 3-1          |

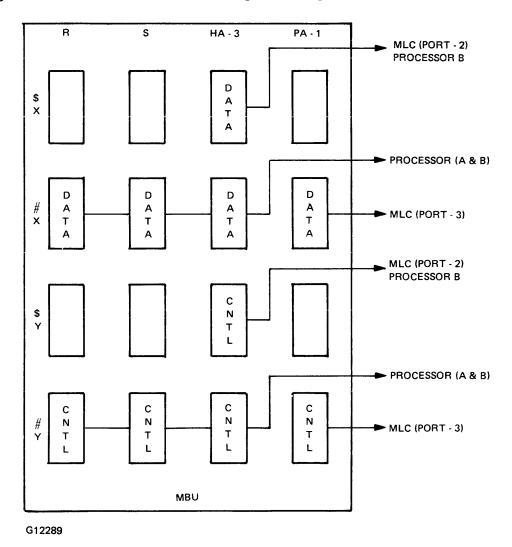

|         | S-Memory Storage Architecture                | 3-1          |

|         | Error Correction Code                        | 3-5          |

|         | MBU Operations                               | 3-6          |

|         | Refresh                                      | 3-7          |

|         | Micro Fetch (Micro-operator Stream Mode)     | 3-7          |

|         | Defined Field Read                           | 3-7          |

|         | Defined Field Write                          | 3-7          |

|         | Defined Field Swap                           | 3-8          |

|         | 22-Bit Read (Diagnostic Read)                | 3-8          |

|         | 22-Bit Write (Diagnostic Write)              | 3-8          |

|         | Echo Write Data                              | <b>3-9</b>   |

|         | Echo Write Data                              | 3-9          |

|         |                                              | 3-9          |

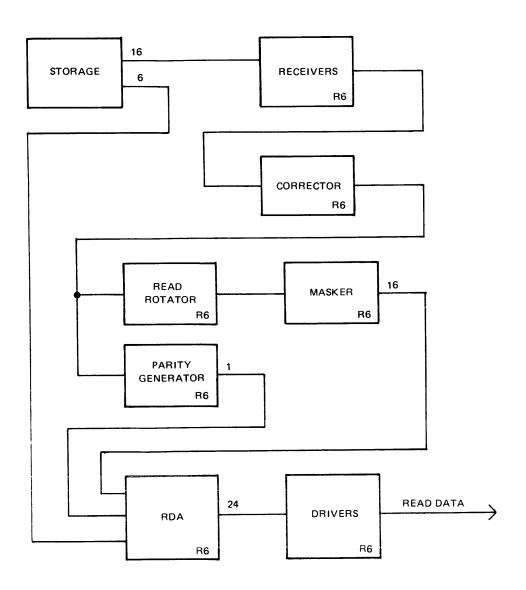

|         | Read and Clear Error Log                     | 3-9          |

|         | No-Op (Host Adapter Diagnostic)              | 3-9          |

|         | Dispatch Read                                | 3-10         |

|         | Dispatch Write                               | 3-10         |

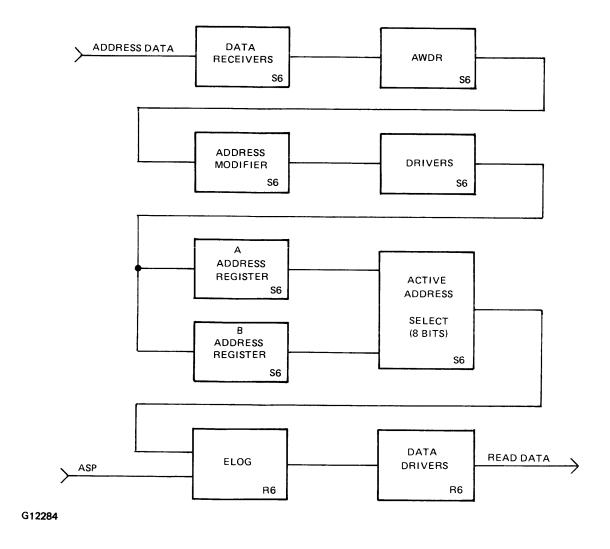

|         | MBU Functional Detail                        | 3-10         |

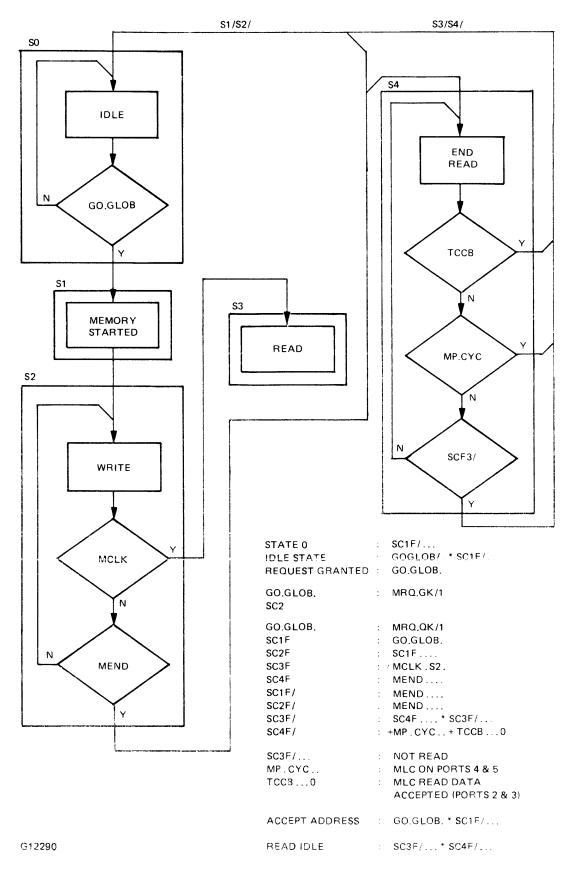

|         | Memory Cycle Initiation                      | 3-10<br>3-10 |

|         | State Machine                                | 3-10<br>3-20 |

|         | Address Loading and Modification             |              |

|         | Address Register Characteristics             | 3-20         |

|         | Address Modification                         | 3-20         |

|         | Address Out-of-Bounds                        | 3-21         |

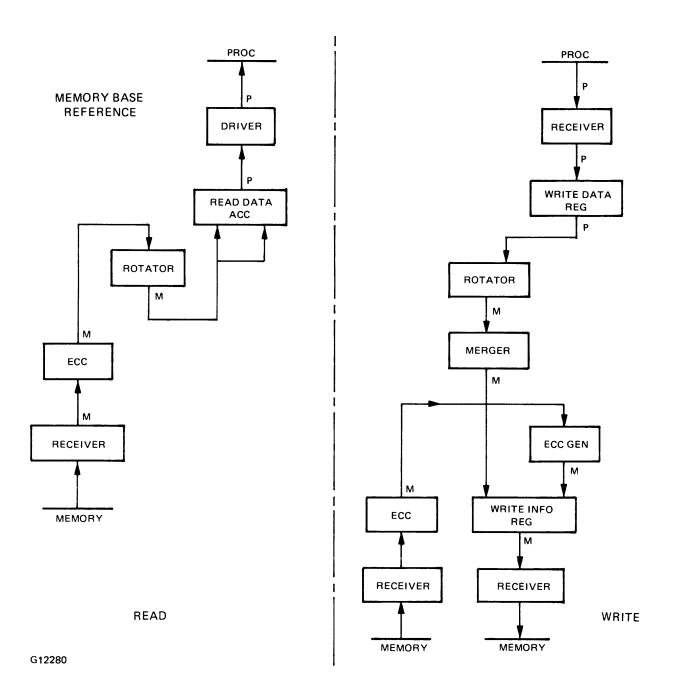

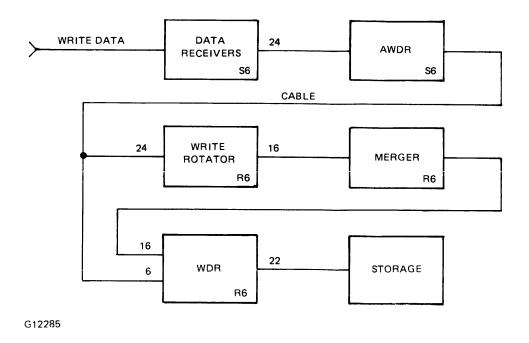

|         | Read Data                                    | 3-22         |

|         | Read Data Selection                          | 3-22         |

|         | Syndrome Generation                          | 3-22         |

|         | Syndrome Decode and Error Correction         | 3-22         |

|         | Error Correction                             | 3-23         |

|         | Read Data Rotation                           | 3-23         |

|         | Read Data Masking                            | 3-24         |

|         | Read Data Accumulator                        | 3-24         |

|         | Data Accumulation                            | 3-24         |

|         | Read Data Parity                             | 3-24         |

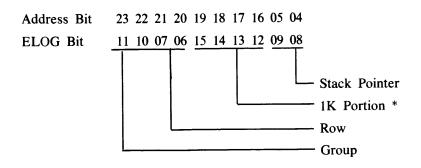

|         | Write Data                                   | 3-23         |

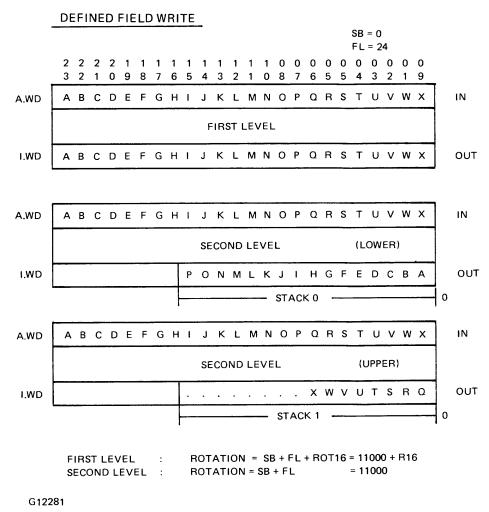

|         | Write Data Rotation                          | 3-25         |

|         | Write Data Rotation                          | 3-25         |

|         |                                              |              |

|         | Write Data Merger                            |              |

|         |                                              |              |

|         | Write Data Register                          | 3-29         |

|         | Rotation Control                             | 3-30         |

|         | Masking                                      | 3-30         |

|         | Mask Generator                               | ່ າ າາ       |

|         | Mask Control                                 | ່າວາ         |

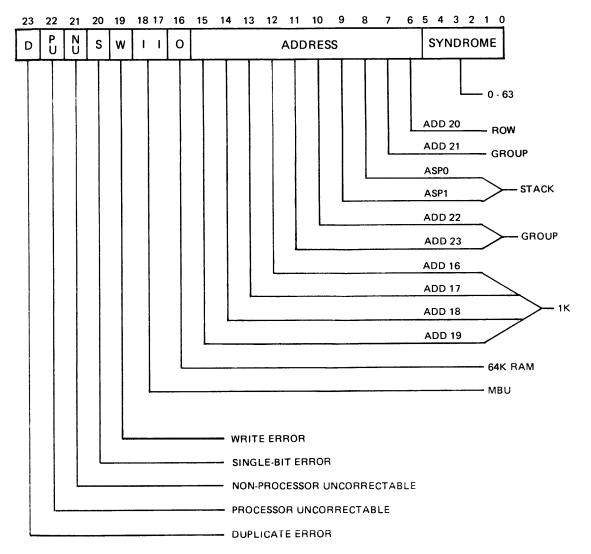

|         | Error Handling                               | 2 25         |

|         | Address Out-of-Bounds                        | 2 25         |

|         | Error Log Info mation                        | 226          |

|         | Diagnostic Logic                             | •            |

| 1127396 |                                              | vii          |

## **TABLE OF CONTENTS (Cont)**

| Section  |                                  | Title                                                                                                                | Page         |

|----------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------|

| 3        | CIRCUIT OPERATIONAL DETAIL - 1   | B 1900 S-MEMORY (Cont)                                                                                               |              |

|          |                                  |                                                                                                                      | 3-36         |

|          |                                  |                                                                                                                      | 3-30         |

|          | Write 22 Bits                    |                                                                                                                      | 3-38         |

|          | Read 22 Bits                     |                                                                                                                      | 3-38         |

|          | Read Error Log                   |                                                                                                                      | 3-39         |

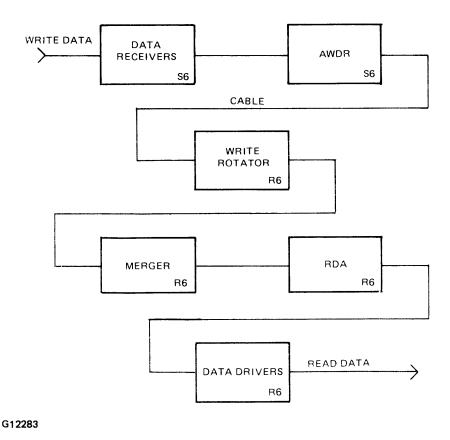

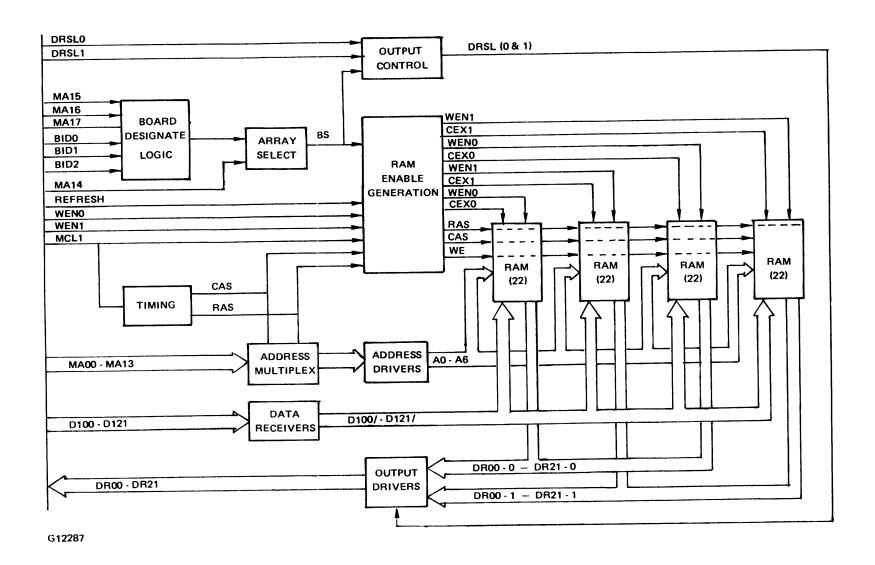

|          | Storage Board Functional Detail  |                                                                                                                      | 3-41         |

|          | Functions and Operations         |                                                                                                                      | 3-41         |

|          | Read Cycle                       |                                                                                                                      | 3-41         |

|          | Read-Modify-Write Cycle          |                                                                                                                      | 3-41         |

|          | Refresh Cycle                    |                                                                                                                      | 3-43         |

|          | System Commands                  |                                                                                                                      | 3-43         |

|          | Stream (Micro-Operator Fetch)    |                                                                                                                      | 3-43         |

|          |                                  |                                                                                                                      | 3-43         |

|          |                                  |                                                                                                                      | 3-43         |

|          |                                  |                                                                                                                      | 3-43<br>3-43 |

|          |                                  |                                                                                                                      | 3-43<br>3-43 |

|          | Storage Board Input Signals      |                                                                                                                      | 3-43         |

|          | Storage Board Output Signals     |                                                                                                                      | 3-45         |

|          | Addressing                       |                                                                                                                      | 3-45         |

|          |                                  |                                                                                                                      | 3-45         |

|          | Array and Word Selection         |                                                                                                                      | 3-45         |

|          | Board Designation                |                                                                                                                      | 3-45<br>3-45 |

|          |                                  |                                                                                                                      | 3-45<br>3-46 |

|          | Address Transfer Timing          |                                                                                                                      | 3-46<br>3-46 |

|          | Data-Out Drivers                 |                                                                                                                      | 3-46<br>3-46 |

|          | -5 Volt Monitor Circuit          |                                                                                                                      |              |

| 4        | CIRCUIT OPERATIONAL DETAIL =     | HOST ADAPTER-3                                                                                                       | 3-46         |

| ·        | Physical Characteristics         | ·····                                                                                                                | 4-1          |

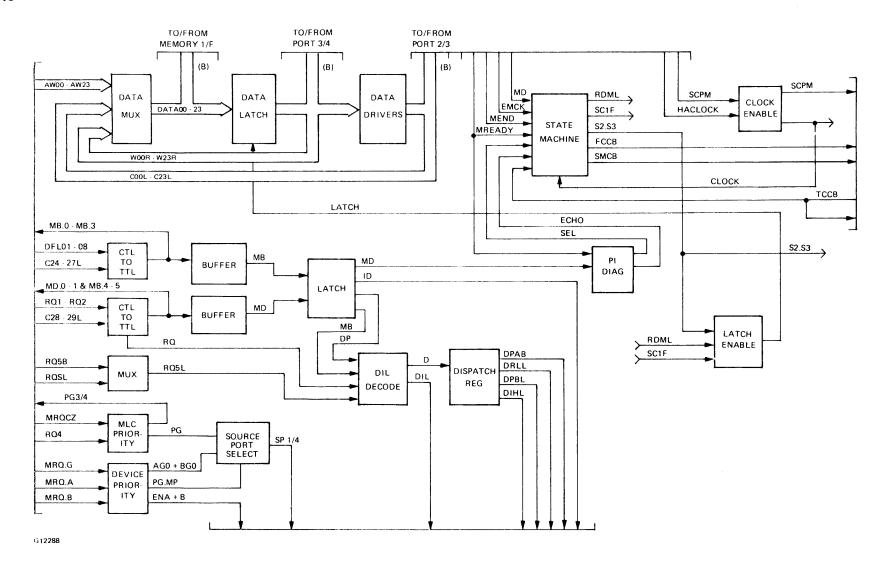

|          | Functional Characteristics       |                                                                                                                      | 4-3          |

|          | State Counter                    |                                                                                                                      | 4-8          |

|          | State 0 (S0)                     |                                                                                                                      | 4-8          |

|          | State 1 (S1)                     |                                                                                                                      | 4-8          |

|          | State 2 (S2)                     |                                                                                                                      | 4-8          |

|          |                                  |                                                                                                                      | 4-9          |

|          | State A (SA)                     |                                                                                                                      | 4-9          |

|          |                                  |                                                                                                                      | 4-9          |

|          |                                  | $\cdot \cdot $ | 4-9          |

|          |                                  |                                                                                                                      | 4-12         |

|          |                                  |                                                                                                                      | 4-15         |

|          | Processor Selection              |                                                                                                                      | 4-15         |

|          |                                  |                                                                                                                      | 4-18         |

|          |                                  |                                                                                                                      | 4-19         |

|          | Dispatch Register                |                                                                                                                      | 4-19         |

|          | Dispatch interrupt Level (DIL) . |                                                                                                                      | 4-20         |

|          |                                  |                                                                                                                      | 4-20         |

|          | Source Port Detection            |                                                                                                                      | 4-22         |

| <b>A</b> |                                  |                                                                                                                      | 4-24         |

| Α        | GLOSSARY OF TERMS                |                                                                                                                      | <b>A-1</b>   |

## LIST OF ILLUSTRATIONS

| Figure                   | Title                                                  | Page                      |

|--------------------------|--------------------------------------------------------|---------------------------|

| 2-1                      | B 1900 Diagnostic/Maintenance Panel                    | 2-3                       |

| 2-2                      | D/M Panel Cabling                                      |                           |

| 2-3                      | Console Switch Logic                                   | 2-5                       |

| 2-4                      | REGISTER GROUP Switch Schematic                        | 2-7                       |

| 2-5                      | REGISTER SELECT Switch Logic                           | 2-8                       |

| 2-6                      | HALT Push Button Logic                                 | 2-8                       |

| 2-7                      | RUN Indicator Logic                                    | 2-9                       |

| 2-8                      | ERROR Indicator Logic                                  | 2-9                       |

| 2-9                      | LOAD Push Button Logic                                 | 2-12                      |

| 2-10                     | INC Push Button Logic                                  | 2-13                      |

| 2-11                     | SINGLE MICRO/NORMAL Switch Logic                       | 2-13                      |

| 2-12                     | OVER TEMP Circuit Logic                                | 2-15                      |

| 2-13                     | CLEAR Push Button Logic                                | 2-17                      |

| 2-14                     | START Push Button Logic                                | 2-18                      |

| 2-15                     | INTERRUPT Switch Logic                                 | 2-19                      |

| 2-16                     | Functional Block Diagram of Clock Card (Card K)        | 2-20                      |

| 2-17                     | Clock Generation (A) and Calibration, Distribution (B) | 2-21                      |

| 2-18                     | Clock Waveforms                                        | 2-23                      |

| 2-19                     | Data Routing to the Main Exchange                      | 2-24                      |

| 2-20                     | Block Diagram, B 1900 Processor                        | 2-25                      |

| 2-21                     | Functional Block Diagram of Card G                     | 2-27                      |

| 2-22                     | Fetch Structure                                        | 2-31                      |

| 2-23                     | U Register Logic                                       | 2-34                      |

| 2-24                     | Functional Block Diagram of Card H                     | 2-35                      |

| 2-25                     | Cache Memory Organization                              | 2-36                      |

| 2-26                     | Cache Memory Layout                                    | 2-37                      |

| 2-27                     | Cache Key Compare Logic                                | 2-38                      |

| 2-28                     | Console Lamp Display of Cache Key                      | 2-39                      |

| 2-29                     | M Register Logic                                       | 2-40                      |

| 2-30                     | Functional Block Diagram of Card J                     | 2-41                      |

| 2-31                     | A Register Block Diagram                               | 2-42                      |

| 2-32                     | Examples of Pushing Into and Popping from A-Stack      | 2-44                      |

| 2-33                     | A-Stack Block Diagram                                  | 2-45                      |

| 2-34                     | Signal Flow for a Pop                                  | 2-45                      |

| 2-35                     | Signal Flow for a Push                                 | 2-45<br>2-48              |

| 2-36                     | Scratchpad Layout                                      | 2 <del>-4</del> 6<br>2-49 |

| 2-37<br>2-38             | MSSW Register Logic                                    | 2-49                      |

| 2-38<br>2-39             | PERM and PERP Register Logic                           | 2-51                      |

| 2-39<br>2-40             | Functional Block Diagram of Card A                     | 2-55                      |

| 2-40<br>2-41             | FA Register Logic                                      | 2-56                      |

| 2-41<br>2-42             | Functional Block Diagram of Card B                     | 2-58                      |

| 2-42                     | Functional Block Diagram of Card D                     | 2-38                      |

| 2-43<br>2-44             | Functional Block Diagram of Card E                     | 2-62                      |

| 2- <del>44</del><br>2-45 | Functional Block Diagram of Card F                     | 2-64                      |

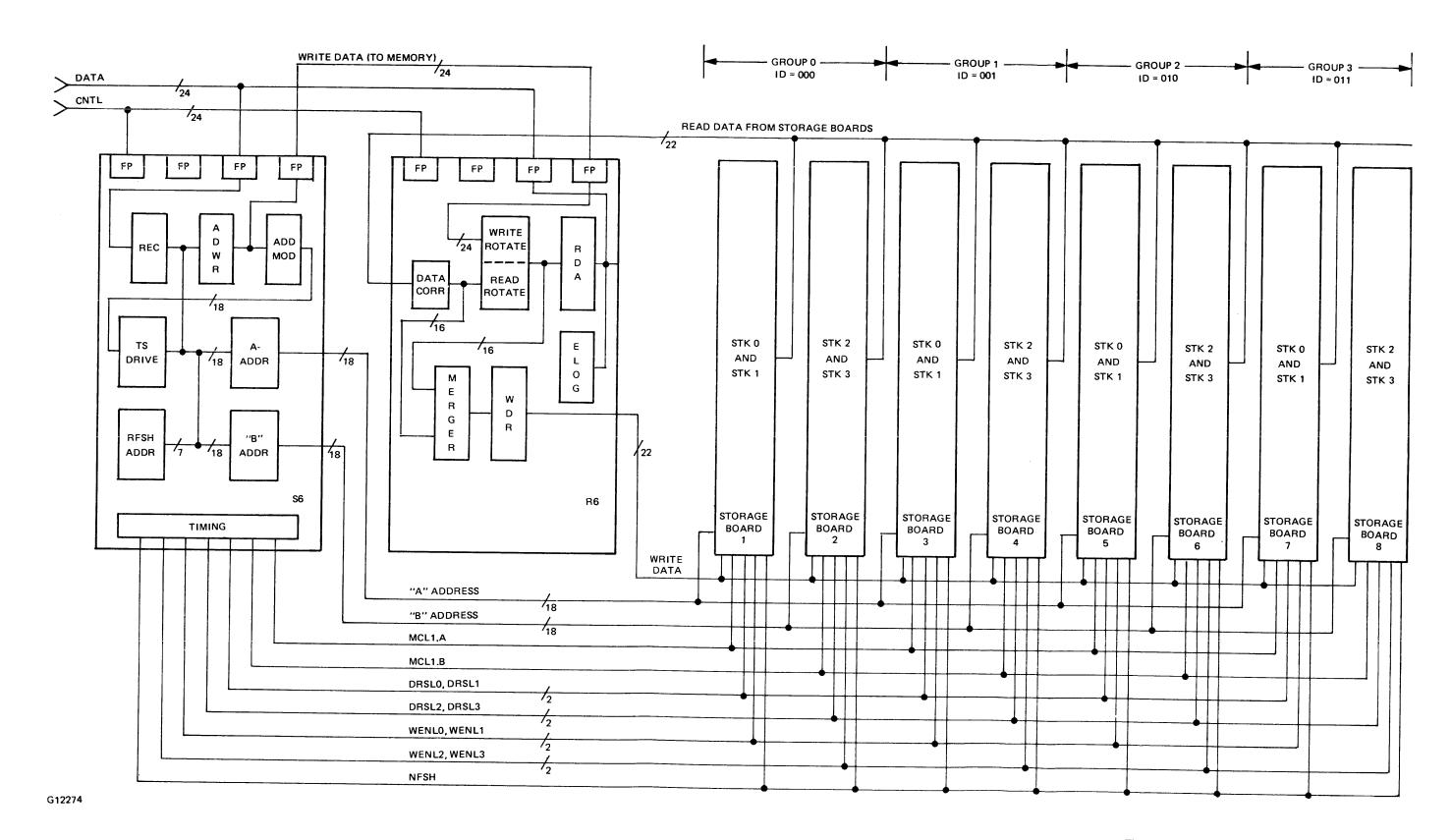

| 3-1                      | B 1900 S-Memory Organization                           | 3-3                       |

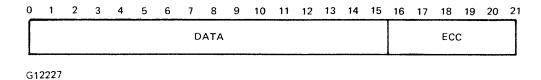

| 3-1                      | 22-Bit Storage Word                                    | 3-5                       |

| 3-2                      | Diagnostic Read/Write Data Format                      | 3-9                       |

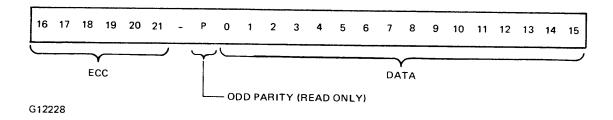

| 3-4                      | B 1900 MBU, Functional Block Diagram                   | 3-11                      |

| 1127396                  | ,                                                      | <i>3 11</i>               |

## **LIST OF ILLUSTRATIONS (Cont)**

Title

**Figure**

Page

|            |                                                                         | _    |

|------------|-------------------------------------------------------------------------|------|

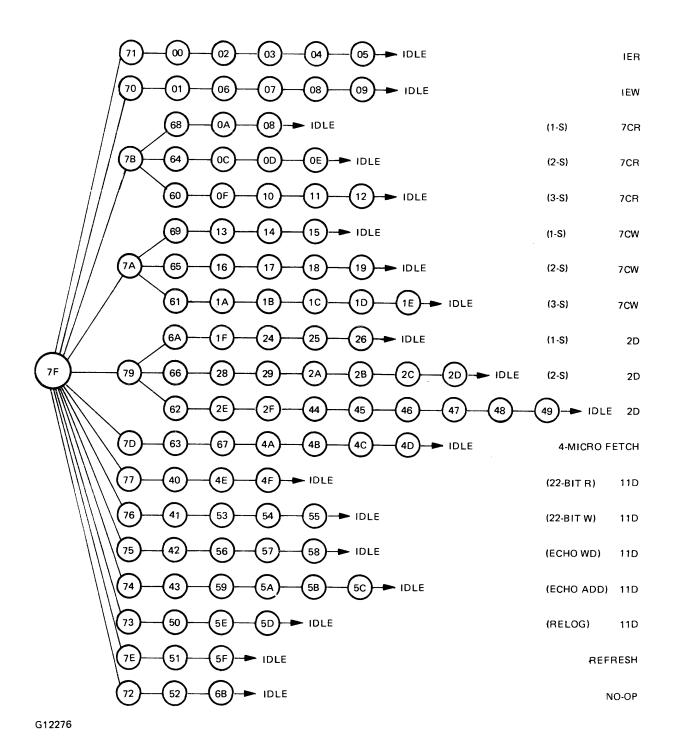

| 3-5        | State Machine Flow, Card S6                                             | 3-13 |

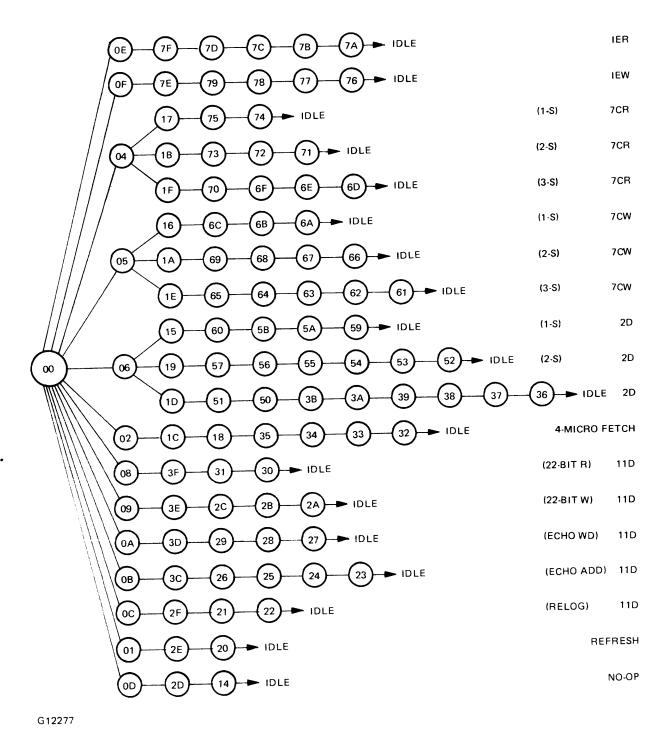

| 3-6        | State Machine Flow, Card R6                                             |      |

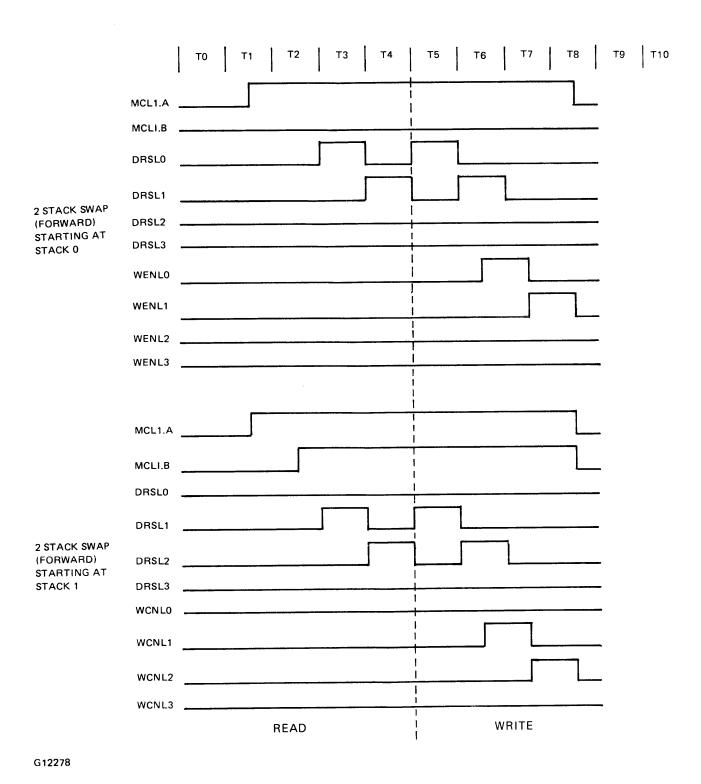

| 3-7        | Swap Timing (2-Stack Forward)                                           |      |

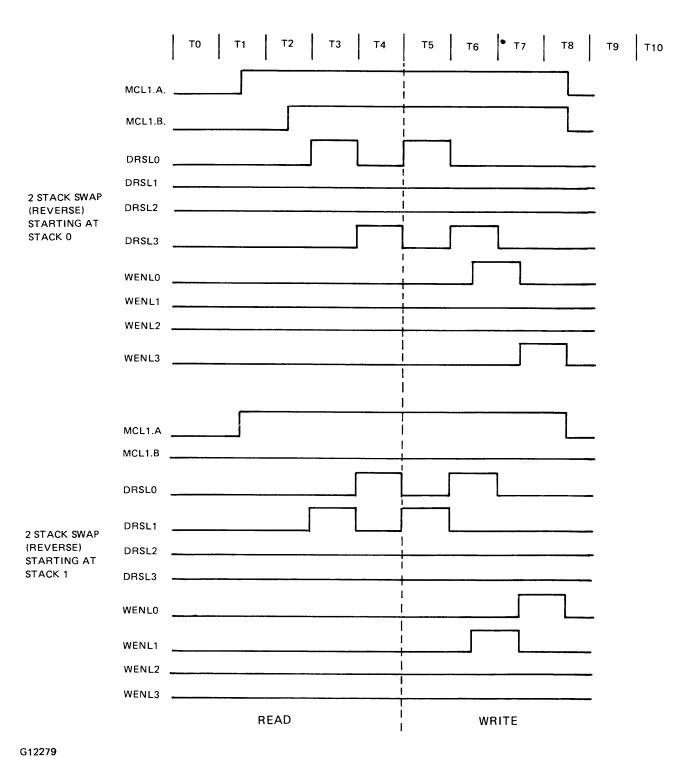

| 3-8        | Swap Timing (2-Stack Reverse)                                           |      |

| 3-9        | Memory/Processor Referencing                                            |      |

| 3-10       | Write Rotator Function                                                  | 3-27 |

| 3-11       | Error Log Register                                                      | 3-34 |

| 3-12       | 11D Echo Write Data Path                                                | 3-36 |

| 3-13       | 11D Echo Address Data Path                                              | 3-37 |

| 3-14       | 11D Write 22 Bits Data Path                                             | 3-39 |

| 3-15       | 11D Read 22 Bits Data Path                                              | 3-40 |

| 3-16       | Functional Block Diagram, B 1900 Storage Board                          |      |

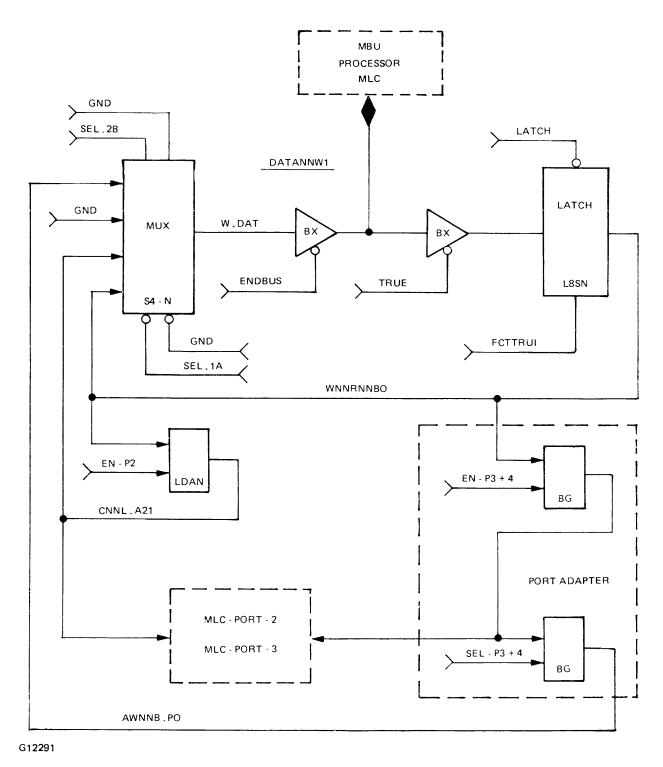

| 4-1        | HA-3 Functional Block Diagram                                           | 4-2  |

| 4-1<br>4-2 | HA-3 Frontplane Cabling                                                 | 4-3  |

| 4-2        |                                                                         | 4-10 |

| 4-3<br>4-4 | HA-3 State Flows                                                        |      |

|            | HA-3 Data Paths                                                         |      |

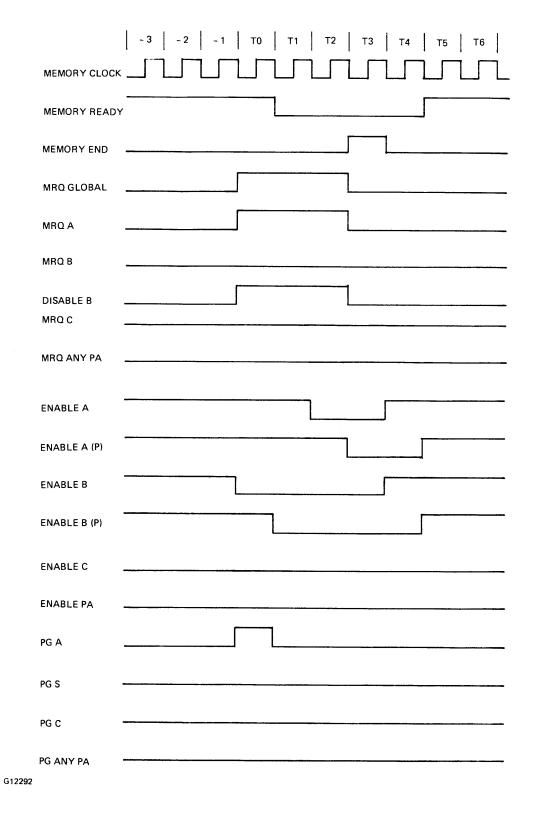

| 4-5        | S-Memory Request Sequence for Processor A                               |      |

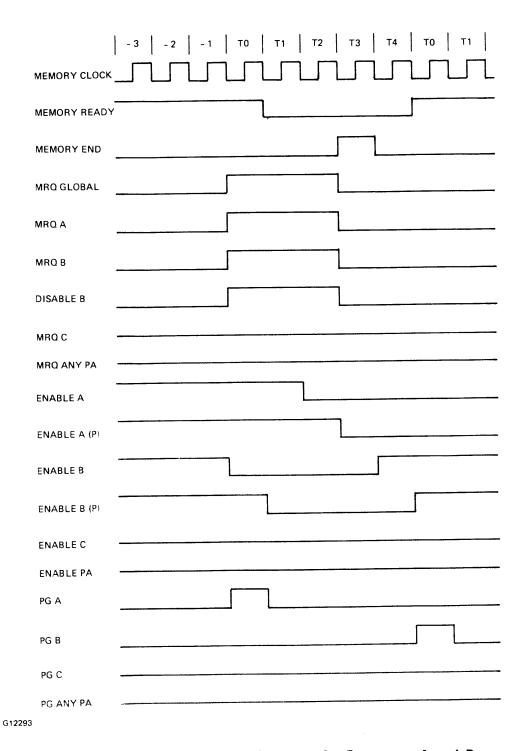

| 4-6        | S-Memory Request Sequence for Processors A and B                        |      |

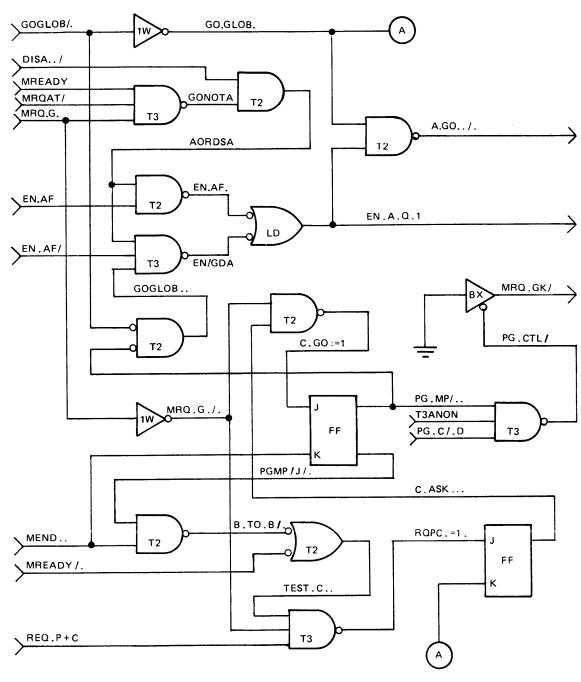

| 4-7        | Memory Request Priority Logic                                           | 4-16 |

| 4-8        | Processor Selection Logic for Memory Access Priority                    |      |

| 4-9        | Dispatch Interrupt Logic                                                | 4-21 |

| 4-10       | Port Absent Detection                                                   |      |

| 4-11       | Source Port Detection                                                   |      |

| 4-12       | Diagnostic Read FALSE Level (data path)                                 |      |

| 4-13       | Diagnostic Echo Write Data (all variants)                               |      |

| 4-14       | Diagnostic Read or Echo Latch                                           | 4-27 |

| 4-15       | Diagnostic Echo Port 3 or 4 (PA-1)                                      |      |

| 4-16       | Diagnostic Echo Port 2                                                  |      |

| 4-17       | Memory Read Data to Port 3 or 4 (PA-1)                                  |      |

| 4-18       | Memory Read Data to Port 2                                              |      |

| 4-19       | Address and Write Data to MBU from Port 2                               |      |

| 4-20       | Address and Write Data to MBU from Port 3 or 4                          | 4-33 |

|            | LIST OF TABLES                                                          |      |

| Table      | Title                                                                   | Page |

| 2-1        | REGISTER GROUP/REGISTER SELECT Switch Combinations                      | 2.5  |

| 2-1        | LOAD Push Button: Console Switch Contents Loading                       |      |

| 2-2        | Displaying Cache, S-Memory, and ELOG After Using LOAD to Load Addresses |      |

| 2-3<br>2-4 | Actions With REGISTER SELECT at Position 6                              |      |

| 2-4<br>2-5 | Interaction Between SINGLE MIC/NORMAL and MODE Switches                 |      |

| 2-6        | MICRO SOURCE Switch Position Codes and Meanings                         |      |

| 2-6<br>2-7 | Results of Bit-ORing MICRO SOURCE and MSSW                              |      |

| 2-7<br>2-8 | CPU and CPL Control over ALU Results                                    |      |

|            |                                                                         |      |

| 3-1        | Check Bit Generation                                                    |      |

| 3-2        | Syndrome Generation                                                     | 3-5  |

| X          |                                                                         |      |

## LIST OF TABLES (Cont)

| Table | Title                                              | Page   |

|-------|----------------------------------------------------|--------|

| 3-3   | Syndrome Patterns for Single-Bit Errors            | . 3-6  |

| 3-4   | MBU Operations                                     | 3-6    |

| 3-5   | State Sequence for a 2-Stack Read                  | 3-15   |

| 3-6   | Data Cable Signal Description                      | 3-16   |

| 3-7   | Control Cable Signal Descriptions                  | . 3-17 |

| 3-8   | Address Modification                               | 3-21   |

| 3-9   | Error Correction Truth Table                       | 3-23   |

| 3-10  | Rotation and Masking Equations                     | 3.29   |

| 3-11  | Starting Mask Truth Table                          | 2.31   |

| 3-12  | Ending Mask Truth Table                            | . 3-32 |

| 3-13  | ELOG Echo Address Bits                             | 2.38   |

| 4-1   | MBU to HA-3 Control Cable (Daisy-Chained to Users) | A_A    |

| 4-2   | MLC and Processor B Control Cable and Data Cable   | . 4-5  |

| 4-3   | HA-3 Frontplane Pin Assignments                    | 1.6    |

| 4-4   | HA-3 Backplane Pin Assignments                     | . 4-7  |

| 4-5   | Request Level Coding                               | 412    |

| 4-6   | 11D Micro Operations affecting HA-3                | . 4-24 |

1127396

# SECTION 1 BASIC PRINCIPLES

This FETM includes information on B 1905 and B 1955 single-processor systems as well as the B 1985 dual-processor system.

Material that would ordinarily be included in this section is adequately covered in the B 1900 Central Systems Technical Manual, Volume 1, Operation and Maintenance, Form No. 1127388.

Other material pertinent to B 1900 Central Systems is included in the following three manuals:

- 1. B 1800 Series Central Systems Technical Manual, Volume 1, Operation and Maintenance; Form No. 1098282.

- 2. B 1800 Series Central Systems Technical Manual, Volume 3, Theory of Operation; Form No. 1095551.

- 3. B 1700 I/O Base Technical Manual; Form No. 1053352.

1127396

## SECTION 2 CIRCUIT OPERATIONAL DETAIL

#### INTRODUCTION

This section provides detailed descriptions of the circuits and operation of the B 1900 processor, S-Memory, and Host Adapter. The processor description includes discussions of the console interface logic, the system clock, the microinstruction fetch-decode-execute structure, Cache Memory, the processor registers, the 4-bit and 24-bit function boxes, and the I/O and S-Memory interfaces.

Also presented is a discussion of the I/O Distribution Card and signal distribution within the I/O Base. Not described are the circuits and functions of the individual I/O controls, which are described in individual technical manuals.

#### CONSOLE INTERFACE LOGIC

The console controls represent an extension of the processor control logic that allows manual selection of micro-operator functions. The console provides an operator interface with the processor and permits overall control of system operation, monitoring of processor activity, and maintenance/testing procedures. The majority of actions that can be initiated from the console can also be specified by microinstructions.

The console controls are grouped into two panels: the Operator (Op) panel and the Diagnostic/Maintenance (D/M) panel. In the B 1985 and B 1955, all six push buttons (POWER, INTRPT, CLEAR, START, MODE, REWIND) of the Op panel are in a strip in the top right corner of the cabinet. In the B 1905, the Op panel is distributed: the POWER and INTRPT push buttons are on the left side of the ODT keyboard and the other four push buttons are adjacent to the cassette drive unit, which is behind the front access door and above the D/M panel.

#### **Operator Panel**

The Op panel provides basic functional access to the processor. The panel includes six function switches with integral indicators:

| Switches | Indicators  |

|----------|-------------|

| POWER    | (red light) |

| INTRPT * | RUN         |

| CLEAR *  |             |

| START *  | TEST STATE  |

| MODE     | NORMAL/MTR  |

| REWIND   | BOT         |

|          |             |

<sup>\*</sup> Duplicated on D/M panel

Functions that are duplicated on the D/M panel are discussed in the subsection titled Duplicate Console Functions.

1127396

#### **TEST STATE Indicator**

A lighted TEST STATE indicator in the START push button indicates that the processor is in a state other than the normal execution state. Several conditions can enable the TEST STATE indicator:

INTERRUPT switch on D/M panel is up. (CC register bit 3 = 1.) SINGLE MICRO/NORMAL switch is at SINGLE MICRO. MICRO SOURCE switch is not at NORMAL.

#### MODE Push Button, NORMAL/MTR Indicators

The MODE push button allows the operator to select the processor's operating mode, and the indicators NOR-MAL/MTR show the current mode. In NORMAL mode, processor logic is configured to accept microinstructions from Cache or S-Memory; in MTR mode, the logic is configured to accept microinstructions from cassette tape.

If MODE is pressed while NORMAL is lighted, the MTR mode is entered. Normally-open contacts close and +12V is applied to the MTR lamp. Also, a TRUE level is removed from the NORMAL net. This net is routed through the cassette logic and D/M panel logic where it is ORed with the SINGLE MIC/NORMAL switch. If this switch is at SINGLE MIC, data movement from cassette to processor is inhibited. SINGLE MIC puts the processor into step operation; that is, each time START is pressed, one micro is executed and the processor halts. NORMAL on the SINGLE MIC/NORMAL switch signifies continuous micro execution.

If MODE is pressed with MTR lighted, processor logic is returned to the normal configuration and micros are accepted from Cache or S-Memory, as specified by the MICRO SOURCE switch or the MSSW register.

#### BOT/RWD Push Button/Indicator

Pressing BOT/RWD provides a signal to rewind the magnetic tape cassette. The BOT indicator is off if the tape is not completely rewound and goes on when the tape reaches the beginning-of-tape marker and stays on until the tape moves off the marker.

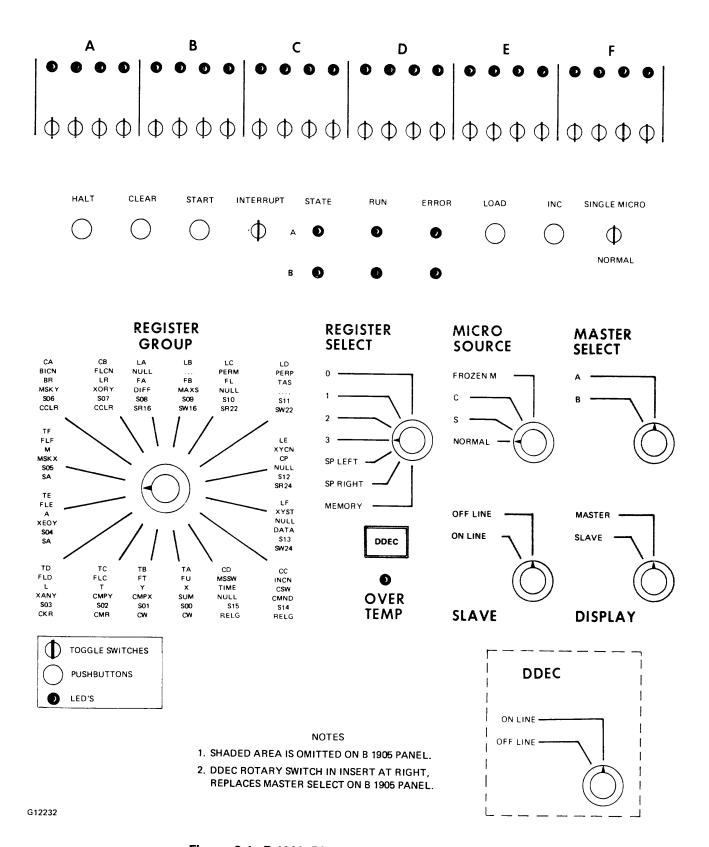

#### Diagnostic/Maintenance Panel

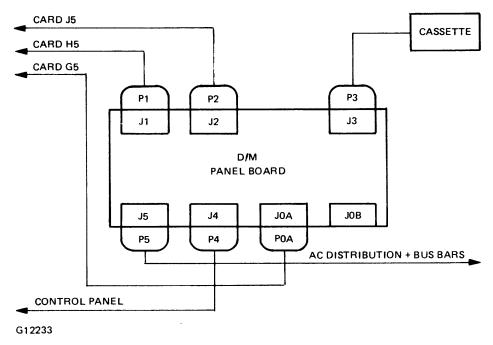

The D/M panel (Figure 2-1) is used primarily for diagnosing system failures, testing circuit functions, and making temporary software changes. The panel is available for use by system operators and programmers as well as field engineers. Figure 2-2 shows how the D/M panel is cabled into the processor.

The D/M panel provides the following functions:

#### **All Systems**

24 Console Switches24 Console Lamps

Push Buttons: HALT, CLEAR, START, LOAD, INC Toggle Switches: INTERRUPT, SINGLE MIC/NORMAL

Rotary Switches: REGISTER GROUP, REGISTER SELECT, MICRO SOURCE

Indicators: STATE, RUN, ERROR, OVER TEMP

**B 1905**

Rotary Switch: DDEC (ON LINE/OFF LINE)

B 1955 and B 1985

Rotary Switches: MASTER SELECT, SLAVE, DISPLAY Push Button Indicator: DDEC (ONLINE/OFFLINE) Indicators (second set): STATE, RUN, ERROR

Figure 2-1. B 1900 Diagnostic/Maintenance Panel

Figure 2-2. D/M Panel Cabling

#### Console Lamps

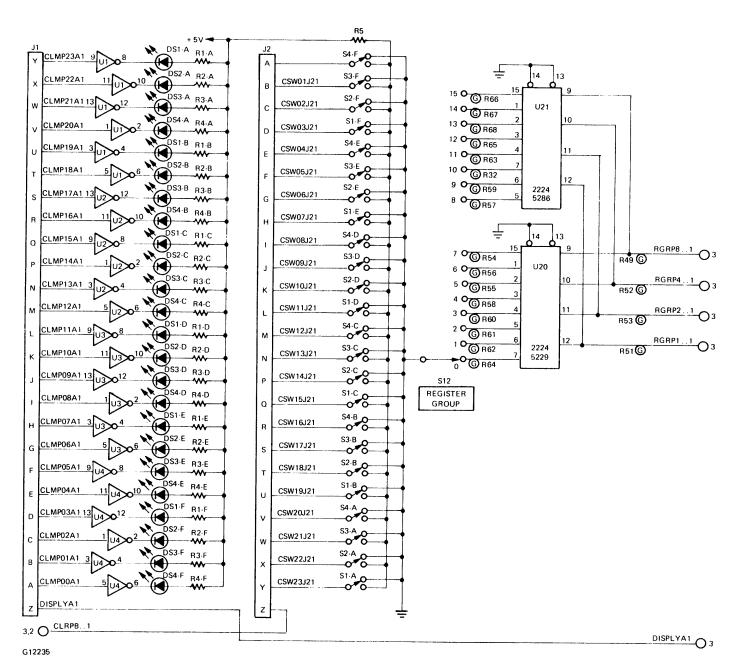

The 24 console lamps are light-emitting diodes (LEDs) that can display the contents of selected registers and memory locations when the processor is halted.

The enable signal for the console lamps is a nanoregister output, a signal that allows the contents of the MEX to be latched and routed to the console lamps.

#### Console Switches

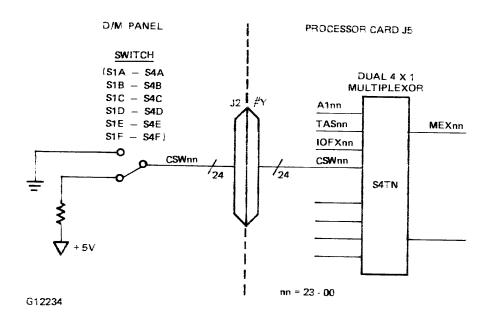

The 24 console switches are 2-position toggles that provide a TRUE output in the up (ON) position. The switches are used to enter data for loading registers or to provide data for console writes to Cache or S-Memory.

Figure 2-3 illustrates the means by which the console switches enable data to the processor through card J. For simplicity, the logic for only one switch is shown. When a console switch is moved to the up (ON) position, a TRUE is applied to the 4-to-1 multiplexer on card J. Select lines and output control lines determine which input is gated to the multiplexor outputs.

Figure 2-3. Console Switch Logic

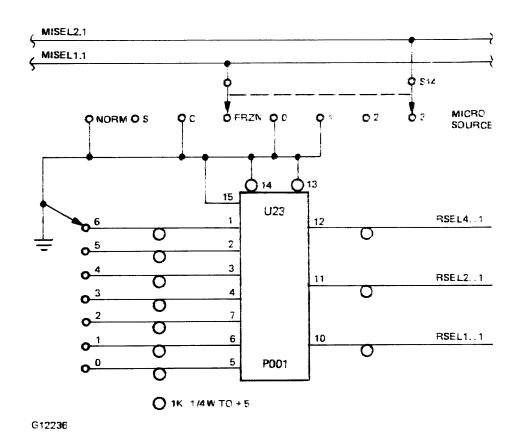

## REGISTER GROUP and REGISTER SELECT Switches

These two rotary switches are used together to provide selection of a total of 112 (16 X 7) possible conditions. REGISTER GROUP (RG) has 16 functional positions. The position labeled TA is considered position 0; clockwise rotation takes the switch through positions 1 to 15. REGISTER SELECT (RS) has seven positions, 0 through 6 reading down. Table 2-1 lists the specific entities and functions available with each combination of settings of the two switches.

Table 2-1. REGISTER GROUP/REGISTER SELECT Switch Combinations

| REGISTER<br>GROUP  |    |      | REGISTE | ER SELECT S | vitch Position |             | -      |

|--------------------|----|------|---------|-------------|----------------|-------------|--------|

| Switch<br>Position | 0  | 1    | 2       | 3           | SP<br>LEFT     | SP<br>RIGHT | MEMORY |

| 0                  | TA | FU   | X       | SUM         | S00A           | S00B        | CW     |

| 1                  | TB | FT   | Y       | CMPX        | SOLA           | SOIB        | CW     |

| 2                  | TC | FLC  | T       | CMPY        | S02A           | S02B        | CMR    |

| 3                  | TD | FLD  | L       | XANY        | S03A           | S03B        | CKR    |

| 4                  | TE | FLE  | A       | XEOY        | S04A           | S04B        | SA     |

| 5                  | TF | FLF  | M       | MSKX        | S05A           | S05B        | SA     |

| 6                  | CA | BICN | BF      | MSKY        | S06A           | S06B        | SA     |

| 7                  | CB | FLCN | LR      | XORY        | S07A           | S07B        | CCLR   |

| 8                  | LA | NULL | FA      | DIFF        | S08A           | S08B        | SR16   |

| 9                  | LB |      | FB      | MAXS        | S09A           | S09B        | SW16   |

| 10                 | LC | PERM | FL      | NULL        | S10A           | S10B        | SR22   |

| 11                 | LD | PERP | TAS     |             | SILA           | SIIB        | SW22   |

| 12                 | LE | XYCN | CP      | NULL        | S12A           | S12B        | SR24   |

| 13                 | LF | XYST | NULL    | DATA        | S13A           | S13B        | SW24   |

| 14                 | CC | INCN | CSW     | CMND        | S14A           | S14B        | RELG   |

| 15                 | CD | MSSW | TIME    | NULL        | S15A           | S15B        | RELG   |

All possible combinations of positions 0, 1, 2, and 3 of RS and positions 0-15 of RG define all the addressable registers and allow them to be selected for display or modification. The binary values of the RG/RS combinations also are used in certain micros to address specific registers. While the processor is in HALT, the contents of the particular register selected are displayed in the console lamps and the register is available for loading from the console switches.

Combinations of positions 4 (SP LEFT) and 5 (SP RIGHT) of RS with positions 0-15 of RG address each of the 16 left and 16 right Scratchpad words.

Combinations of position 6 (MEMORY) of RS and positions 0-15 of RG enable certain Cache and S-Memory operations and allow examination of the Error Log (ELOG) register.

Figure 2-4 is a schematic representation of the REGISTER GROUP switch and Figure 2-5 shows the REGISTER SELECT switch logic. Switch positions are interpreted binarily: the four lines from RG provide 0000-1111 and the three lines from RS provide 000-111. The output lines are gated to PROMs for decoding into the various control lines that perform the function or address the register specified by the switches.

These switches are discussed in greater detail in the subsection titled LOAD Push Button.

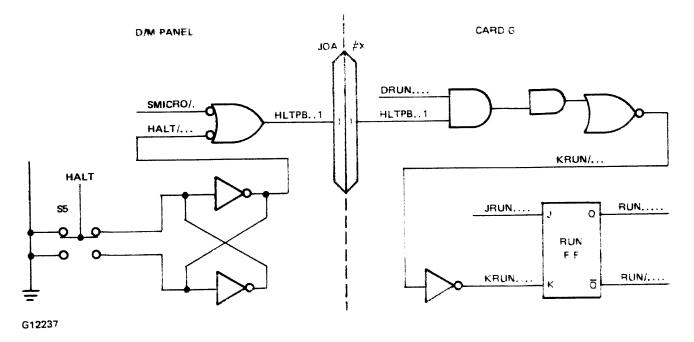

#### **HALT Push Button**

HALT is a momentary push button that is used to halt the system. The processor, upon receipt of the halt signal, completes the micro presently in the execute phase and comes to an orderly halt. Figure 2-6 shows the logic of the HALT push button circuit

In the figure, the switch (S5) is shown in its normal (RUN) position. Pressing HALT applies a LOW to an RS-type flip-flop which causes signal HALT/... to go LOW, setting the Halt Request to halt the processor after execution of the current micro.

#### STATE Indicator

The STATE indicator, when lit, indicates that bit 03 of the CC register is set. Control of this lamp is dependent entirely on the software, which must programmatically control the setting or re-setting of bit 03.

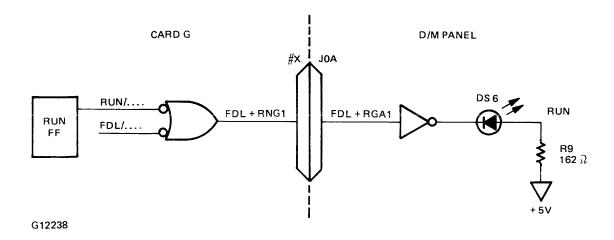

#### **RUN Indicator**

The RUN indicator is used to show that the processor is in the RUN state in NORMAL mode or that the cassette is being driven forward in the MTR mode. The lamp is driven by a term called FDL+RNG1 from card G5. Figure 2-7 illustrates the logic for the RUN indicator.

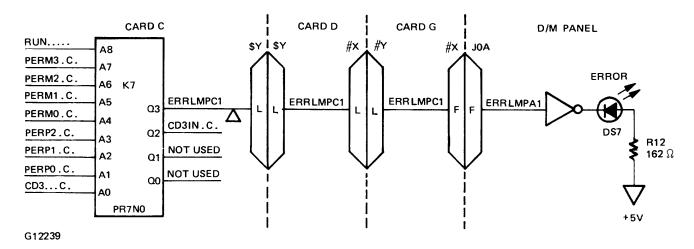

#### **ERROR** Indicator

The ERROR indicator lights as the result of the detection of any one of several errors that turn on one or more bits in the PERM and PERP registers. PERP and PERM bits have the following meanings:

- PERP bit 3 Always reset (0)

- 2 Cache Key parity error

- 1 M-Register parity error

- 0 Uncorrectable cassette error

- PERM bit 3 Microinstruction time-out

- 2 S-Memory field out of physical bounds

- 1 S-Memory Error Log register change

- 0 Uncorrectable S-Memory error in processor operation

Figure 2-4. REGISTER GROUP Switch Schematic

Figure 2-5. REGISTER SELECT Switch Logic

Figure 2-6. HALT Push Button Logic

Figure 2-7. RUN Indicator Logic

The processor comes to an immediate halt if PERP bit 2 or 1 or 0 or PERM bit 3 goes TRUE, or if PERM bit 2 goes TRUE on a micro fetch operation. The processor comes to a controlled MCP halt if PERM bit 2 or 0 goes TRUE on a deta operation. When PERM bit 1 goes TRUE, the Error Log is updated.

Figure 2-8 shows the ERROR indicator control logic. Note that each of the PERM and PERP register bits is an input to a PROM. The presence of a TRUE level on any of these lines results in the indicator lighting when the processor halts, that is, term RUN..... goes LOW.

Figure 2-8. ERROR Indicator Logic

1127396 2-9

#### LOAD Push Button

LOAD is a momentary-contact push button with one output line. This output is used to determine the proper system reaction, which depends on the settings of the REGISTER GROUP/REGISTER SELECT switches. Pressing LOAD causes the actions specified in Tables 2-2. Table 2-3 describes the contents of the console lamps after S-Memory or Cache locations have been selected by using LOAD. Table 2-4 includes a description of the use of LOAD to clear Cache.

The term LDATAA/1, enabled when LOAD is pressed, serves as an input to the PROMs on card G that are used for decoding D/M switch settings.

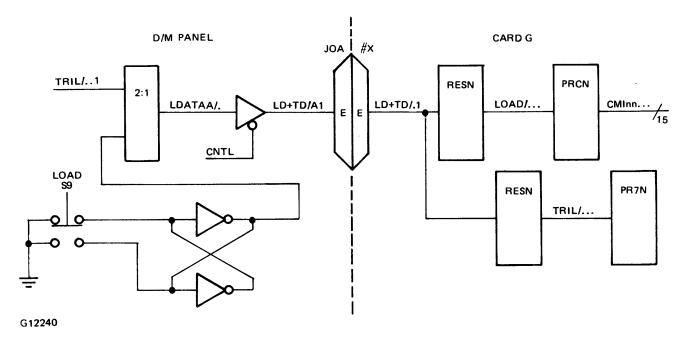

Figure 2-9 shows the logic for the LOAD push button.

Table 2-2. LOAD Push Button: Console Switch Contents Loading

| RS   | RG    | ID     | Pressing LOAD loads switch contents to          |

|------|-------|--------|-------------------------------------------------|

| 0-3  | all   | ** *   | The specified register. Exceptions: DATA, CMND  |

| 3    | 13    | DATA * | The I/O Bus; RC is issued.                      |

| 3    | 14    | CMND * | The I/O Bus; CA is issued.                      |

| 4, 5 | all   | - *    | The Scratchpad location selected.               |

| 6    | 0-1   | CW     | The Cache location specified by the A register. |

|      |       |        | (Switches contain 16 data bits.)                |

| 6    | 6-7   | CCLR   | (See Table 2-4.)                                |

| 6    | 8-9   | SW16   | The S-Memory location specified by FA.          |

|      |       |        | (Switches contain 16 data bits.)                |

| 6    | 10-11 | SW22   | The S-Memory location specified by FA.          |

|      |       |        | (Switches contain ECC + 16 data bits.)          |

| 6    | 12-13 | SW24   | The S-Memory location specified by FA.          |

|      |       |        | (Switches contain 24 data bits.)                |

| 6    | 14-15 | RELG   | (See Table 2-3.)                                |

|      |       |        |                                                 |

#### **NOTES**

Loading takes place when LOAD is pressed with the processor in HALT.

RS = REGISTER SELECT switch

RG = REGISTER GROUP switch

ID = Applicable RG switch label at the setting specified

<sup>\*</sup> The contents of these locations are displayed in the console lamps as long as they are selected.

<sup>\*\*</sup> The following cannot be loaded: BICN, FLCN, XYCN, XYST, INCN, TAS, CSW, TIME, SUM, CMPX, CMPY, XANY, XEOY, MSKX, MSKY, XORY, DIFF, MAXS, U.

Table 2-3. Displaying Cache, S-Memory, and ELOG After Using LOAD to Load Addresses

| RS | RG    | ID   | Console lamps display                                                                          |

|----|-------|------|------------------------------------------------------------------------------------------------|

| 6  | 2     | CMR  | The micro plus parity in the Cache location specified by the A register. (Rightmost 17 lamps.) |

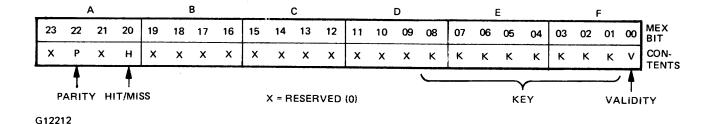

| 6  | 3     | CKR  | The Cache Key in the Cache location specified by the A register. (Bits 22, 20, 8-0.)           |

| 6  | 8-9   | SR16 | 16 bits (data) of FA-specified S-Memory location.                                              |

| 6  | 0-11  | SR22 | 22 bits (ECC + data) of FA-specified S-Mem location.                                           |

| 6  | 12-13 | SR24 | 24 bits (data) of FA-specified S-Memory location.                                              |

| 6  | 14-15 | RELG | ELOG contents. ELOG is cleared; display remains.                                               |

#### **NOTES**

Display is visible with processor in HALT.

RS = REGISTER SELECT switch

RG = REGISTER GROUP switch

ID = Applicable RG switch label at the setting specified

Table 2-4. Actions With REGISTER SELECT at Position 6

| RS | RG  | ID   | Action                                                                                                                            |

|----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 6  | 4-5 | SA   | Stop on A. When these settings are selected, if the contents of the A1 register become equal to the contents                      |

| 6  | 6-7 | CCLR | of the leftmost 20 console switches, the processor halts. Cache CLEAR. With processor in HALT, pressing LOAD clears Cache Memory. |

#### **NOTES**

RS = REGISTER SELECT switch

RG = REGISTER GROUP switch

ID = Applicable RG switch label at the setting specified

Figure 2-9. LOAD Push Button Logic

#### INC (Increment) Push Button

INC is a momentary-contact push button used to increment the A register or the FA register. REGISTER SELECT is set to MEMORY and REGISTER GROUP is used to select the register and the increment, as follows:

The A register is incremented by 16 when INC is pressed with the processor in HALT with RG at CW (Cache Write), CMR (Cache Micro Read), or CKR (Cache Key Read).

The FA register is incremented by 16 when INC is pressed with the processor in HALT with RG at SR16 (S-Memory Read 16), SW16 (S-Memory Write 16), SR22 (S-Memory Read 22), or SW22 (S-Memory Write 22).

The FA register is incremented by 24 when INC is pressed with the processor in HALT with RG at SR24 (S-Memory Read 24) or SW24 (S-Memory Write 24).

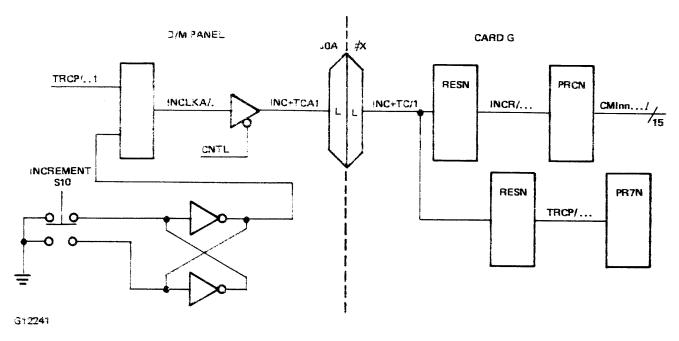

The logic for INC is shown in Figure 2-10. Interpretation of the REGISTER GROUP/REGISTER SELECT and INC outputs is controlled by the LOAD push button PROMs.

#### SINGLE MICRO/NORMAL Switch

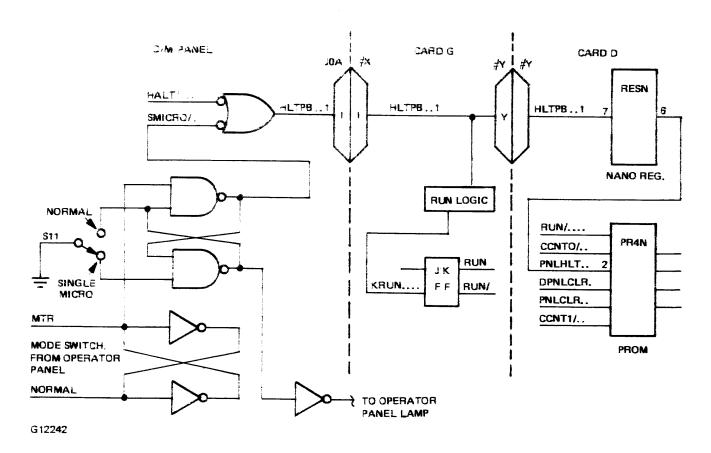

With this switch in the SINGLE MICRO position, pushing START causes the processor to execute one micro and return to HALT. In NORMAL position, micros are successively executed. These functions are influenced by the setting of the MODE switch on the Op panel. Figure 2-11 shows this interaction.

With MODE at NORMAL, a LOW level is propagated from the Op panel through the net NORMAL. This level is applied to an RS-type flip-flop and the TRUE output is gated with the SINGLE MICRO output to generate the SMICRO/. term. This resets the RUN flip-flop that causes micro instructions to execute one at a time, because KRUN.... does not reset RUN until a micro is completed. When S11 is in the NORMAL position a TRUE level is generated to SMICRO/., which prevents the stepping logic from being enabled.

Figure 2-10. INC Push Button Logic

Figure 2-11. SINGLE MICRO/NORMAL Switch Logic

Table 2-5 specifies the interactions. Note that the SINGLE MICRO/NORMAL switch has no effect on the continuous execution of micros accessed from cassette tape.

Table 2-5. Interaction Between SINGLE MIC/NORMAL and MODE Switches

| Single Micro | Mode   | Action                                                                                |

|--------------|--------|---------------------------------------------------------------------------------------|

| NORMAL       | NORMAL | Processor continuously executes micros from source designated by MICRO SOURCE switch. |

| SINGLE MICRO | NORMAL | Processor executes one micro each time START is pressed.                              |

| NORMAL       | MTR    | Processor continuously executes micros from cassette tape.                            |

| SINGLE MICRO | MTR    | Processor continuously executes micros from cassette tape.                            |

#### MICRO SOURCE Switch

MICRO SOURCE is a 4-position rotary switch that generates two binary encoded lines used by the processor fetch structure to specify the source of micros to the M register. Switch positions, output codes, and meanings are specified in Table 2-6.

The micro source can also be selected programmatically by the settings of bits 1 and 0 of the MSSW register. The interpretation of bits 00, 01, 10, or 11) is identical to the switch code.

The contents of the switch are bit-ORed with the register bits. The results of the logical combinations are shown in Table 2-7.

The MTR position of the MODE switch overrides all settings of the MICRO SOURCE switch.

Table 2-6. MICRO SOURCE Switch Position Codes and Meanings

| Position     | Code | Source of Micros                   |  |  |

|--------------|------|------------------------------------|--|--|

| NORMAL (0)   | 00   | Cache (S-Memory on misses)         |  |  |

| S (1)        | 01   | S-Memory only                      |  |  |

| C (2)        | 10   | Cache only                         |  |  |

| FROZEN M (3) | 11   | M register (micro does not change) |  |  |

Table 2-7. Results of Bit-ORing MICRO SOURCE and MSSW

|        | Register |    |    |    |  |

|--------|----------|----|----|----|--|

| Switch | 00       | 01 | 10 | 11 |  |

| 00     | 00       | 01 | 10 | 11 |  |

| 01     | 01       | 01 | 11 | 11 |  |

| 10     | 10       | 11 | 10 | 11 |  |

| 11     | 11       | 11 | 11 | 11 |  |

#### Over Temperature Indicator

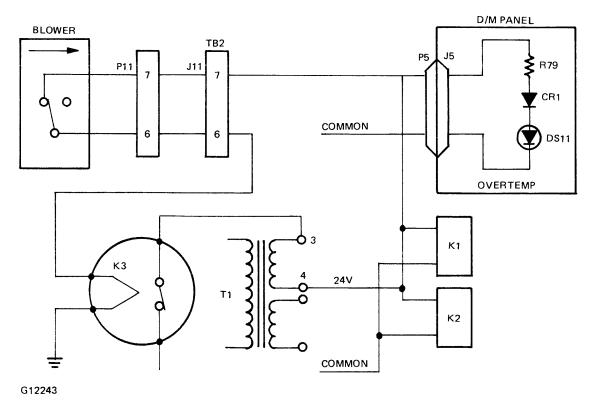

To circulate cooling air, the cabinet is provided with a blower assembly. If a blower malfunctions, the OVER TEMP indicator provides a visual alarm. The OVER TEMP circuit is shown in Figure 2-12.

Control circuits for the indicator are contained within the AC Distribution Box. Blower air is sensed by a switch in the fan assembly. When the air supplied by the fan is sensed as insufficient, the switch closes, energizing relay K3 with 24 volts from transformer T1. The application of power picks K3 which, through its wiper, provides 24 volts to the OVER TEMP lamp and to relay K2. When K2 is picked, the 24 volts is removed from relay K1 and all AC power is removed. To restore power to the system, the POWER push button must be cycled: first OFF, then ON.

Figure 2-12. OVER TEMP Circuit Logic

1127396 2-15

#### **DDEC Switch**

A disk drive electronics controller may be included in the B 1900 central system cabinet. The DDEC switch, which is a push button in the B 1985 and B 1955 and a rotary switch in the B 1905, provides the same ON LINE/OFF LINE capability here as on a stand-alone controller, permitting the DDEC to be operated locally or under system control.

#### Switches for Two-Processor Systems

Three switches on the B 1985/B 1955 D/M panel apply specifically to two-processor operation: MASTER SE-LECT, SLAVE, and DISPLAY. The cable that connects Processor A to the D/M panel runs from J0A on the panel to Processor A, card G. Similarly, a cable from J0B on the panel is connected to Processor B, card G.

#### MASTER SELECT SWITCH

This two-position rotary switch enables the user to designate either Processor A or Processor B as master. The other processor is automatically designated as slave.

#### SLAVE SWITCH

This two-position rotary switch allows the slave processor to be placed on or off line.

#### DISPLAY SWITCH

This two-position rotary switch allows selection of Processor A or Processor B for display in the console lamps.

#### NOTE

DISPLAY may be switched with the system either in RUN or in HALT. MASTER SELECT switch and SLAVE must only be switched with the system in HALT; switching either with the system in RUN may cause an unrecoverable halt.

#### **Duplicate Console Functions**

CLEAR. START, and INTERRUPT are functions that are implemented by pushbuttons or switches.

#### **CLEAR Push Button**

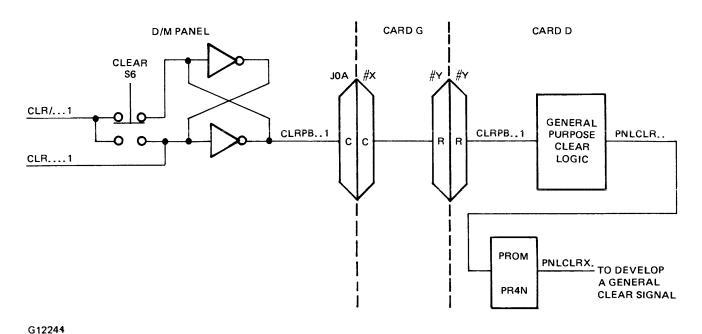

CLEAR is a momentary push button that is used to clear the major working registers of the processor. Figure 2-13 shows the logic.

CLEAR is active only while the processor is in the HALT state.

Pressing CLEAR generates a TRUE level that enables CLRPB..1 to come TRUE. This signal propagates through the General Purpose Clear logic that develops the general clear signal PNLCLR\*, which is routed to the rest of the processor for the following functions:

- 1. Enables the ALU on card E to output all zeros to the MEX for loading the registers listed in 2, below.

- 2. Clears registers M. A. BR. PERP, PERM, MSSW. CC, and CD by loading zeroes.

- 3. Clears all processor state flip-flops.

- 4. Clears Cache unless MICRO SOURCE is at C (Cache only).

Figure 2-13. CLEAR Push Button Logic

#### START Push Button

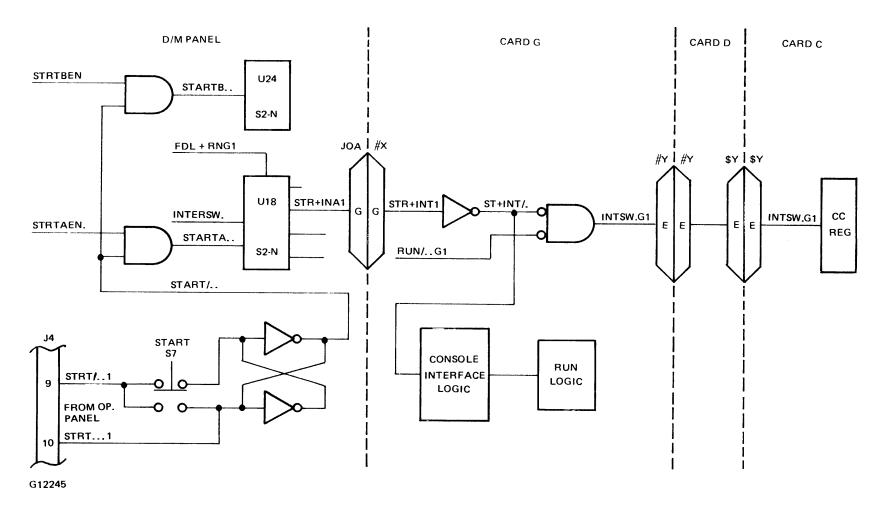

The function of the START push button is to cause the processor to transfer the system from the LOAD/DISPLAY state to the RUN state. In addition, if the processor is in the MTR mode, the START push button initiates a cassette start signal. Figure 2-14 shows the logic for the START push button.

Pressing START applies a TRUE level to the input of an RS-type flip-flop and generates the START/.. term. In the B 1985 system, START/.. is ANDed with STRTAEN. and STRTBEN. to start one of the processors. The gated term is called STARTn.. and is applied to a two-input multiplexor. If FDL+RNG1 is TRUE, then INSTRTA1 becomes TRUE and propagates to the console interface logic which starts the RUN Logic.

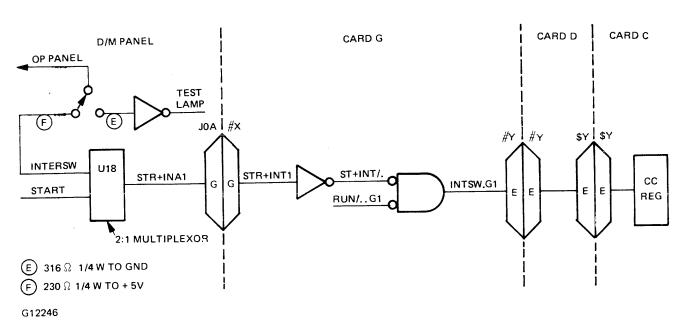

#### INTERRUPT Switch

INTERRUPT, a toggle on the D/M panel and a push button on the Op panel, is used to bring the processor to an orderly, software-controlled halt. This is accomplished by setting bit 0 of the CC register. Software interrogates this bit for a 1 condition, as shown in Figure 2-15.

When INTERRUPT is operated, the INTERSW. signal is generated on the D/M Panel. This signal is ORed with the signal START at the 2-to-1 multiplexor, U18. It is then routed to card G where it is ANDed with the RUN/..G1 signal and sent to card C where it sets CC0.

#### SYSTEM CLOCK

Card K, the I/O Distribution and Clock card, plugs into the processor backplane. Several clock signals are generated on this card for use by the system. These signals are distributed via backplane connections and frontplane coaxial connectors. There are three versions of this card: one operates at 6 MHz (167-nanosecond cycle) and the other two at 4 MHz (250-nanosecond cycle). Clock outputs are always available when power is applied to the system.

1127396 2-17

Figure 2-14. START Push Button Logic

Figure 2-15. INTERRUPT Switch Logic

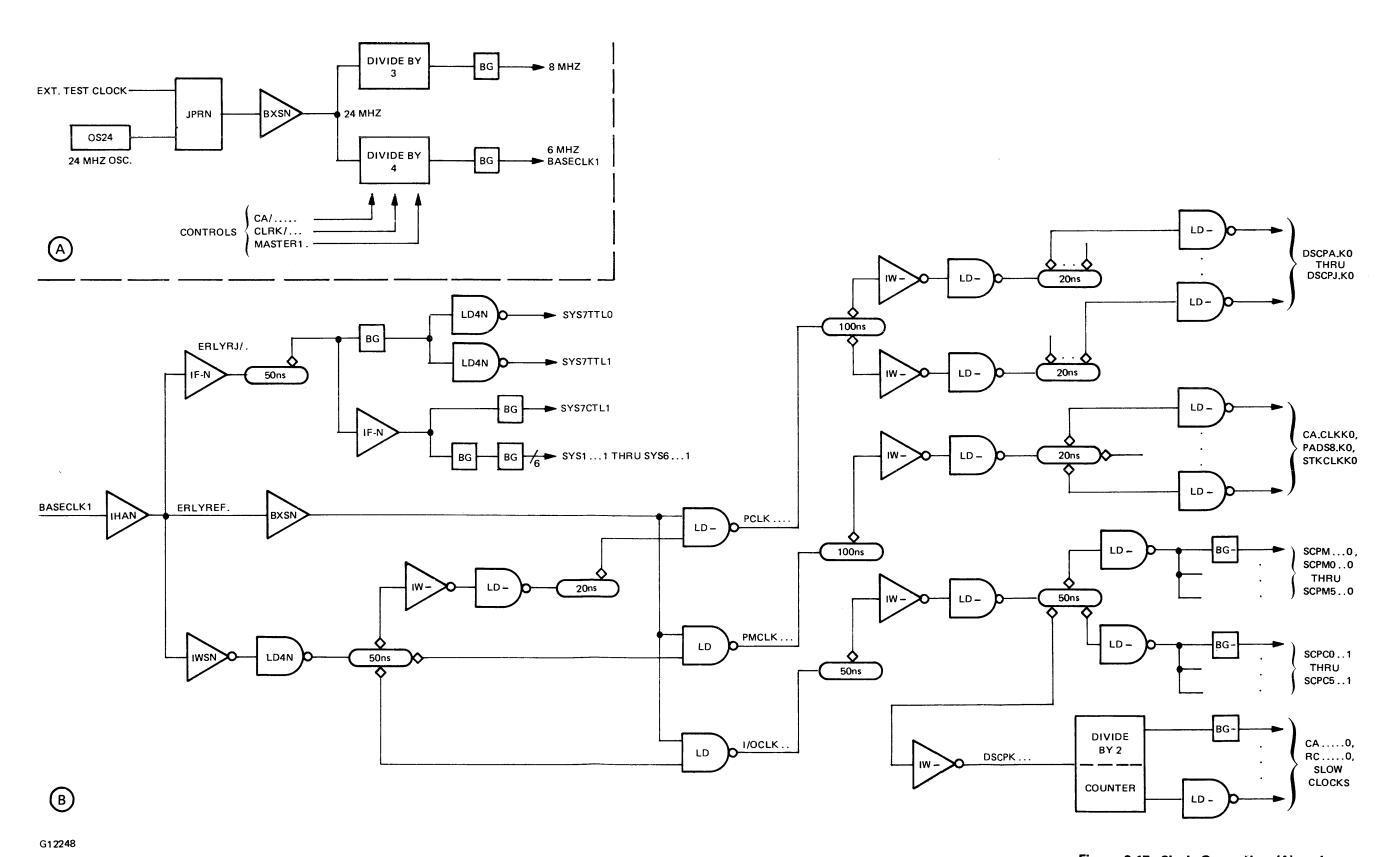

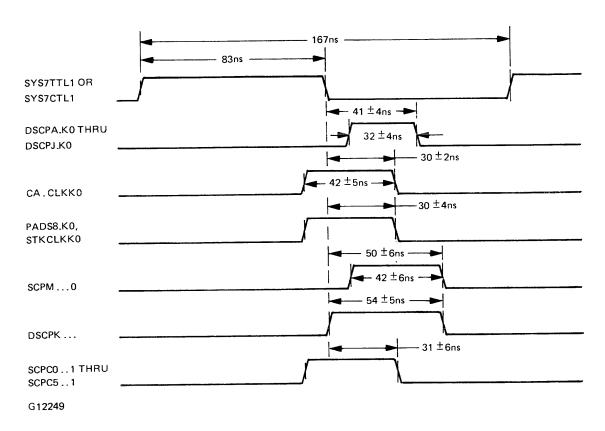

Figure 2-16 is a functional block diagram of the clock card, Figure 2-17 shows clock generation, calibration and distribution, and Figure 2-18 provides waveforms.

#### **Processor Clocks**

Processor clocks, signals DSCPA.KO through DSCPJ.KO, are approximately 33 nanoseconds wide. By shifting the leading edge signal LDEDGE.. and gating it with early reference signal ERLYREF., clocks of different pulse widths can be achieved. The basic processor clock PCLK.... is generated by the same method through the two delay lines, which give a total of 70 nanoseconds of adjustment range. Additional delay lines, one of 100 nanoseconds and two of 20 nanoseconds each, provide the necessary phase delay. Processor clocks are buffered by separate LD4Ns to the backplane.

#### Cache Memory Clocks

The three Cache Memory clocks are 1) the Scratchpad clock PADS8.KO, 2) the A-Stack clock STKCLKKO, and 3) the Cache Memory clock CA.CLK00. These clocks are adjusted for the correct pulse width by overlapping the ERLYREF. and LDEDGE.. signals and by phase-shifting through two additional delay lines. These clocks are buffered by separate LD4Ns to the backplane.

#### Memory Base Unit Clocks

The two MBU clocks are SYS7TTL0, and SYS7TTL1. Both are TTL, both are driven by LD4Ns, and both are used with MBU 7/8. SYS7TTL1, used in the B 1985 and the B 1955, is located at #EX at the doghouse on card K. SYS7TTL0, used with the B 1905, is found on the backplane of the card K.

These MBU clocks originate from ERLYRF/.., early reference clock. A 50-nanosecond delay line provides control for the phase shift between the reference clock and the rest of the system.

Figure 2-16. Functional Block Diagram of Clock Card (Card K)

#### System Clocks

Six system clocks are available for use with multiline controls and extensions. These signals, SYS1...1 through SYS6...1, are identical to the MBU clock up to the point of the 50-nanosecond delay. (See Figure 2-16.) All are of the same pulse width as the MBU clocks, and provide a fixed phase delay of about 7 nanoseconds with respect to the reference clock. clock. System clocks are routed to frontplane doghouse connectors #HX, #KX, #PX, #SX, #VX and #YX. These clocks are used with Multiline Controls and Multiline Extensions.

#### I/O Clocks

The I/O clocks are generated by the I/O Distribution logic. Adjustment of these clocks for correct pulse width and phase shift is similar to that of the processor clocks. The basic clock is fanned out after delay into three separate groups:

#### **SCPMnXXX**

Seven clocks, driven by BG-Ns at the backplane and used for I/O conrols that share the same backplane with the processor.

#### **SCPCnXXX**

Six clocks, routed to frontplane doghouse connections and used for I/O controls in separate backplanes and I/O extensions in daisy-chain configurations.

#### **DSCPKXXX**

A signal that, through additional logic, generates the Command Active signal CA....., the Response Complete signal RC....., and the slow clocks.

Figure 2-17. Clock Generation (A) and Calibration, Distribution (B)

Figure 2-18. Clock Waveforms

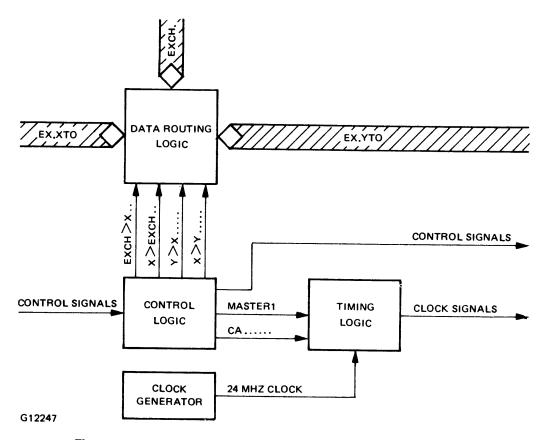

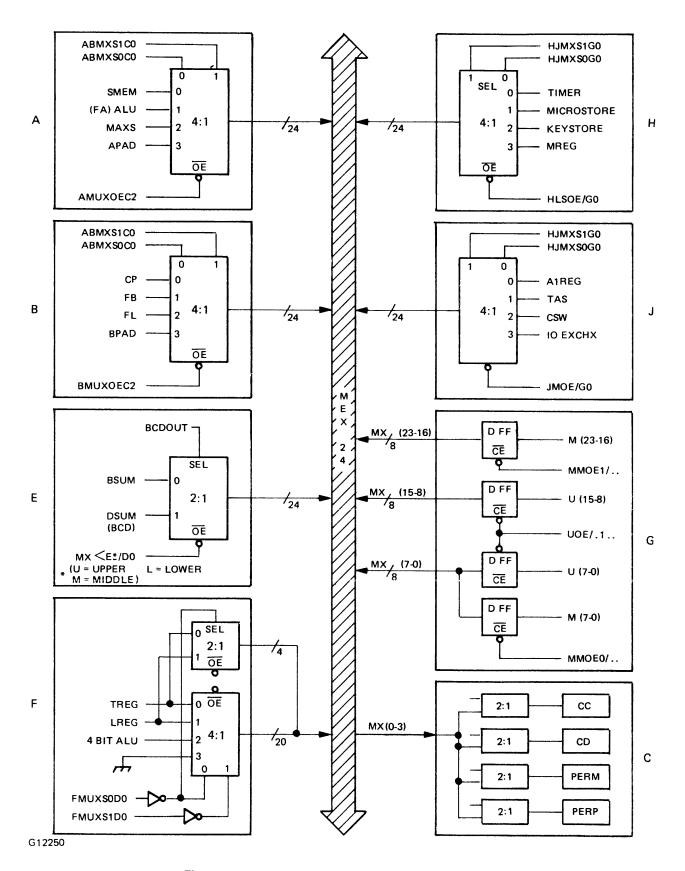

#### MAIN EXCHANGE

The Main Exchange (MEX) is a 24-bit-wide bus used for transferring data from a source such as the I/O exchange, the memory interface, or a working register to a destination. Control of the MEX for data transfers is enabled by the decoding of a microinstruction. Data routing to the MEX is shown in Figure 2-19.

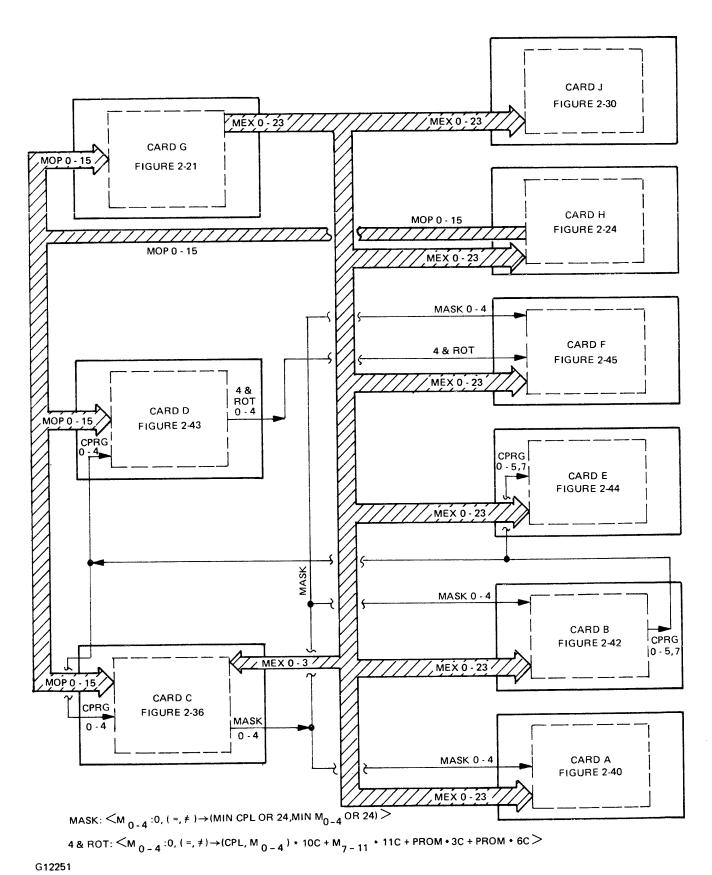

#### PROCESSOR CARD FUNCTIONS

The following subsections refer to the functions of the nine cards that contain the processing capabilities of the central system. These cards are identified by the letter designations A through J (I is omitted). Logically and in the descriptions that follow, the cards are organized into three groups: card G is the control card for cards H and J, card C is the control card for cards A and B, and card D is the control card for cards F and E.

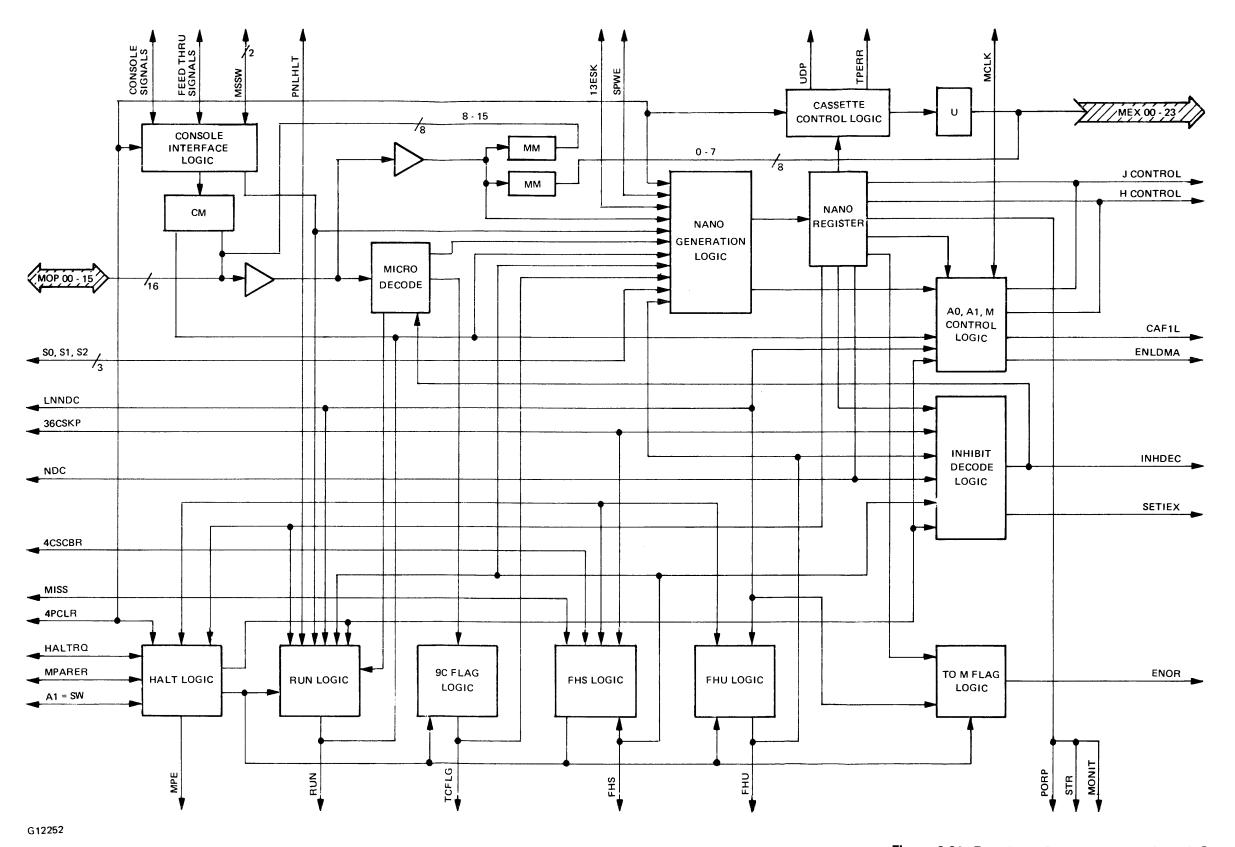

Figure 2-20 is a block diagram of the B 1900 processor. Functional block diagrams of the cards are presented in the appropriate subsections.

1127396 2-23

Figure 2-19. Data Routing to the Main Exchange

Figure 2-20. Block Diagram, B 1900 Processor

# Card Group G, H, J

Card G, the control card, includes the following logical functions:

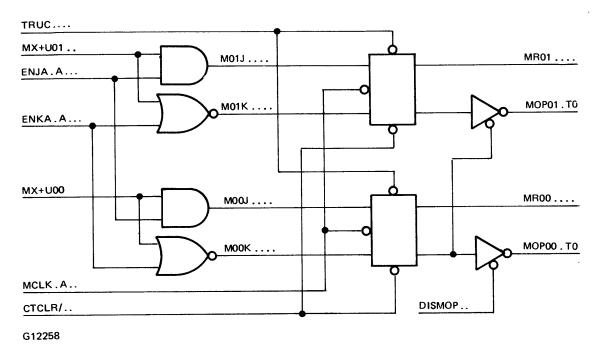

- 1. Buffering of the MOP lines from cards G and H and decoding of the micros as they appear on the MOP lines.

- 2. Generation of control signals from PROMs for cards H and J.

- 3. Enabling of PROM outputs resulting from the decoding of micros to the nanoregister. The nanoregister is distributed to all three control cards and holds the control states required to fulfill the actions specified by the microinstruction.)

- 4. Processor RUN/HALT flip-flop and associated logic.

- 5. Micro sequence pipeline control logic. Fetch, decode, and execute functions are sequenced, depending on processor state and mode.

- 6. Micro sequence alteration control logic, to deal with micros that change the normal micro sequence.

- 7. MTR mode control logic. When the processor is in MTR mode, data and the ECC from the cassette is fed bit by bit to the U register. When the micro is completely assembled in U, it is loaded into the M register for decoding and execution, unless the prior micro was a 1C Move from U, which causes the contents of U to be treated as data.

- 8. Cache Memory fill control logiç, including the FHS flip-flop. If the source for micros is NORMAL and the needed micro is missing, an automatic Cache-fill operation takes place under control of this logic.

- 9. Processor Initialization. GPCLR... (General Processor Clear) occurs 1) when the system is powered up, 2) when CLEAR is pressed with the processor halted, or 3) when HALT and CLEAR are simultaneously pressed with the processor running.

- 10. Card H and card J control logic.

- 11. CM and MM register control logic. CM holds the contents of the console switches; MM provides the next 16 bits of a micro if needed.

- 12. Console Op panel and D/M panel interface logic.

- 13. Cassette and U register control logic, including mechanism control, state sequencer, single-micro signal generation, and syndrome register and error correction logic.

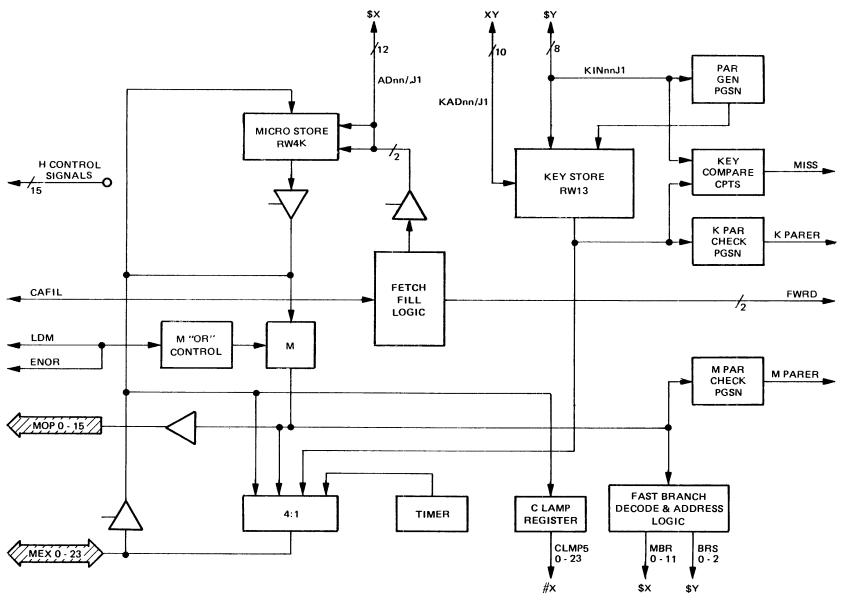

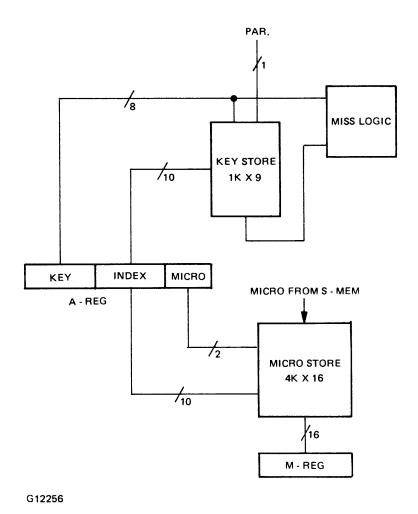

#### Card H includes

- 1. Cache micro and key store and parity generation, the M register, and related logic.

- 2. Fast-branch decode and address logic.

- 3. Timer logic.

- 4. Console lamps register latches and drivers.

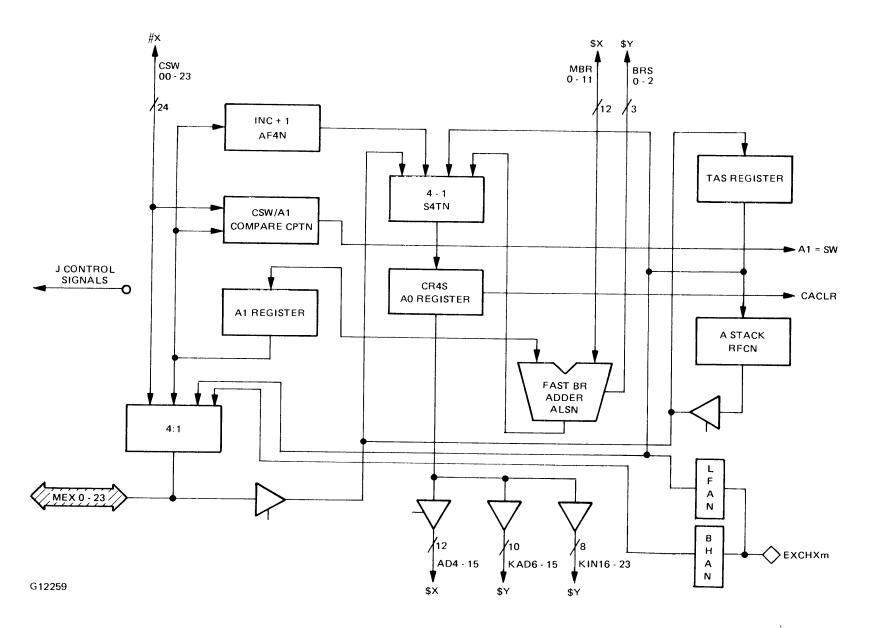

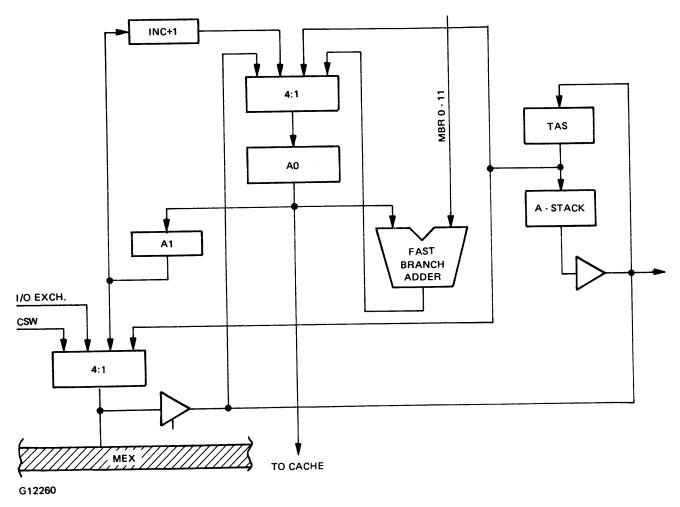

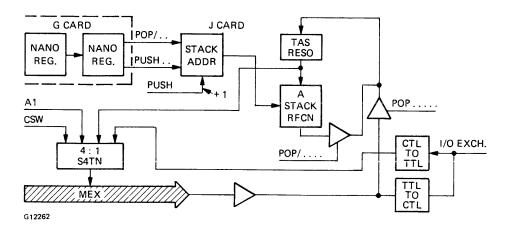

#### Card J includes

- 1. The A register and related logic. A, the microprogram address register, consists of two parts, A0 and A1.

- 2. Logic for comparing the console switches with the A1 register.

- 3. Fast-branch execution circuitry.

- 4. The A-Stack and the associated TAS (top of A-Stack) register.

- 5. TTL/CTL and CTL/TTL conversion for the 24-bit path from the MEX to the I/O exchange.

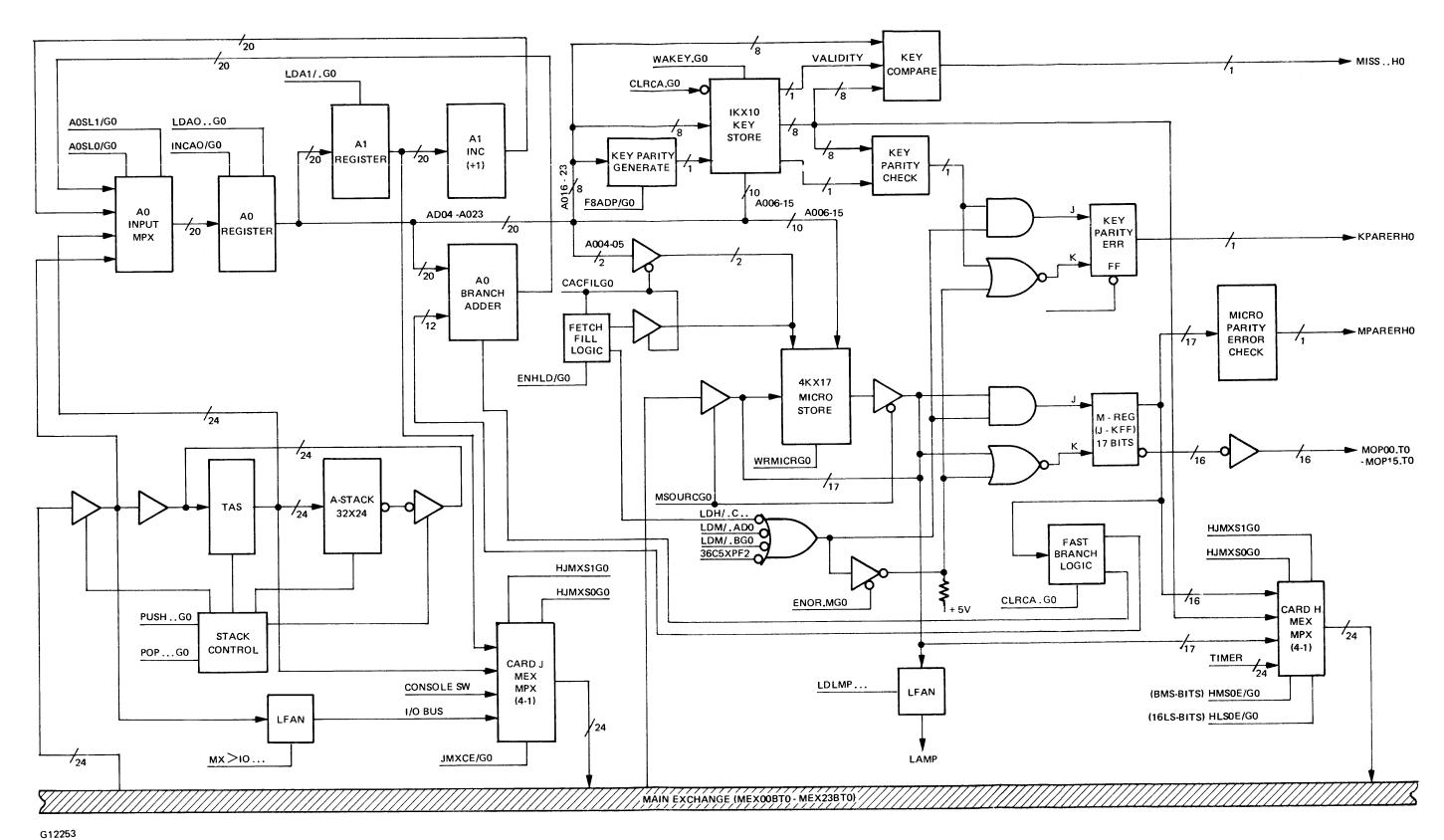

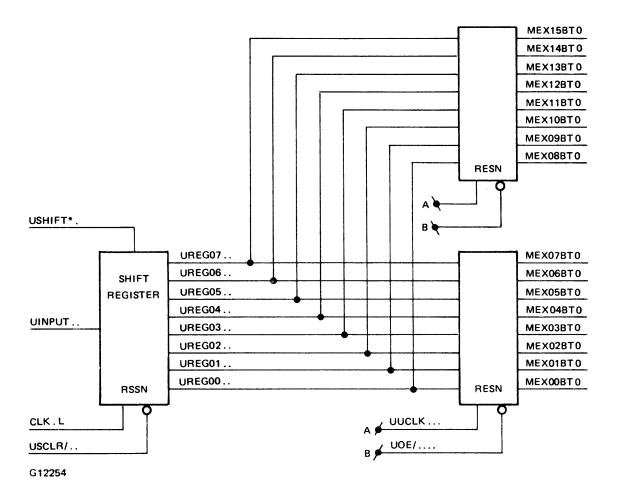

Figures 2-21, 2-24, and 2-30 are functional block diagrams of cards G, H, and J respectively.

#### Card G

The functions contained on card G (Figure 2-21) are outlined under the subsection titled Card Group G, H, J. Some detail on the micro fetch decode processes and nano generation is provided in the following subsections.

Figure 2-21. Functional Block Diagram of Card G

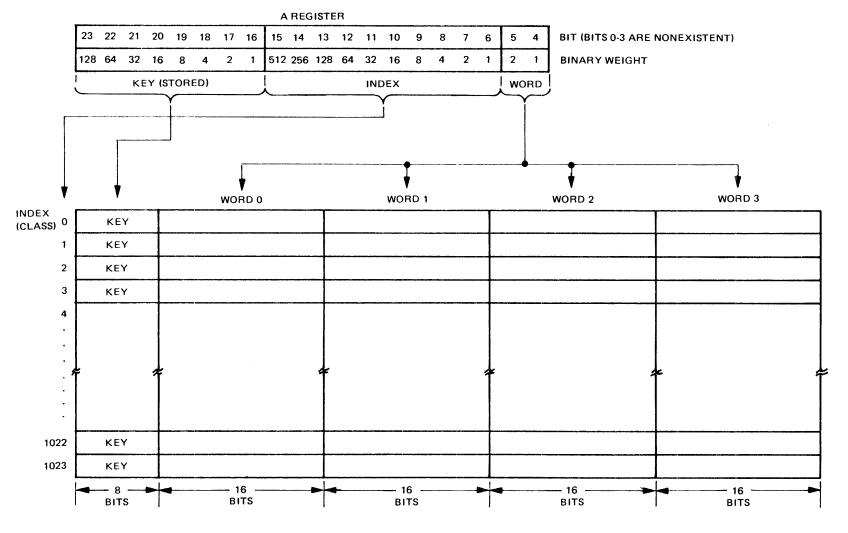

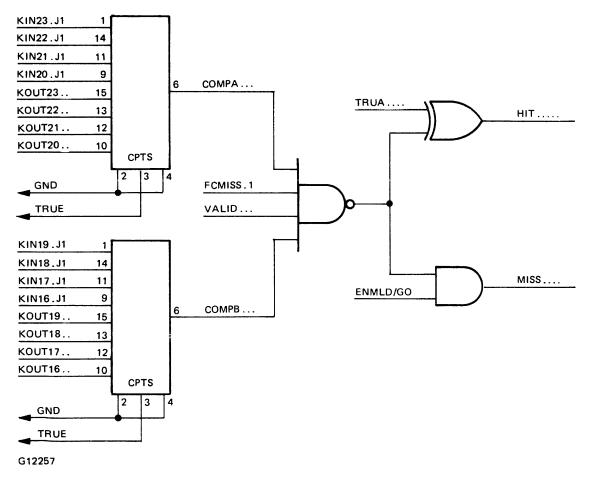

## FETCH STRUCTURE

The fetch structure, distributed among cards G, H, and J, includes Cache Memory, the A and M registers, and the A-Stack. The A register is used to point to a micro for execution, the M register receives the micro before it is decoded, and the A-Stack is used in special cases to store the contents of the A register. Also included as part of this structure is the Top-of-A-Stack (TAS) logic and the A register manipulation logic. The basic function of the fetch structure is to load micros into the M register, from which they are put on the MOP lines and distributed to the control cards for decoding into nanoinstructions and subsequent execution.

Figure 2-22 diagrams the fetch structure.

#### DECODE STRUCTURE

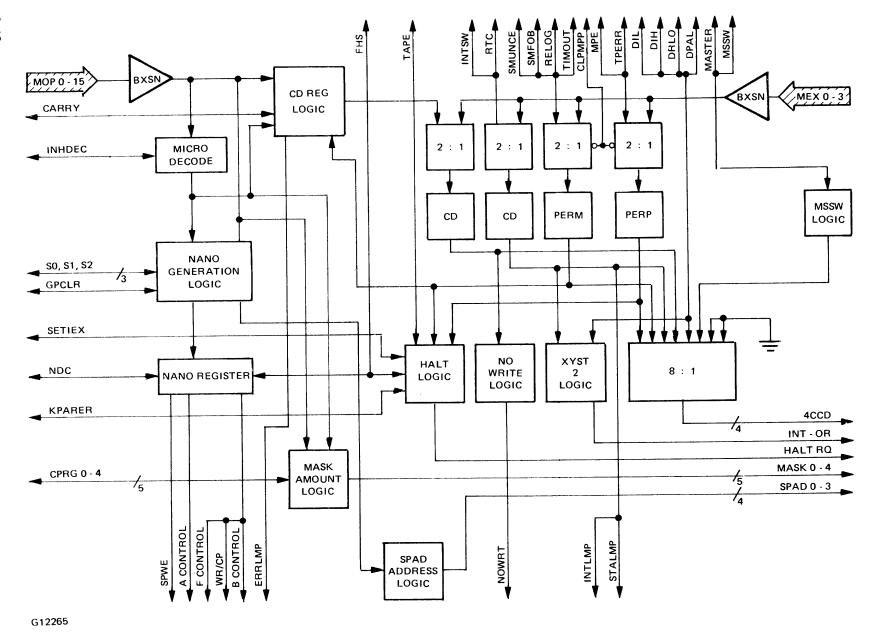

The basic function of the micro decode logic is to manipulate the MOP lines in such a way that a micro and its variants are converted to address lines. These address lines are routed to the PROMs.

The decode structure provides the transition between the microinstruction and one or more nanoinstructions. The decode phase begins with the output of the micro from the M register, and continues until the nano is available on the output of the Micro Decode PROMs on cards G, C, and D.

The M register outputs are the MOP lines. A 16-bit bus is used to move MOP line data to the three control cards for decoding. The decoded PROM outputs are the nanos that are moved to the nanoregister for execution.

Several signals control the decoding process from the time a micro appears at the M register until the one or more resulting nanoinstructions are loaded into the nanoregister:

NDC..... Nano Decode Complete

LN..... Last Nano

LNNDC/.. Last Nano, Nano Decode Complete

DISM.... Disable M Register INHDEC.. Inhibit Decode

As soon as the M register is loaded, its output is available to the decode logic. A Move 24-bit Literal (9C) micro requires a delay in decoding the next micro in M; therefore, the signal DISM prevents the literal in the M register from being sent the decode logic.

The control signal NDC, when TRUE, indicates that decoding of the present nano is complete. NDC is also used to increment the nano sequence counter.

The control signal LN is gated with NDC to indicate the completion of the micro. LN is TRUE when present sequence number PS#n and last sequence number (LS#n) are equal.

The control signal LNNDC is sent to card G to start the fetch cycle and increment the A0 register.

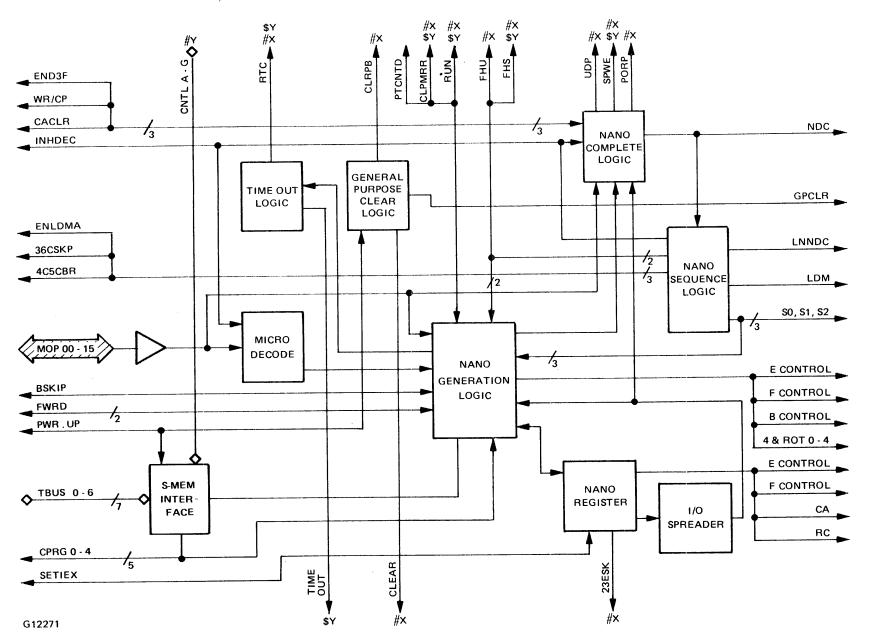

Buffers for the MOP lines as well as the actual micro decode logic are included on cards G, C, and D. Each of the cards contains the portion of the decode logic and nano register that relates to the functions of the related data cards. Card D contains all the nano sequencing, including the nano-complete logic.

The encode logic generates some control terms from the ANDing or ORing of key MOP lines. The MOP lines are sent to AND gates to generate terms like MD=0 (D subfield of M=0), which are sent to the decode PROMs.

Figure 2-22. Fetch Structure

#### NANO GENERATION LOGIC

The logic implemented to control the generation of the bits that make up the nanoinstruction is in the form of stored logic contained within a PROM network. The binary address formed by the decoded MOP lines is applied to the input lines and a preprogrammed output is derived. The output of the PROM is directed to the nano register. The PROMs use several networks as input, including a sequence counter, the decoded MOP lines, and micro-subset lines. The nano instructions are generated on all three control cards.

## NANO SEQUENCE LOGIC

Nano sequence logic controls the number of nanos required to execute a micro. For example, three nanos are required to complete a Bias (3E) micro execution. The MOP lines are sent to four PROMs which generate an LS#n equal to 2, which is one less than the number of nanos required to execute the micro. The PS#n (present is counted up each time NDC is TRUE, and LN is generated when LS#n and PS#m are equal. The sequence counter that generates PS#n is reset by LN\*NDC, indicating the end of the micro.

#### U REGISTER

The U register is a 16-bit register used to accumulate the serial bit input from the cassette tape. The U register is addressable as a source register only.

The register comes into play when the processor is in MTR mode. Micros from the cassette tape are moved bit-serially into U. When 16 bits have been accumulated, the register's contents are automatically moved to the M register for execution.

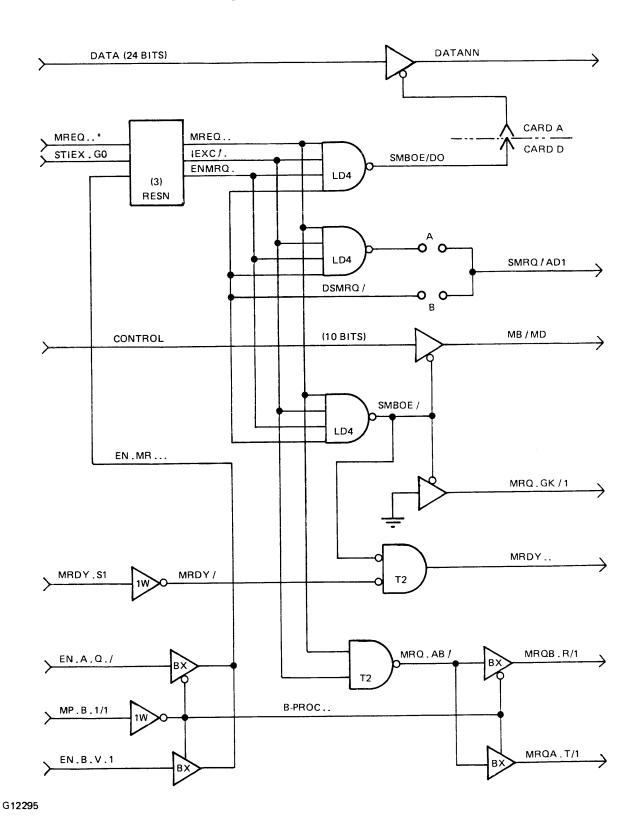

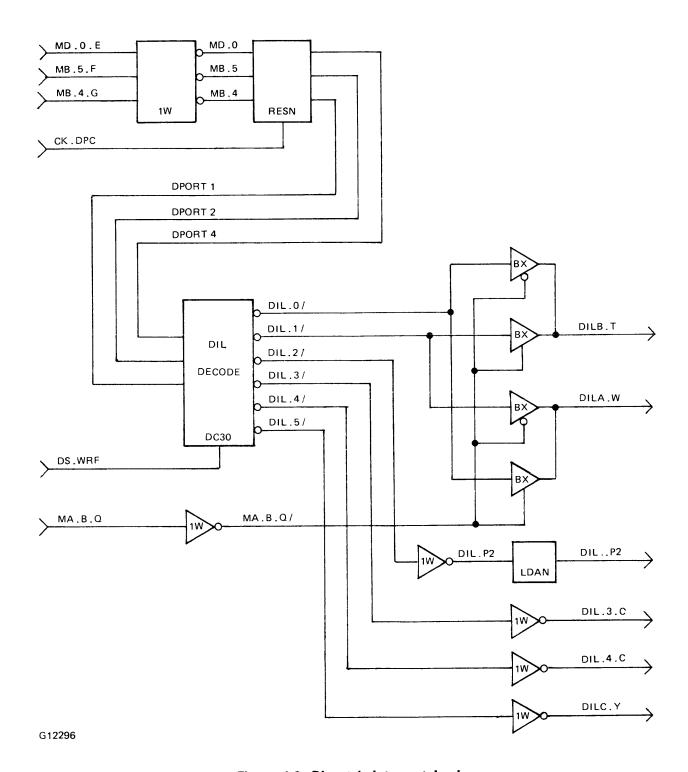

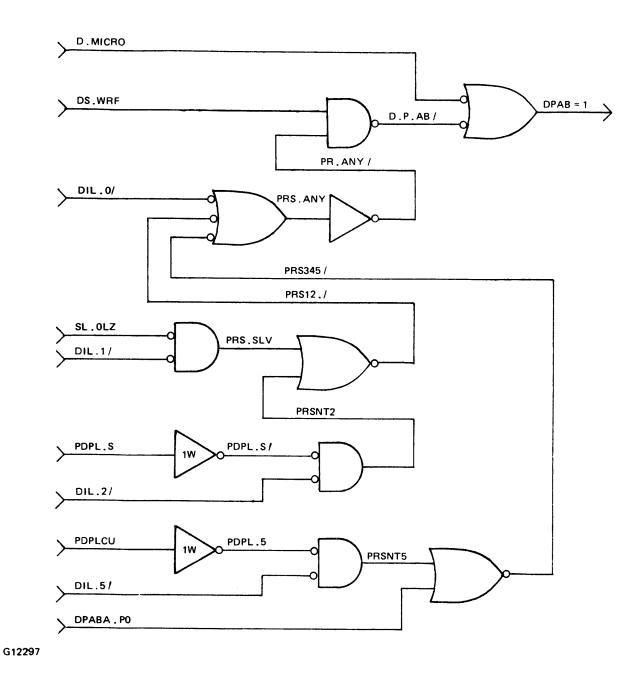

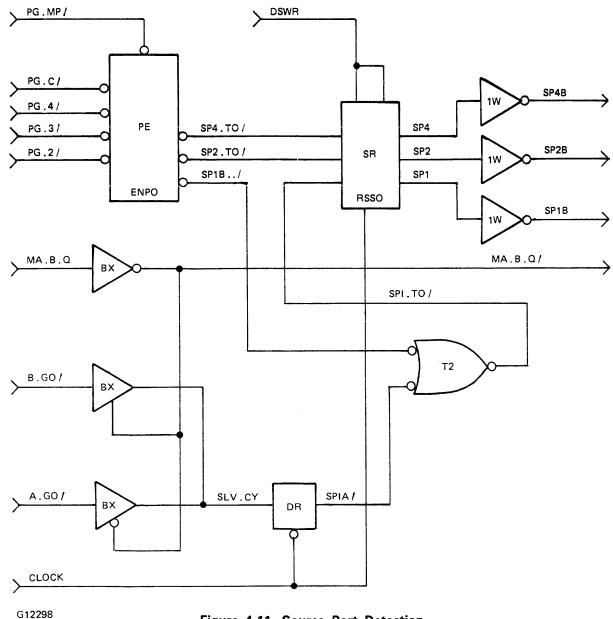

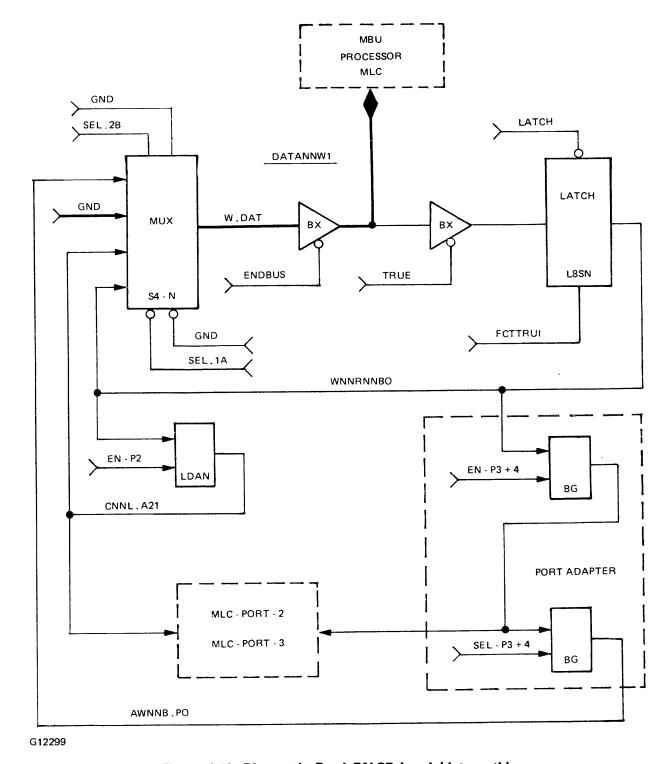

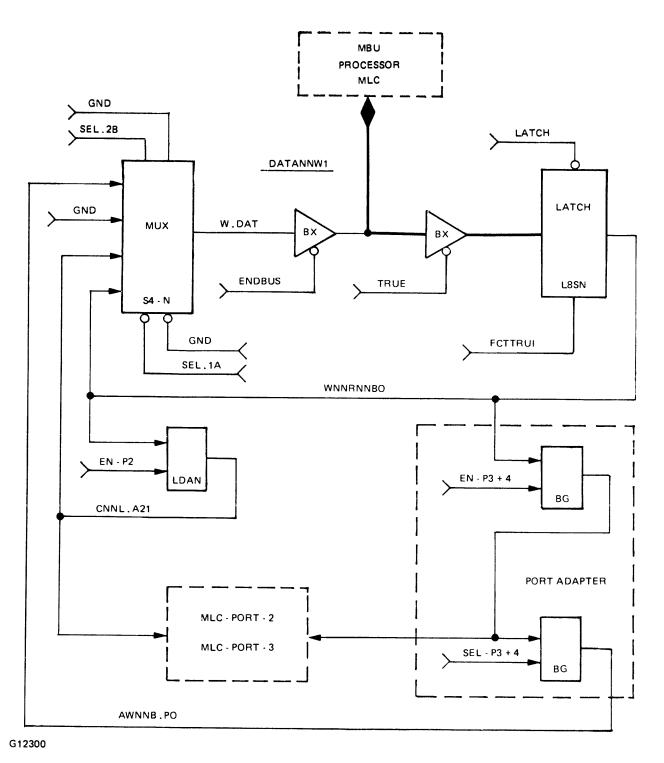

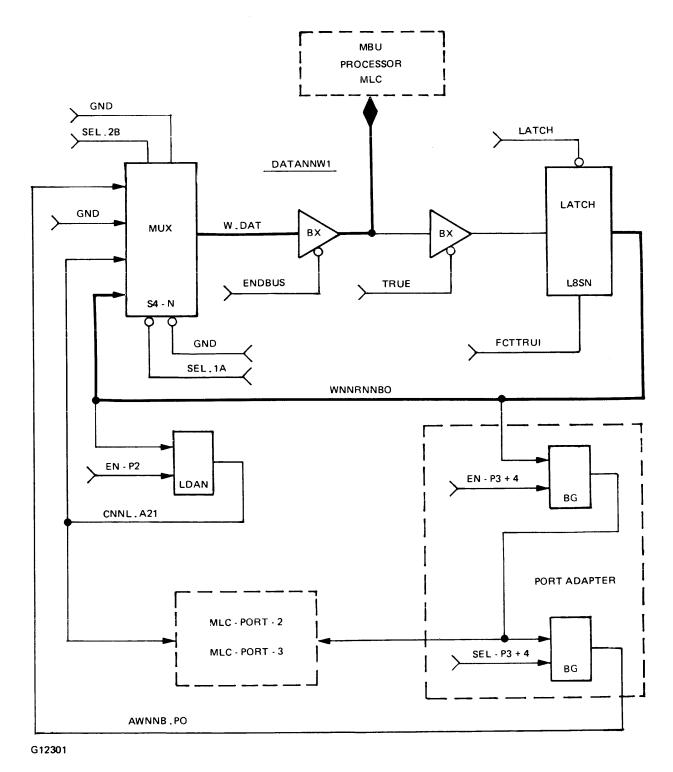

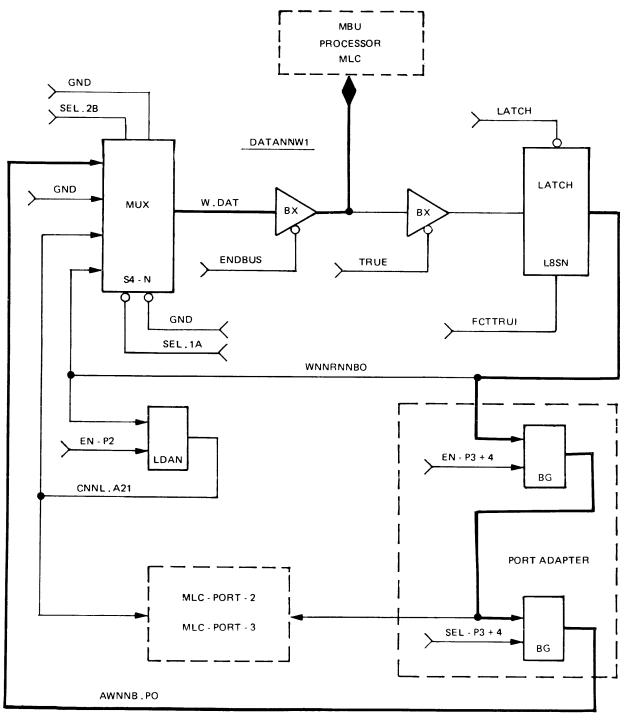

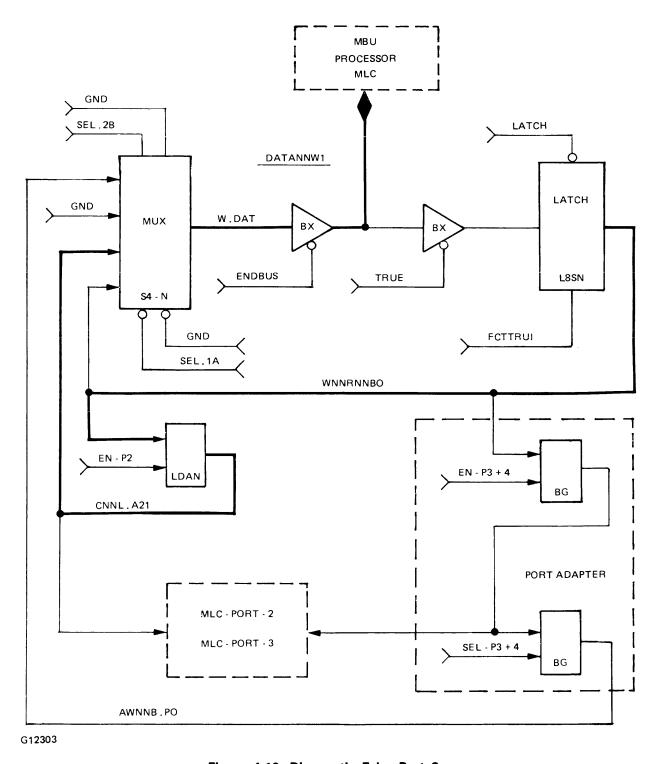

When a micro that references U as a source is being executed, the contents of U are moved directly to the destination rather than to M. This data is not treated as a micro. If M is the destination, the data from U is bit-ORed with the current contents of M. Following execution of the exception micro, the next 16 bits from U go to M for execution, as before.