# Burroughs

# Data Communications Processor REFERENCE MANUAL

# Burroughs DATA COMMUNICATIONS PROCESSOR

REFERENCE MANUAL

**Burroughs Corporation**

Detroit, Michigan 48232

\$5.00

#### COPYRIGHT® 1970 BURROUGHS CORPORATION

#### AA 146563

The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be forwarded using the Remarks Form at the back of the manual, or may be addressed directly to Systems Documentation, Sales Technical Services, Burroughs Corporation, 6071 Second Avenue, Detroit, Michigan 48232.

#### TABLE OF CONTENTS

| SECTION | TITLE                                               | ŧΕ  |

|---------|-----------------------------------------------------|-----|

|         | INTRODUCTION xvi                                    | .i. |

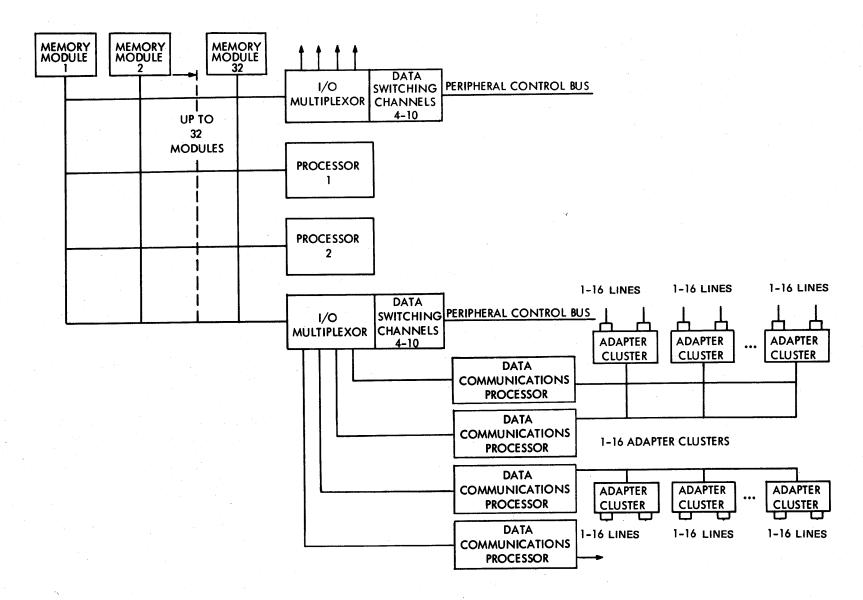

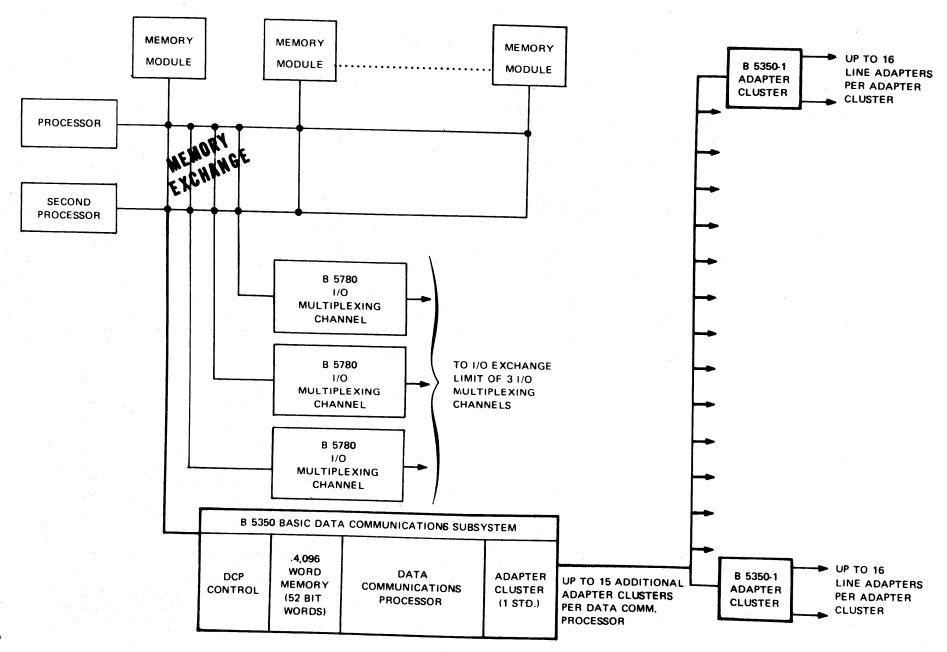

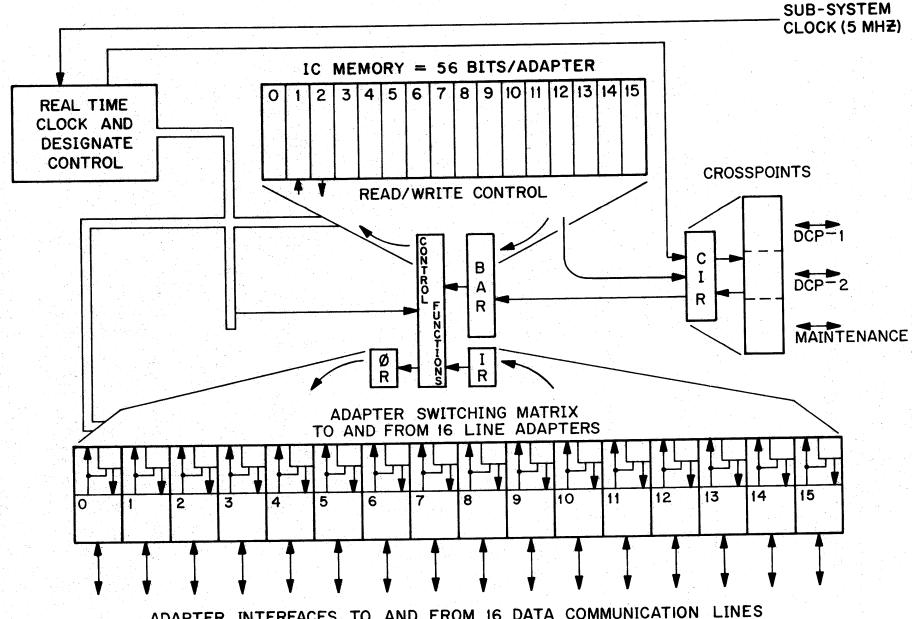

| 1       | DATA COMMUNICATIONS PROCESSOR SYSTEM CONFIGURATIONS |     |

|         | General                                             |     |

|         | Data Communications Processor (DCP) 1-1             |     |

|         | Adapter Cluster                                     |     |

|         | Line Adapters                                       |     |

|         | Operation                                           |     |

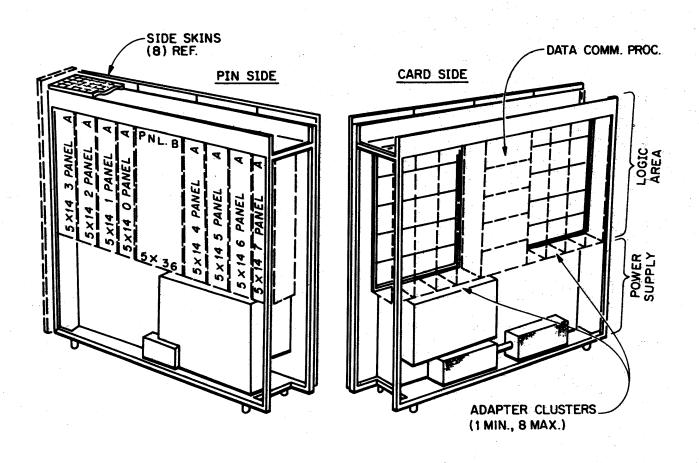

|         | Data Communications Cabinet                         |     |

|         | Cluster Cable                                       |     |

|         | Cluster Exchange                                    |     |

|         | Data Communications Processor Optional              |     |

|         | Local Memory                                        |     |

| 2       | DATA COMMUNICATIONS PROCESSOR                       |     |

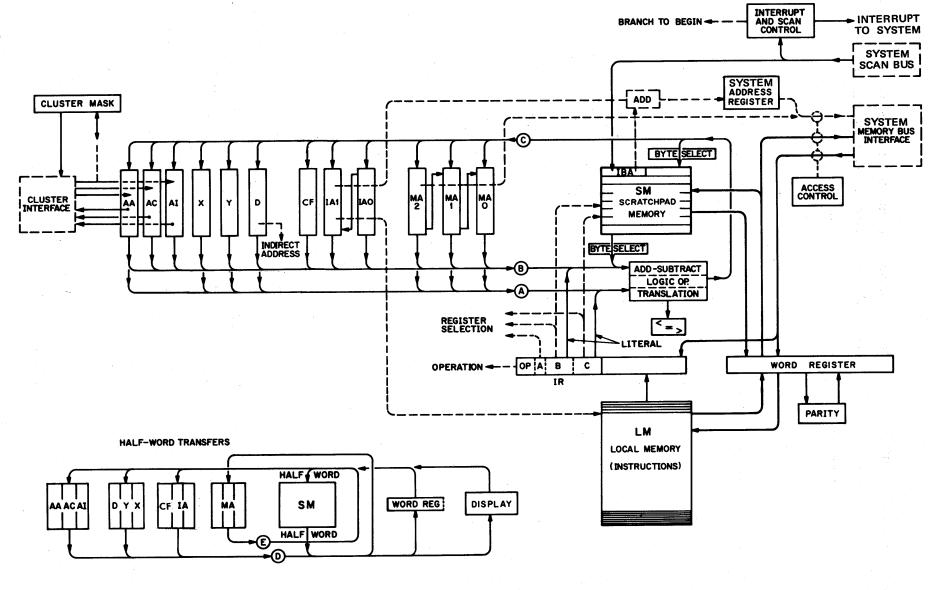

|         | General                                             |     |

|         | Nomenclature                                        |     |

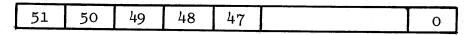

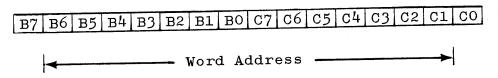

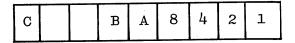

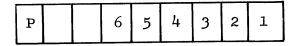

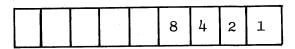

|         | Bit Numbering                                       |     |

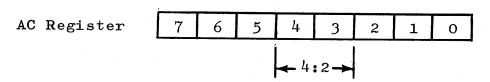

|         | Designation of Fields 2-3                           |     |

|         | Designation of Single Bits 2-3                      |     |

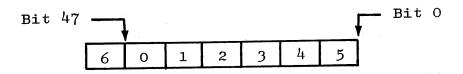

|         | Byte Designation 2-4                                |     |

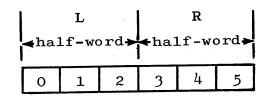

|         | Half-Word Designation 2-4                           |     |

|         | Adapter Cluster Interface Registers 2-5             |     |

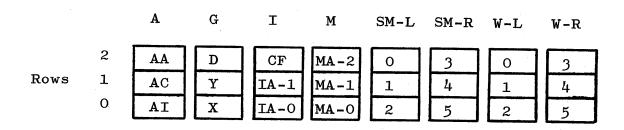

|         | Adapter Address Register (AA) 2-5                   |     |

|         | Adapter Control Register (AC) 2-5                   |     |

|         | Adapter Information Register (AI) 2-5               |     |

|         | General Purpose Registers 2-5                       |     |

|         | D Register 2-5                                      |     |

|         | Y Register                                          |     |

|         | X Register                                          |     |

|         | Comparison Register (CF) 2-6                        |     |

|         | Memory Address Registers                            |     |

|         | Memory Address Registers (MA-2, MA-1, and MA-0)     |     |

|         |                                                     |     |

| SECTION  | TITLE PAGE                                          |

|----------|-----------------------------------------------------|

| 2 (cont) | Instruction Address Registers 2-9                   |

|          | System Address Register (BA) 2-10                   |

|          | Full Word Registers                                 |

|          | Instruction Register (IR) 2-10                      |

|          | Word Register (W)                                   |

|          | Cluster Mask Register                               |

|          | Memories                                            |

|          | Scratchpad Memory (SM) 2-11                         |

|          | Reserved Locations 2-12                             |

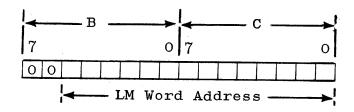

|          | Local Memory (LM)                                   |

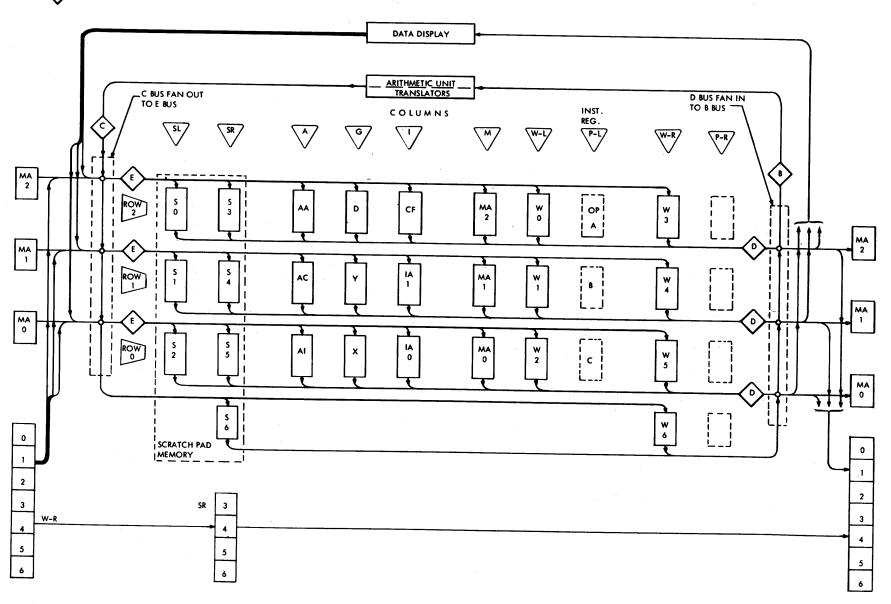

|          | Basic Half-Word and Byte Organization 2-12          |

|          | D Bus                                               |

|          | E Bus                                               |

|          | Full Word Transfer 2-13                             |

|          | Arithmetic, Logical, and Translation                |

|          | Section                                             |

|          | A Bus                                               |

|          | B Bus                                               |

| •        | C Bus                                               |

|          | Hardware Translators (B 5700) 2-14                  |

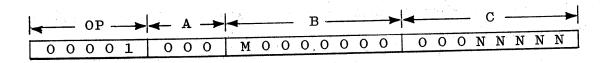

|          | Instruction Format 2-17                             |

|          | Instruction Half-Word 2-17                          |

|          | Op Field 2-18                                       |

|          | A Field                                             |

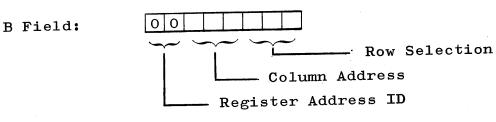

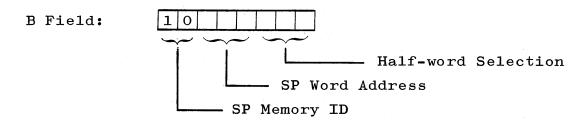

|          | B Field                                             |

|          | Literal 2-20                                        |

|          | B:C Branch Address (Groups 0 and 1)                 |

|          |                                                     |

|          |                                                     |

|          |                                                     |

|          |                                                     |

|          | Scratchpad Memory Address (Groups 2, 3, and 4) 2-23 |

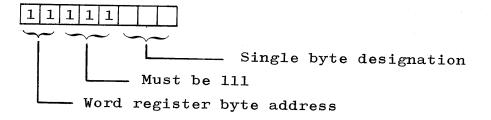

|          | Word Register Byte Address 2-24                     |

| SECTION  | TITLE                                    |     |     |   | PAGE |

|----------|------------------------------------------|-----|-----|---|------|

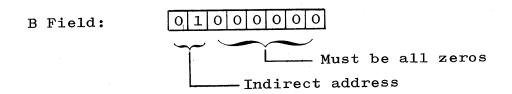

| 2 (cont) | Indirect Address (Groups 2, 3, and 4)    | :   |     | • | 2-26 |

|          | Special Indirect Address                 | •   | •   |   | 2-26 |

|          | B Address Used As Destination Address    | ι • |     | • | 2-26 |

|          | C Field                                  |     |     |   | 2-26 |

|          | Literal                                  |     |     |   | 2-27 |

|          | C Address                                |     |     |   | 2-27 |

|          | Register Address                         |     | •   |   | 2-27 |

|          | Scratchpad Memory Address                | •   |     | • | 2-27 |

|          | Word Register Byte Address .             |     |     | • | 2-27 |

|          | Indirect Address                         |     |     |   | 2-27 |

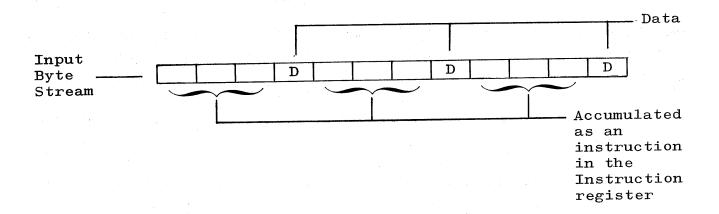

|          | Fetch Cycle                              |     |     |   | 2-28 |

|          | Instruction Fetch                        |     |     |   | 2-28 |

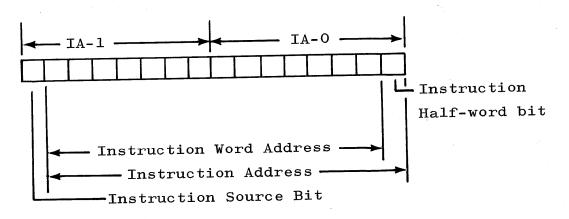

|          | Instruction Address                      |     | •   |   | 2-28 |

|          | Fetch From Local Memory, Normal Sequence | •   |     |   | 2-29 |

|          | Fetch From Local Memory, After Branch    |     |     |   | 2-29 |

|          | Fetch From System Memory                 |     |     |   | 2-29 |

|          | Fetch Cycle                              |     |     |   | 2-30 |

|          | Parity Check                             | •   | •   |   | 2-30 |

|          | Tag Check                                |     |     |   | 2-30 |

|          | L Instruction Passed Over                | •   | •   |   | 2-30 |

|          | Transfer of R Instruction                | • 1 | •   | • | 2-30 |

|          | Instruction Address Count Up             | • ( | •   | • | 2-31 |

| N.       | Fault Interrupts                         |     |     | • | 2-31 |

|          | Priority Among Faults                    |     |     | • | 2-33 |

|          | Fault Instruction Execution              |     |     | • | 2-34 |

|          | Attention Needed Timer                   |     |     | • | 2-34 |

|          | Scan Bus (B 6700)                        |     | •   | • | 2-35 |

|          | Scan-Out Information Word (B 6700)       |     |     |   | 2-35 |

|          | Ready And Scan Access Obtained (B 6700   |     |     |   | 2-36 |

|          | Not Ready (B 6700)                       | •   | , , | • | 2-36 |

| SECTION  | TITLE                               | PAGE         |

|----------|-------------------------------------|--------------|

| 2 (cont) | Invalid Scan Orders (B 6700)        | 2-36         |

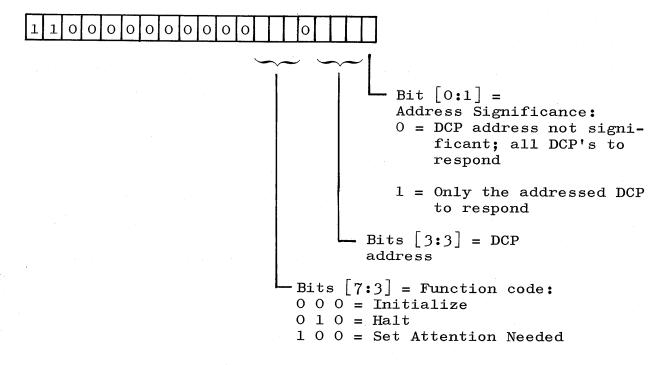

|          | Initialize [000] (B 6700)           | 2-37         |

|          | Set Attention Needed [100] (B 6700) | 2-37         |

|          | Halt [010] (B 6700)                 | 2-37         |

|          | Pseudo Scan Bus (B 5700)            | 2-37         |

|          | Initialize (B 5700)                 | 2-38         |

|          | Set Attention Needed (SAN) (B 5700) | 2-38         |

|          | Halt (B 5700)                       | 2-38         |

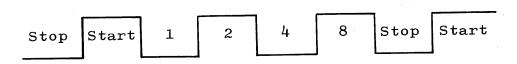

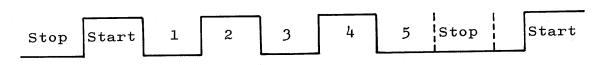

|          | Bootstrap Mode                      | 2-38         |

|          | Functional Description              | 2-39         |

|          | Enter Bootstrap Mode                | 2-39         |

|          | Exit Bootstrap Mode                 | 2-40         |

|          | Operational Description             | 2-40         |

|          | Versatility                         | 2-40         |

| 3        | INSTRUCTIONS                        | 3-1          |

|          | General                             | 3-1          |

|          | Unit Time                           | 3-1          |

|          | Indirect Address                    | 3-1          |

|          | Main Memory Access                  | 3-1          |

|          | Adapter Write Timing Specification  | 3-1          |

|          | Undefined Operation Codes           | 3-2          |

|          | Undefined Addresses                 | 3-3          |

|          | Invalid Instructions                | 3-3          |

|          | Instruction Format                  | 3 <b>-</b> 3 |

|          | Group O Instructions                | 3-3          |

|          | Idle                                | 3-3          |

|          | Adapter Write                       | 3-4          |

|          | Adapter Interrogate                 | 3-5          |

|          | Stop/Branch On Breakpoint           | 3-6          |

|          | Shift MA Right                      | 3-7          |

|          | Set System Interrupt                | 3 <b>-</b> 9 |

|          | Set Cluster Mask Register           | 3-9          |

|          | Read Cluster Mask Register          | 3-9          |

| SECTION  | TITLE                                                | PAGE          |

|----------|------------------------------------------------------|---------------|

| 3 (cont) | Group 1 Instructions                                 | 3-10          |

|          | Adapter Read When Attention Needed                   | 3-10          |

|          | Adapter Read If Needed                               | 3-11          |

|          | Decrement Y, Branch if Y Is Zero                     | 3-12          |

|          | Decrement Y, Branch if Y Is Non-Zero                 | 3-12          |

|          | Branch If System Attention Needed                    | 3-13          |

|          | Branch                                               | 3-13          |

|          | Branch Relative With X                               | 3-14          |

|          | Branch Relative Indirect                             | 3-15          |

|          | Group 2 Instructions                                 | 3-16          |

|          | Move Half-Word                                       | 3-16          |

|          | Local Memory Read, Indirect Address                  | 3-17          |

|          | Scratchpad Memory Read                               | 3-17          |

|          | Local Memory Read, Direct Address                    | 3-18          |

|          | Local Memory Write, Indirect Address                 | 3 <b>-</b> 19 |

|          | Scratchpad Memory Write                              | 3-19          |

|          | Local Memory Write, Direct Address                   | 3-20          |

|          | Main Memory Read                                     | 3-20          |

|          | Main Memory Write Unconditional                      | 3-21          |

|          | Main Memory Write-Read Unconditional (N/A to B 5700) | 3-21          |

|          | Main Memory Protected Write (N/A to B 5700)          | 3-22          |

|          | Main Memory Write-Read Protected                     |               |

|          | (N/A to B 5700)                                      | 3-23          |

|          | Group 3 Instructions                                 | 3-24          |

|          | Half-Word Add                                        | 3-24          |

|          | Half-Word Add, Literal In B                          | 3-24          |

|          | Half-Word Subtract                                   | 3-25          |

|          | Half-Word Subtract, Literal In B                     | 3-26          |

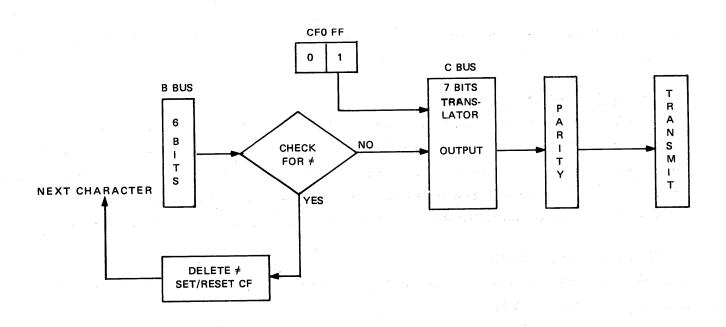

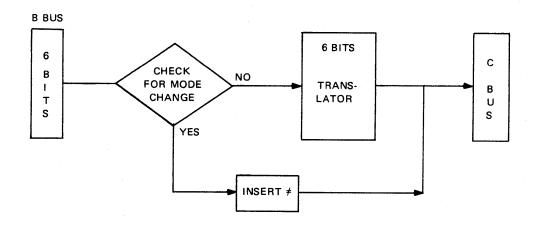

|          | Translate (B 6700)                                   | 3-26          |

|          | Translate (B 5700)                                   | 3-27          |

|          | Parity                                               | 3-28          |

| SECTION                                  | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PAGE              |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 3 (cont)                                 | Group 4 Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-29              |

| en e |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-29              |

|                                          | Add, Literal In B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-30              |

| No. 1 to the second second               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-30              |

|                                          | Subtract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-30              |

|                                          | Subtract, Literal In B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-31              |

|                                          | Subtract, Literal In C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-32              |

| •                                        | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3 <b>-</b> 32     |

|                                          | Logical AND, Literal In B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-33              |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-33              |

|                                          | Logical AND-OR MA, Literal In C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-34              |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 <b>-</b> 34     |

|                                          | Logical OR, Literal In B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3 <b>-</b> 35     |

|                                          | Logical OR, Literal In C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3 <b>-</b> 36     |

|                                          | Logical Exclusive OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-36              |

|                                          | Logical Exclusive OR, Literal In B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-37              |

|                                          | Logical Exclusive OR, Literal In C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 <b>-</b> 38     |

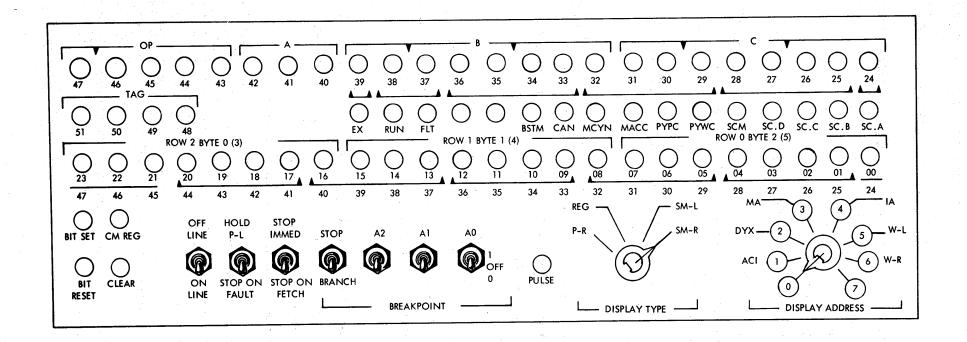

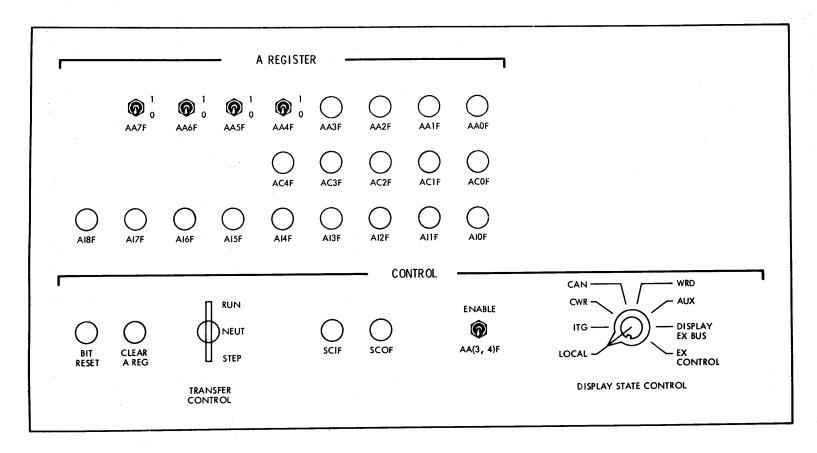

| 4 D                                      | OCP DISPLAY PANEL AND MAINTENANCE AIDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-1               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . <u>.</u><br>4-1 |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1               |

| <b>S</b> (1) (1) (1)                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-1               |

|                                          | and the second s | 4-3               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 <b>-</b> 3      |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-3               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-4               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-5               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-5               |

|                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-5               |