Burroughs

B 5220

CENTRAL CONTROL

TECHNICAL MANUAL

PROPERTY OF AND TO BE RETURNED TO

# Burroughs

PRINTED IN U.S.A. 3/16/64 B 5220.51

B 5220.51 i

March 29, 1965

TABLE OF CONTENTS

| SUBJECT                                                          | TITLE                                                                                                         | DATE                                                          |                                              |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6                      | PREVENTIVE MAINTENANCE  Daily (Not Applicable) Weekly (Not Applicable) Monthly Quarterly Semi-Annually Annual | March 16,<br>March 16,<br>March 16,                           | 1964<br>1964<br>1964<br>1964                 |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7               | TROUBLESHOOTING  Test Switches and Indicators                                                                 | March 16,<br>March 16,<br>March 16,                           | 1964<br>1964<br>1964<br>1964                 |

| 3<br>3.1<br>3.2<br>3.3<br>3.4                                    | ADJUSTMENTS IntroductionClock Pulse WidthVariable BiasDelay Multi                                             | March 16,                                                     | , 1964<br>, 1964                             |

| 4.1<br>4.2<br>- 4.3                                              | ASSEMBLY AND DISASSEMBLY  Voltage Regulator Wire Wrap Pins Packages                                           |                                                               | 1964                                         |

| 5.1<br>5.2<br>5.4                                                | INSTALLATION Introduction                                                                                     | March 16,                                                     | , 1964<br>, 1964                             |

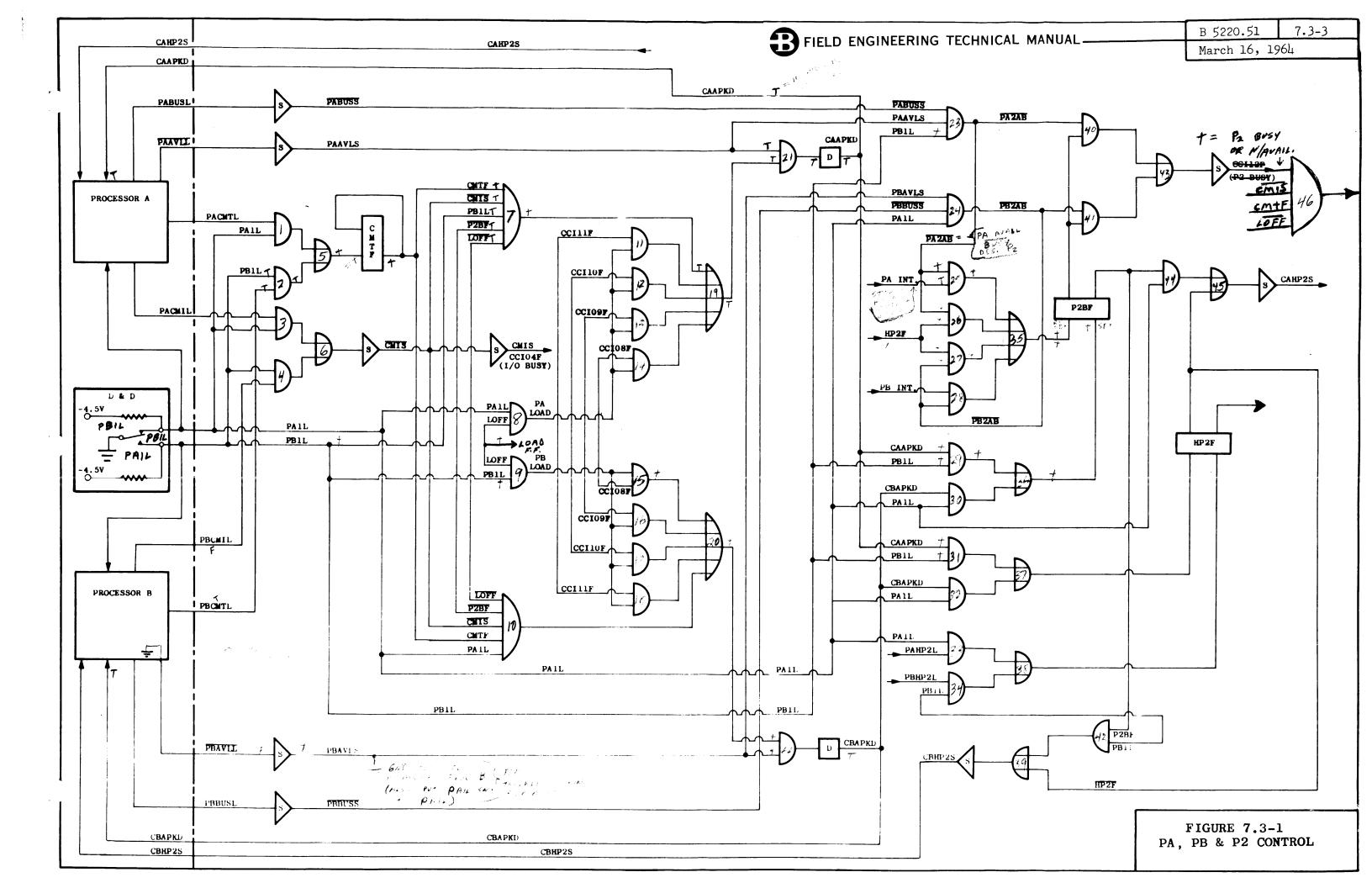

| 7<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8<br>7.9 | FUNCTIONAL DESCRIPTION  Introduction                                                                          | March 16,<br>March 16,<br>March 16,<br>March 16,<br>March 16, | 1964<br>1964<br>1964<br>1964<br>1964<br>1964 |

# LIST OF ILLUSTRATIONS

| FIGURE                                                                                                                         | TITLE                                      | PAGE                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2-1<br>2.2-2<br>2.2-3<br>2.4-1<br>2.6-1<br>2.6-2<br>2.6-3                                                                    | Dual, Right and Left No. 2 Unwrapping Tool | 2.2-1<br>2.2-1<br>2.2-2<br>2.4-1<br>2.6-1<br>2.6-2<br>2.6-4                                                                                                |

| 3.2-1<br>3.2-2<br>3.3-1<br>3.4-1                                                                                               | One Megacycle Pulse Train                  | 3.2-1<br>3.2-1<br>3.3-1<br>3.4-1                                                                                                                           |

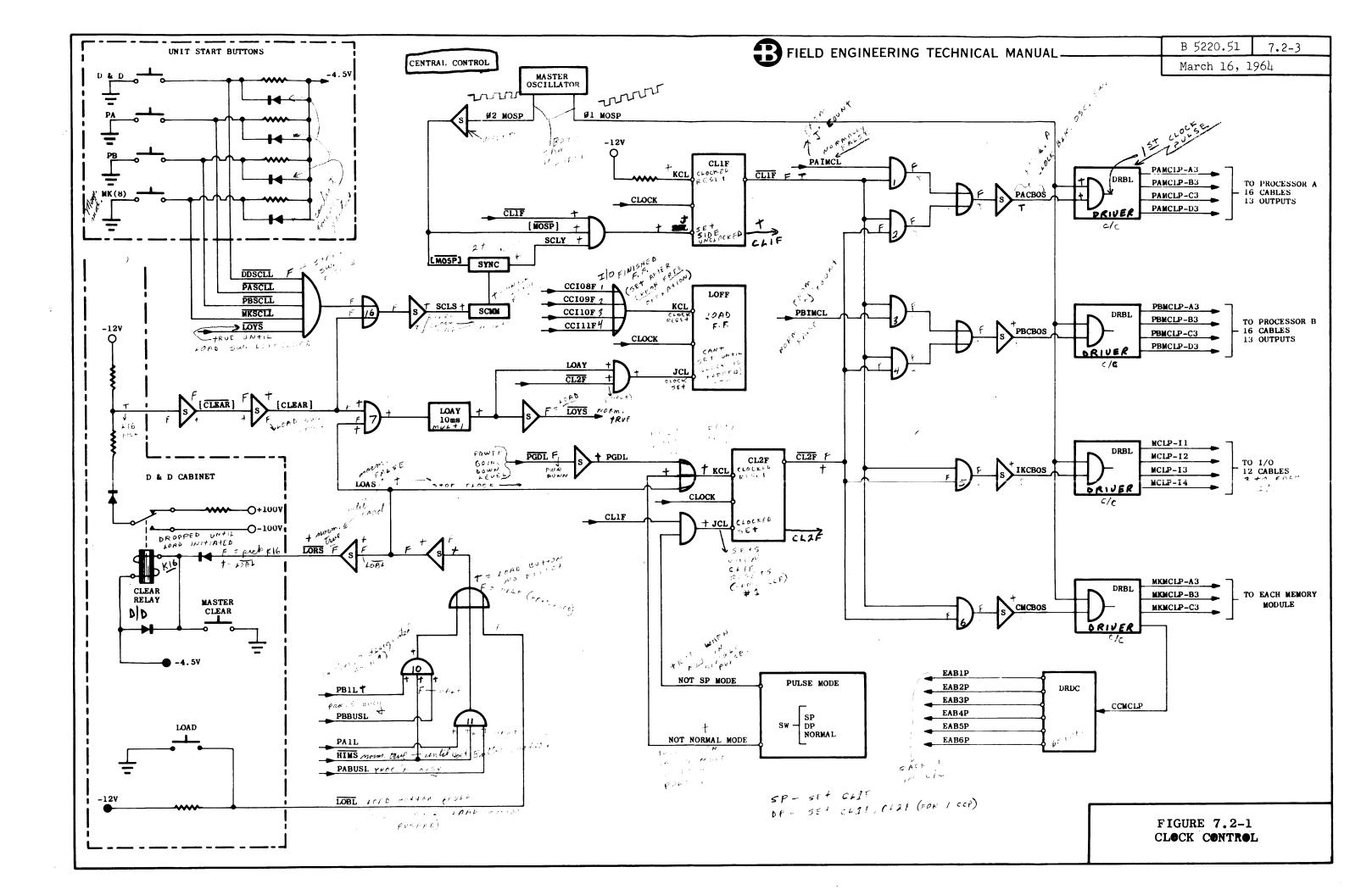

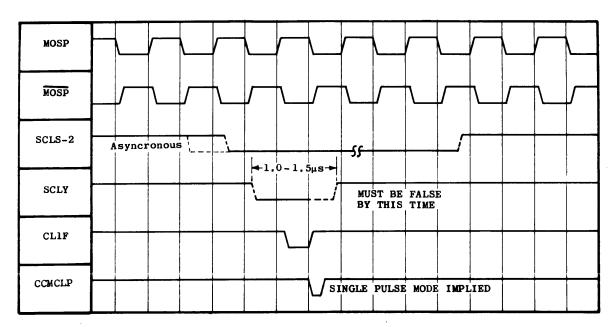

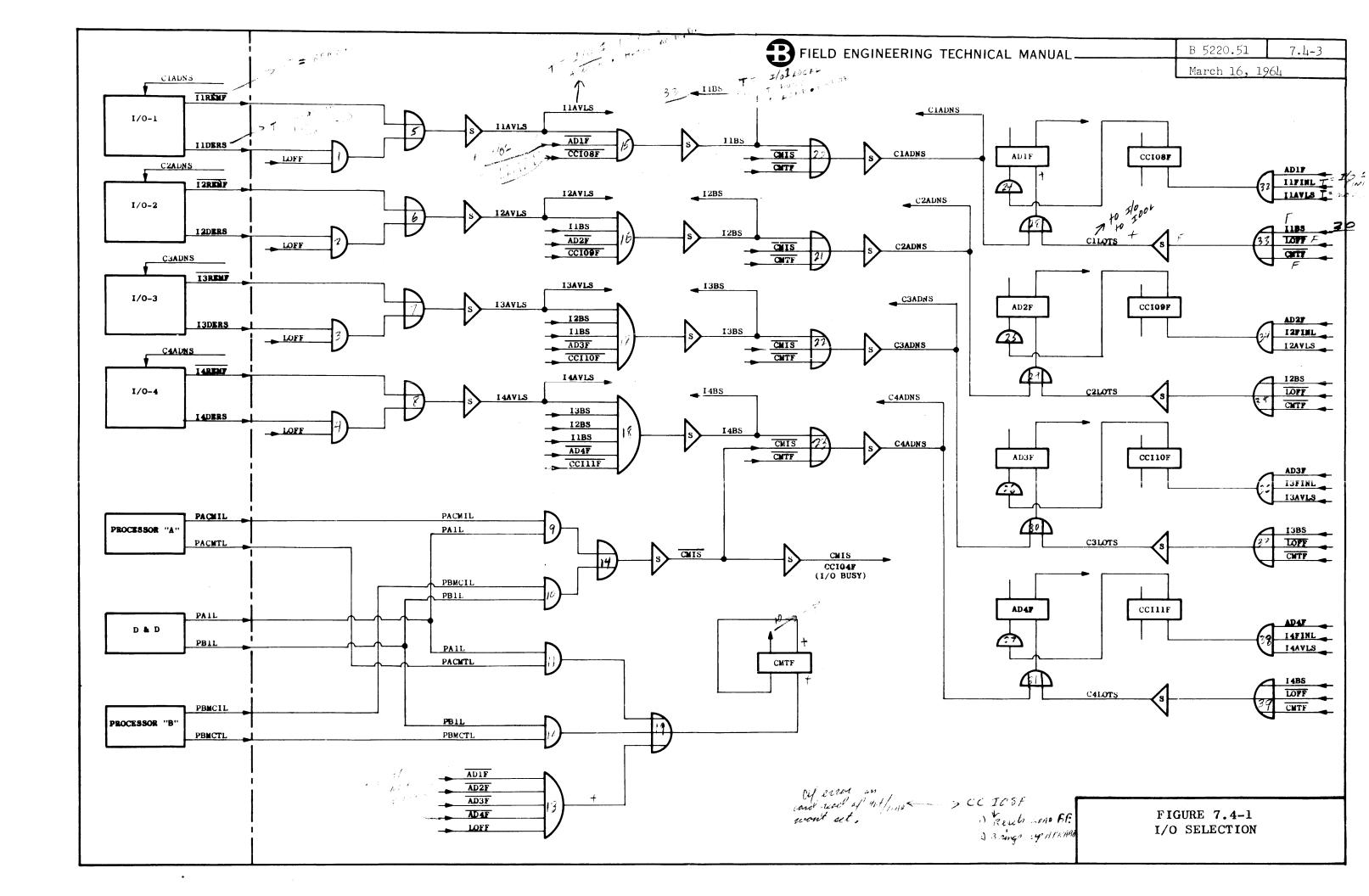

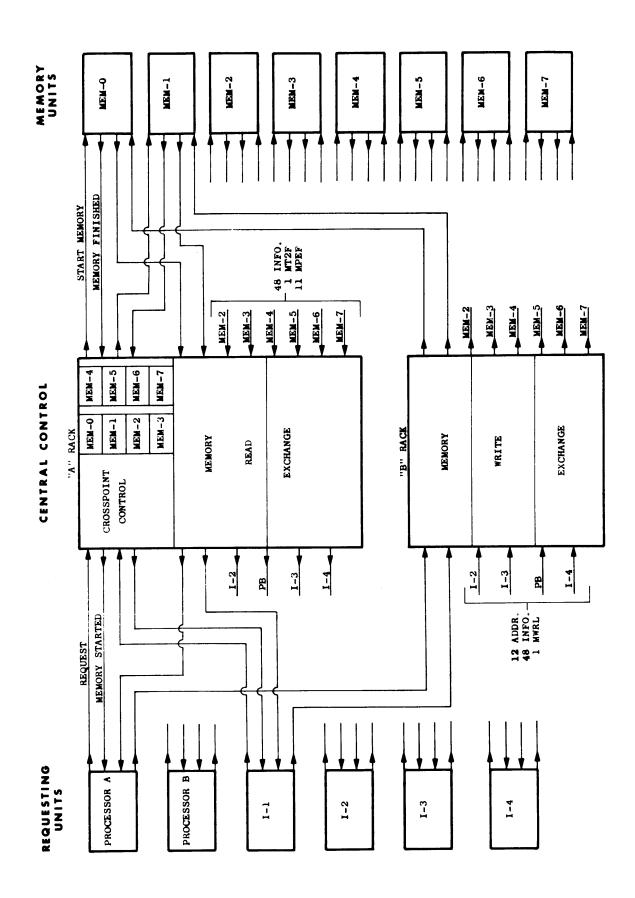

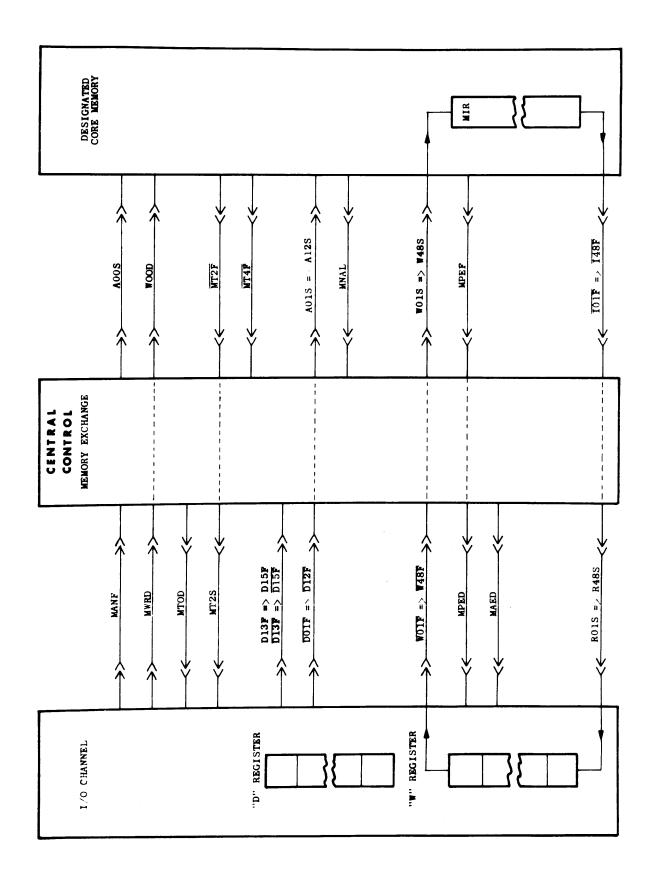

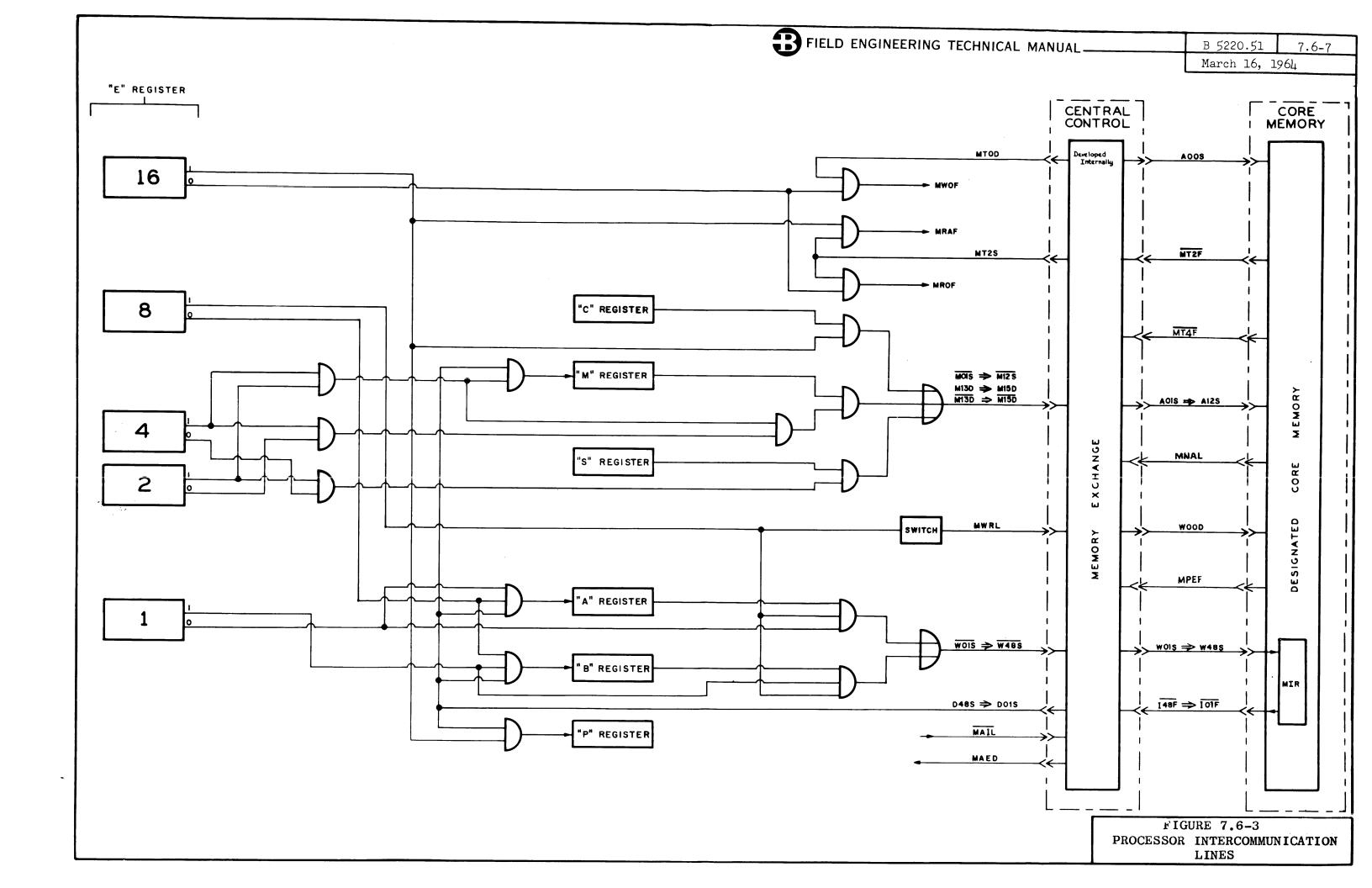

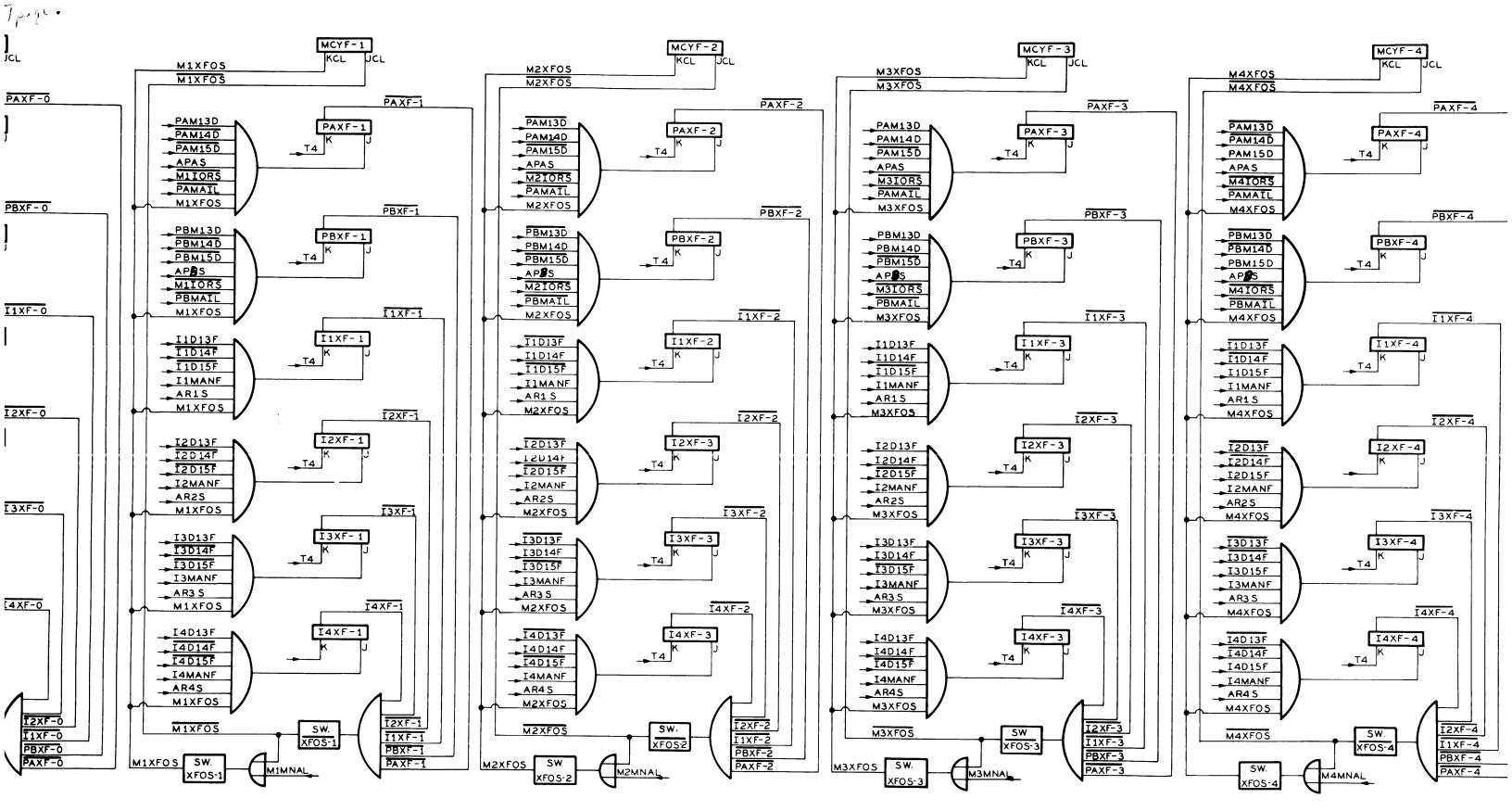

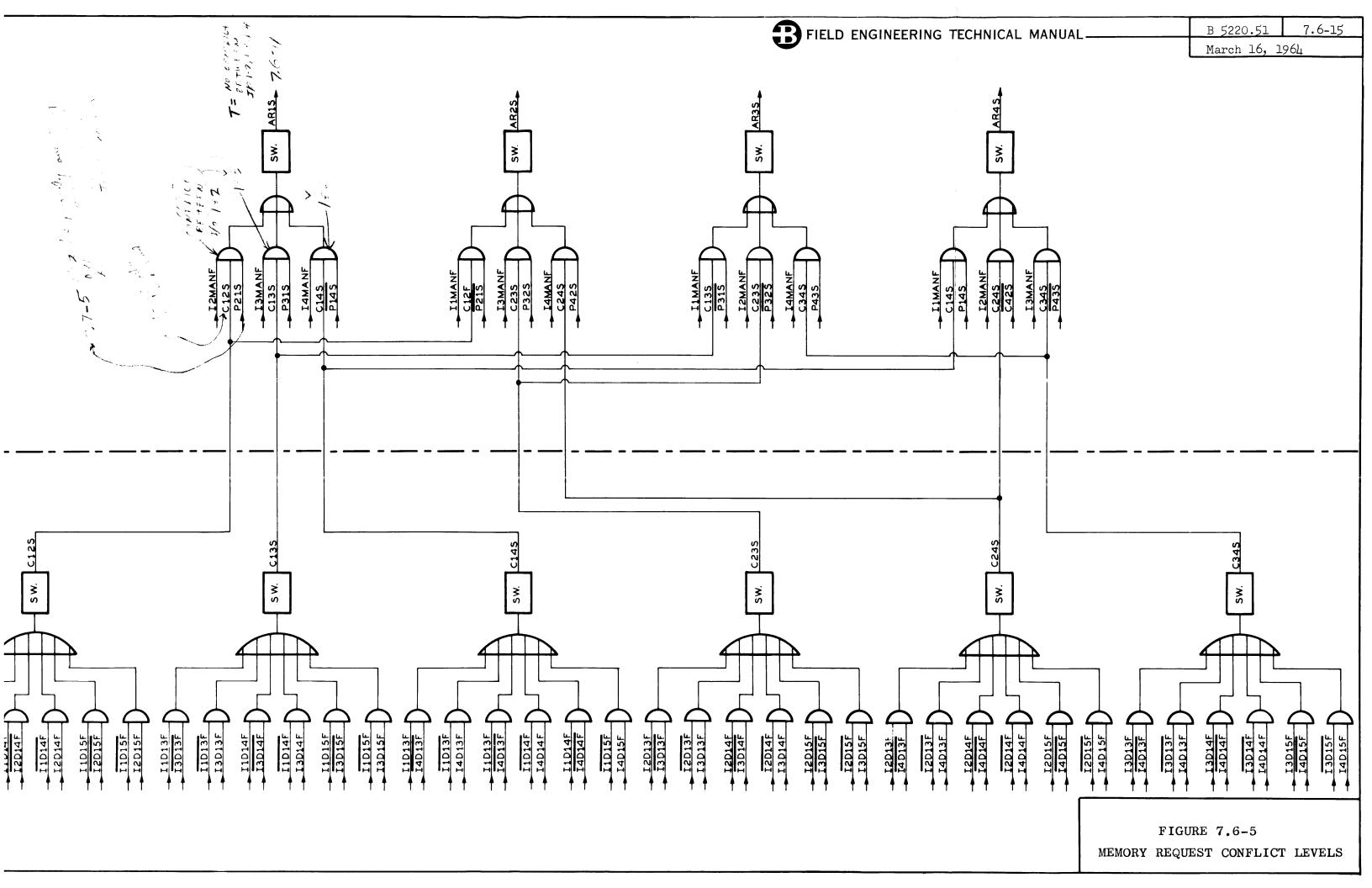

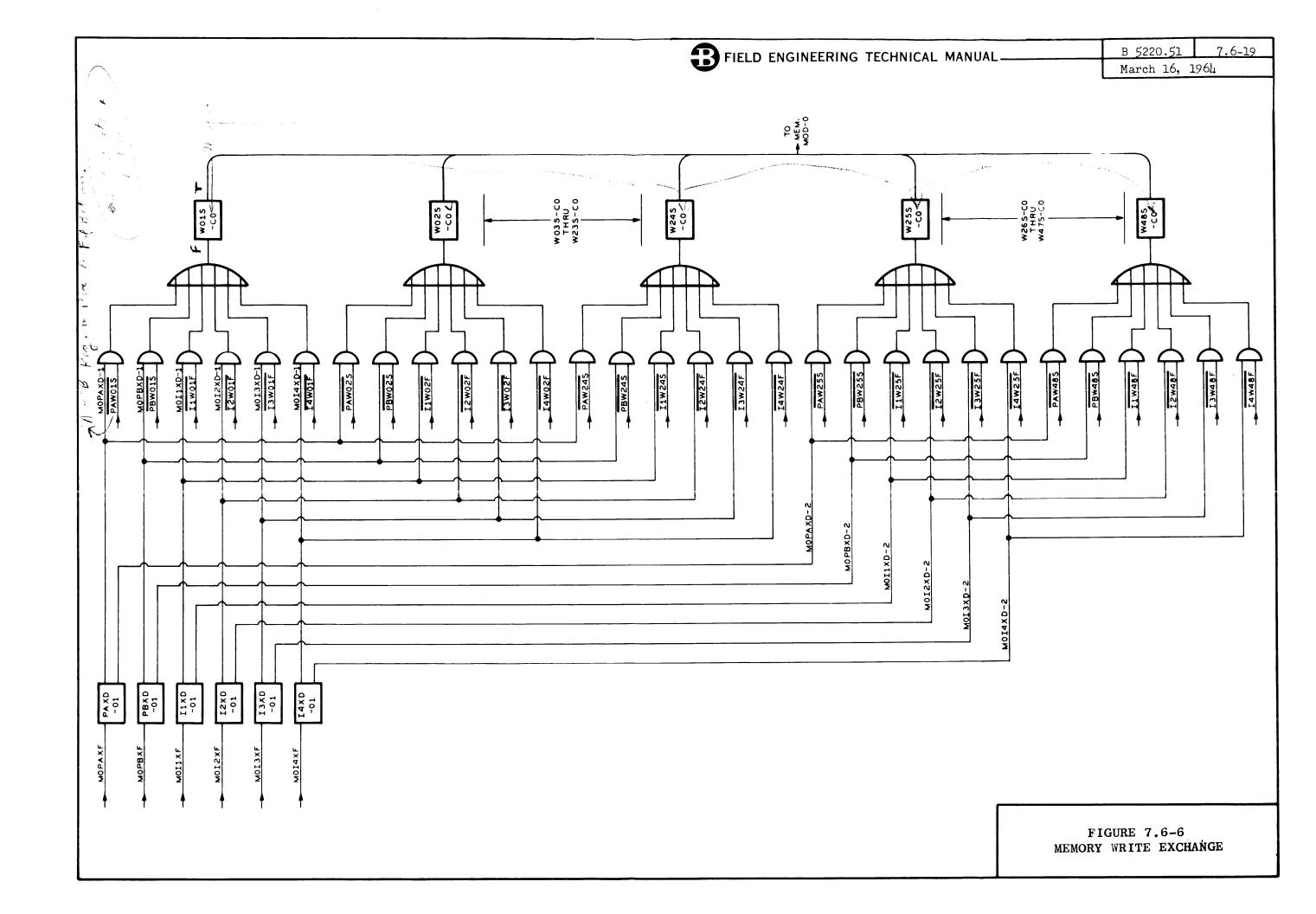

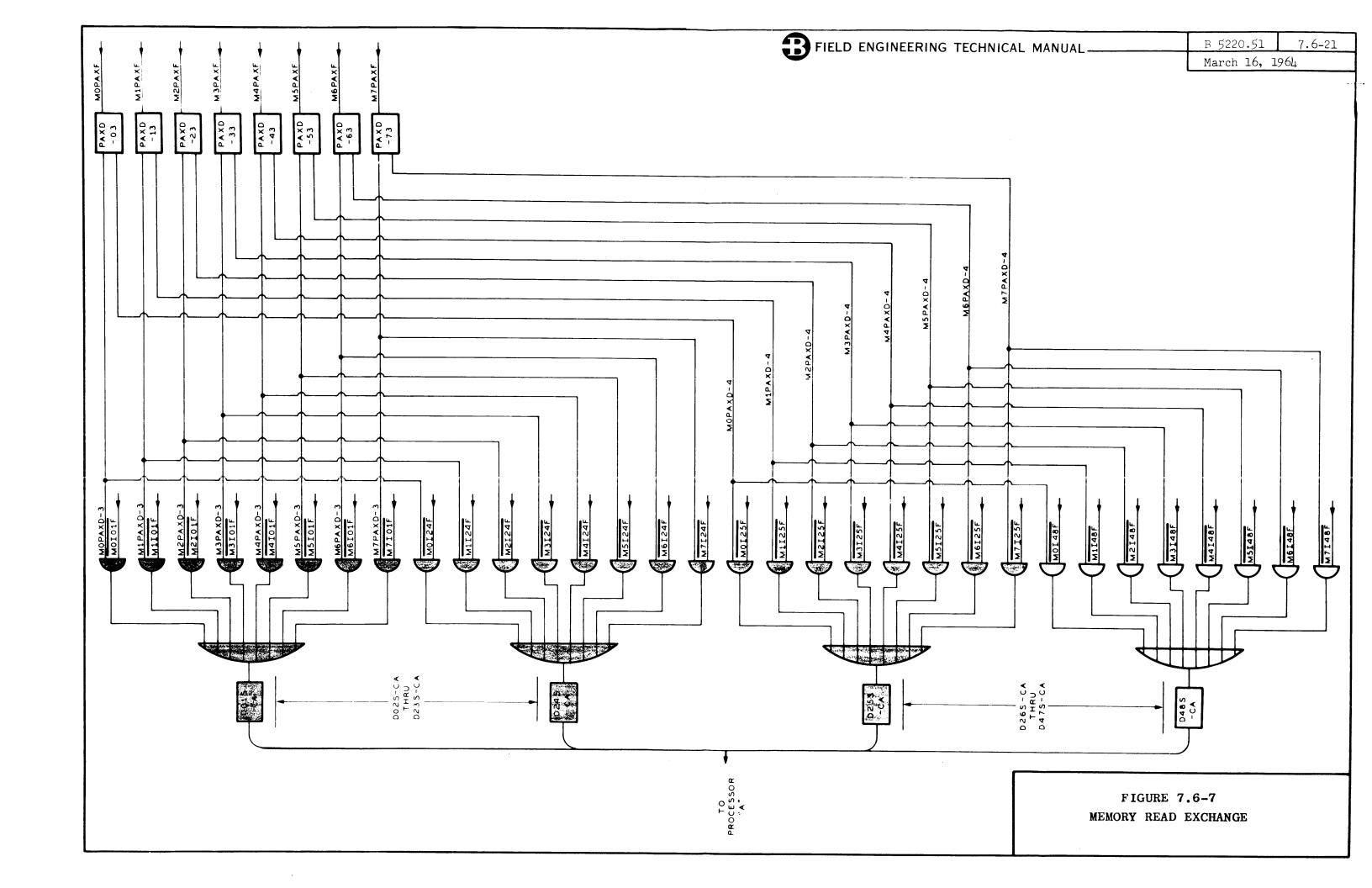

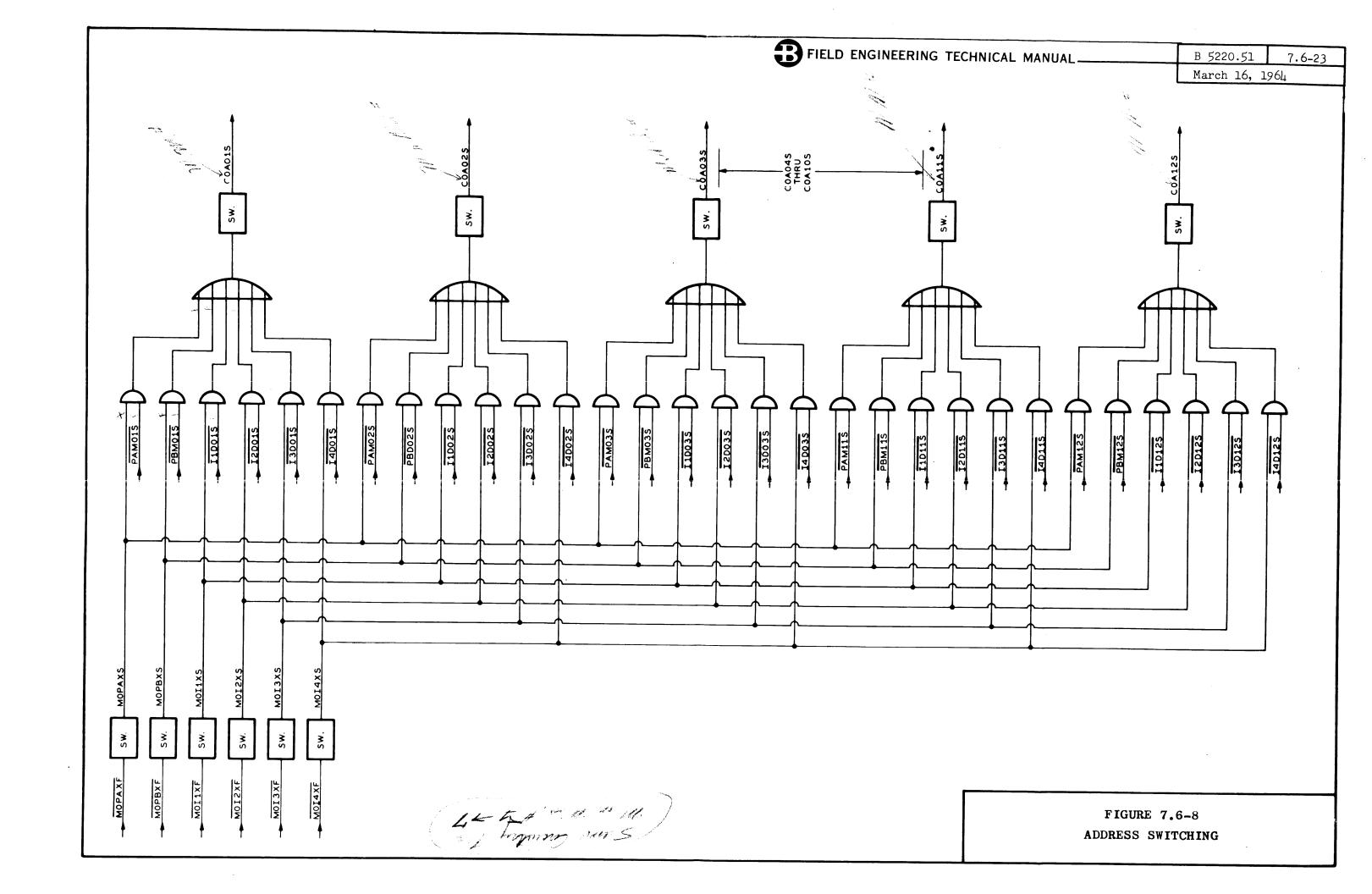

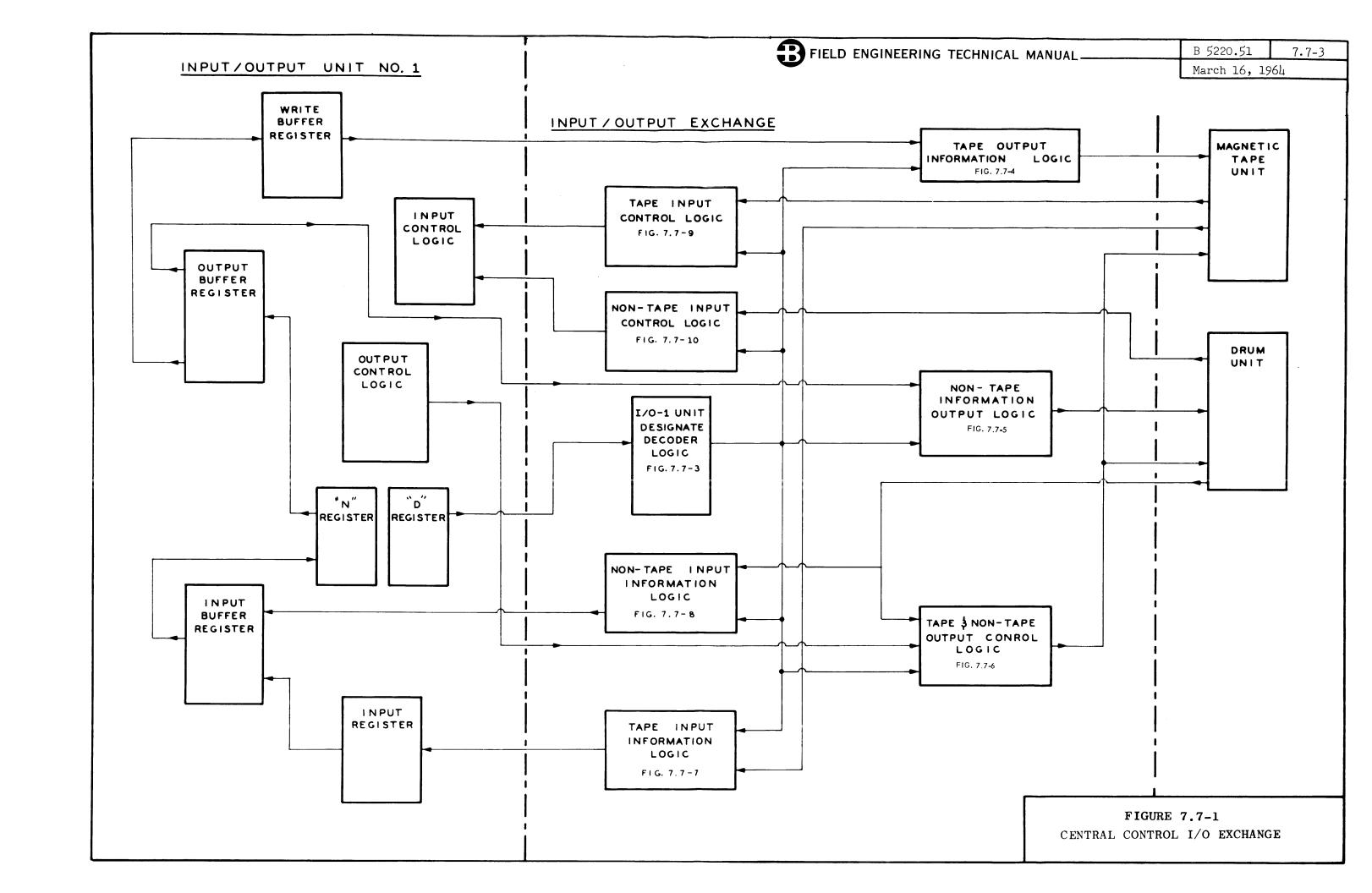

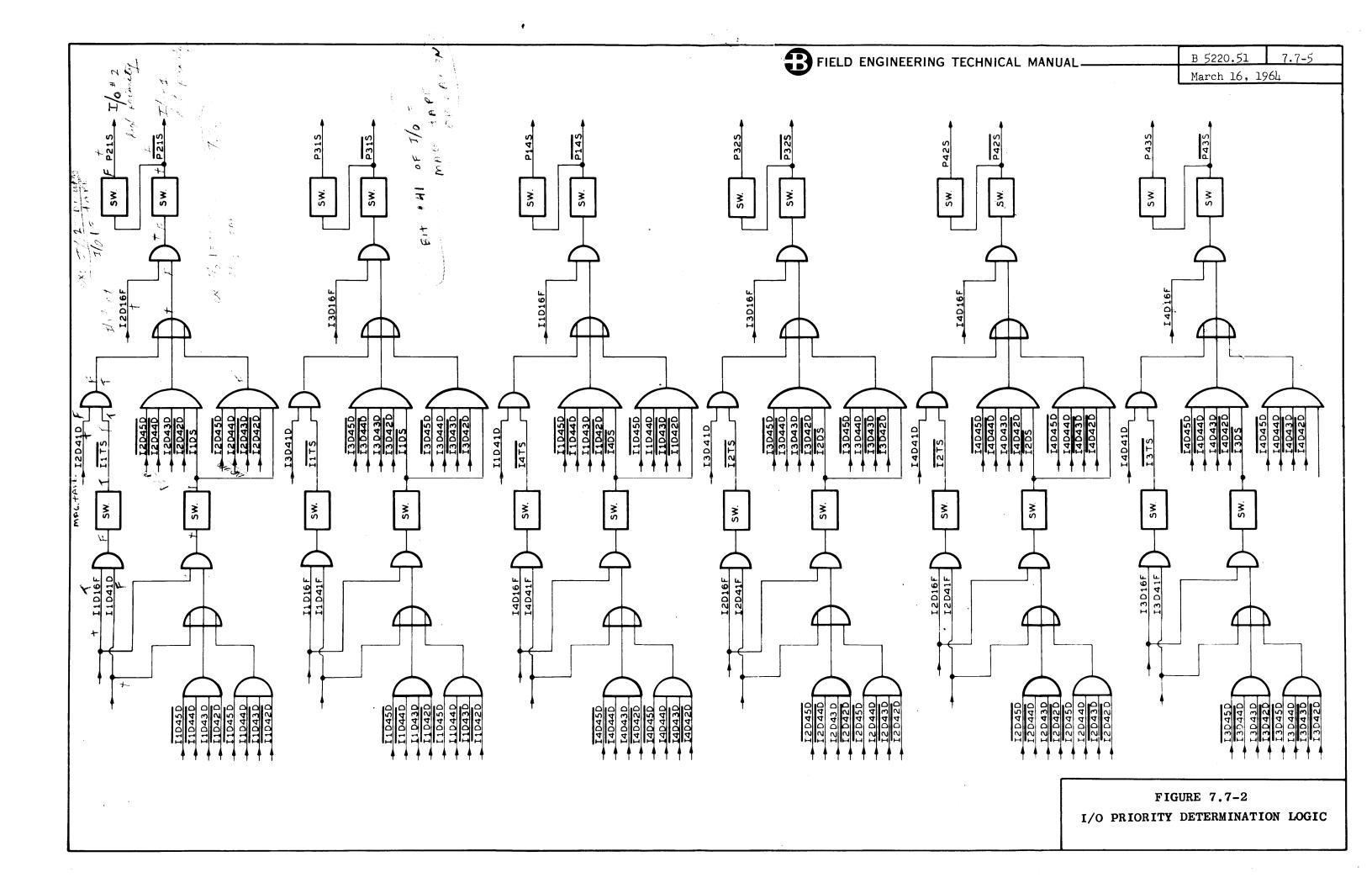

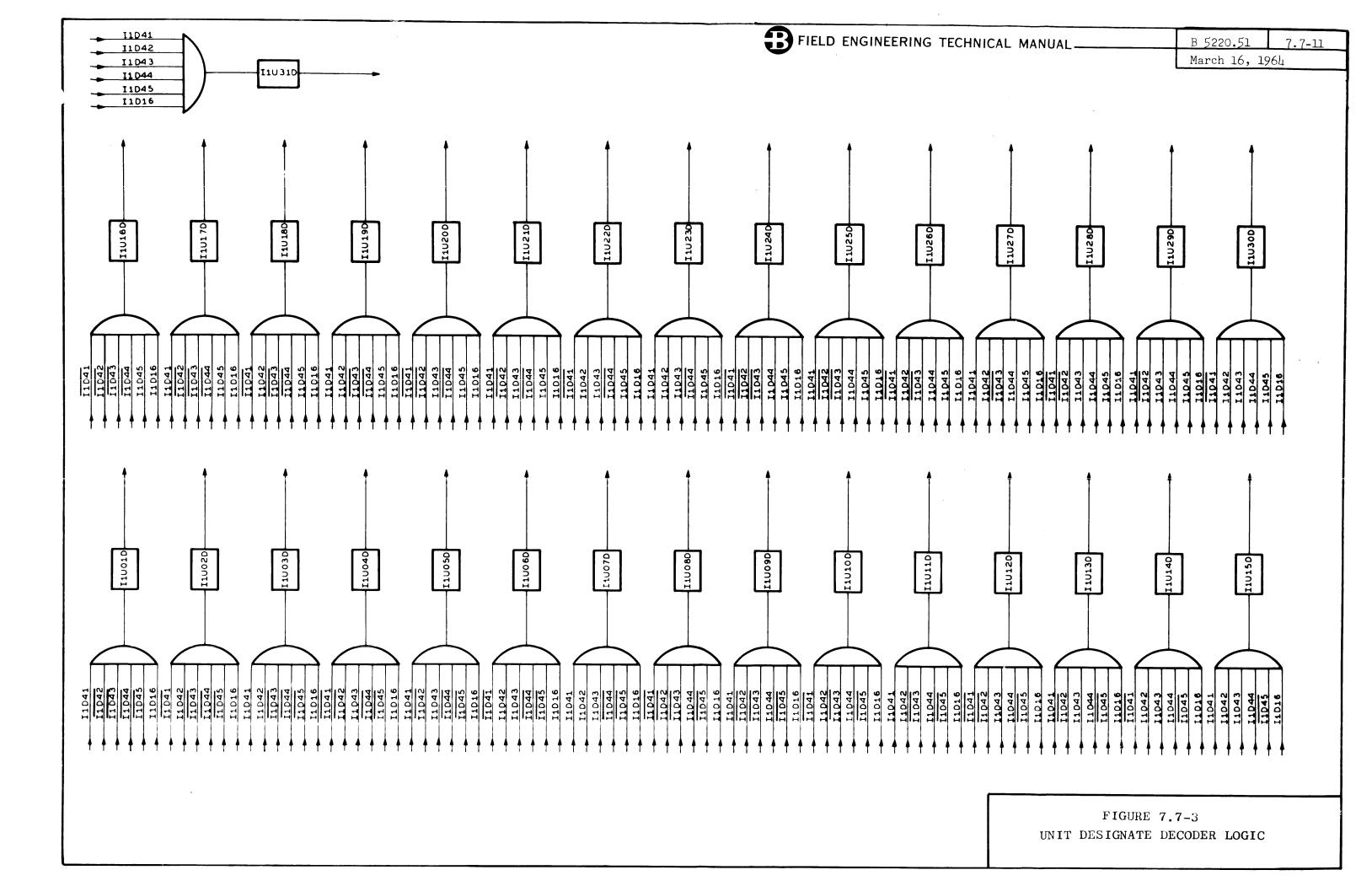

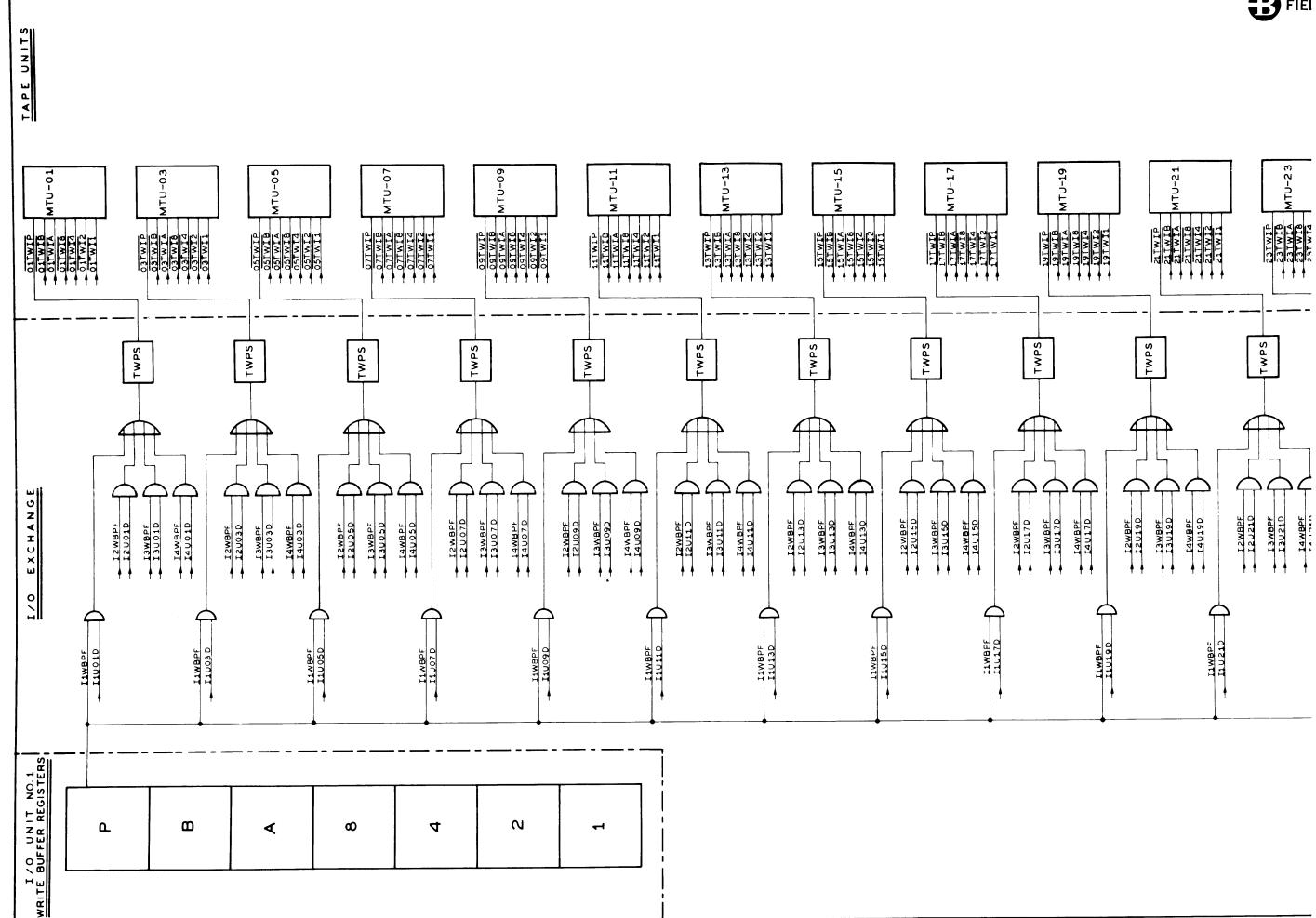

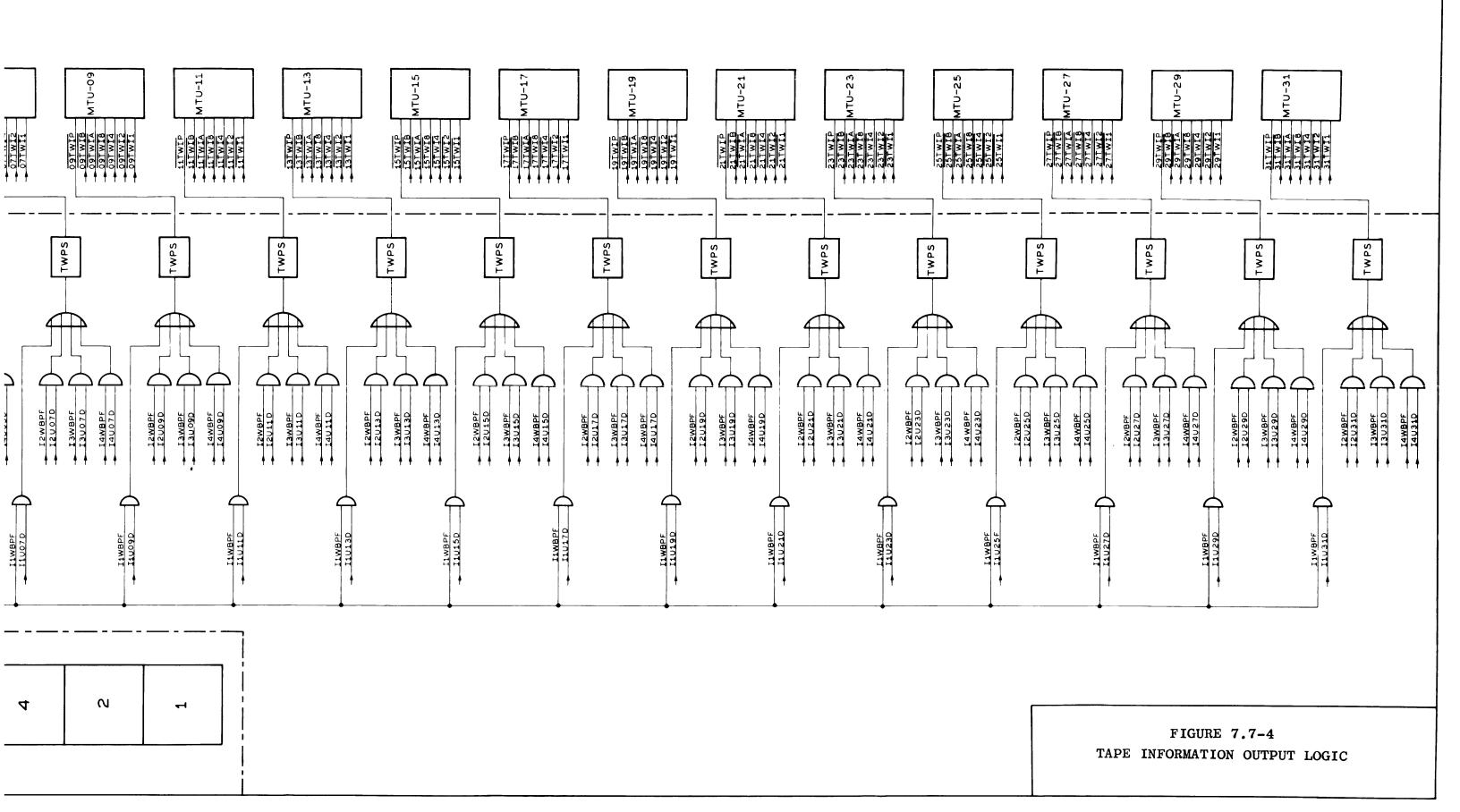

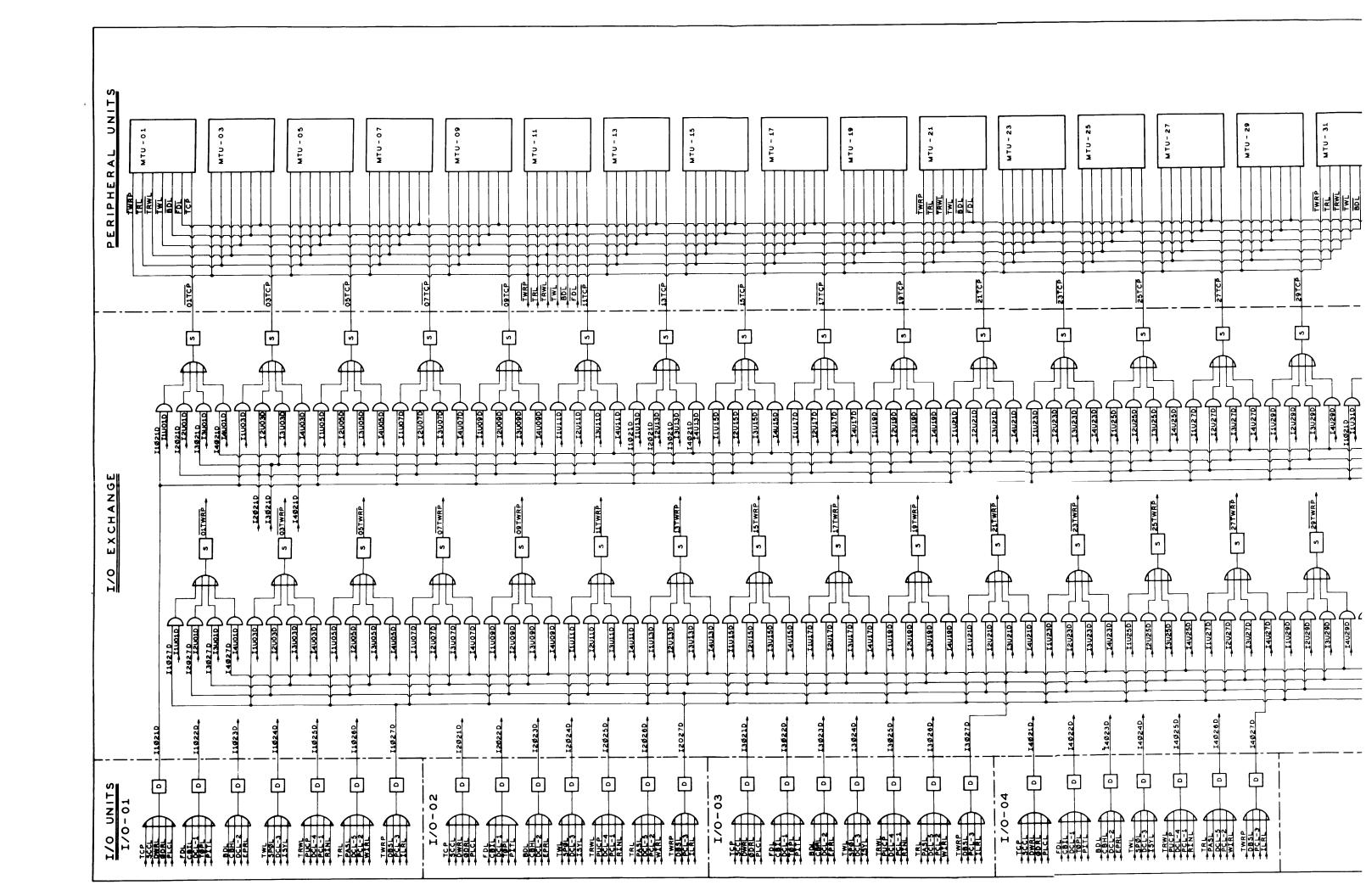

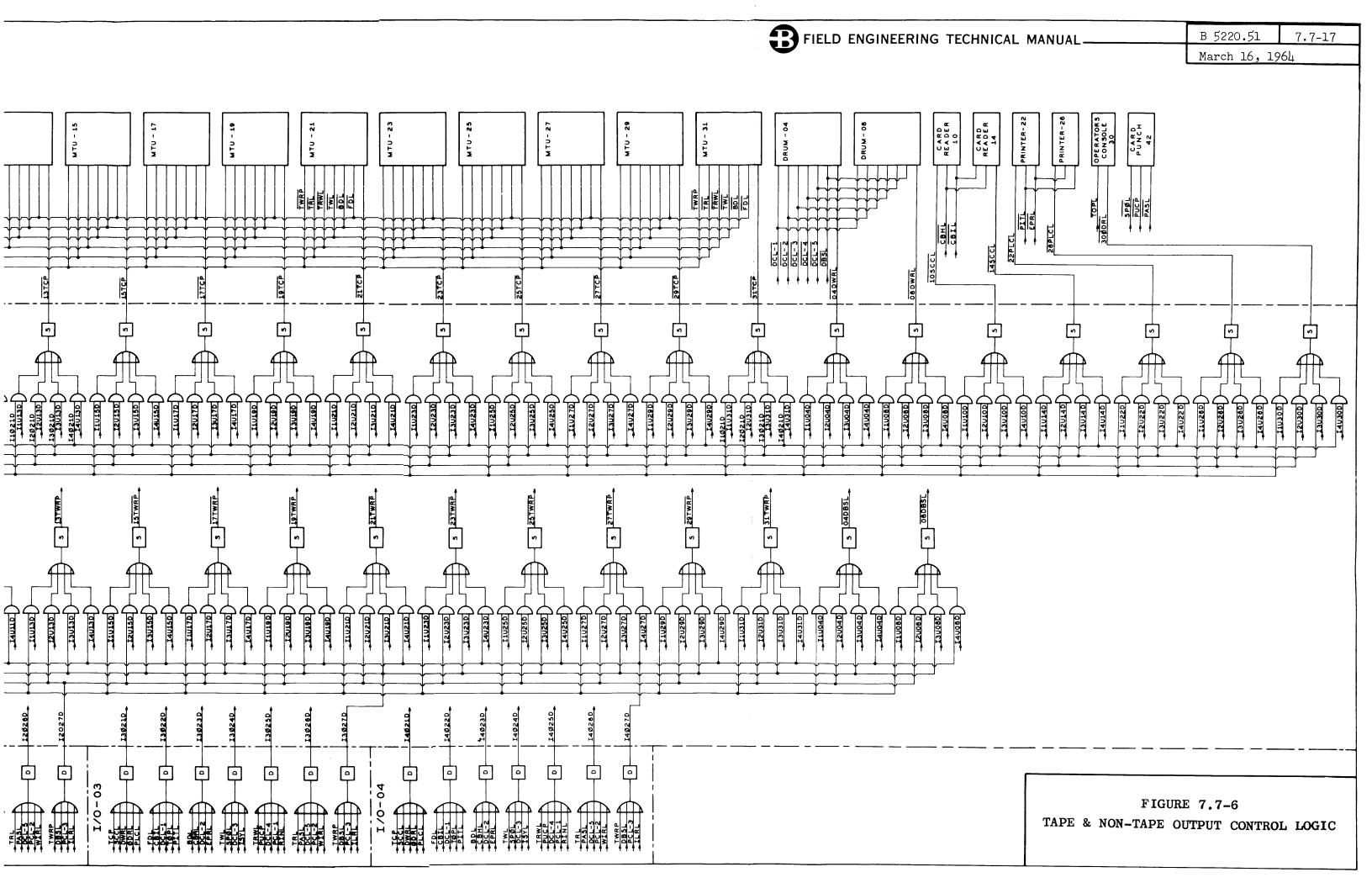

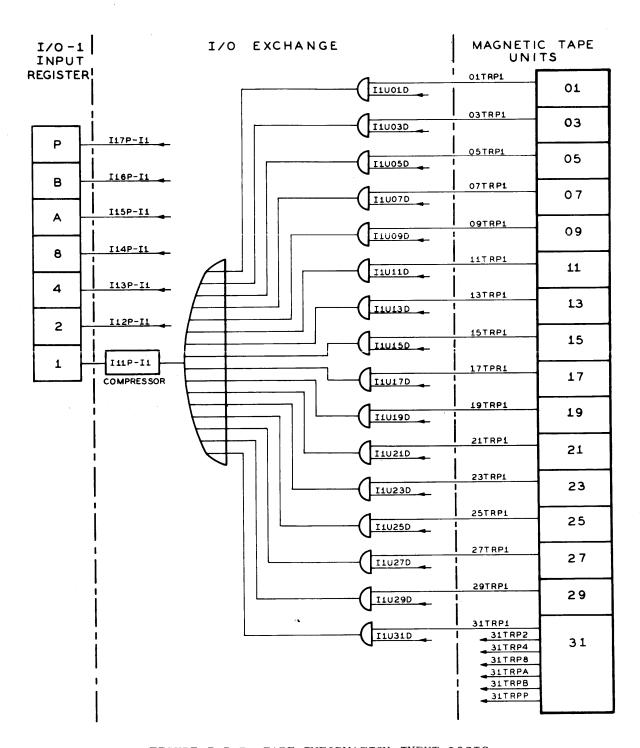

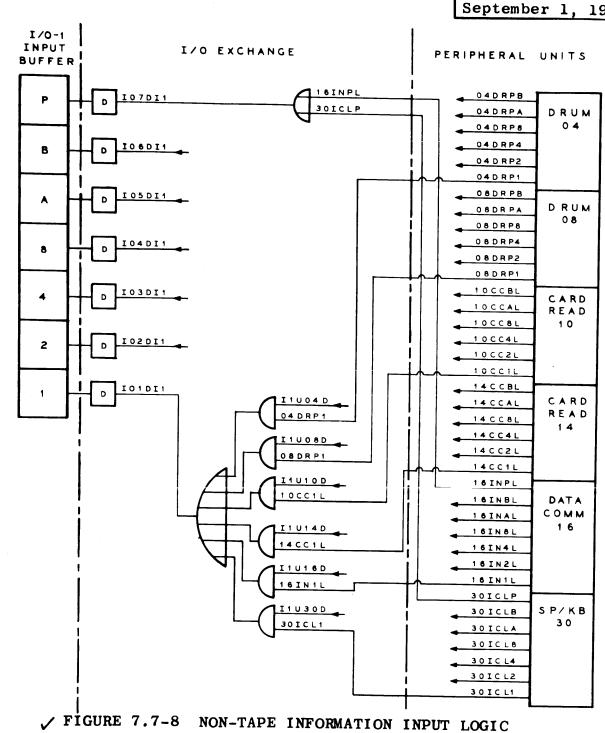

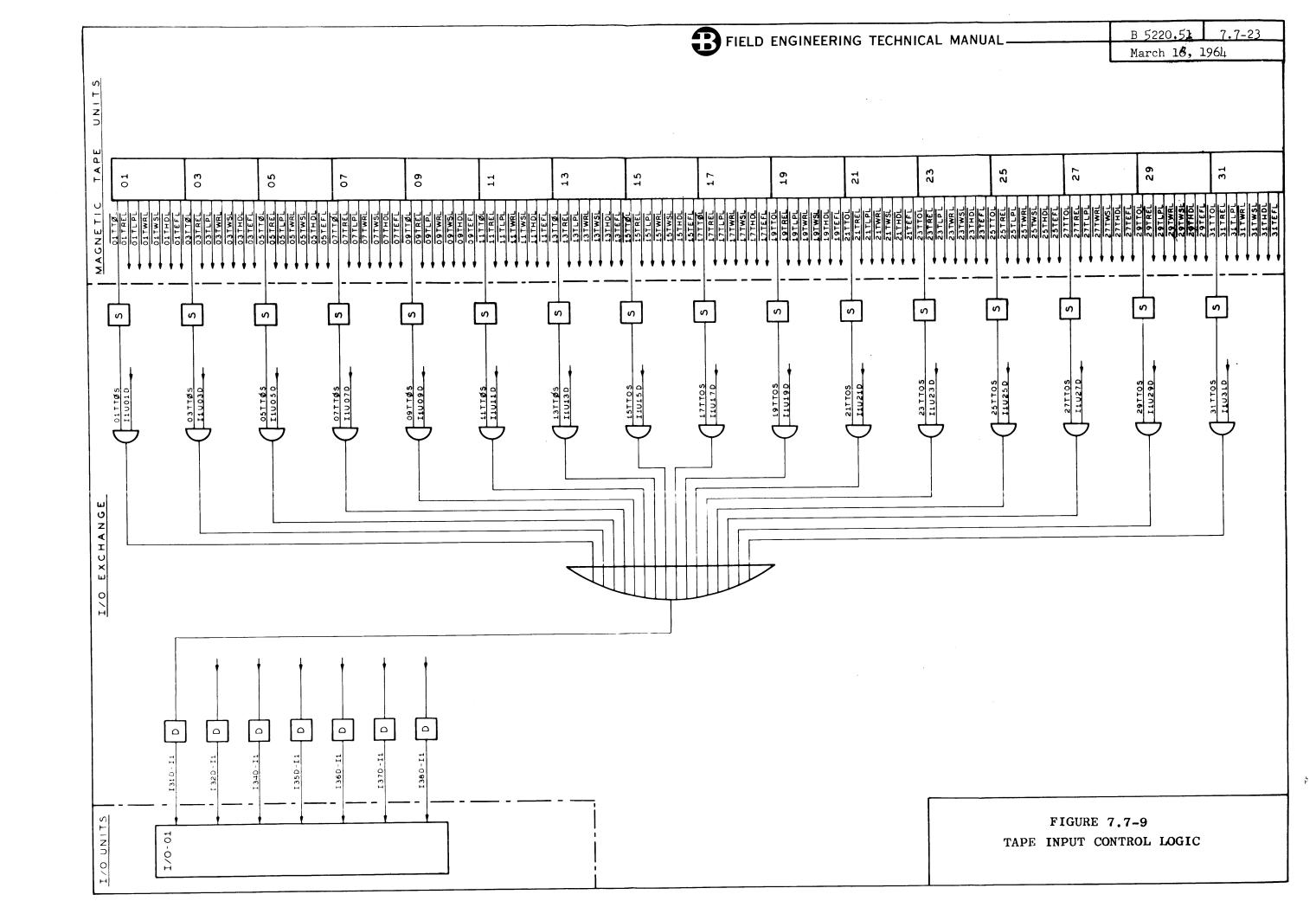

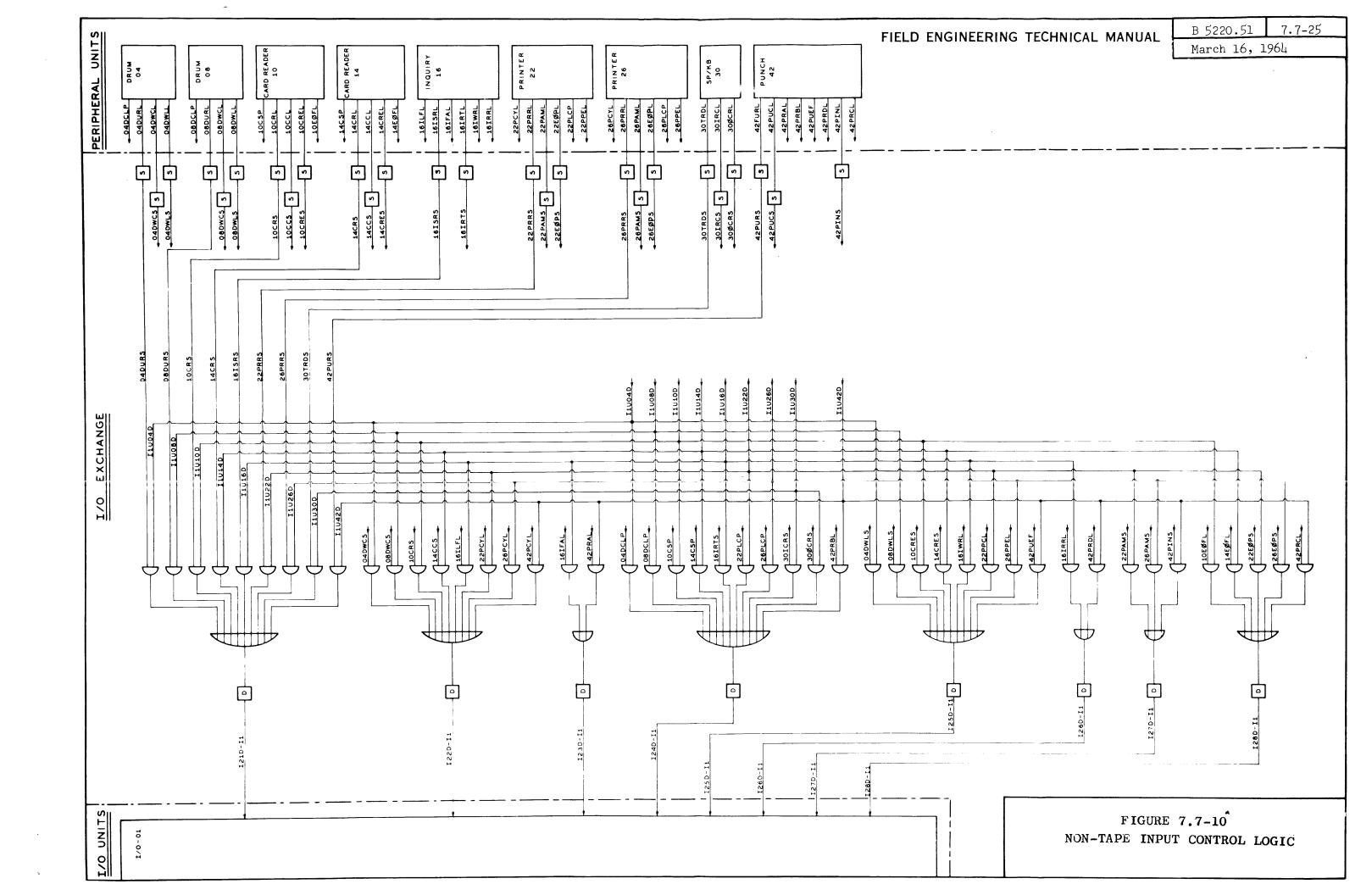

| 7.2-1 7.2-2 7.3-1 7.4-1 7.5-1 7.6-2 7.6-3 7.6-4 7.6-5 7.6-6 7.6-7 7.6-8 7.7-1 7.7-2 7.7-3 7.7-4 7.7-5 7.7-6 7.7-7 7.7-9 7.7-10 | Clock Control                              | 7.2-3<br>7.2-5<br>7.3-3<br>7.4-3<br>7.6-4<br>7.6-2<br>7.6-19<br>7.6-19<br>7.6-23<br>7.7-3<br>7.7-1<br>7.7-15<br>7.7-15<br>7.7-2<br>7.7-2<br>7.7-2<br>7.7-2 |

|                                                                                                                                | LIST OF TABLES                             |                                                                                                                                                            |

| TABLE                                                                                                                          | TITLE                                      | PAGE                                                                                                                                                       |

| 5.2-1<br>5.2-2                                                                                                                 | Inter-Unit Cable ListInter-Gate Cable List | 5.2 <b>-</b> 1<br>5.2 <b>-</b> 5                                                                                                                           |

| 7.5-1                                                                                                                          | Interrupts and Address Locations           | 7 <b>.</b> 5 <b>-</b> 2                                                                                                                                    |

B 5220.51 1.1-1

March 16, 1964

# SECTION 1

# PREVENTIVE MAINTENANCE

1.1 DAILY

(Not Applicable)

1.2 WEEKLY

(Not Applicable)

B 5220.51

1.3-1

March 16, 1964

# 1.3 MONTHLY

#### CHECKS

- 1. Plenum Filters.

- a. Replace as condition warrants.

- 2. Clock Pulse width (Subject 3.2).

- 3. Clock Variable bias (Subject 3.3).

- 4. Clock Pulse Frequency (Subject 3.2).

- 5. Clean Fan Screens.

B 5220.51 1.4-1

March 16, 1964

# 1.4 QUARTERLY

#### CHECKS

- 1. Over and under voltage sensing.

- a. Verify voltage sensing. (Reference Subject 5.6 of the Power Supply Manual). Monitor the Voltage Regulators output according to Subject 5.5 of the Power Supply Manual. (Use precision voltmeter).

# 1.5 SEMI-ANNUALLY

#### CHECKS

- 1. 10 ms LOAD delay multi for proper setting (Subject 3.4).

- 2. Excessive ripple in all DC supplies. (Refer to Subject 5.6 of the Power Supply Manual).

1.5-1

#### LUBRICATION

#### Fan Lubrication

Lubricate Rotron Muffin fans with Anderol L-826 using special oil injector.

```

Oil Injector . . . . . Pt. No. 11838588

Oil . . . . . . . . Pt. No. 11838596

```

#### PROCEDURE

The exhaust fans are lubricated by inserting the Oil Injector needle through a self-sealing rubber cap located in the center of the motor hub.

Note that on most units a Gold Seal label is mounted over the rubber plug; this series of fans is called the Gold Seal series.

- 1. Fan grill, remove and clean as necessary.

- 2. Remove air from Oil Injector by holding the needle up and pressing on the plunger.

- 3. Place Oil Injector needle at the center of circle marked on the Gold Label (on the O34 series place needle approximately 1/8" from the edge of the rubber cap).

- 4. Position the needle at an angle of approximately 45° to the surface of the label and point it toward the center of the rubber cap.

- 5. Pierce the label and the concealed self-sealing rubber cap located under the label.

- 6. Insert the needle approximately 1/4".

- 7. Depress the plunger of the Oil Injector to allow approximately 1/16" of oil to escape. Rotating the fan will relieve air pressure and allow oil to flow into the oil chamber.

# FIELD ENGINEERING TECHNICAL MANUAL\_

B 5220.51 1.6-1

March 16, 1964

# 1.6 ANNUAL

#### CHECKS

- 1. Wiring and Cables.

- check all wiring visually, paying special attention to voltage regulator area and any wires or cables carrying power.

B 5220.51

2.1-1

March 16, 1964

# **SECTION 2**

# **TROUBLESHOOTING**

# 2.1 TEST SWITCHES AND INDICATORS

#### INTRODUCTION

The Functional Analysis of Central Control test switches and indicators is explained in the D & D Manual, Section 2.

B 5220.51 2.2-1

March 16, 1964

# 2.2 SPECIAL TOOLS

In addition to the normal tools provided for maintenance of the B 5220 Central Control Unit, the following special tools are also provided:

- 1. Diode-stick cutters

- 2. Wire-wrap tools

- 3. Cover-removal tool

- 4. Package handles

# DIODE STICK CUTTING TOOL (P/N 11838109)

The Diode Sticks provided as spares are uncut. The diode stick cutter is a plier-type device which can be used to cut the diode sticks as needed. Care must be taken when using the cutter to keep from breaking the bond between the diodes or resistors and the common bus. The diode-stick tool must not be used for any other purpose.

#### WIRE UNWRAP TOOL (P/N 11838058)

The hand unwrapping tool (see Figure 2.2-1) is used when it is necessary to remove a wire from a pin. The tool has two ends; one end is for wires which are wrapped in a clock-wise direction; the other end is for wires which are wrapped in a counter-clock-wise direction. To use this tool, proceed as follows:

- 1. Determine the direction of wrap and insert the appropriate end of the tool over the pin.

- 2. Rotate the tool until the wire is sufficiently uncoiled so that it can be removed from the pin.

FIGURE 2.2-1 DUAL, RIGHT AND LEFT NO. 2 UNWRAPPING TOOL

#### WIRE WRAP TOOL (P/N 11838042)

The wire-wrap tool is a hand-wrapping tool and is shown in Figure 2.2-2. The tool will wrap a standard field change wire.

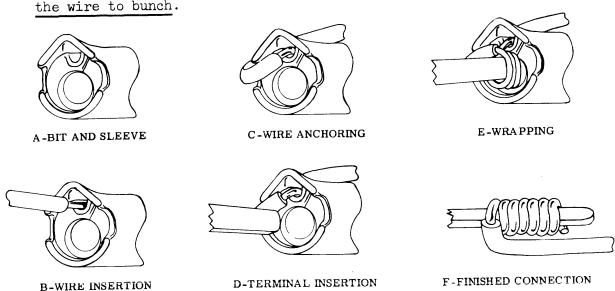

Figure 2.2-3, A through F, shows the steps used to wrap a connection. If a wire was previously wrapped, the portion of the wire which was wrapped cannot be used again.

If the old wire is not long enough to strip off enough insulation to permit another wrap, a new wire must be routed in its place. To wrap a new wire, proceed as follows:

- 1. Remove the insulation from the end of the wire. Approximately 1 1/2" of wire is required for a six-turn connection of 24-gauge wire.

- 2. Place the tool over the wire as shown in Figure 2.2-3B.

- 3. Anchor the wire as shown in Figure 2.2-3C and insert the tool over the pin as shown in Figure 2.2-3D.

- 4. Rotate the tool in a clockwise direction. The wire will wrap around the pin as shown in Figure 2.2-3E and F. Too much pressure will cause the wire to bunch.

FIGURE 2.2-3 WIRE WRAPPING

The following should be used as a guide when installing FCNs, or when making wire wrap changed in the field.

- Number of turns The minimum number of turns (per connection) of bare wire is FIVE, and the maximum number is SEVEN. The maximum number of turns of insulation preceding the bare wire is THREE for any connection.

- 2. <u>Insufficient Insulation</u> Wire insulation shall be no greater than 1/32" from wire wrap connections.

- 3. Wire and Terminal Contact The bare wire and terminal must make contact on all corners following the point at which the origin of the number of turns are counted.

March 16, 1964

- 4. Separation of Turns Turns may have a maximum separation of 1/2 the thickness of wire being used to make the wrapped connection.

- 5. Excessive Tail Wire The wire tail shall be construed as being "that end of bare wire which follows the last wrap." The wire tail shall be parallel to the terminal surface within 1/32".

- 6. Overlapping of Turns This condition is caused when succeeding wraps overlap the ones previously made. If this condition exists, it will be necessary to make a new connection.

- 7. Clearance There shall be at least 1/32" clearance between grid pattern connections, terminals, bare wire or components.

- 8. <u>Height</u> The maximum clearance between the connector block and the first turn of the first connection shall be 1/16".

- 9. Height for Single Wire Wrap The maximum height for a single wire wrap shall be 1/4".

- 10. Height for Two Wire Wraps The maximum height for two wire wrap connections shall be 1/2".

- 11. Unwrapping The wire wrap connection shall be capable of being unwrapped from the wire wrap terminal without breaking. The unwrapping operation shall be done with a standard unwrapping tool only, so as to insure the life of the wire wrap terminal.

- 12. Wire Re-use IF A WIRE WAS PREVIOUSLY WRAPPED, THE PORTION OF THE WIRE WHICH WAS WRAPPED CANNOT BE USED AGAIN. If the old wire is not long enough to strip off enough insulation to permit another wrap, a new wire must be routed in its place. Soldering a wire wrapped connection directly at the wire wrapped terminal shall not be permitted at any time.

- 13. Terminal Re-use Prior to rewrapping, the terminal shall be inspected for plating loss, corrosion or other damage. The evidence of any damage, plating loss or corrosion will in effect cause the wire connection not to maintain the high degree of quality and reliability which is required. The terminal, therefore, must be replaced with a new terminal.

# COVER-REMOVAL TOOL (P/N 80551)

The cover-removal tool is a 3/8" Allen-Set-screw wrench. The short end is cut off to approximately 1/2" and a plastic handle is inserted on the long portion of the wrench.

PACKAGE HANDLES (P/N 77213)

Special non-conduction handles are provided for use in removing packages. These handles must be removed from the package before the gates are closed.

| в 5220.51 | 2.3-1 |

|-----------|-------|

| March 16. | 1964  |

#### 2.3 PRECAUTIONS

Adhere to the following steps to insure equipment safety.

- 1. Do not use a battery-buzzer for continuity checking. The buzzer current exceeds the maximum current rating for diodes and transistors in CC.

- 2. Do not use the first two low scales (X1 or X10) on the Triplet ohmmeter for continuity checking. On these scales, the meter current exceeds the maximum current rating for diodes and transistors in CC.

- 3. Do not remove packages or diode sticks when power is Up.

- 4. Care must be taken when using Scope or Jumper Clip Leads to prevent touching adjacent pins. Use Minigator Clips with insulators or the Wire Wrap Pin Probe Tip (Part No. 11838547).

- 5. Use extreme caution when working on the plug-in side of the panels. Avoid hitting packages when moving the scope.

- 6. Do not attempt to force a TRUE level with -12V.

- 7. A ground jumper may be used to force a FALSE level.

NOTE

Connect clip to the point to be grounded prior to making ground connection.

- 8. Do not pull Cable Plugs with POWER ON at either end of the cable.

- 9. Only soldering irons that have an isolation transformer may be used.

- 10. Scope ground to prevent ground loops and noise interference, use only the ground clip on the scope probe. Attach it to a suitable ground as near as possible to the point being observed.

# 2.4 CLOCK CONTROL LOAD BUTTON

#### CHECKS

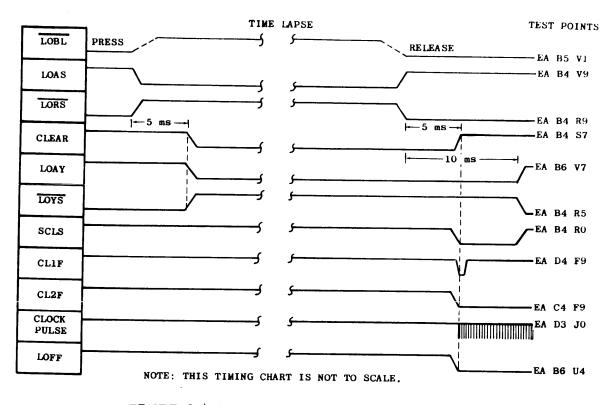

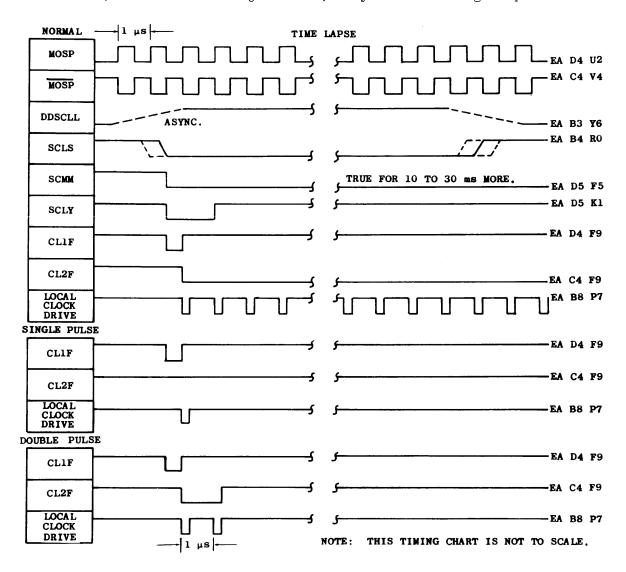

Refer to Figure 2.4-1 (Load Button Timing Chart) to aid in the check out of the LOAD logic.

FIGURE 2.4-1 LOAD BUTTON TIMING CHART

The steps listed below should be taken to check the Clock Control Load Button Logic.

- 1. To check the CLEAR function of the LOAD logic, set a few flip-flops in the CC (CLIF and CL2F must be off). Pressing the LOAD button on the CC Display Panel will clear all flip-flops, releasing it will turn on LOFF and CL2F.

- 2. The Delay Multi LOAY (EA B6 V7), should be checked for proper delay.

- 3. Sync scope (positive) on LOAS (EA B4 V9) and measure the delay from the time LOAS goes false to the time LOAY goes false. Timing should be 10 ms.

- 4. Using the same sync (LOAS), scope SCIS (EA B4 RO) while pressing LOAD button. SCLS will be true for a period equal to the LOAY delay minus the CLEAR relay contacts delay. This time should be about 5 ms.

- 5. The LOAD button cannot be activated if Processor 1 is busy. This can be checked by testing the following two equations.

- 1. + PAlL•PABUSL

- 2. + PBlL•PBBUSL

# NOTE

These equations are taken from page COO6 of the CC Logic Book, IOAS input.

6. Check the 4 KCL inputs to LOFF making sure each interrupt clears it with a clock pulse.

# 2.5 CHECKOUT OF REAL TIME CLOCK

On the CC Display Panel, switch the Clock Mode switch to "NORMAL".

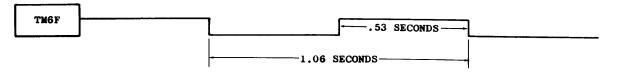

The Real Time Clock should be counting once every 16.6 ms. Scope the true output of TM6F (EA B5 F9). This is the "32 bit" flip-flop and should be going true every 1.06 seconds. See illustration below.

The proper complementing of TM6F will reflect the operation of the entire counter.

If counting seems erratic, switch the Clock Mode switch to "double pulse". Clear the Real Time counter register and pulse the counter with the Start Clock button.

A count may not be obtained with each depression of the Start button because the clock pulse must be ANDED with 60 cycles (TMOY).

| B 5220.51 | 2.6-1 |

|-----------|-------|

| March 16, | 1964  |

# 2.6 PHYSICAL ORIENTATION

#### INTRODUCTION

The Central Control Unit is an integral part of the B 5000 Main Frame. This frame is comprised of Processor, I/O, D & D, Central Control and Memory.

#### GENERAL RACK LAYOUT

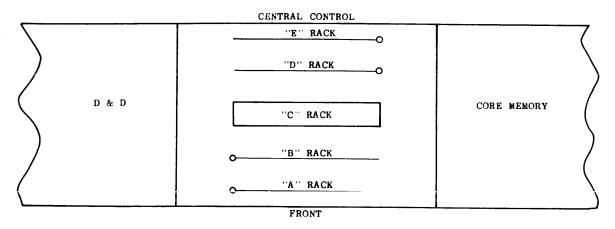

The rack locations are shown in Figure 2.6-1. There are five racks in Central Control.

FIGURE 2.6-1 RACK LOCATIONS

Note that upon removal of the cover, the wiring side of the panel is exposed. The packages are found on the inside of the panel.

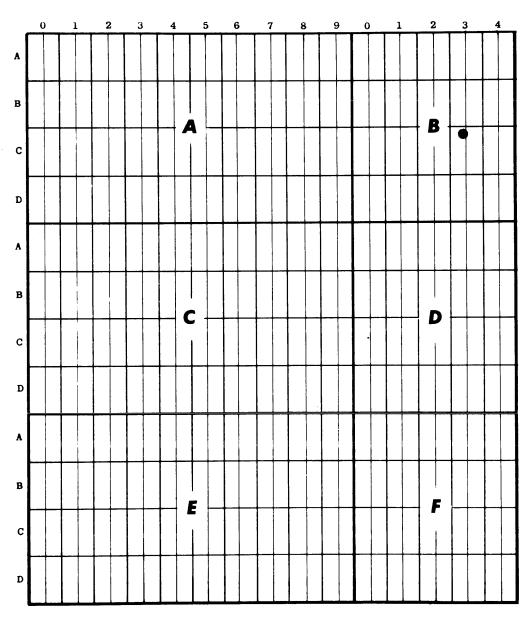

The C rack differs from the other racks and will be explained later. The remaining racks, A, B, D and E are devoted to Central Control Logic. Each of these racks have three frames, which are divided into two panels. Refer to Figure 2.6-2.

The layout of the rack, or gate as it is sometimes referred to, is shown with the orientation numbers used for reference. The numbers across the top of the rack are the column numbers used in referencing the location of packages. The letters in the large circles denote the panel letter. Notice that panels A, C and E are full panels utilizing all 10 columns, while panels B, D and F are half panels utilizing only five columns. Each panel is subdivided into four rows marked A, B, C and D. This subdividing locates a connector block which can hold four flip-flops or 20 diode sticks. The connector block is subdivided into strips of connectors which are designated by two coordinates. Across the top, the columns are marked 0 through 9, while along the side, the rows are lettered A through Y, with G, I, O and Q left out. Therefore the following location would have this meaning:

CONNECTOR BLOCK LOCATION, AND PIN LOCATION WITHIN THE CONNECTOR

AB C3  $D_4$  is located approximately by block dot on Figure 2.6-2.

A = "A" Rack

B = "B" Panel

$C = {}^{"}C^{"}Row$

3 = 3rd Column

D = D Row of Connector Block

4 = Column of Connector Block

FIGURE 2.6-2 PANEL ORIENTATION (WIRING SIDE)

# FIELD ENGINEERING TECHNICAL MANUAL B 5220.51 2.6-3 March 16, 1964

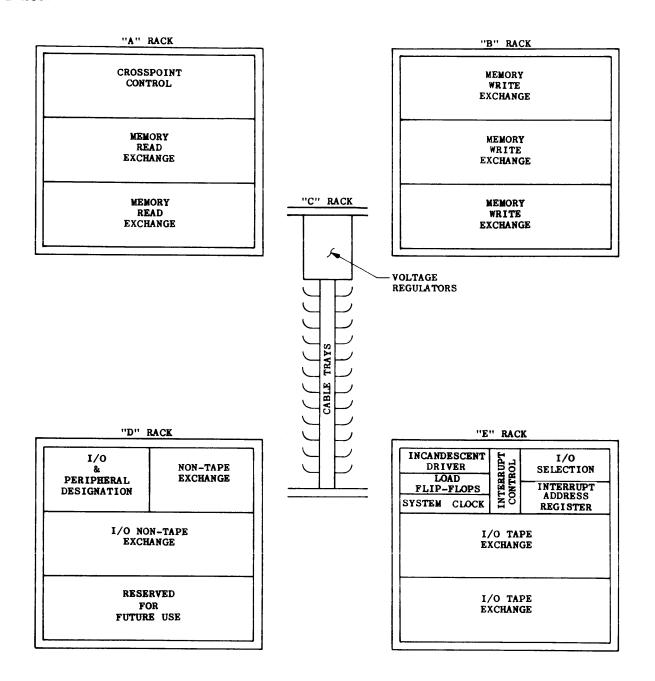

Because of the interaction of the various modules and wiring, the logical gates may not, mechanically, be located near each other. This makes it difficult to localize a certain area on the panels and assign it to a specific group of logics. The frames are fairly well assigned with the assignments shown in Figure 2.6-3.

#### "A" RACK

On the "A" rack, panels A and B contain the crosspoint flip-flops with the associated logic necessary to select the flip-flops.

Panels C, D, E and F contain part of the associated logic for the Memory Read Exchange. This includes the Memory Read Crosspoint Drivers.

#### "B" RACK

All panels of the "B" rack contain the Memory Write Exchange Crosspoint Drivers and the associated logical gating necessary to select them when the crosspoint flip-flops are set.

#### "C" RACK

This rack is a fixed unit within the cabinet for Central Control. The top section of this rack contains the Power Pack, which is a DC voltage regulator for the -1.2V. -4.5V, and the -12V supply to the Central Control and Display and Distribution units. The voltage regulator is described in the B 5000 System Power Supply Manual.

The lower section of this rack contains 12 troughs which are used to convey interconnecting cables from one cabinet to another.

#### "D" RACK

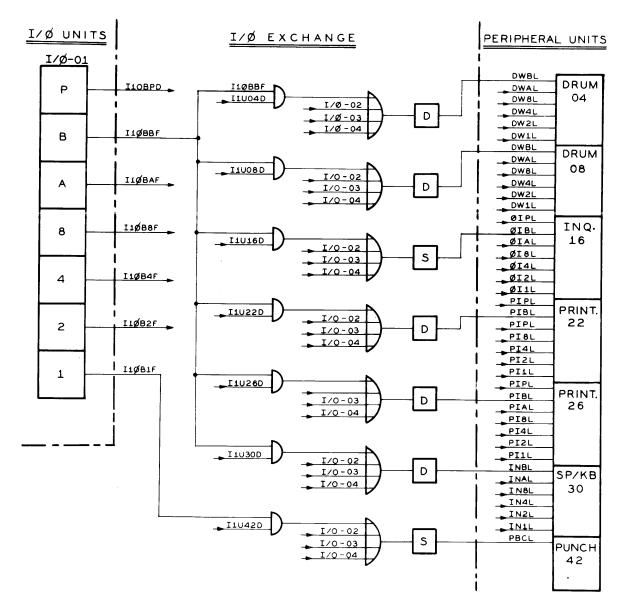

Panel A of the "D" rack contains the I/O and peripheral designate gating for I/O Exchange.

Part of Panel A and all of Panel B contain part of the Non-Tape Control and Information lines logic.

Panels C, D, E and F contain the rest of the logic for Non-Tape Control and Information lines.

#### "E" RACK

Panels A and B of the "E" rack contain the Incandescent Driver packages for the system, the Load Control, System Clock and Clock Control, the Interrupt Control logics, Interrupt Address Register and I/O selection logics.

Panels C, D, E and F contain the logic for Magnetic Tape Control and information lines.

FIGURE 2.6-3 CENTRAL CONTROL RACK LAYOUT

B 5220.51 2.7-1 March 29, 1965

2.7 RIN INDEX

RIN INDEX FOR THE B 5220 CENTRAL CONTROL UNIT, MODEL 1 (78493)

|         | INSTAL.          |                   |                   |                                                                           |

|---------|------------------|-------------------|-------------------|---------------------------------------------------------------------------|

| RIN NO. | TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED | DESCRIPTION                                                               |

| 5005 .  | 2.0              |                   | 102 ⇒ 113         | Improved manner with which the cables are secured.                        |

| 5010    | 2.0              |                   | 102 ⇒ 113         | Installation of adhesive identification labels on each cable connector.   |

| 5012    | 2.0              |                   | 102 ⇒ 113         | Change pulse per cycle rate at which the Real Time Clock is counted.      |

| 5019    | 0.5              |                   | 102 > 113         | Change clock cables between Central Control and Memory.                   |

| 5028    | 0.5              |                   | 102 → 113         | Extends lower limit of the -4.5V regulator.                               |

| 5029    | 0.5              |                   | 102 ⇒ 113         | Installation of cable supports to pre-<br>vent pinching of cables.        |

| 5040    | 0.5              |                   | 102 ⇒ 113         | Correct the termination of P31S and P31S'.                                |

| 5041    | 10.0             |                   | 102 ⇒ 113         | Implements backspace lines for Paper<br>Tape Reader.                      |

| 5043    | 4.0              |                   | 102 > 113         | Removes a portion of the frame to relieve cable stress.                   |

| 5052    | 1.0              |                   | 102 ⇒ 113         | Replace clock cables with standard types.                                 |

| 5072    | 1.5              |                   | 102 ⇒ 113         | "A" Rack Document release and unused wiring removal.                      |

| 507251  | 0.5              | corrects<br>5072  | 102 > 113         | (same as RIN 5072)                                                        |

| 5076    | 0.l<br>per cable |                   | 102⇒ 113          | Key pin support for all yellow and green single key pin cable connectors. |

| 5078    | 1.0              |                   | 102 ⇒ 113         | Change to double driver package to eliminate oscillations.                |

| 5079    | 0.5              |                   | 102 ⇒ 113         | Release of updated documents for Central Control "E" Rack.                |

| RIN NO.            | INSTAL.<br>TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED | DESCRIPTION                                                                                                            |

|--------------------|-----------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|

| 5079 <b>S</b> 1    | 2.5                         | 5079              | 102 ⇒113          | Change Stick cuts to conform with Docu-<br>ments released by RIN 5079.                                                 |

| 5091               | 1.0                         | 5103<br>5106      | 102⇒113           | Provide additional cables for exchanging a B 5000 Processor to a B 5500.                                               |

| 5094               | 4.0                         |                   | 102⇒113           | Plug-in heatsink replacement to prevent the shorting of the collectors in common heatsinks.                            |

| 5094 <b>S</b> 1    | 1.0                         | 5094              | 102>113           | Supply transistors for installation of RIN 5094.                                                                       |

| 5100               | 4.0                         |                   | 102⇒ 113          | Provide a quad connector retaining device to insure proper seating of the connector.                                   |

| 5103<br>·          | 7.0                         | 5041              | 102⇒113           | Installation of new cable connector during re-routing of peripheral signal lines.                                      |

| 5106               | 28.5                        | 5103              | 102⇒113           | Installation of re-routed peripheral ready lines for Interrogate operator, plus change to External Interrupt Priority. |

| 5107               | 1.0                         | 5106              | 102⇒113           | Removal of PRRS termination. These signals are now terminated in the Processor.                                        |

| 5113               | 2.0                         | 5114              | 102⇒113           | Provide a single pulse or double pulse level to the 4µs Memory.                                                        |

| 51 2l <sub>1</sub> | 0.5                         |                   | 102⇒ 113          | Installation of a washer on the crystal pins, of the oscillator, to eliminate possible shorting.                       |

|                    |                             |                   |                   |                                                                                                                        |

|                    |                             |                   |                   |                                                                                                                        |

|                    |                             |                   |                   |                                                                                                                        |

|                    |                             |                   |                   |                                                                                                                        |

March 29, 1**9**65

RIN INDEX FOR THE B 5220 CENTRAL CONTROL UNIT, MODEL 2 (11975323)

| RIN NO.    | INSTAL.<br>TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED | DESCRIPTION                                                                                    |

|------------|-----------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------|

| 5028       | 0.5                         |                   | 114 ⇒ UP          | Extends lower limit of the -4.5V regulator.                                                    |

| 5031       | 4.0                         |                   | 114 ⇒ UP          | Add designate of Disk File for priority resolution and interrupts.                             |

| 5043       | 4.0                         |                   | 114 ⇒ UP          | Removes a portion of the frame to relieve cable stress.                                        |

| 5072       | 1.5                         |                   | 114 <b>⇒</b> UP   | "A" Rack Document release and unused wiring removal.                                           |

| 507281     | 0.5                         | corrects<br>5072  | 114 <b>⇒</b> UP   | (same as RIN 5072)                                                                             |

| 5076       | 0.1<br>per cable            |                   | 114 ⇒ UP          | Key pin support for all yellow and green single key pin cable connectors.                      |

| 5078       | 1.0                         |                   | 114 <b>⇒</b> UP   | Change to double driver package to eliminate oscillations.                                     |

| 5079       | 0.5                         |                   | 114 ⇒ UP          | Release of updated documents for Central                                                       |

| 507981     | 2.5                         | 5079              | 114 ⇒ UP          | Control "E" Rack. Change Stick cuts to conform with Docu- ments released by RIN 5079.          |

| 5082       | 10.0                        |                   | 114 ⇒ UP          | Correct Inquiry signal cable; correct logic to O6FW2L' and I3I250; add missing -4.5V and -12V. |

| 5083       | 1.0                         | 5031<br>5082      | ll¼ ⇒ UP          | Add designate for Disk File for priority resolution and interrupts.                            |

| 5084       | 10.0                        | 5083              | 114 ⇒ UP          | Implements backspace lines for Paper<br>Tape Readers.                                          |

| 5085       | 1.5                         | 5084              | 114 ⇒ UP          | Removal of 16INPL input logic from I3I07D.                                                     |

| 5091       | 1.0                         | 5 <b>0</b> 85     | 114 <b>⇒</b> UP   | Provide additional cables for exchanging a B 5000 Processor to a B 5500.                       |

| <b>l</b> ( | ļ                           |                   |                   |                                                                                                |

| RIN NO.         | INSTAL.<br>TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED | DESCRIPTION                                                                                                            |

|-----------------|-----------------------------|-------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|

| 5094            | 4.0                         |                   | 114 ⇒ UP          | Plug-in heatsink replacement to prevent<br>the shorting of the collectors in common<br>heatsinks.                      |

| 5094 <b>S</b> 1 | 1.0                         | 5094              | 114 ⇒ UP          | Supply transistors for installation of RIN 5094.                                                                       |

| 5100            | 4.0                         |                   | 114 <b>⇒</b> UP   | Provide a quad connector retaining de-<br>vice to insure proper seating of the<br>connector.                           |

| 5102            | 8.5                         | 5085              | 11¼ <b>⇒</b> UP   | Installation of new cable connector during re-routing of peripheral signal lines.                                      |

| 5106            | 28.5                        | 5102              | 11¼ ⇒ UP          | Installation of re-routed peripheral ready lines for Interrogate operator, plus change to External Interrupt Priority. |

| 5107            | 1.0                         | 5106              | 114 ⇒ UP          | Removal of PRRS termination. These signals are now terminated in the Processor.                                        |

| 5113            | 2.0                         | 5114              | 11¼ → UP          | Provide a single pulse or double pulse level to the 4µs Memory.                                                        |

| 5124            | 0.5                         |                   | 114 ≯ UP          | Installation of a washer on the crystal pins, of the oscillator, to eliminate possible shorting.                       |

| 5127            | 0.5                         |                   | 114 ≯ UP          | Correct an erroneous part number callout in Module Locator.                                                            |

|                 |                             |                   |                   |                                                                                                                        |

|                 |                             |                   |                   |                                                                                                                        |

|                 |                             |                   |                   |                                                                                                                        |

|                 |                             |                   |                   |                                                                                                                        |

B 5220.51 3.1-1

March 16, 1964

# SECTION 3

# **ADJUSTMENTS**

# 3.1 INTRODUCTION

This section contains the necessary instructions for making all adjustments within the Central Control unit.

| В | 522 | 0.51 | 3.2-1   |  |

|---|-----|------|---------|--|

|   |     | - /  | <br>0() |  |

March 16, 1964

# 3.2 CLOCK PULSE WIDTH

The following steps should be taken to adjust the Clock Pulse Width:

- 1. With the Clock Mode switch in the "single pulse" position, sync scope (negative) on the leading edge of SCLS, EA B4 RO. Scope the local Clock Driver at EA B8 P7. When the START button is pressed, observe for a single pulse.

- 2. Change the Clock Mode to "double pulse" position. With the same sync and scope conditions as above, press the START button and observe for two pulses 1  $\mu s$  apart.

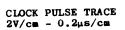

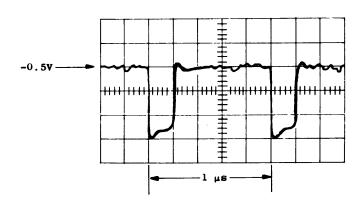

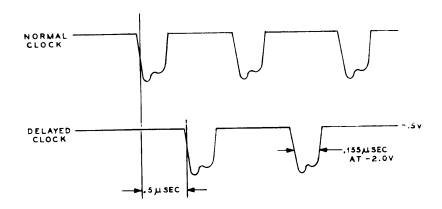

- 3. Check the Master Oscillator for a 1 megacycle square wave by switching the Clock Mode to "normal" and pressing the START button while scoping the output of the Master Oscillator at EA D4 S2. A 1 megacycle pulse train should be present. (Refer to Figures 3.2-1 and 3.2-2).

FIGURE 3.2-1 ONE MEGACYCLE PULSE TRAIN

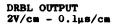

4. Set the pulse width, (at the -2 volt level) to .155 microseconds by adjusting the pot on the DRBLs using Figure 3.2-2.

| SCOPE POINT | POTENTIOMETER<br>LOCATION |

|-------------|---------------------------|

| EA C3 CO    | EA C3 A2                  |

| EA D3 CO    | EA D3 A2                  |

| SCOPE POINT | POTENTIOMETER<br>LOCATION |

|-------------|---------------------------|

| EA C3 RO    | EA C3 N2                  |

| EA D3 RO    | EA D3 N2                  |

FIGURE 3.2-2 DRBL WAVE SHAPE AND ADJUSTMENT TABLE

| B 5220.51  | 3.3-1     |

|------------|-----------|

| M 1 7 ( 70 | <b>(1</b> |

March 16, 1964

#### 3.3 VARIABLE BIAS

The following steps should be taken to adjust the Variable Bias:

- 1. Check the Master Oscillator output for a 1 megacycle square wave.

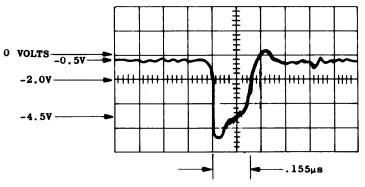

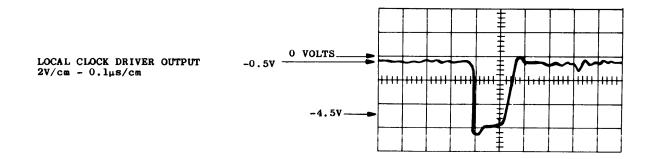

- 2. With the Clock Mode switch in "normal", press the START button and scope the output of the local clock driver, MCLD-EA (Pin EA B8 P7). A 1 megacycle pulse train should be present. (Refer to Figure 3.2-1).

- 3. Set the false level of the clock pulse to .5V by adjusting the variable bias package at EA C8 A7.

- 4. Move the scope probe to the output of the other local clock driver, MCLD-AA (Pin AA B6 P7). Set the false level to -.5V by adjusting the variable bias at AA B7 N2. (Refer to Figure 3.3-1).

FIGURE 3.3-1 LOCAL CLOCK DRIVER WAVE SHAPE

| B 5220.51 | 3.4-1 |

|-----------|-------|

| March 16, | 1964  |

#### 3.4 DELAY MULTI

Figure 3.4-1 shows all pulses concerned with START Button Timing and includes each of the switch positions. If trouble is suspected in this area, Figure 3.4-1 will be of real value, but for DELAY adjustments, only the following steps are necessary.

FIGURE 3.4-1 START BUTTON TIMING CHART

- 1. To adjust Delay Multi LOAY, EA B6 V7, sync scope (positive) on LOAS, EA B4 V9. Measure the delay from the time LOAS goes false to the time LOAY goes false. This should be about 10 ms but is not critical.

- 2. Using the same sync, scope SCLS at EA B4 RO while pressing the LOAD button. SCLS should be true for a period equal to the LOAY delay minus the CLEAR relay contacts delay. This time should be about 5 ms.

# NOTE

Be sure to use the LOAD button to start the checks as LOAY will not be obtained from using the START button.

| B 5220.51 |    | 3.5-1 | _ |

|-----------|----|-------|---|

| September | 1, | 1966  |   |

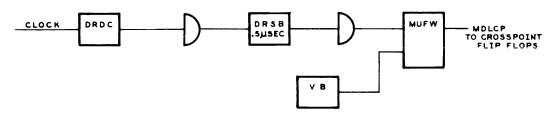

# 3.5 DELAYED CLOCK PULSE

To adjust the delayed clock pulse:

- 1. Place the "A" probe on the normal clock at AAB6P7.

- 2. Place "B" probe on the delayed clock at AAC7J0.

- 3. Sync EXTERNAL-NEGATIVE on the normal clock at AAB6P7.

- 4. Adjust the DRSB (AAC7N2) for .5 usec delay between the leading edges of the normal and the delayed clock. See Figure 3.5-1.

- 5. Adjust the MUFW (AAC7A2) for a delayed clock width of .155 usec at the -2.0 volt level.

- 6. Set the false level to -.5V by adjusting the VB package at (AAC6A7).

FIGURE 3.5-1 DELAYED CLOCK PULSE

Section 7.2 contains a functional description of the delayed clock.

B 5220.51 4.1-1

March 16, 1964

# SECTION 4

# ASSEMBLY AND DISASSEMBLY

# 4.1 VOLTAGE REGULATOR

Refer to Section 4 of the Power Supply Manual for the procedure to disassemble and assemble the Voltage Regulator.

B 5220.51 4.2-1

March 16, 1964

# 4.2 WIRE WRAP PINS

#### REMOVAL

- 1. Remove wires with unwrapping tool.

- 2. If pin is bent, straighten it with long nose pliers.

- 3. Push on pin from the wire side with long nose pliers. As soon as the pin clears the block (package side), grasp the pin with the pliers and pull it out.

- 4. If the pin is broken off flush with the pin block, use a small drift punch or another pin held with the pliers to drive the pin out.

#### REPLACEMENT

- 1. Insert the pin in the block from the package side of the gate. Make sure that the pin is inserted correctly (the contact side of the pin points away from the slot on the side of the pin hole).

- 2. Take the long-nose pliers and pull on the pin from the wire side until the pin is even with adjacent pins. Do not pull it too far or the pin block may be damaged.

NOTE

The M row pins are U shaped and do not extend through to the package side.

| в 5220.51 | 4.3-1 |

|-----------|-------|

| March 16, | 1964  |

# 4.3 PACKAGES

#### INSTALLATION AND REMOVAL

- 1. All parallel plate packages with the exception of the Local Clock Drivers will be fitted with a permanent handle for insertion and extraction.

- 2. Diode and resistor sticks will have a tool provided for insertion and extraction.

#### CAUTION

This tool must be removed before the gate is closed or the package may be damaged.

#### WARNING

Power must be OFF before removing any element.

B 5220.51 5.1-1 September 1, 1966

#### SECTION 5

INSTALLATION

# √ 5.1 INTRODUCTION

The installation and check out of the Central Control Unit will follow the check out of primary power and cabinet regulators as described in the Power Supply Manual, Section 5.

All of the cables connecting to and used within Central Control are listed in Subject 5.2 of this manual.

The inter-gate cables in the latter part of the listing have already been installed, and are listed for reference only.

The cable listing is for a maximum system. However, those cables for units not part of the customer system will not be shipped.

To add new units to a system, refer to Subject 5.5.

<sup>/</sup>Changes or additions since last issue.

March 16, 1964

# 5.2 POWER AND INFORMATION CABLING

#### POWER CABLES

Previously installed cables for power checkout should include those numbered: 25-23, 25-32, 25-41 adn 209.

To complete the power wiring, the following cables should be installed: 25-11, 25-12, 225, 226, 231, 254 and 255.

Refer to the cable list (Table 5.2-1) for location and routing. When completed, check off all of the cables installed up to this time.

#### INFORMATION CABLES

The remaining CC cables are for information and control purposes. Install the cables in the order listed, follow the tray routing indicated and check off each cable as it is installed.

TABLE 5.2-1 INTER-UNIT CABLE LIST

| CABLE | CABLE FUNCTION             | FROM  |           | TO    |              | VIA  |

|-------|----------------------------|-------|-----------|-------|--------------|------|

| NO.   |                            | UNIT  | CONNECTOR | UNIT  | CONNECTOR    | TRAY |

| 1-0A  | MEMORY WRITE, ADD EXCHANGE | СС    | BA AO A7  | MEM-0 | AJ J1 A2     | 3R   |

| 1-0B  | MEMORY WRITE, ADD EXCHANGE | СС    | BA AO N7  | MEM-0 | AJ J1 N2     | 3R   |

| 1-1A  | MEMORY WRITE, ADD EXCHANGE | CC    | BA BO A7  | MEM-1 | AJ J1 A2     | 4R   |

| 1-1B  | MEMORY WRITE, ADD EXCHANGE | CC    | BA BO N7  | MEM-1 | AJ J1 N2     | 4R   |

| 1-2A  | MEMORY WRITE, ADD EXCHANGE | cc    | BA CO A7  | MEM-2 | AJ J1 A2     | 3R   |

| 1-2B  | MEMORY WRITE, ADD EXCHANGE | СС    | BA CO N7  | MEM-2 | AJ J1 N2     | 3R   |

| 1-3A  | MEMORY WRITE, ADD EXCHANGE | cc    | BC AO A7  | MEM-3 | AJ J1 A2     | 8R   |

| 1-3B  | MEMORY WRITE, ADD EXCHANGE | СС    | BC AO N7  | MEM-3 | AJ J1 N2     | 8R   |

| 1-4A  | MEMORY WRITE, ADD EXCHANGE | CC    | BC BO A7  | MEM-4 | AJ J1 A2     | 4R   |

| 1-4B  | MEMORY WRITE, ADD EXCHANGE | CC    | BC BO N7  | MEN-4 | AJ J1 N2     | 4R   |

| 1-5A  | MEMORY WRITE, ADD EXCHANGE | СС    | BC CO A7  | MEM-5 | AJ J1 A2     | 8R   |

| 1-5B  | MEMORY WRITE, ADD EXCHANGE | СС    | BC CO N7  | MEN-5 | AJ J1 N2     | 8R   |

| 1-6A  | MEMORY WRITE, ADD EXCHANGE | СС    | BE AO A7  | MEM-6 | AJ J1 A2     | 5R   |

| 1-6B  | MEMORY WRITE, ADD EXCHANGE | СС    | BE AO N7  | MEM-6 | AJ J1 N2     | 5R   |

| 1-7A  | MEMORY WRITE, ADD EXCHANGE | СС    | BE BO A7  | MEM-7 | AJ J1 A2     | 9R   |

| 1-7B  | MEMORY WRITE, ADD EXCHANGE | cc    | BE BO N7  | MEM-7 | AJ J1 N2     | 9R   |

| 2-0A  | MEMORY READ EXCHANGE       | MEM-0 | AJ K1 A7  | CC    | AC AO A2     | 3F   |

| 2-0B  | MEMORY READ EXCHANGE       | MEM-0 | AJ K1 N7  | CC    | AC AO N2     | 3F   |

| 2-1A  | MEMORY READ EXCHANGE       | MEM-1 | AJ K1 A7  | CC    | AC BO A2     | 6F   |

| 2-1B  | MEMORY READ EXCHANGE       | MEM-1 | AJ K1 N7  | CC    | AC BO N2     | 6F   |

| 2-2A  | MEMORY READ EXCHANGE       | MEM-2 | AJ K1 A7  | СС    | AC CO A2     | 5R   |

| 2-2B  | MEMORY READ EXCHANGE       | MEM-2 | AJ K1 N7  | CC    | AC CO N2     | 5R   |

| 2-3A  | MEMORY READ EXCHANGE       | MEM-3 | AJ K1 A7  | CC    | AC DO A2     | 7F   |

| 2-3B  | MEMORY READ EXCHANGE       | MEM-3 | AJ K1 N7  | CC    | AC DO N2     | 7F   |

| 2-4A  | MEMORY READ EXCHANGE       | MEM-4 | AJ K1 A7  | СС    | AE AO A2     | 4R   |

| •     |                            |       |           | Conti | nued on next | page |

Table 5.2-1 Power Cables

|              |                               | <u> </u> | FROM      |       | то        | VIA        |

|--------------|-------------------------------|----------|-----------|-------|-----------|------------|

| CABLE<br>NO. | FUNCTION                      | UNIT     | CONNECTOR | UNIT  | CONNECTOR | TRAY       |

| 2-4B         | MEMORY READ EXCHANGE          | MEM-4    | AJ K1 N7  | CC    | AE AO N2  | 4R         |

| 2-5A         | MEMORY READ EXCHANGE          | MEM-5    | AJ K1 A7  | cc    | AE BO A2  | 8F         |

| 2-5B         | MEMORY READ EXCHANGE          | MEM-5    | AJ K1 N7  | cc    | AE BO N2  | 8F         |

| 2-6A         | MEMORY READ EXCHANGE          | MEM-6    | AJ K1 A7  | cc    | AE CO A2  | 6F         |

| 2-6B         | MEMORY READ EXCHANGE          | MEM-6    | AJ Kl N7  | cc    | AE CO N2  | 6F         |

| 2-7A         | MEMORY READ EXCHANGE          | MEM-7    | AJ K1 A7  | cc    | AE DO A2  | 9F         |

| 2-7B         | MEMORY READ EXCHANGE          | MEM-7    | AJ Kl N7  | cc    | AE DO N2  | 9F         |

| 3-1          | I/O INPUT LINES               | cc       | EC AO A2  | 1/0-1 | AC DO A7  | 3F         |

| 3-2          | I/O INPUT LINES               | cc       | EC BO A2  | 1/0-2 | AC DO A7  | 3R         |

| 3-3          | I/O INPUT LINES               | cc       | EC CO A2  | 1/0-3 | AC DO A7  | 5R         |

| 3-4          | I/O INPUT LINES               | cc       | EC DO A2  | I/0-4 | AC DO A7  | 5F         |

| 4-1A         | I/O MEMORY READ EXCHANGE      | cc       | AC CO A7  | I/0-1 | AE AO N2  | 7R         |

| 4-1B         | I/O MEMORY READ EXCHANGE      | cc       | AC CO N7  | 1/0-1 | AE BO N2  | 7R         |

| 4-2A         | I/O MEMORY READ EXCHANGE      | cc       | AC DO A7  | 1/0-2 | AE AO N2  | 7R         |

| 4-2B         | I/O MEMORY READ EXCHANGE      | cc       | AC DO N7  | 1/0-2 | AE BO N2  | 7R         |

| 4-3A         | I/O MEMORY READ EXCHANGE      | CC       | AE CO A7  | 1/0-3 | AE AO N2  | 10R        |

| 4-3B         | I/O MEMORY READ EXCHANGE      | cc       | AE CO N7  | 1/0-3 | AE BO N2  | 10R        |

| 4-4A         | I/O MEMORY READ EXCHANGE      | CC       | AE DO A7  | I/0-4 | AE AO N2  | 10F        |

| 4-4B         | I/O MEMORY READ EXCHANGE      | cc       | AE DO N7  | 1/0-4 | AE BO N2  | 10F        |

| 5-1A         | I/O MEMORY WRITE EXCHANGE     | 1/0-1    | AE CO N7  | cc    | BA CO A2  | 5R         |

| 5-1B         | I/O MEMORY WRITE EXCHANGE     | 1/0-1    | AE DO A7  | cc    | BA CO N2  | 5R         |

| 5-2A         | I/O MEMORY WRITE EXCHANGE     | 1/0-2    | AE CO N7  | cc    | BC AO A2  | 5R         |

| 5-2B         | I/O MEMORY WRITE EXCHANGE     | 1/0-2    | AE DO A7  | cc    | BC AO N2  | 5R         |

| 5-3A         | I/O MEMORY WRITE EXCHANGE     | 1/0-3    | AE CO N7  | СС    | BC CO A2  | 7R         |

| 5-3B         | I/O MEMORY WRITE EXCHANGE     | 1/0-3    | AE DO A7  | СС    | BC CO N2  | 7R         |

| 5-4A         | I/O MEMORY WRITE EXCHANGE     | 1/0-4    | AE CO N7  | СС    | BC CO A2  | 10R        |

| 5-4B         | I/O MEMORY WRITE EXCHANGE     | 1/0-4    | AE DO A7  | СС    | BE CO N2  | 10R        |

| 6-1          | I/O OUTPUT LINES              | 1/0-1    | AC BO A7  | СС    | EC AO N2  | 3 <b>F</b> |

| 6-2          | I/O OUTPUT LINES              | 1/0-2    | AC BO A7  | cc    | EC BO N2  | 3F         |

| 6-3          | I/O OUTPUT LINES              | 1/0-3    | AC BO A7  | СС    | EC CO N2  | 5R         |

| 6-4          | I/O OUTPUT LINES              | 1/0-4    | AC BO A7  | СС    | EC DO N2  | 5F         |

| 7-A          | INTERRUPT & CONTROL           | СС       | EA CO A7  | PA    | DA CO N2  | 8F         |

| 7-B          | INTERRUPT & CONTROL           | СС       | EA CO N7  | PB    | DA CO N2  | 2F         |

| 8-AA         | Pk MEMORY WRITE EXCHANGE      | PA       | DE CO N7  | CC    | BA AO A2  | 7F         |

| 8-AB         | Pk MEMORY WRITE EXCHANGE      | PA       | DC BO A7  | СС    | BA AO N2  | 5F         |

| 8-BA         | Pk MEMORY WRITE EXCHANGE      | PB       | DE CO N7  | CC    | BE AO A2  | 8 <b>F</b> |

| 8-BB         | Pk MEMORY WRITE EXCHANGE      | PB       | DC BO A7  | СС    | BE AO N2  | 5F         |

| 9-AA         | Pk MEMORY READ EXCHANGE       | СС       | AC AO A7  | PA    | EE DO A2  | 7F         |

| 9-AB         | Pk MEMORY READ EXCHANGE       | СС       | AC AO N7  | PA    | EE CO N2  | 5F         |

| 9-BA         | Pk MEMORY READ EXCHANGE       | СС       | AE AO A7  | PB    | EE DO A2  | 8F         |

| 9 <b>-BB</b> | Pk MEMORY READ EXCHANGE       | cc       | AE AO N7  | PB    | EE CO N2  | 5F         |

| 10 <b>-A</b> | INTERRUPT & CONTROL           | PA       | EA DO A7  | СС    | EA CO A2  | 7F         |

| 10-B         | INTERRUPT & CONTROL           | PB       | EA DO A7  | СС    | EA CO N2  | 3 <b>F</b> |

| 11           | PAPER TAPE - RDR/PUNCH SIGNAL | СС       | DC AO N7  | D & D | DD J8     | 5 <b>F</b> |

| 12-1         | MAGNETIC TAPE - TTU - A       | cc       | EE AO A2  | D & D | DE L1     | 7F         |

| 12-2         | MAGNETIC TAPE - TTU - B       | CC       | EC DO N7  | D & D | DE L2     | 8R         |

| 12-3         | MAGNETIC TAPE - TTU - C       | CC       | EE AO N2  | D & D | DE L3     | 7F         |

| 12-4         | MAGNETIC TAPE - TTU - D       | CC       | EE AO N7  | D & D | DE L4     | 8R         |

Continued on next page

B 5220.51

5.2-3

March 16, 1964

## (Table 5.2-1 Continued)

| CABLE    | FUNCTION                            |                                         | FROM      |                | ТО           |             |  |

|----------|-------------------------------------|-----------------------------------------|-----------|----------------|--------------|-------------|--|

| NO.      |                                     |                                         | CONNECTOR | UNIT           | CONNECTOR    | TRAY        |  |

| 12-5     | MAGNETIC TAPE - TTU - E             | СС                                      | EE BO A2  | D & D          | DE L5        | 7 <b>F</b>  |  |

| 12-6     | MAGNETIC TAPE - TTU - F             | СС                                      | EE BO A7  | D & D          | DE L6        | 9 <b>F</b>  |  |

| 12-7     | MAGNETIC TAPE - TTU - H             | СС                                      | EE BO N2  | D & D          | DE L7        | 9 <b>F</b>  |  |

| 12-8     | MAGNETIC TAPE - TTU - J             | СС                                      | EE BO N7  | D & D          | DE L8        | 9 <b>F</b>  |  |

| 12-9     | MAGNETIC TAPE - TTU - K             | СС                                      | EE CO A2  | D & D          | DE M1        | 11F         |  |

| 12-10    | MAGNETIC TAPE - TTU - L             | СС                                      | EE CO A7  | D & D          | DE M2        | 10 <b>F</b> |  |

| 12-11    | MAGNETIC TAPE - TTU - M             | СС                                      | EE CO N2  | D & D          | DE M3        | 11F         |  |

| 12-12    | MAGNETIC TAPE - TTU - N             | CC                                      | EE CO N7  | D & D          | DE M4        | 10F         |  |

| 12-13    | MAGNETIC TAPE - TTU - P             | СС                                      | EE DO A2  | D & D          | DE M5        | 11F         |  |

| 12-14    | MAGNETIC TAPE - TTU - R             | СС                                      | EE DO A7  | D & D          | DE M6        | 10 <b>F</b> |  |

| 12-15    | MAGNETIC TAPE - TTU - S             | CC                                      | EE DO N2  | D & D          | DE M7        | 11F         |  |

| 12-16    | MAGNETIC TAPE - TTU - T             | СС                                      | EE DO N7  | D & D          | DE M8        | 10 <b>F</b> |  |

| 13       | PRINTER KEYBOARD SIGNAL             | СС                                      | DC AO A2  | D & D          | DD J1        | 3F          |  |

| 15-1     | 100/500 CPM PUNCH SIGNAL            | СС                                      | DC CO A2  | D & D          | DD K1        | 5 <b>F</b>  |  |

| 17-1     | #1 200/800 CPM READER SIGNAL        | СС                                      | DC CO N2  | D & D          | DD K3        | 5F          |  |

| 17-2     | #2 200/800 CPM READER SIGNAL        | СС                                      | DC CO N7  | D & D          | DD K4        | 5F          |  |

| 19       | INQUIRY SIGNAL                      | CC                                      | DC AO A7  | D & D          | DD J2        | 4F          |  |

| 20-1     | #1 PRINTER SIGNAL                   | СС                                      | DC DO A2  | D & D          | DD K5        | 6F          |  |

| 20-2     | #2 PRINTER SIGNAL                   | СС                                      | DC DO A2  | D & D          | DD K7        | 6F          |  |

| 21       | PAPER TAPE PUNCH SIGNAL             | СС                                      | DC BO A7  | D & D          | DD J6        | 4F          |  |

| 22       | PAPER TAPE READ SIGNAL              | СС                                      | DC DO A7  | D & D          | DD K2        | 8 <b>F</b>  |  |

| 23-1     | #1 DRUM SIGNAL                      | СС                                      | DC BO A2  | D & D          | DD J5        | 4F          |  |

| 23-2     | #2 DRUM SIGNAL                      | СС                                      | DC BO N2  | D & D          | DD <b>J7</b> | 4F          |  |

| 25-11    | (#00 AWG) GROUND                    | D & D                                   | DA J1 03  | СС             | CA K1 07     | 2R          |  |

| 25-12    | (#00 AWG) GROUND                    | D & D                                   | DA J1 03  | СС             | CU K1 07     | 2R          |  |

| 25-23    | (#10 AWG) +20V                      | D & D                                   | DB L4 05  | СС             | CS K1 12     | 1 <b>F</b>  |  |

| 25-32    | (#12 AWG) +50V                      | D & D                                   | DB L1 05  | CC             | CT N2 04     | 1F          |  |

| 25-41    | (#12 AWG) -33V                      | D & D                                   | DB J2 05  | СС             | CT N2 01     | 1R          |  |

| 37       | CC INDICATOR INPUT                  | CC                                      | EA AO A2  | D & D          | AH J1        | 2F          |  |

| 38       | CC INDICATOR INPUT                  | СС                                      | AA AO A2  | D & D          | AH Kl        | 2F          |  |

| 39       | CC INDICATOR INPUT & MANUAL CONTROL | CC                                      | AA AO N2  | D & D          | AH Ll        | 2F          |  |

| 40       | CC MANUAL CONTROL                   | D & D                                   | AH M1     | СС             | EA AO N2     | 2F          |  |

| 41       | CC MANUAL CONTROL                   | D & D                                   | AH N1     | СС             | AA BO A2     | 2F          |  |

| 42       | CC MISCELLANEOUS                    | D & D                                   | AH Pl     | СС             | EA BO A2     | 2F          |  |

| 140      | POWER GATE "A" - D & D              | CC                                      | CS 07     | D & D          | AE AO A7     | 1R          |  |

| 170      | CLOCK CABLE I/O-1                   | СС                                      | EA D2 Y6  | 1/0-1          | AA C7 Y4     | 2R          |  |

|          |                                     |                                         |           |                | AC B8 L4     |             |  |

|          |                                     |                                         |           |                | AE C6 Y9     |             |  |

| 171      | CLOCK CABLE I/O-2                   | СС                                      | EA D2 Y7  | 1/0-2          | AA C7 Y4     | 2R          |  |

|          |                                     |                                         |           | † <del>-</del> | AC BS L4     |             |  |

|          |                                     | † · · · · · · · · · · · · · · · · · · · |           | 1              | AE C6 Y9     |             |  |

| 172      | CLOCK CABLE I/O-3                   | CC                                      | EA D2 Y8  | 1/0-3          | AA C7 Y4     | 2R          |  |

|          |                                     | <u> </u>                                |           |                | AC B8 L4     |             |  |

|          |                                     | 1                                       |           | <b> </b>       | AE C6 Y9     | 1           |  |

| 173      | CLOCK CABLE 1/0-4                   | СС                                      | EA D2 Y9  | 1/0-4          | AA C7 Y4     | 2R          |  |

| <u> </u> |                                     | †                                       | t         | <b>†</b>       | AC BS L4     | 1           |  |

|          |                                     | 1                                       | <b>T</b>  | <b>T</b>       | AE C6 Y9     | <b>T</b>    |  |

| 175      | PA CLOCK CABLE "A" RACK             | СС                                      | EA C2 L6  | PA             | AA C5 L9     | 2R          |  |

| L        |                                     |                                         |           | Conti          | nued on next | 20.00       |  |

# (Table 5.2-1 Continued)

| CABLE    |                                       |         | FROM       | -     | то         | VIA        |

|----------|---------------------------------------|---------|------------|-------|------------|------------|

| NO.      | FUNCTION                              | UNIT    | CONNECTOR  | UNIT  | CONNECTOR  | TRAY       |

| 175      | PA CLOCK CABLE "A" RACK               | CC      | EA C2 L6   | PA    | AC C5 L9   | 2R         |

| -        |                                       |         |            |       | AE C5 L9   |            |

| 176      | PA CLOCK CABLE "B" RACK               | CC      | EA C2 L7   | PA    | BA C6 L9   | 2R         |

|          |                                       |         |            |       | BC C6 L9   |            |

|          | ,                                     |         |            |       | BE C5 L9   |            |

| 177      | PA CLOCK CABLE "D" RACK               | CC      | EA C2 L8   | PA    | DA C6 L9   | 2R         |

|          |                                       |         |            |       | DC C6 L9   |            |

|          |                                       |         |            |       | DE C6 L9   |            |

| 178      | PA CLOCK CABLE "E" RACK               | CC      | EA C2 L9   | PA    | EA B6 Y9   | 2R         |

|          |                                       |         |            |       | EE B6 Y9   |            |

| 179      | PA CLOCK CABLE "J" RACK               | СС      | EA C2 L5   |       | JC C6 L9   |            |

|          |                                       |         |            |       | JE C6 L9   |            |

| 180      | PB CLOCK CABLE "A" RACK               | CC      | EA C2 Y6   | PB    | AA C5 L9   | 2R         |

|          |                                       |         |            |       | AC C5 L9   |            |

|          |                                       |         |            |       | AE C5 L9   |            |

| 181      | PB CLOCK CABLE "B" RACK               | CC      | EA C2 Y7   | PB    | BA C6 L9   | 2R         |

|          |                                       |         |            |       | BC C6 L9   |            |

|          |                                       |         |            |       | BE C5 L9   |            |

| 182      | PB CLOCK CABLE "D" RACK               | CC      | EA C2 Y8   | PB    | DA C6 L9   | 2R         |

|          |                                       |         |            |       | DC C6 L9   |            |

| <b> </b> |                                       |         |            |       | DE C6 L9   |            |

| 183      | PB CLOCK CABLE "E" RACK               | CC      | EA C2 Y9   | PB    | EA B6 Y9   | 2R         |

|          |                                       |         | <u> </u>   |       | EE B6 Y9   |            |

| 184      | PB CLOCK CABLE "J" RACK               | СС      | EA C2 Y5   | PB    | JC C6 L9   | 2R         |

|          |                                       |         |            |       | JE C6 L9   |            |

| 187      | MO CLOCK CABLE .                      | CC      | EA D2 L2   | MEM-0 | AJ J1 Y9   | 2F         |

| 188      | M1 CLOCK CABLE                        | CC      | EA D2 L3   | MEM-1 | AJ J1 ¥9   | 2F         |

| 189      | M2 CLOCK CABLE                        | CC      | EA D2 L4   | MEM-2 | AJ J1 Y9   | NT         |

| 190      | M3 CLOCK CABLE                        | СС      | EA D2 L5   | MEM-3 | AJ J1 ¥9   | NT         |

| 191      | M4 CLOCK CABLE                        | СС      | EA D2 L6   | MEM-4 | AJ J1 Y9   | 2F         |

| 192      | M5 CLOCK CABLE                        | CC      | EA D2 L7   | MEM-5 | AJ J1 Y9   | 2F         |

| 193      | M6 CLOCK CABLE                        | CC      | EA D2 L8   | MEM-6 | AJ J1 Y9   | 2F         |

| 194      | M7 CLOCK CABLE                        | CC      | EA D2 L9   | MEM-7 | AJ J1 Y9   | 2F         |

| 209      | (#0 AWG) -19V                         | PS      | DA M4 B2   | СС    | CA J1 01   | 2R         |

| 225      | (#14 AWG) 115VAC (FAN CIRCUIT)        | D & D   | FAK1 06/07 | СС    | FAK1 06/07 | NT         |

| 226      | (#14 AWG) 115VAC (FAN CIRCUIT)        | СС      | FAK1 06/07 | M-SS1 | FAK1 06/07 | NT         |

| 231      | (#12 AWG) 115VAC (CONVENIENCE CIRCUIT | ) D & D | DFP1 03/04 | cc    | HBL1 01/02 | NT         |

|          |                                       |         |            |       | HBL2 01/02 |            |

| 254      | POWER CONTROL                         | D & D   | DC L1      | СС    | DC CO A7   | 9 <b>F</b> |

| :265     | POWER CONTROL                         | D & D   | DC L1      | СС    | EC AO N7   | 9 <b>F</b> |

B 5220.51

5.2-5

March 16, 1964

Table 5.2-2 Inter-Gate Cable List

| CABLE      | DVDVOTV OV                       |      | FROM        |      | то          | VIA        |

|------------|----------------------------------|------|-------------|------|-------------|------------|

| NO.        | FUNCTION                         | UNIT | CONNECTOR   | UNIT | CONNECTOR   | TRAY       |

| 24-25      | HEAT & EXCESS CURRENT SENSE      | CC   | AA A1 YO    | CC   | VOLT. REG.  | 1R         |

| 70         | CC INTER-GATE                    | cc   | EA BO A7    | CC   | AA BO N2    | 3R         |

| 71-A       | CC INTER-GATE                    | СС   | AA CO A7    | CC   | BA DO A2    | NT         |

| 71-B       | CC INTER-GATE                    | CC   | AA CO N7    | CC   | BC DO A2    | NT         |

| 71-C       | CC INTER-GATE                    | cc   | AA DO A7    | CC   | BE BO A2    | NT         |

| 72         | CC INTER-GATE                    | cc   | AE BO A7    | cc   | AA CO N2    | NT         |

| <b>7</b> 3 | CC INTER-GATE                    | cc   | DA DO N2    | CC   | EA AO N7    | NT         |

| 75-1       | CC INTER-GATE                    | СС   | EC AO A7    | CC   | DA AO A2    | NT         |

| 75-2       | CC INTER-GATE                    | CC   | EC BO A7    | CC   | DA BO A2    | NT         |

| 75-3       | CC INTER-GATE                    | CC   | EC CO A7    | CC   | DA CO A2    | NT         |

| 75-4       | CC INTER-GATE                    | cc   | EC DO A7    | CC   | DA DO A2    | NT         |

| 128        | CC POWER GATE "D"                | cc   | DA BO N7    | CC   | CS 14       | 1 <b>F</b> |

| 129        | CC POWER GATE "D"                | cc   | DC BU N7    | CC   | CS 15       | 1 <b>F</b> |

| 131        | CC POWER GATE "A"                | CC   | AA BO N7    | CC   | CS 01       | 1R         |

| 132        | CC POWER GATE "A"                | cc   | AC BO N7    | CC   | CS 02       | 1R         |

| 133        | CC POWER GATE "A"                | CC   | AE BO N7    | CC   | CS 03       | 1R         |

| 134        | CC POWER GATE "B"                | cc   | BA DO A7    | CC   | CS 04       | 1R         |

| 135        | CC POWER GATE "B"                | cc   | BC DO A7    | CC   | CS U5       | 1R         |

| 136        | CC POWER GATE "B"                | cc   | BE CO A7    | CC   | CS 06       | 1R         |

| 137        | CC POWER GATE "E"                | CC   | EA BO N7    | CC   | CS 11       | 1 <b>F</b> |

| 138        | CC POWER GATE "E"                | CC   | EC BO N7    | CC   | CS 12       | 1F         |

| 139        | CC POWER GATE "E"                | cc   | EE AO A7    | CC   | CS 13       | 1 <b>F</b> |

| 195        | CC CLOCK CABLE "E" RACK          | cc   | EA D2 Y5    | cc   | EA B7 Y9    | NT         |

| 196        | CC CLOCK CABLE "A" RACK          | cc   | EA D2 Y4    | CC   | AA B5 Y9    | 2F         |

| 197-9      | CC "A" GATE - GROUND             | cc   | GATE "A"    | cc   | CA K1 01    | NT         |

| 197-10     | CC "B" GATE - GROUND             | СС   | GATE "B"    | CC   | CA K1 02    | NT         |

| 197-11     | CC "D" GATE - GROUND             | СС   | GATE "D"    | cc   | CU K1 02    | NT         |

| 197-12     | CC "E" GATE - GROUND             | СС   | GATE "E"    | CC   | CU K1 01    | NT         |

| 235        | (#14 AWG) 115VAC - REGULATOR FAN | СС   | FA K1 01/12 | cc   | CR J1 03/04 | NT         |

## 5.3 POWER AND SYSTEM CLOCK CHECKS

#### INTRODUCTION

It is assumed that all system power and information cables have been installed, the voltage regulators in all units and voltage control and sensing has been checked out according to instructions in the Power Supply Manual, Section 5.

#### CHECKS

The following steps should be taken before applying power to the system.

- 1. Check all units for broken wires, loose connections, etc.

- 2. See that all packages, plugs, cards etc., are firmly plugged in.

- 3. Put the DC Lockout switch in the LOCKOUT position and bring up power.

- 4. Assuming system power holds normally, throw the DC LOCKOUT switch down, while observing the voltage sensing panel in D & D for any indication of power failure.

- 5. If there are any indications of DC failure, refer to Section 3 of the Power Supply Manual for a recheck of voltage regulators and overcurrent sensing adjustments.

- 6. Turn the DC LOCKOUT switch again to the "LOCKOUT" position. Check the -12V, -4.5V, -1.2V and +20V at the CC regulators to verify that these voltages are removed.

- 7. Bring up DC power again (4 and 5), and check for proper set and reset of all flip-flops on the CC display panel in the D & D unit.

- 8. Check the System Clock as explained in Section 3 of this manual.

B 5220.51 5.4-1 September 1, 1966

## 15.4 DUMMY PLUGS (GROUND CLOSURES)

#### INTRODUCTION

Certain points must be grounded by dummy plugs in Central Control to prevent floating levels when a unit is not present.

#### NOTE

Dummy plugs for I/O 4 and PB are not required starting with systems shipped after June 1966.

The following dummy plugs must be installed if the unit is not present.

| PLUG | UNIT  | LEVEL GROUNDED           | LOCATION |

|------|-------|--------------------------|----------|

| Х    | PA    | MAIL, DO2S, DO7S         | ACAOA7   |

| х    | PA    | BUSL, CMIL               | EACOA2   |

| х    | PB    | MAIL, DO2S, DO7S         | AEAOA7   |

| х    | PB    | BUSL, CMIL               | EACON2   |

| х    | I/O 2 | MANF, RO7S, RO2S         | ACD0A7   |

| х    | 1/0 3 | MANF, RO7S, RO2S         | AECOA7   |

| х    | I/O 4 | MANF, RO7S, RO2S         | AEDOA7   |

| Y    | 1/0 2 | D16, Z46, <del>Z46</del> | ECBON2   |

| Y    | 1/0 3 | D16, Z46, <del>Z46</del> | ECCON2   |

| Y    | I/O 4 | D16, Z46, <del>Z46</del> | ECDON2   |

| Z    | PB    | 101F                     | EACON7   |

√Changes or additions since last issue.

| в 5220.51 |   | 5.5-1  |

|-----------|---|--------|

| September | 1 | , 1966 |

### 5.5 ADDING UNITS TO THE SYSTEM

#### INTRODUCTION

To reduce the number of unused pluggables sent to the field, unused pluggables are unloaded from Central Controls shipped after June 1966. The Central Control is loaded, however, for the BASIC SYSTEM configuration as defined below.

#### BASIC SYSTEM

#### The BASIC SYSTEM consists of:

1 Data Processor "A"

1 Central Control

1 Display and Distribution

l Disk File Control

1 Operators Console

1 Power Supply

3 I/O Control Units

5 Core Memories

8 Tape Transports

1 Data Communication Control 2 Card Readers

1 Card Punch

2 Printers

#### MODIFICATION KITS

Table 5.5-1 shows which modification kits must be installed when new units are added to the B5500 system. Each modification kit requires a set of instructions for adding pluggables and cables and for removing ground closures. These instructions are covered under MODIFICATION INSTRUCTIONS and are listed by kit designations (B\*, C, etc.).

TABLE 5.5-1

| UNIT     |    | DP -B | 1/0-4 |

|----------|----|-------|-------|

|          |    | B*    | M *   |

| M EM - 5 | F* | C.    | G     |

| MEM-6    | Н* | D     | J     |

| M EM - 7 | K* | E     | L     |

#### NOTE

Those modification kits which have an asterisk (\*) must be installed before those modification kits without an asterisk. For example, if DP-B is being added to a system which already has a MEM-5, then modification kit B\* and C must be installed. Modification kit F\* was installed previously with MEM-5. If I/O-4 is being added to a system, then those modification kits in Table 5.5-2 must also be installed.

Table 5.5-2 shows which modification kits must be installed when new peripheral units are added.

**TABLE 5.5-2**

| UNIT    |      | 1/0-4 |

|---------|------|-------|

|         |      | M *   |

| TTU-K   | AA*  | AK    |

| TTU-L   | AB*  | AL    |

| TTU-M   | -AC* | AM    |

| TTU-N   | AD*  | AN    |

| TTU-P   | AE*  | AP    |

| TTU-R   | AF*  | AR    |

| TTU-S   | AG*  | AS    |

| TTU-T   | AH*  | AT    |

| DFC #2  | N*   | P     |

| PTR #1  | R*   | S     |

| PTR #2  | T*   | Ü     |

| PTP #1  | V*   | W     |

| PTP #2  | X*   | Y     |

| DRUM #1 | A*   | Q     |

| DRUM #2 | I*   | Z     |

B 5220.51 5.5-3 September 1, 1966

### MODIFICATION INSTRUCTIONS

Instructions for Modification Kit B\*

To add DP-B, install the following pluggables:

| ASSEMBLY #   | LOCATION             | ASSEMBLY #                              | LOCATION             | ASSEMBLY #   | LOCATION             | ASSEMBLY #   | LOCATION  |

|--------------|----------------------|-----------------------------------------|----------------------|--------------|----------------------|--------------|-----------|

| 1178 4147    | AE A2 N2             | 1180 1883-29                            | AA D5 L2*            | 1182 8985-29 | AE A6 Y7             | 1182 8985-29 | AE B7 L9  |

| ***          | AE A4 N7             | .,                                      | AA D5 L5*            | 1.           | AE A6 Y8             | 11           | AF Al YO  |

| **           | AE A5 N2             |                                         | AA D5 L8*            | **           | AE A6 Y9             | 11           | AF Al Yl  |

| **           | AE B2 A2             | -1                                      | AA D5 Y2*            |              | AE A7 YO             | **           | AF Al Y2  |

| **           | AE B4 A7             |                                         | AA D5 Y5*            | (1)          | AE A7 Y1             | .,           | AF Al Y3  |

| 11           | AE B5 A2             | 11                                      | AA D5 Y8*            | **           | AE A7 Y2             | ,,           | AF Al Y4  |

| **           | AF AO N2             | ••                                      | AA D6 L1*            | ••           | AE A7 Y3             | *1           | AF Al Y5  |

| *1           | AF AO N7             |                                         | AA D6 L4*            | **           | AE A7 Y4             | **           | AF Al Y6  |

| **           | AF BO A2             | 11                                      | AA D6 Y1*            | *1           | AE A7 Y5             | **           | AF Al Y7  |

| **           | AF BO A7             | 11                                      | AA D6 Y4*            | **           | AE A7 Y6             | **           | AF Al Y8  |

|              |                      |                                         |                      | **           | AE A7 Y7             | 11           | AF A1 Y9  |

| 1180 1883-04 | AA C4 Y2             | 1115 7377                               | AB AO N7             | **           | AE A7 Y8             |              | AF A2 Y0  |

|              | AE A5 L6             | .,                                      | AB A4 N2             | 11           | AE A7 Y9             | **           | AF A2 Y1  |

| .,           | AE A5 L7             | 11                                      | AB BO N7             | N            | AE B2 L7             | ,,           | AF A2 Y2  |

| **           | AE A8 L1             |                                         | AB CO N7             | 19           | AE B2 L8             |              | AF A2 Y3  |

|              |                      | .,                                      | AB DO N7             | 14           | AE B2 L9             | "            | AF A2 Y4  |

| 1180 1883-16 | AA C3 L2             |                                         |                      | 1.7          | AE B3 L0             |              | AF A2 Y5  |

| **           | AA C3 L3             | 1193 3462                               | AE AI Y9             | 11           | AE B3 L1             | "            | AF A2 Y6  |

| **           | AA C3 L4             | **                                      | AE A4 Y4             | **           | AE B3 1.2            | **           | AF A2 Y7  |

| **           | AA C3 L5             | ,,                                      | AE A5 L5             | **           | AE B3 L3             | **           | AF A2 Y8  |

|              | AA C3 Y6             | 11                                      | AE A9 Y9             | 0            | AE B3 L4             | **           | AF A2 Y9  |

| **           | AA C3 Y7             | **                                      | AE B1 1.9            | **           | AE BO LO             | "            | AF A3 YO  |

| 11           | AA C3 Y8             |                                         | AE B4 L4             | ш            | AF B3 16             |              | AF A3 Y1  |

| **           | AA C3 Y9             | 11                                      | AE B9 L9             | 11           | AE B5 L5             | ,,           | AF A3 Y2  |

| **           | AB AO Y4             |                                         |                      |              | AE B5 L6             | 11           | AF A3 Y3  |

| **           |                      | 1182 8985-29                            | AE A2 Y7             | **           | AE B5 L7             | **           | AF A3 Y4  |

| **           | AB BO Y4             | **                                      | AE A2 Y8             | +1           | AE B5 L8             | ••           | AF B1 L0  |

| **           | AB CO Y4             | *1                                      | AE A2 Y9             | 11           | AE B5 L9             | 11           | AF B1 L1  |

| 11           | AB DO Y4             | **                                      | AE A3 YO             | 11           | AE B6 L0             | **           | AF B1 L2  |

|              |                      | **                                      | AE A3 Y1             | **           | AE B6 L1             | ***          | AF B1 L3  |

| 1180 1883-17 | AA C3 L6             | • • • • • • • • • • • • • • • • • • • • | AE A3 Y2             | 17           | AE B6 L2             | 11           | AF B1 L4  |

| "            | AA C3 L7             | 11                                      | AE A3 Y3             | , H          | AE B6 L3             | 11           | AF Bl L5  |

| **           | AA C3 L8             | **                                      | AE A3 Y4             | 11           | AE B6 L4             | 11           | AF Bl L6  |

| .,           | AA C3 L9             | 11                                      | AE A3 Y5             | **           | AE B6 L5             | .0           | AF B1 L7  |

| ,,           | AA C3 Y2             | **                                      | AE A3 Y6             | **           | AE B6 L6             | **           | AF Bl L8  |

| *1           | AA C3 Y3             | **                                      | AE A5 Y5             | ***          | AE B6 L7             | ***          | AF B1 L9  |