# Burroughs B 5281

CENTRAL PROCESSOR

TECHNICAL MANUAL

PROPERTY OF AND TO BE RETURNED TO

# Burroughs

**B 5000 DATA PROCESSING SYSTEM**PRINTED IN U.S.A. 2-16-65 B 5281.51

# ✓ CHANGES OR ADDITIONS

On "Revised" pages, the check mark ( $\checkmark$ ) shown to the left of items or subject titles indicates changes or additions since last issue.

в 5281.51

February 16, 1965

#### TABLE OF CONTENTS

| SUBJECT          | TITLE                         | DATE         |       |

|------------------|-------------------------------|--------------|-------|

| 1                | PREVENTIVE MAINTENANCE        |              |       |

| 1.1              | Daily                         | February 16, | 7065  |

| 1.2              | Weekly                        |              |       |

| 1.3              | Monthly                       | February 16, |       |

| 1.4              |                               | February 16, |       |

|                  | Quarterly                     | February 16, |       |

| 1.5              | Semiannually                  | February 16, | 1965  |

| 2                | TROUBLESHOOTING               |              |       |

| 2.1              | Test Routines                 | February 16, | 1965  |

| 2.2              | Test Switches and Indicators  | February 16, |       |

| 2.3              | Special Tools                 | February 16, |       |

| 2.4              | RIN Index                     | February 16, |       |

| 3                | ADJUSTMENTS                   |              |       |

| 3.1              | Variable Bias                 | TI-1- 1/     | ٦٥/٢  |

| J•±              | variable blas                 | February 16, | 1965  |

| 4                | ASSEMBLY AND DISASSEMBLY      |              |       |

| 4.1              | Regulator                     | February 16, | 1965  |

| 4.2              | Wire Wrap Pins                | February 16, | 1965  |

| 4.3              | Pins In Winchester Plug       | February 16, |       |

| 4.4              | Packages                      | February 16, |       |

|                  | 1                             | ,            | _, _, |

| 5                | INSTALLATION                  |              |       |

| 5.1              | Cabling Processor A           | February 16, | 1965  |

| 5.2              | Cabling Processor B           | February 16, |       |

| 6                | CIRCUIT ANALYSIS              | •            |       |

| 7                | FUNCTIONAL DESCRIPTION        |              |       |

|                  | WORD MODE OPERATORS           |              |       |

| 7.1              | Single Length Add (ADLL)      | E-b 76       | ٦٥٤٢  |

| I • ±            | Single Length Cubtreet (CDLI) | February 16, |       |

| 7.2              | Single Length Subtract (SULL) | February 16, |       |

|                  | Single Length Divide (DV1L)   | February 16, |       |

| 7.3              | Single Length Multiply (MUlL) | February 16, |       |

| 7.4              | Integer Divide (DV3L)         | February 16, |       |

| 7.5              | Remainder Divide (DV4L)       | February 16, | 1965  |

| 7.6              | Double Length Add (AD2L)      |              |       |

|                  | Double Length Subtract (SU2L) | February 16, | 1965  |

| 7.7              | Double Length Divide (DV2L)   | February 16, | 1965  |

| 7.8              | Double Length Multiply (MU2L) | February 16, | 1965  |

| 7.9              | Logical "AND (LOAL)           | February 16, |       |

| 7.10             | Logical "OR" (LOOL)           | February 16, |       |

| 7.11             | Logical Equivalence (LOEL)    | February 16, |       |

| 7.12             | Logical Negate (LONL)         | February 16, |       |

| 7.13             | B=A (BEQL)                    | repluary 10, | 1705  |

| · • • >          | $B \ge A  (BEGL)$             |              |       |

|                  |                               |              |       |

|                  | B > A (BGAL)                  |              |       |

|                  | $B \leq A  (BLEL)$            |              |       |

|                  | B < A (BIAL)                  |              |       |

| Printed in U.S.A | B ₹ A (BNEL)                  | February 16, | 1965  |

| zimiou m U.S.A   | •                             |              |       |

# TABLE OF CONTENTS (Continued)

| SUBJECT      | TITLE                                                                 | DATE        |         |

|--------------|-----------------------------------------------------------------------|-------------|---------|

| 7 7          | Common Edulat Romal (CERT)                                            |             |         |

| 7.14         | Compare Field Equal (CFEL) Compare Field Low (CFLL)                   | February 16 | 1965    |

| 7.15         | Syll. Branch Fwd. Cond. (BFCL)                                        | rebluary 10 | , 1,00  |

| ( • ± )      | Syll. Branch Bkwd. Cond. (BBCL)                                       |             |         |

|              | Word Branch Fwd. Cond. (JFCL)                                         |             |         |

|              | Word Branch Bkwd. Cond. (JBCL)                                        | February 16 | , 1965  |

| 7.16         | Syll. Branch Fwd. Uncond. (BFUL)                                      | -           |         |

|              | Syll. Branch Bkwd. Uncond. (BBUL)                                     |             |         |

|              | Word Branch Fwd. Uncond. (JFUL)                                       |             |         |

|              | Word Branch Bkwd. Uncond. (JBUL)                                      |             |         |

| 7.17         | Branch Return (RJPL)                                                  | February 16 | , 1965  |

| 7.18         | Store Dest. (BSDL)                                                    |             | . 30/7  |

|              | Store Non Dest. (BSNL)                                                | February 16 | , 1965  |

| 7.19         | Integer Store Dest. (ISDL)                                            |             |         |

|              | Integer Store Non Dest. (ISNL)                                        |             |         |

|              | Cond. Integer Store Dest. (CSDL) Cond. Integer Store Non Dest. (CSNL) | February 16 | 1065    |

| 7.20         | Dial A (DIAL)                                                         | rebluary in | J, 1707 |

| 1.20         | Dial B (DIBL)                                                         | February 16 | 5. 1965 |

| 7.21         | Transfer bits (TRFL)                                                  | February 16 |         |

| 7.22         | Reset Flag Bit (RFBL)                                                 | 1071 1111 1 | ., _,-, |

| , •          | Set Flag Bit (SFBL)                                                   | February 16 | 5, 1965 |

| 7.23         | Test Flag Bit (TFBL)                                                  | February 16 |         |

| 7.24         | Reset Sign Bit (MSPL)                                                 | -           |         |

|              | Set Sign Bit (MSNL)                                                   |             |         |

|              | Change Sign Bit (CSSL)                                                | February 16 | 5, 1965 |

| 7.25         | Mark Stack (MSOL)                                                     | February 16 |         |

| 7.26         | Enter Character Mode (ECML)                                           | February 16 | , 1965  |

| 7.27         | Return Normal (RNML)                                                  | E - 1 7.4   | מ מסער  |

| 7 00         | Return Special (RSPL)                                                 | February 16 |         |

| 7.28         | Exchange (EXCL) Duplicate (DUPL)                                      | February 16 |         |

| 7.29<br>7.30 | Delete Top of Stack (DELL)                                            | February 16 |         |

| 7.31         | Stack Search for Flag (SSFL)                                          | February 16 |         |

| 7.32         | Load (LODL)                                                           | February 10 |         |

| 7.33         | Index (INDL)                                                          | February 10 | 5, 1965 |

| 7.34         | Construct Operand Call (MDAL)                                         | •           |         |

|              | Construct Descriptor Call (MDUL)                                      | February 1  | 5, 1965 |

| 7.35         | Set Variant (VARL)                                                    | February 1  | 5, 1965 |

| 7.36         | No Op (NOPL)                                                          | February 1  |         |

| 7.37         | Variable Field Isolate (VFIL)                                         | February 1  | 5, 1965 |

| 7.38         | F & S Reg. Set/Store (FXSL)                                           | February 1  |         |

| 7.39         | List Link Look Up (LLLL)                                              | February 1  | 5, 1965 |

| 7.40         | Inter. Peripheral Status (IPSL)                                       | D-b 7       | 4 3064  |

| 7 17         | Inter. I/O Channel (TIOL)                                             | repruary 1  | 5, 1905 |

| 7.41         | "F" Field To Core Field (FCXL)                                        |             |         |

|              | "F" Field To "F" Field (FFXL)<br>Core Field to "C" Field (CCXL)       |             |         |

|              | Core Field to "F" Field (CFXL)                                        | February 1  | 5. 1965 |

|              | Sole Field to F Field (orkh)                                          | 10014419 1  | -, -,-, |

# TABLE OF CONTENTS (Continued)

| SUBJECT                                                                              | TITLE                                                                                                                                                             | D                                            | ATE                                           |                                                              |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|--------------------------------------------------------------|

| 7.42                                                                                 | Branch Fwd. Non Dest. (ZFNL) Branch Bkwd. Non Dest. (ZBNL) Branch Fwd. Dest. (ZFDL) Branch Bkwd. Dest. (ZBDL)                                                     | February                                     | 16,                                           | 1965                                                         |

|                                                                                      | CHARACTER MODE OPERATORS                                                                                                                                          |                                              |                                               |                                                              |

| 7.43<br>7.44<br>7.45<br>7.46                                                         | Begin Loop (BELL)                                                                                                                                                 | February                                     | 16,                                           | 1965                                                         |

| 7.47<br>7.48<br>7.49<br>7.50                                                         | Compare Less (SLTL) Compare Not Equal (SNEL) End Loop (ENLL) Exit Character Mode (RECL) In Line Exit Character Mode (ILEL) Field Add (FADL) Field Subtract (FSUL) | February<br>February                         | 16,<br>16,                                    | 1965<br>1965                                                 |

| 7.51<br>7.52<br>7.53                                                                 | Field Add Aux. (FAXL) Field Subtract Aux. (FSXL) Increase Tally (INTL) Input Convert (ICOL) Jump Forward Conditional (CFJL)                                       | February<br>February                         | 16,<br>16,                                    | 1965<br>1965                                                 |

| 7.54                                                                                 | Jump Forward Unconditional (FWJL)Jump Out of Loop (JOLL)                                                                                                          |                                              |                                               |                                                              |

| 7.55                                                                                 | Jump Out of Loop Conditional (CJOL)Jump Reverse Conditional (CRJL) Jump Reverse Unconditional (REJL)                                                              | _                                            |                                               |                                                              |

| 7.56<br>7.57<br>7.58<br>7.59<br>7.60<br>7.61<br>7.62<br>7.63<br>7.64<br>7.65<br>7.66 | Output Convert (OCOL)                                                                                                                                             | February February February February February | 16,<br>16,<br>16,<br>16,<br>16,<br>16,<br>16, | 1965<br>1965<br>1965<br>1965<br>1965<br>1965<br>1965<br>1965 |

| 7.67<br>7.68                                                                         | Skip Forward Destination (FSDL)Skip Forward Source (FSSL)                                                                                                         | February                                     | 16,                                           | 1965                                                         |

|                                                                                      | Skip Reverse Source (RSSL)                                                                                                                                        | February                                     | 16,                                           | 1965                                                         |

# TABLE OF CONTENTS (Continued)

| SUBJECT                                                       | TITLE                                                                                                                                                                                                  | DA                                                             | TE                              |                                              |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------|----------------------------------------------|

| 7.69 7.70 7.71 7.72 7.73 7.74 7.75 7.76                       | Skip Reverse Destination (RSDL)                                                                                                                                                                        | February February February February February                   | 16,<br>16,<br>16,<br>16,        | 1965<br>1965<br>1965<br>1965<br>1965         |

| 7.77<br>7.78<br>7.79<br>7.80<br>7.81<br>7.82<br>7.83<br>7.84  | Test For Not Equal (TNEL)                                                                                                                                                                              | February February February February February February February | 16,<br>16,<br>16,<br>16,<br>16, | 1965<br>1965<br>1965<br>1965<br>1965<br>1965 |

|                                                               | CONTROL STATE & MISCELLANEOUS                                                                                                                                                                          |                                                                |                                 |                                              |

| 7.85<br>7.86<br>7.87                                          | Communicate (COML)                                                                                                                                                                                     | February                                                       | 16,                             | 1965                                         |

| 7.88<br>7.89<br>7.90<br>7.91                                  | Descriptor Call Syllable (DCSL) Exit (REWL)                                                                                                                                                            | February                                                       | 16,                             | 1965                                         |

| 7.92                                                          | Initiate P2 (PTOL)Initiate P1 (INIL) Initiate Load                                                                                                                                                     | February                                                       | 16,                             | 1965                                         |

| 7.93<br>7.94<br>7.95<br>7.96<br>7.97<br>7.98<br>7.99<br>7.100 | Initiate P2 Initiate For Test (IFTL) Interrogate Interrupt (IINL) I/O Release (IORL) Literal Syllable (LTSL) Program Release (PREL) Read Timer (RDTL) Store For Interrupt (SFIL) Store For Test (SFTL) | February February February February February February February | 16,<br>16,<br>16,<br>16,<br>16, | 1965<br>1965<br>1965<br>1965<br>1965<br>1965 |

# FIELD ENGINEERING TECHNICAL MANUAL —

B 5281.51 v February 16, 1965

#### LIST OF ILLUSTRATIONS

| FIGURE                  | TITLE                                                                         | PAGE                    |

|-------------------------|-------------------------------------------------------------------------------|-------------------------|

| 2.3-1<br>2.3-2<br>2.3-3 | Dual, Right and Left Hand, Unwrapping Tool<br>Wire Wrap Tool<br>Wire Wrapping | 2.3-1<br>2.3-2<br>2.3-2 |

| 7.5-1                   | Exponent Add Shift Paths                                                      | 7.5-2                   |

|                         |                                                                               |                         |

|                         | LIST OF TABLES                                                                |                         |

| TABLE                   | TITLE                                                                         | PAGE                    |

| 5.1-1<br>5.2 <b>-</b> 1 | Installation Cabling - Processor A Installation Cabling - Processor B         | 5.1-1<br>5.2-1          |

B 5281.51 1.1-1 February 16, 1965

#### SECTION 1

#### PREVENTIVE MAINTENANCE

#### 1.1 DAILY

- 1. Run selected Test Routines or MTR if available. The selection would be based on:

- a. Possible troubles encountered during operation or P.M.

- b. Running all Test Routines available in rotation as soon as reasonable.

B 5281.51 1.2-1 February 16, 1965

#### 1.2 WEEKLY

1. Check that each fan is operating.

# FIELD ENGINEERING TECHNICAL MANUAL-

B 5281.51 1.3-1 February 16, 1965

## 1.3 MONTHLY

- 1. Check Variable Bias Level. Refer to Subject 3.1.

- 2. Inspect (and replace, if necessary) air filters.

- 3. Check clock width and frequency. Refer to Central Control Technical Manual, Subject 3.2.

# FIELD ENGINEERING TECHNICAL MANUAL—

B 5281.51 1.4-1 February 16, 1965

# 1.4 QUARTERLY

- 1. Clean fan screens

- 2. Check regulator output -12V, -1.2V, -4.5V according to Subject 5.6 of the Power Supply Manual.

# FIELD ENGINEERING TECHNICAL MANUAL -

B 5281.51 1.5-1 February 16, 1965

### 1.5 SEMIANNUALLY

Lubricate Rotron Muffin fans with Anderol L-826 using special oil injector.

| Oil | Injector | Part No. | 11838588 |

|-----|----------|----------|----------|

| Oil |          | Part No. | 11838596 |

#### PROCEDURE

The exhaust fans are lubricated by inserting the Oil Injector needle through a self-sealing rubber cap located in the center of the motor hub.

Note that on most units a Gold Seal label is mounted over the rubber plug; this series of fans is called the Gold Seal series.

- 1. Remove and clean the fan grill as necessary.

- 2. Remove air from Oil Injector by holding the needle up and pressing on the plunger.

- 3. Place Oil Injector needle at the center of circle marked on the Gold Label (on the 034 series place needle approximately 1/8" from the edge of the rubber cap).

- 4. Position the needle at an angle of approximately 45° to the surface of the label and point it toward the center of the rubber cap.

- 5. Pierce the label and the concealed self-sealing rubber cap located under the label.

- 6. Insert the needle approximately 1/4".

- 7. Depress the plunger of the Oil Injector to allow approximately 1/16" of oil to escape. Rotating the fan will relieve air pressure and allow oil to flow into the oil chamber.

B 5281.51 2.1-1 February 16, 1965

#### SECTION 2

#### **TROUBLESHOOTING**

## 2.1 TEST ROUTINES

#### INTRODUCTION

The following is a list of test routines for the B 5500 Data Processing System. For a detail description of each test, refer to Test Routine Manual (11985942).

| TR 5203 TR 5204 TR 5205 TR 5206 TR 52207 TR 5221 TR 5222 TR 5230 TR 5331 TR 53332 TR 53334 TR 53336 TR 53340 TR 55556 TR 55556 TR 55558 TR 55558 TR 55560 TR 5901 TR 5902 TR 5903 TR 9995 | Compare Operators Test Bit Operators Test Relative Address Test Logical Operators Test Integer Stores Test Core Memory Test Drum Memory Test Character Mode Test Arithmetic Operators Test Secl/Fetch Test Sub-Level Test Varf Lodl Store Test I/O Test Magnetic Tape Unit Test S.P.O. Keyboard Test Magnetic Tape Compatibility Test Interaction Test Paper Tape Reader Test Paper Tape Punch Test Data Com Control Sub-System Test Chaining Routine Card Lister Routine I/O Utility Routine |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TR 9995                                                                                                                                                                                   | Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TR 9996                                                                                                                                                                                   | Sub-Routine Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TR 9997                                                                                                                                                                                   | Mantissa Adder Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TR 9998                                                                                                                                                                                   | Control State And Interrupt Test                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>A-</b> 11173549 <b>-</b>                                                                                                                                                               | A Speed Up Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A-11159258-                                                                                                                                                                               | E Disc File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                           | .1169901 Disc Test Routine Part 1                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SW 1                                                                                                                                                                                      | 1169919 Disc Test Routine Part 2                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SW 1                                                                                                                                                                                      | 1169927 Disc Test Routine Part 3                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SW A-111734                                                                                                                                                                               | 26-B Marginal Tape Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

B 5281.51 2.2-1 February 16, 1965

# 2.2 TEST SWITCHES AND INDICATORS

A description of the Test Switches and Indicators will be found in the D&D Manual, Subject 2.2.

| В 5281.51   | 2.3-1  |

|-------------|--------|

| February 16 | , 1965 |

#### 2.3 SPECIAL TOOLS

In addition to the normal tools provided for maintenance of the B 5000 system, the following special tools are also provided:

- 1. Diode-stick cutters.

- 2. Wire wrapping tools.

- 3. Cable-connector-pin insertion and removal tools.

- 4. Cover-removal tool.

- 5. Package handles.

#### DIODE STICK CUTTING TOOL (P/N 11838109)

The Diode Sticks provided as spares are uncut. The diode stick cutter is a plier-like device which can be used to cut the diode sticks as needed. Care must be taken when using the cutter to keep from breaking the bond between the diodes or resistors and the common bus. The diode stick tool must not be used for any other purpose.

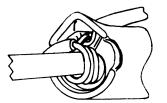

#### WIRE UNWRAPPING TOOL (P/N 11838058)

The hand unwrapping tool (see Figure 2.3-1) is used when it is necessary to remove a wire from a pin. The tool has two ends; one end is for wires which are wrapped in a clockwise direction; the other end is for wires which are wrapped in a counter-clockwise direction. To use this tool, proceed as follows:

- 1. Determine the direction of wrap and insert the appropriate end of the tool over the pin.

- 2. Rotate the tool until the wire is sufficiently uncoiled so that it can be removed from the pin.

FIGURE 2.3-1 DUAL, RIGHT AND LEFT HAND, UNWRAPPING TOOL

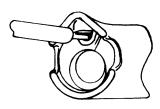

WIRE WRAPPING TOOL (P/N 11838042)

The wire wrapping tool is a hand-wrapping tool and is shown in Figure 2.3-2. The tool will wrap a standard field change wire.

FIGURE 2.3-2 WIRE WRAPPING TOOL

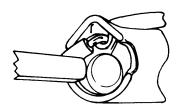

Figure 2.3-3, A through F, shows the steps used to wrap a connection. If a wire was previously wrapped, the portion of the wire which was wrapped cannot be used again. If the old wire is not long enough to strip off enough insulation to permit another wrap, a new wire must be routed in its place. To wrap a new wire proceed as follows:

- 1. Remove the insulation from the end of the wire. Approximately 1-1/2" of wire is required for a six-turn connection of  $2\mu$ -gauge wire.

- 2. Place the tool over the wire as shown in Figure 2.3-3B.

- 3. Anchor the wire as shown in Figure 2.3-3C and insert the tool over the pin as shown in Figure 2.3-3D.

- 4. Rotate the tool in a clockwise direction. The wire will wrap around the pin as shown in Figure 2.3-3E and F. Too much pressure will cause the wire to bunch.

A-BIT AND SLEEVE

C-WIRE ANCHORING

E-WRA PPING

**B-WIRE INSERTION**

**D-TERMINAL INSERTION**

F-FINISHED CONNECTION

FIGURE 2.3-3 WIRE WRAPPING

B 5281.51 2.3-3

February 16, 1965

CABLE-CONNECTOR PIN INSERTION TOOL (P/N 11838075

Refer to Subject 4.3 of this manual for a description of how to use this tool.

CABLE-CONNECTOR PIN REMOVAL TOOL (P/N 11838067)

Refer to Subject 4.3 of this manual for a description of how to use this tool.

COVER REMOVAL TOOL (P/N 80551)

The Cover Removal tool is a 3/8" Allen-set-screw wrench. The short end is cut off to approximately 1/2" and a plastic handle is inserted on the long portion of the wrench.

PACKAGE HANDLES (P/N 77213)

For those packages or sticks which are not provided with handles special non-conducting handles are available. These handles must be removed from the package before the gates are closed.

B 5281.51 2.4-1 February 16, 1965

# 2.4 RIN INDEX

RIN INDEX FOR THE B 5281 PROCESSOR UNIT (78494)

| RIN NO. | INSTAL.<br>TIME IN<br>HOURS | PRE-<br>REQUISITE | UNITS<br>EFFECTED | DESCRIPTION                                                                                  |

|---------|-----------------------------|-------------------|-------------------|----------------------------------------------------------------------------------------------|

| 5004    | 2.0                         |                   | 102 → 147         | Improves manner in which cables are secured.                                                 |

| 5024    | 1.0                         |                   | 102 > 147         | Replaces end panel washers with proper size.                                                 |

| 5028    | 0.5                         |                   | 102 ⇒ 159         | Extends lower limit of the -4.5V regulator.                                                  |

| 5043    | 4.0                         |                   | 102 → 147         | Removes a portion of the frame to relieve cable stress.                                      |

| 50111   | 0.5                         |                   | 102 → 147         | Adds missing ground wire at location EEBlYO                                                  |

| 5047    | 4.0                         |                   | 102 ⇒ 147         | Changes JOOZD1 input logic to function for word branch operators.                            |

| 5051    | 4.0                         |                   | 102 > 159         | Make stick cut changes, making hard-<br>ware agree with documents.                           |

| 5052    | 1.0                         |                   | 102 > 147         | Replace clock cables with standard types.                                                    |

| 5076    | 0.1<br>per cable            |                   | 102 > 147         | Key pin support for all yellow and green single key pin cable connectors.                    |

| 5078    | 1.0                         |                   | 102 ⇒ UP          | Change to double driver package to eliminate oscillations.                                   |

| 5094    | 4.0                         |                   | 102 ⇒ UP          | Plug-in heatsink replacement to prevent the shorting of the collectors in common heatsinks.  |

| 509481  | 1.0                         |                   | 102 ⇒ UP          | Supply transistors for installation of RIN 5094.                                             |

| 5100    | 4.0                         |                   | 102 ⇒ UP          | Provide a quad connector retaining de-<br>vice to insure proper seating of the<br>connector. |

| 5110    | 2.5                         |                   | 102 ⇒ UP          | "Z" level corrections for "D" Rack.                                                          |

| 5111 3.0 102 $\Rightarrow$ UP "Z" level corrections for "E" Ra 5112 0.5 102 $\Rightarrow$ UP "Z" level corrections for "J" Ra 5117 0.5 102 $\Rightarrow$ UP Release a revised Equation Book. 5119 0.8 102 $\Rightarrow$ UP Removes extra termination of E04 | QUISITE EFFECTED | TIME IN PRE-<br>HOURS REQUISITE | RIN NO. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|---------|

| 5117 0.5 102 ⇒ UP Release a revised Equation Book.                                                                                                                                                                                                          | 102 ⇒ UP         | 3.0                             | 5111    |

|                                                                                                                                                                                                                                                             | 102 ⇒ UP         | 0.5                             | 5112    |

| 5119 0.8 102 > UP Removes extra termination of EO4                                                                                                                                                                                                          | 102 ⇒ UP         | 0.5                             | 5117    |

|                                                                                                                                                                                                                                                             | 102 ⇒ UP         | 0.8                             | 5119    |

|                                                                                                                                                                                                                                                             |                  |                                 |         |

B 5281.51 3.1-1 February 16, 1965

#### SECTION 3

#### **ADJUSTMENTS**

#### 3.1 VARIABLE BIAS

Set the false level of the clock pulse to -0.5V by adjusting the variable bias packages. See chart below for locations:

| 4 |     |      |     |

|---|-----|------|-----|

| A | AC7 | CC7  | EC7 |

|   | A2  | A2   | A2  |

| В | AC8 | CC8  | EC7 |

| P | A2  | A2   | A2  |

|   | CC8 | EC8  |     |

| J | A2  | A2   |     |

|   | AC8 | CC8  | EC8 |

|   | A2  | A2   | A2  |

| E | AB8 | E 88 |     |

|   | N2  | N2   |     |

| ке: | rerend               | ce: | DA   | Page | ; 5 |

|-----|----------------------|-----|------|------|-----|

| В   | Rack<br>Rack<br>Rack | 65. | 96.8 | 36.0 |     |

| D   | Rack<br>Rack         | 65. | 96.8 | 39.0 |     |

NOTE

Verify that clock width has been properly adjusted prior to making the above adjustment. See Central Control Manual, Subject 3.2.

The above checks can be made at one point on each Clock Driver. Put scope on the following pins to see both clock width and Variable Bias level. At this point, Variable Bias level should be -0.6V.

| A Rack               | B Rack               | J Rack               | D Rack               | E Rack               |

|----------------------|----------------------|----------------------|----------------------|----------------------|

| AA C6 B7<br>AC C6 B7 | BA C7 B7<br>BC C7 B7 | JC C7 B7<br>JE C7 B7 | DA C7 B7<br>DC C7 B7 | EA B7 P7<br>EE B7 P7 |

| AE C6 B7             | BE C6 B7             |                      | DE C7 B7             | ,                    |

# FIELD ENGINEERING TECHNICAL MANUAL -

B 5281.51 4.1-1 February 16, 1965

## SECTION 4

# ASSEMBLY AND DISASSEMBLY

# 4.1 REGULATOR

See Section 4 of the Power Supply Manual.

B 5281.51 4.2-1 February 16, 1965

#### 4.2 WIRE WRAPPED PINS

#### REMOVAL

- 1. Remove wires with unwrapping tool.

- 2. If pin is bent, straighten it with long nose pliers.

- 3. Push on pin from the wire side with long nose pliers. As soon as the pin clears the block (package side), grasp the pin with the pliers and pull it out.

- 4. If the pin is broken off flush with the pin block, use a small drift punch or another pin held with pliers to drive the pin out.

#### REPLACEMENT

- 1. Insert the pin in the block from the package side of the gate. Make sure that the pin is inserted correctly (the contact side of the pin points away from the slot on the side of the pin hole).

- 2. Take the long-nose pliers and pull on the pin from the wire side until the pin is even with adjacent pins. Do not pull it too far or the pin block may be damaged.

NOTE

The M row pins are U shaped and do not extend through to the package side.

| в 5281.51   | 4.3-1  |

|-------------|--------|

| February 16 | , 1965 |

#### 4.3 PINS IN WINCHESTER PLUG

#### INTRODUCTION

The pins in the Winchester plugs are held in place by a circular spring clip which clips on at the approximate center of the pin. When the pin is fully inserted, the spring clip expands into a groove in the block. This holds the spring in place.

#### REMOVAL

- 1. Obtain the cable-pin removal tool (P/N 11838067)

- 2. Slide the removal tool over the end of the pin until contact is made with the spring clip. Do not put any side strain on the removal tool since there is danger of breaking it. Apply slight pressure to the tool and the pin should become free.

#### REPLACEMENT

- 1. Use a crimper to connect the pin to its wire.

- 2. Insert the pin into the plug using the cable-pin insertion tool (P/N 11838075). Take care not to damage the spring clip.

# FIELD ENGINEERING TECHNICAL MANUAL

| в 5281.51 | 4.4-1 |      |

|-----------|-------|------|

| February  | 16,   | 1965 |

## 4.4 PACKAGES

#### INTRODUCTION

Packages, diode sticks, and resistor sticks are removable. Handles are provided which fit into the package extensions.

#### CAUTION

Some handles must be removed before the gate is closed or the package may be damaged. See Subject 2.3.

#### WARNING

Power must be OFF before removing any element.

B 5281.51 5.1-1 February 16, 1965

#### SECTION 5

#### INSTALLATION

#### 5.1 CABLING - PROCESSOR A

#### INTRODUCTION

The listings in the following table show the cables which are required to be plugged in during installation of Central Processor A. Power quads to each gate should not be plugged in until the regulators have been checked out. Some cables in the listing may have been previously installed as part of system check out.

TABLE 5.1-1 INSTALLATION CABLING - PROCESSOR A

| CABLE NO. | TINOT YOU                        | F                   | ROM         | то          |           | VIA        |  |

|-----------|----------------------------------|---------------------|-------------|-------------|-----------|------------|--|

| CABLE NO. | FUNCTION                         | UNIT CONNECTOR UNIT |             | UNIT        | CONNECTOR | TRAY       |  |

| 7-A       | INTERRUPT & CONTROL              | cc                  | EA CO A7    | PA          | DA CO N2  | 8F         |  |

| 8-AA      | DP-MEMORY WRITE EXCHANGE         | PA DE CO-N7 CC      |             |             | BA AO A2  | 7 <b>F</b> |  |

| 8-AB      | DP-MEMORY WRITE EXCHANGE         | PA                  | DC BO A7    | СС          | BA AO N2  | 5F         |  |

| 9-AA      | DP-MEMORY READ EXCHANGE          | СС                  | AC AO A7    | PA          | EE DO A2  | 7 <b>F</b> |  |

| 9-AB      | DP-MEMORY READ EXCHANGE          | СС                  | AC AO N7    | PA          | EE CO N2  | 5 <b>F</b> |  |

| 10-A      | INTERRUPT & CONTROL              | PA                  | EA DO A7    | сс          | EA CO A2  | 7F         |  |

| 24-26     | HEAT & EXC. CURRENT SENSE        | PA                  | PA BB A3 Y9 |             | CS J1 01  | NT         |  |

|           |                                  |                     |             | PA<br>VOLT. | CS J1 02  | NT         |  |

|           |                                  |                     |             | [REG.]      | CT K1 02  | NT         |  |

| 25-5      | POWER (GROUND)                   | D & D               | DA J1 08    | PA          | CU K1 07  | 2R         |  |

| 25-6      | POWER (GROUND)                   | D & D               | DA J1 08    | PA          | CA K1 07  | 2R         |  |

| 25-25     | POWER (+20V)                     | D & D               | DB L4 03    | PA          | CS K1 12  | 2F         |  |

| 25-34     | POWER (+50V)                     | D & D               | DB L1 03    | PA          | CT K1 04  | 2F         |  |

| 25-43     | POWER (-33V)                     | D & D               | DB J2 03    | PA          | CT K1 01  | 2F         |  |

| 45-A      | INDICATOR INPUT                  | PA                  | AB B4 N7    | D & D       | AN J1     | 4F         |  |

| 46-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | AD B4 N7    | D & D       | AN K1     | 4F         |  |

| 47-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | AF B4 N7    | D & D       | AN L1     | 4F         |  |

| 48-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | BF A4 A7    | D & D       | AN R1     | 4F         |  |

| 49-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | BD D4 N7    | D & D       | AN S1     | 4F         |  |

| 50-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | BB B4 N7    | D & D       | AT J1     | 4F         |  |

| 51-A      | INDICATOR INPUT                  | PA                  | JE DO N2    | D & D       | AT S1     | 4F         |  |

| 52-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | JC CO N2    | D & D       | AN N1     | 4F         |  |

| 53-A      | INDICATOR INPUT & MANUAL CONTROL | PA                  | DE BO N2    | D & D       | AT K1     | 4F         |  |

| 54-A      | MANUAL CONTROL                   | D & D               | AN M1       | PA          | AB C4 N7  | 4F         |  |

| 55-A      | MANUAL CONTROL                   | D & D               | AT R1       | PA          | JE CO N2  | 4R         |  |

TABLE 5.1-1 (CONTINUED)

| CARLE NO  | FUNCTION                         | F                                                | 'ROM        |                                                  | то          | VIA  |  |

|-----------|----------------------------------|--------------------------------------------------|-------------|--------------------------------------------------|-------------|------|--|

| CABLE NO. | FUNCTION                         | UNIT                                             | CONNECTOR   | UNIT                                             | CONNECTOR   | TRAY |  |

| 56-A      | INDICATOR INPUT & MANUAL CONTROL | <del>                                     </del> |             | D & D                                            | AN Pl       | 4R   |  |

| 57-A      | INDICATOR INPUT & MANUAL CONTROL | PA DA BO N2                                      |             | D & D                                            | AT L1       | 4R   |  |

| 58-A      | INDICATOR INPUT & MANUAL CONTROL | PA                                               | EA BO N2    | D & D                                            | AT M1       | 4R   |  |

| 59-A      | MANUAL CONTROL & TEST SWITCH     | D & D                                            | AT T1       | PA                                               | EA CO A2    | 4R   |  |

| 60-A      | MANUAL CONTROL                   | D & D                                            | AT N1       | PA                                               | EE BO A2    | 4R   |  |

| 61-A      | INDICATOR INPUT                  | PA                                               | EE BO N2    | D & D                                            | AT Pl       | 4R   |  |

| 144-1A    | POWER (GATE J)                   | PA                                               | JC BO N7    | REG.                                             | CS 07       | NT   |  |

| 144-2A    | POWER (GATE J)                   | PA                                               | JE BO N7    | REG.                                             | CS 08       | NT   |  |

| 145-A     | POWER (GATE A)                   | PA                                               | AB B4 N2    | REG.                                             | CS 01       | NT   |  |

| 146-A     | POWER (GATE A)                   | PA                                               | AD B4 N2    | REG.                                             | CS 02       | NT   |  |

| 147-A     | POWER (GATE A)                   | PA                                               | AF B4 N2    | REG.                                             | CS 03       | NT   |  |

| 148-A     | POWER (GATE B)                   | PA                                               | BB B4 N2    | REG.                                             | CS 04       | NT   |  |

| 149-A     | POWER (GATE B)                   | PA                                               | BD B4 N2    | REG.                                             | CS 05       | NT   |  |

| 150-A     | POWER (GATE B)                   | PA                                               | BF B4 N2    | REG.                                             | CS 06       | NT   |  |

| 151-A     | POWER (GATE D)                   | PA                                               | DA BO N7    | REG.                                             | CS 11       | NT   |  |

| 152-A     | POWER (GATE D)                   | PA                                               | DC B0 N7    | REG.                                             | CS 12       | NT   |  |

| 153-A     | POWER (GATE D)                   | PA                                               | DE BO N7    | REG.                                             | CS 13       | NT   |  |

| 154-A     | POWER (GATE E)                   | PA                                               | EA BO N7    | REG.                                             | CS 14       | NT   |  |

| 155-A     | POWER (GATE E)                   | PA                                               | EC BO N7    | REG.                                             | CS 15       | NT   |  |

| 156-A     | POWER (GATE E)                   | PA                                               | EE BO N7    | REG.                                             | CS 16       | NT   |  |

| 175       | CLOCK (GATE A)                   | СС                                               | EA C2 L6    | PA                                               | AA C5 L9    | 2R   |  |

|           |                                  |                                                  |             |                                                  | AC C5 L9    | 2R   |  |

|           |                                  |                                                  |             |                                                  | AE C5 L9    | 2R   |  |

| 176       | CLOCK (GATE B)                   | сс                                               | EA C2 L7    | PA                                               | BA C6 L9    | 2R   |  |

|           |                                  |                                                  |             |                                                  | BC C6 L9    | 2R   |  |

|           |                                  |                                                  |             | <del>                                     </del> | BE C5 L9    | 2R   |  |

| 177       | CLOCK (GATE D)                   | СС                                               | EA C2 L8    | PA                                               | DA C6 L9    | 2R   |  |

|           |                                  |                                                  |             | ļ                                                | DC C6 L9    | 2R   |  |

|           |                                  |                                                  |             |                                                  | DE C6 L9    | 2R   |  |

| 178       | CLOCK (GATE E)                   | СС                                               | EA C2 L9    | PA                                               | EA B6 Y9    | 2R   |  |

|           |                                  | <del>                                     </del> |             | †                                                | EE B6 Y9    | 2R   |  |

| 179       | CLOCK (GATE J)                   | СС                                               | EA C2 L5    | PA                                               | JC C6 L9    | 2R   |  |

|           |                                  | <u> </u>                                         |             | <b>†</b>                                         | JE C6 L9    | 2R   |  |

| 197-1     | GROUND (GATE A)                  | PA                                               | GROUND BUS  | REG.                                             | CU K1 01    | NT   |  |

| 197-2     | GROUND (GATE B)                  | PA                                               | GROUND BUS  | REG.                                             | CU K1 02    | NT   |  |

| 197-3     | GROUND (GATE D)                  | PA                                               | GROUND BUS  | REG.                                             | CU K1 02    | NT   |  |

| 197-4     | GROUND (GATE E)                  | PA                                               | GROUND BUS  | REG.                                             | CU K1 01    | NT   |  |

| 197-17    | GROUND (GATE J)                  | PA                                               | GROUND BUS  | REG.                                             | CA J1 01    | 2R   |  |

| *205      | POWER (-19V)                     | PS                                               | DA K2 B2    | REG.                                             | CA K1 04    | NT   |  |

| 229       | 115V FAN                         | <del> </del>                                     | FA K1 06/07 | <del></del>                                      | FA K1 06/07 |      |  |

| 231       | 115V CONVENIENCE                 | <del>                                     </del> | DF P1 03/04 | <del> </del>                                     | HB L1/L2    | NT   |  |

| 201       | 1101 CONTENTENCE                 | ע איי                                            | DF PI 03/04 | 1 -4                                             | 01/02       | 1 1  |  |

<sup>\*</sup> NORMALLY INSTALLED AS INDICATED IN SECTION 5.2 OF THE POWER SUPPLY MANUAL.

| в 5281.51   | 5.2-1 |

|-------------|-------|

| February 16 | 7065  |

## 5.2 CABLING - PROCESSOR B

#### INTRODUCTION

The table listed below shows cabling for Central Processor B. The power quads should not be plugged in until the regulators have been checked out.

TABLE 5.2-1 INSTALLATION CABLING - PROCESSOR B

| CABLE        | FUNCTION                         |       | FROM      | TO     |           | VIA        |

|--------------|----------------------------------|-------|-----------|--------|-----------|------------|

| NO.          | FUNCTION                         | UNIT  | CONNECTOR | UNIT   | CONNECTOR | TRAY       |

| 7-B          | INTERRUPT & CONTROL              | CC    | EA CO N7  | PB     | DA CO N2  | 2F         |

| 8-BA         | MEMORY WRITE EXCHANGE            |       | DE CO N7  | CC     | BE AO A2  | 8F         |

| 8-BB         | MEMORY WRITE EXCHANGE            | PB    | DC BO A7  | CC     | BE AO N2  | 5 <b>F</b> |

| 9-BA         | MEMORY READ EXCHANGE             | CC    | AE AO A7  | PB     | EE DO A2  | 8F         |

| 9- <b>BB</b> | MEMORY READ EXCHANGE             | СС    | AE AO N7  | PB     | EE CO N2  | 5 <b>F</b> |

| 10-B         | INTERRUPT & CONTROL              | PB    | EA DO A7  | CC     | EA CO N2  | 3 <b>F</b> |

| 24-27        | HEAT & EXCESS CURRENT SENSE      | PB    | BB A3 Y9  | Грв 7_ | CS J1 01  | NT         |

|              |                                  |       |           | VOLT   | CS J1 02  | NT         |

|              |                                  |       |           | REG.   | CS K1 02  | NT         |

| 25-7         | POWER (GROUND)                   | D & D | DA Ji 07  | PB     | CU K1 07  | 2R         |

| 25-8         | POWER (GROUND)                   | D & D | DA J1 07  | PB     | CA K1 07  | 2R         |

| 25-26        | POWER (+20V)                     | D & D | DB L4 02  | PB     | CS K1 12  | 2F         |

| 25-35        | POWER (+50V)                     | D & D | DB L1 02  | PB     | CT K1 04  | 2F         |

| 25-44        | POWER (-33V)                     | D & D | DB J2 02  | PB     | CT K1 01  | 2 <b>F</b> |

| 45-B         | INDICATOR INPUT                  | PB    | AB B4 N7  | D & D  | AN J1     | 4R         |

| 46-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | AB B4 N7  | D & D  | AN Kl     | 4R         |

| 47-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | AF B4 N7  | D & D  | AN L1     | 4R         |

| 48-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | BF A4 A7  | D & D  | AN R1     | 4R         |

| 49-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | BD D4 N7  | D & D  | AN S1     | 4R         |

| 50-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | BB B4 N7  | D & D  | AT Jl     | 4R         |

| 51-B         | INDICATOR INPUT                  | PB    | JE DO N2  | D & D  | AT S1     | 4R         |

| 52-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | JC CO N2  | D & D  | AN N1     | 4R         |

| 53-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | DE BO N2  | D & D  | AT K1     | 4R         |

| 54-B         | MANUAL CONTROL                   | D & D | AN M1     | PB     | AB C4 N7  | 4R         |

| 55-B         | MANUAL CONTROL                   | D & D | AT R1     | PB     | JE CO N2  | 4F         |

| 56-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | DC AO A2  | D & D  | AN Pl     | 4F         |

| 57-B         | INDICATOR INPUT & MANUAL CONTROL | PB    | DA BO N2  | D & D  | AT L1     | 4F         |

| 58-B         | INDICATOR INPUT                  | PB    | EA BO N2  | D & D  | AT Ml     | 4F         |

| 59-B         | MANUAL CONTROL & TEST SWITCH     | D & D | AT T1     | PB     | EA CO A2  | 4F         |

| 60-B         | MANUAL CONTROL                   | D & D | AT N1     | PB     | EE BO A2  | 4 <b>F</b> |

| 61-B         | INDICATOR INPUT                  | PB    | EE BO N2  | D & D  | AT Pl     | 4F         |

| 144-1B       | POWER (GATE J)                   | PB    | JC BO N7  | REG.   | CS 07     | ИT         |

| 144-2B       | POWER (GATE J)                   | PB    | JE BO N7  | REG.   | CS 08     | NT         |

| 145-B        | POWER (GATE A)                   | PB    | AB B4 N2  | REG.   | CS 01     | NT         |

Continued on next page

TABLE 5.2-1 (CONTINUED)

| CABLE        | FUNCTION           | FROM  |              | то   |              | VIA  |

|--------------|--------------------|-------|--------------|------|--------------|------|

| NO.          | FORCITOR           | UNIT  | CONNECTOR    | UNIT | IT CONNECTOR |      |

| 146-B        | POWER (GATE A)     | PB    | AD B4 N2     | REG. | CS 02        | NT   |

| 147-B        | POWER (GATE A)     | PB    | AF B4 N2     | REG. | CS 03        | NT   |

| 148-B        | POWER (GATE B)     | PB    | BB B4 N2     | REG. | CS 04        | NT   |

| 149-B        | POWER (GATE B)     | PB    | BD B4 N2     | REG. | CS 05        | NT   |

| 150-B        | POWER (GATE B)     | PB    | BF B4 N2     | REG. | CS 06        | NT   |

| 151-B        | POWER (GATE D)     | PB    | DA BO N7     | REG. | CS 11        | NT   |

| 152-B        | POWER (GATE D)     | PB    | DC BO N7     | REG. | CS 12        | NT   |

| 153-B        | POWER (GATE D)     | PB    | DE BO N7     | REG. | CS 13        | NT   |

| 154-B        | POWER (GATE E)     | PB    | EA BO N7     | REG. | CS 14        | NT   |

| 155-B        | POWER (GATE E)     | PB    | EC BO N7     | REG. | CS 15        | NT   |

| 156-B        | POWER (GATE E)     | PB    | EE BO N7     | REG. | CS 16        | NT   |

| 180          | CLOCK (GATE A)     | СС    | EA C2 Y6     | PB   | AA C5 L9     | 2R   |

|              |                    |       |              |      | AC C5 L9     | 2R   |

|              |                    |       |              |      | AE C5 L9     | 2R   |

| 181          | CLOCK (GATE B)     | CC    | EA C2 Y7     | PB   | BA C6 L9     | 2R   |

|              |                    |       |              |      | BC C6 L9     | 2R   |

|              |                    |       |              |      | BE C5 L9     | 2R   |

| 182          | CLOCK (GATE D)     | CC    | EA C2 Y8     | PB   | DA C6 L9     | 2R   |

|              |                    |       |              |      | DC C6 L9     | 2R   |

|              |                    |       |              |      | DE C6 L9     | 2R   |

| 183          | CLOCK (GATE E)     | СС    | EA C2 Y9     | PB   | EA B6 Y9     | 2R   |

|              |                    |       |              |      | EE B6 Y9     | 2R   |

| 184          | CLOCK (GATE J)     | CC    | EA C2 Y5     | PB   | JC C6 L9     | 2R   |

|              |                    |       |              |      | JE C6 L9     | 2R   |

| 197-5        | GROUND (GATE A)    | PB    | GROUND BUS   | REG. | CU K1 01     | NT   |

| 197-6        | GROUND (GATE B)    | PB    | GROUND BUS   | REG. | CU K1 02     | NT   |

| 197-7        | GROUND (GATE D)    | PB    | GROUND BUS   | REG. | CU K1 02     | NT   |

| 197-8        | GROUND (GATE E)    | PB    | GROUND BUS   | REG. | CU K1 01     | NT   |

| 197-18       | GROUND (GATE J)    | PB    | GROUND BUS   | REG. | CA K1 04     | NT   |

| <b>*2</b> 06 | POWER (-19V)       | PS    | DA M7 B2     | PB   | CA J1 01     | 2R   |

| 230          | 115VAC FAN         | M-SS2 | FA K1 06/07  | PB   | FA K1 06/07  | NT   |

| 231          | 115VAC CONVENIENCE | D & D | DF P1 03/04  | PB   | HBL1/L2 01/0 | 2 NT |

| 232          | 115VAC CONVENIENCE | M-SS2 | HBL1/L2 01/0 | 2 PB | HB L1 01/02  | NT   |

<sup>\*</sup> NORMALLY INSTALLED AS INDICATED IN SECTION 5.2 OF THE POWER SUPPLY MANUAL.

#### NOTE

Refer to D & D DA's Page 56.02.03.0 for sensing wire deletion with two Processors.

# FIELD ENGINEERING TECHNICAL MANUAL-

B 5281.51 6.1-1 February 16, 1965

## SECTION 6

# CIRCUIT ANALYSIS

See Power Supply Manual, Section 6.

B 5281.51 7.1-1 February 16, 1965

#### SECTION 7

#### FUNCTIONAL DESCRIPTION

## 7.1 SINGLE LENGTH ADD (AD1L) - SINGLE LENGTH SUBTRACT (SULL)

#### PURPOSE

Algebraically ADD or SUBTRACT the two Operands in the top of the stack. When the operation is complete, the "B" Register will contain the sum or difference. The "A" Register will be set to EMPTY, the "B" Register is set to FULL and the "B" Register Flag bit is set to ZERO.

#### SUMMARY OF OPERATION

When the "A" Register is equal to zero (WO6L), the answer is contained in the "B" Register.

When the "B" Register is zero and the "A" Register is NOT zero ( $\overline{WO6L}$  • WO7L), the "B" Register is replaced by the contents of the "A" Register.

If the "A" and "B" Registers equal zero (WO6L • WO7L), the answer will equal zero and it will be contained in the "B" Register. Thus, all of the "B" Register is cleared. In either case, the operation is terminated.

Providing that the Mantissa signs and the exponents of the Operands are equal, the Mantissas are added and the sum placed in the "B" Register. If the sum exceeds 13 octal digits, the Mantissa of the sum is shifted right one octal place, rounded, and the exponent algebraically increased by one.

When the exponents of the Operands are equal but the Mantissa signs are unequal, the difference of the Mantissas with appropriate sign is placed in the "B" Register. If the exponents of the Operands are unequal, the Operands are aligned. When the alignment causes the smaller Operand to be shifted right 14 or more octal places, the larger Operand is the result. If the alignment causes less than 14 octal shifts, the last digit shifted out is checked for four or greater. Should it be four or greater, a round will result during addition.

If the signs of the Operand are equal, the Mantissas are added and the sum placed in the "B" Register. In case the sum does not exceed 13 octal digits, the last digit shifted out of the Register is used for rounding the result. When the sum is 14 digits, the Mantissa in the "B" Register is rounded to 13 digits.

When the signs of the Operand are unequal, the digits are complemented as they are shifted out of the Register during alignment. In effect, the equivalent of a 15 digit subtraction occurs in this latter case and the result is rounded to the 13 most significant digits of the 15 digit result.

When the result has an exponent of greater than +63, the Exponent Overflow bit is set in the Interrupt Register. The "B" register contains the correct Mantissa; Mantissa sign, and Exponent sign. The magnitude of the correct exponent is contained in the Exponent Field of the "B" register Modulo 64.

#### 7.2 SINGLE LENGTH DIVIDE (DV1L)

#### PURPOSE

The Single Precision Divide Operator (DVIL) will divide the number in the "B" Register by the number in the "A" Register. The quotient is found in the "B" Register. Fourteen significant quotient digits are developed and then rounded to thirteen.

If the Mantissa of the number in the "B" Register is zero, the "B" Register is cleared. If the Mantissa of the number in the "A" Register is zero, the Divide by Zero Interrupt is set. In either case, the operation is terminated.

When the exponent overflows or underflows, the appropriate Interrupt bit is set. The correct exponent is found in the "B" Register, Modulo 64.

#### SUMMARY OF OPERATIONS

During stack adjustment, mark the "A" Register EMPTY. This is because the divisor will not be considered valid information after the operation is completed. Also, clear the Flag bit in the "B" Register to mark the information as an Operand. After the Registers have been LOADED, normalization will begin.

Set the Divide by Zero Interrupt if the "A" Register Mantissa is zero. Terminate the Operator if either Operand is zero. If neither Operand is zero, check the 13th octade. If it is zero, shift the Mantissa left and decrease the exponent of the associated word until the 13th octade is NOT zero.

When both Mantissas are normalized, the first cycle of the divide operation is allowed. If the sign of the "A" Register Mantissa is negative, complement the sign of the "B" Register Mantissa. In any divide operation opposite signs result in a negative result and similar signs result in a positive result.

Set QO2F ON to initiate exponent adjustments and complement the sign of the "A" Register exponent to cause the algebraic sum of the two exponents to ultimately result in a difference operation.

The process of division is basically similar to the usual principle of repetitive subtraction. The operation starts out in subtraction and increases the quotient digit until the remainder goes below zero. The cycle then uses the quotient predictor to gate the operation either into the same subtract cycle or, into an add to the complemented remainder. In each case, this forms the quotient digit in the fewest arithmetic operations.

When a digit has been formed in the 13th position of the quotient, the 14th is formed, examined and operations are terminated. If the last digit is 4 or more, the quotient is rounded.

The 42 bits of the "A" and "B" Registers are added and placed in the "B" Register. Since the "A" Register is a complement, this is the equivalent of a subtraction.

If the subtraction is successful, the remainder of the decrement is above zero. Count the quotient digit up one for each operation that will not cause the remainder to go below zero. When the operation causes it to go below zero, the combination will force the remainder to go into complement form. This indicates that the formation of the quotient digit is now completed.

The quotient predictor establishes whether the next quotient digit will be  $\mu$  or more (WO $\mu$ L), or, if it will be less than  $\mu$  (WO $\mu$ L). If it is  $\mu$  or more, the operation will add a true "A" to a complement remainder (effectively a subtraction) and will count the next quotient digit down. When the sum of a complemented remainder and the true "A" overflow, the corrections to the quotient digit have been made and the remainder is in true form. This type of cycle is best thought of as a corrective adjustment of the quotient digit based on the number of times the add cycle proves the assumed value of the quotient digit to be in error.

If the quotient digit is less than  $\mu$ , the operation is best formed by the subtract operation which was just exited. The remainder will be in complement form and shifted to the left one place to re-position it for the subtract cycle to follow.

If the quotient predictor shows the next digit will be zero, the cycle will continue shifting the "B" and "X" Registers and counting the "N" Register.

If there has been sufficient pulses, X13L vanishes and is replaced by  $\overline{\text{X13L}}$ .  $\overline{\text{X13L}}$  signals a normalized quotient. Since all non-integer arithmetic operators must have normalized Mantissas, the divide operation will form the first significant quotient digit in either the first or second octade position of the temporary storage "X" Register.

When the quotient digit is in the first position, 13 shifts will bring it into X13L and the 14th digit will be formed. If it is in the second position, 14 shifts will be needed and the 15th digit will be formed. If the count of shifts in the "N" Register is 14, the first quotient digit formed is zero, and the existing value is 8 times larger than was expected. Therefore, reduce the exponent by one.

The rounding of the Mantissa will be an add of one into the "B" Register. If the exponent sign is negative and the high order bit is ON, set the Exponent Underflow Interrupt. If the exponent sign is positive and the high order exponent bit is ON, set the Exponent Overflow Interrupt.

## 7.3 SINGLE LENGTH MULTIPLY (MUIL)

#### PURPOSE

To algebraically MULTIPLY two Operands in the "A" and "B" Registers and leave the product in the "B" Register.

#### SUMMARY OF OPERATIONS

Adjust the stack as required to LOAD the two Operands into the "A" and "B" Registers. Mark the "A" Register as UNOCCUPIED and clear the Flag bit of the "B" Register. This insures that the "A" Register at the end of the operation is marked as EMPTY and that the final result is flagged as an Operand.

With the common requirement that both the "A" and "B" Registers be LOADED and a Single Precision Multiply Operation is being performed (MULL); clear the "B" Register and terminate the operation if either the "A" or "B" Mantissa equals zero (WO6L + WO7L). When one of the multipliers is zero, the answer is zero.

If the "A" and "B" Registers are LOADED, the Mantissas of the "A" and "B" Registers are NOT zero ( $\overline{\text{WO6L}} \bullet \overline{\text{WO7L}}$ ), and a multiply operation with the exponents of the "A" and "B" Registers NOT equal to zero ( $\overline{\text{MU1L}} \bullet \overline{\text{W71L}} + \overline{\text{MU1L}} \bullet \overline{\text{W72L}}$ ), the "A" and "B" Registers are normalized. When the most significant octade is equal to zero; shift the Mantissa left by octades, set the low order octade equal to zero, and count the exponent down one. This shift and count down of the exponent will continue until the Mantissa is normalized.

If the exponents of the "A" and "B" Registers are zero (J93L), turn ON Q05F to record the fact that the two Operands are integers (non-floating point). If the result is integer, do NOT normalize.

When both Operands are integers, or both Operands are normalized; initiate Multiply. The multiplier ("B" Mantissa) is shifted to the "X" Register. The Mantissa of the "B" Register is cleared to assemble the partial-final product.

The "B" Register exponent is counted plus one. This is to give the 13th additional count of the exponent. In a Multiply operation, if 13 digits are multiplied by 13 digits, the answer is 26 digits in length. However, since the 13 least significant digits of the final answer are lost, add thirteen to the exponent. One is added here and 12 more in the exponent Add operation.

QO2F going ON starts the Exponent Add Operation which goes on concurrently and independently with the Multiply. It terminates when the exponents have been added together.

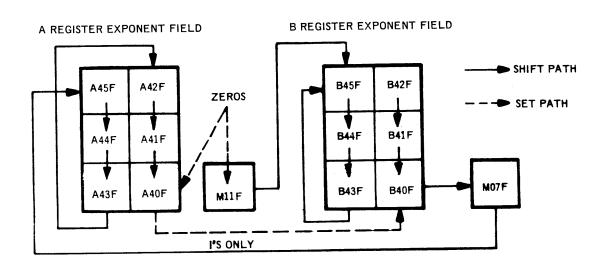

Because the Exponent Add Operation is common to several operators, a separate instruction sheet has been made up for it. Refer to Subject 7.7, Pages 2 and 3.

If the least significant bit of the multiplier is OFF (BOIF) and sensed at the same time as we shift, it indicates that the multiplier is an even number. The multiplicand is then doubled by shifting it left by one bit position.

The least significant bit of the "A" Register (AOlF) is set to zero and the status of the multiplicand is recorded by using the three least significant bits of the "M" Register as a counter. Count these up by one. This records the fact that the multiplicand has been doubled (2A).

Should the "N" Register be equal to zero (NEZL), set the high order digit of the "X" Register to zero. This insertion of a zero happens only on the first shifts of the "X" Register and is a flag between the multiplier digits and the digits of the answer that will be shifted into the "X" Register as developed.

In the case of a zero multiplier, just shift the "B" and "X" Registers until a non-zero multiplier is in X1.

When the multiplier is equal to one, add the contents of the "B" Register and the "A" Register and place the result back in the "B" Register.

If the multiplier digit in the "X" Register is 2 or  $\mu$ , the left shift of the "A" Register Level (ALSL) is true and the least significant bit of the "M" Register is OFF ( $\overline{\text{MOIF}}$ ). This indicates that the multiplicand is in its original state (A) or in the complement of the original state ( $\overline{\text{A}}$ ). The multiplicand is doubled by shifting "A" and the extension of "A" left one bit. The multiplicand counter MO1 thru MO3 is counted up one to record the new state of "A" (2A,  $\overline{\text{2A}}$  or  $\overline{\mu}$ A,  $\overline{\mu}$ A).

If the multiplier digit is 3; do the first add, then double the multiplicand for the second add cycle.

If the right shift of "A" Level (ARSL) is true; shift "A" and the extension of "A" (MO4 thru MO6) right one bit. This halves the multiplicand. Count the multiplicand counter (MO3 thru MO1) down by one to record the status of the multiplicand. ARSL is formed by a combination of the state of the multiplicand and the value of the multiplier digit.

If the complement of "A" shift level is true (ACSL), this will indicate the next multiplier digit is -0 thru -4. Complement "A", the extension of "A" (MO6 thru MO4), and the Carry Flip-flop (QOIF). ACSL is developed from the combination of the state of the multiplicand (2A, A etc.), and the status of the current multiplier digit in the "X" Register.

Unconditionally, add the partial product in the "B" Register to the multiplicand in the "A" Register and place the results back in the "B" Register. The "A" Register remains the same.