# Burroughs 3

B 6800 System

REFERENCE MANUAL

PRICED ITEM

# Burroughs 3

B 6800 System

**REFERENCE MANUAL**

Copyright @ 1977, Burroughs Corporation, Detroit, Michigan 48232

PRICED ITEM

Printed in U.S. America July 1977 5001290

Burroughs believes that the information described in this manual is accurate and reliable, and much care has been taken in its preparation. However, no responsibility, financial or otherwise, is accepted for any consequences arising out of the use of this material. The information contained herein is subject to change. Revisions may be issued to advise of such changes and/or additions.

Correspondence regarding this document should be addressed directly to Burroughs Corporation, P.O. Box 4040, El Monte, California 91734, Attn: Publications Department, TIO—West.

#### LIST OF EFFECTIVE PAGES

| Issue Page              | Issue Page                     |

|-------------------------|--------------------------------|

| Title Original          | 7-1 thru 7-33 Original         |

| ii Original             | 7-34                           |

| iii Original            | 8-1 thru 8-15 Original         |

| iv                      | 8-16                           |

| v thru xxii Original    | 9-1 thru 9-4 Original          |

| 1-1 thru 1-31 Original  | 10-1 thru 10-8 Original        |

| 1-32                    | 11-1 thru 11-23 Original       |

| 2-1 thru 2-39 Original  | 11-24 Blank                    |

| 2-40 Blank              | 11-25 thru 11-34 Original      |

| 3-1 thru 3-18 Original  | 12-1 thru 12-8 Original        |

| 4-1 thru 4-55 Original  | 13-1 thru 13-7 Original        |

| 4-56                    | 13-8 Blank                     |

| 5-1 thru 5-3 Original   | A-1 thru A-5 Original          |

| 5-4 Blank               | A-6                            |

| 5-5 thru 5-67 Original  | B-1 thru B-6 Original          |

| 5-68                    | C-1 thru C-2 Original          |

| 5-69 thru 5-76 Original | D-1 thru D-2 Original          |

| 6-1 thru 6-8 Original   | Index-1 thru Index-14 Original |

#### TABLE OF CONTENTS

| Section |                                             | Page       |

|---------|---------------------------------------------|------------|

|         | INTRODUCTION                                | xxi        |

| 1       | SYSTEM DESCRIPTION                          | 1-1        |

|         | General                                     | 1-1        |

|         | Scope of This Manual                        | 1-1        |

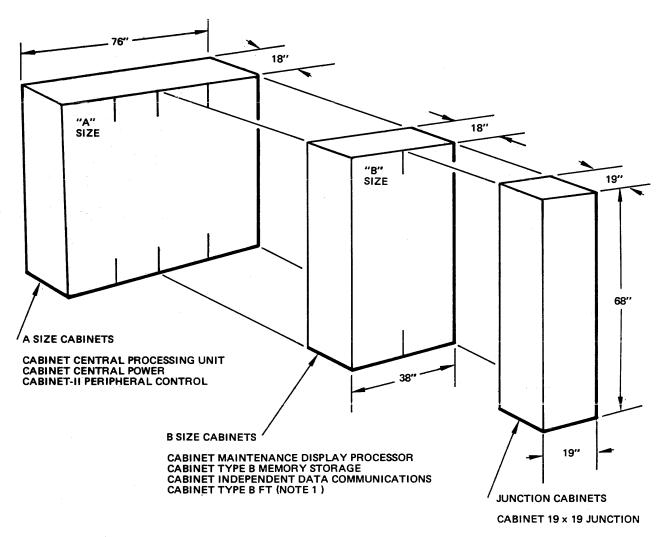

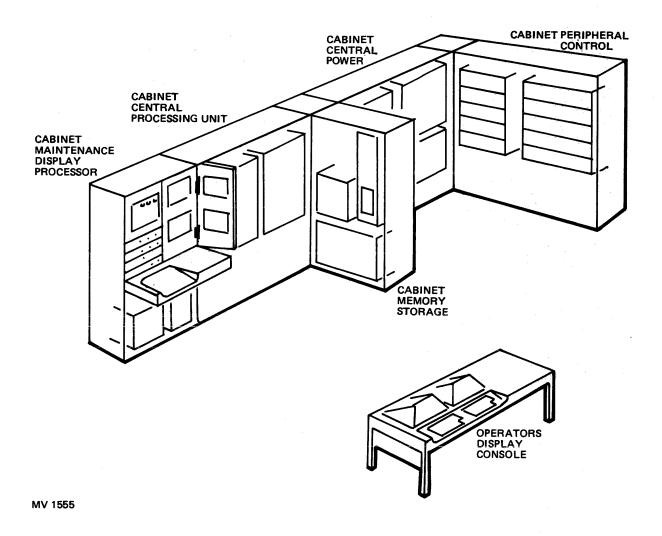

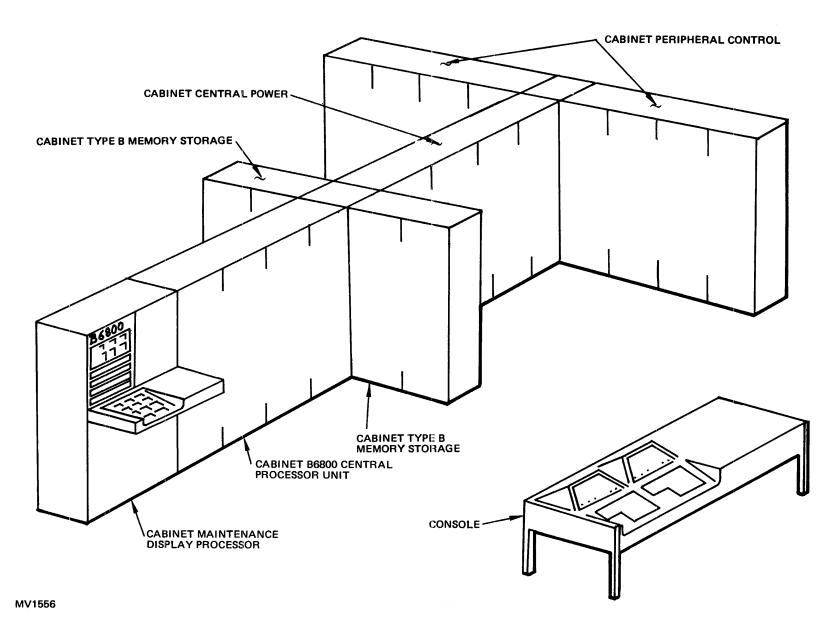

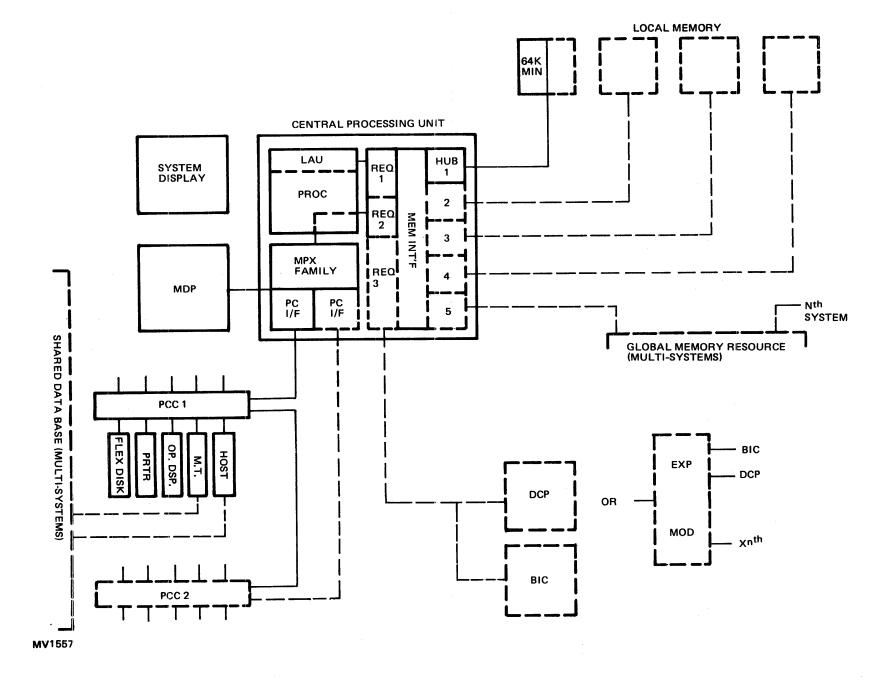

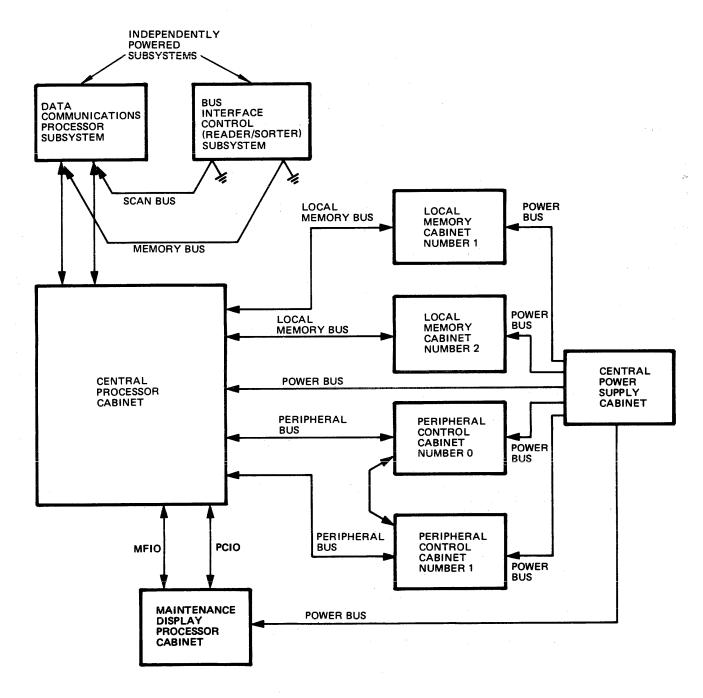

|         | B 6800 Hardware System Organization         | 1-1        |

|         | B 6800 System Hardware Module Organization  | 1-5        |

|         | B 6800 Module Interfaces                    | 1-5        |

|         | B 6800 Central Processing Unit Cabinet      | 1-7        |

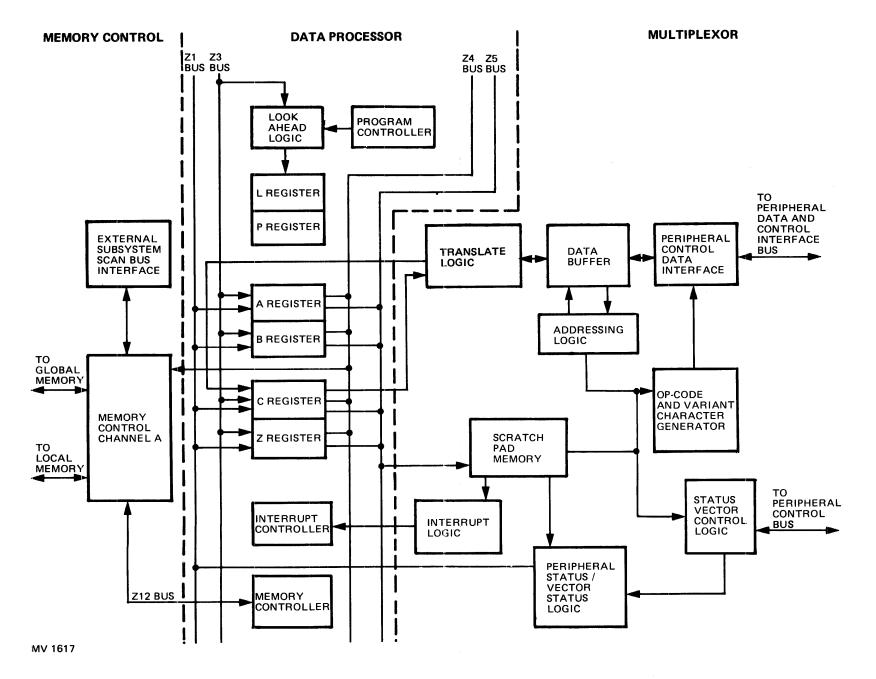

|         | Data Processor Module                       | 1-8        |

|         | Multiplexor Module (IO Processor)           | 1-9        |

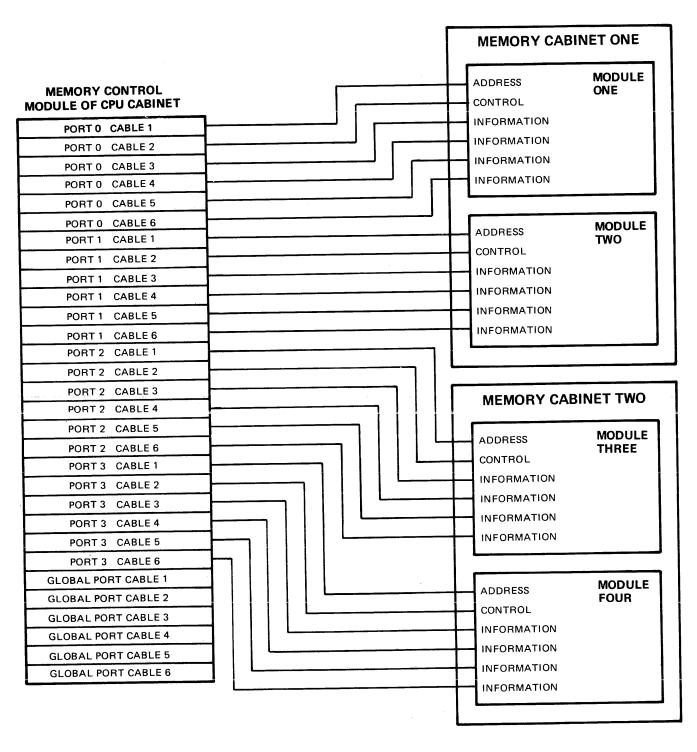

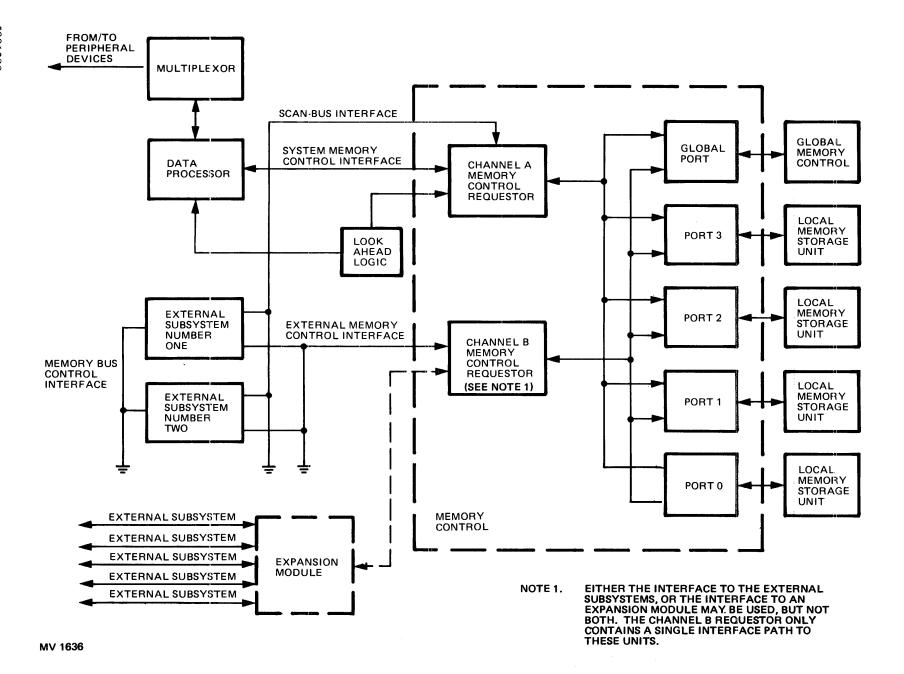

|         | Memory Control Module                       | 1-10       |

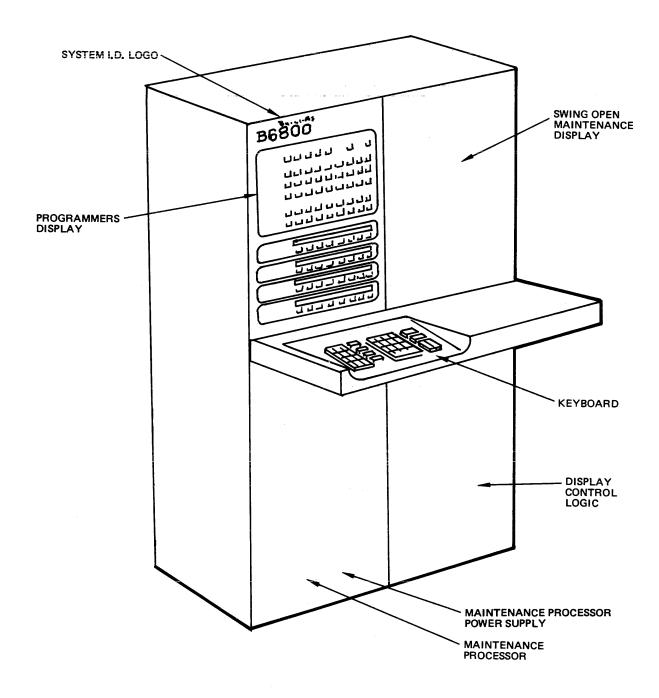

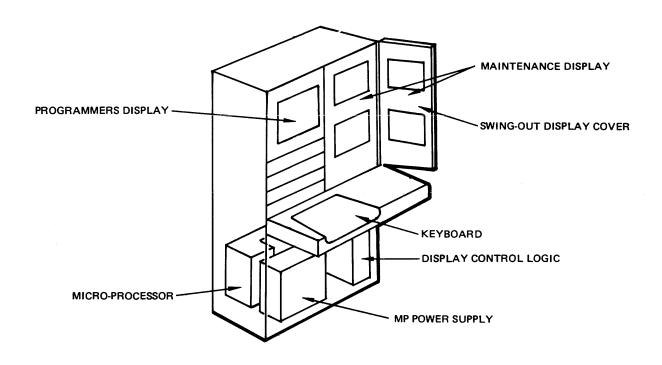

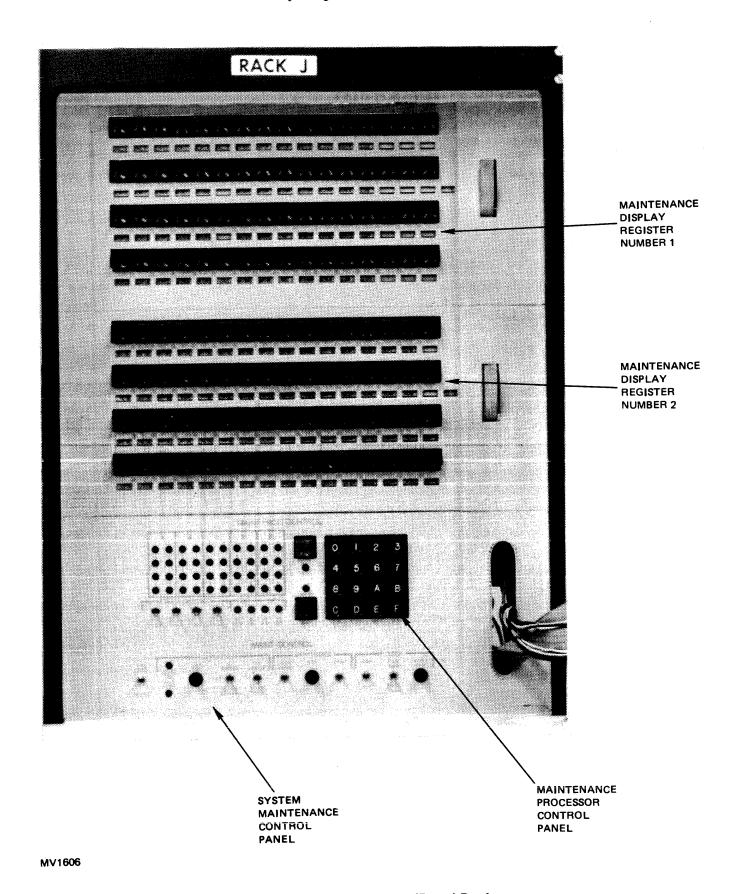

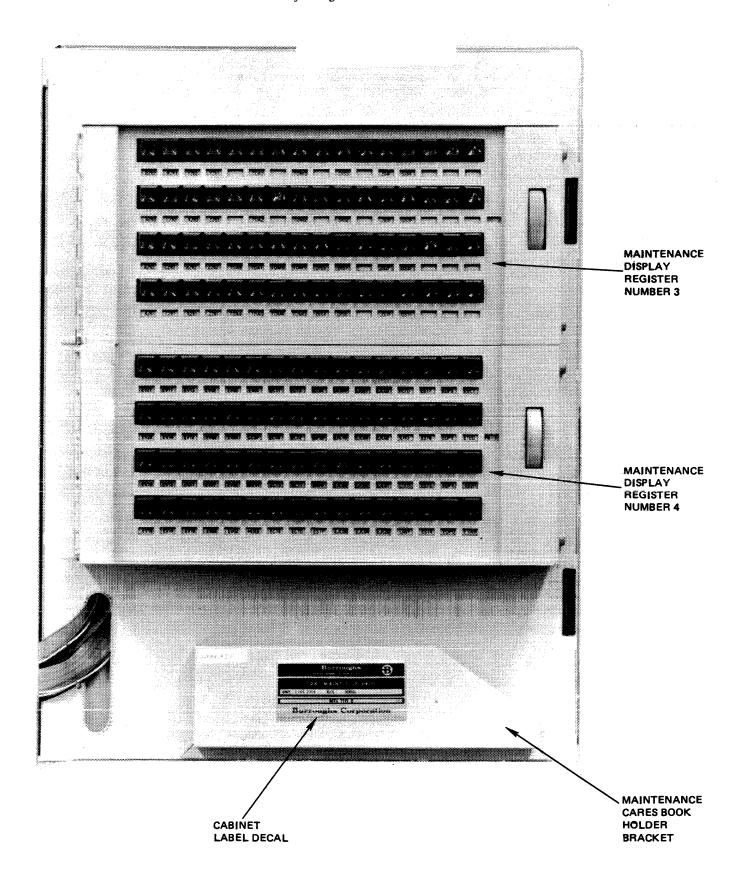

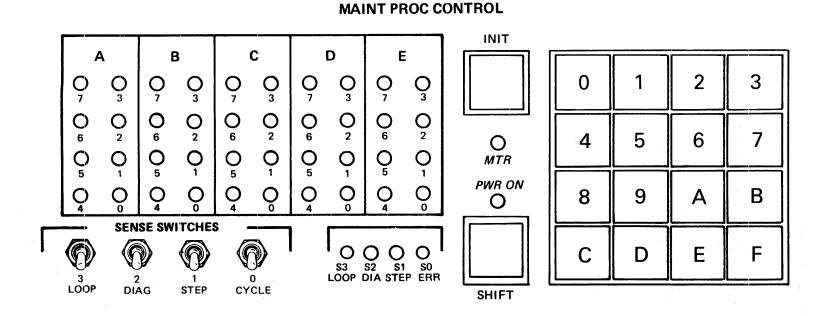

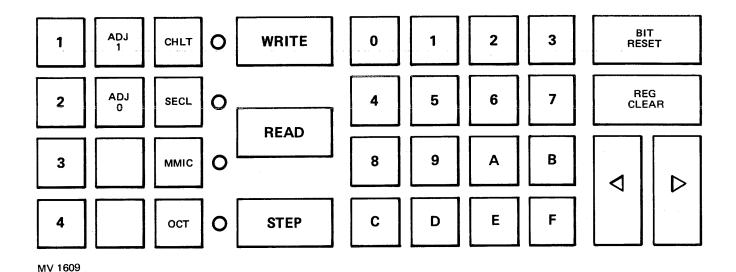

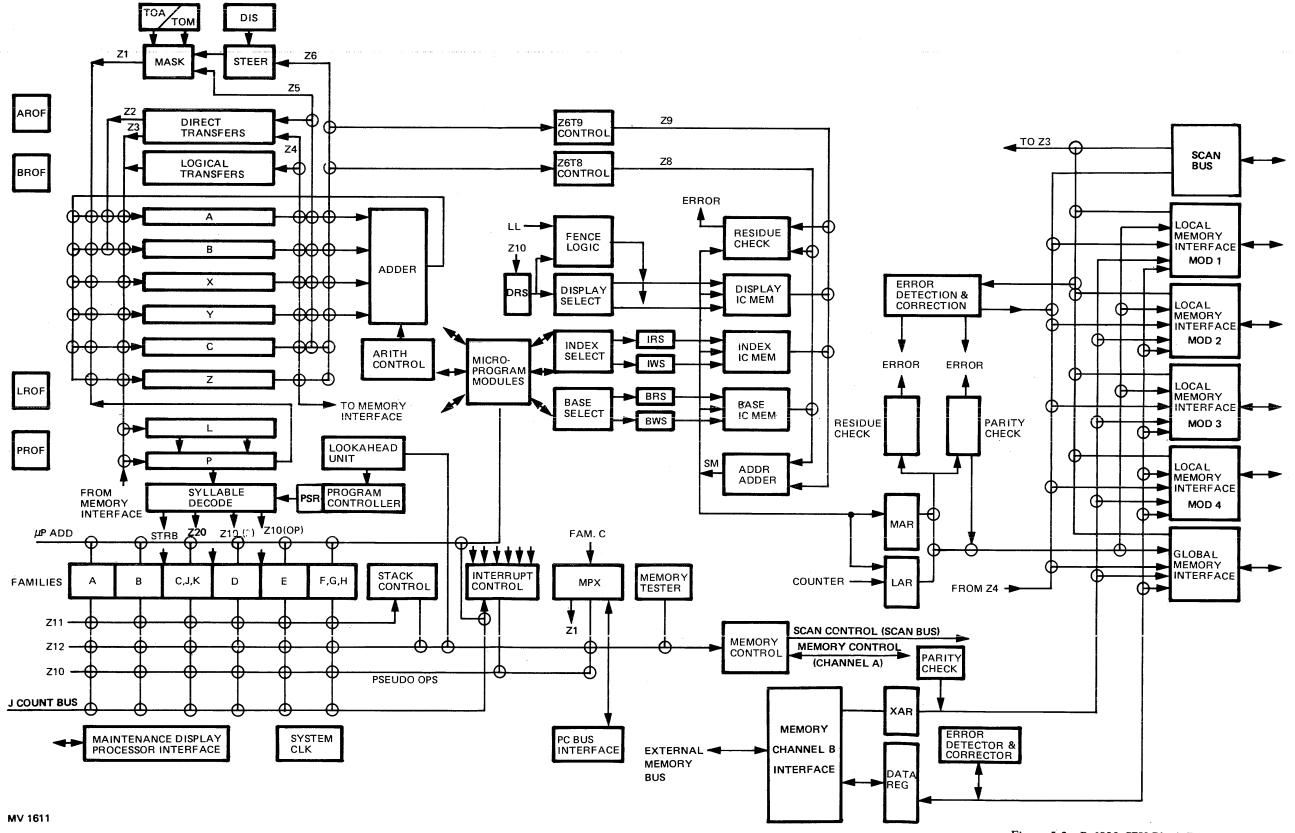

|         | B 6800 Maintenance Display Processor        | 1-12       |

|         |                                             | 1-17       |

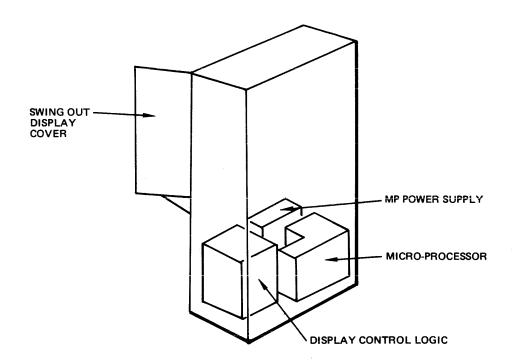

|         | Display Control Logic                       | 1-17       |

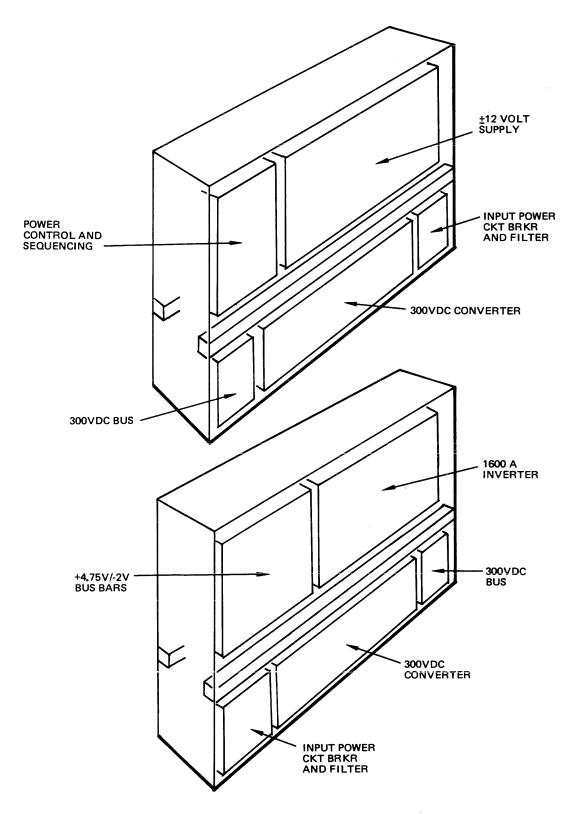

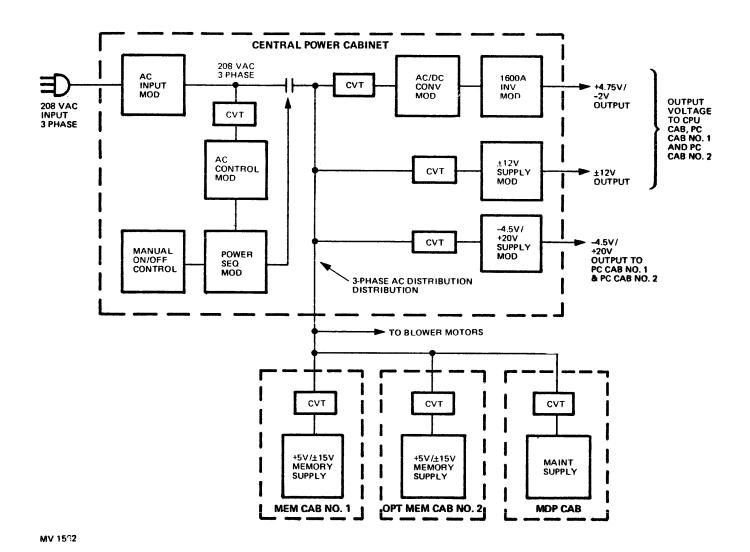

|         | B 6800 Central Power Supply Cabinet         | 1-17       |

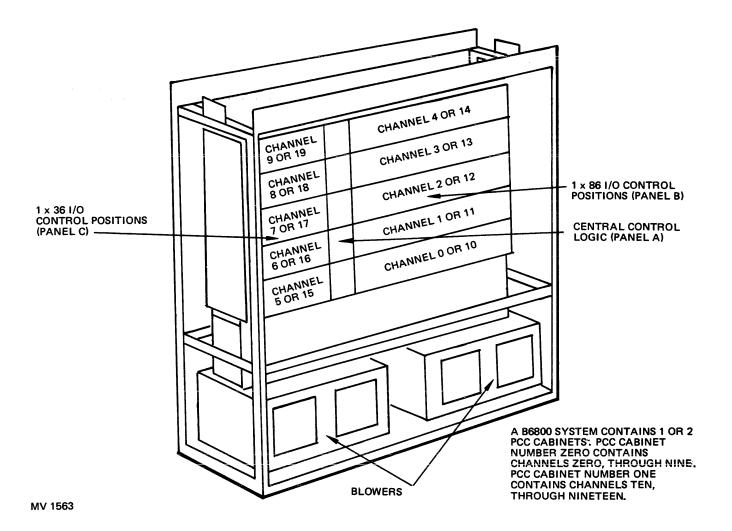

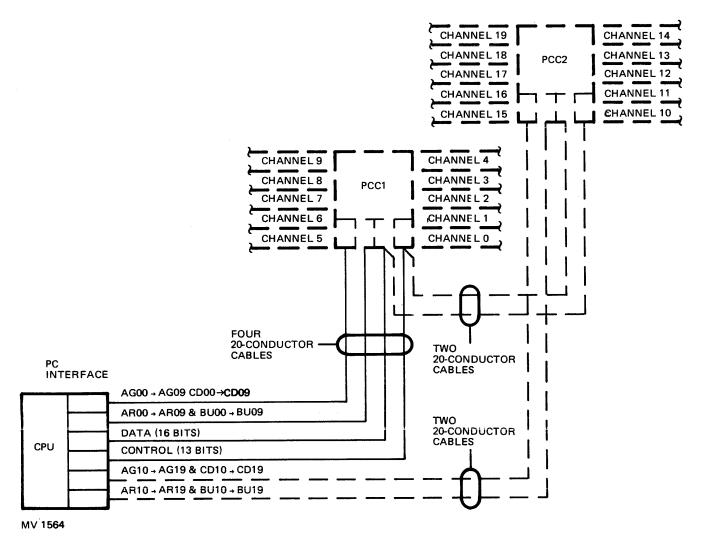

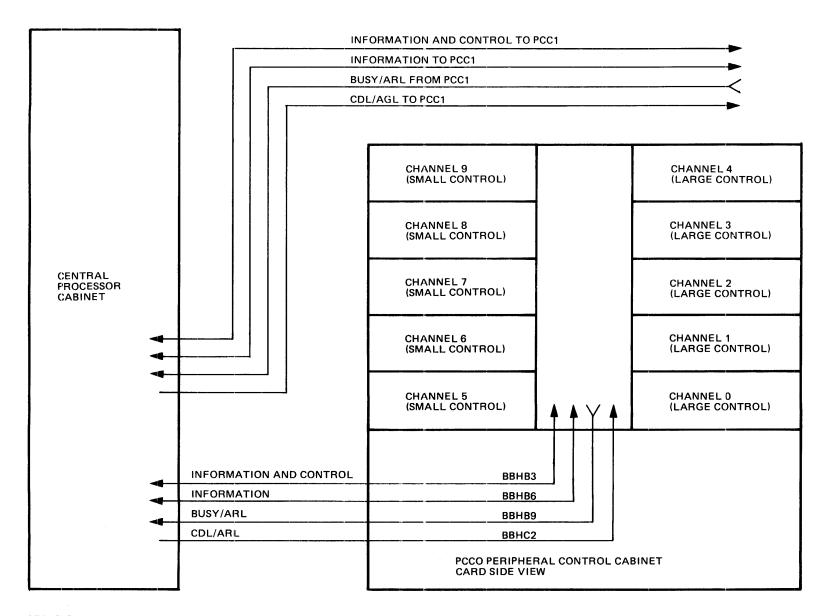

|         | B 6800 Peripheral Control Cabinet           |            |

|         | B 6800 System Peripheral Controls           | 1-18       |

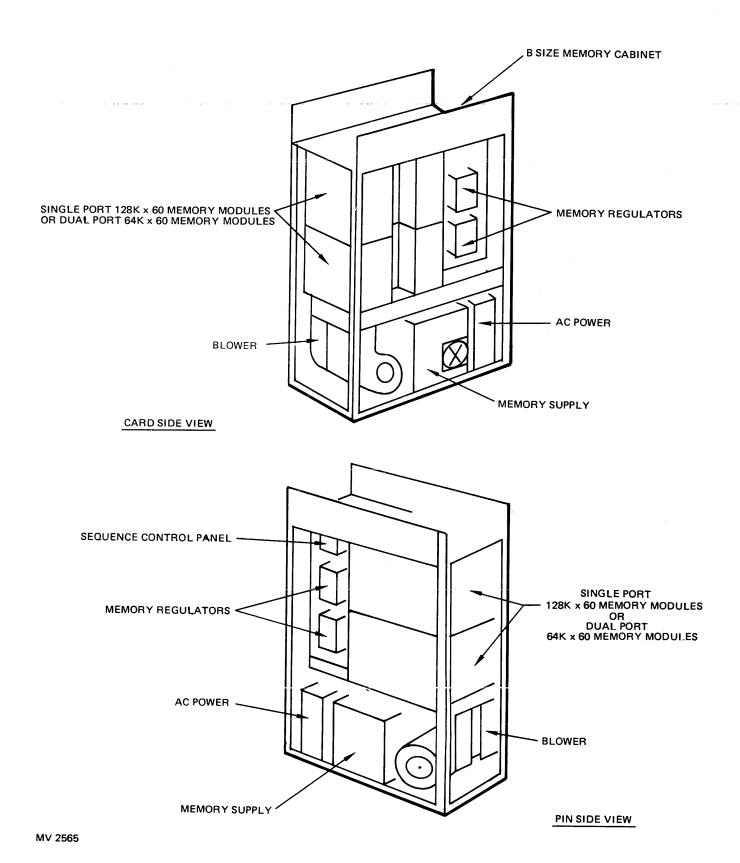

|         | B 6800 Memory Cabinets                      | 1-21       |

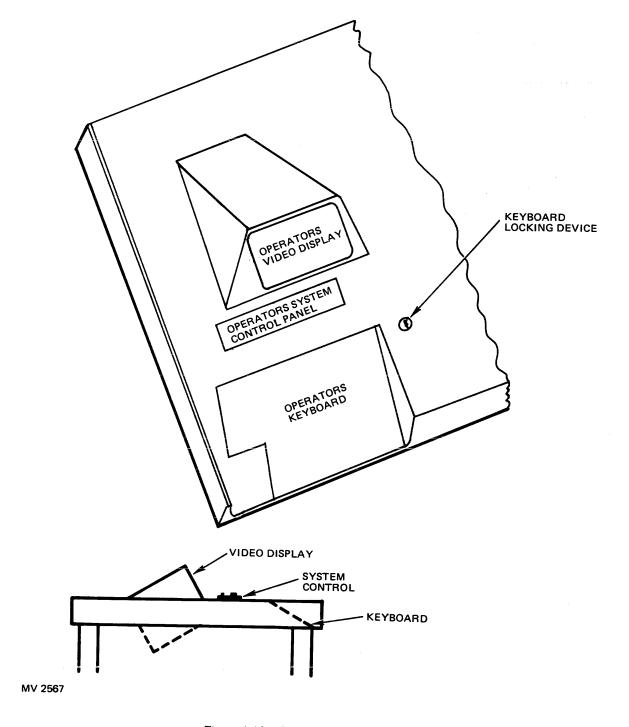

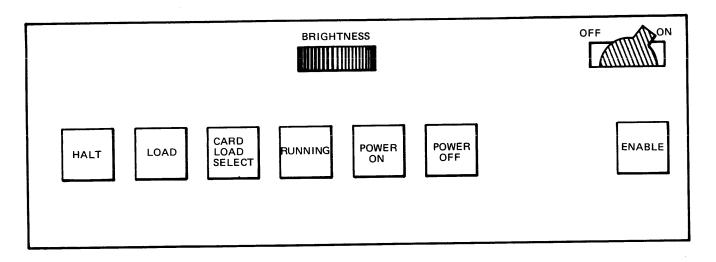

|         | B 6800 Operators Display Console            | 1-25       |

|         | B 6800 Optional Units                       | 1-30       |

| 2       | DATA REPRESENTATION                         | 2-1        |

| _       | General                                     | 2-1        |

|         | Internal Character Codes                    | 2-3        |

|         | Number Bases ,                              | 2-3        |

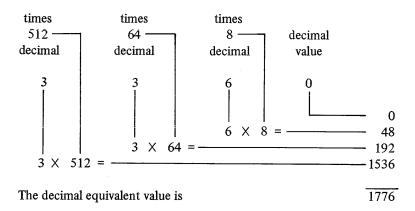

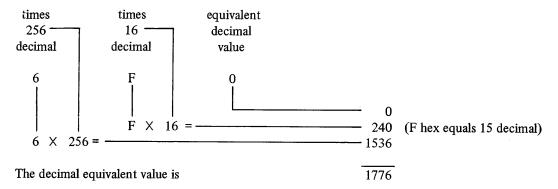

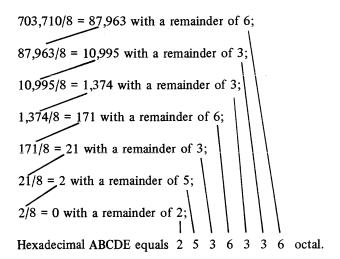

|         | Number Conversion                           | 2-6        |

|         |                                             | 2-6        |

|         | Decimal to Nondecimal                       | 2-6<br>2-6 |

|         | Nondecimal to Decimal                       | 2-0<br>2-7 |

|         | Nondecimal to Nondecimal                    |            |

|         | Word Types and Physical Word Layouts        | 2-10       |

|         | Character Type Words                        | 2-10       |

|         | Operands                                    | 2-10       |

|         | Single Precision Operand                    | 2-12       |

|         | Double Precision Operand                    | 2-13       |

|         | Logical Operands                            | 2-15       |

|         | Data Descriptors                            | 2-15       |

|         | Step Index Words                            | 2-18       |

|         | Software Words                              | 2-19       |

|         | Indirect Reference Words                    | 2-20       |

|         | Program Control Words                       | 2-23       |

|         | Mark Stack Control Words                    | 2-25       |

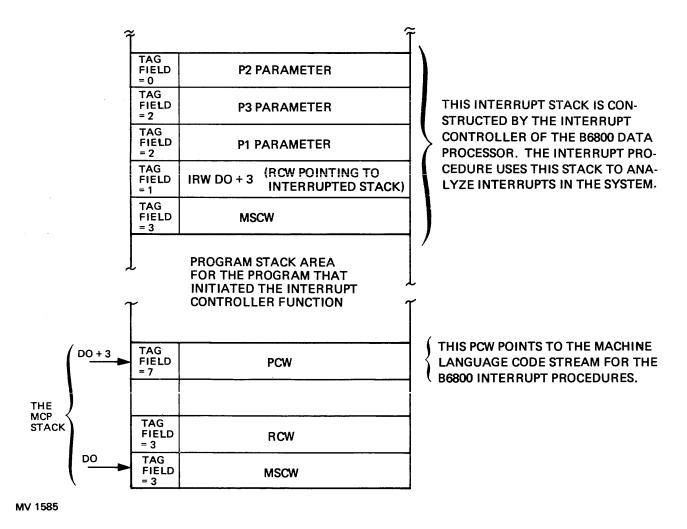

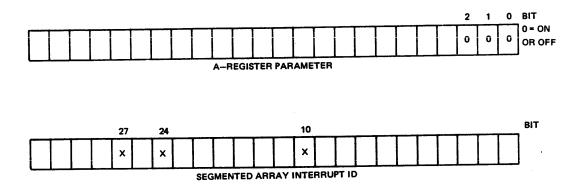

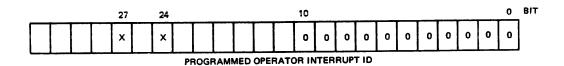

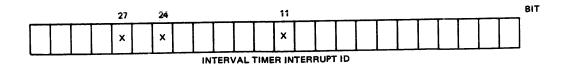

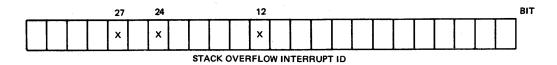

|         | Interrupt Parameter Words                   | 2-26       |

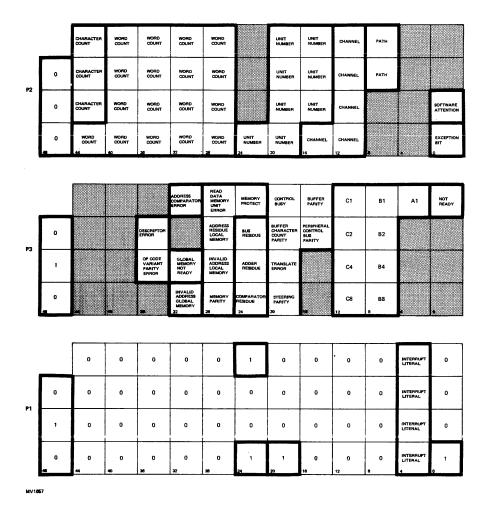

|         | P1 Parameter                                | 2-27       |

|         | P3 Parameter                                | 2-28       |

|         | P2 Parameter                                | 2-28       |

|         | Return Control Words                        | 2-32       |

|         | Program Words (Code Words)                  | 2-34       |

|         | Program Segments and the Segment Descriptor | 2-36       |

|         |                                             | 2-30       |

|         | Top of Stack Control Words                  | 4-31       |

5001290

## TABLE OF CONTENTS (Cont)

| Section |                                                  | Page |

|---------|--------------------------------------------------|------|

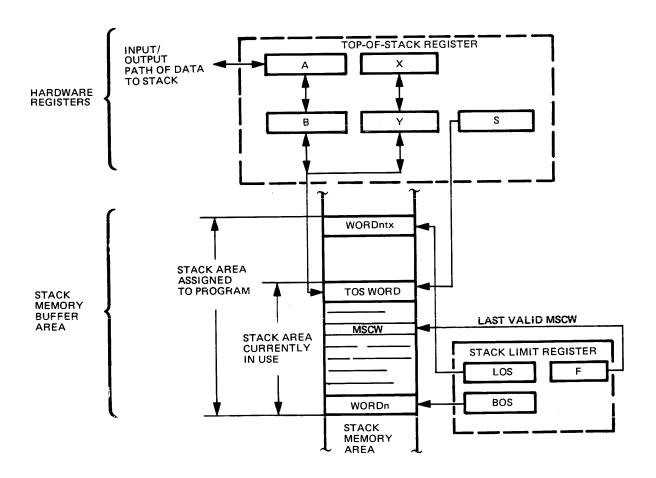

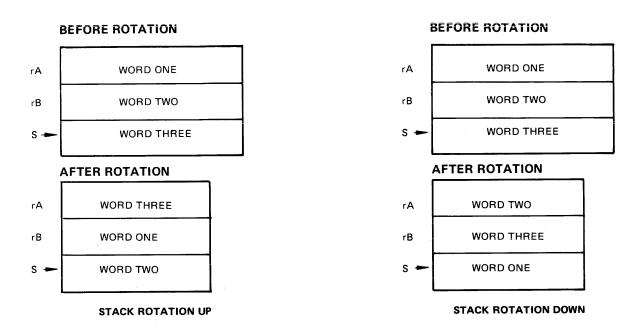

| 3       | STACK AND REVERSE POLISH NOTATION                | 3-1  |

|         | The Stack                                        | 3-1  |

|         | General                                          | 3-1  |

|         | Base and Limit of Stack                          | 3-2  |

|         | Bi-Directional Data Flow in the Stack            | 3-2  |

|         | Stack Push Down                                  | 3-2  |

|         | Stack Push Up                                    | 3-2  |

|         | Double Precision Stack Operation                 | 3-3  |

|         | Top-of-Stack Register Conditions                 | 3-3  |

|         | Stack Adjustments                                | 3-3  |

|         | Data Addressing                                  | 3-5  |

|         | Data Descriptor                                  | 3-5  |

|         | Presence Bit                                     | 3-5  |

|         | Index Bit                                        | 3-5  |

|         | Invalid Index                                    | 3-5  |

|         | Valid Index                                      | 3-5  |

|         | Read-Only Bit                                    | 3-6  |

|         | Copy Bit                                         | 3-6  |

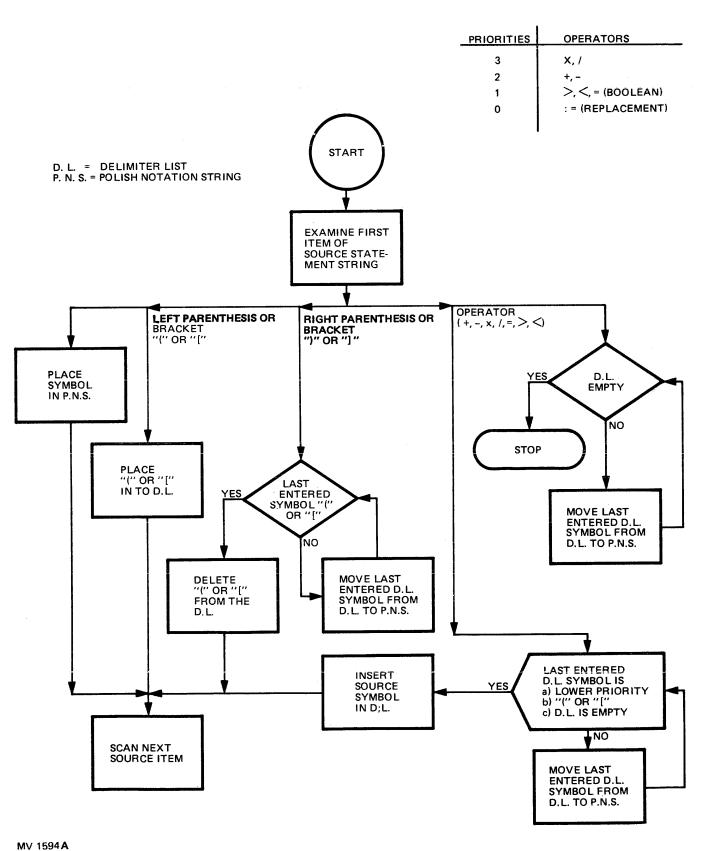

|         | Reverse Polish Notation                          | 3-6  |

|         | General                                          | 3-6  |

|         | Simplified Rules for Generation of Polish String | 3-6  |

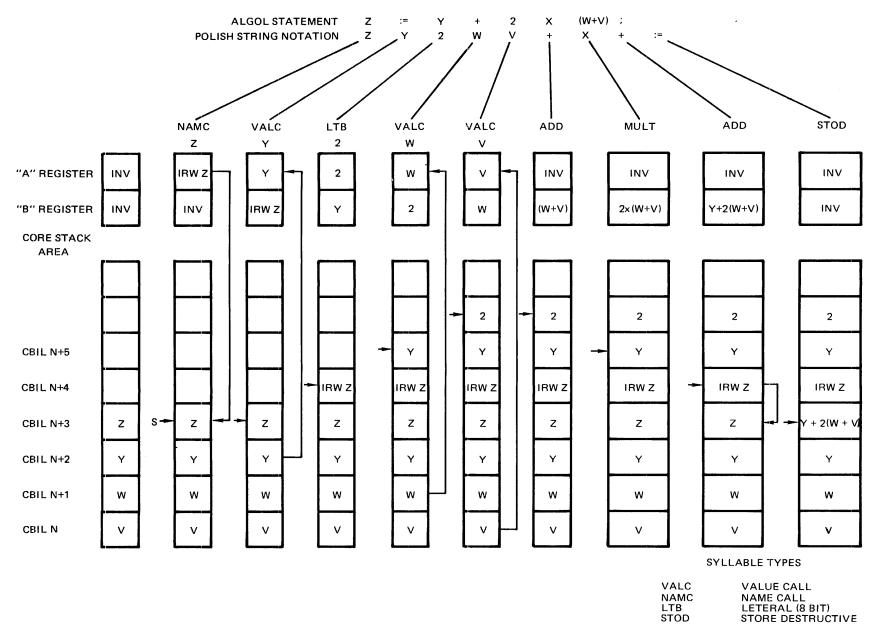

|         | Polish String                                    | 3-8  |

|         | Rules for Evaluating a Polish String             | 3-8  |

|         | Simple Stack Operation                           | 3-8  |

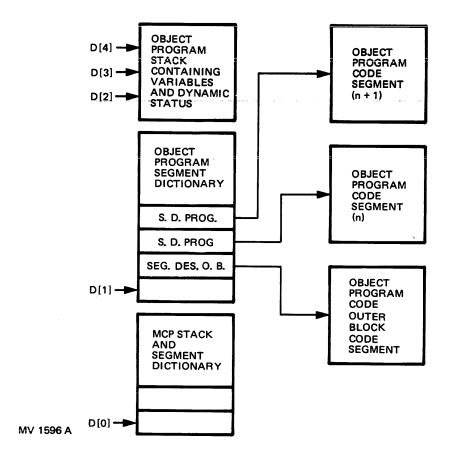

|         | Program Structure in Local Memory                | 3-11 |

|         | Local Memory Area Allocation                     | 3-11 |

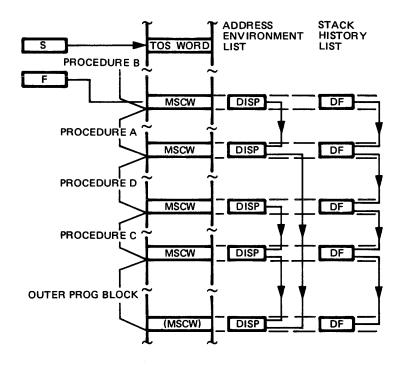

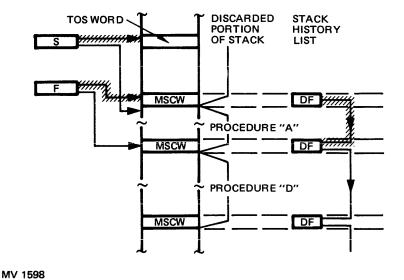

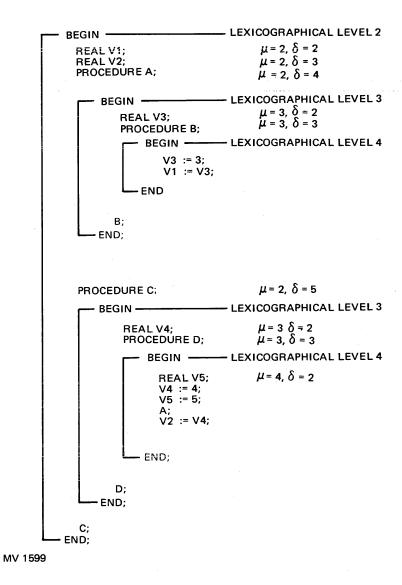

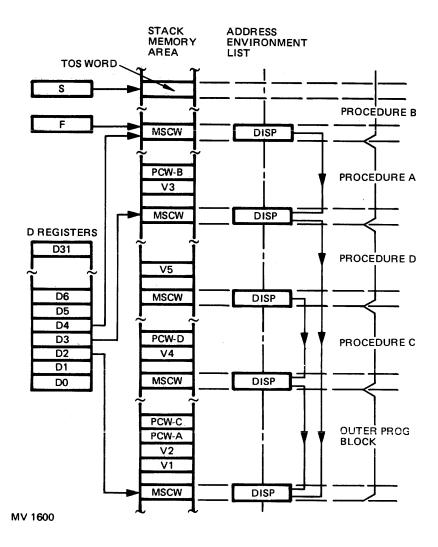

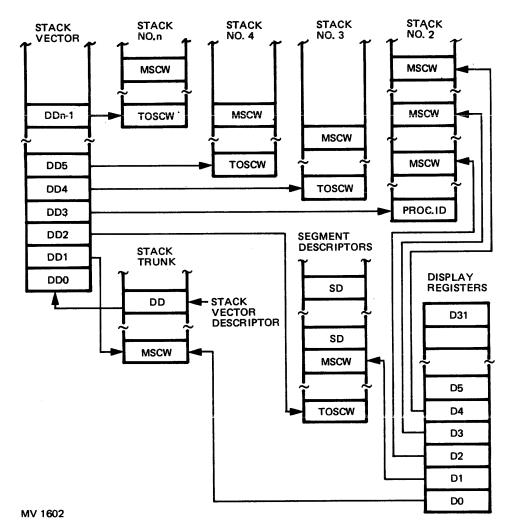

|         | Stack-History and Addressing-Environment Lists   | 3-12 |

|         | Mark Stack Control Word Linkage                  | 3-12 |

|         | Stack Deletion                                   | 3-12 |

|         | Relative-Addressing                              | 3-12 |

|         | Base of Address Level Segment                    | 3-12 |

|         | Absolute Address Conversion                      | 3-13 |

|         | Multiple Variables with Common Address Couples   | 3-13 |

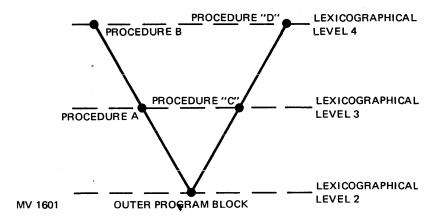

|         | Address Environment Defined                      | 3-15 |

|         | Mark Stack Control Word Linkage                  | 3-15 |

|         | Stack History Summary                            | 3-13 |

|         | Multiple Stacks and Reentrant Code               | 3-17 |

|         | Level Definition                                 | 3-17 |

|         | Reentrance                                       | 3-17 |

|         | Job-Splitting                                    | 3-17 |

|         | Stack Descriptor                                 | 3-17 |

|         | Stack Vector Descriptor                          | 3-17 |

|         | Presence Bit Interrupt                           | 3-18 |

|         |                                                  | 2.10 |

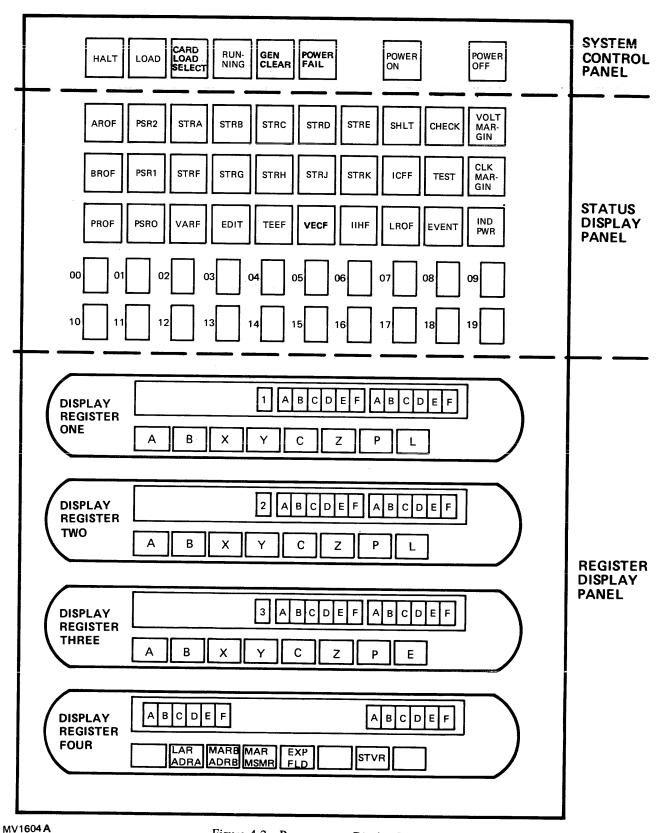

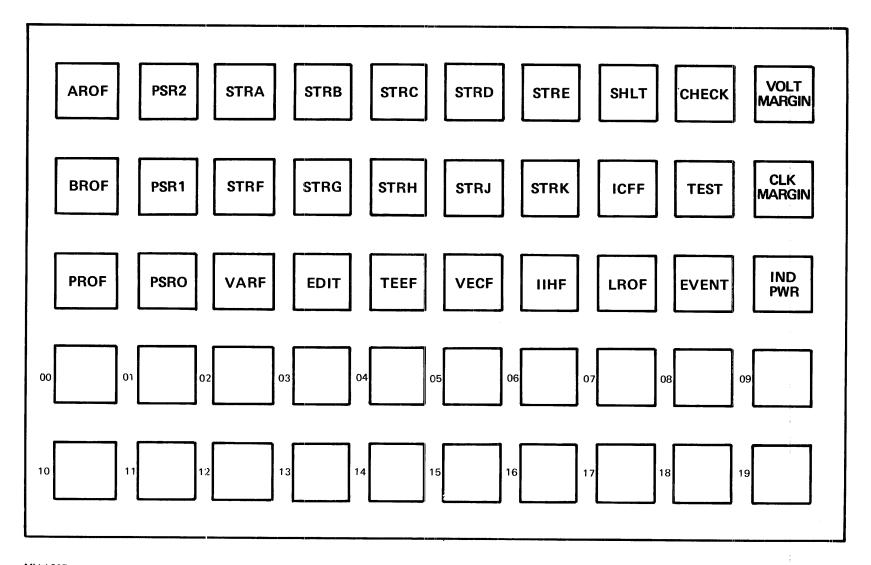

| 4       | MAJOR REGISTERS AND CONTROL PANELS               | 4-1  |

|         | Display Panels                                   | 4-1  |

|         | Programmers Display Panel                        | 4-1  |

|         | System Control Panel                             | 4-1  |

|         | Status Display Panel                             | 4-4  |

## TABLE OF CONTENTS (Cont)

| Pag        |

|------------|

|            |

| 4-1        |

| 4-1        |

| 4-1        |

| 4-2        |

| 4-2        |

| 4-2        |

| 4-2        |

| 4-2        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-3        |

| 4-4        |

| 4-4<br>4-4 |

| 4-4<br>4-4 |

| 4-4        |

| 4-4<br>4-4 |

| 4-4        |

| 4-4        |

| 4-4        |

| 4-4<br>4-4 |

| 4-4<br>4-4 |

|            |

| 4-4        |

| 4-5        |

| 4-5        |

| 5-         |

| 5-         |

| 5-         |

| 5.         |

| 5.         |

| 5.         |

| 5.         |

| . 5        |

| 5          |

| 5-         |

| 5.         |

| 5.         |

| 5.         |

| 5-1        |

|            |

5001290 vii

## **TABLE OF CONTENTS (Cont)**

| Section |                                                               | Page         |

|---------|---------------------------------------------------------------|--------------|

| 5       | SYSTEM CONCEPT (Cont)                                         |              |

|         | Arithmetic Controller                                         | 5-10         |

|         | Exponent and Mantissa Adders                                  | 5-10         |

|         | Interrupt Controller                                          | 5-10         |

|         | Interrupt Parameters                                          | 5-10         |

|         | Syllable Dependent Interrupts                                 | 5-14         |

|         | Memory Protect Interrupt                                      | 5-15         |

|         | Invalid Operand Interrupt                                     | 5-15         |

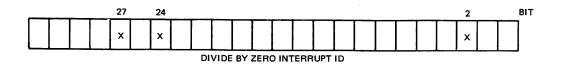

|         | Divide by Zero Interrupt                                      | 5-15         |

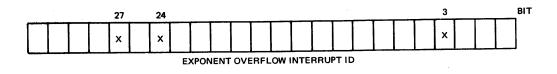

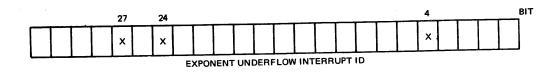

|         | Exponent Overflow and Underflow Interrupt                     | 5-16         |

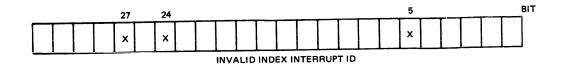

|         | Invalid Index Interrupt                                       | 5-16         |

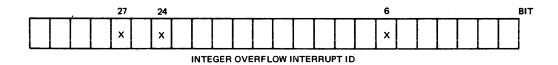

|         | Integer Overflow Interrupt                                    | 5-17         |

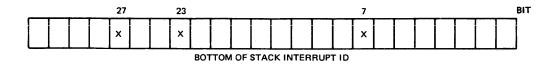

|         | Bottom of Stack Interrupt                                     | 5-17         |

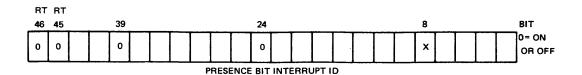

|         | Presence Bit Interrupt                                        | 5-17         |

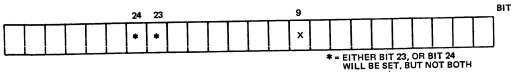

|         | Special Consideration-Presence Bit Interrupts                 | 5-18         |

|         |                                                               | 5-18         |

|         | Data-Dependent Presence Bit Interrupt                         | 5-18         |

|         | Procedure-Dependent Presence Bit Interrupt                    | 5-18         |

|         | Program Restart                                               | 5-18         |

|         | Sequence Error Interrupt                                      | 5-10<br>5-19 |

|         | Segmented Array Interrupt                                     | 5-20         |

|         | Programmed Operator Interrupt                                 |              |

|         | Interval Timer Interrupt                                      | 5-20<br>5-21 |

|         | Stack Overflow Interrupt                                      | 5-21<br>5-21 |

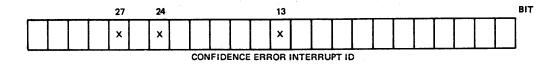

|         | Confidence Error Interrupt                                    | 5-21<br>5-21 |

|         | Operator Independent Interrupts                               |              |

|         | External Interrupts                                           | 5-21         |

|         | I/O Finish, Data Communications, and Status Change Interrupts | 5-22         |

|         | Alarm Interrupts                                              | 5-22         |

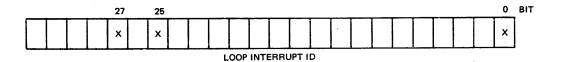

|         | Loop Interrupts                                               | 5-23         |

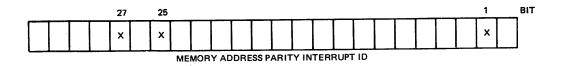

|         | Memory Address Interrupts                                     | 5-23         |

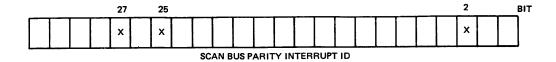

|         | Scan Bus Parity Interrupts                                    | 5-23         |

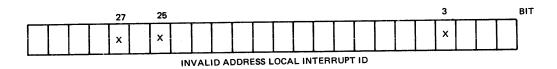

|         | Invalid Address-Local Interrupts                              | 5-24         |

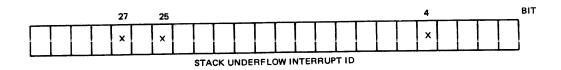

|         | Stack Underflow Interrupts                                    | 5-24         |

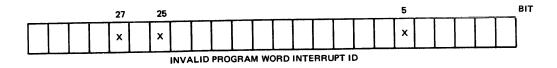

|         | Invalid Program Word Interrupts                               | 5-24         |

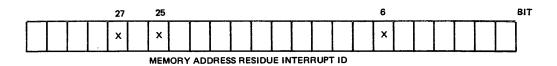

|         | Memory Address Residue Interrupts                             | 5-24         |

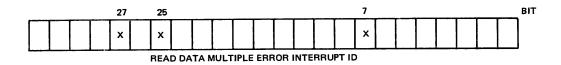

|         | Read Data Multiple Error Interrupts                           | 5-25         |

|         | Invalid Address-Global Interrupts                             | 5-25         |

|         | Global Memory Not Ready Interrupts                            | 5-25         |

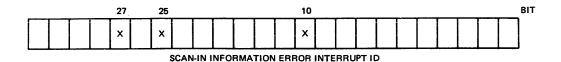

|         | Scan-In Information Error Interrupts                          | 5-25         |

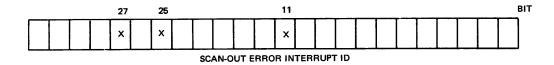

|         | Scan-Out Error Interrupts                                     | 5-26         |

|         | General Control Interrupts                                    | 5-26         |

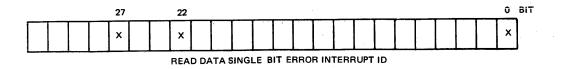

|         | Read Data Single Error Interrupts                             | 5-26         |

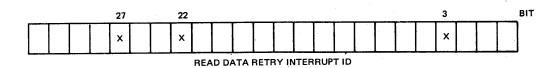

|         | Read Data Retry Interrupts                                    | 5-27         |

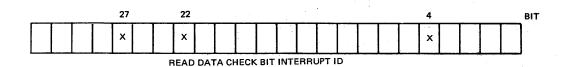

|         | Read Data Check Bit Interrupts                                | 5-27         |

|         | Address Retry Interrupts                                      | 5-27         |

|         | Hardware Interrupts                                           | 5-28         |

## TABLE OF CONTENTS (Cont)

| Section |                                                           | Page |

|---------|-----------------------------------------------------------|------|

| 5       | SYSTEM CONCEPT (Cont)                                     |      |

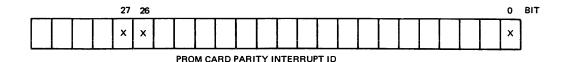

|         | PROM Card Parity Interrupts                               | 5-28 |

|         | RAM Card Parity Interrupts                                | 5-28 |

|         | Bus Residue Interrupts                                    | 5-29 |

|         | Adder Residue Interrupts                                  | 5-29 |

|         | Compare Residue Interrupts                                | 5-29 |

|         | String Operators                                          | 5-30 |

|         | Memory Controller                                         | 5-30 |

|         | Control State/Normal State                                | 5-31 |

|         | Multiplexor Function                                      | 5-31 |

|         | Data Processor Scan-In Functions to the Multiplexor       | 5-31 |

|         | Data Processor Scan-Out Functions to the Multiplexor      | 5-33 |

|         | Data Processor Scan-Out Functions to External Subsystems  | 5-35 |

|         | Multiplexor Scan-In Functions                             | 5-35 |

|         | Interrogate Peripheral Status Multiplexor Function        | 5-35 |

|         | Interrogate IO Path Multiplexor Function                  | 5-35 |

|         | Read Time of Day Multiplexor Function                     | 5-37 |

|         | Read Interrupt Register Multiplexor Function              | 5-38 |

|         | Interrogate Unit Type Multiplexor Function                | 5-39 |

|         | Interrogate IO Path Address Multiplexor Function          | 5-39 |

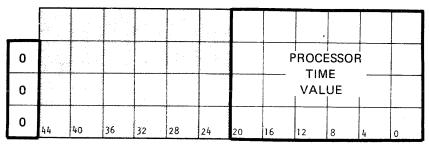

|         | Read Processor Time Counter Multiplexor Function          | 5-42 |

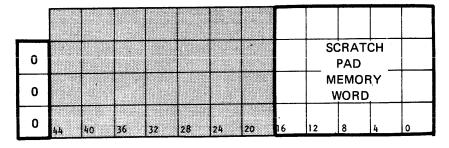

|         | Read Scratch Pad Word Multiplexor Function                | 5-43 |

|         | Interrogate IO Path Address Override Multiplexor Function | 5-45 |

|         | Read Interrupt Literal Multiplexor Function               | 5-45 |

|         | Read Interrupt Mask Multiplexor Function                  | 5-45 |

|         | Multiplexor Scan-Out Functions                            | 5-45 |

|         | Set Time of Day Multiplexor Function                      | 5-46 |

|         | Set Interrupt Mask Multiplexor Function                   | 5-46 |

|         | Set Pseudo Busy Multiplexor Function                      | 5-46 |

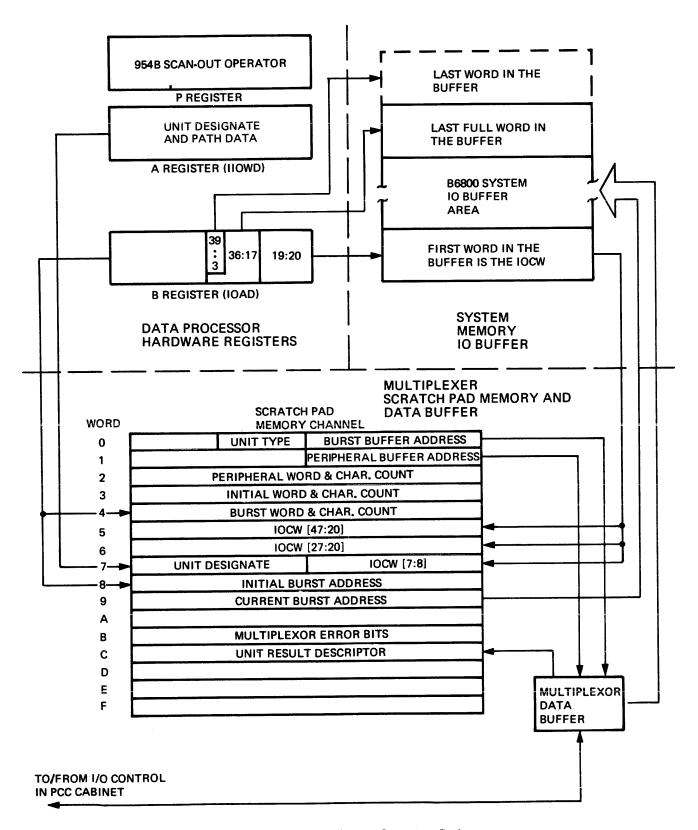

|         | Software Aspects of IO Operations in the B 6800 System    | 5-46 |

|         | Ready Status                                              | 5-50 |

|         | Status Change                                             | 5-52 |

|         | Input Output Operations                                   | 5-53 |

|         | IO Device Numbering System                                | 5-53 |

|         | Initiate Input Output Operation                           | 5-54 |

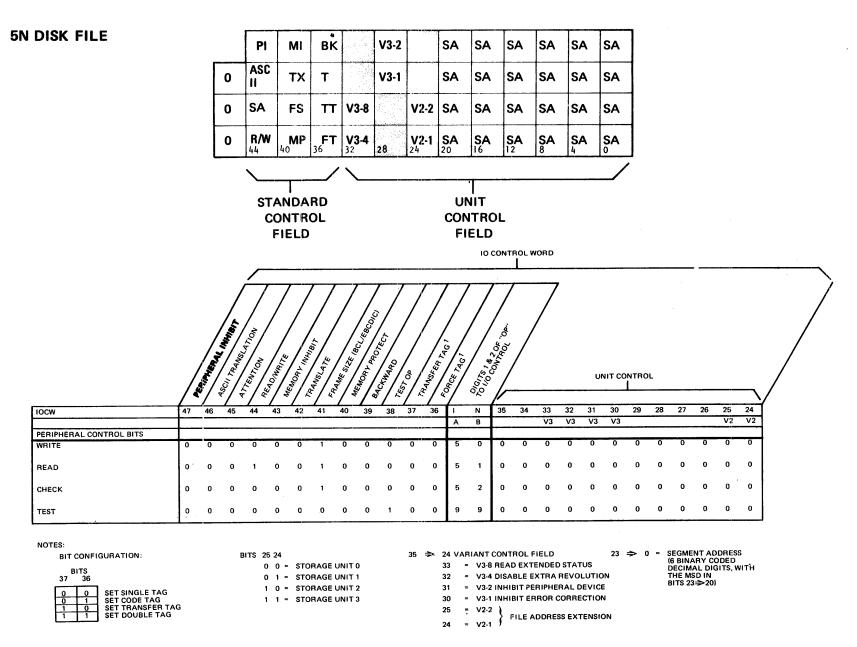

|         | IIOWD Format                                              | 5-56 |

|         | IOAD Format                                               | 5-56 |

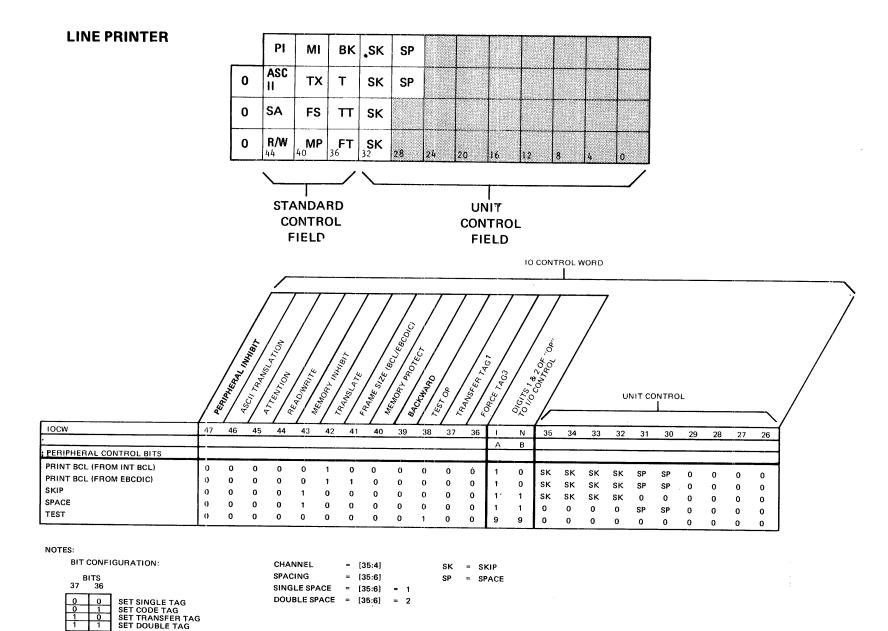

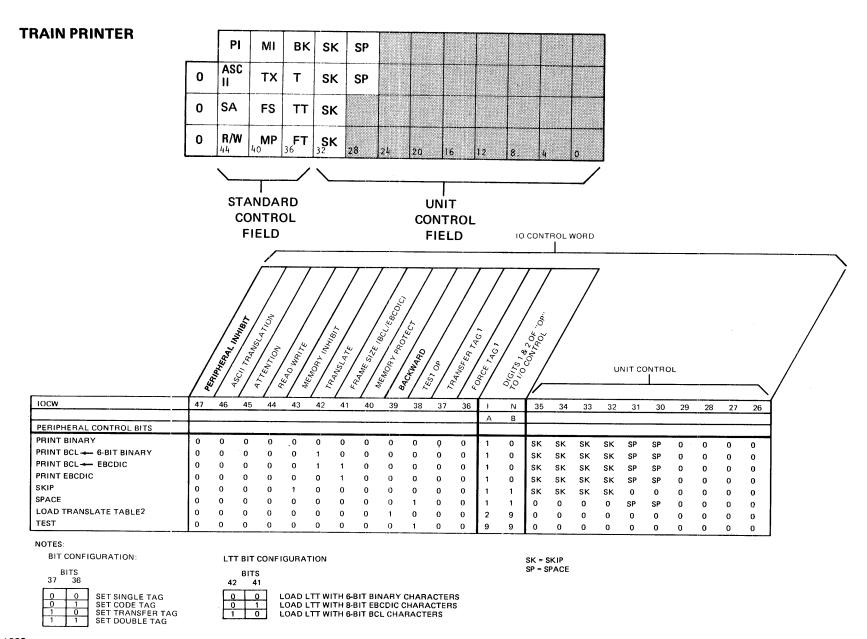

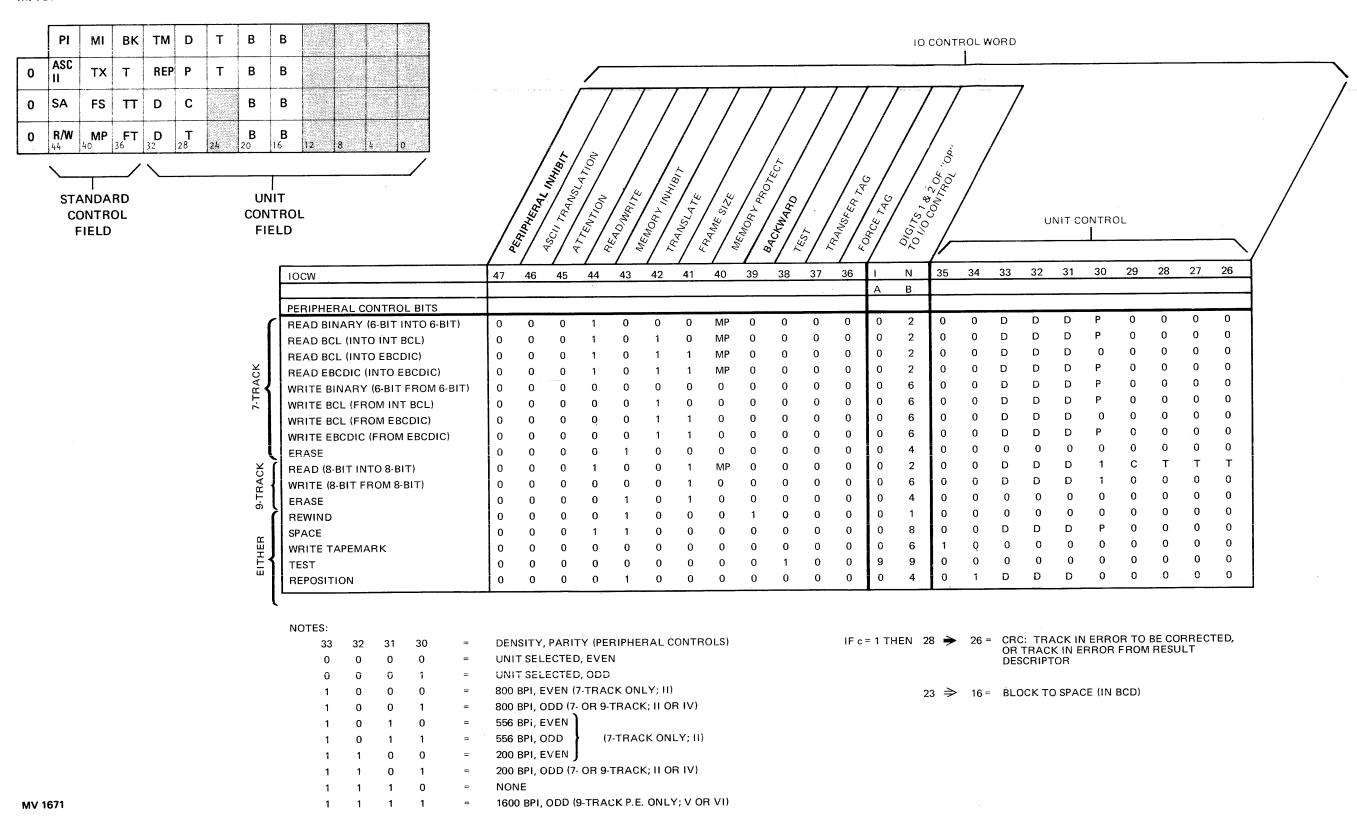

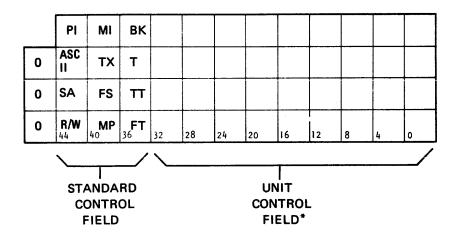

|         | IOCW Format                                               | 5-56 |

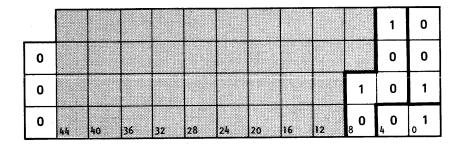

|         | Scratch Pad Memory                                        | 5-58 |

|         | Data Buffer Logic                                         | 5-60 |

|         | OP Code and Variant Character Generator                   | 5-61 |

|         | Status Vector Control Circuits                            | 5-62 |

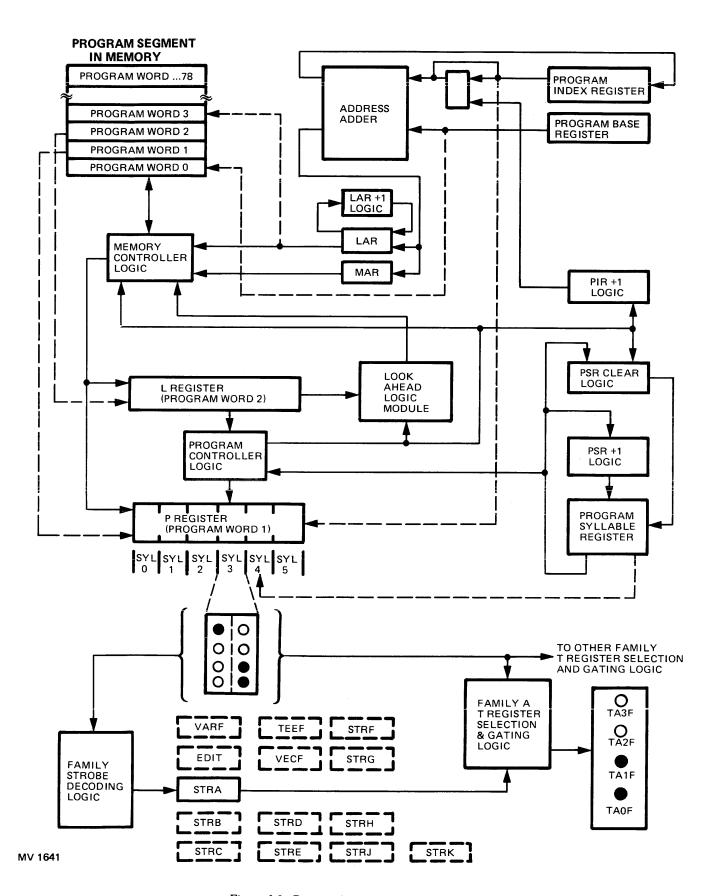

|         | Memory Organization                                       | 5-63 |

|         | System Memory Interface                                   | 5-64 |

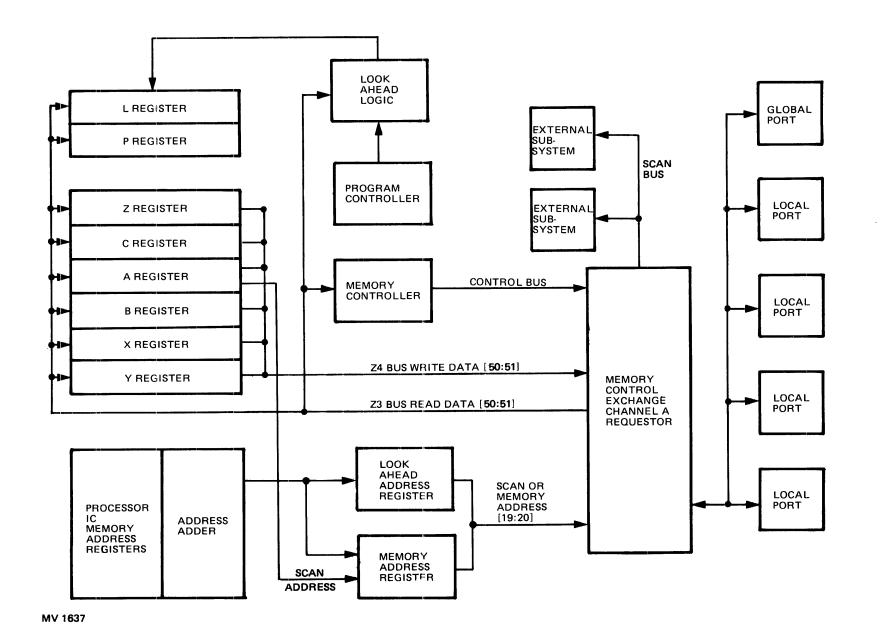

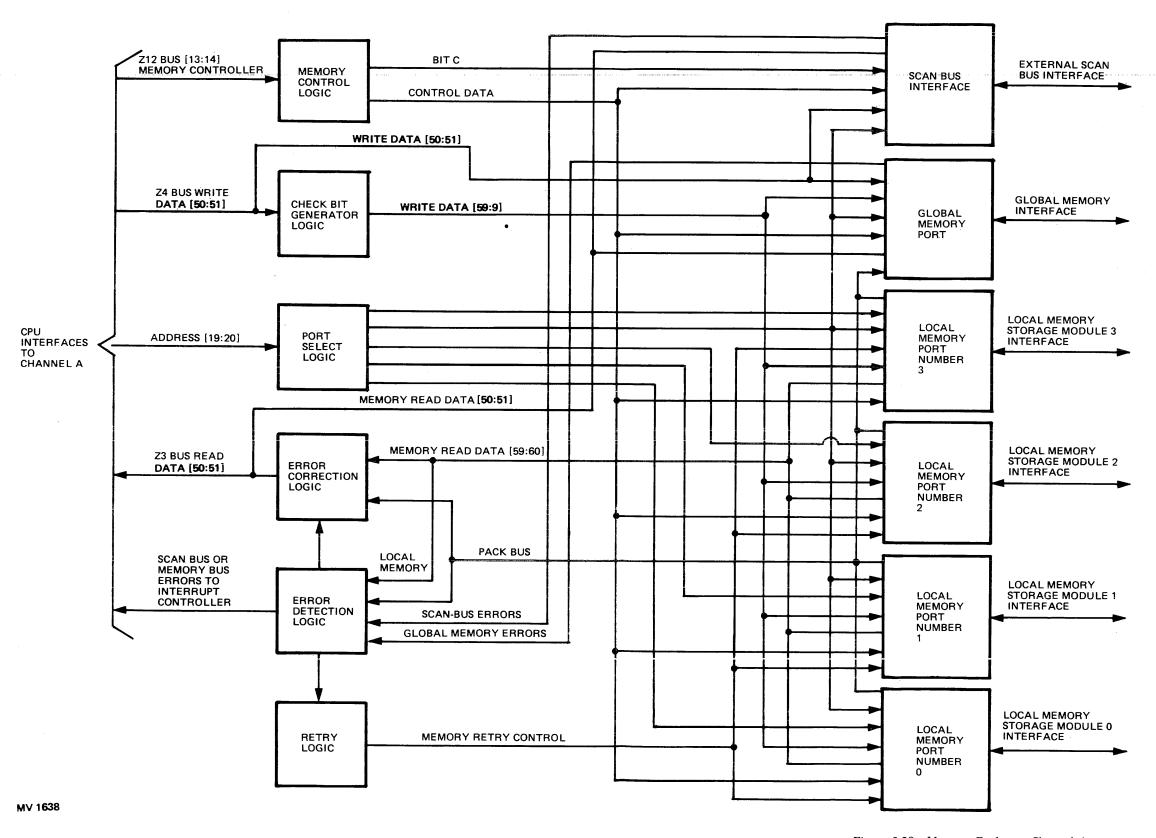

|         | Channel A Memory Requestor                                | 5-64 |

|         | Memory Error Detection and Correction                     | 5-69 |

|         | <del>-</del>                                              |      |

5001290 ix

#### TABLE OF CONTENTS (Cont)

| Memory Retry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Section |                                                 | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------|------|

| Global Memory   S-71     Scan Bus Operations   S-72     Channel B Memory Requestor   S-72     Memory Storage Unit Port Interface   S-72     Local Memory Port Interface Control Logic   S-74     Scan Bus Port Interface Control Logic   S-74     Scan Bus Port Interface Control Logic   S-75     Memory Tester Logic   S-76     General   S-76     General   S-76     General   S-76     Pand T Registers   S-76     Pand T Registers   S-76     Operation Types   S-76     Pand T Registers   S-76     Operation Types   S-76     Value Call   S-76     Operation Types   S-76     Operators   S-77     Operators   S-77     PRIMARY MODE OPERATORS   S-77     General   S-77     Add (ADD) 80   S-77     Add (ADD) 80   S-77     Subtract (SUBT) 81   S-72     Multiply (MULT) 82   S-72     Extended Multiply (MULT) 84   S-72     Divide (DIVD) 83   S-73     Integer Divide (RDIV) 85   S-73     Integer Divide (RDIV) 85   S-73     Integerize, Truncated (NTIA) 86   S-74     Set to Single-Precision, Truncated (SNGT) CC   S-74     Set to Single-Precision, Truncated (SNGT) CC   S-75     Set to Single-Precision, Truncated (SNGT) CC   S-75     Logical Operators   S-75     Capter Than Operators   S-75     Greater Than Operators   S-75     Greater Than Operators   S-75     Greater Than Operators   S-75     Capter Than Operators   S-75     Capter Stan Operators   S-75     Capter Than Opera   | 5       | SYSTEM CONCEPT (Cont)                           |      |

| Global Memory   S-71     Scan Bus Operations   S-71     Channel B Memory Requestor   S-72     Memory Storage Unit Port Interface   S-72     Local Memory Port Interface Control Logic   S-74     Scan Bus Port Interface Control Logic   S-74     Scan Bus Port Interface Control Logic   S-75     Memory Tester Logic   S-75     Memory Tester Logic   S-76     PROGRAM OPERATORS   G-1     General   G-1     Syllable Addressing and Syllable Identification   G-1     Syllable Format and Addressing   G-1     P and T Registers   G-1     Operation Types   G-2     Name Call   G-2     Value Call   G-2     Value Call   G-4     Operators   G-7     PRIMARY MODE OPERATORS   T-1     Arithmetic Operators   T-1     Arithmetic Operators   T-1     Add (ADD) 80   T-1     Auditply (MULT) 82   T-2     Extended Multiply (MULT) 82   T-2     Extended Multiply (MULT) 84   T-2     Integer Divide (DIV) 83   T-2     Integer Divide (DIV) 84   T-3     Remainder Divide (RDIV) 85   T-3     Integerize, Truncated (NTIA) 86   T-3     Integerize, Truncated (NTIA) 86   T-3     Integerize, Truncated (NTIA) 86   T-3     Logical Operators   T-4     Set to Single-Precision, Truncated (SNGT) CC   T-4     Set to Single-Precision (XTRD) CE   T-5     Logical Operators   T-5     Logical Operators   T-5     Logical Operators   T-5     Logical Operators   T-5     Cogleal No (LAND) 90   T-5     Logical Operators   T-5     Cogleal No (LEON) 91   T-5     Cogleal No (LEON) 92   T-5     Cogleal No (LEON) 93   T-5     Cogleal No (LEON) 94   T-5     Cogleal No (LEON) 95   T-5     Cogleal No (LEON) 95   T-5     Cogleal No (LEON   |         | Memory Retry                                    | 5-71 |

| Scan Bus Operations   5-71     Channel B Memory Requestor   5-72     Memory Storage Unit Port Interface   5-72     Local Memory Port Interface Control Logic   5-74     Scan Bus Port Interface Control Logic   5-75     Memory Tester Logic   5-75     Memory Tester Logic   5-76     PROGRAM OPERATORS   6-1     Syllable Addressing and Syllable Identification   6-1     Syllable Format and Addressing   6-1     Pand T Registers   6-1     Operation Types   6-2     Name Call   6-2     Value Call   6-2     Operation Types   6-2     Name Call   6-2     Operation Types   6-7     PRIMARY MODE OPERATORS   7-1     Arithmetic Operators   7-1     Arithmetic Operators   7-1     Add (ADD) 80   7-1     Subtract (SUBT) 81   7-2     Multiply (MULX) 8F   7-2     Extended Multiply (MULX) 8F   7-2     Extended Multiply (MULX) 8F   7-2     Divide (DIVD) 83   7-3     Integer Divide (RDIV) 85   7-3     Integerize, Rounded (NTGR) 87   7-4     Set to Single-Precision, Tuncated (SNGT) CC   7-5     Logical Operators   7-5     Logical Operators   7-5     Logical Operators   7-5     Logical Departor of Tuncated (SNGT) CC   7-6     Set to Single-Precision, Tuncated (SNGT) CC   7-7     Set to Single-Precision, Rounded (SNGT) CC   7-7     Set to Single-Precision, Tuncated (SNGT) CC   7-7     Set to Single-   |         |                                                 | 5-71 |

| Channel B Memory Requestor  Memory Storage Unit Port Interface Local Memory Port Interface Control Logic S-72  Local Memory Port Interface Control Logic S-75  Scan Bus Port Interface Control Logic S-75  Memory Tester Logic S-76  6 PROGRAM OPERATORS 6-1  General Syllable Addressing and Syllable Identification General Syllable Format and Addressing General P and T Registers Operation Types G-2  Name Call Value Call Operators General Arithmetic Operators Add (ADD) 80 T-1  Add (ADD) 80 T-1  Add (ADD) 80 T-1  Subtract (SUBT) 81  Multiply (MULT) 82 Extended Multiply (MULX) 8F Divide (DIV) 83 Integer Divide (DIV) 83 Integer Divide (DIV) 85 Integer Divide (DIV) 85 Integer Divide (DIV) 85 Integerize, Rounded (NTGR) 87 Type-Transfer Operators Set to Single-Precision, Truncated (SNGT) CC Set to Single-Precision, Rounded (SNGT) CC Set to Greater Than or Equal (CREQ) 93 Relational Operators Greater Than or Equal (CREQ) 88 Less Than or Equal (CREQ) 88 Less Than or Equal (LESQ) 88 Less Than or Equal (LESQ) 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                 | 5-71 |

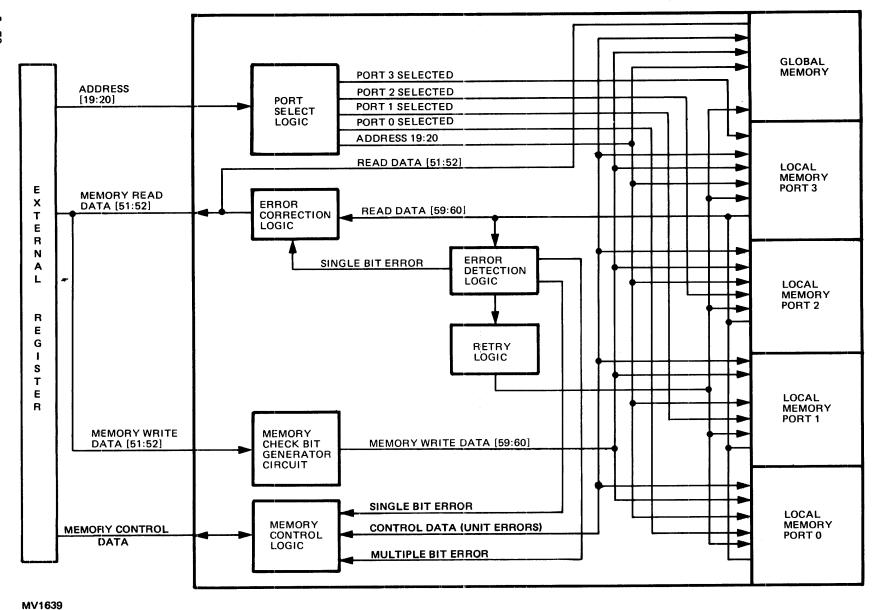

| Memory Storage Unit Port Interface   5-72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                                 | 5-72 |

| Local Memory Port Interface Control Logic   5.74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                 | 5-72 |

| Scan Bus Port Interface Control Logic   5-75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                                                 | 5-74 |

| Memory Tester Logic   S-76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                                                 | 5-75 |

| General   Syllable Addressing and Syllable Identification   Syllable Format and Addressing   G-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                 | 5-76 |

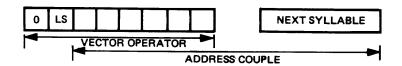

| Syllable Addressing and Syllable Identification       6-1         Syllable Format and Addressing       6-1         P and T Registers       6-1         Operation Types       6-2         Name Call       6-2         Value Call       6-4         Operators       6-7         7 PRIMARY MODE OPERATORS       7-1         General       7-1         Arithmetic Operators       7-1         Add (ADD) 80       7-1         Subtract (SUBT) 81       7-2         Multiply (MULT) 82       7-2         Extended Multiply (MULX) 8F       7-2         Divide (DIVD) 83       7-2         Integer Divide (IDIV) 84       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGT) CC       7-4         Set to Single-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical Operators       7-5         Logical Precision (XTND) 90       7-5         Logical Regate (LNOT) 92       7-5         Logical Equivalence (LECV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6       | PROGRAM OPERATORS                               |      |

| Syllable Format and Addressing   6-1     P and T Registers   6-1     Operation Types   6-2     Name Call   6-2     Value Call   6-4     Operators   6-7     PRIMARY MODE OPERATORS   7-1     General   7-1     Arithmetic Operators   7-1     Add (ADD) 80   7-1     Subtract (SUBT) 81   7-2     Multiply (MULT) 82   7-2     Extended Multiply (MULX) 8F   7-2     Divide (DIVD) 83   7-2     Integer Divide (RDIV) 84   7-3     Remainder Divide (RDIV) 85   7-3     Integerize, Truncated (NTIA) 86   7-3     Integerize, Rounded (NTGR) 87   7-4     Set to Single-Precision, Truncated (SNGT) CC   7-4     Set to Single-Precision, Rounded (SNGT) CC   7-4     Set to Double-Precision (XTND) CE   7-5     Logical Operators   7-5     Logical Pagate (LNOT) 92   7-5     Logical Regate (LNOT) 92   7-5     Logical Regate (LNOT) 92   7-5     Greater Than (GRTR) 8A   7-6     Greater Than or Equal (GREQ) 89   7-7     Euss Than or Equal (LSEQ) 8B   7-7     Less Than or Equal (LSEQ) 8B   7-7     Less Than or LESS) 88   7-7     Today Carlon of    |         | General                                         | -    |

| P and T Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | Syllable Addressing and Syllable Identification |      |

| Operation Types   6-2     Name Call   6-2     Value Call   6-4     Operators   6-7     PRIMARY MODE OPERATORS   7-1     General   7-1     Arithmetic Operators   7-1     Add (ADD) 80   7-1     Subtract (SUBT) 81   7-2     Multiply (MULT) 82   7-2     Extended Multiply (MULX) 8F   7-2     Divide (DIVD) 83   7-2     Integer Divide (IDIV) 84   7-3     Remainder Divide (RDIV) 85   7-3     Integerize, Truncated (NTIA) 86   7-3     Integerize, Rounded (NTGR) 87   7-4     Type-Transfer Operators   7-4     Set to Single-Precision, Rounded (SNGT) CC   7-4     Set to Single-Precision (XTND) CE   7-5     Logical Operators   7-5     Logical AND (LAND) 90   7-5     Logical Negate (LNOT) 92   7-5     Logical Negate (LNOT) 92   7-5     Logical Regate (LNOT) 92   7-5     Coreater Than (GRTR) 8A   7-6     Greater Than or Equal (GREQ) 89   7-7     Less Than or Equal (LSEQ) 8B   7-7     Less Than or Equal (LSEQ) 8B   7-7     Less Than (LESS) 88   7-7     Less Than (LESS   |         | Syllable Format and Addressing                  |      |

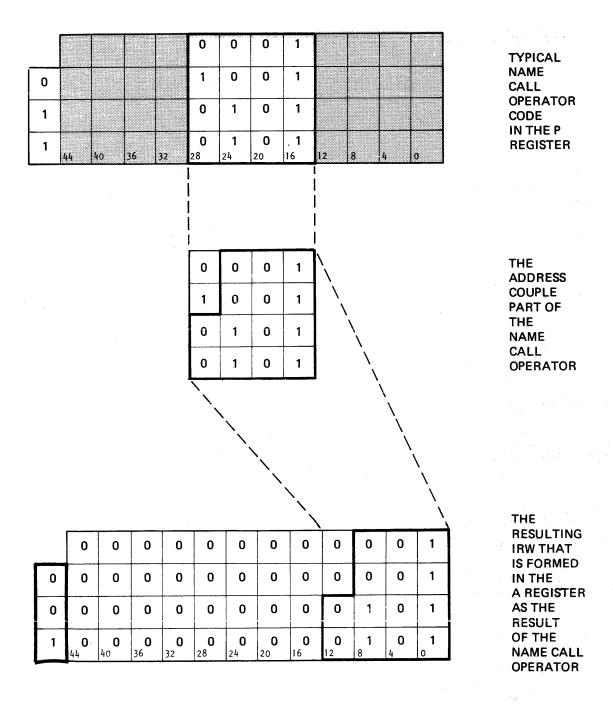

| Name Call   6-2   Value Call   6-4   Operators   6-7   PRIMARY MODE OPERATORS   7-1   General   7-1   Arithmetic Operators   7-1   Add (ADD) 80   7-1   Subtract (SUBT) 81   7-2   Multiply (MULT) 82   7-2   Extended Multiply (MULX) 8F   7-2   Divide (DIVD) 83   7-2   Integer Divide (IDIV) 84   7-3   Integer Divide (IDIV) 85   7-3   Integerize, Truncated (NTIA) 86   7-3   Integerize, Rounded (NTGR) 87   7-4   Set to Single-Precision, Truncated (SNGT) CC   7-4   Set to Single-Precision, Rounded (SNGL) CD   7-5   Logical Operators   7-5   Logical Negate (LNOT) 92   7-5   Logical Regate (LNOT) 92   7-5   Coreater Than (GRTR) 8A   7-6   Greater Than or Equal (GREQ) 89   7-7   Euss Than or Equal (LSEQ) 8B   7-7   Less Than (LESS) 88   7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | P and T Registers                               |      |

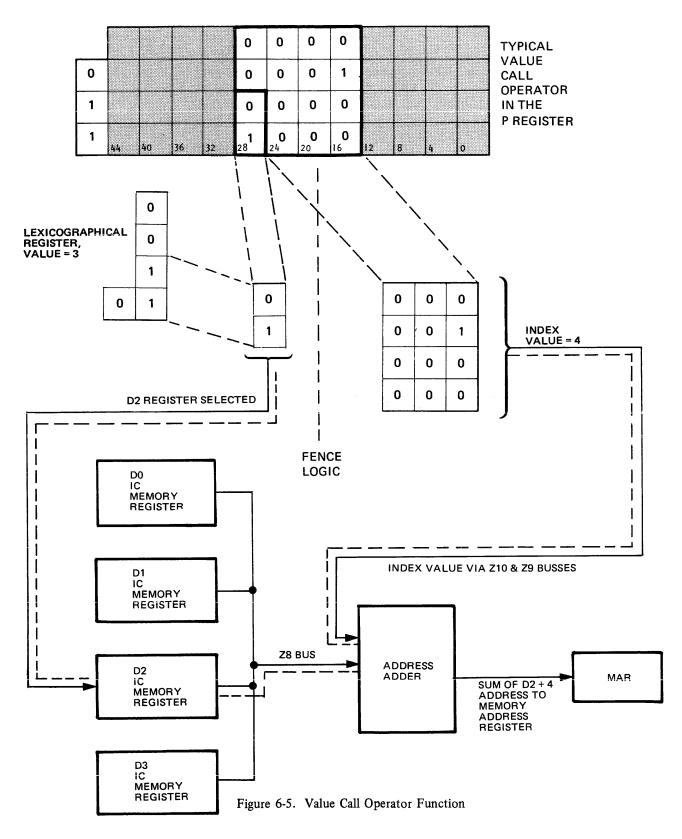

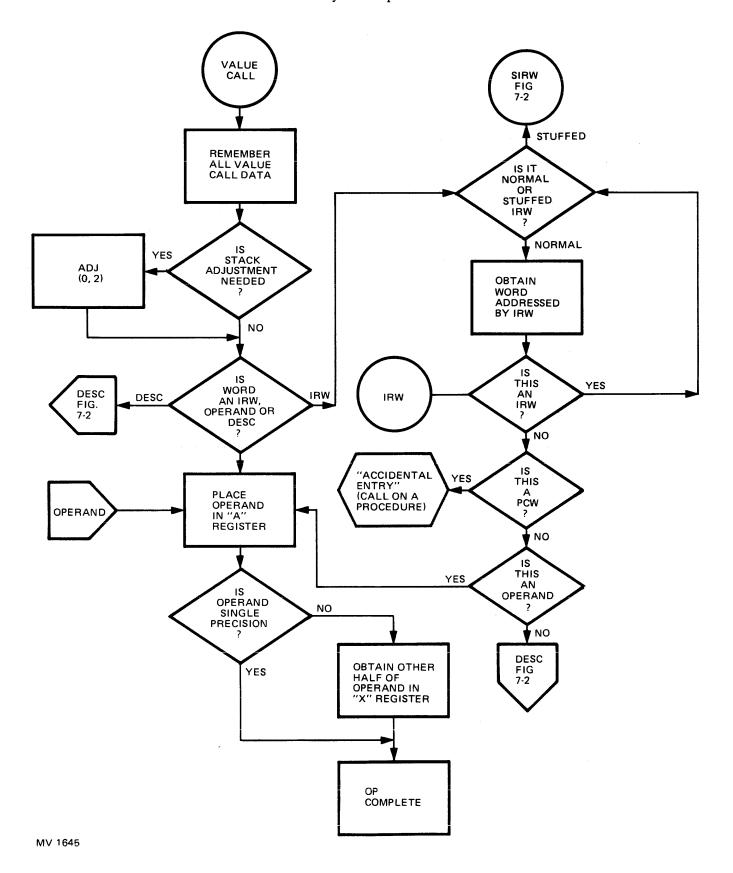

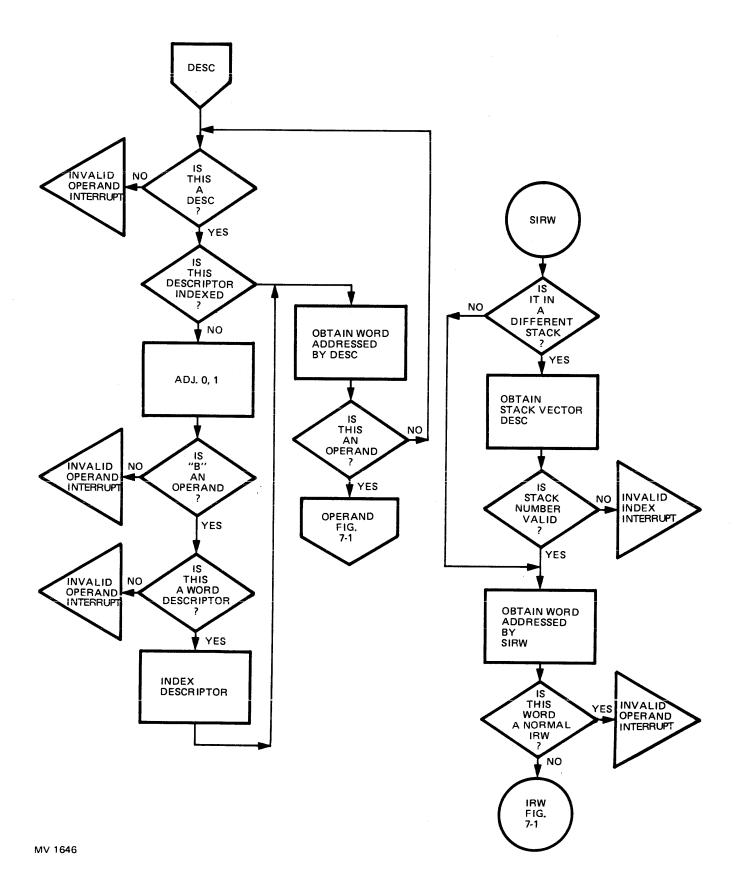

| Value Call       6-4         Operators       6-7         7       PRIMARY MODE OPERATORS       7-1         General       7-1         Arithmetic Operators       7-1         Add (ADD) 80       7-1         Subtract (SUBT) 81       7-2         Multiply (MULT) 82       7-2         Extended Multiply (MULX) 8F       7-2         Divide (DIVD) 83       7-2         Integer Divide (RDIV) 84       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Single-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical Operators       7-5         Logical Pagate (LNOT) 92       7-5         Logical Equivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7 <td></td> <td>Operation Types</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | Operation Types                                 |      |

| Operators         6-7           7 PRIMARY MODE OPERATORS         7-1           General         7-1           Arithmetic Operators         7-1           Add (ADD) 80         7-1           Subtract (SUBT) 81         7-2           Multiply (MULT) 82         7-2           Extended Multiply (MULX) 8F         7-2           Divide (DIVD) 83         7-2           Integer Divide (RDIV) 85         7-3           Integerize, Truncated (NTIA) 86         7-3           Integerize, Rounded (NTGR) 87         7-4           Type-Transfer Operators         7-4           Set to Single-Precision, Truncated (SNGT) CC         7-4           Set to Single-Precision, Rounded (SNGL) CD         7-4           Set to Double-Precision (XTND) CE         7-5           Logical Operators         7-5           Logical Percision (XTND) 90         7-5           Logical Requivalence (LEQV) 93         7-5           Relational Operators         7-5           Greater Than (GRTR) 8A         7-6           Greater Than or Equal (GREQ) 89         7-7           Less Than or Equal (LSEQ) 8B         7-7           Less Than (LESS) 88         7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | Name Call                                       |      |

| 7 PRIMARY MODE OPERATORS 7-1 General 7-1 Arithmetic Operators 7-1 Arithmetic Operators 7-1 Add (ADD) 80 7-1 Subtract (SUBT) 81 7-2 Multiply (MULT) 82 7-2 Extended Multiply (MULX) 8F 7-2 Divide (DIVD) 83 7-2 Integer Divide (IDIV) 84 7-3 Remainder Divide (RDIV) 85 7-3 Integerize, Truncated (NTIA) 86 7-3 Integerize, Rounded (NTGR) 87 7-3 Integerize, Rounded (NTGR) 87 7-4 Set to Single-Precision, Truncated (SNGT) CC 7-4 Set to Single-Precision, Rounded (SNGL) CD 7-4 Set to Duble-Precision (XTND) CE 7-5 Logical Operators 7-5 Logical OR (LOR) 91 7-5 Logical Negate (LNOT) 92 7-5 Logical Negate (LNOT) 92 7-5 Relational Operators 7-5 Greater Than (GRTR) 8A 7-6 Greater Than (GRTR) 8A 7-6 Greater Than or Equal (GREQ) 89 7-7 Equal (EQUL) 8C 7-7 Less Than or Equal (CSEQ) 8B 7-7 Less Than or Legal (LSEQ) 8B 7-7 Less Than or Legal (LSEQ) 8B 7-7 Less Than (LESS) 88 7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         | Value Call                                      |      |

| General   7-1     Arithmetic Operators   7-1     Add (ADD) 80   7-1     Subtract (SUBT) 81   7-2     Multiply (MULT) 82   7-2     Extended Multiply (MULX) 8F   7-2     Divide (DIVD) 83   7-2     Integer Divide (IDIV) 84   7-3     Remainder Divide (RDIV) 85   7-3     Integerize, Truncated (NTIA) 86   7-3     Integerize, Rounded (NTGR) 87   7-4     Type-Transfer Operators   7-4     Set to Single-Precision, Truncated (SNGT) CC   7-4     Set to Single-Precision (XTND) CE   7-5     Logical Operators   7-5     Logical AND (LAND) 90   7-5     Logical Operators   7-5     Logical Equivalence (LEQV) 93   7-5     Relational Operators   7-5     Greater Than (GRTR) 8A   7-6     Greater Than or Equal (GREQ) 89   7-7     Less Than or Equal (LSEQ) 8B   7-7     Less Than or Equal (LSEQ) 8B   7-7     Less Than (LESS) 88   7-7     Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | Operators                                       | 6-7  |

| Arithmetic Operators 7-1 Add (ADD) 80 7-1 Subtract (SUBT) 81 7-2 Multiply (MULT) 82 7-2 Extended Multiply (MULX) 8F 7-2 Divide (DIVD) 83 7-2 Integer Divide (IDIV) 84 7-3 Remainder Divide (RDIV) 85 7-3 Integerize, Truncated (NTIA) 86 7-3 Integerize, Rounded (NTGR) 87 7-4 Type-Transfer Operators 7-4 Set to Single-Precision, Truncated (SNGT) CC 7-4 Set to Single-Precision, Rounded (SNGL) CD 7-5 Logical Operators 7-5 Logical Operators 7-5 Logical OR (LOR) 91 7-5 Logical Negate (LNOT) 92 7-5 Logical Equivalence (LEQV) 93 7-5 Relational Operators 7-5 Greater Than (GRTR) 8A 7-6 Greater Than or Equal (GREQ) 89 7-7 Equal (EQUL) 8C 7-7 Less Than or Equal (LSEQ) 8B 7-7 Less Than (LESS) 88 7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7       | PRIMARY MODE OPERATORS                          |      |

| Add (ADD) 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | General                                         | 7-1  |

| Subtract (SUBT) 81       7-2         Multiply (MULT) 82       7-2         Extended Multiply (MULX) 8F       7-2         Divide (DIVD) 83       7-2         Integer Divide (RDIV) 85       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical OR (LOR) 91       7-5         Logical Negate (LNOT) 92       7-5         Logical Equivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | Arithmetic Operators                            | 7-1  |

| Multiply (MULT) 82 Extended Multiply (MULX) 8F  Divide (DIVD) 83  Integer Divide (IDIV) 84  Remainder Divide (RDIV) 85  Integerize, Truncated (NTIA) 86  Integerize, Rounded (NTGR) 87  Type-Transfer Operators  Set to Single-Precision, Truncated (SNGT) CC  Set to Single-Precision, Rounded (SNGL) CD  Set to Double-Precision (XTND) CE  Logical Operators  Logical AND (LAND) 90  Logical OR (LOR) 91  Logical Negate (LNOT) 92  Logical Equivalence (LEQV) 93  Relational Operators  Greater Than (GRTR) 8A  Greater Than or Equal (GREQ) 89  Equal (EQUL) 8C  Less Than or Equal (LSEQ) 8B  Total  Less Than (LESS) 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | Add (ADD) 80                                    |      |

| Extended Multiply (MULX) 8F  Divide (DIVD) 83  T-2  Integer Divide (IDIV) 84  Remainder Divide (RDIV) 85  Integerize, Truncated (NTIA) 86  Integerize, Rounded (NTGR) 87  Type-Transfer Operators  Set to Single-Precision, Truncated (SNGT) CC  Set to Single-Precision, Rounded (SNGL) CD  Set to Double-Precision (XTND) CE  Logical Operators  Logical AND (LAND) 90  T-5  Logical OR (LOR) 91  Logical Regate (LNOT) 92  Logical Regate (LNOT) 92  Togical Equivalence (LEQV) 93  Relational Operators  Greater Than (GRTR) 8A  Greater Than or Equal (GREQ) 89  Equal (EQUL) 8C  Less Than or Equal (LSEQ) 8B  T-7  Less Than (LESS) 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | Subtract (SUBT) 81                              |      |

| Divide (DIVD) 83       7-2         Integer Divide (IDIV) 84       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical AND (LAND) 90       7-5         Logical OR (LOR) 91       7-5         Logical Negate (LNOT) 92       7-5         Logical Equivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | Multiply (MULT) 82                              | 7-2  |

| Integer Divide (IDIV) 84       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical AND (LAND) 90       7-5         Logical Negate (LNOT) 92       7-5         Logical Requivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | Extended Multiply (MULX) 8F                     | 7-2  |

| Integer Divide (IDIV) 84       7-3         Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical AND (LAND) 90       7-5         Logical Negate (LNOT) 92       7-5         Logical Requivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | Divide (DIVD) 83                                | 7-2  |

| Remainder Divide (RDIV) 85       7-3         Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical AND (LAND) 90       7-5         Logical Pegate (LNOT) 92       7-5         Logical Regate (LNOT) 92       7-5         Logical Equivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                 | 7-3  |

| Integerize, Truncated (NTIA) 86       7-3         Integerize, Rounded (NTGR) 87       7-4         Type-Transfer Operators       7-4         Set to Single-Precision, Truncated (SNGT) CC       7-4         Set to Single-Precision, Rounded (SNGL) CD       7-4         Set to Double-Precision (XTND) CE       7-5         Logical Operators       7-5         Logical AND (LAND) 90       7-5         Logical OR (LOR) 91       7-5         Logical Negate (LNOT) 92       7-5         Logical Equivalence (LEQV) 93       7-5         Relational Operators       7-5         Greater Than (GRTR) 8A       7-6         Greater Than or Equal (GREQ) 89       7-7         Equal (EQUL) 8C       7-7         Less Than or Equal (LSEQ) 8B       7-7         Less Than (LESS) 88       7-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |                                                 | 7-3  |