BJ-8 APRIL, 1966

# **B8500 SYSTEM**

# **REFERENCE MANUAL**

## -Burroughs Corporation-

Defense, Space and Special Systems Group

BJ-8 APRIL, 1966

# **B8500 SYSTEM**

# **REFERENCE MANUAL**

Copyright C 1966 Burroughs Corporation

Burroughs Corporation

Defense, Space and Special Systems Group

The information in this publication is subject to change. Revisions will be issued to advise of such changes and additions.

.

.

,

.

April 1966

# TABLE OF CONTENTS

| INTRODUCTION.                                     |

|---------------------------------------------------|

| CHAPTER 1. SYSTEM DESCRIPTION 1-                  |

| System Configuration                              |

| System Capabilities and Features                  |

| Hardware Modularity                               |

| Central Processor Module                          |

| I/O Module                                        |

| Memory Module                                     |

| Storage Facilities                                |

| System Availability and "Fail Soft" Reliability   |

| Software Modularity                               |

| Uniform Program Structure                         |

|                                                   |

|                                                   |

|                                                   |

| Concurrent Peripheral Operations                  |

| Concurrent Input/Output Operations                |

| Computerized Input/Output Module 1-               |

| Allocation of I/O Channels 1-                     |

| System Expansion                                  |

| Executive Scheduling Program 1-                   |

| Dynamic Allocation of Equipment 1-                |

| Memory Protection                                 |

| Call-by-Name Filing System                        |

| Interrupt and External Request Capabilities       |

| Compilers                                         |

| -                                                 |

| CHAPTER 2. PROGRAMMING FEATURES                   |

| Executive Scheduling Program                      |

| Introduction                                      |

| What is the Purpose of ESP? 2-                    |

| Of What Does ESP Consist and Where is it Located? |

| Functions of the Executive Routines               |

| Functions of the $I/O$ Routines                   |

| What Can ESP Accommodate?       2-                |

| What Does ESP Do?                                 |

| Scheduling                                        |

| Error Recovery                                    |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

|                                                   |

| Working Storage Segment                           |

| Program Reference Table 2-                        |

| Descriptor                                        |

| Description                                       |

| Link                                              |

| File List                                         |

| CHORE Working Area                                |

Page

## TABLE OF CONTENTS (Continued)

|                                         | Page         |

|-----------------------------------------|--------------|

| Cold Job Table                          | 2-5          |

| Hot Job Table                           | 2-5          |

| Interrupt System                        | 2-6          |

| Hardware Functions at Interrupt         | 2-7          |

| Multiprocessor Interrupts               | 2-7          |

| Functions of ESP                        | 2-7          |

| Introduction                            | 2-7          |

| External ESP Programs                   | 2-7          |

| CHORE                                   | 2-9          |

| Collector/Scheduler                     | 2-10         |

| Interpreter/Controller                  |              |

| Internal ESP Programs                   | 2-11         |

| Filing.                                 |              |

| Memory Allocation.                      |              |

| Disk Allocation                         |              |

| Input/Output Processing                 |              |

| Source Language Compilers               |              |

| System Compatibility                    |              |

| TOOL Compiler.                          |              |

| Introduction.                           |              |

| Features of TOOL                        |              |

| ALGOL Compiler                          |              |

|                                         |              |

| Compilation Speed and Specifications    |              |

| FORTRAN IV Compiler.                    |              |

|                                         |              |

| Storage Requirements.                   |              |

| Compiler Speed and Specifications.      |              |

|                                         |              |

| COBOL Compiler                          | 2-20         |

|                                         |              |

| Features of COBOL                       |              |

| Utility Programs                        | 2-27         |

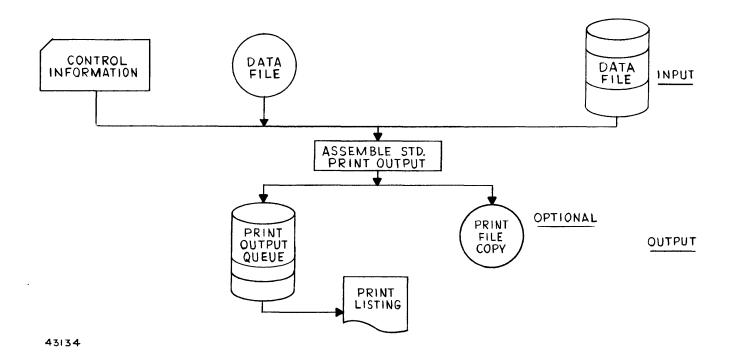

| DIOT (Deal Interface OuT) Print Program |              |

| Program Functions of IDIOT              | 2-27         |

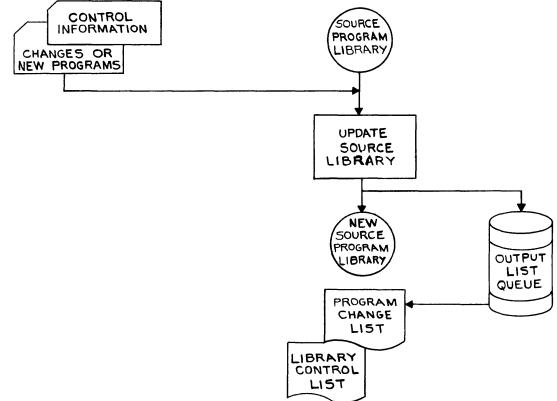

| Source Program Maintenance              | 2-20         |

| Description                             |              |

| Options.                                |              |

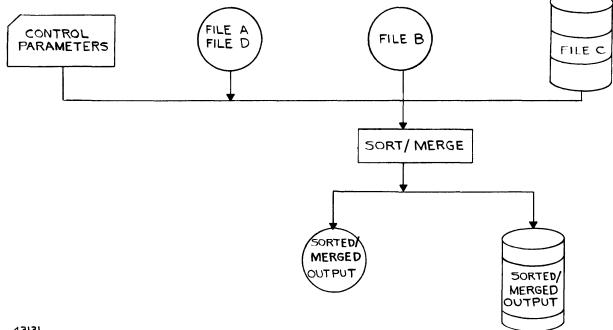

| Generalized Sort/Merge                  |              |

| Description                             | 2-29<br>2-29 |

| Options.                                |              |

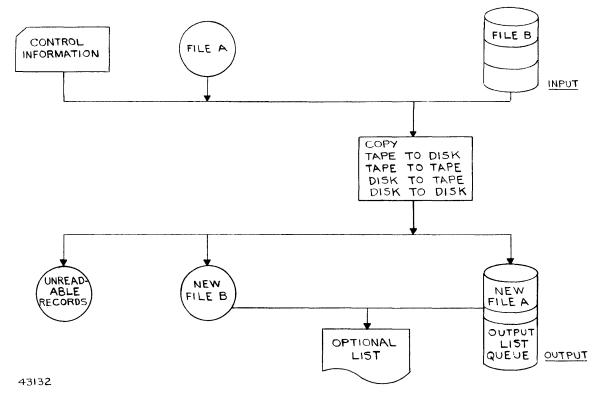

| Data File Copy                          | 2-30<br>2-30 |

|                                         |              |

| Options.                                | 2-30         |

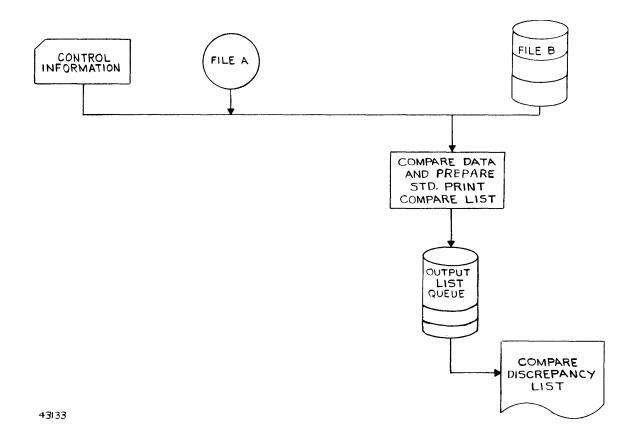

| Data File Compare                       | 2-31         |

| Description                             | 2-31         |

| Options.                                | 2-31         |

| Data File Print                         | 2-32         |

| Description                             | 2-32         |

| Options                                 | 2-32         |

.

## TABLE OF CONTENTS (Continued)

|                                          | Page           |

|------------------------------------------|----------------|

| CHAPTER 3. EQUIPMENT SPECIFICATIONS      | 3-1            |

| General Description                      | 3-1            |

| Central Data Processing System           | 3-1            |

| Peripheral Equipment Systems and Devices | 3-3            |

| B8501 Central Processor Module           | 3-3            |

| General Description                      | 3-3            |

| Functional Description                   | 3-3            |

| Communications Unit                      | 3-9            |

| Interface Characteristics.               | 3-9            |

| Description of Logical Operation.        | 3-9            |

| Advanced Station (ADVAST)                | 3-3            |

| Final Station (FINST)                    | 3-11           |

| Stack Operation                          |                |

| Operational Characteristics              | $3-11 \\ 3-13$ |

| Interrupt Bit Processing                 | 3-13<br>3-13   |

|                                          |                |

| B8505 Memory Module                      | 3-10<br>3-16   |

| General Description                      |                |

| Functional Description                   | 3-10<br>3-16   |

| Control Word.                            | 3-10<br>3-16   |

| Fetch Operations                         | 3-10<br>3-18   |

| Store Operations                         | 3-18<br>3-18   |

| Checking Functions.                      |                |

| Interface Characteristics.               |                |

| B8510 Input-Output Module.               |                |

| Introduction.                            |                |

| Summary                                  |                |

| B8520 Console                            |                |

| General Description                      |                |

| Functional Description                   |                |

| Communications Link                      |                |

| Memory Module Check Facilities           | 3-21           |

| Power Control and Sensing Center.        |                |

| Disk File System                         |                |

| General Description                      |                |

| Physical Description of Electronics Unit |                |

| Physical Description of Storage Module   |                |

| Functional Description                   |                |

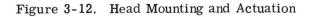

| Disk File Controller                     |                |

| Controller Section                       | 3-27           |

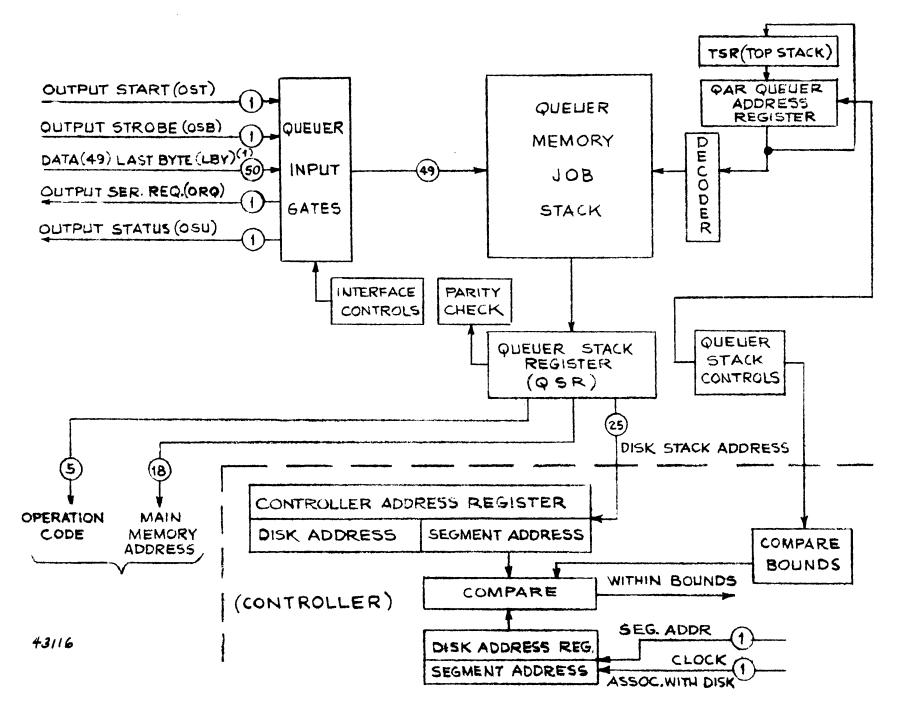

| Queuer Section.                          | 3-32           |

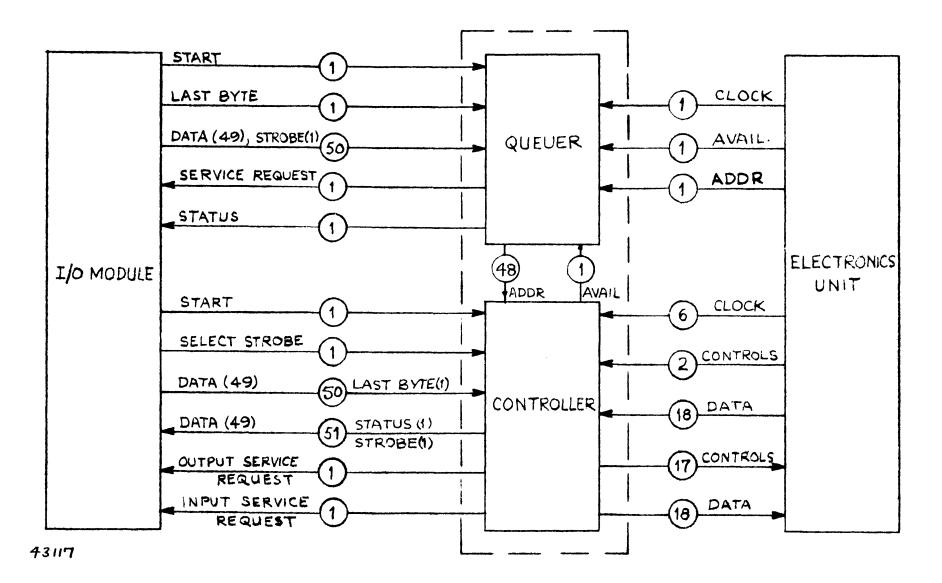

| Interface Characteristics.               | 3-34           |

| Operational Characteristics              | 3-34           |

| Storage Facilities.                      | 3-34           |

| Disk Allocation                          | 3-36           |

| Parallel Reading or Writing              | 3-36           |

| Magnetic Tape System.                    | 3-37           |

| General Description                      | 3-37           |

| Functional Description                   | 3-37           |

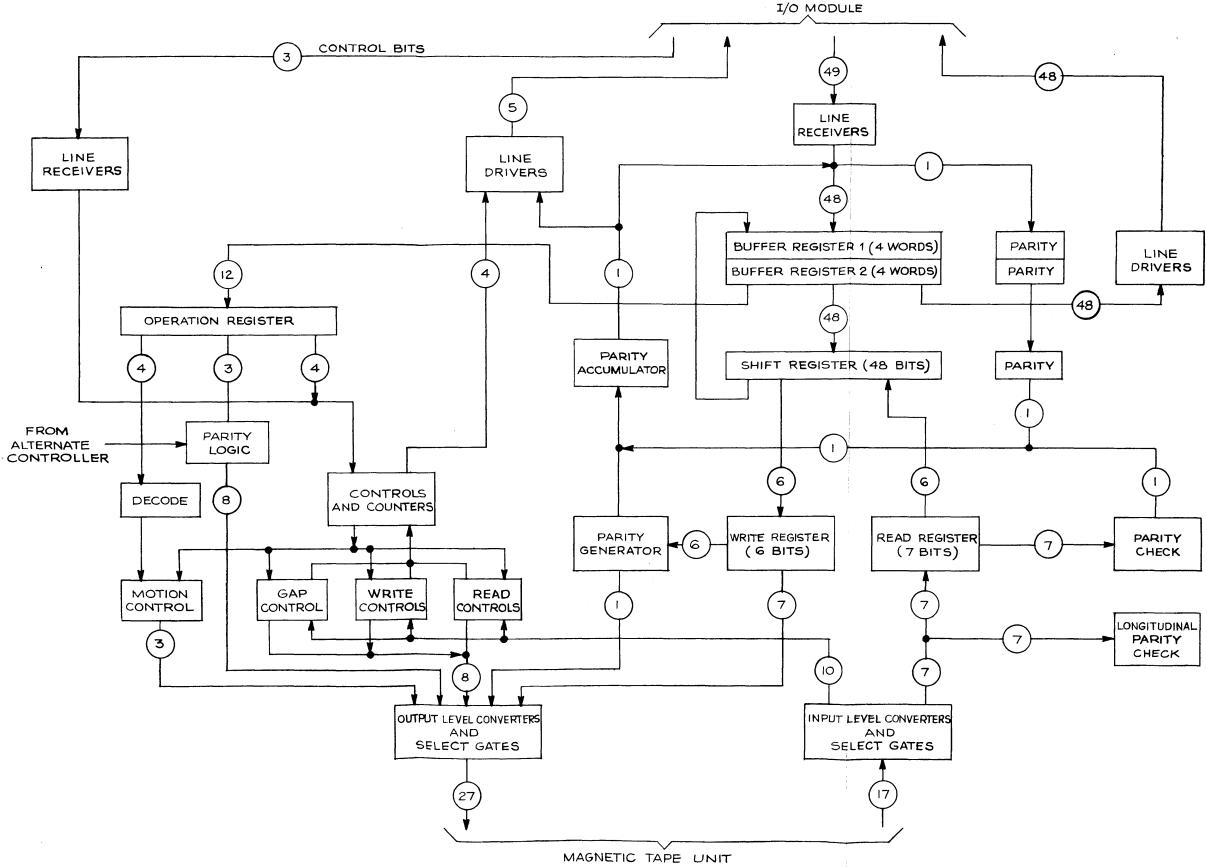

| Magnetic Tape Controller                 | 3-37           |

| Line Drivers and Receivers               | 3-38           |

| MTU Select Register and Parity Logic     | 3-38           |

| Operation Register and Decoder           | 3-38           |

## TABLE OF CONTENTS (Continued)

|            | •                                                                            | _            |

|------------|------------------------------------------------------------------------------|--------------|

|            |                                                                              | Page         |

| Level      | Converters and Select Gates                                                  | 3-38         |

| Data H     | Iandling Registers                                                           | 3-38         |

|            | cter Parity                                                                  |              |

| Word       | Parity                                                                       | 3-41         |

| Contro     | bls and Counters                                                             | 3-41         |

| Write C    | peration                                                                     | 3-41         |

| Read Or    | peration                                                                     | 3-41         |

|            | s of Terminations                                                            | 3-42         |

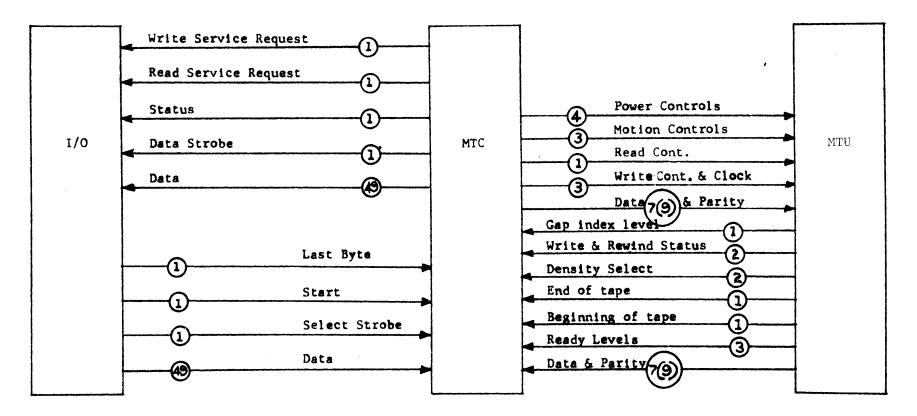

| Interface  | Characteristics.                                                             | 3-42         |

| Operation  | hal Characteristics                                                          | 3-44         |

|            | °S                                                                           | 3-45         |

|            | Description                                                                  |              |

|            | al Description                                                               | 3-46         |

|            | Description                                                                  | 3-46<br>3-46 |

|            | es                                                                           | 3-40<br>3-46 |

| Dhysica    | 1 Description of B303 Card Punch                                             |              |

| Dhysica    | 1 Description of B304 Card Punch.                                            | 3-47<br>3-47 |

| Functions  | al Description                                                               | 3-48         |

|            | Description                                                                  | 3-48         |

|            | · · · · · · · · · · · · · · · · · · ·                                        | 3-48         |

|            | Description                                                                  |              |

|            | al Description                                                               | 3-49         |

|            | Description                                                                  | 3-49         |

|            | nterfacing                                                                   | 3-50         |

|            | Description                                                                  | 3-50         |

|            | on Flow                                                                      | 3-50         |

| Commu      | nications Between Peripheral Equipment and $I/O$ Modules                     | 3-50         |

| Commu      | nications Between I/O Modules and Central Processors                         | 3-51         |

| Commu      | nications Between Processors or I/O Modules and Memory Modules               | 3-51         |

|            |                                                                              |              |

|            |                                                                              | A 1          |

| APPENDIX A | B8500 CHARACTER SET                                                          | A-1          |

|            |                                                                              | <b>р</b> 1   |

| APPENDIX B | CENTRAL PROCESSOR INSTRUCTIONS.                                              | B-1          |

| ADDENDRY O | CENTRAL PROCESSOR INSTRUCTION SYLLABLES VARIANT DEFINITIONS AND              |              |

| APPENDIX C |                                                                              | C-1          |

|            | CONFIGURATIONS                                                               | C-1          |

| APPENDIX D | CENTRAL PROCESSOR WORD FORMATS                                               | D-1          |

| APPENDIX D |                                                                              | <b>D</b> -1  |

| APPENDIX E | ABBREVIATIONS AND ACRONYMS                                                   | E-1          |

|            | TELEVENT CONTRACTOR THAT TO TOTAL THAT I I I I I I I I I I I I I I I I I I I | ~ *          |

| APPENDIX F | POLISH NOTATION AND THE STACK CONCEPT                                        | F-1          |

|            |                                                                              |              |

| APPENDIX G | GLOSSARY                                                                     | G-1          |

# LIST OF ILLUSTRATIONS

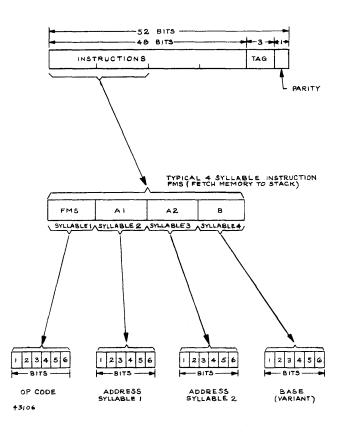

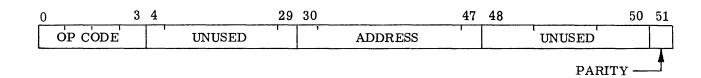

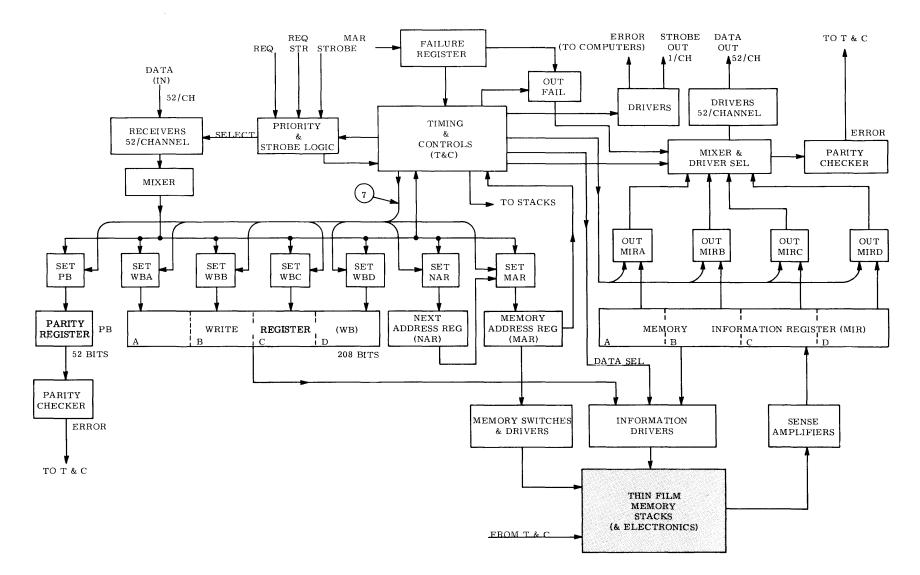

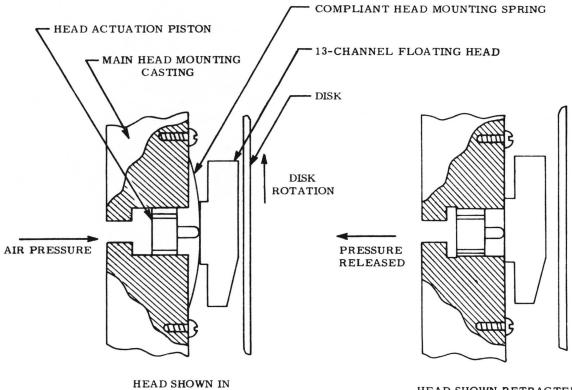

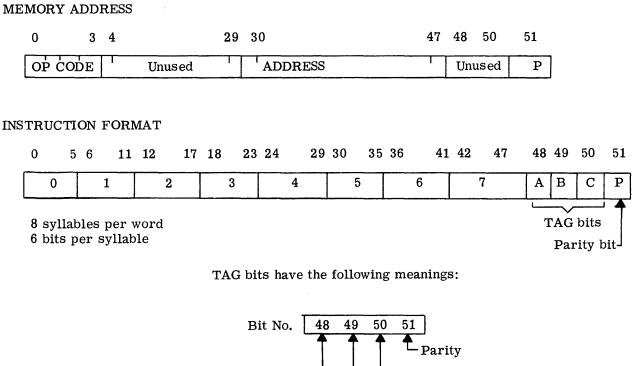

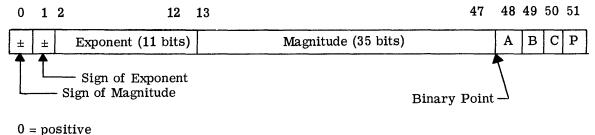

#### Figure Page 1-1 х 1 - 2General Organization of the B8500 System ..... 1 - 0Concurrent Operations in B8500 System..... 1 - 31 - 7Hot Job Table and Sleep Table Linking. ..... 2 - 12-62 - 2Interrupt Flow of Control. 2 - 82 - 32 - 21Example of I/O Processing ..... 2 - 4COBOL Compiler Structure ..... 2 - 242 - 5Source Program Maintenance..... 2 - 282-6Generalized Sort/Merge ..... 2 - 29Data File Copy..... 2 - 72-30 2 - 8Data File Compare..... 2 - 312-9 Data File Input..... 2 - 323 - 1Module Cabinet ..... 3 - 2Functions of Central Processor Stations..... 3 - 23 - 53 - 3Central Processor Module, Block Diagram..... 3 - 73-4 Central Processor Module, Instruction Word Format..... 3 - 123 - 5Central Processor Module, Interrupt Routine Entry..... 3 - 143 - 6Memory Module, Block Diagram..... 3 - 173 - 73 - 203-8 Disk File Subsystem..... 3 - 223 - 9Disk File System Configuration ..... 3 - 233 - 10Disk File Subsystem Modular Design..... 3 - 243 - 113 - 25Disk File Storage Module..... 3 - 12Head Mounting and Actuation ..... 3 - 253 - 13Controller Section, Block Diagram ..... 3 - 29Queuer Section, Block Diagram ..... 3 - 333 - 143 - 15Disk File System, Interface Diagram..... 3 - 353 - 16B425 Magnetic Tape Unit..... 3 - 373 - 17Magnetic Tape Controller, Block Diagram ..... 3 - 393 - 18Magnetic Tape System, Interface Diagram ..... 3-43 3 - 19B129 Card Reader ...... 3 - 453 - 20B303 Card Punch ....... 3 - 463 - 213 - 473 - 22B329 Line Printer ..... 3 - 49System Interface and Information Flow Diagram ..... 3 - 233-52

# LIST OF TABLES

| Table |                                                                                         | Page |

|-------|-----------------------------------------------------------------------------------------|------|

| 1-1   | B8500 Data Processing System-Equipment Configuration and Operational<br>Characteristics | 1-2  |

| 3-1   | Central Processor Module Characteristics                                                | 3-4  |

| 3-2   | Memory Module Characteristics                                                           | 3-15 |

| 3-3   | Format of Control Word for Magnetic Tape Operations                                     | 3-42 |

•

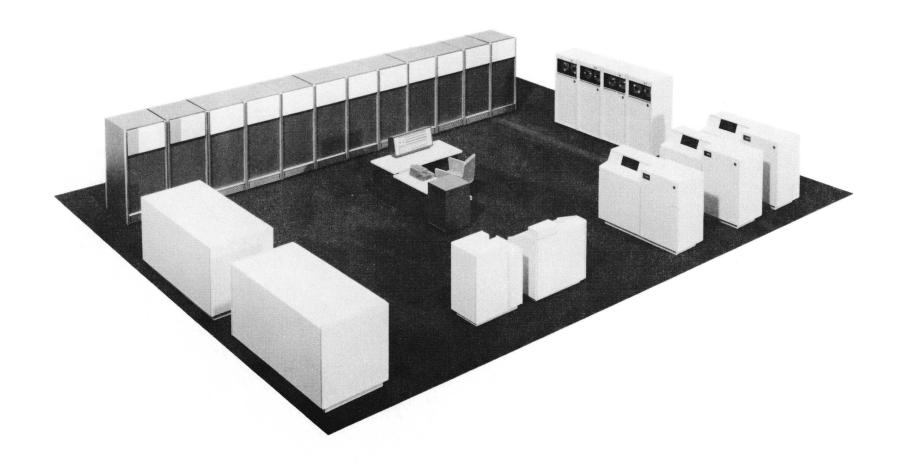

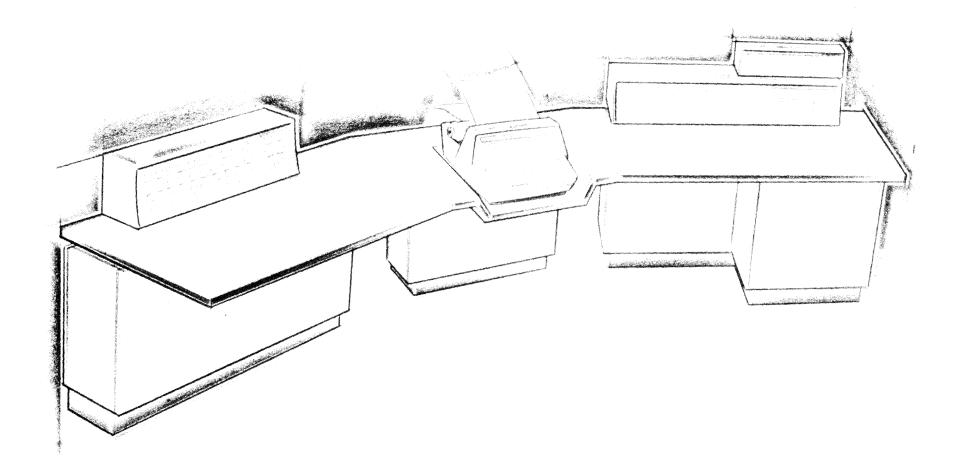

Figure 1-1. B8500 Data Processing System

# INTRODUCTION

The Burroughs B8500 Data Processing System is a very large-scale, modular, high-speed, "third generation", information processor.

The unique, modular hardware and software organization of the B8500 provides a computing system which is flexible, self-regulating, and essentially free from ''down-time''. This modular organization, the various multiprocessing and multi-programming features, and the powerful input-output capabilities of the system guarantee excellent performance over the broad spectrum of data processing tasks ranging from batch and ''brute force'' computation to conversational and on-line time-shared operations.

The B8500 employs the latest proven hardware techniques, including monolithic integrated circuits for the implementation of its logic and magnetic thin-films for the fully-shared random-access memory.

The information presented is intended for use as an introduction for persons unfamiliar with the B8500 System and as a general reference source for individuals engaged in marketing, programming, operating, and maintaining the B8500 System.

Listings and definitions of abbreviations, acronyms, and terms used in this manual are given in Appendices E (abbreviations and acronyms) and G (glossary).

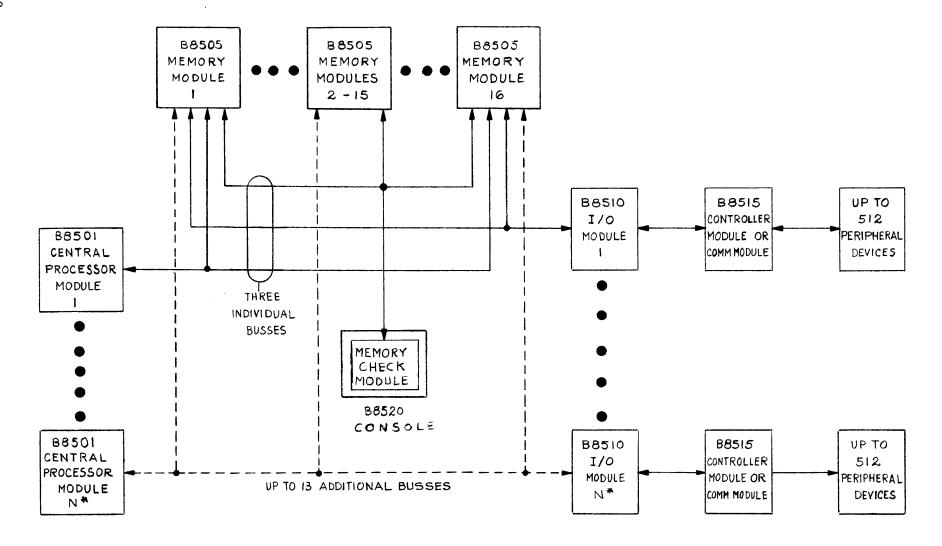

\* TOTAL COMBINATION OF CENTRAL PROCESSOR 43101 AND I/O MODULES CAN BE EXTENDED TO 15.

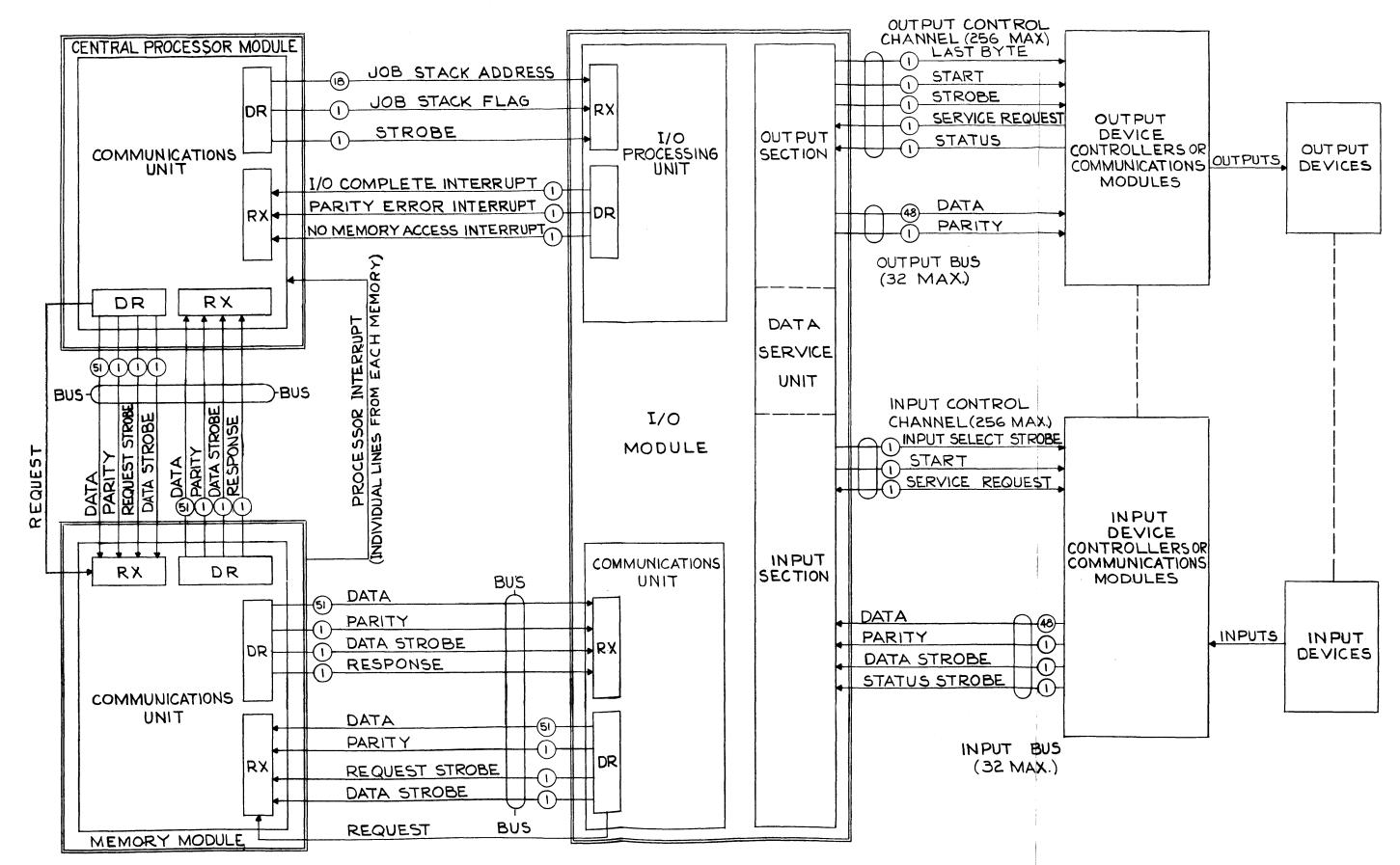

Figure 1-2. General Organization of the B8500 System

## **CHAPTER 1**

# SYSTEM DESCRIPTION

## SYSTEM CONFIGURATION

The configuration of a B8500 Data Processing System depends upon specific applications and expected work loads. The B8500 is essentially a system of systems. Because the B8500 is a modular system, it can be tailor-made to fit a user's current or changing requirements. A typical installation of the B8500 System is shown in Figure 1-1.

Figure 1-2 shows the general organization of the B8500 System. The heart of the system is the Central Data Processing System which is comprised of the B8520 Console and configuration of B8501 Central Processor Modules, B8505 Memory Modules, and B8510 Input/Output (I/O) Modules. The three basic modules (processor, memory and I/O) are arranged into a central system cabinet configuration. A central data processing system may contain one or more processor modules, one or more I/O modules, and a maximum of 16 memory modules. The total combination of processor and I/O modules may be extended to 15 (e.g., if only one processor module is used, 14 I/O modules can be used).

A B8500 System also includes one or more B8515 Controller Modules, Communication Modules, and the necessary number of peripheral devices (such as disk file systems, magnetic tape systems, card readers, etc.) Each I/O module used in a system utilizes 512 simplex channels to handle peripheral devices. Table 1-1 lists the model numbers, names of equipment, and the maximum quantities which may be implemented.

## SYSTEM CAPABILITIES AND FEATURES

Table 1-1 lists the basic capabilities of the equipment modules and peripheral devices used in the B8500 Data Processing System. The following paragraphs describe the general physical and functional features of the system.

## Hardware Modularity

Three basic functions are implemented on the B8500 System: data processing functions, memory functions, and input/output functions. Each function is handled by a type of module specifically designed for its task (i. e., the B8501 Central Processor Module handles the data processing functions, the B8505 Memory Module handles the memory functions, and the B8510 I/O Module handles the input/output functions). All modules of one type are identical. Thus, a standardized interconnection network provides for freedom in the selection of a system configuration.

## TABLE 1-1

## B8500 DATA PROCESSING SYSTEM-EQUIPMENT CONFIGURATION AND OPERATIONAL CHARACTERISTICS

| Model<br>No. | Name                          | Maximum<br>Quantity            | Capability Features                                                                                                                                                                                     |

|--------------|-------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B8520        | Console                       | 1                              | Operator's and test console with capability of automatically testing memory modules                                                                                                                     |

| B8501        | Central Processor<br>Module   | 14*                            | High-speed computation center of B8500<br>System. Performs arithmetic, control, data<br>transfer, and interrupt service functions                                                                       |

|              |                               |                                | Contains four high-spèed local memories<br>20-megacycle clock rate                                                                                                                                      |

| B8505        | Memory Module                 | 16                             | Random access thin-film main memory                                                                                                                                                                     |

|              |                               |                                | Capacity of 16,384 52-bit words (four 52-bit words per location)                                                                                                                                        |

|              |                               |                                | 500 nanosecond cycle time (200 fetch, 300 store)                                                                                                                                                        |

|              |                               |                                | 20 megacycle clock rate                                                                                                                                                                                 |

|              |                               |                                | Maximum data rate: 69 million characters per second                                                                                                                                                     |

| B8510        | Input/Output (I/O)<br>Module  | 14*                            | Extremely high-throughput Input/Output device                                                                                                                                                           |

|              |                               |                                | Thin film local memory with 1024 100-bit<br>word capacity and 500 nanosecond cycle time,<br>1.7 usec service cycle                                                                                      |

| B8515        | Controller Module             | As required                    | Houses peripheral device controller submod-<br>ules which provide the compatibility and<br>buffering between I/O modules and peripheral<br>devices if required                                          |

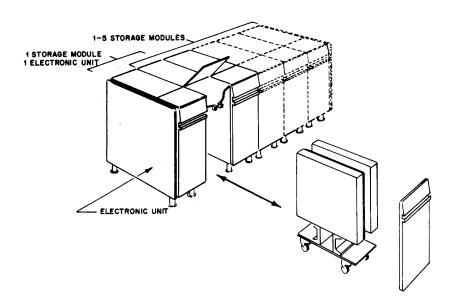

| B470         | Disk File System              | 20 per disk file<br>controller | Fast access mass memory subsystem with 200-million 48-bit words and 30 millisecond access time (average). (Access time is substantially reduced by the use of the ''queuer'' described in this manual.) |

| B471         | Disk File<br>Electronics Unit | 20 per Disk File<br>System     |                                                                                                                                                                                                         |

| B475         | Disk File Storage<br>Module   | 100 per Disk File<br>System    |                                                                                                                                                                                                         |

|              |                               |                                |                                                                                                                                                                                                         |

\* Maximum conbination of I/O and Processor modules is 15.

.

## TABLE 1-1 (continued)

| Model<br>No. | Name                     | Maximum<br>Quantity                   | Capability Features                                                                                 |

|--------------|--------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| B425         | Magnetic Tape Unit       | Eight per Magnetic<br>Tape Controller | Reads and records data at a density of 800<br>bits per inch and a speed of 120 inches per<br>second |

|              |                          |                                       | 2.88-million 48-bit word capacity on each reel of magnetic tape                                     |

|              |                          |                                       | Average transfer time of 9,000 words per second                                                     |

| В124         | Card Reader              | As required                           | 800 cards-per-minute rate                                                                           |

| B129         | Card Reader              | As required                           | 1400 cards-per-minute rate                                                                          |

| B303         | Card Punch               | As required                           | 100 cards-per-minute rate                                                                           |

| B304         | Card Punch               | As required                           | 300 cards-per-minute rate                                                                           |

| B329         | Line Printer             | As required                           | 1040 lines-per-minute rate                                                                          |

|              |                          |                                       | 64 characters (37 alphanumeric and 27 special)                                                      |

|              |                          |                                       | 132 print positions                                                                                 |

|              | Communications<br>Module | As required                           | Interfaces low-speed, voice-grade, and wide<br>band communications lines with I/O modules           |

•

#### B8500 DATA PROCESSING SYSTEM-EQUIPMENT CONFIGURATION AND OPERATIONAL CHARACTERISTICS

## **CENTRAL PROCESSOR MODULE**

The choice of the number of central processor modules and I/O modules depends entirely upon the application of the B8500 System. There may be as many as 16 communications busses connected to the memory modules. and these busses can serve the console and any combination of central processor and I/Omodules. When more than one processor module is used, the Executive Scheduling Program dynamically manages the job assignment of each processor module through the processor's control registers. Thus, any program can be executed by any processor module. There is no fixed master slave relationship between the processor modules. If more than one processor module is available and asynchronous segments of a program are indicated, the segments can be simultaneously processed on the multiple processor modules.

## I/O MODULE

The most important feature of the I/O Module is its independence from the Central Processor Module. In effect, the I/O Module is a separate processor with its own local memory unit, logic and arithmetic functions, and communication capabilities. Because it provides channels for all data transfers between peripheral devices and the System Memory, the I/O Module executes transfers from one peripheral device to another peripheral device independent of direct Central Processor control.

The system operations of the I/O Module are programmed separately from the Central Processor Modules. This programming is coded in an assembly language designed solely for the I/O Module. Then, the symbolic program is assembled into an object program by means of an assembler program written in ALGOL. Input to the assembler is on punched cards. The output consists of a program listing, with relative memory assignments, and a tape that contains the assembled object program for printing and ultimate loading into the B8500.

The simple transfer function between peripheral devices and system memory is similar to the more conventional descriptor-controlled

and buffered I/O Module in the sense that there is a descriptor generated by the Central Processor for each data transfer executed. However, in data transfers to and from peripheral devices, the I/O Module completely controls the I/O operation using parameters stored in the I/O Module's program data area. The execution of buffered I/O can now be treated by Central Processor programs in terms of tape, card, and print files, rather than by individual tape records, card images, and print lines. This means that I/O processing overlaps the Central Processor for long periods of time, rather than the more conventional technique of overlapping a single record. Using this overlap method reduces the number of interrupts to the Central Processor, thereby reducing the amount of software overhead associated with a Control Program.

#### MEMORY MODULE

As required by the workload at an installation, there may be as few as one and as many as sixteen B8505 Memory Modules in a B8500 System. Because each memory module can operate as an independent memory, system programs can be completely relocated to any memory module. All programs, therefore, are written with relative addressing methods to capitalize on the relocatability feature.

#### **STORAGE FACILITIES**

Storage facilities in the B8500 Data Processing System include a hierarchy of memories ranging from 50-nanosecond cycle scratch pad memories to reels of magnetic tape. The storage facilities consist of the following:

• Each B8505 Memory Module has 16,384 52-bit words and a full cycle time of 500 nanoseconds. Words are stored or fetched in four-word groups (208 bits) to enable a maximum data transfer rate of 416 million bits per second for each module.

- The local memory in each I/O Module has 2048 52-bit words and a full cycle time of 500 nanoseconds.

- The local integrated-circuit memories in each processor module have 32 52-bit word and 24 70-bit word capacities and 50 nanosecond cycle times. A 28-word (18 bits per word) associative memory is also contained in each processor.

- The disk file subsystems, each have a capacity of 200 million 48-bit words and an average access time of 30 milli-seconds. Transfer rates average 8 million bits per second (166,666 48-bit words per second).

- The Magnetic Tape Units have storage facilities for serial files on 2400-foot reels of magnetic tape. Each reel of tape has a capacity of 2.88 million 48-bit words. The transfer rate possible is 9,000 words per second.

Programs and data are stored in the high-speed (500 nanosecond), thin-film main memory storage and are vailable when required by operational programs. Data required for actual execution of program steps is automatically fetched, ahead of time, from the 500-nanosecond thin-film memory in a memory module and is stored in the 50-nanosecond thin-film memory in a processor module. The disk file system backs up the 500-nanosecond memory. In general, the Executive Scheduling Program controls the transfer of data from the slower speed peripheral storage devices to the disk file system before allowing a program to run. As much information as is needed at any one time is then transferred into the 500-nanosecond memory by the Executive Scheduling Program.

## System Availability and "Fail Soft" Reliability

The reliability of the system is enhanced by designing the interconnections between equipment modules as a group of parallel networks. This means each module of a specific type is independent of every other module of the same type, both in power supply and data flow.

If a component in a basic equipment unit (i.e., unit at the end of the network) should fail, obviously that particular unit is not operable, and the medium being operated upon will have to be relocated to another basic unit. An example of this might be a magnetic tape transport, where upon component failure, the reel of tape would have to be removed and mounted on another tape unit. If a component in the Magnetic Tape Controller should fail, however, the tape units normally serviced by the defective Controller would remain in operation. They would be serviced by another Controller via a second data path. The Controller assuming this new load would still handle the tape units originally assigned to it. The result is that the system would remain operative, but data flow would be at a reduced rate. Similarly, at the next level in the hierarchy of equipment, if a component in an I/O Module should fail, then an alternate path is available from the Magnetic Tape Controllers to a second I/OModule. In this fail-soft environment, therefore, jobs with high priority will not be materially affected by the failure of an individual component.

Because of the modular concept and interconnection network, on-site modifications for continuing quality improvement, can be made to equipment modules without interrupting the operation of the system. For the same reasons, unscheduled maintenance of the equipment modules can be performed while the system remains on-line.

## Software Modularity

## UNIFORM PROGRAM STRUCTURE

The B8500 operating system consists of an Executive Scheduling Program (ESP), service programs (such as an I/O procedure), and compilers for ALGOL, COBOL, and FORTRAN IV (ASA). Software modularity is achieved by requiring all program segments to conform to a uniform structure. Compilers, as well as the programs they compile, use the uniform program structure.

The Executive Scheduling Program itself uses the uniform program structure. The service routines surrounding ESP have the uniform program structure, but they also enjoy direct access to some of ESP functions.

## Multiprogramming And Multiprocessing

Two of the most important features of the B8500 System are its multiprogramming and multiprocessing capabilities.

Multiprogramming is the concurrent processing of several programs on a "time-sharing" basis. For example, a program is normally made active and run when (1) all of its necessary input information has been assembled on the disk file system, and (2) the required output units are available. While a specific program is waiting for inputs, etc., other programs will have already been running. Therefore, the waiting time on one job is not wasted, and an effective match is made of the fast internal speed and the slower peripheral devices.

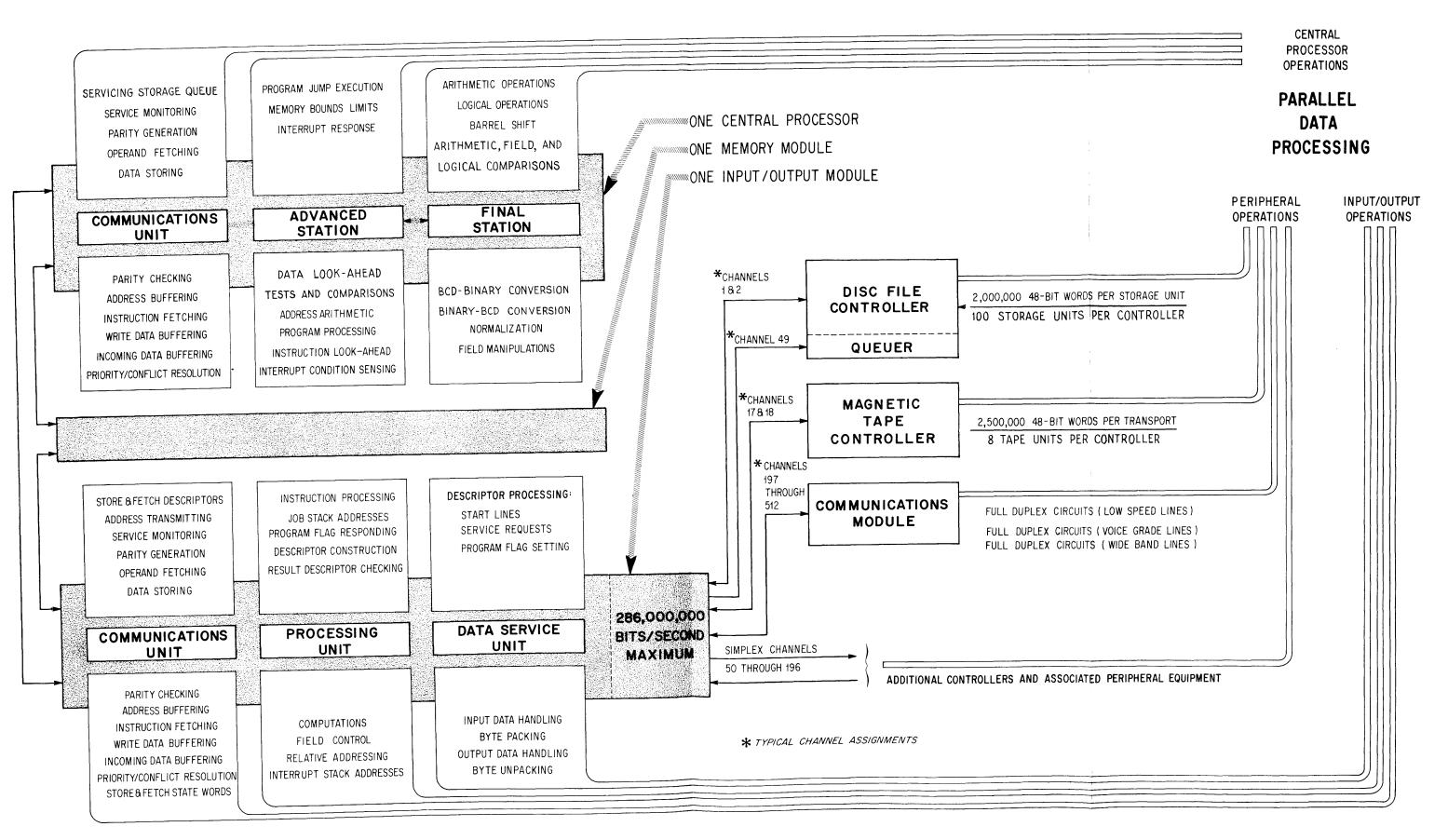

Multiprocessing, which is the simultaneous execution of two or more object programs, is possible on a B8500 System having two or more processor and I/O modules. Thus, when enough memory and peripheral devices are supplied, two processor modules can practically double the throughput of a system. Input/output operations occur nearly independent of the Processor, and are in parallel with processor module operations. Memory/ processor operations can also occur independently of other system operations, because each memory module has its own list of descriptors which it can execute. An example of how concurrent operations may occur in a B8500 System, using only one central processor, one memory module, and one input/output module in conjunction with some peripheral equipment, is shown in Figure 1-3. The three modules are on the left half of the drawing, and the peripheral equipment is on the right half. As indicated in the upper right corner of the drawing, concurrent or parallel data processing occurs in three locations:

Central Processor Operations

**Peripheral Operations**

Input/Output Operations

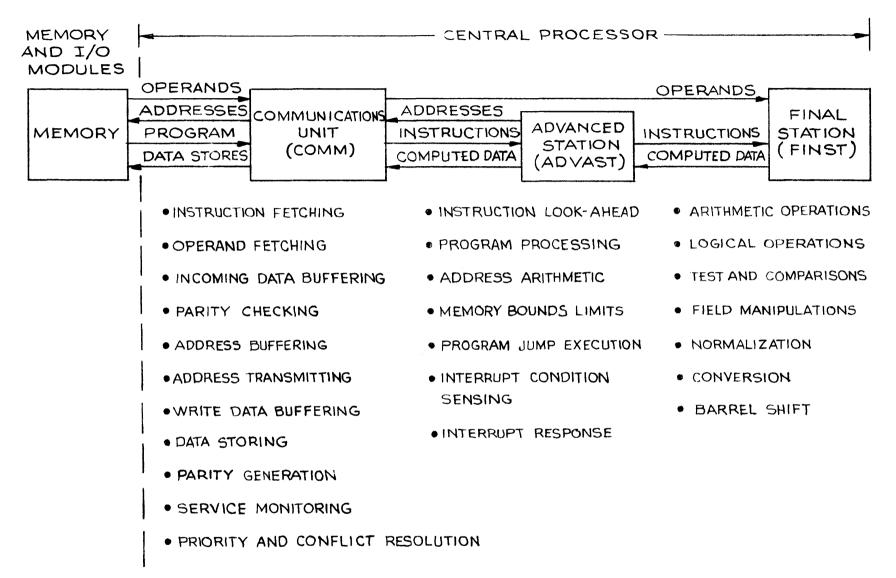

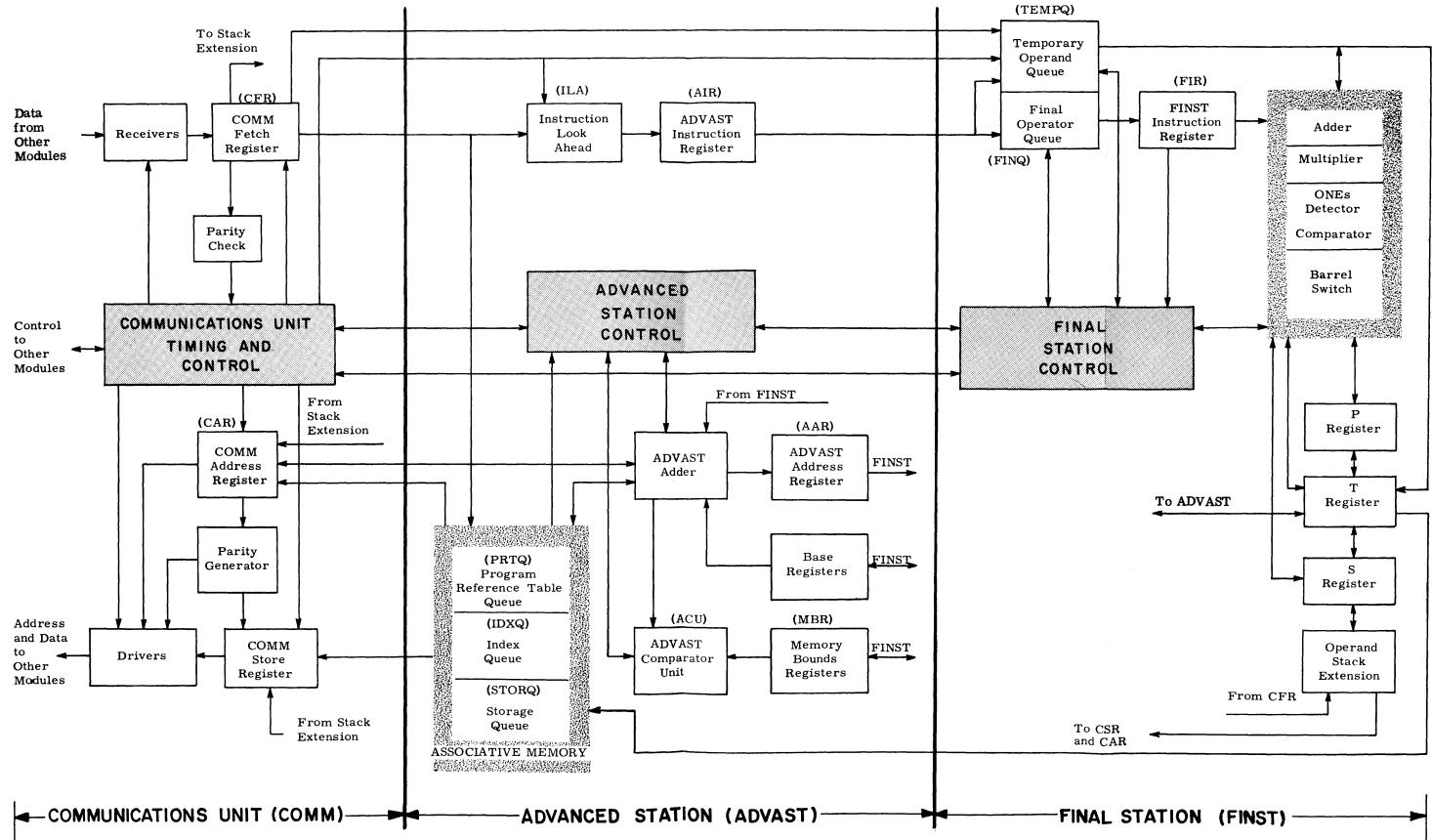

## CONCURRENT CENTRAL PROCESSOR OPERATIONS

The B8500 System goes beyond the conventional technique of buffering I/O peripheral devices with processing operations, commonly known as "reading while writing while computing". It even goes beyond the usual overlapping of a fetch of an instruction from memory with the store of data to memory. The B8500, in addition to using the above time-sharing method. also overlaps the execution of several machine instructions. This advanced degree of time sharing is made possible on the B8500 through the use of multiple "stations" in the Central Processor. Each station has an ultra-fast memory and queues that enable it to partially or completely perform a program instruction while another station is doing likewise. This "compute-while-compute" time-sharing technique, in concept, is analagous to the Store and Forward method used in communications systems.

## CONCURRENT PERIPHERAL OPERATIONS

Concurrent peripheral operations are possible in a B8500 System because the peripheral device controllers contain the necessary logic, storage registers, etc. to allow each controller to process data going to or coming from one of the devices it controls. The Disc File Controller, shown in Figure 1-3, can be assembling an 8-word byte for transmission to the I/O Module, while the Magnetic Tape Controller can be unpacking a 4-word byte for storing on tape. At the same time, the Communications Module can be buffering the interchange of data between the I/O Module and a peripheral device.

## CONCURRENT INPUT/OUTPUT OPERATIONS

As indicated in Figure 1-3, an I/O Module can interface with peripheral devices over any one of 512 simplex channels at a maximum data exchange rate of 286,000,000 bits per second. Such high-speed data transfers are possible when, for example, the I/O Module is communicating with another data processing system. In general, the number of concurrent operations possible in the peripheral equipment controllers connected to one I/O Module is determined by the maximum rate at which the Data Service Unit can handle data, and by the number and types of peripheral devices required by a particular system configuration.

Figure 1-3. Concurrent Operations in B8500 System

## Computerized Input/Output Module

The B8510 I/O Module is capable of simultaneously servicing up to 512 simplex channels and contains an independent processing capability which permits it to perform routine duties without the need to interrupt the processing modules. One of the primary functions of the I/O Module is to automatically (without Central Processor intervention) buffer, into high-speed disk files, the low speed data arriving over communications lines from remote stations. The Central Processor can then service all remote stations from the high-speed disk files and is not inefficiently tied to a lowspeed device, such as a card reader.

The most important feature of the I/O Module is its independence from the Central Processor. In effect, the I/O Module is a separate computer with its own local memory, logic, arithmetic, and communications capabilities. Because the I/O Module provides channels for all transfers of data, such as transfers between the peripheral storage devices and Main Memory, or transfers between two peripheral devices, data transfers are effected independently of direct control from the Central Processor.

## ALLOCATION OF I/O CHANNELS

The numbers and types of devices that can be connected to an I/O Module depend to some extent on how the 512 simplex (one way) channels are utilized. Data is transmitted over a channel one "byte" at a time. A "byte" can consist of 8 words, 4 words, one word, or less than one word (i. e. groups of bits that are submultiples of 48). The 512 simplex channels consist of 256 input channels and 256 output channels, and are allocated as follows:

| Channel Number Byt | te Size                        |

|--------------------|--------------------------------|

| 17 through 48 4 w  | vords<br>vords<br>vord or less |

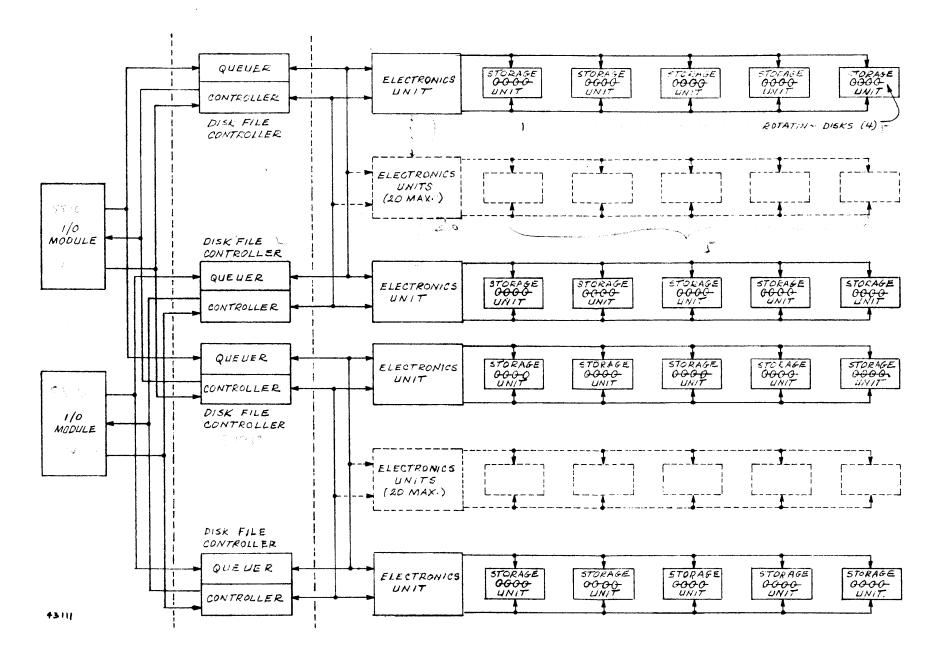

The disk file controllers use 8-word bytes and therefore exchange data over channels 1 through 16. Each disk controller requires one input and one output data channel, plus an additional output channel for the disk queuer. The queuer channels may be from number 49 to 512, as the byte size is not more than one word. Thus one I/O Module can accommodate eight disk file controllers and 800 disk storage units for a total disk file storage capacity of 1.6 billion (48 bit) words. Additional disk file storage requirements are met by using additional I/O Modules.

The magnetic tape controllers use 4-word bytes, and exchange data over channels 17 through 48. Because the magnetic tape system requires simultaneous transmission of data in two directions (duplex), each tape controller requires one input and one output data channel. One I/O Module can accommodate up to 16 tape controllers and 128 tape transports.

## System Expansion

The expansion of the B8500 is enhanced by the modular design concepts implemented in both equipment and programming areas. Additional Processor, Memory, and I/O Modules can be added without modifying existing programs or equipment. Programming systems are designed to utilize whatever equipment is available, and, if more equipment is made available, it is used with a consequent increase in information throughput.

## **Executive Scheduling Program**

## DYNAMIC ALLOCATION OF EQUIPMENT

One of the principal objectives of the Executive Scheduling Program is to dynamically allocate the equipment modules-processors, memory, I/O channels, etc., to a constantly changing set of jobs and thereby achieve a high degree of utilization for all modules. As defined on page 1-6, sharing equipment modules among many programs is called multiprogramming. The ESP goes a step further by multiprogramming a set of jobs that consist of both user requests and operating system functions. As an example, the service functions for jobs that are running or being readied to run are entered in the set of jobs to be done (Hot Job Table) along with the main job entries, and the whole set is multiprogrammed (and multiprocessed if more than one processor is in the system). The segmentation of programs permits a job to be executed with limited memory and the job's requirements for equipment modules are handled dynamically through the course of its execution.

## MEMORY PROTECTION

Memory protection is also included in ESP. Although a job may consist of several software subroutines stored in independent memory locations, both read and write memory protection are provided by data descriptors. Actually much of this protection is provided by hardware design, but it is set up and controlled by ESP.

## CALL-BY-NAME FILING SYSTEM

The filing system of ESP provides reference to files and file items by name rather than by storage medium or absolute address location.

## Interrupt and External Request Capabilities

A comprehensive interrupt system is implemented in the B8500 System to service error conditions and/or requests. The interrupt system provides the Executive Scheduling Program (ESP) with the facility to maintain control of all system functions. ESP includes an interrupt processor program which determines what action is to be taken for each interrupt condition. The interrupt system utilizes a 70-bit condition register and a 70bit mask register. All interrupts are maskable, i.e., a bit in the condition register is set whenever a particular condition exists, but the processor will not respond to the setting of the condition bit unless the corresponding mask bit is set. The mask, then, serves as a multilevel control device. When the processor is operating in the normal mode of operation, it may be interrupted by any unmasked interrupt condition. Once the processor is operating in the control mode of operation, it can only be interrupt conditions (e.g., parity error, no access to memory, etc.) regardless of the mask register settings.

External requests are recognized by the I/OModule. Once the requests are recognized, the I/O service programs may begin the necessary response to the request and accept all further data from the requesting peripheral equipment. A large number of external requests are treated solely by the I/O Module and do not require any further processing. If the request requires central processor handling, entries are made into the job tables for ESP. and the request is scheduled and serviced as a standard I/O procedure. Thus, the normal service to other peripheral equipment is not disrupted. Only a small number of external requests result in immediate interrupts of the central processor.

## Compilers

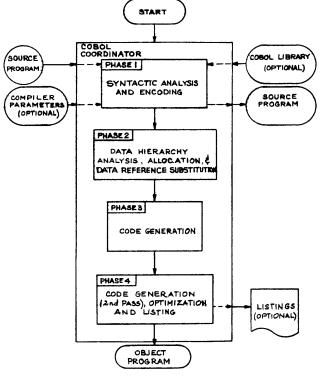

The ALGOL compiler uses the compiling technique known as recursive descent syntactic analysis. This technique compiles quickly, makes modifications easier, and produces efficient object code. The ALGOL compiler implements virtually all of ALGOL-60 and provides extensions for I/O operations, partial word operations, string manipulation, and diagnostics.

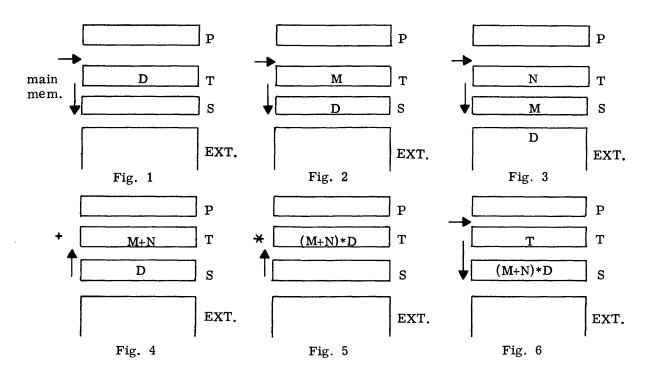

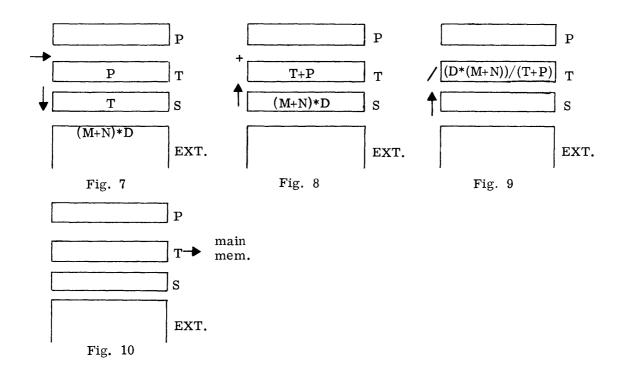

The FORTRAN IV compiler implements the A.S.A. FORTRAN IV language. The compiling is done in one pass using conventional precedence scan techniques. The hardware stack (p. 3-11) used in the B8500 makes this type of analysis very fast.

The COBOL compiler implements D.O.D. COBOL-61, extended. Data segmentation and the ability to independently compile program segments are also included.

Source language programs written in ALGOL, COBOL, or FORTRAN, can be placed in the system's library, and called upon for insertion in other source language programs. The borrowing program need not be written in the same language as the borrowed program.

## **CHAPTER 2**

## **PROGRAMMING FEATURES**

## EXECUTIVE SCHEDULING PROGRAM

## Introduction

The Data Processing Operations Manager, in today's working environment, is faced with the following situation:

1. He has a large number of programs that need to be processed with different priorities and that are scheduled at various times of the day or week or month.

2. He wants to make the most efficient use of a limited number of peripheral devices, but he is willing to sacrifice efficiency if required to meet schedules. For example, he has a large processing work load and uses several complete computer systems to meet his schedules, even though he knows he could save money using one large system with the capability of parallel processing, multiprocessing, and multiprogramming.

3. If a peripheral device or a unit of the computer malfunctions, he loses the use of the computer until he can substitute an alternate unit, or an alternate job, if possible.

4. He needs to know in advance when the system will require data inputs so that valuable computer time will not be wasted while "setting up". To meet the challenge of situations like the one above, the B8500 System has an internal, nonhuman controller, supervisor or operating manager. We call this internal overseer the Executive Scheduling Program; ESP for short. The name is aptly chosen, because it is the administrative program to which all other "worker" programs report for guidance as to their execution. In earlier Burroughs data processing systems, the forerunners of ESP were called MCP and AOSP. No matter what it is called, it is most important to know what it is and what it does. Let us delve further and examine how this nonhuman operations manager, in accomplishing its many functions, does meet the needs of today's operating environment.

## What Is The Purpose Of ESP?

The purpose of the Executive Scheduling Program can be summed up in one sentence. ESP schedules all services (such as memory allocation, loading of memory, assignment of system components both equipment (hardware) and programs (software)), to achieve the maximum utilization of all components of the System. To illustrate, a large number of active programs requiring various services are present in the System, and their current status and required service are recorded. As some component of the System becomes available, e.g., processor, memory space, or a peripheral device, the component is assigned to the active job of highest priority requiring it. An important concept to remember is that each component of the system provides a 'unit' of service, and then goes on to service another program. The main function of the Executive Scheduling Program, then, is to keep track of the services required by programs and to schedule these services as components (hardware or software) become available.

## Of What Does ESP Consist And Where Is It Located?

ESP is a master program (software), comprising many special routines that provide automatic control over those functions listed below. These special routines can be logically divided into two groupings: Executive Routines and I/O Routines.

## FUNCTIONS OF THE EXECUTIVE ROUTINES

The Executive routines perform the following functions:

1. Handle analysis and service of internal (operational, error, and power) interrupts.

2. Schedule the computer and peripheral equipment, including remote terminals.

3. Handle program loading, file retrieval, and file maintenance.

4. Handle system protection and recovery, including memory and file protection, reruns, individual program recovery, and report on the current statur of programs being executed and being scheduled.

## FUNCTIONS OF THE I/O ROUTINES

The I/O routines perform the following functions:

1. Perform accessing commands, including scheduling, error checking, return facilities, and direct the transfer of data to file handler buffers.

2. Process the file handler functions.

3. Perform communications operations, including receiving input communications data, activating a user's program to process the data, accepting output communication data from the user program, and transmitting this data.

ESP resides in three separate locations in the B8500 System. It is stored on magnetic tape as the primary source for changes made to it. The complete program is also in disk storage, and serves as the primary source while operating. Segments of ESP are always in Main Memory for program execution. Main Memory contains enough of ESP to call forth from disk storage whatever other segments are required to perform a task.

## What Can ESP Accommodate?

ESP is written to operate on the minimum B8500 System configuration, or to accommodate the maximum B8500 System configuration. This approach permits easy inclusion of new modules to the system, and permits the dynamic readjustment of the system in the event of a module failure.

## What Does ESP Do?

As stated before, ESP is composed of special routines that provide automatic control over such functions as scheduling, program loading, allocation of memory, input/output operations, and time sharing of processors in the multiprocessing of user programs. In doing these ESP automates many of the functions that were previously performed by an operator. ESP controls the environment and operation to the extent that the major action of the system operator is one of response to system needs rather than offering direction to the system, as shown in the following examples:

## SCHEDULING

One of the operator's tasks which has been automated is the scheduling of the processing system. ESP schedules jobs automatically according to priorities, time-of-day, deadlines, etc. ESP even informs the operator of the requirement for data (files) or special forms (checks, etc.) in advance of actual processing start time. The operator can then ensure that the data and forms are available to the system when required. ESP can make such advance requests because, as it schedules devices and programs, it is aware of the requirements of all programs that are to be run. Due to the advanced software approach of the Executive Scheduling Program the operator need not be aware of precisely which jobs are being executed during a given instant.

## ERROR RECOVERY

Another task taken from the operator is error recovery. Files that have been altered by a program and are subsequently found to be in error, are restored by ESP with a minimum of operator intervention. Copies of all altered records are placed on an audit trail tape for reference and available for reconstruction using standardized recovery routines.

## USAGE ACCOUNTING

Still another function assumed by ESP is accounting and reporting. Processor usage statistics are accumulated by ESP. ESP maintains records of user program processing times for billing and accounting.

## **Uniform Program Structure**

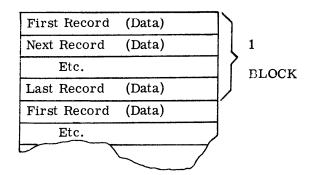

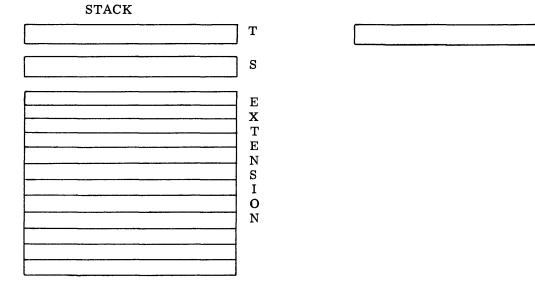

Program segmentation is a basic requirement of a time sharing system having many users, because it permits a large number of active programs to be present in the system, concurrently. A B8500 program may be considered as the output of one compilation, consisting of: program segments, data segments, an operand stack extension, a working storage segment, a program reference table, file list, CHORE (CHain Of Runs Executive) working area, cold job table, and a hot job table (Figure 2-1).

An active program (one that is in the hot job table) must retain in main memory one program segment, an operand stack, a working storage segment, and a program reference table. A large program may also require additional program and data segments during its execution. Whatever segments are required the allocation of these memory segments is provided at the time the program or data segments are referenced, through descriptors in the program reference table. The descriptors define the segments as they appear on disk storage. When the segments are allocated in main memory, the descriptors are altered to provide a means of communication between the separately allocated segments within main memorv.

#### **PROGRAM SEGMENTS**

A program segment is a logical, independent grouping of instructions and constants which is reentrant. The maximum segment size is 4096 words. Therefore, the output of a compilation may consist of many program segments. The compiler must provide a description of the linkage between program segments and external procedures called by the object code. All computer-generated program segments are independent of position in main memory. They can be placed anywhere in main memory and be executed relatively from the starting position of each segment. The Base Program Register (BPR) contains the absolute address of the starting point of the program segment currently being executed. At any time, the program step within the segment being executed is defined by the Program Count Register (PCR). The PCR designates not only the word but also the syllable (all relative to the BPR) that contains the operator presently being executed in the Advance Station within the Central Processor

When a program jump to another segment occurs, the BPR will be altered to reference the starting position of the newly called segment. The PCR will contain the relative address of the first instruction to be executed within the new segment.

Program segments can only be read and are protected against accidental modification by placing them outside the area bounded by the Memory Bounds Registers, which define the read/write areas for a program. Program segments are referenced by program descriptors (in the program reference table) which must have an appropriate tag configuration. This prevents reading the program segments as data objects.

## DATA SEGMENTS

A data segment is a block of storage which is accessed through a PRT descriptor having alternate bounds tag configuration. Data segments can be shared on a system or run basis. They can be read only or read/write objects. Data segments are used to represent arrays, I/O buffers, and similar constructs which require contiguous memory locations. Data segments are addressed relative to the lower boundary of an alternate bounds descriptor. The alternate lower bounds (ABL) value points to the starting point of the Data Segment, the alternate bounds upper (ABU) value points to the last entry in the segment. These registers provide both read and write memory protection.

## **OPERAND STACK EXTENSION**

The stack extension, located in main memory, is a logical supplement to the central processor's hardware operand stack, and uses the push down concept for evaluation of Polish strings. The memory allocated to the stack extension is dependent upon the amount requested by CHORE. One stack is allocated and will be used by all runs within a single CHORE compilation. Memory protection is provided by the stack bounds upper and stack bounds lower limits. Any attempt to read or write data outside of the allotted area will cause a bounds violation interrupt.

## WORKING STORAGE SEGMENT

The working memory segment contains a user's temporary and Global data. The working memory segment is addressable relative to either the Base Data Register (BDR) or the Base Index Register (BXR). The BDR is the reference point for the Global (Common) data area. Global or Common refers to that data which can be used by all program segments of all active programs. The BXR is the base address for data that is local to the segment of the object program that is currently being processed. When a jump to another segment is executed, the BXR is incremented to provide the new segment with its own local working area. Parameters to be passed to the called segment, prior to the execution of the jump, are stored relative to the new BXR. During the implementation of the jump operation, a return control word is placed in location zero relative to the new BXR. The return control word contains the information required to return to the caller and resume processing. This structure provides the method for subroutine nesting and recursion.

## PROGRAM REFERENCE TABLE

The program reference table (PRT) is a readonly segment and contains program descriptors that will provide links to all segments generated by the compilation. All descriptors within the program reference table are relative to the PRT base register and bounded by the Program Reference Table Limit (PRTL) to prevent a reference beyond the area allocated to the PRT. The compilers generate a PRT entry for each reference to a program segment or a data segment. Each PRT entry consists of a program descriptor, description, and a link.

## Descriptor

The descriptor contains the information required to access a segment and is either a jump control word (used to access program segments) or an alternate bounds word (used to access data segments). The alternate bounds word also applies bounds around the data object, allowing the data object to be allocated outside the normal working area. The alternate bounds descriptor also designates the segment as a read-only or a read/write object.

## Description

The description contains the information required to obtain, establish and control the associated object. Some of the information contained in the description is object name, file name, position in file, size, and type of descriptor required to access the segment.

## Link

The PRT contains one link word per descriptor and is required to link the descriptor to the description of the object. Since all that is required to run a program is one program segment, a PRT, stack and a working storage area, it is very likely that the next segment that is required will not be located in main memory. All references to segments other than the segment currently in process must be made via the PRT. If a segment is not in main memory its descriptor will be tagged "not present" and upon any reference to the descriptor the processor will be interrupted, transferring control to ESP. ESP first deactivates the calling program, keeping track of the program step on which this occurred. Then, utilizing the link word, ESP will find the description of the called object, and through interpretation of the description, ESP will allocate space, and the referenced segment will be loaded into main memory. The proper descriptor for this new segment will be formed and placed in the PRT. The calling program will be reactivated to make a second call on the segment, via the PRT. This time the segment will be present. and processing will continue.

## FILE LIST

The compilers will produce as part of their output a file list. The file list will contain the names and characteristics of all files referenced by the compilation. When the compilation is readied an entry is placed in the generated PRT that points to the file list. The file list, although generated by the compiler, is inaccessible to the user. When the compiler-generated code references a file (for reading, opening, etc.) it will reference through the file list descriptor in its PRT. Parameters such as relative position in file list, record name, block name, etc., are placed in the parameter area prior to execution.

There are three levels of file lists; Compilation, Run, and CHORE. The output of a compilation is a series of program units which can not be further subdivided, for example, a subroutine in ALGOL, or a paragraph in COBOL. A Run may consist of one or many compilations. A CHORE is a collection of Runs which performs a job from start to finish, i.e., "Salary Payroll".

The CHORE file list contains entries for all files used by a CHORE. When a Run is established as being active in the system, the subset of the CHORE file list belonging to the Run is entered into Main Memory and pointers to it are entered in the Hot Job Table (HJT). The Run file list is further subdivided on a compilation basis.

#### CHORE WORKING AREA

The CHORE working area is a segment of memory which is common to all runs within a CHORE. The size of the working area is specified at the CHORE level. This working area is for passing parameters and data from CHORE to Run, Run to CHORE, and Compilation to Compilation. It is a data segment accessible only to user compilations which are part of the series of runs called CHORE. The first word of the working area is reserved for use as the "Sequence Switch". The remainder of the area is free to be used as the need dictates.

At the object program level, this working area is a data segment, with a fixed name and is of the type "CHORE job's" (global). For a CHORE job's segment, in addition to each run being a user of the segment, CHORE is also a user, so the segment remains intact between runs. This segment will always be supplied by CHORE and will be available during the execution of the object (worker) program. It is the responsibility of the compiler, or user, if he desires, to ask for use of the area via a PRT entry.

At object program time, the CHORE working area can be completely modified, if desired. The area is treated the same as any other data segment belonging to the run. At the source language level, the working area can be operated on using whatever mechanisms available in the particular source language. "STATUS-SWITCH-1, ON STATUS IS..." is an example of its use in COBOL.

## COLD JOB TABLE

Cold jobs are descriptions of potential candidates for execution. A collection of these cold jobs is maintained in mass storage and called the cold job table. A cold job entry remains in the System from the time it is introduced for running (by CHORE) until its outputs are delivered (completed by the System). Information contained in the cold job entry includes the method of determining its priority, the class of job (conversational, batch, deadline, real time), estimated running time, amount of storage required, predecessor cold job links, age, data files, maximum core segment size, etc. To summarize, the information contained in the cold job table is what is required to introduce jobs into the system, based on current and anticipated computer load matched against the priority of the job to be performed.

## HOT JOB TABLE

It is convenient for descriptive purposes to consider the Hot Job Table as logically divided into three parts: Start, State, and Control/Accounting.

<u>Start:</u> Within the program structure and other objects which constitute the requirements for a run, the start portion of the HJT is the link between the external structures of interrupt responders, allocators, filing, etc. The start portion of the HJT is nothing more than a PRT consisting of a few entries corresponding to the run's stack, file list and first program structure.

State: The information which must be stored in order to obtain a "picture" of an active object program so that, if it is interrupted, it can be resumed at a later point in time. The interrupted process is resumed by restoring the saved information so that it appears that the process has never been interrupted. This information consists mainly of processor registers and conditions of flip-flops.

<u>Control/Accounting</u>: This information includes such items as status, I/O counts, time counts, abnormal condition exits (overflow, EOF), priority, links to its associated Sleep Table, Cold Job Table, and File List, etc.

## **Interrupt System**

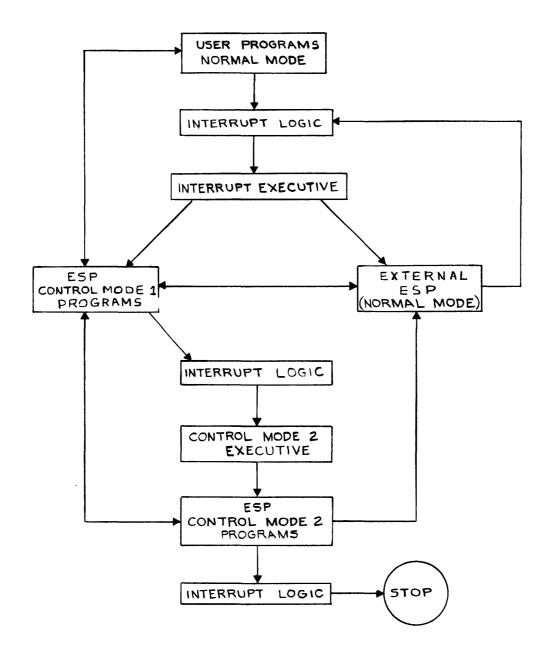

The B8500 central processor has a very comprehensive interrupt system, detecting 70 error and system control conditions. (See Table of Interrupts.) Upon interrupt or an ESP call the central processor is transferred from User program control to ESP program control, i.e., from Normal mode (User mode) to control mode 1 (ESP Mode). The central processor has three modes of operation, Normal mode, Control mode 1, and Control mode 2 (the latter two are ESP modes). Normal mode has a restricted instruction set and a maximum number of allowable interrupts. The control modes have a complete instruction set and minimum number of allowable interrupts. A control mode program can attempt to determine the cause of a normal mode interrupt by minimizing the possibility of further interrupt. During the processing of a User or worker type program in Normal mode the interrupt conditions that are allowed to interrupt the User's execution are restricted by the ESP. This is accomplished by controlling the content of the User's interrupt mask register.

Each time an allowable interrupt occurs and the processor is placed in a control mode, entries

must be made in the Hot Job Table or Sleep Table describing the temporarily suspended program structure. A Hot Job Table entry is made upon transfer of processing from a User program to ESP. The Hot Job Table contains three sections; start, control and accounting, and state. For each interrupt the state section contains a record of the central processor's registers at the time of interrupt and a status indication of the reason this User structure has been suspended.

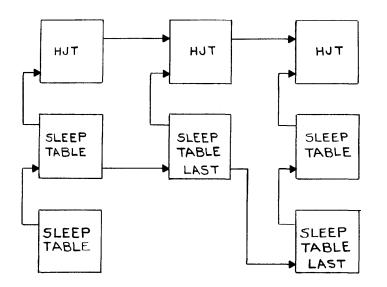

The sleep table entry space is allotted at the same time space is allocated for the rest of the program structure. A sleep table entry is one created upon the temporary suspension of an ESP process, and contains all of the values required to resume the suspended ESP process. There is at least one sleep table space assigned to each HJT. One sleep table entry is made for each ESP process that is waiting to be resumed. Each sleep table entry contains a status field indicating whether it is ready to run, whether it is waiting for an I/O operation, etc. Each sleep table entry is linked to its corresponding HJT, and to subsequent sleep entries, if any; otherwise, it is marked as the last sleep table entry in the chain connected to the HJT. Sleep table entries are also linked to all other sleep table entries in order to facilitate scanning (see figure 2-1.)

Figure 2-1. Hot Job Table and Sleep Table Linking

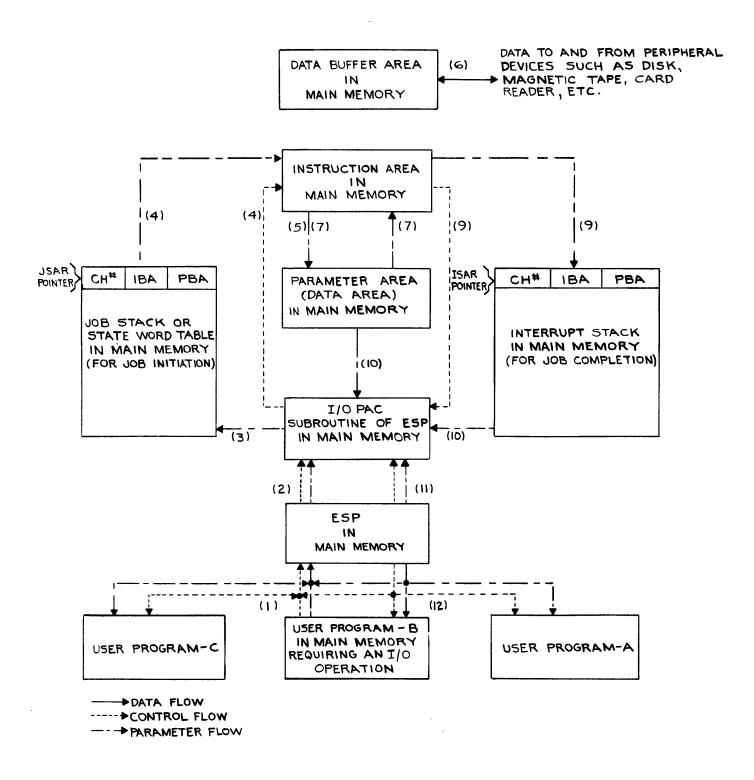

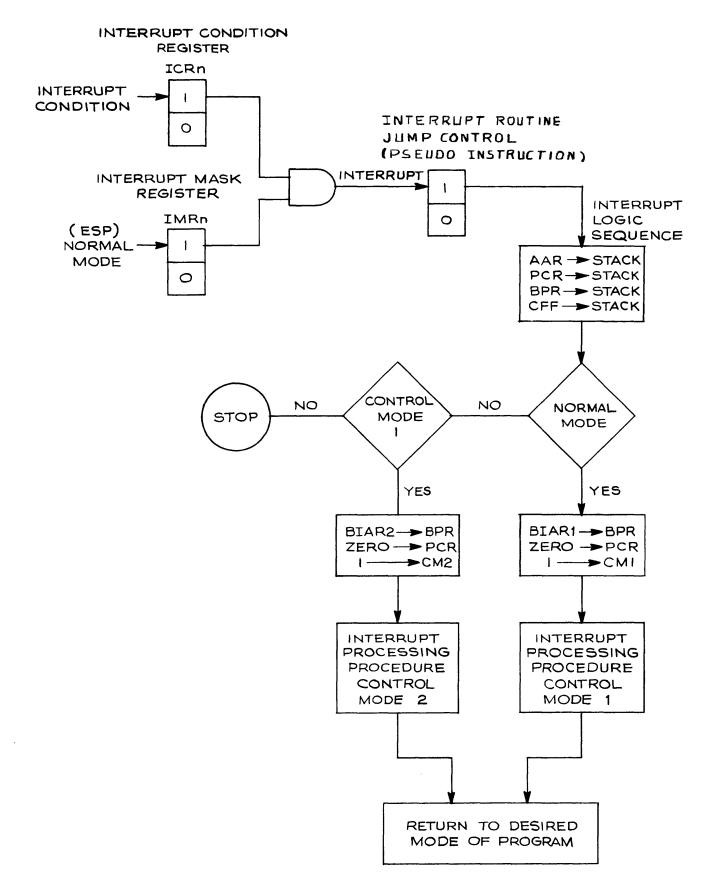

After entering control mode 1 (see Figure 2-2), a processor may be interrupted regardless of the mask register setting: by computer noaccess-to-memory condition, computer parity error, stop instruction, etc. An interrupt occurring during control mode 1 will cause a processor to enter control mode 2. The occurrence of any of the above interrupt conditions while in control mode 2 will cause the processor to halt.

#### HARDWARE FUNCTIONS AT INTERRUPT

The transfer from User program execution (Normal Mode) to ESP interrupt service program execution (control mode 1) is accomplished by the central processor logic, after all Instructions in the final instruction queue (FINQ) have been executed. The current base program register (BPR), program count register (PCR), ADVAST address register (AAR), and specific control flipflops are placed in the operand stack. The current value of the base interrupt register number 1 (BIAR1) is placed in BPR. The value of BIAR1 is determined by ESP (at the time the User structure is actuated) and designates the base address of the interrupt service routine. The program count register (PCR) is set to zeros. The next instruction to be executed is taken from the memory location indicated by BPR and PCR. The interrupt service routine will make a HJT entry for the User structure, link the HJT entry into the HJT priority chain, test for the interrupt condition, and transfer control to the ESP subroutine indicated by the interrupt. Upon completion of interrupt service the HJT status field is set to "ready to run". The processor then looks for something to do. It scans the sleep tables and the hot job tables and selects the program with the highest priority that is ready to run. At this time the loading of the processors is also evaluated to determine if more programs can be scheduled on the System.

#### **MULTIPROCESSOR INTERRUPTS**

The B8500 System is a multiprocessor system with all processors physically identical. There is no master-slave type of relationship, therefore special care is taken to insure that not more than one processor will be interrupted by the same system control interrupt, i.e., I/Ocomplete. This is accomplished by ESP controlling, for each processor the individual mask registers that determine which conditions are allowed to interrupt that processor. Also, critical areas of the interrupt service routines of the ESP are "locked out" with software controls. For example, if two processors attempt to use the same "critical" interrupt service routine at the same time, the first processor will set a software "lock" upon entrance to the routine, and the second processor, upon finding the routine locked, will be diverted to another function.

## **Functions Of ESP**

#### INTRODUCTION

Although CHORE, Collector/Scheduler, and Interpreter/Controller routines are considered part of ESP, they are implemented as user programs. Hence, these three routines are called "External ESP" programs. Communications between these programs and the rest of ESP, called "Internal ESP" (Filing, I/O, Allocation, etc.), is accomplished as follows:

External to External-Procedure jump, segment jump as appropriate, tables accessible to routines communicating with each other, i.e., identical to methods used by normal user programs as produced by ALGOL, FORTRAN, etc.

Internal to Internal-Procedure jump, segment jump, or special transfers where required (e.g., switch BDR/BXR), via PRT global area, and tables or queues.

External to Internal-By macro call. It is highly desirable that this interface be the same as that for any user program and the ESP. Any special interfaces required are kept to a minimum. System tables are used both internally and externally.

Internal to External-Internal answers to external macro calls, common tables.

#### EXTERNAL ESP PROGRAMS

External ESP consists of the following functions:

- 1. CHORE (CHain Of Runs to be Executed)

- 2. Collector/Scheduler (C/S)

- 3. Interpreter/Controller (I/C).

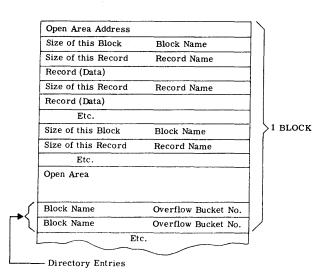

Figure 2-2. Interrupt Flow of Control

#### CHORE

The scheduling concepts implemented on the B8500 Computing System require that the system has information concerning the acquisition and processing of computer tasks. The conventional method of using control cards becomes inefficient, because most information about tasks can be prestored, and can be called automatically with or without parameters. Using this method, control cards are only needed to supply parameters to prestored tasks and to supply data regarding deviations from normal processing.

A run is defined as the execution of the combined outputs of one or more compilations. It is desirable to connect runs (which could have originated from different source languages) into a single process. It is also desirable to have decision making and parameter passing as allowable functions in the mechanism which combines runs.

A language has been developed in which a chain of runs is specified to the Operating System (ESP) so that the chain of runs can be scheduled and executed efficiently. Specifications in this language are called CHORE (CHain OF Runs Executive). The CHORE compiler accepts a source routine written in the CHORE language and produces a directive list that is used by the Operating System to schedule and control the described chain of runs.

A CHORE routine is compiled from source language and filed on a master CHORE file, along with many other CHORE routines. A CHORE routine is activated in one of three methods:

1. Automatically by the system based on a cycle specification in the CHORE file.

2. On command from an external device such as a card reader or teletype.

3. On call from a worker program or ESP.

In any of the above methods, the CHORE routine and associated parameters are merged to form an executable CHORE task which is introduced to ESP for scheduling, collection, and execution.

A CHORE routine is divided into three basic sections. The sections are: IDENTIFICA-TION, DATA, and PROCEDURE.

The Identification Section identifies the CHORE routine to the system. Information such as deadline, priority, and repetition cycle are defined to the system. Parameters required by the CHORE routine on a command call (worker or external device) or a cyclic call are also defined.

The Data Section provides a list of files required to initiate the CHORE routine. Included are all input files and program files used by the CHORE routine.

The Procedure Section contains the logic to be followed in executing the CHORE routine. The Procedure Section can be divided into segments to implement overlay. The Procedure Section is logically divided into run segments to provide the sequencing of control through the runs in the CHORE routine. Statements that control file input, output, and printing are provided, along with statements for the creation of files. Logical statements for transferring control, testing, communication with runs, and overlaying segments are also provided in this section.

An example of processing a CHORE task (a series of runs hereafter called CHORE), using all three functional programs of External ESP follows.

A CHORE is written and punched on cards in the CHORE source language. The source language cards are placed in a card reader and a button at the card reader is depressed, signaling the presence of work to be processed. The I/O PAC Routine of ESP, on detecting the signal, causes a card responder program to be activated by the Collector/Scheduler. After scanning the initial cards, the Responder calls on C/S requesting the activation of the CHORE which calls for execution of the CHORE compiler. The request from the card reader is taken as a command and the CHORE for the CHORE Compiler is entered in a table, from which it will be ultimately scheduled.