|         | and the control of t |

|---------|----------------------------------------------------------------------------------------------------------------|

|         | PREFACE 1                                                                                                      |

|         | RELATED SPECIFICATIONS 1                                                                                       |

| 1 .     | GENERAL DESCRIPTION 2                                                                                          |

| 2       | ARCHITECTURAL CHARACTERISTICS 3                                                                                |

| 3       | SYSTEM STRUCTURE 4                                                                                             |

| 3.1     | PROCESS AND MODULE ADDRESSING ENVIRONMENTS 4                                                                   |

| 3.1.1   | Process Environments 6                                                                                         |

| 3.1.2   | Module Code (Read Only) Environment 6                                                                          |

| 3-1-3   |                                                                                                                |

| 3.2     | Module Data Environment 6 SYSTEM ADDRESSING STRUCTURE 7 System Segment Dictionary 7                            |

| 3.2.1   | System Segment Dictionary 7                                                                                    |

| 3.2.2   | Segment Dictionaries 8                                                                                         |

| 3.2.3   | Segment Distinuaries 8 Segment Descriptors 9                                                                   |

| 3.2.3.1 | LOCAL/GLOBAL Segment Descriptors 12                                                                            |

| 3.2.3.2 | COPY Segment Descriptors 13                                                                                    |

|         | Segment Descriptor Address 13                                                                                  |

|         | Segment Dictionary Address                                                                                     |

|         | Entry Point Address 14                                                                                         |

| 3.3     | PROCESSING STRUCTURE 16                                                                                        |

| 3.3.1   | Process Stack 19                                                                                               |

| 3.3.2   | Process State Record 20                                                                                        |

| 3.3.3   | Process Static Segment Dictionary 21                                                                           |

| 3-3-4   | Module Static Data Segment Dictionary 21                                                                       |

| 3.3.5   | Module Code Segment Dictionary 21                                                                              |

| 3.3.6   | Dynamic (Procedure Local) Data And Parameters 21                                                               |

| 3.3.7   | Process Dynamic Segment Dictionary 21                                                                          |

| 3.3.3   | Addressable S-registers 22                                                                                     |

| 3.4     | INSTRUCTION FORMATS 23                                                                                         |

| 3-4-1   | Operator Description 23                                                                                        |

| 3-4-2   | Operand Description 23                                                                                         |

| 3.4.2.1 | Primary Syllable 24                                                                                            |

|         | Literal (LIT) 24                                                                                               |

|         | Register (REG) 25                                                                                              |

|         | Top-Of-Stack (TDS) 25                                                                                          |

|         | Reference (REF) 26                                                                                             |

| 3.4.2.2 | Extension Syllables 27                                                                                         |

|         | Address (ADDR) 27                                                                                              |

|         | Segment (SEG) Extension 28                                                                                     |

|         | Offset (OFFS) Extension 28                                                                                     |

|         | Length (LGTH) 'Extension 29                                                                                    |

|         | Field Extension (EXTY) 29                                                                                      |

| 3.4.2.3 | ,                                                                                                              |

| 3.4.2.4 | Indirect Addressing And Indexing (IX Field) 30                                                                 |

ii

| 3.5     | DATA TYPES                                             | 32   |

|---------|--------------------------------------------------------|------|

| 3.5.1   | Unsigned Numeric (UN)                                  | 34   |

| 3.5.2   | Signed Numeric (SN)                                    | 34   |

| 3.5.3   | Unsigned Display (U))                                  | 34   |

| 3.5.4   | Signed Display (SD)                                    | 34   |

| 3.5.5   | Hexadecimal (HX)                                       | 34   |

| 3.5.6   | Character (CH)                                         | 35   |

| 3.5.7   | Integer (FI)                                           | 35   |

| 3.5.8   | Single Precision Real (RS)                             | 35   |

| 3.5.9   | Double Precision Real (RD)                             | 35   |

| 3.6     | EXCEPTION MECHANISMS                                   | 36   |

| 3-6-1   | Fault Structure                                        | 36   |

| 3.6.1.1 | Absent Descriptor Fault                                | 36   |

| 3.6.2   | Interrupt Structure                                    | 36   |

| 3.7     | INPUT/OUTPUT STRUCTURE                                 | 37   |

| 4       | INSTRUCTION SET                                        | 38   |

| 4.1     | PROCESS SEQUENCE CONTROL                               | 42   |

|         | History                                                | 44   |

|         | Parameters                                             | 44   |

|         | Locals                                                 | 44   |

|         | The Process Dynamic Segment Dictionary                 | 44   |

|         | Procedure Call Sequence                                | 46   |

| 4.1.2   | Mark-stack                                             | 46   |

| 4.1.2   | Procedure-call                                         | - 51 |

| 4.1.3   | Procedure-return                                       | 54   |

| 4.1.4   | Conditional-exit                                       | 57   |

| 4.1.5   | Branch                                                 | 57   |

| 4.1.6   | Conditional Branches                                   | 58   |

| 4-1-6-1 | Branch-LSS                                             | 58   |

| 4.1.6.2 | Branch-LEQ                                             | · 58 |

| 4.1.6.3 | Branch-EQL                                             | 58   |

| 4-1-6-4 | Branch-NEQ                                             | 58   |

| 4.1.6.5 | Branch-GEQ                                             | 58   |

| 4-1-6-6 | Branch-GTR                                             | `58  |

| 4.1.6.7 | Branch-on-overflow                                     | 58   |

| 4.1.6.8 | Branch-on-no-overflow                                  | 58   |

| 4.1.7   | Process Control And Coordination And Processor Allocat | 59   |

| 4-1-7-1 | Master Controller Commands                             | 60   |

|         | Activate-process                                       | 60   |

|         | Wait                                                   | 60   |

|         | Yield-to-process                                       | 61   |

| 4-1-7-2 | Processor Commands                                     | 61   |

|         | Gostosidle                                             | 61   |

iii

|        | Execute-process 61                                                                                                                                                            |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | Set-PRI 62                                                                                                                                                                    |

| 4.2    | ARITHMETIC 63                                                                                                                                                                 |

| 4.2.1  | Add 63                                                                                                                                                                        |

| 4.2.2  | Add-one 63                                                                                                                                                                    |

| 4.2.3  | Increment 63                                                                                                                                                                  |

| 4.2.4  | Increment-by-one 64                                                                                                                                                           |

| 4.2.5  | Increment Increment-by-one Subtract Subtract-one Decrement                                                                                                                    |

| 4.2.6  | Subtract-one \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                                                                                                                             |

| 4.2.7  | Decir e mente                                                                                                                                                                 |

| 4.2.8  | Decrement-by-one 64                                                                                                                                                           |

| 4.2.9  | Multiply (two forms) 64                                                                                                                                                       |

| 4.2.10 | Divide (two forms) 65                                                                                                                                                         |

| 4.2.11 | Remainder-divide                                                                                                                                                              |

| 4.2.12 | Double (two forms)                                                                                                                                                            |

| 4.2.13 | Halve (two forms) 65                                                                                                                                                          |

| 4.2.14 | Absolute-value (two forms) $V$ $C^{h'}, C^{h'}$ 66                                                                                                                            |

| 4.2.15 | Double (two forms)  Halve (two forms)  Absolute-value (two forms)  Negate (two forms)  100104                                                                                 |

| 4.3    | 10010VE                                                                                                                                                                       |

| 4.3.1  | And (two forms) 67                                                                                                                                                            |

| 4.3.2  | Or (two forms) 67                                                                                                                                                             |

| 4.3.3  | Exclusive-or (two forms) . & 67                                                                                                                                               |

| 4.3.4  | Not (two forms)  RELIGIONAL  Compare  Compare-under-table  Compare-with-zero  Class-test  Range-compare  Bounds-check (two forms)  OPERAND MANIPULATE                         |

| 4.4    | RELIGIONAL 45                                                                                                                                                                 |

| 4-4-1  | Compare 59                                                                                                                                                                    |

| 4.4.2  | Compare-under-table 80                                                                                                                                                        |

| 4.4.3  | Compare-with-zero 69                                                                                                                                                          |

| 4-4-4  | Compare-under-table Compare-with-zero Class-test Range-compare Bounds-check (two forms) OPERAND MANIPULATE Clear Push-operand Move Move-right-justified Move-data Move-repeat |

| 4.4.5  | Range-compare (C) 69                                                                                                                                                          |

| 4.4.6  | Bounds-check (two forms) $h^{\alpha}$ $h^{\alpha}$ 70                                                                                                                         |

| 4.5    | OPERAND MANIPULATE                                                                                                                                                            |

| 4.5.1  | Clear 71                                                                                                                                                                      |

| 4.5.2  | Push-operand Push-operand 71                                                                                                                                                  |

| 4.5.3  | Move But Cluber 71                                                                                                                                                            |

| 4.5.4  | Move-right-justified 71                                                                                                                                                       |

| 4.5.5  | Kove-data Y                                                                                                                                                                   |

| 4.5.6  | Hote repeat                                                                                                                                                                   |

| 4.5.7  | Edit 72                                                                                                                                                                       |

| 4.5.8  | Scan-string-match 72                                                                                                                                                          |

| 4.5.9  | Scan-string-no-match 72                                                                                                                                                       |

| 4.5.10 | Scan-set-member 72                                                                                                                                                            |

| 4.5.11 | Search-set-of-records 72                                                                                                                                                      |

| 4.5.12 | Translate 72                                                                                                                                                                  |

iv

| 17      | Shift-units-right (two forms)        | 73       |

|---------|--------------------------------------|----------|

| 4.5.13  |                                      | 73       |

| 4.5.14  | Shift-units-left (two forms)         |          |

| 4.5.15  | Shift-bits-right (two forms)         | 73       |

| 4.5.16  | Shift-bits-left (two forms)          | 73       |

| 4.6     | POINTER MANIPULATE                   | 74       |

| 4.6.1   | Construct-address                    | 74       |

| 4.8.3   | Push-address                         | 74       |

| 4.8.4   | Push-name (STUFF)                    | 74       |

| 4.7     | BIT MANIPULATE                       | 75       |

| 4.7.1   | Set-bit                              | 75       |

| 4.7.2   | Reset-bit                            | 75       |

| 4.7.3   | Complement-bit                       | 75       |

| 4.7.4   | Test-bit                             | 75       |

| 4.8     | EXPONENT MANIPULATE                  | 76       |

| 4.8.1   | Set-exponent                         | 76       |

| 4-8-2   | Increment-exponent                   | 76       |

| 4.8.3   | Add-to-exponent                      | 76       |

| 4.8.4   | Convert-exponent-decimal             | 76       |

| 4.9     | MISCELLANEOUS                        | 77       |

| 4.9.1   | Initiate I/O                         | 77       |

| 4.9.2   | Reset-overflow-flip-flop             | 77       |

| 4.9.3   | Set-condition-flip-flops             | 77       |

| 4.9.4   | Event                                | 77       |

| 4.9.5   | Monitor                              | 77       |

| 4.9.6   | Read Timer                           | 77       |

| 4.9.7   | Set Timer                            | 77       |

| 5       | COMPATIBILITY MODE                   | 78       |

| 5.1     | COMPATIBILITY MODE PROCESS STRUCTURE | 78       |

| 5.2.1   | FOUR-BIT MODE                        | 80       |

| 5.2.2   | EIGHT-BIT MODE                       | 81       |

| 5.3     | INSTRUCTION REPRESENTATION           | 81       |

| 5.3.1   | INSTRUCTION FORMAT                   | 82       |

| 5.3.2   | OPERATOR CODE                        | 83       |

| 5.3.3   | FIELD LENGTH - FORMAT A              | 83       |

|         | Indirect Field Length - Format A     | 83       |

| 5.3.3.2 | Literals                             | 84       |

| 5.3.4   | ADDRESSES                            | 86       |

| 5.3.4.1 | Non-Extended Format                  | 86       |

| 5.3.4.2 | Extended Format                      | 87       |

| 5.3.4.3 | Address Indexing                     | 87       |

| 5.3.4.4 | Address Controller                   |          |

| 5.3.5   | OVERLAPPING FIELDS                   | 88       |

| 5.5     | LOGICAL UNITS                        | 89<br>90 |

| ノーブ     | LUUILAI UNIIS                        | 4()      |

|         | OUEDE OU ELTD ELOD                                     | 0.0        |

|---------|--------------------------------------------------------|------------|

| 5.5.1   | OVERFLOW FLIP-FLOP                                     | 90         |

| 5.5.2   | COMPARISON FLIP-FLOPS                                  | 91         |

| 5.5.6   | INDEX REGISTERS                                        | 92         |

| 5.5.7   | MODE FLIP-FLOPS                                        | 93         |

| 5.5.7.1 | EBCDIC-ASCII Mode Flip-Flop                            | 93         |

| 5.5.7.2 | User Program Flip-Flop                                 | 93         |

| 5.5.7.3 | BCT Mode Flip-Flop                                     | 93         |

| 6.0     | COMPATABILITY HODE INSTRUCTIONS                        | 93         |

| 6.1     | FIXED LENGTH ARITHMETIC INSTRUCTIONS                   | 96         |

| 6.1.1   | Instruction Formats                                    | 96         |

| 6.1.1.1 | One Address Instructions                               | 97         |

| 6.1.1.2 | 4~Digit Instruction                                    | 97         |

| 6.1.2   | Data Formats                                           | 98         |

| 6.1.3   | OP's 50,51,52,53,54,55,57,58,59 (Integer Instructions) | 98         |

| 6.1.4   | OP's 70 - 79 (Real Instructions)                       | 100        |

| 6.1.5   | OP 84 - ACC (Accumulator Manipulate Instruction)       | 102        |

| 6.1.6   | Setting Proper Sign, Exponent, and Comparisons         | 103        |

| 6.1.7   | Implied Store Operations                               | 103        |

| 6.1.8   | Error Traps                                            | 103        |

| 6.2     | ARITHMETIC INSTRUCTIONS, VARIABLE FIELD LENGTH         | 105        |

| 6-2-1   | OP 01 - INC (Add-Two Address)                          | 106        |

| 6.2.2   | OP 03 - DEC (Subtract-Two Address)                     | 107        |

| 6.2.3   | OP 02 - ADD (Add-Three Address)                        | 107        |

| 6.2.4   | DP 04 - SUB (Subtract-Three Address)                   | 108        |

| 6.2.5   | OP 05 - MPY (Multiply)                                 | 108        |

| 6.2.6   | OP 06 - DIV (Divide)                                   | 109        |

| 6.3     | BRANCH INSTRUCTIONS                                    | 109        |

| 6.3.1   | Address Branch                                         | 110        |

| 6.4     | DP 30 - BCT (Communicate)                              | 111        |

| 6.6     | OP 31 - NTR (Enter)                                    | 111        |

| 6.7     | CP 32 ~ EXT (Exit)                                     | 112        |

| 6.8     | DP 08 - MVD (Hove Data 3-Address)                      | 113        |

| 6.9     | OP 10 - MVA (Hove Alphanumeric)                        | 114        |

| 6.10    | OP 11 - MVN (Nove Numeric)                             | 1.16       |

| 6.11    | OP 12 - MVH (Hove Ward)                                | 118        |

| 6.12    | OP 13 - MVC (Move And Clear Word)                      | 118        |

| 6.13    | OP 14 - MVR (Move Repeat)                              | 119        |

| 6.14    | OP 45 - CPA (Compare Alphanumeric)                     | 120        |

| 6.15    | OP 46 - CPN (Compare Numeric)                          | 121        |

| 6.16    | OP 15 - TRN (Translate)                                | 122        |

| 6.17    | OP 09 - MVL (Move Links)                               |            |

| 6.18    | SCAN INSTRUCTIONS                                      | 123        |

| 6.18.1  | OP 16 - SDE (Scan to Delimiter - Equal)                | 124<br>124 |

| VILUEI  | - VI IV - OV. IJEGU EV VELIKIJE - FUUALI               | 1/4        |

.

## PREFACE

This specification provides the complete, comprehensive description of the system structure; of the arithmetic, logical, string, branching, state switching and input/output (I/O) operations; and of the interruption and fault handling mechanisms that comprise the MS-3 S-Machine.

# RELATED SPECIFICATIONS

The information contained in the following documents is pertinent to this specification.

MS-3 Architecture Votes #1 - #12.

.

### GENERAL DESCRIPTION

1

The system is designed to operate with a Master Control Program (MCP) that coordinates and executes all I/D intructions, handles exception conditions, and supervises scheduling and execution of multiple programs (i.e., time multiplexing of processes).

A program consists of one or more source modules. Source modules consist of symbolic descriptions of algorithms (procedures) and data areas (module "own", process global and procedure local). Source modules are compiled into object modules. A process is the execution of a program and is characterized by a sequential flow of control through invoked object modules.

MS-3 provides facilities for efficient switching from one process to another, traversing through modules, relocation of processes in processor memory and for storage protection.

A 3

## ARCHITECTURAL CHARACTERISTICS

Some of the architectural characteristics of the MS-3 S-Machine are:

Decimal addressing to the digit.

Decimal arithmetic.

2

Addressable S-registers.

Indirect addressing.

Facilities for modular programming.

COBOL type string operations on 4-bit and 8-bit units.

FORTRAN type storage unit oriented operations.

Storage protection via segmentation.

•

# SYSTEM STRUCTURE

3

#### 3.1 PROCESS AND MODULE ADDRESSING ENVIRONMENTS

An environment consists of logical storage partitions called segments. The symbolic name of a segment is called a segment descriptor. Segment descriptors are contained in either an environment segment dictionary or the System Segment Dictionary.

The segments of an environment may be addressed relative to the base of the environment segment dictionary (called local addressing) or they may be addressed relative to the base of system memory (called global addressing).

An addressing environment is characterized (defined) by its environment segment dictionary.

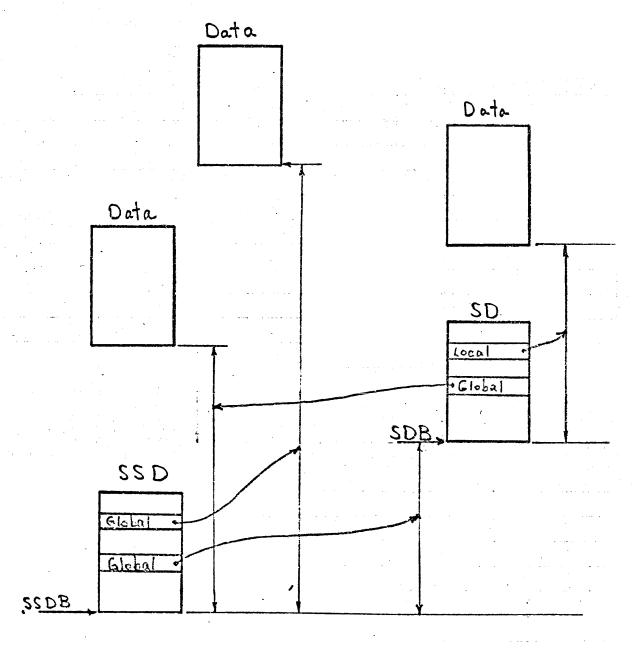

See Figure 3-1 for the logical representation of an environment.

. .

## 3.1 PROCESS AND MODULE ADDRESSING ENVIRONMENTS (Continued).

FIGURE 3-1. The Logical Representation Of An Environment

6

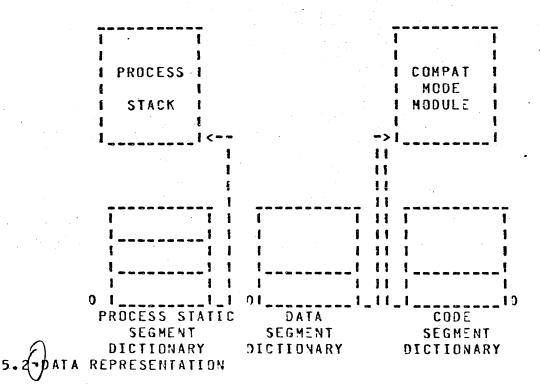

# 3.1.1 Process Environments

Each process has associated with it a process static environment and a process dynamic environment:

The process static environment consists of segments which are global to the process. These include a process stack.

The process dynamic environment consists of segments of data which have been passed from modules other than the current one.

# 3.1.2 Module Code (Read Only) Environment

A code environment contains segments of code and read-only data for a module.

# 3.1.3 Module Data Environment

A data environment contains the static, as opposed to parametric, data segments of a module.

7

#### 3.2 SYSTEM ADDRESSING STRUCTURE

#### 3.2.1 System Segment Dictionary

The System Segment Dictionary (SSD) defines and protects addressable areas of memory via descriptors. This SSD serves as a global collection of descriptors which primarily, but not exclusively, define environment segment dictionaries. The SSD base (SSDB) is the first (lowest) valid address discovered by the processor at initial load time. The SSDB value is known by the S-Machine at all times.

A ~ 8

### 3.2.2 Segment Dictionaries

Segment dictionaries characterize environments. An environment segment dictionary either locates or defines and protects addressable areas of memory via segment descriptors. Environment segment dictionaries are described by entries in the SSD, thus, the base of an environment segment dictionary is SSDB relative.

9

### 3.2.3 Segment Descriptors

Segment descriptors are word addressed (i.e., on modulo 10 digit boundaries). Segment descriptors contain segment dictionary base (SDB) relative addresses (modulo 100 digits) or SSDB relative addresses or SSD indexes.

Segment descriptors are ten digits long and have formats defined by the following fields:

#### 1) descriptor type

The descriptor type field is two bits long. The descriptor type may designate that the descriptor is:

- a) a local (segment dictionary) base relative address (LOCAL)

- b) a global (SSD) base relative address (GLOBAL)

- c) a copy descriptor (an address relative to a SSD entry) (CDPY)

- d) a miscellaneous format (MISC)

#### 2) usage type

The usage type field is two bits long and the values depend on the descriptor type.

If the descriptor type is LOCAL or GLOBAL then the usage type may designate that the area the descriptor defines is:

#### a) Read Only data

Access to the described area is limited to a read operation. Attempts to access the area in some other way will result in an access fault (protection violation).

#### b) Read/Write data

The area may be read from or written into. Other forms of access will generate a fault.

10

#### 3.2.3 Segment Descriptors (Continued)

c) Execute Only code

Data (code) within the area may only be executed. Read or write access will generate a fault.

d) Read/Execute code

Similar to Execute Only but only a write access will generate a fault. This allows Read Only data in a code segment.

If the descriptor type is COPY then the usage type may designate that the descriptor points to:

- a) a segment descriptor of any type

- b) a segment dictionary address

- c) a module code segment address (is the first word of a module entry point pair)

If the descriptor type is MISC then the usage type may designate:

- a) an absent memory area (rest of descriptor is software defined)

- b) a module entry point data address and code offset (the second word of an entry point pair)

Table 3-1 designates the codes for the various type combinations.

11

3.2.3 Segment Descriptors (Continued)

| 1 desc 1 | descr | ı   | usage | 1 | symbol | l meaning l                               |

|----------|-------|-----|-------|---|--------|-------------------------------------------|

| I type I | type  | 1   | type  | 1 | •      | 1                                         |

| 1 1      | code  | i   | · · · | 1 |        | f f                                       |

| 1        |       |     |       | - |        | <b> </b>                                  |

| I MISC I |       | 1   |       | 1 |        | 1                                         |

| 1 1      | 0 0   | i   | 0 0   | 1 | ABS    | I absent - area not in physical mem I     |

|          | 0 0   | ı   | 0 1   | ı | -      | I reserved I                              |

|          | 0 0   | 1   | 1 0   | 1 | EP2    | <pre>1 2nd half of entry point pair</pre> |

| 1 1      | 0 0   | 1   | 1 1   | i | -      | I reserved I                              |

| I LOCALI |       | 1   |       | 1 |        | į                                         |

| 1 1      | 0 1   | ŧ   | 0 0   | 1 | L/R    | I local, Read Only (SDB relative) I       |

| i i      | 0 1   | 1   | 0 1   | • | L/R/W  | I local. Read/Write I                     |

| 1 1      | 0 1   | ı   | 1 0   | 1 | L/E    | I local, Execute Only                     |

| i i      | 0 1   | į   | 1 1   | 1 | L/E/R  | 1 local, Execute/Read Only 1              |

| IGLOBALI |       | i   |       | 1 |        | 1                                         |

| 1 1      | 1 0   | 1   | 0 0   | 1 | G/R    | I global, as above (SSDB relative) I      |

| ii       | 1 0   | i   | 0 1   | i | G/R/W  | "                                         |

| i        | 1 0   | i   | 1 0   | i | G/E    |                                           |

|          | 1 0   | į   | 1 1   | i | G/E/R  |                                           |

| COPY     | • 0   | •   | . • • | ì | 0,2,11 | 1                                         |

| 1 1      | 1 1   | •   | 0 0   | • | SEG    | i copy of a segment descriptor            |

| 1 1      | 1 1   | ,   | 0 1   | i | SD     | dictionary desc I                         |

| 1 6      | 1 1   | 1   | 1 0   | • | EP1    | I first half of an entry point pair I     |

|          | 1 1   | ,   | 1 1   | í | ( L    | I reserved                                |

|          |       | •   |       | i |        | 1                                         |

|          |       | - ` |       |   |        |                                           |

TABLE 3-1. Segment Descriptor Types.

### 3.2.3.1 LOCAL/GLOBAL Segment Descriptors

|   |      |      | 5    |      |      | 9 |

|---|------|------|------|------|------|---|

| • |      |      | 1    |      |      | ! |

| • | •    |      | . 1  |      | •    | 1 |

| • | į    |      | •    |      |      | į |

| 1 | <br> | <br> | <br> | <br> | <br> | 1 |

Type Fields (digit 0)

For LOCAL/GLOBAL descriptors the type fields (T = Descriptor Type - eight-bit and four-bit; Usage Type - two-bit and one-bit) specify how to form an address and what operations are permitted upon the data located at that address.

Size Field (digits 1-4)

The size field specifies the length of the described area in units of 100 digits (the two low-order digits are implied and have a value of zero).

0000 means a length of zero.

9999'00' is the largest segment size in digits.

Base Field (digits 5-9)

The base field specifies the relative location of the described area. A base represents a seven digit number; the low-order digits are implied and have a value of zero. If the type is LOCAL, the beginning of the area is computed relative to the base of the relevant segment dictionary (i.e., the segment dictionary containing the descriptor). If the type is GLOBAL, the beginning of the area is computed relative to the base of the SSD.

A 13

#### 3.2.3.2 COPY Segment Descriptors

# SEGMENT DESCRIPTOR ADDRESS

| 0   |   | 1 |    |   | 5         | . 9    |

|-----|---|---|----|---|-----------|--------|

| 1   |   |   |    |   |           |        |

| 1   | Ī | • | 1  |   | 1//////// | //1    |

| 1 T | ı | S | SD | X |           | / / /! |

| 1   | Į |   |    |   | 1//////// | 111    |

| 1   |   |   |    |   |           | 1      |

Type Fields (digit 0)

This descriptor type represents a "copy" of a descriptor in the SSD.

SSD Index Field (digits 1-4)

The SSD index (SSDX) field contains a (word) index into the SSD, where the "real" descriptor is to be found. Segment numbers are not applied to this type.

# SEGMENT DICTIONARY ADDRESS

| 0   |   | 1 |   |   |   |   |   | 5  |     |   |   | 7 |   |   |   | 9 |

|-----|---|---|---|---|---|---|---|----|-----|---|---|---|---|---|---|---|

| 4   |   |   |   |   |   |   |   |    |     |   |   |   | - |   |   | 1 |

| 1   | ı |   |   | • |   | • | 1 | 1  | 1 1 | • | 1 |   | ŧ |   | 8 | 1 |

| 1 T | I |   | S | 5 | D | X | 1 | 11 |     | 1 | ı |   | S | Ε | G | ì |

| 1   | 1 |   |   |   |   |   | 1 | 1  | 1 1 | • | 1 |   |   |   |   | • |

| !   |   |   | - |   |   |   |   |    |     |   |   |   | - |   |   | ! |

Type Fields (digit 0)

This descriptor type represents a "copy" of a descriptor in a segment dictionary.

SSD Index Field (digits 1-4)

The SSDX field contains a (word) index into the SSD for a descriptor that defines where the segment dictionary of the "real" descriptor is to be found.

Segment Number (digits 7-9)

14

## SEGMENT DICTIONARY ADDRESS (Continued)

The segment number (SEG) is applied to the segment dictionary descriptor to obtain the "real" descriptor.

#### ENTRY POINT ADDRESS

| 0            | 1     | 5              | -7     | 9.  |

|--------------|-------|----------------|--------|-----|

| 1 1<br>1 T 1 | S S D | X IM A S       | KI S E | G   |

| <br>10       | 11    | 15             |        | 19  |

| i 1          | SSD   | * ! *<br>X ! 0 | FFSE   | T I |

Entry points have to do with inter-module procedure call and branching. They must occur in pairs.

Type Field (digit 0)

Digit 0 designates an entry-point-1 (EP1) type of descriptor.

SSDX Field (digits 1-4)

This field identifies the descriptor for the next module's code segment dictionary.

MASK Field (digits 5-6)

This field will specify an interrupt and fault mask, etc.

SEG Field (digits 7-9)

This field contains the segment number of the code segment. This segment is relative to the segment dictionary specified by the SSDX field.

15

# ENTRY POINT ADDRESS (Continued)

Type Field (digit 10)

Digit 10 designates an entry-point-2 (EP2) type of descriptor.

SSDX Field (digits 11-14)

This SSDX identifies the descriptor for the next module's data segment dictionary.

Offset Field (digits 15-19)

This field contains the (digit) offset within the code segment of EP1 at which execution will next commence. The size of this field means that only the first 99999 digits of a code segment may be ENTERed (directly) via an entry point pair.

#### 3.3 PROCESSING STRUCTURE

A process is the execution of a program and is characterized by the sequential flow of control through invoked object modules. Module invocation is accomplished via the process sequence control instructions (Procedure-call, Branch). Called procedures may be located in the current (intra) module or in some external (inter) module.

The system provides for 1) passing parameters to the called procedure, 2) saving the current environment (as appropriate), 3) acquiring a new environment if a procedure external to the current module is being called, 4) accessing data passed by reference, and 5) restoring the correct environment when the procedure is exited.

Intra/inter-module procedure entry history is maintained in a Process Stack. The information contained in this area includes 1) the type of call (intra/inter module), 2) the instruction pointer (segment number and offset), and 3) the location of the previous history information.

A process is specified by naming a process state record (PSR). Each PSR contains the information necessary to reinitiate the process on the processor.

At any time the addressing range or scope of a module being executed as part of a process is defined directly by three environments one pseudo environment and a set of addressable registers and indirectly by another environment.

These are respectively:

- Process static environment. This environment is characterized by the process static segment dictionary.

- 2) Module data environment. This environment is characterized by the module static data segment dictionary. Associated with this environment is a current data segment which allows a short form of operand address description.

- 3) Module code environment. This environment is characterized by the module code segment dictionary. Associated with this environment is a current code

17

### 3.3 PROCESSING STRUCTURE (Continued)

segment which allows a short form of branch address description.

- 4) Procedure parameters and local data (this is the pseudo environment). Storage for these is allocated from a Process Stack which is located via the process static segment dictionary.

- 5) The addressable registers are addressed via a register type operand description and are located via the process state record.

- 6) Process dynamic environment. This environment is characterized by the process dynamic segment dictionary. Segment descriptors for parameters passed by reference are actually located in the process dynamic environment and are referenced via corresponding operand descriptions in the Process Stack.

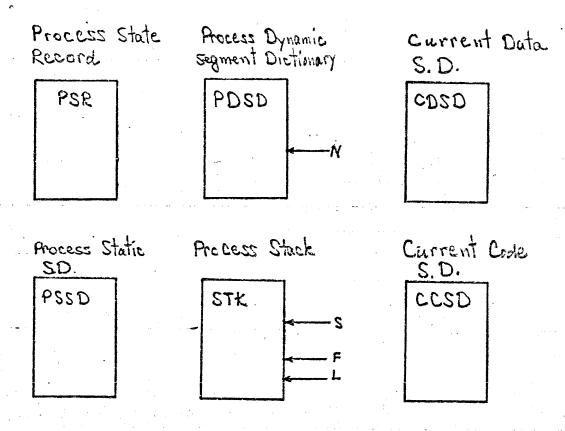

See Figure 3-2 for a diagram of the various addressing environments in a process's direct addressing space.

### 3.3 PROCESSING STRUCTURE (Continued)

FIGURE 3-2. Process Direct Addressing Space.

19

## 3.3.1 Process Stack

By definition, segment zero (the zero'th entry) process static segment dictionary defines the Process Stack area. Space for history linkage, parameters and local variables (temporary storage) is allocated in a LIFO manner Addressing is relative to the last this stack. information deposited by the Mark-stack instruction. information is termed a Mark Stack Control Word (MSCW). Local (L), historical (F) and top-of-stack (S) pointers are associated with the Process Stack. L, F and S are manipulated b y the Mark-stack (MKST), Procedure-call (ENTER) and Procedure-return (EXIT) operators. pointer is also manipulated via the TOS operand type.

Bounds checking on the Process Stack and the process dynamic segment dictionary must be performed whenever their stack pointers are changed. Such checking should use an equal condition only. Thus the fault-handling procedure will not get bounds checks.

20

# 3.3.2 Process State Record

The Process State Record (PSR) is not addressable by the process. This area contains all the variables that are needed for process initiation.

21

# 3.3.3 Process Static Segment Dictionary

The process static segment dictionary is a process wide segment dictionary (referenced by environment number one in an operand description — see section 3.4.2). The process static segment dictionary does not change during the life of the process. This segment dictionary describes areas global to the process.

# 3.3.4 Module Static Data Segment Dictionary

A module static data segment dictionary defines data areas (referenced by environment number two in an operand description) of current interest. The module static data segment dictionary is dynamic in that the current segment dictionary may be changed via the ENTER. EXIT or intermodule branch instructions.

# 3.3.5 Module Code Segment Dictionary

A module code segment dictionary defines those code segments (referenced by environment number three in a transfer of control intruction) of current interest. The module code segment dictionary is dynamic in the same fashion as the module data segment dictionary.

# 3.3.6 Dynamic (Procedure Local) Data And Parameters

Dynamic data and procedure parameters are placed in the Process Stack along with the procedure history. These variables are referenced by environment number zero and no segment number in an operand description.

# 3.3.7 Process Dynamic Segment Dictionary

The process dynamic segment dictionary is a segment dictionary which is not directly accessible by a process, but is used to contain the address of parameters passed by reference. This segment dictionary is referenced by an environment number of zero in an operand description (which contains a segment number) that was constructed in the Process Stack by a Push-name (STUFF) instruction. The

A 22

# 3.3.7 Process Dynamic Segment Dictionary (Continued)

space allocation within this segment dictionary operates in a stack or LIFO manner. The addressing is relative to its base. The MKST and STUFF instructions cause the name (N) pointer to be manipulated. The process dynamic segment dictionary is not addressable via the process static segment dictionary.

# 3.3.8 Addressable S-registers

The S-machine provides sixteen addressable registers for use as index registers or accumulators. Each register is ten digits long. Double length operands may extend over two registers.

23

#### 3.4 INSTRUCTION FORMATS

Instructions are composed of an Operator Description followed by zero, one, two or three Operand Descriptions. Instructions consist of byte modulo syllables which must begin on an even address.

# 3.4.1 Operator Description

The first byte of an instruction contains the Operator Description which is encoded and defines the operation (Op) to be performed. All unassigned Op codes are reserved and will cause a program fault if encountered. Each Op code implies the number of Operand Descriptions which follow.

## 3.4.2 Operand Description

Each Operand Description consists of a Primary Syllable, optionally followed by one or more Extension Syllables. The Primary Syllable may vary in length from one to four bytes. Each Extension Syllable is two bytes long.

24

#### 3.4.2.1 Primary Syllable

The Primary Syllable may be one of four categories: Literal (LIT), Register (REG), Top-Of-Stack (TOS) and Reference (REF). The primary syllables for LIT, REG and TOS are two bytes long. The primary syllable for REF may vary in length from one to four bytes. The first digit of each primary syllable specifies which category the operand belongs to, as well as giving further formatting information for the REF category.

The formats of the Primary Syllables for Literal, Register, Top-Of-Stack and Reference Operand Descriptions are as follows:

## LITERAL (LIT)

| 1 - | • |       |   |     |    |   |   | - 1 |

|-----|---|-------|---|-----|----|---|---|-----|

| ŧ   | 9 | 1     | ٧ | 1   |    | ı |   | 1   |

| ŧ.  |   | - 1 - |   | - 1 | ٥. | Į |   | ı   |

| ł   | 0 | ŧ     | N | 1   | /  | 1 |   | t   |

| 1 - |   | ١.    |   | - 1 | L  | ı | D | 1   |

| 1   | 0 | ì     |   | 1   |    | 1 |   | I   |

| 1 - |   | · i   | Ţ | ŧ   |    | 1 |   | Į   |

| I   | 1 | t     |   | 1   |    | ı |   | I   |

| 1 - |   |       |   |     |    |   |   | - i |

The first digit specifies a literal operand.

V specifies variable or fixed-length operand.

N specifies numeric or string operand.

T is the type, selecting the appropriate ro from the table in section 3.5.

L is the length of the literal in digits.

D is the first digit of data in the literal.

The number of extension syllables which follow is determined by the formula ((L-1) DIV 4).

25

## REGISTER (REG)

The first digit indicates that this is a register operand.

V, N and T are the same as for LIT.

L is the length of the operand in digits.

R specifies which one of the 16 general-purpose registers contains the operand.

No Extension Syllables follow.

## TOP-OF-STACK (TOS)

The first digit indicates that this is a top-of-stack operand.

V. N and T are the same as for LIT.

L is the length of the operand in digits.

The address is assumed to be the current top of the procedure call stack. Use of this form causes the TDS

26

# TOP-OF-STACK (TOS) (Continued)

pointer to be incremented past the end of the operand

(TOS := TOS + L).

No Extension Syllables follow.

### REFERENCE (REF)

|          | <b>-</b> |   |   |   | ~ |     |   |    | - 1 |

|----------|----------|---|---|---|---|-----|---|----|-----|

| 1 7      | ŧ        |   | 1 | ı | 1 | 1   | 1 | 1  | 1   |

| <b>!</b> | 1        | Ξ | 1 |   | 1 |     | 1 |    | 1   |

| 1 1      | ţ        |   | 1 |   | ŧ |     | • |    | 1   |

| 1        | 1        |   | 1 | L | 1 | IX  | • | SS | 1   |

| f X      | 1        |   | 1 |   | f |     | ŧ |    | ŧ   |

|          | 1        | I | ł |   | 1 |     | 1 |    | 1   |

| IS       | 1        |   | į | 1 | ı | · 1 | 1 | 1  | 1   |

| 1        |          |   |   |   |   |     |   |    | - 1 |

Both V and N may not be zero.

Each of L. IX and SG may or may not be present. Thus eight possible formats exist, of one, two, three or four bytes in length.

X specifies the presence of the IX Field.

S specifies the presence of the SG Field.

V specifies the presence of the L Field as well as specifying whether the operand is variable or fixed length.

N. T and L are the same as for TOS.

E specifies the Environment (see section 3.1).

IX specifies the indexing or indirection (see section 3.4.2.4).

SG specifies the segment number.

The number of Extension Syllables is variable (see section 3.4.2.2).

27

#### 3.4.2.2 Extension Syllables

Each Extension Syllable for a Literal operand is of the form:

Extensions for Reference operands may be of type Address, Segment, Offset, Length or Extension. Extension Syllables are fetched repeatedly until an Address syllable is encountered.

#### ADDRESS (ADDR)

If the first digit of a Reference Extension is 0 through 9, the type is Address, and contains a full four digits of address specification. This address is relative to the context established by the rest of the Operand Description.

#### SEGMENT (SEG) EXTENSION

| 1 - |   |     |    |     | 1 |

|-----|---|-----|----|-----|---|

| 1   | 1 | 1   | 1  | i   | • |

| 1   |   | - 1 |    |     | 1 |

| ŧ   | 0 | 1   |    |     | 1 |

| į.  |   | - 1 | SE | G.  | ì |

| 1   | 1 | į   |    | •   | ı |

| 1 - |   | - 1 |    |     | i |

| 1   | 1 | i   | 1  | 1 . | i |

| 1   |   |     |    |     | ! |

A first digit of hex 'B' specifies that the Extension is a Segment type.

SEG field specifies the segment number and overides the S field of the Primary Syllable.

#### OFFSET (OFFS) EXTENSION

| 1 . |   |     |    |     | 1 |

|-----|---|-----|----|-----|---|

| 1   | 1 | 1   | 1  | 1   | • |

| 1   |   | - 1 |    |     | ŧ |

| Ţ   | 1 | •   | •  |     | 1 |

| 1   |   | • 1 | OF | = 8 | 1 |

| 1   | 0 | 1   |    |     | 1 |

| 1.  |   | • 1 |    |     | 1 |

| 1   | 3 | 1   | 1  | 1   | 1 |

| 1   |   |     |    |     | ! |

A first digit of hex 'C' specifies that the Extension is an Offset type.

OFFS field specifies three digits of offset to be added to the address after all indirection has taken place.

#### LENGTH (LGTH) EXTENSION

| Į |   |     |     | 1    |  |

|---|---|-----|-----|------|--|

| ŧ | 1 | ŧ   | 1   | 1 1  |  |

| ŧ |   | 1   |     | 1    |  |

| ŧ | 1 | 1   |     | 1    |  |

| 1 |   | 1 . | LGT | '4 E |  |

| ı | 0 | 1   |     | - 1  |  |

| I |   | 1   |     | 1    |  |

| 1 | 1 | 1   | i   | 1 1  |  |

| • |   |     |     |      |  |

A first digit of hex 'D' specifies that the Extension is a Length type.

LGTH field specifies three digits of operand length.

Values of V and N are set to V=1, N=0 regardless of the values specified in the Primary Syllable. The value of the LGTH field overrides the L field of the Primary Syllable.

#### FIELD EXTENSION (EXTN)

| ŧ |   |   |     | 1   |    |

|---|---|---|-----|-----|----|

| I | 1 | 1 | ŧ   | 1 1 | l  |

| 1 |   | 1 |     | 1   |    |

| İ | 1 | 1 |     |     | ١. |

| Ĭ |   | 1 | EXT | 4 1 | Ì  |

| į | 1 | i |     | . 1 | 1  |

| ŧ |   | Į |     | -{  | Ì  |

| Į | 1 | 1 | 1   | 1 1 |    |

| ŧ |   |   |     | 1   |    |

A first digit of hex "F" specifies that the Extension Syllable is a Field Extension type.

EXTN field specifies three digits which are to be used as the high-order digits of the Extension Syllable which immediately follows this syllable.

EXTN may precede the ADDR, OFFS, or LGTH syllables.

#### 3.4.2.3 Indirect Length

Indirect Length may be specified in the L field of either a TOS or REF operand. The format is as follows:

The two high-order bits of the first digit specify that length indirection is to be used.

R specifies one of the general purpose registers which will contain the actual length to be used. The entire register is used (excluding sign), but the length is checked against the maximum allowed for the specified data type.

### 3.4.2.4 Indirect Addressing And Indexing (IX Field)

The presence of an IX field in the Primary Syllable allows specification of indirect addressing and/or indexing. The IX field is formatted as follows:

| 1 |   | • • |   | . 1 |

|---|---|-----|---|-----|

| ŧ |   | 1   |   | ŧ   |

|   |   | - 1 |   | 1   |

| ı | P | ŧ   |   | ı   |

| ŧ |   | - i | R | ı   |

| ŧ | X | ŧ   |   | I   |

| ŧ |   | - 1 |   | ı   |

| ŧ | I | 1   |   | I   |

| 1 |   |     |   | . 1 |

I = 1 specifies that indirect addressing is to be applied.

X = 1 specifies that indexing is to be applied.

R specifies one of the general-purpose registers which is to be used for an index value.

31

### 3.4.2.4 Indirect Addressing And Indexing (IX Field) (Continued)

P specifies pre-indexing or post-indexing. If P = 0 (pre-indexing) the contents of the specified register are added to the address of the operand before any indirect address fetch takes place. If P = 1 (post-indexing) the contents of the specified register are added to the final address of the operand after all indirection has been resolved.

When indirect addressing is specified, the operand address references a memory location from which an operand description is to be fetched (Primary Syllable and Extension Syllables). The specified location must be an even address. All formats and requirements for Operand Descriptions in an instruction apply to indirectly fetched Operand Descriptions as well.

32

### 3.5 DATA TYPES

The following data types are primitive to the S-Machine. The column of the table is selected based on the V and N bits of an operand description and the row is specified by the type field of the same operand description.

|   |      |    |        |     |            |     |               | _ 1 |

|---|------|----|--------|-----|------------|-----|---------------|-----|

| 1 | Type | 1  | String | 1   | Variable   | 1   | Fixed         | - 1 |

| 1 | Code | 1  |        | Į   | Numeric    | ı   | Numeric       | ı   |

| 1 | •    | 1  | •      | 1   |            | 1   |               | ı   |

| ı |      | ŧ  | V=1.N= | 1 ( | V=1, $N=1$ | 1   | V = 0 • N = 1 | 1   |

| 1 |      | -1 |        | - 1 |            | - [ | ~~~~~         | - 1 |

| 1 | 0    | 1  | НX     | ŧ   | UN         | i   | RS            | 1   |

| ŧ | 1    | 1  | *      | ı   | SN         | ı   | FI            | ł   |

| ı | 2    | 1  | СН     | ţ   | บบ         | i   | RD            | 1   |

| 1 | 3    | 1  | *      | ı   | SD         | ŧ   | null          | ı   |

| 1 |      |    |        |     |            |     |               | - 1 |

Where \* means illegal type.

General characteristics are:

### String

Left justification, padding with blanks, right truncation and no data checking.

#### Variable Numeric

Right justification, padding with zeros, no store on overflow and data is validated. The maximum allowable field length for arithmetic operations is twenty units.

#### Fixed Numeric

No store on overflow.

33

#### 3.5. DATA TYPES (Continued)

The data type may be "null" in any of several cases:

- a) The operator requires only an address.

- b) The type and length is specified at a prior or subsequent level in a chain of indirect addresses.

- c) The type and length of a previous operand is to be used.

The following subsets of the data types are referenced collectively in this document:

```

string (S)

= HX > CH

numeric (N)

= UN, UD, SN, SD, FI, RS, RD

floating-point (R) = RS, RD

= UN, UD, SN, SD, FI

integer (I)

signed-integer

= SN, SD, FI

unsigned-integer

= UN, UD

eight-bit

= UD, SD, CH

four-bit

= UN, SN, FI, RS, RD, HX

eight-bit numeric = UD, SD

four-bit numeric

= UN, SN, FI, RS, RD

four-bit integer

= UN, SN, FI

```

34

# 3.5.1 Unsigned Numeric (UN)

Four-bit units which may contain only BCD values 0 through 9. Used only for arithmetic operations, the validity of the BCD digits is checked, the number is considered to be right justified and there is no store on an overflow condition. The maximum length is 20 digits.

# 3.5.2 Signed Numeric (SN)

Four-bit units where the leftmost unit is interpreted as: C = plus, D = minus, other values are illegal. The remaining units are the same as UN. The maximum length is 20 digits plus the sign digit (21 digits total).

# 3.5.3 Unsigned Display (UD)

Eight bit units which may only contain EBCDIC codes for zero through nine, except that leading blanks are treated as zeros. Used only for arithmetic operations, the units are validated to be "FO" through "F9", the number is considered to be right justified and there is no store on an overflow condition. The maximum length is 20 units.

# 3.5.4 Signed Display (SD)

The same as UD, except that the high-order four bits (zone) of the leftmost unit is treated the same as the leftmost unit in SN. The maximum length is 20 units.

## 3.5.5 Hexadecimal (HX)

Four-bit units. Used only for string manipulation operations, all bit combinations are valid, the contents are left justified in the field and truncation occurs from the right. The maximum length is memory size.

35

# 3.5.6 Character (CH)

Eight-bit units. Has the same characteristics as HX.

## 3.5.7 Integer (FI)

The same as SN except that the number of units (length) is fixed at 9 digits plus the sign digit (10 digits total - the same size as the index registers).

# 3.5.8 Single Precision Real (RS)

This is a unit with one bit signs for the mantissa and exponent (0 = plus, 1 = minus), a six bit exponent (binary power of 10) and the next eight digits are a BCD mantissa. The decimal point is assumed to be to the left of the mantissa. The mantissa is validated to ensure that it contains BCD digits only. The total length is ten digits.

# 3.5.9 Double Precision Real (RD)

The same as RS except that the mantissa is 18 BCD digits. The total length is 20 digits.

36

### 3.6 EXCEPTION MECHANISMS

## 3.6.1 Fault Structure

Faults are defined to be exception conditions which can be blamed on the currently running process. All are handled by:

- Generating a MSCW.

- 2) Inserting one and possibly two parameters into the STK. The first parameter identifies the fault. The second parameter is specific to the kind of fault (see the description of the Absent fault).

- 3) Performing an ENTER to a standard entry point for the type of fault (e.g., PSSD, 3).

#### 3.6.1.1 Absent Descriptor Fault

This fault occurs if fetch trips across a segment descriptor with a usage type of Absent.

The parameters are:

- 1) An indication that this is an absent descriptor fault.

- 2) A COPY descriptor which identifies the offensive segment dictionary entry (this goes in the STK, not the PDSD).

# 3.6.2 Interrupt Structure

See section 4.1.7.

A 37

3.7 INPUT/OUTPUT STRUCTURE

See section 4.1.7.

A 38

# INSTRUCTION SET

4

The following abbreviations are used for operands in instruction descriptions:

O1; O2 ... any operands

S1; S2 ... string operands

N1; N2 ... numeric operands

R1; R2 ... real operands

T1; T2 ... table operands

A1; A2 ... address operands

Operand types are checked to validate that they are in the appropriate subset allowed for an instruction.

Table 4-1 describes the conversions which take place between operands of different data types. When on operand is a sending (SND) field and one a receiving (RCV) field, the sending operand type is converted into the receiving operand type. When two operands are both sending fields, the internal type conversion for an operation is made as follows:

- a) data type precedence is UN, UD, FI, SN, SD, RS, RD, HX, CH

- b) the operand whose type is to the left is converted to the type of the other operand.

Instructions which use different types for special purposes (bit manipulation, exponent manipulation, snifts, etc.) are treated as specified in the instruction description.

No receiving field may overlap any sending field.

The codes used in Table 4-1 have the following meanings:

0 = overflow protection (no store)

F = float

N = normalize

R = right justify

L = left justify, right truncation

T = truncate fractional part

B = pad with blanks

Z = pad with zeros

S = sign is lost

39

### INSTRUCTION SET (Continued)

- 4 = zones are stripped

- 8 = zones are set to 'F'

- + = sign is set to plus

- C = BCD check on appropriate fields

A 40

# INSTRUCTION SET (Continued)

| 1 * R    | 1     |         |       |        |            |                |                | <br>         |                    |

|----------|-------|---------|-------|--------|------------|----------------|----------------|--------------|--------------------|

| S        | 1     | CH      | UN    | I SN I | ו<br>ו ט   | SD             | FI             | RS '         | RD                 |

| i HX     | L     | l [     |       | 0      |            |                | 1 0 1<br>1 0 1 | l 0          |                    |

|          | Z     |         | IRZ I | RZ+ 1  | RZ         | 8 1<br>1 RZ+ 1 | RZ+ I          | N Z+ 1       | N I<br>Z+ I<br>C I |

| CH (     |       | L.      | 1     | 1 0 I  | 1<br>1 0 1 |                | 0 4            | 1 0<br>1 F 4 | 0<br>F4            |

|          | ! Z ! | B  <br> | RZ C  |        |            | RZ+            | RZ+            |              |                    |

| i<br>I I |       | L       | 0     | 0 1    | 0          | <br>  ()       | 0              | <br>         | 0<br>F             |

|          | Z !   | B8 i    |       | RZ+I   |            |                | RZ+            |              |                    |

| SN       | LS    | LS      | 0 S I | <br>   | 0 S        | 0              | 0 1            | 0  <br>  F   |                    |

|          | Z 1   | B8 1    | RZ I  |        | 8 1        | B I            |                | N I          | I N I              |

TABLE 4-1. The Implied Type Conversions For Move Operations.

41

## INSTRUCTION SET (Continued)

| * R<br>* C<br>S * V |                                  |                        | nga gaya                  | ergelos      |                    |                               |              | <br>                  | <br>             |

|---------------------|----------------------------------|------------------------|---------------------------|--------------|--------------------|-------------------------------|--------------|-----------------------|------------------|

| D *                 | і нх                             | СН                     | UNI                       | SN           | ו פט               | SD                            | FI           | RS                    | RD               |

| บอ                  | i                                | I. I<br>I B I          | 4 1<br>1 RZ 1             | 0            | RZ I               | RZ+ 1                         | 4  <br>  RZ+ | N     Z+              |                  |

| SD                  | 1 LS  <br>1 LS  <br>1 4  <br>1 Z | l B                    | 0 S  <br>4  <br>RZ  <br>C | 4 I<br>RZ I  | RZ I               |                               |              | F 4  <br>  N  <br>  Z | _                |

| FI                  | LS                               | l 38 i                 |                           |              | RZ I               |                               |              |                       | D<br>F<br>N<br>Z |

| RS                  | ! LS ! ! T ! ! Z                 | LS I                   | OS<br>T<br>RZ<br>C        | I T I        | 8 1<br>1 RZ 1      | 0 1<br>- 1<br>- 8 1<br>- RZ 1 | 0            | 0    <br>  N  <br>  Z | I O I            |

| RD                  | 1 T                              | 1 T 1<br>1 BB 1<br>1 1 | T  <br>                   | 0   1<br>  T | T 1<br>8 1<br>RZ 1 | 8 I<br>RZ I                   | l RZ I       |                       |                  |

TABLE 4-1 (continued). Implied Type Conversions.

### 4.1 PROCESS SEQUENCE CONTROL

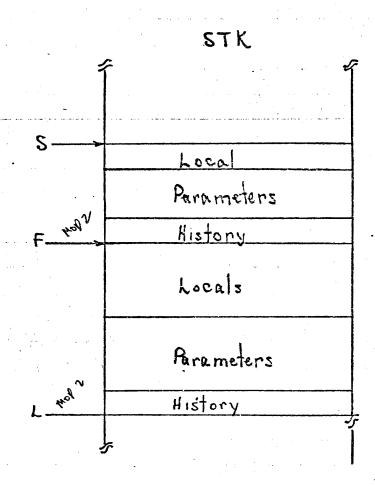

A Process Stack (STK) is maintained as segment zero of the process static segment dictionary. Within this segment, the S-Machine provides a local (pseudo) environment. Procedure call and return operations change the local environment. Two S-Machine registers are used to define this local environment.

The Local (L) register identifies the base of the currently valid local environment. The L register value is always even (i.e., a byte address).

PUSH TOS

The Stack (S) register identifies the first available cell in the Process Stack. It is a digit address.

A third S-Machine register, the History (F) a historical name) register is used in procedure call to reference the most recent history information.

Figure 4-1 illustrates the partioning of the Process Stack.

### PROCESS SEQUENCE CONTROL (Continued)

FIGURE 4-1. The Process Stack.

A

#### THE STRUCTURE OF THE MS-3 S-MACHINE

44

### HISTORY

The information pointed to by the L and F registers is tendigits (one word) of history information. This information is placed in the STK by the Mark-stack (MKST) operator as the first instruction in the procedure call sequence. The history word allows the S-Machine to recover the proper (previous) state following a Procedure-return (EXIT) instruction.

### **PARAMETERS**

The next area in the local environment contains any parameters passed to the procedure. Such parameters are placed in the stack by operations which specify the top-of-stack type destination operand. Parameters may also cause information to be placed in the process dynamic segment dictionary (PDSD).

### LOCALS

The third area in a local environment may contain local storage for the procedure.

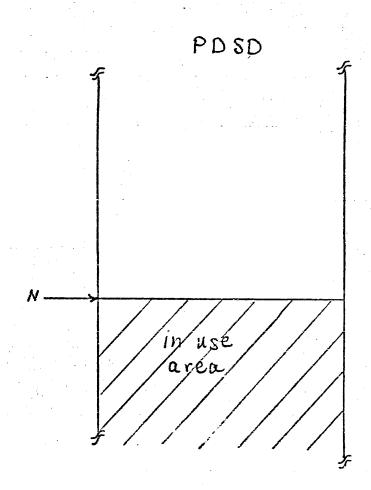

## THE PROCESS DYNAMIC SEGMENT DICTIONARY

In order to pass parameters by reference (address) in a secure fashion, the PDSD is used. The PDSD operates in a stack like manner; information is entered as a result of the Push-name (STUFF) and Procedure-call (ENTER) operators and is removed by the EXIT operator. The PDSD is word oriented and data is always on word (modulo 10 digit) boundaries. The S-Machine maintains a Name (N) register to the first free word in the PDSD. Figure 4-2 illustrates the PDSD.

# THE PROCESS DYNAMIC SEGMENT DICTIONARY (Continued)

FIGURE 4-2. The Process Dynamic Segment Dictionary.

46

## PROCEDURE CALL SEQUENCE

The normal procedure call consists of:

- 1) Executing a MKST operator to record appropriate history information (F and S will be changed).

- 2) Build parameters in the Process Stack (S and possibly N will be changed).

- 3) Execute an ENTER operator, specifying where to transfer control. ENTER will record necessary return information and establish a new local environment.

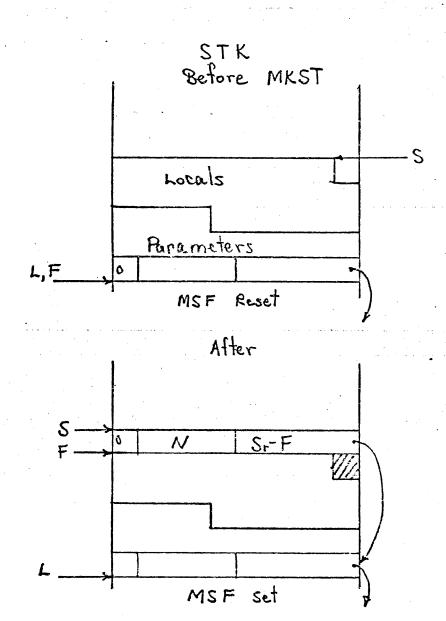

## 4.1.2 Mark-stack

MKST

The MKST operator causes a word (10 digits) of history information to be entered into the Process Stack. The S and F registers are changed.

STK History Word (Markstack Control Word - MSCW) Format

| <b>340</b> | <b>-</b> 0 |   |   |   |   |   | 5 |     |   | . 9 | ) |

|------------|------------|---|---|---|---|---|---|-----|---|-----|---|

| 1          |            |   |   |   |   |   |   |     |   |     | ! |

| 1          | 5          |   | • | Ŋ | • | 1 |   | D   | L | •   | 1 |

| .1         |            | 1 |   | • |   | t |   | . : |   |     | 1 |

| 1          |            |   |   |   |   |   |   |     |   |     | 1 |

#### S = State Bits

The eight-bit contains the Mark Stack Flag (MSF). The MSF is set by a MKST operator and reset by an ENTER operator. This flag is used during an EXIT operation.

The four, two and one-bits are reserved.

### N = PDSD Pointer

This four digit field contains the value of the N register at the instant of the MKST operation. (Since N is a word address, useful PDSDs are limited to 99990 digits in size.)

## 4.1.2 Mark-stack (Continued)

DL= Dynamic Link

This link tells how to find the immediately preceding MSCW and how to reset S and F. Since MSCWs are to be on an even address, but S might be odd at the time the MKST is executed, some adjustment is performed. The new value of F is to be S rounded up to a byte boundary (i.e., S plus the low order bit of S - call it Sr). Sr-F is stored in the DL field. The low order bit of S also has to be kept (TBS). Local environments are thus limited to 99998 digits.

The sequence of steps is:

- 1) Lay down the MSCW at Sr.

- 2) F := Sr

S := F + 10

3) MSF is set

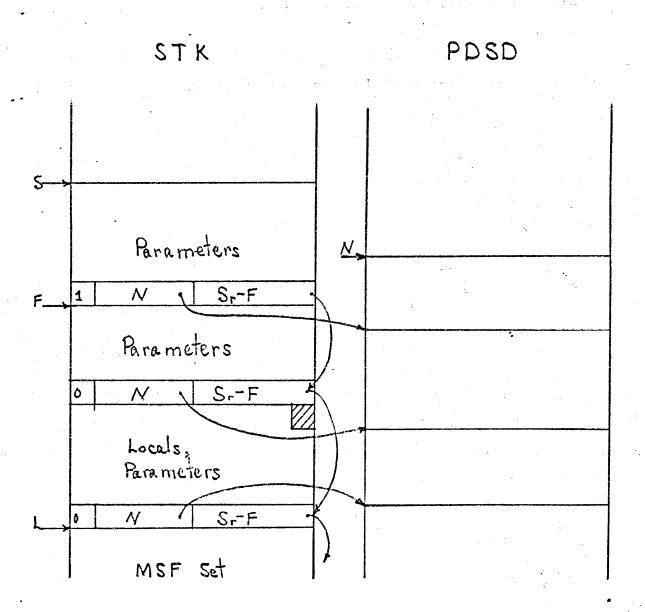

The PDSD is not affected. Figure 4-3 illustrates the mark stack sequence.

# 4.1.2 Mark-stack (Continued)

FIGURE 4-3. The Mark Stack Sequence.

# 4.1.2 Mark-stack (Continued)

### Parameter Building Notes:

The F register always references the most recent MSCW; addressing, however, is performed relative to the L register. Thus data items within the current local environment are addressed as before and may be passed as parameters.

Parameters may be placed in the Process Stack above the history information by using the Top-Of-Stack address type as the destination operand. S is adjusted and checked for stack overflow.

If parameters are passed by reference, data may also be entered into the PDSD and N will be adjusted.

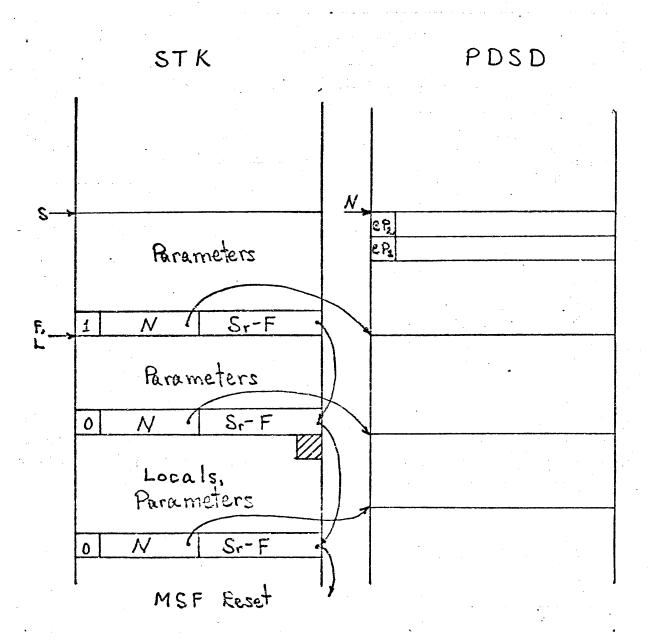

Figure 4-4 illustrates a repeated MKST operation and parameter insertion before an ENTER operation is performed. This situation would arise naturally in case of a procedure call, one of whose parameters was the result of a function call.

# 4.1.2 Mark-stack (Continued)

FIGURE 4-4. A Process Stack With Un-Entered MSCWs.

51

## 4.1.2 Procedure-call

#### ENTER A1

An ENTER operator is executed after any procedure parameters have been placed in the STK to:

- 1) Record the necessary return information.

- 2) Adjust the local environment and, if necessary, the module data and code environments.

- 3) Transfer control to the specified address (A1).

The ENTER operator's single operand specifies the location to which execution control is to be transfered.

The sequence of operations is:

- 1) Operand fetch.

- Return information storage.

- 3) Environment updating.

- 4) Transfer of control.

#### Operand Fetch

A transfer address may be specified in one of two ways;

- a) by a simple address (segment number, offset)

- b) by an entry point pair.

Both of these forms might be preceded by various amounts of indirection. The net result of operand fetch will be a code segment and offset. If an entry point is discovered, new code and data environments are specified as well.

#### Return Information

After operand fetch, two words of return information are deposited in the PDSD at N and N+1. N is set to N+2. The format of these Remember Control Words (RCWs) is exactly that of an entry point pair (segment descriptor types EP1

52

# 4.1.2 Procedure-call (Continued)

and EP2) containing information appropriate to the current state of the S-Machine. Namely, the code and data segment dictionary SSDXs and the segment number and offset within the code stream of the next instruction following the ENTER.

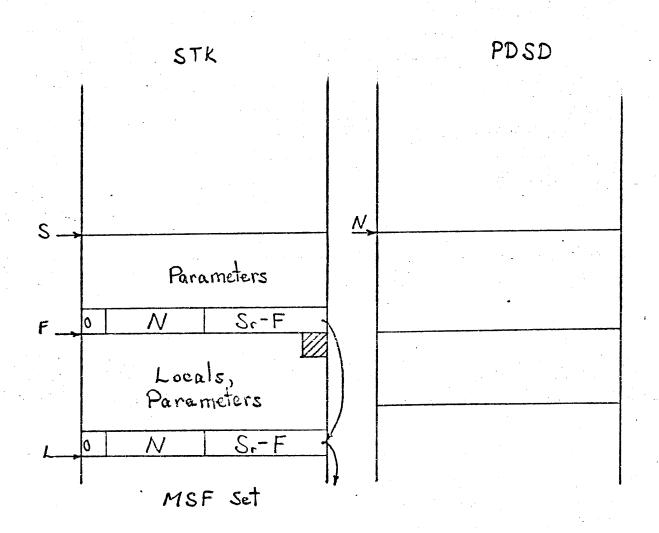

### Environment Updating

- If in the course of operand fetch, an entry point descriptor was encountered, the code and data environments are changed to those specified in the entry point. The final sequence before transfering control is:

- 1) L := F

- 2) MSF is reset

### Transfer Of Control

Control passes to the address generated as the result of fetch (i.e., this address identifies the next code to fetch). Figure 4-5 illustrates the Process Stack state following an ENTER operation.

# 4.1.2 Procedure-call (Continued)

FIGURE 4-5. The Process Stack After An ENTER Operation.

A 54

## 4.1.3 Procedure-return

#### EXIT

It is EXIT's responsibility to restore the state of the caller.

- a) The RCWs at N-2 and N-1 are evaluated to:

- 1) establish the new code address

- 2) determine if the code and data environments must be changed (i.e., if the SSDXs in the RCWs differ from the current processor values)

- Note: The state of the S-Machine should not be changed until this evaluation is complete.

Absent descriptors might be encountered in the process. It is necessary to ensure that the proper machine state is available. The same concept applies during ENTER operand fetches.

- b) The appropriate state of the S-Machine is restored from EP1 and EP2 (i.e., the RCWs).

- c) The appropriate state of the STK and PDSD is restored as follows:

- the word pointed to by the L register is accessed (i.e., this is the MSCW corresponding to the current local environment)

- 2) the N (PDSD) pointer is set to the value in the MSCH

- 3) F := L MSCH.DL

- S := F (odd/even bit)

- 4) L := L MSCW.DL

if the MSCW.MSF bit is set then pick up the MSCW now pointed to by L and repeat step four

55

# 4.1.3 Procedure-return (Continued)

d) Control is passed to the code address generated from EP1 and EP2.

Figure 4-6 illustrates the state of the STK and PDSD after this operation.

# 4.1.3 Procedure-return (Continued)

FIGURE 4-6. The Process Stack After An Exit Operation.

57

# 4.1.4 Conditional-exit

### 4.1.5 Branch

#### BRANCH A1

A branch to an entry point operates just like the corresponding portion of an ENTER operation. In addition a condition may have to be evaluated.

The main difference between ENTER and BRANCH is that no history information is saved for BRANCH.

The sequence of operations is:

- 1) Operand fetch.

- 2) Environment updating.

- 3) Transfer of control.

Operand Fetch

A transfer address may be specified in one of two ways;

- a) by a simple address (segment number, offset)

- b) by an entry point pair.

Both of these forms might be preceded by various amounts of indirection. The net result of operand fetch will be a code segment and offset. If an entry point is discovered, a new code and data environment are specified as well.

Environment Updating

If in the course of operand fetch, an entry point descriptor was encountered, the code and data environments are changed to those specified in the entry point.

Transfer Of Control

Control passes to the address generated as the result of fetch.

58

| 4.1.6 | Conditional | Branches |

|-------|-------------|----------|

|       |             |          |

- 4.1.6.1 Branch-LSS

- 4.1.6.2 Branch-LEQ

- 4.1.6.3 Branch-EQL

- 4.1.6.4 Branch-NEQ

- 4.1.6.5 Branch-GEQ

- 4.1.6.6 Branch-GTR

- 4.1.6.7 Branch-on-overflow

- 4.1.6.8 Branch-on-no-overflow

# 4.1.7 Process Control And Coordination And Processor Allocation

For process control and coordination and processor allocation there exists a Master Controller (MC). The MC coordinates process execution via a bit vector designated the Ready Vector. The bits in this Ready Vector are uniquely assigned, in priority order, to Primary and Supplemental Processes.

A Primary Process is one which specifies the execution of a sequence of processor instructions. A Primary Process has a Process State Record (PSR) which contains (directly and/or by reference) the environment in which those instructions are executed.

A Supplemental Process is primarily a queuing device. A Supplemental Process has a Control Block (C3) whose normal usage is to record the occurance of an external event (such as the completion of an I/O process or the timeout of the interval timer), so that a Primary Process may synchronize itself with reality.

There also exists a Process-Control Vector (PCV), indexed in parallel with the Ready Vector, which locates the Process Record or Control Block, identifies the process type and gives the Running Priority of the process.

The processor has the following registers accessible by the MC:

- PRI The index in the Ready Vector and PCV of the process currently being executed.

- RPR The Running Priority of the process currently being executed. (This is not necessarily the same value as in PRI.)

60

#### 4.1.7.1 Master Controller Commands

The MC accepts the following commands from the processor:

- 1) Activate Process n.

- 2) . Wait.

- Yield To Process n.

The MC also accepts the "Activate Process n" command from the I/O Subsystem and from the Interval Timer or, if the MC is a part of the I/O Subsystem, it may cause this action itself.

## ACTIVATE-PROCESS

#### START N1

The Process-Number, N1. is compared to the processor's RPR register. If N1 is not greater than RPR. bit N1 is set in the Ready Vector and the operation is complete. Otherwise, the processor is commanded to Go-to-idle, the bit in the Ready Vector for the processor's current process (given by the PRI register) is set, the value N1 is placed into PRI, and the processor is commanded to commence execution of that process.

# TIAW

#### WAIT