# V-SERIES SPECIFICATIONS DISTRIBUTION LIST EMSG - MISSION VIEJO

SPECIFICATION NO: 1993 5220 SPECIFICATION TITLE: MEMORY CONTROL & CACHE MOD

REVISION LETTER: D DATE OF ISSUE: 06-23-89

\_\_\_\_\_\_\_

| MISS | SION VIEJO, CA. |        | CONTINUED - MISSION VIEJO, CA.   |

|------|-----------------|--------|----------------------------------|

|      |                 |        | J. RUCKER MS 520                 |

| D.   | ABALOS          | MS 105 | J. SINGLETON MS 205              |

| J.   | BARRETT         | MS 310 | H. SOHL MS 165                   |

| F.   | BEUGER          | MS 380 | S. SOLOMON MS 135                |

| R.   | BIGHAM          | MS 195 | T. STERNAL MS 165                |

| D.   | BRITTLE         | MS 275 | D. STONE MS 285                  |

| R.   | CAIRNS          | MS 235 | W. TERRY MS 215                  |

| c.   | DOOLING         | MS 165 | T. VECCHIARELLI MS275 (2 COPIES) |

| s.   | ESCOBAR         | MS 115 | D. WALSH MS 170                  |

| J.   | GEORGE          | MS 135 | R. WARREN MS 135                 |

| в.   | GOULD           | MS 175 | P. WORCESTER MS 135              |

| F.   | HAAS            |        | J. YETTER MS 165                 |

| D.   | HANSON          | MS 205 |                                  |

| R.   | HARRIS          | MS 135 |                                  |

| Α.   | HATCH           | MS 150 |                                  |

| s.   | HERMAN          | MS 225 | PASADENA, CA.                    |

| J.   | HORKY           | MS 170 |                                  |

| M.   | JACOBS          | MS 165 | J. BURTON                        |

| Μ.   | KALLAL          | MS 105 | J. COLBURN                       |

| c.   | KING            | MS 225 | N. FLEMING                       |

| W.   | LESH            | RSM115 | R. KATHOL                        |

| c.   | LEUTHEN         | MS 170 | C. NUSE                          |

| D.   | MACMILLAN       | MS 285 | W. TREINEN CC 6130               |

| J.   | MARTIN          | MS 195 | J. VANZWALUWENBURG               |

| R.   | MATHEWS         | MS 225 |                                  |

| v.   | MCCLELLAND      | MS 165 |                                  |

| R.   | MENDOZA         | MS 135 |                                  |

| J.   | MOLASH          | MS 135 | TREDYFFRIN, PA.                  |

| в.   | MORRIS          |        |                                  |

| W.   | MURRAY          | MS 165 | A. WORKS                         |

| Μ.   | NAKAMOTO        | MS 195 |                                  |

| М.   | OGRADY          | MS 380 |                                  |

| s.   | PATRICK         |        |                                  |

|      | POTTER          | MS 135 |                                  |

| R.   | QUAYLE          | MS 135 |                                  |

For changes in this distribution list, contact D. Patten, M.V. Release and Configuration.

| n demonstrative de la constante de la constant |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TOTAL PROPERTY AND ALL ALL ALL ALL ALL ALL ALL ALL ALL AL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ARTHUR PROPERTY AND ARTHUR |

| THE PROPERTY OF THE PROPERTY O |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| **************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ***************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| THE PERSON NAMED IN THE PE |

# Company Confidential

1993 5220

# MEMORY CONTROL AND CACHE MODULE

# **ENGINEERING DESIGN SPECIFICATION**

GENERAL SYSTEMS GROUP

ORANGE COUNTY

ISYS RESTRICTED

Entry/ Medium Systems Group PASADENA DEVELOPMENT CENTER

V500 MEMORY CONTROL AND CACHE MODULE

## ENGINEERING DESIGN SPECIFICATION

|     |                        | RE VISIONS                                                                               |                                  |                                                                    |

|-----|------------------------|------------------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------|

| REV | REVISION<br>ISSUE DATE | PAGES REVISED ADDED DELETED OR<br>CHANGE OF CLASSIFICATION                               | PREPARED BY                      | APPROVED BY                                                        |

| А   | ECN 50426              | Initial Issue<br>JUNE 5, 1986                                                            | D. Castle D. Call L. Simpson     | D. Welbourn  H. Li  21:                                            |

| В   | ECN 52003              | Updated to expand the description of                                                     | L. Simpson                       | R. Young  J. Chen  Lau  M. Ho                                      |

|     | 02-24-88               | Cache per REE 099715.                                                                    | Jampson<br>Y. Chang<br>Afu Chang | R. Young  R. Young  A. Gomez  H. Li  N. Fleming  Northern  2/18/86 |

| C   | ECN 95797              | UPDATED TO INCLUDE PAGES 122A, 123A, 127A, 204A, 205A ADDED TO THE END OF THIS DOCUMENT. |                                  | mel K<br>5.23.89                                                   |

The information contained herein is UNISYS RESTRICTED and shall not be reproduced or disclosed to anyone outside of UNISYS CORPORATION without prior written release from the general patent counsel of UNISYS CORPORATION.

EDS25

Entry/ Medium Systems Group PASADENA DEVELOPMENT CENTER

V500 MEMORY CONTROL AND CACHE MODULE

## ENGINEERING DESIGN SPECIFICATION

UNISYS RESTRICTED PAGES REVISED. ADDED. DELETED OR CHANGE OF CLASSIFICATION REVISION ISSUE DATE PREPARED BY APPROVED BY D. Welbourn D. Castle Initial Issue Α ECN 50426 Akilocum D. Cath JUNE 5, 1986 Simpson R. Young /Chen 41, Lau В IECN 52003 Updated to expand the description of M. Ho Simpson 02-24-88 Cache per REE 099715. Gomez Fleming

EDS25

| - |

|---|

|   |

|   |

## UNISYS

GENERAL SYSTEMS GROUP

ORANGE COUNTY

MEMORY CONTROL AND CACHE MODULE

COMPANY CONFIDENTIAL

# ENGINEERING DESIGN SPECIFICATION

| REV | REVISION<br>ISSUE DATE | PAGES REVISED ADDED, DELETED OR CHANGE OF CLASSIFICATION                                                | PREPARED SY | APPROVED BY                   |

|-----|------------------------|---------------------------------------------------------------------------------------------------------|-------------|-------------------------------|

| D   | 6/2 <b>3</b> /89       | To correct errors in header, footer and format; folded in changes made in Rev. C into text of document. | S. Solomon  | Mue 1<br>6/23/89<br>M. Jacobs |

|     |                        |                                                                                                         |             |                               |

|     |                        |                                                                                                         | ·           |                               |

|     |                        | ·                                                                                                       |             |                               |

|     |                        |                                                                                                         |             |                               |

|     |                        |                                                                                                         |             | `                             |

|     |                        |                                                                                                         |             |                               |

| ·   |                        | ·                                                                                                       |             |                               |

'THE INFORMATION CONTAINED IN THIS DOCUMENT IS CONFIDENTIAL AND PROPRIETARY TO UNISYS AND IS NOT TO BE DISCLOSED TO ANYONE OUTSIDE OF UNISYS WITHOUT THE PRIOR WRITTEN RELEASE FROM THE PATENT DIVISION OF UNISYS.'

#### 1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

### TABLE OF CONTENTS

| 1         | PURPOSE                         | 1               |

|-----------|---------------------------------|-----------------|

| 2         | APPLICABLE DOCUMENTS PAGE       | 1               |

| 3         | OVERVIEW                        | 2               |

| 3.1       | COMMANDS                        | 5               |

| 3.2       | CACHE                           | 6               |

| 3.3       | INTERFACES                      | 6               |

| 4         | FUNCTIONS                       | 8               |

| 4.1       | READ DATA COMMAND PAGE          | 8               |

| 4.2       | WRITE DATA COMMAND PAGE         | 9               |

| 4.3       |                                 | 10              |

| 4.4       | WRITE BASE TABLE COMMAND PAGE   | 11              |

| 4.5       | WRITE LIMIT TABLE COMMAND PAGE  | 11              |

| 4.6       |                                 | 11              |

| 4.7       | READ LIMIT TABLE COMMAND PAGE   | 11              |

| 4.8       | READ ERROR REPORT COMMAND PAGE  | 12              |

| 4.9       | READ ERROR ADDRESS COMMAND PAGE | 12              |

| 4.10      |                                 | 13              |

| 4.11      |                                 | 14              |

| 4.12      |                                 | $\overline{14}$ |

| 4.13      |                                 | 15              |

| 4.14      |                                 | 16              |

| 4.15      |                                 | 17              |

| 4.16      |                                 | 18              |

| 4.17      |                                 | 18              |

| 5         |                                 | 19              |

| 5.1       |                                 | 19              |

| 5.1.1     |                                 | 20              |

| 5.1.2     |                                 | 24              |

| 5.1.3     |                                 | 26              |

| 5.2       |                                 | 30              |

| 5.2.1     |                                 | 32              |

| 5.2.2     |                                 | 36              |

| 5.2.3     |                                 | 40              |

| 5.2.4     |                                 | 41              |

| 5.2.5     |                                 | 43              |

| 5.2.6     |                                 | 44              |

|           |                                 | 45              |

| 5.3       |                                 | 46              |

| 6         |                                 | 47              |

| 6.1       |                                 | 47              |

| 6.1.1     |                                 | 48              |

| 6.1.2     |                                 | 50              |

| 6.1.3     |                                 | 51              |

| 6.1.4     |                                 | 51              |

| 6.2       |                                 | 52              |

| 6.2.1     |                                 | 52              |

| 6.2.2     |                                 | 52<br>53        |

| 6.2.3     |                                 | 53              |

| 6.3       |                                 | 54              |

| 6.3.1     |                                 | 55              |

| O • O • T | INTRICKY CONCREMENTOR           | در              |

### 1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

| 6.3.2  | ERROR DETECTOR AND CORRECTOR              |   |   | • | PAGE         | 56  |

|--------|-------------------------------------------|---|---|---|--------------|-----|

| 6.3.3  | OUTPUT INTERFACE                          |   |   |   | PAGE         | 56  |

| 6.4    | ERROR RECORDER                            |   |   |   | PAGE         | 57  |

| 7      | CACHE DESCRIPTION                         |   | • | • | PAGE         | 58  |

| 7.1    | INTERNAL CACHE INTERFACES                 |   | • | • | PAGE         | 58  |

| 7.1.1  | INTERFACE TO AW INPUT QUEUE               | • |   |   | PAGE         | 58  |

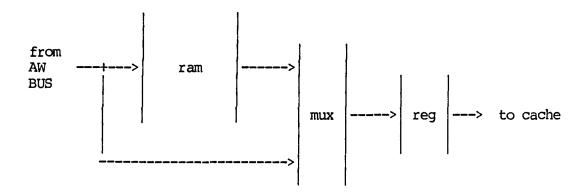

| 7.1.2  | INTERFACE TO DATA SECTION                 |   |   |   | PAGE         | 63  |

| 7.1.3  | MEMORY REQUEST INTERFACE                  |   |   |   | PAGE         | 64  |

| 7.1.4  | SPY INTERFACE                             | • | • |   | PAGE         | 66  |

| 7.2    | WRITE-BACK ALGORITHM                      |   |   |   | PAGE         | 67  |

| 7.2.1  | OVERVIEW                                  |   |   |   | PAGE         | 67  |

| 7.2.2  | DETAILED DESCRIPTION                      |   |   |   | PAGE         | 70  |

| 7.3    | SPY MECHANISM                             |   |   |   | PAGE         |     |

| 7.4    | DIRECTORY SECTION                         |   |   |   | PAGE         |     |

| 7.4.1  | OVERVIEW                                  |   |   |   | PAGE         |     |

| 7.4.2  | DETAILED DESCRIPTION                      |   |   |   | PAGE         |     |

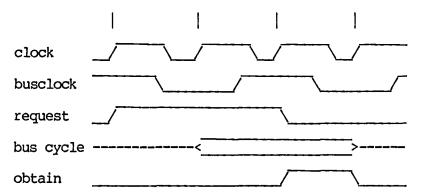

| 8      | TIMING                                    |   |   |   | PAGE         |     |

| 8.1    | ADDRESS SECTION TIMING OF READ OPERATION. |   |   |   | PAGE         |     |

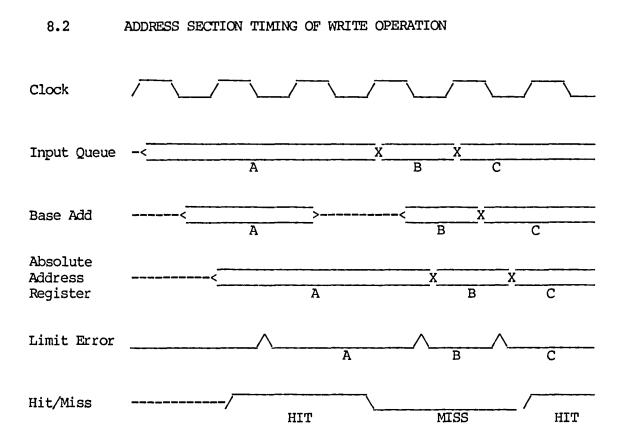

| 8.2    | ADDRESS SECTION TIMING OF WRITE OPERATION |   |   |   | PAGE         |     |

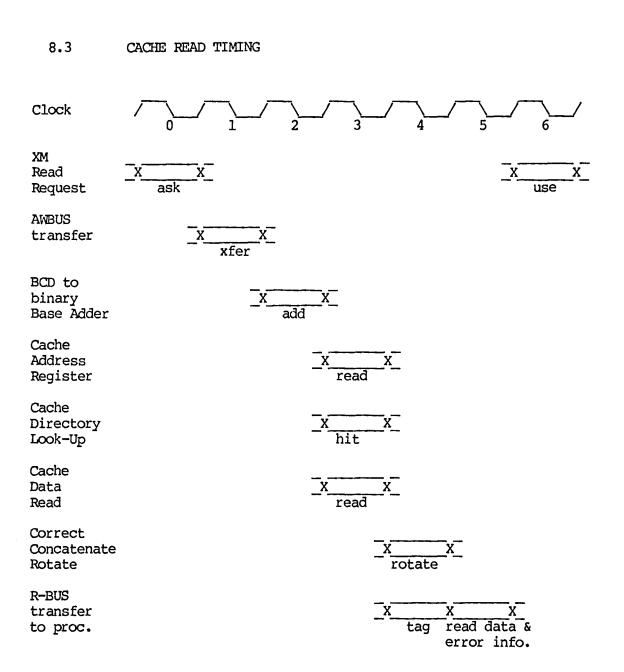

| 8.3    | CACHE READ TIMING                         |   |   |   | PAGE         |     |

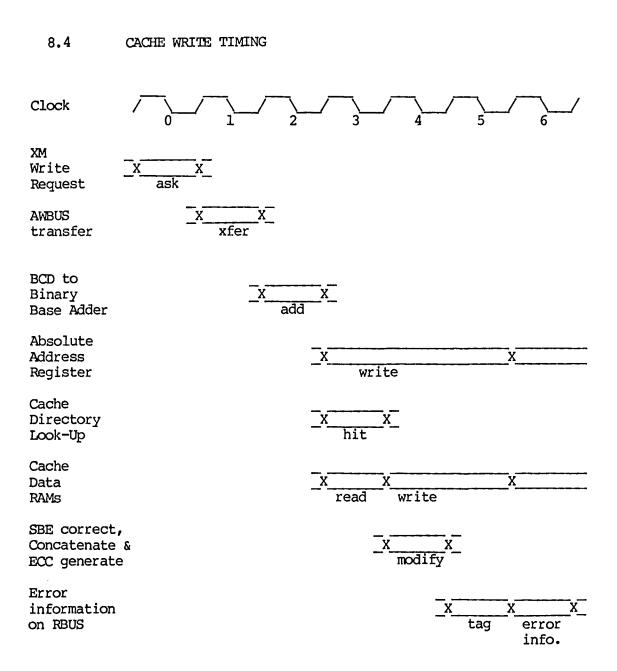

| 8.4    | CACHE WRITE TIMING                        | • | • | • | PAGE         |     |

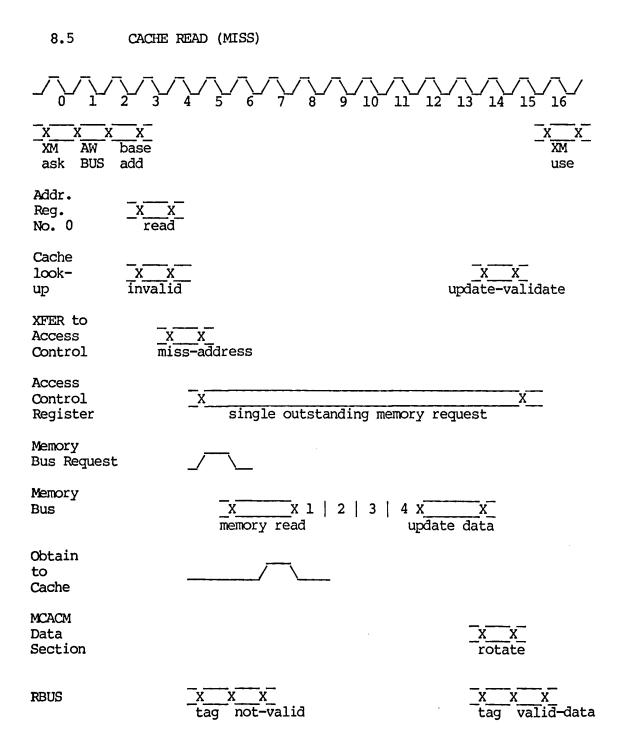

| 8.5    | CACHE READ (MISS)                         |   |   |   | PAGE         |     |

| 8.6    | CACHE WRITEBACK TIMING                    |   |   |   | PAGE         |     |

| 9      | ERROR DETECTION AND HANDLING              |   |   |   | PAGE         |     |

| 9.1    | MCACM BROKEN STATE DEFINITIONS            |   |   |   | PAGE         |     |

| 10     | SYSTEM MAINTENANCE INTERFACE              |   |   |   | PAGE         |     |

| 10.1   | INTERNAL STATE ACCESS                     |   |   |   | PAGE         |     |

| 10.2   | CLOCK CONTROL                             |   |   |   | PAGE         | 87  |

| 10.3   | MCACM SYSTEM-FATAL ERROR SIGNAL           |   |   |   | PAGE         | 87  |

| 10.4   | STOP LOGIC.                               |   |   |   | PAGE         | 88  |

| 10.4.1 | STOP ON CACHE UPDATE.                     |   |   |   |              | 88  |

| 10.4.2 |                                           |   |   |   | PAGE<br>PAGE | 89  |

| 10.4.3 | STOP ON WRITE DATA                        |   |   |   | PAGE         | 90  |

| 10.4.4 | STOP ON SPY REQUEST                       |   |   |   | PAGE         | 91  |

| 10.4.5 | ***                                       |   |   |   |              | 92  |

| 10.4.5 | STOP ON RBUS ERROR                        |   |   |   | PAGE         |     |

|        | STOP ON WRITE ABORT                       |   |   |   | PAGE         | 92  |

| 10.4.7 | STOP ON FLUSH                             |   |   |   | PAGE         | 92  |

| 10.4.8 | MAINTENANCE MONITOR OF WRITE-ABORT        |   |   | • |              | 92  |

| 11     | FRONTPLANE AND BACKPLANE DEFINITION       |   |   | • | PAGE         | 93  |

| 11.1   | ADDRESS BOARD BACKPLANE DEFINITION        |   |   | • | PAGE         | 93  |

| 11.1.1 | ADDRESS AND WRITE BUS (from processor)    |   |   | • | PAGE         | 93  |

| 11.1.2 | RBUS (to processor)                       |   |   | • | PAGE         | 93  |

| 11.1.3 | MEMORY ADDRESS BUS                        |   |   | • | PAGE         | 94  |

| 11.1.4 | MEMORY BUS ARBITRATION SIGNALS            | - | - | • | PAGE         | 94  |

| 11.1.5 | MAINTENANCE INTERFACE BUS                 |   |   | • | PAGE         | 95  |

| 11.2   | DATA BOARD BACKPLANE DEFINITION           |   |   | • | PAGE         | 96  |

| 11.2.1 | READ BUS                                  |   |   | • | PAGE         | 96  |

| 11.2.2 | BIDIRECTIONAL MEMORY DATA BUS             |   |   | • | PAGE         | 96  |

| 11.2.3 | MAINTENANCE INTERFACE BUS                 |   |   |   | PAGE         | 96  |

| 11.3   | MEMORY CONTROL FRONTPLANE DEFINITION      |   |   |   | PAGE         | 97  |

| 11.3.1 | DATA SECTION CONTROL SIGNALS              |   |   |   | PAGE         | 97  |

| 11.3.2 | RANDOM INTER-BOARD SIGNALS                |   |   | • | PAGE         | 97  |

| 12     | ARRAY SPECIFICATIONS                      |   |   | • | PAGE         | 98  |

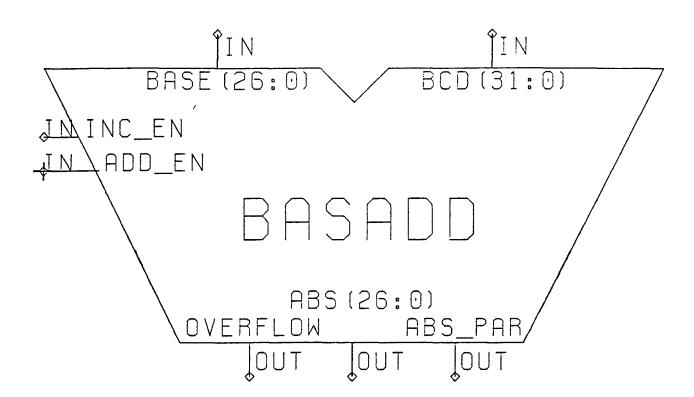

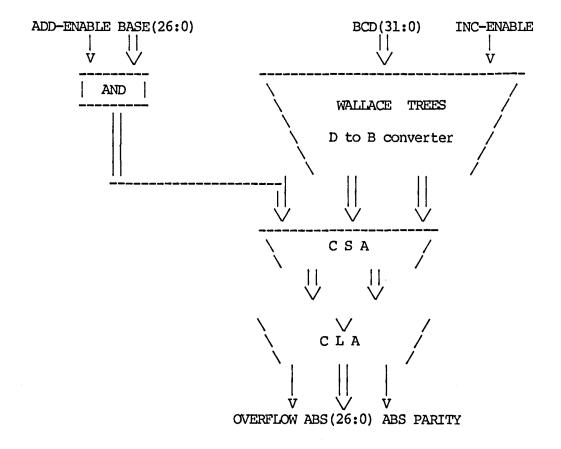

| 12.1   | BASADD                                    |   |   | • | PAGE         | 98  |

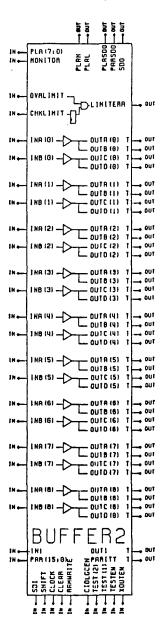

| 12.2   | BUFFER2                                   | • | • | • | PAGE         | 103 |

#### 1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

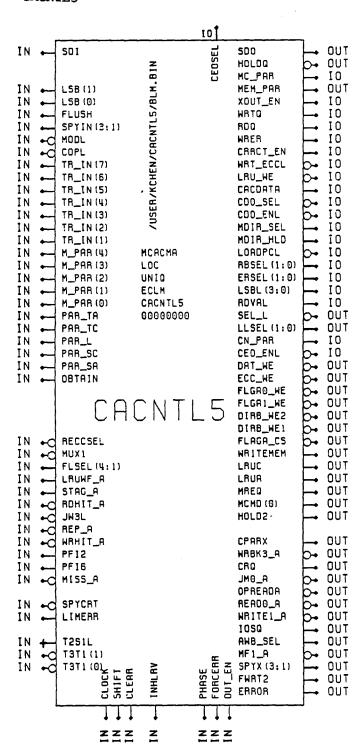

| 12.3  | CACN  | TL5 |     | •   |     | •          | •   | •   | •  | • |   | • | • | • |   |   | • |   | • | • |   | • | PAGE | 111 |

|-------|-------|-----|-----|-----|-----|------------|-----|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|------|-----|

| 12.4  | CAFL  | AG6 |     | •   |     | •          | ٠   | •   | •  |   |   | • |   | • | • |   |   |   | • |   |   | • | PAGE | 118 |

| 12.5  | CHAD  | DR3 |     | •   | •   | •          |     |     | •  | • | • | • |   | • | • | • |   |   |   | • | • | • | PAGE | 124 |

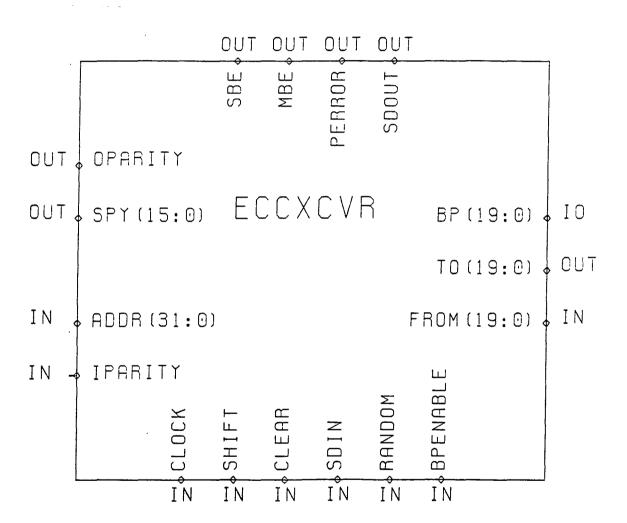

| 12.6  | ECCX  | CV. | •   |     | •   | •          | •   | •   | •  | • |   | • | • | • | • | • | • |   |   | • | • | • | PAGE | 128 |

| 12.7  | ERREX | C2. | •   |     |     |            |     |     | •  | • | • |   |   |   | • |   | • |   |   |   | • |   | PAGE | 133 |

| 12.8  | LMIC  | HK. | •   | •   | •   |            | •   | •   | •  | • |   | • | • |   |   | • | • |   | • |   |   | • | PAGE | 137 |

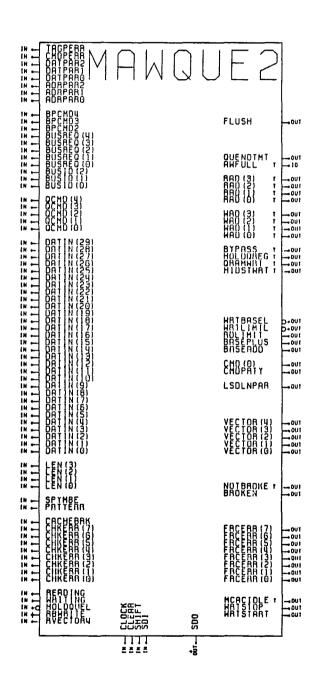

| 12.9  | MAWQI | UE2 |     | •   | •   | •          |     |     | •  |   | • | • | • |   | • |   | • |   |   |   | • | • | PAGE | 141 |

| 12.10 | MCEC  | C2. | •   | •   | •   | •          | •   | •   | •  | • | • | • | • |   |   |   | • |   | • |   | • | • | PAGE | 155 |

| 12.11 | MCNTI | L5. | •   | •   | •   |            | •   | •   | •  | • | • | • |   | • | • | ٠ |   |   |   | • |   | • | PAGE | 158 |

| 12.12 | RAMAI | RR. | •   | •   | •   | •          | •   | •   | •  | • | • | ٠ | • | • | • | • | • |   |   |   | • | • | PAGE | 174 |

| 12.13 | ROTC  | AT. | •   | •   | •   | •          |     | •   | •  |   | • | • |   | • | • |   | • | • | • |   | • | • | PAGE | 177 |

| 13    | TERM  | SA  | ND  | DI  | EF. | [N]        | IT: | 101 | NS | • | • | • | • | • | • | • | • | • | • | • | • | • | PAGE | 181 |

| 14    | CHAI  | N D | EF. | IN: | IT. | <b>(O)</b> | NS  | •   | •  | • | • | • |   | • | • |   | • | ٠ | • |   | • | • | PAGE | 186 |

| 14.1  | MA.   |     | •   | •   | •   | •          | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | PAGE | 186 |

| 14.2  | MD.   |     | •   | •   | •   | •          | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | PAGE | 244 |

| 14.3  | YMA . |     | •   | •   | •   | •          | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | PAGE | 297 |

| L4.4  | YMD . |     |     | •   | •   | •          | •   |     | ٠  | • | • | • |   | • | • | • | • | • | • | • | • | • | PAGE | 306 |

|       |       |     |     |     |     |            |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |   |      |     |

UNISYS CORPORATION MISSION VIEJO

#### 1993 5220 REV. D GENERAL SYSTEMS GROUP V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### TABLE OF ILLUSTRATIONS

| Fig. | 3-1  | Block Diagram of Memory Control and Cache Module . | PAGE | 3   |

|------|------|----------------------------------------------------|------|-----|

| Fig. | 3-2  | V500 Main Memory and Cache Structure               | PAGE | 4   |

| Fig. | 4-1  | MCACM Command Codes                                | PAGE | 8   |

| Fig. | 4-2  | Example of Write Data Formats                      | PAGE | 9   |

| Fig. | 4-3  | Read I/O Hardware Register Definitions             | PAGE | 14  |

| Fig. | 4-4  | Write I/O Hardware Register Definitions            | PAGE | 15  |

| Fig. | 5-1  | Address and Write Bus Interface Signals            | PAGE | 20  |

| Fig. | 5-2  | Memory Control and Cache Module Commands           | PAGE | 22  |

| Fig. | 5-3  | Definition of Tag Field                            | PAGE | 23  |

| Fig. | 5-4  | Address and Write Bus Access Arbitration Signals . | PAGE | 24  |

| Fig. | 5-5  | Read Bus interface Signals                         | PAGE | 26  |

| Fig. | 5-6  | Definition of Error Vector                         | PAGE | 28  |

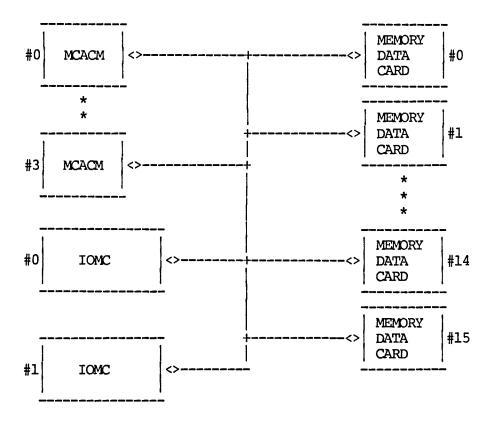

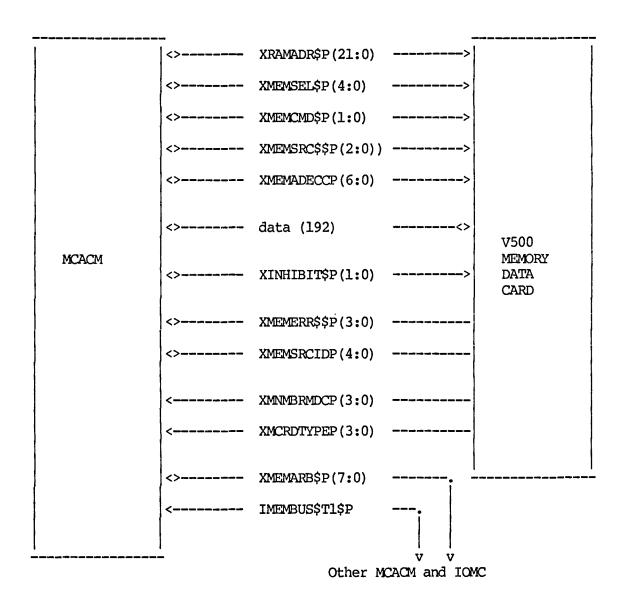

| Fig. | 5-7  | Main Memory Storage Structure Interconnections     | PAGE | 30  |

| Fig. | 5-8  | Memory Data Card Interface                         | PAGE | 31  |

| Fig. | 5-9  | Memory Address Bus Requestor ID Field Definition . | PAGE | 33  |

| Fig. | 5-10 | Address Bus Error Correction Code                  | PAGE | 34  |

| Fig. | 5-11 | Address Bus Syndrome to bit-in-error Decode Table. | PAGE | 35  |

| Fig. | 5-12 | Data Bus Error Correction Code                     | PAGE | 37  |

| Fig. | 5-13 | Data Bus Syndrome to bit-in-error Decode Table     | PAGE | 38  |

| Fig. | 5-14 | "Any-Number" Memory Interleaving Scheme            | PAGE | 41  |

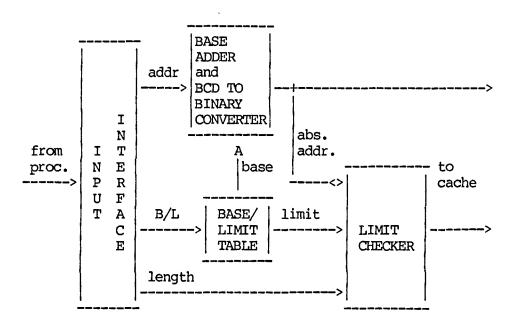

| Fig. | 6-1  | Block Diagram of Memory Control Address Section    | PAGE | 47  |

| Fig. | 6-2  | Input Interface State Transition Table             | PAGE | 49  |

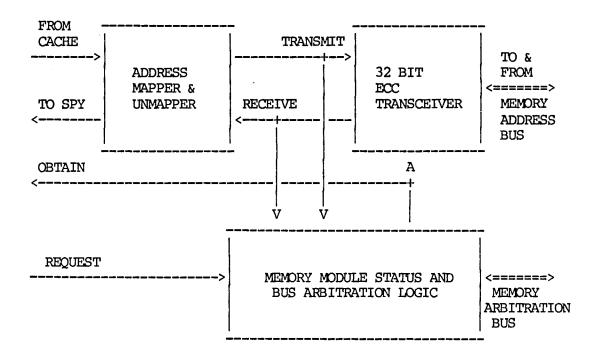

| Fig. | 6-3  | Block Diagram of Memory Request and Access Control | PAGE | 52  |

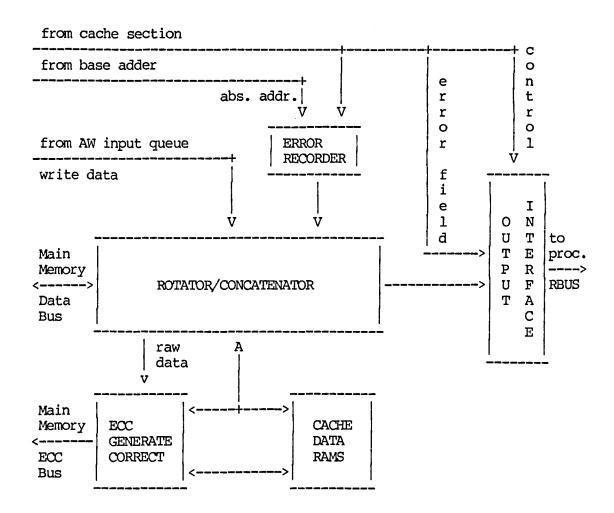

| Fig. | 6-4  | Block Diagram of MCACM Data Section                | PAGE | 54  |

| Fig. | 7-1  | Internal Cache Command Decoding Table              | PAGE | 60  |

| Fig. | 7-2  | Block Diagram of Cache Data Interface              | PAGE | 63  |

| Fig. | 7–3  | Four States of Cached Data                         | PAGE | 68  |

| Fig. | 7-4  | Cache Actions for Spy Detected External Requests . | PAGE | 72  |

| Fig. | 7-5  | Cache Actions for Processor Requests               | PAGE | 75  |

| Fig. | 7-6  | Cache translator-pipeline registers                | PAGE | 76  |

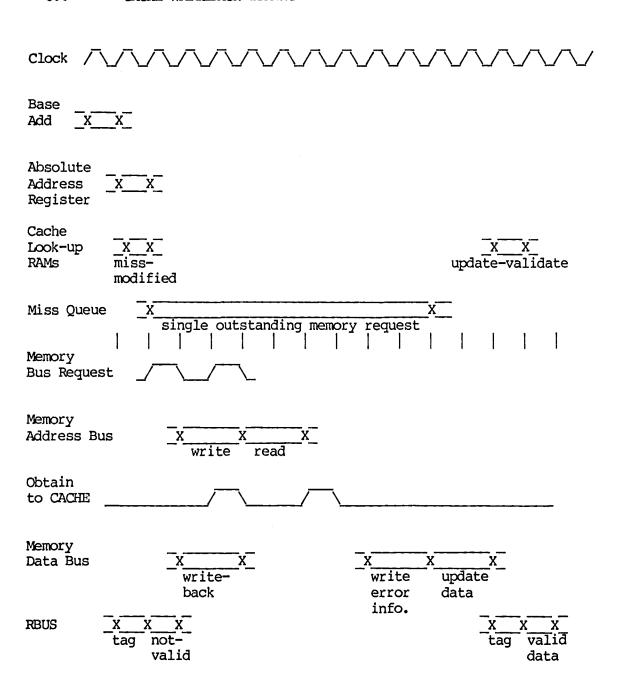

| Fig. |      | Timing of Address Section (Reads)                  | PAGE | 78  |

| Fig. |      | Timing of Address Section (Writes)                 | PAGE | 79  |

| Fig. | 8-3  | Timing of Read Hit                                 | PAGE | 80  |

| _    | 8-4  | Timing of Write Hit                                | PAGE | 81  |

| Fig. |      | Timing of Cache Update (read miss)                 | PAGE | 82  |

| Fig. | 8-6  | Timing of Cache Write-Back (read miss)             | PAGE | 83  |

| _    | 12-1 | The Structure of the Base Adder                    | PAGE |     |

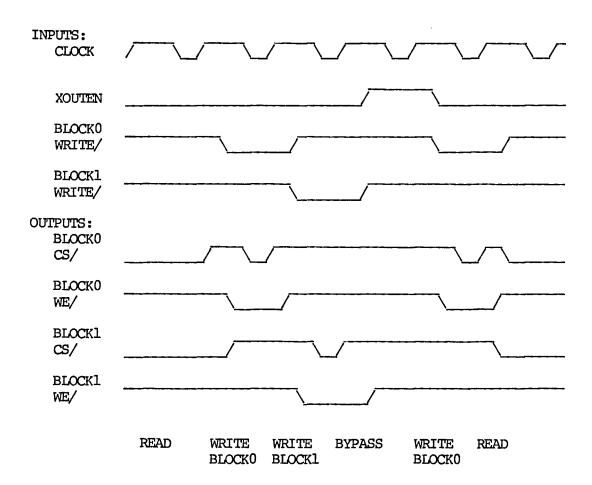

| Fig. |      | Write-Enable and Chip-Select Timing Diagram        | PAGE |     |

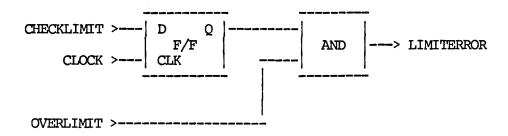

|      | 12-3 | Limit Error Detection Circuit                      | PAGE |     |

|      | 12-4 | Encoding of non-fatal errors                       | PAGE |     |

|      | 12-5 | Encoding of fatal errors                           | PAGE |     |

|      | 12-6 | Encoding of BROKEN errors                          | PAGE | 136 |

| rig. | 12-7 | FIFO queue structure                               | PAGE |     |

| ig.  | 12-8 | Classes of commands handled by MAWQUE2             | PAGE | 150 |

|      |      |                                                    |      |     |

#### 1 PURPOSE

This specification defines the memory control and cache module which in conjunction with the memory storage structure performs the main memory function for the V500 System.

### 2 APPLICABLE DOCUMENTS

| 1257 6005<br>Al, Al4, Al6<br>1995 5301 | Corporate Environmental Standards<br>Corporate Technical Standards<br>V500 Circuit Rules |

|----------------------------------------|------------------------------------------------------------------------------------------|

| XXXX XXXX                              | V500 Element Rules                                                                       |

| XXXX XXXX                              | V500 Chip Chart                                                                          |

| 1997 5390                              | V Series Instruction Set                                                                 |

| 1993 5279                              | V500 Architecture                                                                        |

| 1993 5163                              | V500 System                                                                              |

| 1993 5170                              | V500 System Index                                                                        |

| 1993 5204                              | V500 Execute Module Engineering Design Spec                                              |

| 1993 5212                              | V500 Fetch Module Engineering Design Spec                                                |

| 1993 5238                              | V500 Memory Data Card SDS                                                                |

| 1993 5253                              | I/O Memory Concentrator Eng Design Spec                                                  |

| 1993 5329                              | Data Transfer Module Engineering Design Spec                                             |

| 1993 5337                              | Fault Detection Guidelines                                                               |

| 1993 5295                              | System Maintenance Controller                                                            |

| 1993 5303                              | V500 Maintenance Subsystem                                                               |

| 1998 5266                              | Maintenance Users Guide                                                                  |

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### 3 OVERVIEW

The memory control and cache module provides the read and write mechanism for the V500 processor to 500 Mbytes of main memory in a multi-tasking, multi-processor environment. The main memory is divided into process dependent areas which are scheduled by the operating system. Each read or write request to memory specifies an area-relative address and a base indicant which selects which of the memory areas to access.

The memory control and cache module is a link in the memory hierarchy extending from processor scratch-pad registers outwards through main memory, to disks, then tape libraries.

The memory control is split into 2 sections which provide the interfaces between the processor, I/O, cache, and main memory. The first section is an interface between the processor and the cache which is optimized to provide 10 digit operands in a hardware independent format. The second section is an interface between cache and main memory which is optimized for the block-level transactions of cache.

The central portion of the memory control and cache module is the cache memory. The V500 cache memory is organized in 40 digit blocks. There are 2 blocks of 1024 sets in the cache memory. This provides 40,960 bytes of cache memory.

## 3 OVERVIEW (Continued)

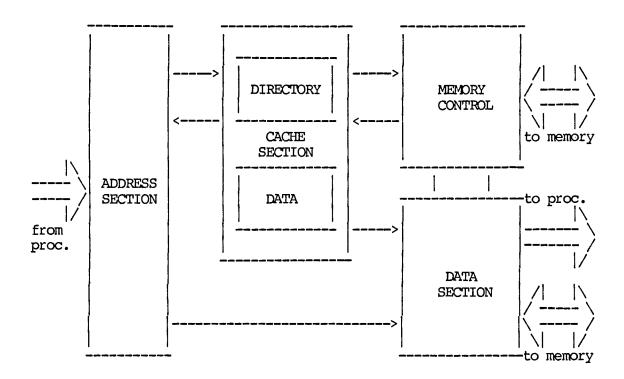

Fig. 3-1 Block Diagram of Memory Control and Cache Module

The memory control and cache module contains 4 separate sections. These 4 sections are: address, memory control, data, and cache. This specification describes the operation and interfaces of the memory control and cache module, then each of these sections in detail.

### 3 OVERVIEW (Continued)

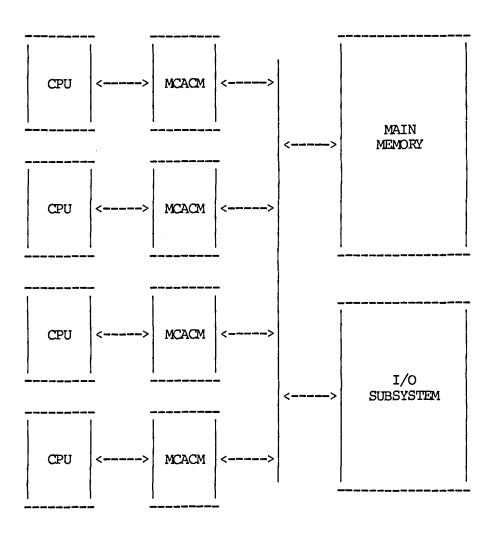

Fig. 3-2 V500 Main Memory and Cache Structure

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### 3.1 COMMANDS

The memory control and cache module provides an interface between the processor and main memory. The MCACM does memory reads and writes for the processor. The MCACM also does the read-with-lock to arbitrate software interlocks between processors in a system.

The memory control and cache module maintains a set of base and limit tables. These tables contain the base and limit addresses of memory areas. Each memory request must specify which memory area to use. The memory request address is then added to the appropriate base address to obtain the absolute memory address. The absolute memory address is then compared to the limit address to check for limit errors.

Whenever a memory request causes or encounters an error, an error flag is returned to the requesting processor module. A subsequent read error report returns the physical memory address and information for the MCP error log.

A special command is also provided which allows the processor to communicate with the I/O subsystem. This communication is done on the main memory address and data buses through the I/O memory concentrators. The I/O memory concentrators accept a subset of the main memory commands across the memory interface. The I/O memory concentrator acts like a logical memory data card.

There are certain commands which the memory control ignores. These No Operation commands are provided to allow non-standard communications between processor modules. An example is a process switch wherein the execute module needs to redirect the fetch module into a new code stream. This implementation was chosen because additional backplane buses are expensive and this type of communication is infrequent.

There are 4 pipe flush commands. These flush commands cause the memory control and cache module to abort any outstanding read requests. These commands are used to reduce the penalty of pre-fetching operands and instructions when a branch prediction is incorrect. All 4 flush commands are treated the same by MCACM but not by

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

the processor modules.

#### 3.2 CACHE

The memory control contains a 81,920 digit cache memory. The cache memory is organized as 1024 of 2 block sets of 40 digits. The cache is controlled with a distributed write-back algorithm which simplifies multiple processor interdependencies.

The cache memory utilizes a spy mechanism to monitor the main memory address bus. When a read from another processor is a hit into local cache and the cache data has been modified, then the cache signals the memory module to disable its outputs and the cache supplies the data, instead of the memory module. The techniques used to insure consistency are discussed later.

#### 3.3 **INTERFACES**

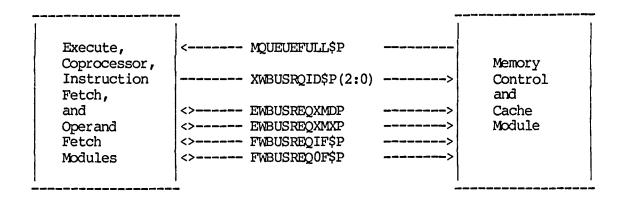

The MCACM interfaces to all three major elements of the V500 processor: the processor modules, the main memory structure, and the I/O subsystem. Each interfaces have different requirements, accounting for most of the complexity of the memory control and cache module.

The processor to MCACM data interface contains BCD address and write data (if any) as well as other relevant information concerning the processor's request. This bus is called the address and write bus (or AWBUS). The AWBUS access arbitration is distributed; requestor determines if it has the highest priority. technique is fast enough to allow arbitration and data transfer on the same clock cycle.

The MCACM to processor return interface is much simpler than the AWBUS. Only read data and an error vector are returned on this bus. The processor modules determine the destination by analyzing a tag field which is sent one clock cycle prior to the data. This allows the processor time to decide where to latch the data. A cache miss, which is an exception, can result in not having data to send for the tag that was already sent. Therefore, a data valid signal is sent to inform the processor module which bus transactions are valid.

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### 3.3 INTERFACES (Continued)

The MCACM to main memory address and data interface is quite complex because of the long time delay for signals which must cross between both cabinets of a multi-processor system. The memory address bus and the memory data bus are both bidirectional two-clock buses. The bus protocol is relatively simple, however, data is returned a certain number of clocks after a cycle has been requested.

Communication between the V500 processor and the I/O subsystem is conducted through the MCACM. This communication occurs over the main memory address and data bus; the IOMC acts like a memory data card. The I/O Translator and MCP also communicate through data structures in main memory which do not use this path.

#### 4 FUNCTIONS

The memory control and cache module responds to commands from the processor. The command field is part of the AWBUS, which is described in Section 5.1. Figure 4-1 is a numeric list of the memory control and cache module commands.

| 00 - Reserved 10 - Write PC 01 - Read Data 11 - Read PC 02 - Write I/O 12 - Read Error Address                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03 - Read I/O 13 - Read Error Report 04 - Test Error Detection 14 - Reserved 05 - Read Base Table 15 - Reserved 06 - Reserved 16 - Read with Lock 07 - Read Limit Table 17 - Reserved 08 - No Operation 0 18 - Write-Back 09 - No Operation 1 19 - Write Base Table 0A - No Operation 2 1A - Reserved 0B - No Operation 3 1B - Write Limit Table |

| OC - Flush O 1C - Reserved OD - Flush 1 1D - Write Data                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                  |

| 09 - No Operation 1 19 - Write Base Table                                                                                                                                                                                                                                                                                                        |

Fig. 4-1 MCACM Command Codes

#### 4.1 READ DATA COMMAND

The read data command requests up to 10 digits of main memory data. The returned data is left justified and padded with trailing zeros. Data is always returned from cache, therefore, if it is not already in cache it is first loaded into cache from main memory and then sent to the processor.

Whenever the requested data spans two blocks of memory, the MCACM generates two main memory requests to obtain the desired data. The MCACM concatenates these requests and returns the data. This is called operand read. The V500 processor's memory data cards do not have the ability to concatenate data onto the memory backplane like the B4900. Throughout this document the term "operand read" is used

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

to describe this concatenation across block boundaries.

#### 4.2 WRITE DATA COMMAND

The write data command writes data from the processor into cache memory. The write data must be aligned as it is to appear in a "mod-10" 10 digit main memory word. The length of the supplied data may be up to 10 digits long as long as it does not cause the data to extend beyond the boundaries of a 10 digit word. Figure 4-2 shows two examples of writes; it shows the desired write and the series of commands required to accomplish it.

#### Examples:

To write 01234 at address 93 for 5.

Write: Address = 093, Length = 5, Data = xxx01234xx

To write 6789 at address 78 for 4.

lst Write: Address = 078, Length = 2, Data = xxxxxxxx67

2nd Write: Address = 080, Length = 2, Data = 89xxxxxxxx

Fig. 4-2 Example of Write Data Formats

If the addressed block is not "writeable" by the cache, then a main memory cycle is initiated to obtain a "writeable" copy before the write is done.

The memory control and cache module assists instruction retry in the V500 processor by aborting a write operation that contains a hardware generated error. After such a fatal error has been detected in a write operation, the remaining write operations in the pipeline are ignored. Write commands are handled after the processor requests an error report, which resets the MCACM. This allows the processor to do instruction level retry without external intervention.

UNISYS CORPORATION MISSION VIEJO

1993 5220 REV. D GENERAL SYSTEMS GROUP V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### 4.3 READ WITH LOCK COMMAND

The read-with-lock command has been provided to allow interprocessor software interlocks. The read-with-lock command is a hybrid of the read and write commands which reads the previous data while writing new data. The read-with-lock command allows the processor to execute the lock and unlock instructions defined in Section 20.4 of the V Series Instruction Set Specification. These lock and unlock instructions depend on the value of a lock status field. This status field is part of a data structure addressed by the instruction. A certain value in this status field corresponds to an available lock while other values indicate the lock is not available.

Processors trying to obtain a lock, execute read-with-lock command with the "unavailable" value in the data field. The read-with-lock command writes this value into the addressed memory location, which is usualy the lock status field, and returns the previous value of the field.

The memory subsystem is designed so that only processor can do this at a time. The first processor to write the "unavailable" value into the status field "available" receives as the previous value. processor has gotten the lock. The next processor to try this also writes the "unavailable" value into the status field but gets back the previous value which is already "unavailable".

The format of the data in a read-with-lock command is best described as a write which also reads the prior contents of the addressed location. The format of the data to be written into memory is the same as data for a write data command. The format of the data that is returned from memory is the same as the data from a read data command.

NOTE: The data format of a write operation does not allow data to cross "mod-10" boundaries; therefore, the read-with-lock command does not allow it either.

#### 4.4 WRITE BASE TABLE COMMAND

The write base table command writes the absolute address from the address field into the base table entry specified by the Base Indicant Field. The base address must be MOD 10.

#### 4.5 WRITE LIMIT TABLE COMMAND

The write limit table command writes the absolute address from the address field into the limit table entry specified by the base indicant field. The limit address must be MOD 10.

#### 4.6 READ BASE TABLE COMMAND

The read base table command returns the absolute base address from the base table entry specified by the base indicant field. The base address is returned in the internal 27-bit binary format.

Note: The processor must pop the Read Base results immediately after issuing a Read Base Command. Failure to do so may result in invalid data. This is because the tag specified in the command may be returned more than once by MCACM: only the first one is accompanied by valid data.

#### 4.7 READ LIMIT TABLE COMMAND

The read limit table command returns the absolute limit address from the limit table entry specified by the base indicant field. The limit address is returned in the internal 27-bit binary format.

Note: The processor must pop the Read Limit results immediately after issuing a Read Limit Command. Failure to do so may result in invalid data. This is because the tag specified in the command may be returned more than once by MCACM: only the first one is accompanied by valid data.

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

#### 4.8 READ ERROR REPORT COMMAND

The read error report command is used in conjunction with the

read error address command to get details about hardware failures which resulted in a fatal error being reported to the processor module. The read error report command and the read error address command must both be issued to reset the error recorder and to allow future write commands to be handled. The read error report command must be issued before the read error address command.

The read error report command returns the memory data card number, the memory module location, and the error syndrome of the first-worst error that occured since the last error report was requested.

The read error report command causes the error recorder to stop accumulating errors and hold the current error until after the read error address command has been serviced. This assures that the error address is for the error report.

#### 4.9 READ ERROR ADDRESS COMMAND

The read error address command is used in conjunction with the read error report command to get details about hardware failures which resulted in a fatal error being reported to the processor module. The read error report command and the read error address command must both be issued to reset the error recorder and to allow future write commands to be handled. The read error report command must be issued before the read error address command.

The read error address command returns the absolute BCD address of the same first-worst error that was reported in response to the read error report command. The error address is in the internal 27 bit binary format. The error address is right justified with leading zeros.

The read error address command allows the error recorder to restart accumulating errors after supplying the address of the current error. This assures that the error address matches the error report. The read error address command also resets the write-abort lockout condition; caused by

1993 5220 REV. D V500 MEMORY CONTROL AND CACHE MODULE ENGINEERING DESIGN SPECIFICATION

write errors.

#### 4.10 WRITE PC COMMAND

The write PC command performs the dual purpose of separating instructions that write and assisting write error reporting. The execute module sends the PC (address of the current instruction) to the memory control and cache module with this command before the first write data command of any instruction that writes data. The 2 functions of this command are:

#### Separation of write instructions

This prevents instructions, which modify memory, from completing out of order in the memory control and cache module. This is necessary because out of order completion could prevent instruction retry. The write PC command prevents the memory control and cache module from handling any new write requests (from the processor) until all outstanding requests have been completed.

#### Error reporting

The PC of the current instruction is stored in a special PC register before any write requests are accepted from the processor. When a write request causes or contains an error, an error information field is sent to the processor. This guarantees that the proper PC is reported for any error occuring during the operation of a write request. An error detected during a write operation causes future write requests to be ignored until a read PC command is handled. This limits the possible data corruption to the single instruction which failed.

The PC is supplied in the write data field (NOT the address field) for a write PC command.

The memory control and cache module stores the PC in a special PC register in the data section of the memory control and cache module; therefore, the base indicant and address fields are "don't cares" for this command.

#### 4.11 READ PC COMMAND

The read PC command is used by the execute module to determine the instruction address which caused a write error in the memory control and cache module. The read PC command returns the PC, which is stored in a special PC register in the rotate/concatenate section, to the processor.

The PC is stored in a special PC register. Therefore, the address, base indicant, and write data fields are "don't cares" for this command. The PC does not go through any BCD to or from binary conversion. All 40 bits (10 digits) of the PC register are returned unaltered to the processor.

#### 4.12 READ I/O COMMAND