# Burroughs Corporation MICRO COMPONENTS GROUP

MEMORY ENGINEERING

RANCHO BERNARDO PLANT

COMPANY CONFIDENTIAL

V500 MEMORY DATA CARD

## SYSTEMS DESIGN SPECIFICATION

|             | REVISIONS                |                                                                                       |                          |                                                      |  |  |  |

|-------------|--------------------------|---------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------|--|--|--|

| REV.<br>LTR | REVISION<br>ISSUE DATE   | PAGES REVISED. ADDED. DELETED OR CHANGE OF CLASSIFICATION                             | PREPARED BY              | APPROVED BY                                          |  |  |  |

| A           |                          | Review copy (not released)                                                            | L. Simpson               | D. Castle D.Castl                                    |  |  |  |

| В           | 10/27/86<br>ECN<br>52053 | Incorporate new CTRL-ARRAY modifications including busy timeout counter Initial Issue | L. Hanson M. Fitzsimmons | D. Lau<br>D. Kom<br>H. Li<br>Aprodu                  |  |  |  |

|             | <b>.</b>                 |                                                                                       |                          | R. Young  D. Welbourn  J. Chen                       |  |  |  |

|             |                          |                                                                                       |                          | Rancho Bernardo:  M. Fitzsimmons  J. Rudy  Langledon |  |  |  |

| •           |                          |                                                                                       |                          | R. Rhodes  M. G. Williams                            |  |  |  |

|             |                          |                                                                                       |                          | ę.                                                   |  |  |  |

|                                                                     |         |                  |            |        |           |      |      | _ |

|---------------------------------------------------------------------|---------|------------------|------------|--------|-----------|------|------|---|

|                                                                     |         | 10/27/           | /86        |        |           | 1993 | 5238 |   |

| BURROUGHS CORPORATION<br>Bystems development grou<br>Pasadena plant |         |                  | <br>MEMORY |        | +<br>`ADD |      |      |   |

| . '                                                                 |         | ( ∨⊐⊌€<br>¦<br>, | PHENORI    | Unin ( | טחתט      |      |      | - |

| COMPANY<br>CONFIDENTIAL                                             | SYSTEMS | DESIGN           | SPECIFI    | CATION | Rev. B    | Page | = !  |   |

|                                                                     |         |                  |            |        |           |      |      |   |

### TABLE OF CONTENTS

| 1       | PURPOSE                                              |   | מאכר ז                                  |

|---------|------------------------------------------------------|---|-----------------------------------------|

| 1       |                                                      |   |                                         |

| 2       | APPLICABLE DOCUMENTS                                 |   |                                         |

| 3       | OVERVIEW                                             |   | PAGE 5                                  |

| 4       | FUNCTIONS                                            |   | PAGE 5                                  |

| 4.1     | COMMANDS                                             |   |                                         |

| 4.7     | INTERNAL REFRESH                                     |   |                                         |

| 5       | •                                                    |   |                                         |

|         |                                                      | - |                                         |

| 5.1     | ADDRESS BUS                                          |   |                                         |

| 5.1.1   | MEMORY COMMAND FIELD - KMEMCMD\$\$P(1:0)             |   | PAGE 9                                  |

| 5.1.2   | REQUESTOR ID FIELD - KMEMREQIDP(2:0)                 |   | PAGE . 9                                |

| 5.1.3   | MODULE SELECT FIELD - KMODSEL\$\$P(4:0)              |   | PAGE: 10                                |

| 5.1.4   | ADDRESS FIELD - KRAMADR\$P(21:0)                     |   |                                         |

| 5.2     | DATA BUS                                             |   |                                         |

|         |                                                      |   | •                                       |

| 5.2.1   | DATA FIELD - XRAMDT(3:0)\$P(39:0)                    | - |                                         |

| 5.2.2   | DATA BUS HAMMING CODE FIELD - XRAMEC(3:0)\$\$P(7:0). | - | , , , , , , , , , , , , , , , , , , , , |

| 5.3     | STATUS INTERFACE                                     | * | PAGE 16                                 |

| 5.3.1   | CABINET SOURCE - XMCABSRC\$\$\$P                     |   | PAGE : 16                               |

| 5.3.2   | SOURCE ID (5 bits) - XMEMSRCID\$P(4:0)               |   | PAGE 16                                 |

| 5.3.3   | SOURCE PARITY - XMEMSRCPAR\$P                        |   |                                         |

| 5.3.4   | ERROR FIELD - XMEMERR\$P(3:0)                        |   |                                         |

| 5.4     | SPY INTERFACE - XINHDATXFRAP                         |   |                                         |

| 5.5     | CONFIGURATION BUS                                    |   |                                         |

| 5.5.1   | NUMBER OF MEMORY DATA CARDS - XNMBRMDC\$P(3:0)       |   |                                         |

| 5.5.2   | TYPE OF MEMORY DATA CARD - XCRDTYPE\$P(3:0)          |   |                                         |

| 8       | DESCRIPTION OF OPERATION                             |   |                                         |

| 6.1     | POWER-ON-CLEAR CONFIGURATION                         |   |                                         |

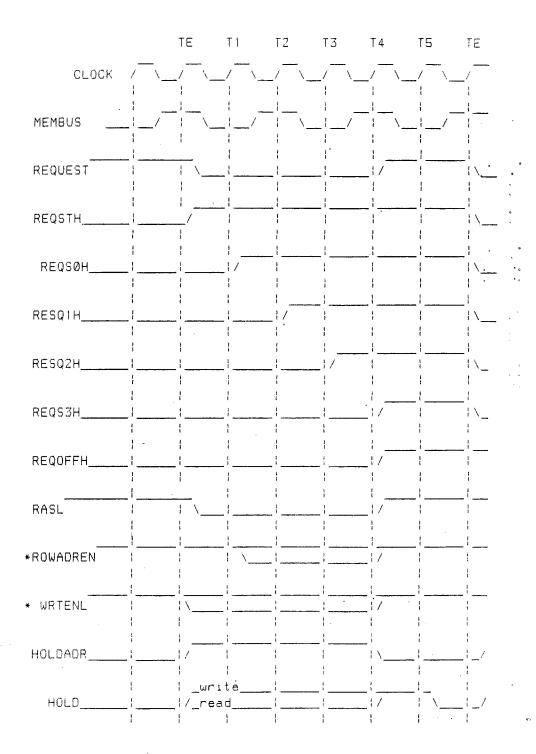

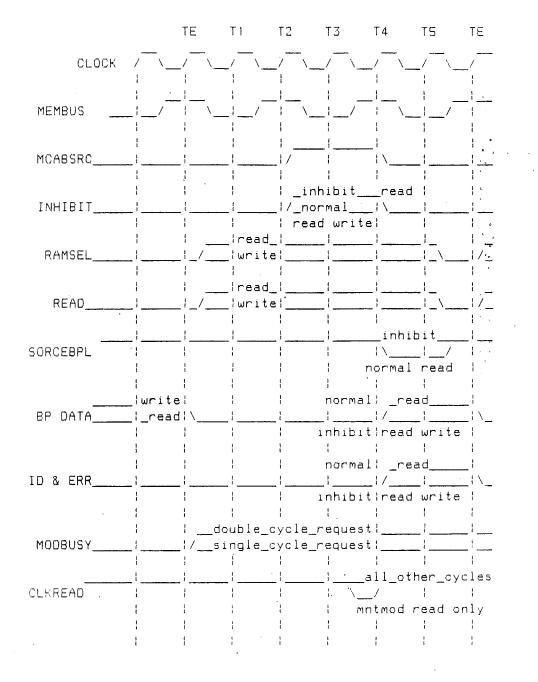

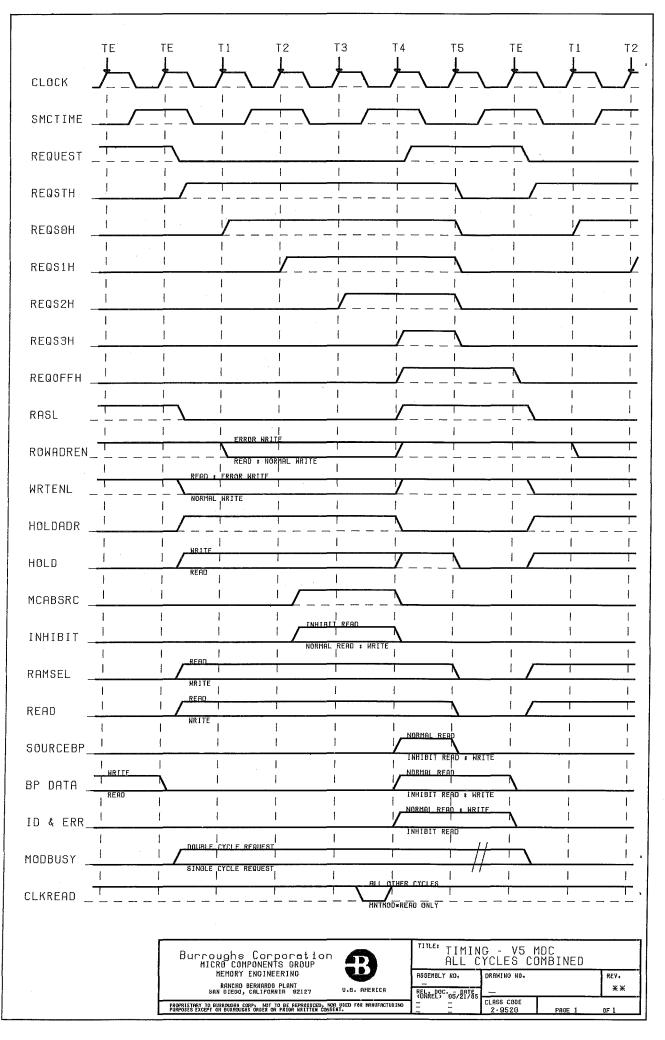

| 5.2     | MEMORY TIMING                                        |   |                                         |

| 7       | ERROR DETECTION AND HANDLING                         |   |                                         |

| •       |                                                      |   |                                         |

| 7.1     | REPORTING OF PHYSICAL CARD SLOT ON ERRORS            |   |                                         |

| 7.2     | ERROR CORRECTION                                     |   |                                         |

| 7.2.1   | ADDRESS BUS                                          |   |                                         |

| 7.2.2   | DATA BUS                                             |   |                                         |

| 7.2.2.1 | WRITE                                                |   |                                         |

| 7.2.2.2 | READ                                                 |   | PAGE 27                                 |

| 8       | SYSTEM MAINTENANCE INTERFACE                         |   | PAGE 28                                 |

| 8.1     | CLOCK-MAINTENANCE ARRAY                              | _ | PAGE 28                                 |

| 8.2     | MAINTENANCE AND DATA SHIFT CHAINS                    | • | PAGE 28                                 |

| 9.3     | SINGLE CLOCK OPERATION                               | • | PAGE 28                                 |

|         | CHERENEE OFFICE OFFICE                               | • | PAGE 30                                 |

| 9.4     | SUSPENDED OPERATIONS                                 |   |                                         |

| 8.5.    | FORCE REFRESH                                        | ٠ | PAGÉ 29                                 |

| 8.5     | BUS DRIVERS                                          |   |                                         |

| 9       | -BACKPLANE DEFINITION                                |   |                                         |

| 10      | GATE ARRAY DEFINITIONS                               |   | PAGE 39                                 |

| 10.1    | CONTROL ARRAY - MCTRL                                |   |                                         |

| 10.1.1  | MCTRL FUNCTIONAL OVERVIEW                            |   |                                         |

| 10.1.2  | MCTRL INTERFACES                                     |   |                                         |

|         | THO FINE ENTERNATIONS OF THE FIRST PROPERTY.         | • | THOL TI                                 |

<sup>--</sup>Burroughs Prior Written Consent Required For Disclosure Of This Data--

|                      |         |             |                |         |       | <del></del> |      |      |   |

|----------------------|---------|-------------|----------------|---------|-------|-------------|------|------|---|

|                      |         | 10/27/      | '9 <b>6</b>    |         | •     | ţ           | 1993 | 5238 |   |

| BURROUGHS CORPORATIO | )N -    | + <u>-</u>  |                |         |       | +           |      |      |   |

| SYSTEMS DEVELOPMENT  | GROUP   | i<br>i      |                |         |       |             |      |      |   |

| PASADENA PLANT       |         | U500        | ) MEMOR        | Y DATA  | CARD  |             |      |      |   |

|                      |         |             |                |         |       |             |      |      |   |

| COMPANY              | -       | <del></del> | · <del>-</del> |         |       |             |      |      | _ |

| CONFIDENTIAL         | SYSTEMS | DESIGN      | SPECIF         | ICATION | √ Rev | . 8         | Page | 2    |   |

|                      |         |             |                |         |       |             |      |      | - |

#### TABLE OF CONTENTS (cont'd)

| 10.1.3   | MCTRL FAULT DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10.1.4   | MCTRL BOARD TEST FACILITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.1.5   | MCTRL SHIFT CHAIN DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10.1.6   | MCTRL PIN-OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10.2     | ADDRESS ARRAY - MDADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10.2.1   | MDADD FUNCTIONAL OVERVIEW PAGE 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.2.2   | MDADD INTERFACES PAGE 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10.2.3   | MDADD FAULT DETECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10.2.4   | MDADD BOARD TEST FACILITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10.2.5   | MDADD SHIFT CHAIN DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10.2.5   | MDADD PIN-OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10.3     | DATA ARRAY - MDECC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10.3.1   | MDECC2 FUNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10.3.2   | MDECC2 INTERFACES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.3.3   | MDECC2 CHECK BIT ENCODE TABLE PAGE . 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 10.3.4   | MDECC2 SYNDROME DECODE TO BIT-IN-ERROR TABLE PAGE . 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10.3.5   | MDECC2 SHIFT CHAIN DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10.3.6   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 1      | TERMS AND DEFINITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| APPENDIX | A Company of the Comp |

|          | MAINTENANCE CAHIN LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          | DATA CHAIN LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                |                                                             |                         | +                                   | _ |

|----------------------------------------------------------------|-------------------------------------------------------------|-------------------------|-------------------------------------|---|

| 0.0000000000000000000000000000000000000                        | ND'O DATE DA                                                | 10/27/86                | . 1993 5238                         |   |

| BURROUGHS CORPORATION SYSTEMS DEVELOPMENT GROUP PASADENA PLANT |                                                             | US00 MEMORY DATA CARD   | - <b>+</b>                          |   |

| COMPANY<br>CONFIDENTIAL                                        | SYSTEMS                                                     | DESIGN SPECIFICATION Re | v. B Page 3                         | _ |

|                                                                | TABLE OF                                                    | ILLUSTRATIONS           |                                     | _ |

| FIGURE 5.1 FIGURE 5.2 FIGURE 5.3 FIGURE 5.4 FIGURE 5.5         | ADDRESS BUS HAMMI<br>ADDRESS BUS SYNDR<br>DATA BUS ERROR CO | BACKPLANE INTERFACE     | PAGE 11<br>E TABLPAGE 12<br>PAGE 14 |   |

#### 1 PURPOSE

This specification defines the Memory Data Card (MDC) from which the memory storage structure of the V500 System is constructed.

#### 2 APPLICABLE DOCUMENTS

| 1257 6005         | Corporate Environmental Standards    |

|-------------------|--------------------------------------|

| A1, A14, A16      | Corporate Technical Standards        |

| XXXX XXXX         | Design Guidelines                    |

| 1993 5279         | V500 Architecture                    |

| 1993 5162         | V500 System                          |

| 1993 5170         | V500 System Index                    |

| 1997 5390         | V Series Instruction Set             |

| 1993 5204         | V500 Execute Module (XM)             |

| 1993 5212         | V500 Fetch Module                    |

| 1993 5220         | V500 Memory Control and Cache Module |

| XXXX XXXX         | Inter-Cabinet Buffer Module          |

| 1993 5253         | I/O Memory Concentrator              |

| 1993 5246         | I/O Translator                       |

| 1993 5 <b>329</b> | Data Transfer Module                 |

| 1993 5337         | Fault Detection                      |

| 1993 5295         | System Maintenance Controller        |

| 1993 5303         | V500 Maintenance Subsystem           |

|                         |         | 10/27/ | 86      |        |       | }   | 1993 | 5238 |  |

|-------------------------|---------|--------|---------|--------|-------|-----|------|------|--|

| BURROUGHS CORPORATION   |         | +      |         |        |       | +   |      |      |  |

| SYSTEMS DEVELOPMENT GRO | UP      | 1      |         | •      |       |     |      |      |  |

| PASADENA PLANT          |         | 1 0500 | MEMORY  | DATA   | CARD  |     |      |      |  |

|                         |         | 1      |         |        |       |     |      |      |  |

| COMPANY                 |         | +      |         |        |       |     |      |      |  |

| CONFIDENTIAL            | SYSTEMS | DESIGN | SPECIFI | CATION | V Re∨ | . В | Page | ÷ 5  |  |

|                         |         |        |         |        |       |     |      |      |  |

#### 3 OVERVIEW

The V500 Processor memory storage structure consists of 1 to 16 Memory Data Cards (MDC). Using 256K DRAM technology, each MDC will contain either 524288 20 byte words (half populated), or 1048576 20 byte words (fully populated), plus error correct bits. The words are partitioned such that in certain cases, up to 4 bits in error can be corrected. Data from the output of the card may be corrected in a similar fashion by the requestors. In addition, 1 bit in error on the address and control may be corrected.

The total capacity of the memory subsystem, using 256K DRAMs, is 335,544,320 usable bytes. It is expandable to this quantity in increments of 10,485,760 or 20,971,520 bytes. If 1M DRAMS are used, the capacity may be increased to 1,342,177,280 bytes, with a corresponding increase in expansion increments.

Each memory data card will have a physical location and a logical address. After power-up-clear, each memory data card must be configured to the proper logical address by the maintenance processor. It is important to make the distinction between the physical slot location and the logical address. Each memory data card responds to its logical address. The physical slot location is only used for reporting errors so that the field engineer will be able to replace a failing board.

#### 4 FUNCTIONS

The MDC is organized as four 40 data bit wide sub-modules, each with its own error correction (SEC-DED-S4EC), giving a 48 bit physical sub-module. Each sub-module spans 48 memory SIPs, so that any total failure of one SIP can be corrected.

#### 4.1 COMMANDS

The MDC supports 4 different operations: read-public, read-private, read-modify-write, and write. These commands are described below.

#### READ-PUBLIC

Read a 40 digit block of memory from the location specified on the address bus. The "public" distinction is only recognized by the MCACM. This command allows MCACM's to keep cached copies of unmodified data. The read-public command is used by cache, in response to a read miss, and by the IOMC.

#### READ-PRIVATE

Read a 40 digit block of memory from the location specified on the address bus. The "private" distinction is only recognized by the MCACM. This command forces all other MCACM's to release cached copies of this data. The read-private command is only used by cache, and only in response to a write miss.

#### READ-MODIFY-WRITE

The read-modify-write command is similar to the read-private command. It reads a 40 digit block of memory at the address specified on the address bus. The difference is, this command will force the MDC to turn on MODULE BUSY, and hold it on until the next command. The read-modify-write command is only used by the IOMC, which can read a 40 digit block of data from memory (if cached, from MCACM), modify it, and then write it back to memory.

If the read-modify-write command cycle exceeds 32 ECL system clocks, the MDC will reset the busy condition. This prevents memory requestors from being locked-out by a broken IOMC.

#### WRITE

Write the 40 digit block of memory from the data bus into the location specified on the address bus.

|                                              |                                | +   |   |      |      |

|----------------------------------------------|--------------------------------|-----|---|------|------|

|                                              | 10/27/86                       |     |   | 1993 | 5238 |

| URROUGHS CORPORATION YSTEMS DEVELOPMENT GROU | +<br>P                         | +   |   |      |      |

| ASADENA PLANT                                | V500 MEMORY DATA CARI<br>      | D   |   |      |      |

| OMPANY                                       | +                              |     |   |      |      |

| ONFIDENTIAL                                  | SYSTEMS DESIGN SPECIFICATION R | e∨. | В | Page | 7    |

#### 4.2 INTERNAL REFRESH

Refresh is generated internally on the MDC. There is a MDC busy line from each MDC to all requestors that must be asserted two bus clocks (four system clocks) before a MDC can start a refresh cycle. In the event that a module request is in transit on the bus at the same cycle as the busy signal, this request must be serviced, the MDC will remain busy and do the refresh later.

The MDC will contain sufficient power supply filtering to allow refresh without causing the voltage to drop below the necessary level's for proper operation.

5 INTERFACES

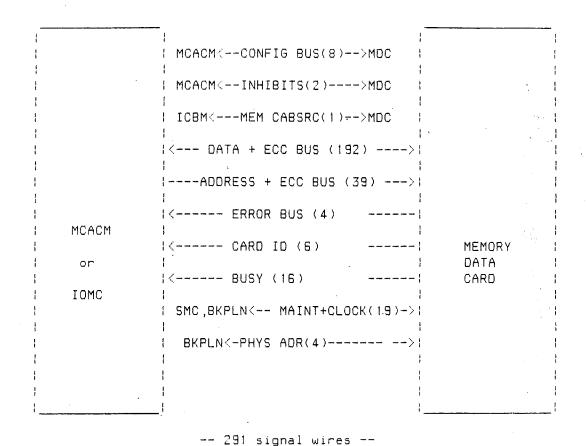

FIGURE 5.1 MEMORY DATA CARD BACKPLANE INTERFACE

COMPANY CONFIDENTIAL

SYSTEMS DESIGN SPECIFICATION Rev. B Page 9

#### 5.1 ADDRESS BUS

The address bus contains 4 fields: command, requestor I.D., module select, and block address. This 32 bit bus is protected by 7 bits of ECC.

#### 5.1.1 MEMORY COMMAND FIELD - KMEMCMD\$\$P(1:0)

The memory data card commands are:

- Ø READ MODIFY WRITE

- 1 WRITE

- 2 READ PUBLIC

- 3 READ PRIVATE

The MDC makes no distinction between read private and read public. These different kinds of reads are used by the MCACM and IOMC to maintain cache consistency.

#### 5.1.2 REQUESTOR ID FIELD - KMEMREQIDP(2:0)

This field is for distributed error detection of the memory bus arbitration logic. The definitions of the values of this field are:

- Ø MCACM Ø

- 1 MCACM 1

- 2 MCACM 2

- 3 MCACM 3

- 4 IOMC Ø

- 5: IOMC 1

- 6 IOMC 2

- 7 IOMC 3

Not used functionally by the MDC. Used in ECC checking and correction of Address Bus.

|                                                                | 10/27/86                   | ,         | 1993 5 | 238 |

|----------------------------------------------------------------|----------------------------|-----------|--------|-----|

| BURROUGHS CORPORATION SYSTEMS DEVELOPMENT GROUP PASADENA PLANT | +                          | ·         |        |     |

| COMPANY                                                        | +                          |           |        |     |

| CONFIDENTIAL SY                                                | STEMS DESIGN SPECIFICATION | DN Rev. B | Page   | 10  |

# 5.1.3 MODULE SELECT FIELD - KMODSEL\$\$P(4:0) (Ranges from 10 to 1F)

This field selects the memory data cards. The processor can accommodate 16 memory cards. The other 16 values are used to select the I/O memory concentrators for memory mapped I/O operations.

When the module secect is "00" hex through "0F" hex, I/0 memory concentrators are selected. When the module select is "10" hex through "1F" hex, memory data cards are selected:  $\frac{1}{2}$

#### 5.1.4 ADDRESS FIELD - KRAMADR\$P(21:0)

The absolute binary module address. This allows addressing 4M blocks per memory data card. This is the size of a memory card which is fully populated with 1M bit DRAM chips.

Each MDC requires 19 to 22 bits of address depending on the type and number of RAM chips it contains. A board that is half-populated with 256k-bit chips requires 19 bits, while a board that is fully-populated with 1meg-bit chips requires 22 bits.

5.1.4 ADDRESS FIELD - KRAMADR\$P(21:0) (Continued)

6 5 4 3 2 1 0 00:= x x % X X X X 02:= x x x X 03:= x x x  $\emptyset 4 := \times \times \times$ 05:= x x x 06:= × × 07:= x x Ø8:= x x 09:= x x x 10:= x x x x x x 11:= x x x 12:= x x x  $\times$   $\times$   $\times$ 14:= ×× 15:= x x 18:= x x x 19:= x x x 20:= × × ×  $21:=\times\times\times\times\times$ 22:= x x x  $23 := \times$  $\times$   $\times$ 24:= × 25:= x  $\times$   $\times$ 26:= × × × 27:=  $\times$   $\times$   $\times$ 28:= -  $\times$   $\times$   $\times$ 29:= x 30:= x  $\times$   $\times$ 31:= ×

FIGURE 5.2 ADDRESS BUS HAMMING CODE FIELD

5.1.4 ADDRESS FIELD - KRAMADR\$P(21:0) (Continued)

0101 1 0 110011001 0 0 1 2100001111 65431 0 0 0 0 0 0 0 0 1 1 0001 \* X X D X D D 28 X D D 13 D 27 12 D 0011 X D D 31 D 20 26 D D 14 M D M D D 10 0101 X D D 29 D 24 22 D D 15 M D ם ס א М Ø111 D Ø8 Ø9 D Ø5 D D M 19 D M D M M D 100 | X D D 30 D 25 23 D D M 16 D 17 D D 1011 D 06 07 D 11 D D M 04 D D M D M M D 1101 D 01 02 D 00 D D M 18 D 1111 03 D D M D M M D D M M D 21 D D M \* = NO BITS IN ERROR X = CHECK BIT IN ERROR D = DOUBLE BIT ERROR M = MULTIPLE BIT ERROR

FIGURE 5.3 ADDRESS BUS SYNDROME TO BIT IN ERROR DECODE TABLE

|                          |         |          |            |             | 1   |      |      |

|--------------------------|---------|----------|------------|-------------|-----|------|------|

|                          |         | 10/27/   | 36         |             | 1   | 1993 | 5238 |

| BURROUGHS CORPORATION    | +       |          |            | <del></del> | +   |      |      |

| SYSTEMS DEVELOPMENT GROU | JP !    |          |            |             |     |      |      |

| PASADENA PLANT           | }       | V500     | MEMORY DA  | ATA CARD    |     |      |      |

|                          | }       |          |            |             |     |      |      |

| COMPANY                  | +       | ;        |            |             |     |      |      |

| CONFIDENTIAL             | SYSTEMS | DESIGN S | SPECIFICAT | TION Rev    | . 8 | Page | 13   |

|                          |         |          |            |             |     |      |      |

#### 5.2 DATA BUS

The 192 data lines are bi-directional, and composed of 160 bits of actual data plus 32 bits of SEC-DED-S4EC code.

#### 5.2.1 DATA FIELD - XRAMDT(3:0)\$P(39:0)

The data bus is divided into four 48 bit groups of 40 bits of data and 8 bits of check bits. There are two reasons for this division: it fits into an array-pair, and it allows full coverage of any single (and total) memory SIP failure. The error code bits 0 and 7 are inverted such that a data word of all zeroes or all ones is detected as invalid. For example, 'proper' words of 0's or 1's are:

5.2.2 DATA BUS HAMMING CODE FIELD - XRAMEC(3:0)\$\$P(7:0)

|     |      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Ø |

|-----|------|---|---|---|---|---|---|---|---|

| 00  | ; =  |   |   |   | Χ | , |   | X | X |

| Ø 1 | : =  |   |   | Χ |   |   |   | Χ | Χ |

| 02  | : =  |   | Χ |   |   |   |   | Χ | Χ |

| 03  | ; =  | Χ |   |   |   |   |   | Χ | Χ |

| 04  | : =  |   |   |   | Χ |   | Χ |   | Χ |

| 05  | :=   |   |   | Χ |   |   | Χ |   | Χ |

| Ø6  | : =  |   | Χ |   |   |   | Χ | • | Χ |

| 07  | : =  | Χ |   |   |   |   | Χ |   | Χ |

| 08  | :=   |   |   |   | Χ |   | Χ | Χ |   |

| 09  | ;=:  |   |   | Χ |   |   | Χ | Χ |   |

| 10  | :=   |   | Χ |   |   | Χ | Χ |   |   |

| 11  | :=   | Χ |   |   |   | Χ | Χ |   |   |

| 12  | ; =  |   |   |   | Χ | Χ | Χ |   |   |

| 13  | ; =  |   |   | Χ |   | Χ | Χ |   |   |

| 14  | ; =  |   | Χ |   |   | Χ |   |   | Χ |

| 15  | : =  | Χ |   |   |   | X |   |   | Χ |

| 16  | : =  |   |   |   | Χ | Χ |   | Χ |   |

| 17  | .; = |   |   | Χ |   | Χ |   | X |   |

| 18  | :=   |   | Χ |   |   | Χ |   | Χ |   |

| 19  | :=   | Χ |   |   |   | Χ |   | Χ |   |

| 20  | ; =  |   | Χ |   | Χ |   |   |   | Χ |

| 21  | :=   |   | Χ |   | Χ |   |   | Χ |   |