NO 88786800 REV 01

DATE 6/13/73 PAGE 1 of

ZCDD

MP17

ENGINEERING SPECIFICATION

Originator:

NO REV DATE PAGE 88786800 0] 6/]3/73 2

| REV. | REVISION RECORD |      |           |                                             |       |      |  |

|------|-----------------|------|-----------|---------------------------------------------|-------|------|--|

| D]   | E.C. O.         | PAGE | PARAGRAPH | DESCRIPTION  MPl7 Engineering Specification | APVD. | DATE |  |

| עט   |                 |      |           | In Engineer ing Specir reaction             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           | ·                                           |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           | ••                                          |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

|      |                 |      |           |                                             |       |      |  |

# ENGINEERING

NO. 88786800 DATE 6/13/73 PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

#### TABLE OF CONTENTS

| 1.0 | 3C0DE        |                                    |  |  |  |  |  |

|-----|--------------|------------------------------------|--|--|--|--|--|

| 2.0 | APPLI        | APPLICABLE DOCUMENTS               |  |  |  |  |  |

| 3.0 | REQUI        | REQUIREMENTS                       |  |  |  |  |  |

|     | 3.1          | Definition                         |  |  |  |  |  |

|     | 3.2          | Block Diagram                      |  |  |  |  |  |

|     | 3.3          | General Description                |  |  |  |  |  |

|     | 3.4          | Physical                           |  |  |  |  |  |

|     | 3.5          | Reliability                        |  |  |  |  |  |

|     | 3.6          | Maintainability                    |  |  |  |  |  |

|     | 3.7          | Environmental                      |  |  |  |  |  |

|     | 3.8          | Refurbishment                      |  |  |  |  |  |

|     | 3.9          | Design Technology and Construction |  |  |  |  |  |

| 4.0 | QUALI'       | TY ASSURANCE PROVISION             |  |  |  |  |  |

|     | 4.1          | Tests and Checks                   |  |  |  |  |  |

|     | 4.2          | Measurements                       |  |  |  |  |  |

|     | 4.3          | Workmanship Verification           |  |  |  |  |  |

|     | 4.4          | Test Methods                       |  |  |  |  |  |

| 5.0 | PREPAI       | RATION FOR DELIVERY                |  |  |  |  |  |

| ۴.0 | NOTES        |                                    |  |  |  |  |  |

|     | <b>6</b> - 1 | Equipment Data Sheet               |  |  |  |  |  |

NO. 88786800 DATE 6/13/73 PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

#### TABLE OF CONTENTS

| 7.0 | APPEN | DIX I MP17 CONFIGURATION                     |

|-----|-------|----------------------------------------------|

|     | 7.1   | Programming                                  |

|     | 7.2   | Repertoire of Instructions {Basic 1700}      |

|     | 7.3   | Enhanced Instructions                        |

|     | 7.4   | 1700 Emulation                               |

|     | 7.5   | Internal I/O and Teletype/Display Controller |

| 8.0 | APPEN | DIX II CONTROLLER CONFIGURATION              |

| 9.0 | APPEN | DIX III GLOSSARY                             |

NO 88786800 REV DL DATE 6/13/73 PAGE

ZCDD

J.O SCOPE

This specification describes a small scale stored program parallel mode digital computer. This computer has the capability of being configured in two ways.

- a. The classical single level processor with a oneto-one relationship of instruction read from storage and a hardware decode and execution takes place.

- A multilevel execution. **b** • In this atmosphere a macro-instruction program is stored in what may be called the main memory system and a micro-instruction program is stored in what may be called a micro-memory system. These memory systems may be one and the same or may be different. In this machine they are different; the micro-memory is smaller in capacity and faster in both access and cycle time. Macro-instructions are read from main memory serially by a portion of the micro-program. The macro instruction is then decoded by a combination hardware/software technique. The hardware portion of the macro-instruction decode is called a transform. The transform process causes the micro-program to form program branches, sets parameters and performs arithmetic or logical operations all in parallel. A transform is performed as if it was a standard stored micro-instruction. Numerous different types of transforms are executed in the process of executing a macro-instruc-Macro-instructions may be decoded either with or without the use of the transform feature, however, use of transforms increase the performance and reduces the number of micro-instructions many fold.

NO 88786800 REV 01 DATE 6/13/73 PAGE

ZCDD

| 2.0 | APPLICABLE DOCUMENTS         |                |                                                     |  |  |  |

|-----|------------------------------|----------------|-----------------------------------------------------|--|--|--|

| 5.1 | Standards and Specifications |                |                                                     |  |  |  |

|     | NCR Standard                 | SK 077-9900005 | 605 Computer Standards                              |  |  |  |

| ,   | CDC Standard                 | 7.30.077       | Computer & Peripheral Equipment Design Requirements |  |  |  |

|     | CDC Manual                   | 60]65800       | 1700 I/O                                            |  |  |  |

|     | CDC Specification            | 11852200       | 1,700 I/O                                           |  |  |  |

|     | CDC Specification            | 52429300       | 1714 Processor                                      |  |  |  |

|     | CDC Specification            | 11858100       | 1200 D24                                            |  |  |  |

|     |                              |                |                                                     |  |  |  |

|     | CDC Manual                   | 14535000       | Micro-Programmable<br>Processor                     |  |  |  |

|     | CDC Specification            | 77950P00       | 1704 Processor                                      |  |  |  |

|     | CDC Specification            | 52308600       | 1774 Processor                                      |  |  |  |

|     | CDC Specification            | 89656500       | CR17 Processor                                      |  |  |  |

|     | CDC Standard                 | 7.30.055       | EMC Performance<br>Requirements                     |  |  |  |

|     | CDC Standard                 | 1.01.000       | Hardware Configuration<br>Management Standards      |  |  |  |

|     | CDC Standard                 | 1.20.007       | Acoustical Noise<br>Standard                        |  |  |  |

01 6/13/73

ZCDD

#### 3.0 REQUIREMENTS

#### System Definition 3.1

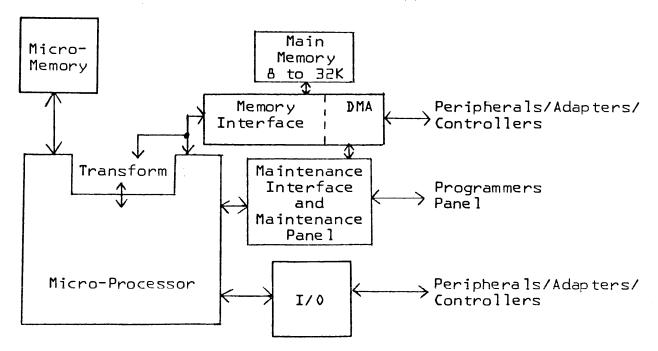

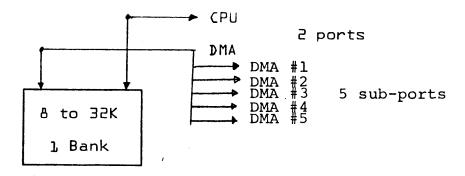

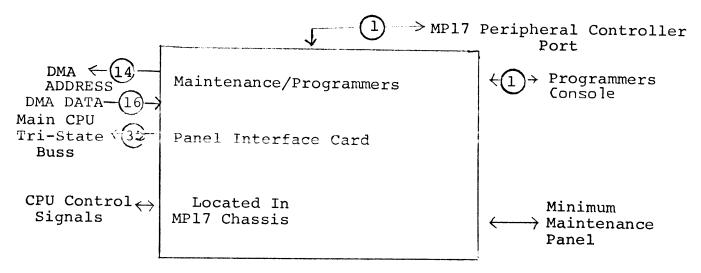

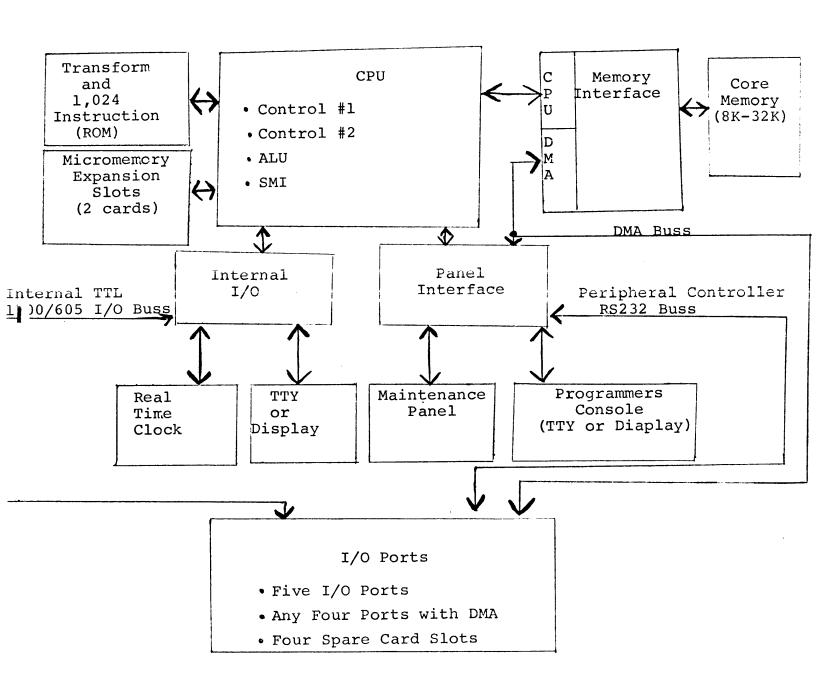

The processor is parallel mode, stored program, digital computer made up of a minimum of three of the six blocks shown in Figure 1 - The Basic System Block dia-The minimum blocks are: gram.

- 1. Micro-processor

- Maintenance interface/maintenance panel 2.

- з. Micro-memory

This minimum configuration could be utilized in a peripheral controller or I/O processor type application. The complete configuration shown in Figure ] is more typical of two-level computer with the microprocessor emulating program stored in the main memory. Figure 1 is the basic processor block diagram defining the MP17 emulation described in Appendix 1.

Figure 1. Basic System Block Diagram Mini-Configuration

Š,

NO. 88786800 DATE<sub>6</sub>/13/73 PAGE

ZCDD

#### 3.3 General Description

#### 3.3.1 Micro-Processor (MP)

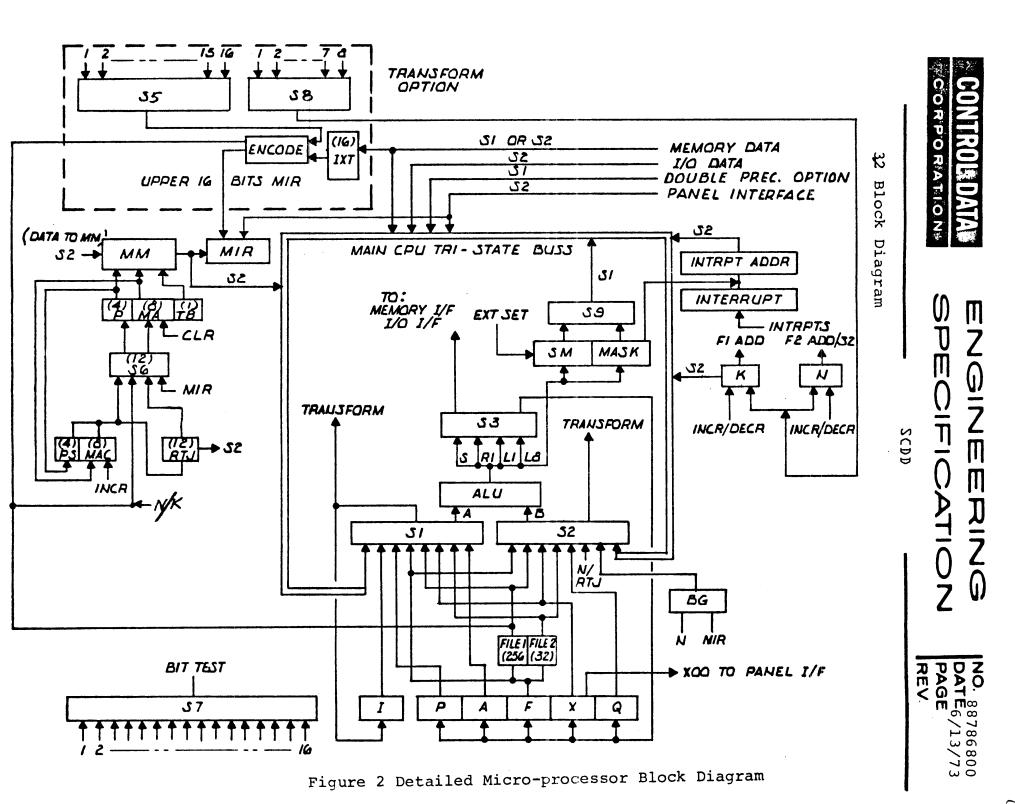

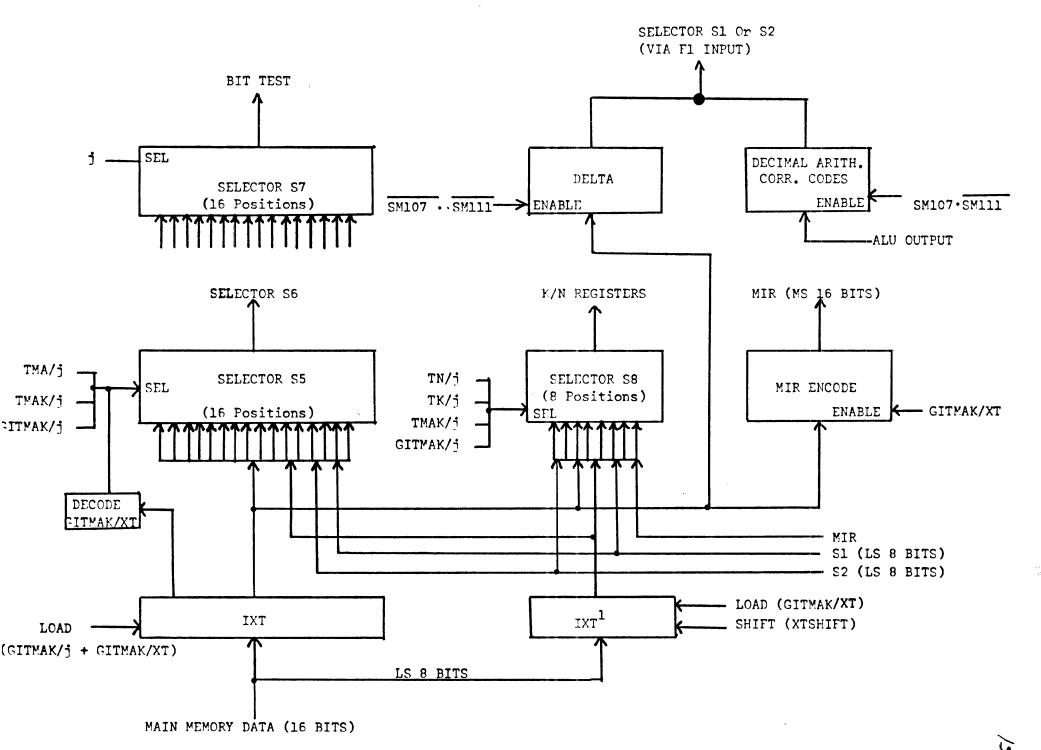

The detailed organization of the MP is shown in Figure 2. This diagram shows that the registers of the MP are interconnected primarily by selectors. The selectors in the diagram are numbered from S1 to S3 and S5 to S9. A selector is a multiplexer that provides for transferring one of several inputs to an output. Selectors S1, S2, S3, and S9 are word-width selectors that provide for the transfer of a complete MP word to the output. Selectors S5, and S8 are 8-bit selectors and provide for the transfer of an 8-bit quantity; Selector S7 is a single bit selector for transferring one of 16 input bits to its output. Selector S6 is a 12 bit selector, and provides for transferring micromemory address to P/MA.

The unlabeled inputs to selectors represent uncommitted logic in the basic MP design, which is specified by the system designer to provide an efficient solution to a specific system design problem. Arrows leaving a register or a data path represent data points that are available on the backpanel wiring of the MP; they are candidate bits of information for connection to the uncommitted logic of the MP. The detailed wiring of the uncommitted selector inputs is performed on the transform module, which is different for each MP application.

## 3.3.1.1 Micromemory and Microcontrol Section

The MP micromemory is an IC memory with a basic memory size of 256 words. Each word is 64 bits long, containing two 32-bit microinstructions. The basic memory size can be expanded to a maximum of 8192 micro-instructions. The micromemory is available in two forms:

1. A read/write micro-memory (RAM) is available for use during program development and in applications that require the MP to be re-programmed or reorganized for multiple applications. This read/write micro-memory can

NO. <sub>88786800</sub> DATE <sub>6/13/73</sub> PAGE REV. <sub>01</sub>

ZCDD

be loaded from an external device, or data can be written into micro-memory under control of the micro-program. The RAM micro-memory expansion cards are available in only one version, this version contains 512 micro-instructions per card.

2. A read only micro-memory (ROM) is available for fixed applications of the MPP. This is programmed during manufacture. It is available only on the transform board of the MP17 1700 emulator, and provides for 1,024 instructions.

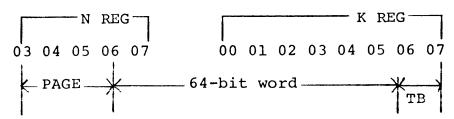

The micromemory is addressed by the P/MA register. The P portion of the register is a page control and consists of four bits specifying up to 16 pages of micromemory. A page consists of 256 words or 512 microinstructions. The MA register is an 8-bit register that specifies one of the 256 microinstruction pairs within the page that is to be the source of the next microinstruction. The T field of the current microinstruction is used to select the upper or the lower of the microinstruction pair as the next microinstruction to be executed. Microinstruction sequencing is designed so that no automatic overflow of addressing from the MA register to the P register occurs; any transfer of control between pages is initiated by a page jump operation, MA transform operation, or clear page operation.

## 3.3.1.1.1 Page/Micromemory Address Register

The P/MA register provides addressing for the micromemory. The micromemory is organized into pages of 256 locations, which provide for 512 microinstructions. The P portion of the register selects one of 16 pages, while the MA provides for selection one of the 256 locations within the page.

NO. 88786800 DATE 6/13/73 PAGE REV. D1

ZCDD

The P portion of the register can be set from a microinstruction, from the PS, from the RTJ register, or from an output of the transform module. The micromemory address portion of the register can be set from a microinstruction, from the MAC, from the RTJ register, or from an output of the transform module. The MA portion of the register has no sequencing capability; this is provided by the MAC. The combination N/K register can provide an address to P/MA for micromemory Read/Write operand references.

#### 3.3.1.1.2 Memory Address Counter

The MAC is a counter which is used to determine the next location within a page following the current location specified in the MA register. In operation, the contents of the MA register is transferred to the MAC at each micromemory reference, then the contents of the MAC is incremented by one to point to this next location. Depending on the sequencing operation specified in the microinstruction, the MAC may or may not be used to obtain the next microinstruction. Sequencing of the MAC is such that location 0 within a page follows location 255 on that page.

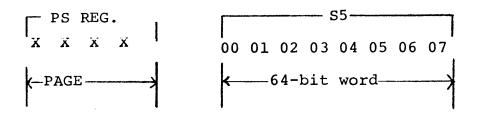

#### 3.3.1.1.3 Page Storage Register (PS)

The PS register is a four bit holding register which, is used to determine the page for the next instruction. In operation the contents of the page register is transferred to the PS at each micromemory reference. Depending on the sequencing operation specified in the microinstruction the PS may or may not be used to obtain the next microinstruction.

#### 3.3.1.1.4 Microinstruction Register

The MIR is a 32-bit register which is used to hold the microinstruction during execution. Data is normally entered into the MIR from the micromemory; either the upper or lower 32 bits of the contents of the micromemory location are gated to the MIR, based on the value of the test bit determined during the preceding microinstruction. A test bit of 0 specifies the upper microinstruction, and a test bit of 1 specifies the lower microinstruction.

NO. DATE PAGE REV.

88786800 6/13/73

SMALL COMPUTER DEVELOPMENT DIVISION

Data may also be transferred into MIR from the maintenance panel interface. This is done as a result of an operator request, it may or may not result in offline mode depending on the function requested.

A transform design option allows data to be transferred from the transform module to the upper 16-bits of the MIR for specialized applications.

#### 3.3.1.1.5 Return Jump Register

The RTJ register is provided to capture the location of the next microinstruction pair at any time, when specified by a microinstruction. When this capture is specified, the contents of MAC is incremented and PS and MAC are stored in the RTJ register. The contents of the RTJ register is unchanged until the next command is given to save a new address. This saving of the next instruction pair location is independent of any actual transfer of control. The output of the RTJ register can be gated to the P/MA register to perform the return operation or the MA portion may be read into the organization of the MPP through selector S2.

### 3.3.1.2 Transforms and the Transform Module

The transform feature of the MPP provides the microprogram with the capability to select any pattern of bits from the data transmission paths of the MPP, to form micromemory addresses to sequence the microprogram, and to set the contents of the K and N register and upper 16 bits of the MIR register.

The transform hardware is packaged on a separate module and is specialized for each particular application. The transforms are implemented on two selectors, S5 and S8 which are located on the transform module along with the bit test selector S7.

Selector S5 is an eight bit wide two position to sixteen position selector which is used to form micromemory addresses A maximum of sixteen different micromemory address (MA) constructions can thus be specified. The MA transformed specifies one of 256 64-bit microwords within a page. The T field code specifies which 32 bit microinstruction is to be executed. If SM207 is set to 1, the transform address will be to the page denoted in the S1 field of the microinstruction. If SM207 is set to 0, the transform

NO. 88786800 DATE 6/13/73 PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

address will reside in the same page as the microinstruction currently being executed. The lower (least significant) eight bits of the output of S2 shall represent MA transform number 7 (j=0111 in C field) on all configurations.

Selector S8 is an eight bit wide two position to sixtten position selector which is used to select a source for loading the K or N register. Two of the sources are fixed; KN transform 0 (j=0000) shall be the output of the lower (least significant) eight bits of S2 and KN transform 6 (j=0110) shall be the output of the lower (least significant) eight bits of the MIR.

A specialized transform of the upper (most significant) 16 bits of the MIR register may be implemented to provide more efficient emulation. In order to utilize this feature, the macro instruction register (referred to as IXT) must be located on the transform module. This feature allows the upper 16 bits of MIR to be loaded directly with information encoded off the IXT register in order to control MPP arithmetic function during macro emulation RNI cycles.

Selector S7 is a one bit wide, two position to thirty two bit position selector, which is used to test a specific condition to determine which microinstruction to execute from the next microinstruction pair. This capability is used by placing a BTU command in the T field of the microinstruction; the lower five bits of the C field (j) determine which of the thirty two possible bits to test. If the tested bit is a one, the upper microinstruction is executed; otherwise, the lower microinstruction is executed.

Bits that can be tested include all the bits available for use in creating transforms and bits associated with any specialized I/O logic.

The following MPP outputs are available for monitoring by the transform module.

- . Sl

- . S2

- . SM Registers

- . MIR

- . Main Memory Read Data Bus

- . Bits 19 and 24 through 31 of micro memory read data

# ENGINEERING REV DATE PAGE

NO 88786800 REV 01 DATE /13/73

ZCDD

- 3.3.1.3 Arithmetic and Logical Unit and Data Transfer Organization

- 3.3.1.3.1 The ALU provides the arithmetic and logical capabilities of the CPU. This unit combines two input words of the system word length, one from the A input provided by \$1 and the other from the B input provided by \$2.

These two inputs are combined according to the function code specified in the microinstruction; the result is delivered simultaneously at the output of the ALU for possible shifting and delivery to the destination register, to the ALU buffer circuit for delivery to the SM and mask registers, and to the memory bus and the panel interface. It is possible to ignore the output of the ALU on any instruction. The result of the ALU operation as to the sign, zero, and magnitude (by means of the carryout test) is available to the test bit logic for instruction sequencing.

Arithmetic operations may be in 1's or 2's complement arithmetic and can operate on either single precision operands or on double precision operands, using the double precision hardware available as an option. Selection of single or double precision and 1 or 2's complement mode is controlled by the microprogram which controls the states of the applicable bits in the SM register.

Also available as an option is the ability to perform split adder operations. For example, in a 1½ bit CPU, a split may be made between the upper and lower 8-bit groups and would allow operations on each group to take place simultaneously. The selection of the split adder is controller by setting or clearing a bit in the SM register. The split has no effect on logical operations, since these do not involve a carry between bits.

NOTE: Design allowances have been made for optional special algorithms of which arithmetic is one. However, design of these options is not presently included in the development.

NO 88786800 REV D1 DATE6/13/73 PAGE 1:5

ZCDD

The data transfer organization of the CPU provides for storing data in one of six working registers and two files and for selecting data to be processed through the ALU. ALU results are transferred back to one of the registers or out of the organization to control external equipment.

The primary data registers are I, P, A, F, X, and  $\mathcal{Q}$ . The names given to the registers are descriptive of the normal use of the registers in an emulation; however, the names are not intended to limit the use of the registers.

#### 3.3.1.3.2 I Register

The I register is a word length register used primarily to hold the emulated software instruction being executed by the CPU. It is also available as input to S1, and therefore, to the A input of the ALU.

Data is entered into the I register from the output of S1. This connection is provided so that datamay be transferred from memory directly to the I register, in addition to performing some other operation on the memory data or transferring the memory data to another register through the ALU.

## 3.3.1.3.3 P Register

The P register is a word length register which receives data from the ALU and whose output is provided to Sl and thus to the A input of the ALU. This is a general purpose register; however, it normally is used to contain the software instruction counter for the emulation of a computer.

## 3.3.1.3.4 A Register

The A register is a word length, general purpose register which receives data from the ALU and provides output to  $S_{\perp}$  and thus to the A input of the ALU.

The A register is mechanized as a shifting regiser, and it can be shifted left or right without the use of the ALU. The A register may also be combined with the Q register to form a double length shifting register, which operates independently of the ALU.

# ENGINEERING SPECIFICATION PAGE /13/73

NO 88786800

ZCDD

#### 3.3.1.3.5 F Register

The F register is a word length, general purpose register which can be read into the A or B input of the ALU. This register is also used as the file entry register and contains the information written into file 1 or file 2 when these files are used as the destination of an ALU operation.

#### 3.3.1.3.6 X Register

The X register is a word length, general purpose register which can be read into the A or B input of the ALU.

#### 3.3.1.3.7 **Q** Register

The Q register is a word length, general purpose register which receives data from the ALU and provides output to S2 and thus to the B side of the ALU. The Q register is mechanized as a shifting register; it may be shifted left or right in conjunction with the A register, without the use of the ALU.

#### 3.3.1.3.8 Register File Usage

Files 1 and 2 are word length, scratchpad, storage register files which are addressed by the K and N registers, respectively.

#### 3.3.1.3.9 File ]

File 1 is a file of 256 general purpose, word-sized registers which are addressed by the contents of the K register: the output of the addressed file is delivered to SI and S2, and thus to the A and B side of the ALU on demand. A S/M bit is provided for selecting either the output of File 1 or output from the transform module as this input to S1 or S2.

NO 88786800 REV 01 DATE 6/13/73 PAGE

ZCDD

3.3.1.3.10 File 2

File 2 is a 32-word file and is addressed by the lower five bits of theN register. It is intended primarily as a source of constants, but may be used as a general purpose, word-sized register which delivers its output to \$1 and \$2, and thus to the A and B side of the ALU.

3.3.1.3.11 Bit Generator

The bit generator is a circuit that generates one bit at any bit position in a word as input to the B side of the ALU. Bits are numbered from left to right as bits O to N, where N is the number of bits in a word minus one. Control todrive the bit generator is derived either from the microinstruction {bits 27 to 31} or from the lower five bits of the N register. Control is usually obtained from the microinstruction. The choice of which input drives the bit generator is based on the setting of a bit in the SM register.

3.3.1.3.12 Selector 1

Sl provides for the selection of one of eight inputs for delivery to the ALU or for delivery to the I register if the I register is selected as a destination in the microinstruction. The selector also provides data for transforms.

Input to the selector is from the following:

- M Input bus

- I register

- ▶ P register

- ▶ Fregister

- File ] or external input {transform}

- ★ X register

- ⊭ File 2

- A register

Output from the selector goes to the following:

- M ALU

- External output or transform

- I register

NO 88786800 REV D1 DATE 6/13/73 PAGE

ZCDD

Input Bus to Selector 1

The input bus is one input to S1 and provides for selection of input data to be transmitted to S1. The data may come from:

- ▶ Data from the external main memory

- Output of the SMregisters or the interrupt mask registers

- Algorithm

#### 3.3.1.3.13 Selector 2

\$2 provides for the selection of one of eight inputs for delivery to the B input of the ALU. In addition, the second output provides for the transfer of information from this selector to the transform module and to themicromemory.

Input to S2 is from the following:

- ▶ F register

- File ↓ or external input {transform}

- X register

- ▶ File 2

- Q register

- M N and RTJ registers

- Bit generator

- Input bus

Input Bus to Selector 2

The input bus provides for submultiplexing of data for input to S2. Inputsto the input bus are:

- Main memory

- Interrupt address

- Micromemory

- I/O system, maintenance panel interface

- \* K register

# ENGINEERING

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

#### 3.3.1.3.14 Status/Mode Register

Module Bits

The SM register allows the microprogram to control the mode of operation and also allows the microprogram to examine the status of certain internal and external conditions. The CPU can access one or two SM registers, referred to as SMl and SM2. Each SM register contains the same number of bits as the basic processor word; sixteen bits for a sixteen bit processor or thirty two bits for a thirty two bit processor. Therefore, the maximum total number of SM bits in a CPU is twice the basic processor word length.

An SM register module contains 16 bits of SM1 and 16 bits of SM2. All 32 bits of an SM module can be set or reset by the microprogram by transferring information to the SM register from the output of the ALU.

The SM register bits are numbered as follows for 16 bit and 32 bit processors.

16 bit CPU: SMl bits numbered S100 to S115;

SM2 bits numbered S200 to S215.

32 bit CPU: SMl bits (first module) numbered

as flags 4-7.

S100 to S115

SMl bits (second module) numbered

S116 to S131

SM2 bits (first module) numbered

S100 to S115

SM2 bits (second module) numbered

S216 to S231.

The individual bits of an SM module have the following additional characteristics.

| SM1 (0-3)<br>SM1 (16-19)<br>SM2 (0-3)<br>SM2 (16-19) | These bits are flag bits which can be set or reset by the SETF and CLRF commands in a microinstruction. These commands provide for addressing up to 16 flags. In a 16 bit processor bits 0-3 of SM1 are address as flags 0-3 and bits 0-3 of SM2 are addressed |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                      | flags 0-3 and bits 0-3 of SM2 are address                                                                                                                                                                                                                      |

Functional Characteristics

NO. DATE PAGE REV.

# SMALL COMPUTER DEVELOPMENT DIVISION

In a 32 bit processor with two SM modules, bits 0-3 of SMl are flags 0-3, bits 16-19 of SMl are flags 4-7, bits 0-3 of SM2 are flags 8-11 and bits 16-19 of SM2 are flags 12-15.

The flag bits are not cleared by a processor master clear, and no external input is provided to these bits.

SM1 (0-3) and SM1 (16-19) are available as a true output from the SM module. SM2 (0-3) and SM2 (16-19) are available as a complement output from the SM module.

| SM1<br>SM2 | (4-7)<br>(20-23)<br>(4-7)<br>(20-23)     | These bits can be set by an external signal and cleared by a processor master clear. These bits are all available as a true and complement output from the SM module.                                                                      |

|------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SM1<br>SM2 | (08-11)<br>(24-27)<br>(08-15)<br>(24-31) | These bits can be set by an external signal and can be cleared by a processor master clear. SM2 (14-15) and SM2 (30-31) can also be cleared by an external signals. These bits are available only as true outputs from the SM module.      |

|            | (12-15)<br>(28-31)                       | These bits can be set by an external signal and can be cleared by a processor master clear. SM1 (14-15) and SM1 (30-31) can also be cleared by an external signal. These bits are available only as complement outputs from the SM module. |

The assignment of status and mode conditions to specific bits of the SM register is a design function. The following assignment of status and mode fits in the minimum standard assignment. Bit assignments which are optional are listed with parenthesis. Bits are identified as S for status and M for mode.

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

| BIT | TYPE | FUNCTION                   |

|-----|------|----------------------------|

| 100 | М    | (Double Precision)         |

| 101 | M    | 1's complement             |

| 102 | M    | Bit generator input from N |

| 103 | M    | (Adder Split)              |

| 104 | S    | Main Memory Parity Error   |

| 105 |      | Open                       |

| 106 | M    | (Enable Interrupt System)  |

| 107 |      | Open                       |

| 108 |      | Open                       |

| 109 | М    | Micro-Halt                 |

| 110 | S    | Overflow                   |

| 111 | М    | (Enable F1)                |

| 112 |      | Open                       |

| 113 | М    | Select XT/MA (R/W MM)      |

| 114 |      | Open                       |

| 115 |      | Open                       |

|     |      |                            |

| 200 |      | Open                       |

| 201 |      | Open                       |

| 202 |      | Open                       |

| 203 |      | Open                       |

| 204 | M    | Autoload                   |

| 205 |      | Open                       |

| 206 |      | Open                       |

| 207 | М    | Select Page XT/MA          |

| 208 |      | Open                       |

| 209 |      | Open                       |

| 210 | M    | Enable MM to MIR           |

| 211 | М    | Enable DMA to MIR          |

| 212 |      | Open                       |

| 213 | S    | Console Request Control    |

| 214 |      | Open                       |

| 215 |      | Open                       |

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

## 3.3.1.3.14.1 CPU Operating Modes

The following CPU operating modes are incorporated into a system during manufacture. The operations are controlled by a mode fit in the SM register, but if an option is not included, the associated mode bit is open in the SM register.

## Double Precision Arithmetic (SM100)

If this mode bit is set to 1 and the double precision hardware option is included, the ALU and the ALU\* on the double precision option module are combined to form a double-word length ALU. This double-word length ALU operates for addition and subtaction but not for logical operations.

If this mode bit is set to 0, the double precision ALU\* is disconnected from the ALU and no operation takes place in ALU\*.

## l's Complement (SM101)

If this mode bit is set to 1, the ALU (and ALU\* for double precision operation) operates in 1's complement arithmetic mode for addition and subtraction.

If the mode bit is set to 0, operations are in 2's complement arithmetic mode for addition and subtraction.

## BG Input From N (SM102)

If this mode bit is set to 1, the bit generator is controlled by the lower five bits of the N register.

If this mode bit is set to 0, the bit generator is controlled by the lower five bits of the microinstruction.

## Adder Split (SM103)

If this mode bit is set to 1, the ALU is split into two independent ALU's at the adder split point for arithmetic operation. The split point is between bits 07 and 08 on a 16-bit processor and between bits 15 and 16 on a 32-bit processor. On a 16-bit processor, both the upper and lower portion of the ALU operate in 2's complement arithmetic. In a 32-bit processor if 1's complement mode is selected, the upper adder operates in 2's complement mode while the lower adder operates in 1's complement mode.

If this mode bit is set to 0, the ALU operates as a single word-size ALU.

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

## Enable Interrupt System (SM106)

If this mode bit is set to 1, the interrupt system of the processor is activated and the INTU test can examine the interrupt system.

The interrupt lines to be enabled/disabled by this mode bit are selectable in groups of four interrupt lines. Therefore on a 16-bit processor any combination of four groups can be controlled by this mode bit and on a 32-bit processor any combination of eight groups can be controlled by this bit. Groups not controlled by the mode bit can be constantly enabled or disabled.

If this mode bit is set to 0, the interrupt system is disabled and the INTU test will always receive a reply of "no interrupt present" on groups controlled by the mode bit.

## Micro Halt (SM109)

If this mode bit is set to 1, any microinstruction with a HALT code in the S field stops the operation of the processor on completion of the microinstruction.

If this mode bit is set to 0, the HALT code in the S field of any microinstruction is ignored.

## Enable Fl (SM111)

If this mode bit is set to 1, the output of File 1 is enabled to Selector S1 or S2. This overrides any selection of an external source.

If this mode bit is set to 0, the output of File 1 is disabled as an input source to Selector S1 or S2. If an external source (such as the transform module) is available it may be enabled to selector S1 or S2 at the same position as defined for F1.

Note that this mode bit must be set to 1 in order to write into Fl.

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

## Select XT/MA (R/W MM) (SM113)

If this mode bit is set to 1 the MA transform determines the micromemory address for read/write micromemory operand references.

If this mode bit is set to 0, the combination N/K register determines the micromemory address for read/write micromemory operand references.

## Autoload (SM204)

If this mode bit is set to 1 the autoload mode is selected on the console interface.

If this mode bit is set to 0 the autoload mode is disabled on the console interface.

## Select Page XT/MA (SM207)

If this mode bit is set to 1 an MA transform can be executed across a page boundary, by setting the desired page in the S field of the microinstruction. Normal S field operations are disabled.

If the mode bit is set to 0 an MA transform is limited to the page in which the microinstruction containing the MA transform command resides. The S field of the microinstruction is decoded for normal operation.

## Enable MM to MIR (SM210)

If this mode bit is set to 1, the output of the micromemory is pre-enabled to the MIR. A page jump or return jump microinstruction must be executed with this mode bit set to 1 to force the actual selection to the page and address selected.

If the mode bit is set to 0, the output of the console interface is pre-enabled to the MIR. A page jump or return jump micro-instruction must be executed with this mode bit set to 0 to force the actual selection. If the processor is master cleared, the console interface is enabled to the MIR.

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

#### Enable DMA to MIR (SM211)

If this mode bit is set to 1 and SM210 is set to 0 and a page jump or return jump microinstruction is executed, main memory data via the console interface is selected to the MIR for microinstruction execution at the page and address selected.

If this mode bit is set to 0 and SM210 is set to 1 and a page or return jump microinstruction is executed, control is transferred back to micromemory at the page and address selected.

#### 3.3.1.3.14.2 MPP Status

The following CPU status bit assignments are incorporated into a system during manufacture. All of these status bits are set by the condition detected; the clearing of the status bit must be performed by the microprogram with the exception of SM1 (bits 14, 15, 30, 31) and SM2 (bits 14, 15, 30, 31) which have an external clear input.

## Main Memory Parity Error (SM104)

This status bit is set to 1 if the main memory interface detects a parity error on data read from memory.

## Overflow (SM110)

This status bit is set to 1 on detection of an overflow condition. The processor provides for three selectable overflow conditions to be tested.

- . Arithmetic overflow microinstruction performing the arithmetic operation is an add or subtract with overflow test and the arithmetic result is inconsistent with the sign of the operands and the arithmetic operation.

- . Binary overflow microinstruction performing the arithmetic operation is an add or subtract with overflow test and a carry out of the most significant bit of the ALU occurred. This condition is tested if an optional binary overflow SM bit is set to 1.

NO. DATE PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

. Decimal Overflow - microinstruion performing the arithmetic operation is a decimal add or subtract with overflow test and decimal overflow occurred. This condition is tested if an optional decimal arithmetic SM bit is set to 1 and the decimal arithmetic algorithm is included on the transform module.

### Console Request Control (SM213)

This status bit is set to 1 if the control console interface is requesting control via the MIR. The microprogram should return control to the console via SM210. This status bit is wired to an interrupt line.

### 3.3.1.3.15 Interrupts and Mask Register

The interrupt system is implemented as a sampled data system at the microprogram level instead of as a true interrupt as used in conventional computers. That is, the interrupt system provides a sampling capability in which a microinstruction can sample the interrupt system to see if there is any interrupt present that has its corresponding mask register bit set to 1. This sample is taken by performing an INTU operation in the T field of any microinstruction. If there is an interrupt in the system whose mask register bit is 1 and the interrupt system is enabled the next microinstruction is executed from the upper of the next microinstruction pair. If there is no such interrupt, the next microinstruction is executed from the lower of the next microinstruction pair.

When an interrupt is recognized, the microprogram samples the interrupt address encoder to identify the most significant (highest priority) interrupt. The interrupt address encoder must be read in the microinstruction following the interrupt test, to be sure of a correct interrupt line address. If the interrupt address is read earlier or later, there is a possibility that the address encoder output is unstable due to a newly-arrived interrupt. The interrupt address is read by performing an INTA operation in the B' field of any microinstruction.

No standard interrupts are defined; the use of the interrupt system and the design of interrupts are functions of the application. Interrupts are identified by the corresponding mask bits which are assigned to control the interrupt recognition. The bits in the mask registers are identified as follows:

NO. DATE PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

## TABLE 3-19. MPP INTERRUPT ADDRESSES (M1)

| Mask Bit | Interrupt Address<br>16 Bit Processor | (Base 10)<br>32 Bit Processor |

|----------|---------------------------------------|-------------------------------|

| M100     | 15                                    | 47                            |

| M101     | 14                                    | 46                            |

| M102     | 13                                    | <b>4</b> 5                    |

| M103     | 12                                    | 44                            |

| M104     | 11                                    | 43                            |

| M105     | 10                                    | 42                            |

| M106     | 9                                     | 41                            |

| M107     | 8                                     | 40                            |

| M108     | 7                                     | 39                            |

| M109     | 6                                     | 38                            |

| M110     | 5                                     | 37                            |

| M111     | 4                                     | 36                            |

| M112     | 3                                     | 35                            |

| M113     | 2                                     | 34                            |

| M114     | 1                                     | 33                            |

| M115     | 0                                     | 32                            |

| M116     |                                       | 15                            |

| M117     |                                       | 14                            |

| M118 ·   |                                       | 13                            |

| M119     |                                       | 12                            |

| M120     | <del></del>                           | 11                            |

| M121     | ~ <b>-</b>                            | 10                            |

| M122     |                                       | 9                             |

| M123     |                                       | 8                             |

| M124     |                                       | 7                             |

| M125     |                                       | 6                             |

| M126     | enn gen                               | 5                             |

| M127     | <b></b>                               | 4                             |

| M128     |                                       | 3                             |

| M129     |                                       | 2                             |

| м130     |                                       | 1                             |

NO. DATE PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

| TD 3  | DIE | < | • | U | _ |

|-------|-----|---|---|---|---|

| .1. Δ | BLE |   | - | • | • |

|       |     |   |   |   |   |

MPP INTERRUPT ADDRESS (M2)

|              | TABLE                         |                                    |

|--------------|-------------------------------|------------------------------------|

| Mask Bit     | Interrupt<br>16-Bit Processor | Address (Base 10) 32-Bit Processor |

| M200         | 31                            | 63                                 |

| M200<br>M201 | 30                            | 62                                 |

| M202         | 29                            | 61                                 |

|              | 28                            | 60                                 |

| M203         | 27                            | 59                                 |

| M204<br>M205 | 26                            | 58                                 |

|              | 25                            | 57                                 |

| M206         | 24                            | 56                                 |

| M207         | 23                            | 55                                 |

| M208         | 22                            | 54                                 |

| M209         | 21                            | 53                                 |

| M210         | 20                            | 52                                 |

| M211         | 19                            | 51                                 |

| M212         | 18                            | 50                                 |

| M213         | 17                            | 49                                 |

| M214         | 16                            | 48                                 |

| M215         | 10                            |                                    |

| M216         | <b></b>                       | 31                                 |

| M217         | <b>~-</b>                     | 30                                 |

| M218         |                               | 29                                 |

| M219         |                               | 28                                 |

| M220         |                               | 27                                 |

| M221         |                               | 26                                 |

| M222         |                               | 25                                 |

| M223         |                               | 24                                 |

| M224         |                               | 23                                 |

| M225         |                               | 22                                 |

| M226         |                               | 21                                 |

| M227         | · <b></b>                     | 20                                 |

| M228         |                               | 19                                 |

| M229         |                               | 18                                 |

| M230         |                               | 17                                 |

| M2 ?         |                               | 16                                 |

|              |                               |                                    |

NO. DATE PAGE REV.

SMALL COMPUTER DEVELOPMENT DIVISION

#### Mask Register 1 (M1)

M100 through M115 (16-bit processor) M100 through M131 (32-bit processor)

#### Mask Register 2 (M2)

M200 through M215 (16-bit processor) M200 through M231 (32-bit processor)

Interrupt addresses are generated by the interrupt address encoder according to the assignments for a 16-bit and 32-bit processor given in Tables 3-19and 3-20.

The interrupt priorities correspond to the interrupt address generated; that is, interrupt address 0 is associated with the highest priority interrupt line and interrupt address 31 is associated with the lowest priority interrupt line in a 16-bit processor. As an example, an interrupt associated with M112 would have priority over an interrupt associated with M111 in a 16-bit processor and an interrupt address of 3<sub>10</sub> would be developed by the interrupt address encoder.

The output from the interrupt address encoder is the complement of the interrupt address for input to S2; thus the transfer of the interrupt address to the X register, for example, would be coded using a -B code in the F field, INTA in the B' field, and X in the D field. This results in the correct interrupt address being transferred.

A design option in the interrupt system provides for activating interrupts in groups of four interrupt lines. Therefore, on a 16-bit processor, any combination of four groups can be controlled by the enable interrupt SM bit(s) and on a 32-bit processor any combination of eight groups can be controlled by SM bit(s). Groups not controlled by SM bit(s) can be allowed to remain active while the remaining interrupts may be enabled or disabled.

Interrupt signals must be steady state when inputted to the interrupt system and indicate the presence of an interrupt when set to a 0. If a pulse type interrupt is required, the pulse interrupt signal is used to set a bit in the SM register; this SM bit is then wired to the interrupt system. On recognizing this interrupt, the microprogram is able to clear the interrupt condition by clearing the SM bit.

NO. DATE PAGE REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

3.3.1.3.16

K Register

3.3.1.3.17

The K register is an 8-bit counter that can be cleared, incremented, or decremented. It is used to address file 1 in addition to any program usage as a counter. The original value of K can be tested against zero by the microinstruction. The contents of K is selectable as an input to S2 via main CPU tri-state buss.

N Register

The N register is an 8-bit counter which may be cleared, incremented, or decremented. It is used to address file 2, control shifts, control the scale operations, and may be used as an iteration counter which controls microinstruction execution for operations such as multiplication and division. It may also be used as a programmed counter, since the original value of N can be tested against zero by the microinstructions. N is selectable as an input to S2 with RTJ.

3.3.1.3.18

N/K Register

The K and N register may be combined to provide operand addresses outside the current operating page. They are gated through S6 to P/MA for this operation. In this operation the five least significant bits of N provide the upper portion of the twelve bit address. The seven most significant bits of K provide the lower portion of the twelve bit address. The least significant bit of K is used to determine upper or lower. A S/M bit determines whether to use N/K Data or the output of the transform module for this operation

NO. 88786800 DATE 6/13/73 PAGE REV. 01

ZCDD

3.3.1.4

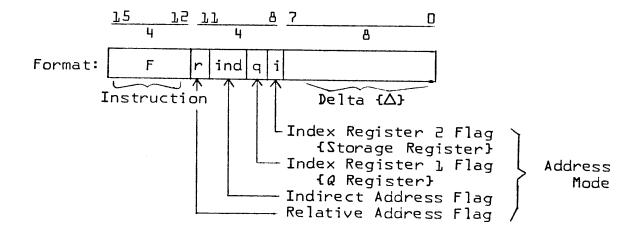

#### Microinstruction Formats

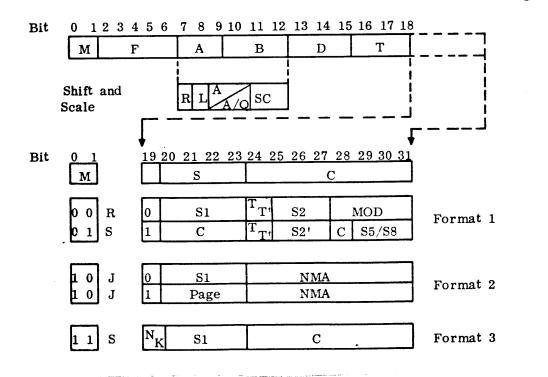

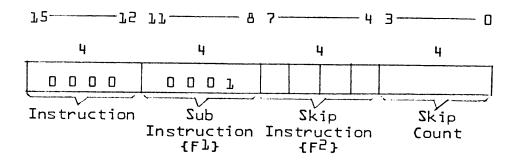

Each micromemory address specifies the location of two microinstructions. Each 32-bit microinstruction is divided into five main sections and is numbered from left to right as bits 0 to 31.

| Bits          | Function                                                                                                     |

|---------------|--------------------------------------------------------------------------------------------------------------|

| 0,1           | Mode (M) field specifies format of S and C field and sequencing mode to obtain next microinstruction pair    |

| 2-15          | ALU control field specifies ALU operation, sources of operands, and destination of result of operation       |

| <b>16-1</b> 8 | Test (T) field specifies method of selecting which microinstruction of next microinstruction pair to execute |

| 19-23         | Special (S) field specifies subformat selection and special operation                                        |

| 24-31         | Constant (C) or suboperation field specifies constants, micromemory addresses, or other codes                |

NO REV DATE PAGE

88786800 01 6/13/73

${\tt ZCDD}$

The total instruction appears as follows:

| 0 | 1 | 2 | •           | <br>15 | 16 | 18 | 19 23 | 24 | 31 |

|---|---|---|-------------|--------|----|----|-------|----|----|

|   | M |   | ALU Control |        |    | T  | S     | С  |    |

The M field specifies one of three addressing modes to be used to obtain the next microinstruction pair from micromemory and also specifies the format to be used in interpreting bits 19 to 31 of the microinstruction as follows:

| <u>M</u> | Addressing Mode | Format for bits 19 to 31 |

|----------|-----------------|--------------------------|

| 00       | Return          | Format 1                 |

| 01       | Sequential      | Format 1                 |

| 10       | Jump            | Format 2                 |

| 11       | Sequential      | Format 3                 |

Figure 5 shows all microinstruction formats. Note that format 1 and format 2 microinstructions have two subformats, which are selected by the value of bit 19.

Figure 5 Microinstruction Formats

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

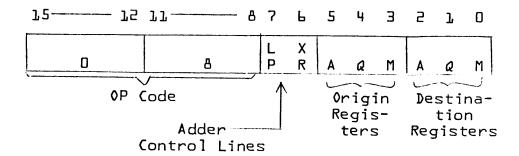

The ALU control fields specify the sources of two operands on which an arithmetic, logical, shift, or scale operation is to be performed and specify the destination of the result of the operation. For arithmetic and logical operations, the ALU control fields consist of the ALU function (F), A source (A), B source (B), and destination (D) fields, shown as follows:

| Bit 2 |   | 6 | 7 | 9 | 10 | 12 | 13 1 | 5 |

|-------|---|---|---|---|----|----|------|---|

|       | F |   | A |   |    | В  | D    |   |

For shift and scale operations, the A and B fields are interpreted as follows:

| Bit | 2 | 6 | 7 | 8 | 9       | 10 | 11 | 12 | 13 | 15 |

|-----|---|---|---|---|---------|----|----|----|----|----|

|     | F |   | R | L | A<br>AG |    | S  | С  |    |    |

The F field specifies shift or scale operation. Bits 7 and 8 specify right or left shifting. Bit 9 specifies whether the A register alone or the A and Q registers together are to be shifted or scaled. Bit 10 is not used, and bits 11 and 12 specify the shift control code. The D field contains a no-operation code for shift and scale operations.

The T field is the conditional branch of the microinstruction and specifies which microinstruction, upper or lower, of the next microinstruction pair to execute. The test can be based on the result of the ALU operation of the current microinstruction or on some other condition.

The codings in the S and C fields depend upon the contents of the M field. The S and C fields are coded in three formats. Format 1 is specified when the M field contains 00 (return mode) or 01 (sequential mode) as follows:

| Bit | 19 | 20 |    | 23 | 24   | 25 | 27 | 28 | 31  |

|-----|----|----|----|----|------|----|----|----|-----|

|     | 0  |    | S1 |    | T T' | S2 |    |    | MOD |

Format 1

| Bit | 19 | 20 |   | 23 | 24      | 25  | 27 | 28 | 29    | 31 |

|-----|----|----|---|----|---------|-----|----|----|-------|----|

|     | 1  |    | C |    | T<br>T' | S2' |    | С  | S5/S8 |    |

NO REV DATE PAGE

88786800 0] 6/13/**73**

ZCDD

The S1 field specifies operations such as main memory read or write operations; alternate codings to be used in the A, B, and D fields; etc. The T/T' bit specifies that the code in the T field is to be interpreted as the normal T code (T/T'=0) or as the alternate T' code (T/T'=1). The subformat select bit, bit 19, determines whether bits 25 through 31 are to be interpreted as S2 codes or as S2' codes. The S2 code can be a constant for driving the bit generator, additional information to control the main memory read or write, or a code to initiate an I/O transfer or other operation. The S2' and S5/S8 codes are associated with transforms.

Format 2 is specified when the M field contains 10 (jump mode), as follows:

| Bit | 19 2 | 20 23 | 24 31 |

|-----|------|-------|-------|

|     | 0    | S1    | NMA   |

|     |      |       |       |

|     | 1    | PAGE  | NMA   |

Format 2

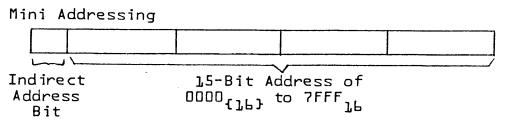

If a jump is specified to a microinstruction pair within the same micromemory page, the subformat select bit is 0; bits 20 to 23 contain a special operation code as in format 1. Bits 24 through 31 contain the micromemory address of the next microinstruction pair. The subformat select bit is 1 when a jump is specified to a different micromemory page; bits 20 through 31 contain the complete micromemory address of the next microinstruction pair.

Format 3 is specified when the M field contains 11 (sequential mode), as follows:

| Bit 19 | 20 | 23 | 24 | 31 |

|--------|----|----|----|----|

| N/K    | S1 |    | C  |    |

This format allows one special operation to be performed as specified by the S1 code and also causes the eight bits of the C field to be transferred to the N register (bit 19 = 1) or to the K register (bit 19 = 0).

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

#### 3.3.1.4.1 M Field {Bits 0 and 1}

The M field defines the major operation taking place in the microinstruction and also specifies the type of sequencing which will be used to obtain the next instruction pair. The operations specified in the M field are listed in Table  $3 \cdot 1 \cdot$

TABLE 3.1. M FIELD OPERATIONS

| M Code | Mnemonic | Operation                                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00     | R        | Select next microinstruction pair in current page from address contained in RTJ register. Use format 1 for special operations.                                                                                                                                                                                                                                                      |

| 01     | s        | Select next microinstruction pair in current page from address contained in MAC (normally next sequential pair, unless suppressed by T field coding). Use format 1 for special operations.                                                                                                                                                                                          |

| 10     | J        | A jump or page jump. Select next microinstruction pair from address specified by bits 24 to 31 of this microinstruction. Address is in current MM page if bit 19 is 0 or from page specified in bits 20 through 23 if bit 19 is 1. Use format 2 for special operations.                                                                                                             |

| 11     | S        | Transfer bits 24 through 31 of this microinstruction to N or K register as specified by bit 19 of this microinstruction. N register is specified if bit 19 is 1, and K register is specified if bit 19 is 0. Select next microinstruction pair in current page from address contained in MAC (normally next sequential microinstruction pair). Use format 3 for special operations. |

#### 3.3.].4.2 F Field (Bits 2 through 6)

The F field specifies the logical or arithmetic operation to be performed by the ALU or the shift or scale operations performed with the A and Q registers. The split adder and the double precision hardware options are described in the following paragraphs.

# ENGINEERING

NO. 88786800 DATE 01 PAGE 6/13/73 REV.

SMALL COMPUTER

DEVELOPMENT DIVISION

The split adder option allows the rain ALU to be split into two independent adders. This split is activated by setting the adder split flag in the SM register. The split blocks the carry between the two portions of the adder. The upper portion of the adder always functions as a 2's complement adder; the lower portion can function as a 1's complement or as a 2's complement adder, depending upon the state of the 1's complement SM register flag (32-bit processor only). In 1's complement mode the carryout of the lower portion is used as the end-around carry bit. In 2's complement mode, both portions of the adder act as independent 2's complement adders. The split adder has no effect on logical operations because no carry is involved in these operations.

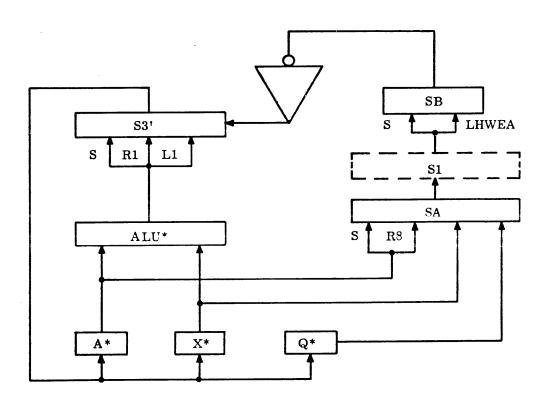

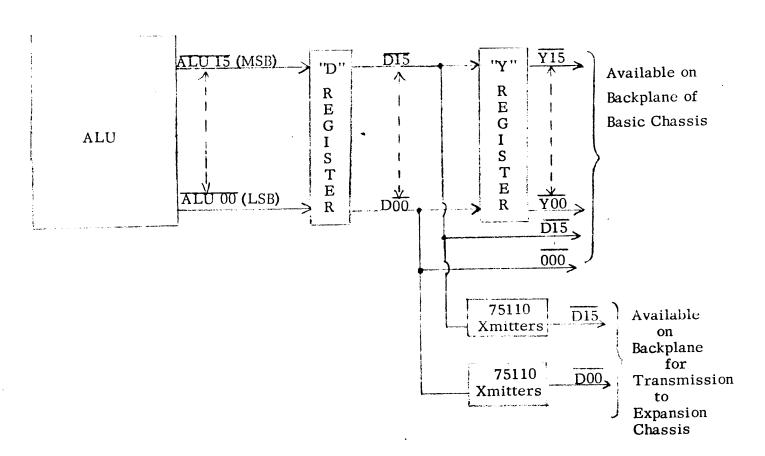

The double precision hardware arithmetic option provides the capability to perform arithmetic on double-length operands. The double precision logic contains three additional registers (A\*, O\*, X\*) and a second ALU (ALU\*) distinct from the main MPP elements. The A\* register is unconditionally inputted to ALU\*. The output of ALU\* can be shifted left and right in a multiply or divide operation, and the output goes to the A\* register. The X\* and O\* registers are loadable only; they cannot be specified as destinations for the results from ALU\*. The O\* register can be shifted during double precision rultiply or divide iterations. The double precision logic, if present, is enabled when the double precision flag is set in the SM register. Figure 6 is a block diagram of the double precision logic.

#### LOGICAL OPERATIONS

The logical operations perform bit-by-bit combinations of the A input and the B input for delivery to the destination. Double precision logical operations cannot be performed on the A\* and X\* registers.

The logical operations are described in Table 3-2,

#### ARITHMETIC OPERATIONS

The arithmetic operators (Table 3-3) operate on either single precision operands (using the main ALU) or double precision operands (if the double precision logic is present and the double precision flag is set in the SM register). Two additional options are provided and coded in the arithmetic function code. The first option provides for a carry input to the adder (indicated by a plus sign in the microinstruction rnemonic). This is used for doing multiple precision arithmetic beyond that provided by the hardware logic. A T field code to check for a carryout of the ALU is provided to determine whether a carry into the ALU should be used on the next arithmetic operation. With the double precision bit set in the SM register, the carryin is entered in the lower bit of the double precision ALU; otherwise, the carryin is entered in the main ALU.

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

Figure L. Double Precision Option Block Diagram

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

TABLE 3-2. LOGICAL OPERATIONS

| F Code | Mnemonic      | A input = 0 0 1 1 B input = 0 1 0 1 |

|--------|---------------|-------------------------------------|

| r Code |               | Bit Result                          |

| 01100  | ZERO          | 0 0 0 0                             |

| 01110  | A•B           | 0 0 0 1                             |

| 01101  | A • - B       | 0 0 1 0                             |

| 01111  | Α             | 0 0 1 1                             |

| 01000  | -A•B          | 0 1 0 0                             |

| 01010  | В             | 0 1 0 1                             |

| 01001  | EOR           | 0 1 1 0                             |

| 01011  | A+B           | 0 1 1 1                             |

| 00100  | -A·-B         | 1 0 0 0                             |

| 00110  | -EOR          | 1 0 0 1                             |

| 00101  | -B            | 1 0 1 0                             |

| 00111  | A+-B          | 1 0 1 1                             |

| 00000  | -A            | 1 1 0 0                             |

| 00010  | -A+B          | 1 1 0 1                             |

| 00001  | <b>-A+-</b> B | 1 1 1 0                             |

| 00011  | ONE           | 1 1 1 1                             |

TABLE 3-3. ARITHMETIC OPERATIONS

| F Code | Mnemonic | Operation                                                |

|--------|----------|----------------------------------------------------------|

| 10100  | SUB      | Subtract B input from A input.                           |

| 11000  | ADD      | Add A and B inputs.                                      |

| 10101  | SUBT     | Subtract with an overflow test.                          |

| 11001  | ADDT     | Add with an overflow test.                               |

| 10110  | SUB-     | Perform A-B-1 input (2's complement only).               |

| 11010  | A DD+    | Perform A + B + 1.                                       |

| 10111  | SUB-T    | Perform SUB-with an overflow test (2's complement only). |

| 11011  | ADD+T    | Perform ADD+ with an overflow test.                      |

|        |          |                                                          |

NO REV DATE PAGE

88786800 D<sub>1</sub> 6/13/73

ZCDD

The second option allows capture of the overflow condition in the SM register (indicated by a T in the instruction mnemonic). If this is indicated, the overflow test is performed by checking the sign of the two inputs to the ALU and by setting a status/mode bit if the result is inconsistent. The status/mode overflow bit is set to 1 when the overflow occurs; it must be set to 0 by a microinstruction which sets that status/mode bit to a 0. Two other optional S/M bits allow checking for binary or decimal arithmetic overflow.

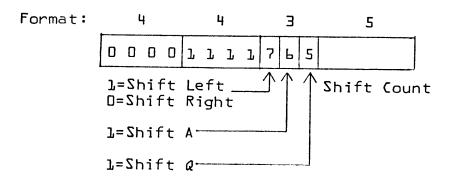

#### SHIFT OPERATIONS

The shift operations in the F field specify a shift of the A register or the AQ register of the main MP organization only; no shift is possible in the double precision registers from this command. The ALU is not used to perform the shift, but will perform some operation based on its decoding of the F field (which should be considered as unknown). The destination will receive this meaningless output unless an NOP is chosen for the destination of the D field.

The type of shift is determined by the coding in bits 7 to 12 of the microinstruction, and the amount of the shift is determined by the number contained in the N register. The operation examines the N register, and, if it is zero, the next microinstruction is executed. The T field codes normally used with a shift are U, L, BIT TEST, and LQL. Other T codes must be used with caution.

If the N register is not zero, a shift of one bit position is taken as specified, N is decremented by one, and the test for zero is repeated as above.

#### The shift conditions are:

- Shift A Shift the A register only.

- Shift AQ Shift the combined A and Q register. The Q register is considered to be the least significant bits of the combined AQ register.

- Shift External (Transform)

- Shift left or right.

- Enter 0 Enter a 0 in the vacated bit position at the end of the register.

- Enter 1 Enter a 1 in the vacated bit position at the end of the register.

- Extend sign Extend the sign (for a right shift only).

- End-around carry Enter the bit coming off the end of the register into the vacated on position at the other end.

All shifts are performed with an F code of 11100. The type of shift is determined by bits 7 through 12 of the microinstruction. The shifts are defined in Table 3-4. If F = 11100 the shifting of A or AQ is inhibited and an external shift is provided for optional use on a transform module.

If F = 11110 the external shift is inhibited and A or AO shifts are enabled.

NO 88786800 REV 01 DATE 6/13/73

SCDD

TABLE 3-4. SHIFT OPERATIONS

| Bit Code |       | 35       | Operation                                                                  |

|----------|-------|----------|----------------------------------------------------------------------------|

| 7 8 9    | 11 12 | Mnemonic | Operation                                                                  |

| 100      | 0 0   | AR0E     | A is right shifted (N) bits, with 0 entered at most significant bit.       |

| 100      | 0 1   | ARSE     | A is right shifted (N) bits, with sign extension.                          |

| 100      | 1 0   | AREA     | A is right shifted (N) bits, with end-around carry.                        |

| 010      | 0 0   | AL0E     | A is left shifted (N) bits, with 0 entered as least significant bit.       |

| 010      | 0 1   | AL1E     | A is left shifted (N) bits, with 1 entered as least significant bit.       |

| 0 1 0    | 1 0   | ALEA     | A is left shifted (N) bits, with end-around carry.                         |

| 101      | 0 0   | AQR0E    | AQ is right shifted (N) bits, with 0 entered as most significant bit in A. |

| 101      | 0 1   | AQRSE    | AQ is right shifted (N) bits, with sign extension.                         |

| 101      | 1 0   | AQREA    | AQ is right shifted (N) bits, with end-around carry.                       |

| 0 1 1    | 0 0   | AQL0E    | AQ is left shifted (N) bits, with 0 entered at least significant bit in Q. |

| 0 1 1    | 1 0   | ÁQLEA    | AQ is left shifted (N) bits, with end-around carry.                        |

NOTE: External shift operations are controlled by same mode lines as the A register.

NO REV DATE

88786800 **0**1 6/13/73

SCDD

#### SCALE OPERATIONS

The scale operations are similar to the shift operations but the stopping of the shift is conditioned on bits 0 and 1 of A not being equal. (The scale point is normally between bits 0 and 1 of the A register. A design option allows the scale point to be specified between different bits in the A register if necessary for efficient floating point emulation.) The maximum number of bits to scale is contained in the N register, and, on completion of the scale, N is decremented by the number of shifts which were necessary to scale the number.

The scale operation is performed as follows:

- 1) Examine N; if it is zero, exit the microinstruction.

- 2) Examine bits 0 and 1 of the A register; if they differ, exit the microinstruction.

- 3) Shift the A or AQ register left by one bit position as specified in the instruction.

- 4) Decrement the N register by one count and go to step 1.

The scale operation is coded the same in bits 7 through 12 of the microinstruction and allows the same left shift options as the shift command. The same comments on exiting the shift and the usable T field codes apply to the scale operation.

All scale operations are performed with an F code of 11111. The type of shift for the scale is determined by bits 7 through 12 of the instruction. The scales are given in Table 3-5.

TABLE 3-5. SCALE OPERATIONS

| Bit   | Code  | Mnemonic   | Operation                                                                    |  |

|-------|-------|------------|------------------------------------------------------------------------------|--|

| 7 8 9 | 11 12 | Willemonic | operation operation                                                          |  |

| 0 1 0 | 0 0   | SL0E       | A is scaled left, with 0 entered as least significant bit.                   |  |

| 0 1 0 | 0 1   | SL1E       | A is scaled left, with 1 entered as least significant bit.                   |  |

| 0 1 0 | 1 0   | SLEA       | A is scaled left, with end-around carry.                                     |  |

| 0 1 1 | 0 0   | SDL0E      | AQ is scaled left, with 0 entered as least significant bit in $\mathbf{Q}$ . |  |

| 0 1 1 | 1 0   | SDLEA      | AQ is scaled left, with end-around carry.                                    |  |

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

#### 3.3.1.4.3 A Field (Bits 7 through 9)

The A field specifies the input to S1 and thus to the A side of the ALU. The eight A codes are expanded by eight A' codes by placing 1010 or 0111 in the S1 field.

The eight A inputs to S1 and to the A side of the ALU are indicated when the S1 field is not 0111 or 1010; the eight A codes specify inputs from the files, the registers, or main memory, according to Table 3-6.

TABLE 3-6. A INPUT OPERATIONS

| A Code | Mnemonic | Operation                                                                                                                                                                                                                                      |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000    | F2       | Use contents of file 2 register as A source input. Current value of N register is used to address register file 2. If value of N is changed in current microinstruction, its initial value is used to reference file register.                 |

| 001    | P        | Use contents of P register as A source.                                                                                                                                                                                                        |

| 010    | I        | Use contents of I register as A source.                                                                                                                                                                                                        |

| 011    | X        | Use contents of X register as A source.                                                                                                                                                                                                        |

| 100    | A        | Use contents of A register as A source.                                                                                                                                                                                                        |

| 101    | F        | Use contents of F register as A source.                                                                                                                                                                                                        |

| 110    | F1       | Use contents of file 1 register or external source as A source. Current value of K register is used to address register file 1. If value of K is changed in current microinstruction, initial value of K is used to reference file register.   |

| 111    | MEM      | Obtain data read from main core memory and use it as A source.  RESTRICTION: A main memory READ command must be given in the preceding microinstruction. This command is restricted to a microinstruction with type A, B or C, execution time. |

NO REV DATE PAGE

88786800 01 6/13/73

ZCDD

The eight A' inputs to S1 and to the A side of the ALU are indicated if the S1 field is 0111 or 1010. The A' codes specify input from the SM registers or mask registers. The A' codes are given in Table 3-7.

TABLE 3-7. A' INPUT OPERATIONS

| A' Code | Mnemonic | Operation                                                                                                                                 |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 000     | SM1      | Use contents of SM register 1 as A source.                                                                                                |