**CYBER 18 COMPUTER SYSTEMS**

# CONTROL DATA® CYBER 18 COMPUTER SYSTEMS

|                                       | REVISION RECORD               |

|---------------------------------------|-------------------------------|

| REVISION                              | DESCRIPTION                   |

| 01                                    | Preliminary edition released. |

| (3/76)                                |                               |

| 02                                    | Manual updated,               |

| (4/76)                                |                               |

| A                                     | Manual updated and released.  |

| (2/77)                                |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

| <del></del>                           |                               |

| <del></del>                           |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

| ·                                     | ·                             |

| · · · · · · · · · · · · · · · · · · · |                               |

|                                       | <del></del>                   |

|                                       | <del></del>                   |

|                                       |                               |

|                                       |                               |

|                                       |                               |

| <del></del>                           |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

|                                       |                               |

| ublication No.<br>96767850            |                               |

© 1976, 1977 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Publications and Graphics Division

4455 Eastgate Mall

La Jolla, California 92037

or use Comment Sheet in the back of this manual.

#### LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE                                                                                                                  | REV                           | PAGE | REV | PAGE | REV | PAGE | REV | PAGE | REV |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------|------|-----|------|-----|------|-----|------|-----|

| Cover Title ii, iii iv v thru viii 1-1 thru 1-3 2-1 thru 2-6 3-1 thru 3-3                                             | <br>A<br>blank<br>A<br>A<br>A |      |     |      |     |      |     |      |     |

| 4-1, 4-2<br>5-1 thru 5-23<br>6-1 thru 6-5<br>7-1 thru 7-12<br>A-1 thru A-8<br>Comment sheet<br>Envelope<br>Back cover | A<br>A<br>A<br>A              |      |     |      |     |      |     |      |     |

|                                                                                                                       |                               |      |     |      |     |      |     |      |     |

|                                                                                                                       |                               |      |     |      |     |      |     |      |     |

|                                                                                                                       |                               |      |     |      |     |      |     |      |     |

|                                                                                                                       |                               |      |     |      |     |      |     |      |     |

|                                                                                                                       |                               |      |     |      | ,   |      |     |      |     |

,مـم سا L.,

### **CONTENTS**

| 1 CYBER 18                               | 1-1        | Basic Instruction Set                       | 5-6  |

|------------------------------------------|------------|---------------------------------------------|------|

|                                          |            | Storage Reference                           | 5-6  |

| 2. CYBER 18 SOFTWARE PRODUCTS            | 2-1        | Register Reference                          | 5-9  |

| Operating Systems                        | 2-1        | Inter-Register                              | 5-9  |

| Mass Storage Operating System (MSOS 5)   | 2-1        | Skip                                        | 5-9  |

| Minimum Operating System (RTOS 3)        | 2-1        | Shift                                       | 5-9  |

|                                          | 2-2<br>2-3 | Enhanced Instructions                       | 5-9  |

| Languages Macro Assembler                | 2-3<br>2-3 | Enhanced Storage Reference                  | 5.10 |

|                                          |            | Field Reference                             | 5-14 |

| Cross Assembler (CLASS)                  | 2-3        | Enhanced Inter-Register                     | 5-14 |

| Micro Assembler                          | 2-3        | Enhanced Skip                               | 5-14 |

| FORTRAN                                  | 2-3        | Decrement and Repeat                        | 5-14 |

| PASCAL                                   | 2-5        | Miscellaneous                               | 5-14 |

| BASIC                                    | 2-6        | Interrupt System                            | 5-17 |

| RPG II                                   | 2-6        | Interrupt Trap Locations                    | 5-17 |

|                                          |            | Mask Register                               | 5-17 |

| 3 APPLICATION SOFTWARE PRODUCTS          | 3-1        | Priority                                    | 5-17 |

| TIMESHARE 3                              | 3-1        | Internal Interrupts                         | 5-17 |

| Manufacturing Industry Accounting System | 3-1        | Operation                                   | 5-17 |

| Interactive Terminal-Oriented System     | 3-2        | Program Protect                             | 5-19 |

| Executive                                | 3-2        | Program Protect Violations                  | 5-19 |

| Terminal Handler                         | 3-2        | Storage Parity Errors Related to            | 0 10 |

| File/Data Manager                        | 3-2        | Program Protection                          | 5-19 |

| Text Editor                              | 3-2        | Set/Clear Program Protect Bit               | 5-19 |

| Terminal File Utilities                  | 3-2<br>3-3 | Programming Requirements                    | 5-19 |

| rermmai rue otilities                    | 3-3        | <u> </u>                                    | 5-19 |

| A CYPED 10 AT DARGII MEDMINAT            | 4 1        | Peripheral Equipment Protection             | 5-20 |

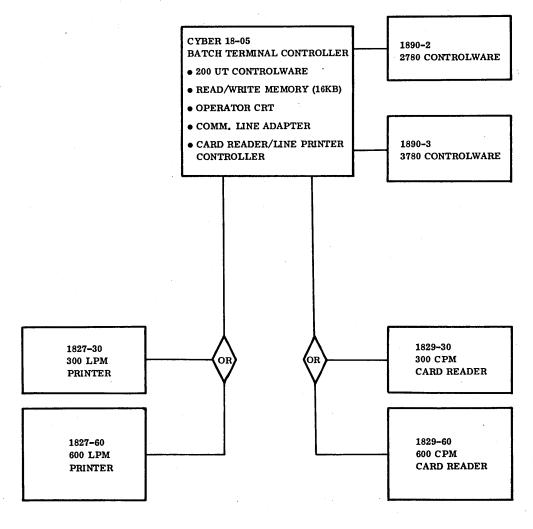

| 4 CYBER 18-05 BATCH TERMINAL             | 4-1        | Input/Output<br>Auto-Data Transfer          | 5-2  |

| Model Description                        | 4-1        | nuto buta iransior                          | 0 2. |

| CYBER 18-05 Batch Terminal Controller    | 4-1        | 6 CYBER 18-20, 18-30 TIMESHARE              |      |

| Batch Terminal Controlware               | 4-1        | COMPUTER CHARACTERISTICS                    | 6-3  |

| CDC 200 User Terminal Emulation          | 4-1        |                                             |      |

| IBM 2780 Emulation                       | 4-2        | Model Descriptions                          | 5-1  |

| IBM 3780 Emulation                       | 4-2        | CYBER 18-20 Processor                       | 6-3  |

|                                          |            | 1870-1 512 Instruction Micro Memory         | 6-2  |

| 5 CYBER 18-10M COMPUTER                  |            | 1870-2 2-48 Instruction Micro Memory        | 6-3  |

| CHARACTERISTICS                          | 5-1        | 1882-16 MOS Main Memory Storage             | 6-   |

| W. J. I. D                               | - 1        | 1882-32 MOS Main Memory Storage             | 6-3  |

| Model Descriptions                       | 5-1        | 1874-1 ECC MOS Array, 192K Bytes            | 6-3  |

| CYBER 18-10M Processor                   | 5-1        | Main Memory                                 | 6-   |

| 1870-1 512 Instruction Micro Memory      | 5-1        | Central Processor                           | 6-3  |

| 1870-2 2048 Instruction Micro Memory     | 5-1        | Macro Instruction Set                       | 6-   |

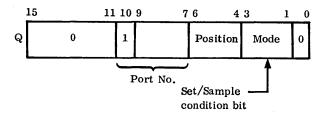

| 1882-16 MOS Main Memory Storage          | 5-1        | Micro Instruction Formats                   | 6-4  |

| 1882-32 MOS Main Memory Storage          | 5-1        |                                             |      |

| Central Processor                        | 5-1        | 7 STANDARD PERIPHERALS                      | 7-   |

| Arithmetic/Logical Unit Data Transfer    | 5-3        |                                             |      |

| Transforms                               | 5-5        | 1811-1 Console Display                      | 7-:  |

| I/O-TTY Module                           | 5-5        | 1811-2 Operators Console                    | 7-   |

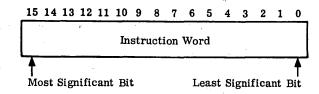

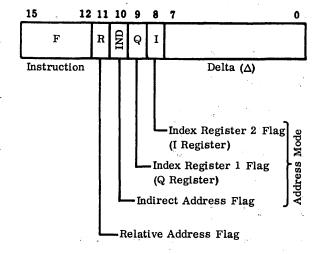

| CYBER 18-10M Instruction Description     | 5-6        | 1828-1 Card Reader/Line Printer Controller  | 7-   |

| Instruction Format                       | 5-6        | 1828-2 Card Reader/Line Printer Controller/ |      |

|                                          |            | Communication Line Adapter                  | 7-   |

96767850 A

| 182        | 9-30 Card Reader                                 | 7-2        | 1860-1 Magnetic Tape Subsystem                     | 7-6        |

|------------|--------------------------------------------------|------------|----------------------------------------------------|------------|

|            | 9-60 Card Reader                                 | 7-2        | 1860-72 Magnetic Tape Transport                    | 7-6        |

|            | 7-2 Impact Printer                               | 7-2        | 1860-2 Dual Magnetic Tape Subsystem                | 7-6        |

|            | 7-30/31 Line Printer                             | 7-3        | 1860-3 Magnetic Tape Subsystem                     | 7-6        |

|            | 7-60 Line Printer                                | 7-3        | 1860-92 Magnetic Tape Transport                    | 7-6        |

|            | 3-4 Cartridge Disk Controller                    | 7-3        | 1860-4 Dual Magnetic Tape Subsystem                | 7-7        |

|            | 6-12 Cartridge Disk Drive                        | 7-4        | 1860-5 Magnetic Tape Subsystem                     | 7-7        |

| 1860       | 6-14 Cartridge Disk Drive                        | 7-4        | 1860-95 Magnetic Tape Transport                    | 7-7        |

|            | 3-1 Storage Module Drive Interface               | 7-4        | 1860-6 Dual Magnetic Tape Subsystem                | 7-8        |

| 1833       | 3-2 Storage Module Drive Interface —             |            | 1843-1 Communication Line Adapter                  | 7-8        |

| I          | Oual CPU                                         | 7-4        | 1843-2 Eight-Channel Communication Line            |            |

| 1833       | 3-3 Storage Module Drive Control Unit            | 7-4        | Adapter                                            | 7-8        |

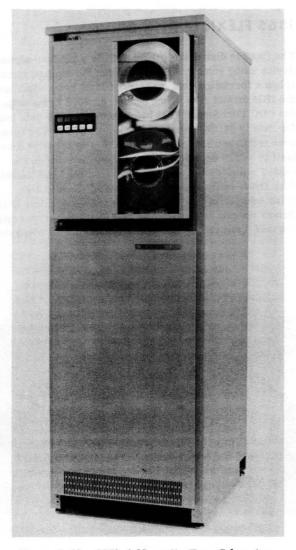

| 186'       | 7-10 Storage Module Drive                        | 7-4        | 1850-1 15 <b>0</b> 0 Series Equipment Adapter      | 7-8        |

| 186        | 7-20 Storage Module Drive                        | 7-5        | 1862-1 Paper Tape Read/Punch Controller            | 7-8        |

| 1833       | 3-5 Flexible Disk Drive Controller               | 7-5        | CYBER 18 Configurator                              | 7-9        |

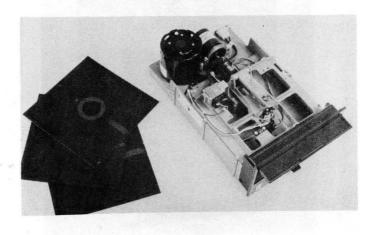

| 186        | 5 Flexible Disk Drive                            | 7-5        |                                                    |            |

|            |                                                  |            | •                                                  |            |

|            |                                                  |            | •                                                  |            |

|            |                                                  |            | •                                                  |            |

|            |                                                  |            |                                                    |            |

|            |                                                  | APPE       | NDIX                                               |            |

|            |                                                  |            |                                                    |            |

| A          | MACRO INSTRUCTION EXECUTION TIMES                | A-1        |                                                    |            |

|            |                                                  |            | •                                                  |            |

|            |                                                  |            | ·                                                  |            |

|            |                                                  |            |                                                    |            |

|            |                                                  |            |                                                    |            |

|            |                                                  |            |                                                    |            |

|            |                                                  | FIG        | URES                                               |            |

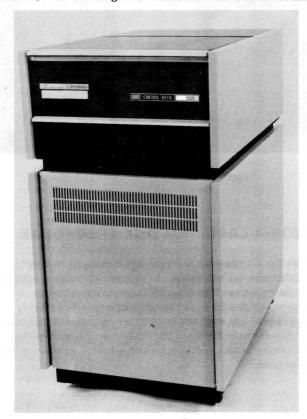

| 1-1        | CYBER 18 Series Product Family                   | 1-1        | 7 A 1007 7 Impact Drinton                          | 7-3        |

| 2-1        | CYBER 18 Mass Storage Operating                  |            | 7-4 1827-7 Impact Printer 7-5 1827-30 Line Printer | 7-3<br>7-3 |

| 2-1        | System (MSOS 5)                                  | 2-1        |                                                    | 7-3<br>7-3 |

| 2-2        | CYBER 18 Mass Storage FORTRAN                    | 2-1        | 7-6 1827-60 Line Printer                           |            |

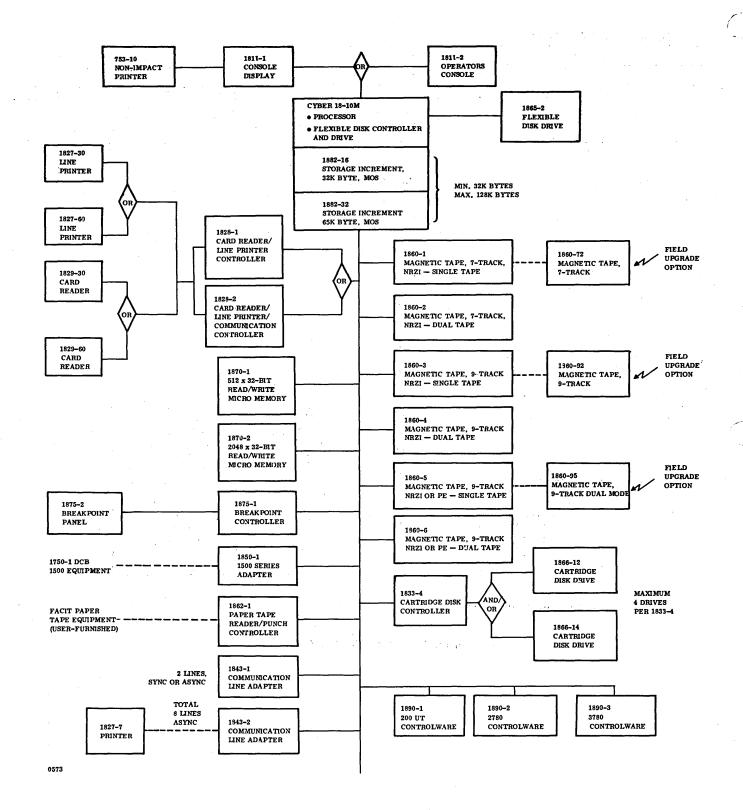

| 2-2<br>4-1 | Typical CYBER 18-05 Configuration                | 4-2        | 7-7 1866 Cartridge Disk Drive                      | 7-4        |

| 5-1        |                                                  | . 4-2      | 7-8 1867 Storage Module Drive                      | 7-5        |

| 9-1        | Detailed Block Diagram of CYBER 18-10M Processor | 5-2        | 7-9 1865 Flexible Disk Drive                       | 7-5        |

| E 0        |                                                  | 5-2<br>5-3 | 7-10 1860-1 Magnetic Tape Subsystem                | 7-6        |

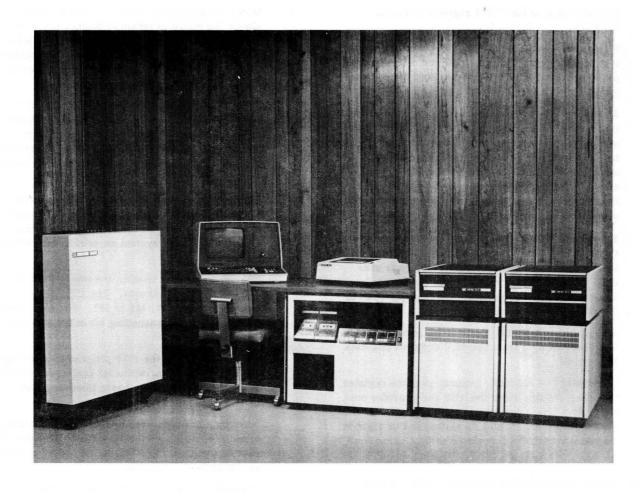

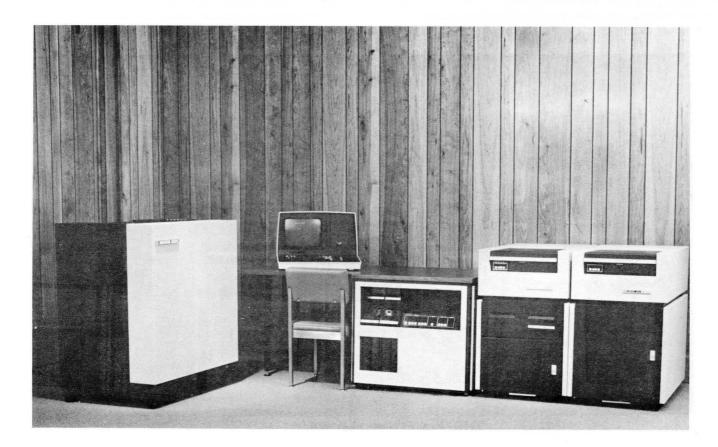

| 5-2        | Typical CYBER 18-10M Configuration               |            | 7-11 1860-4 Dual Magnetic Tape Subsystem           | 7-7        |

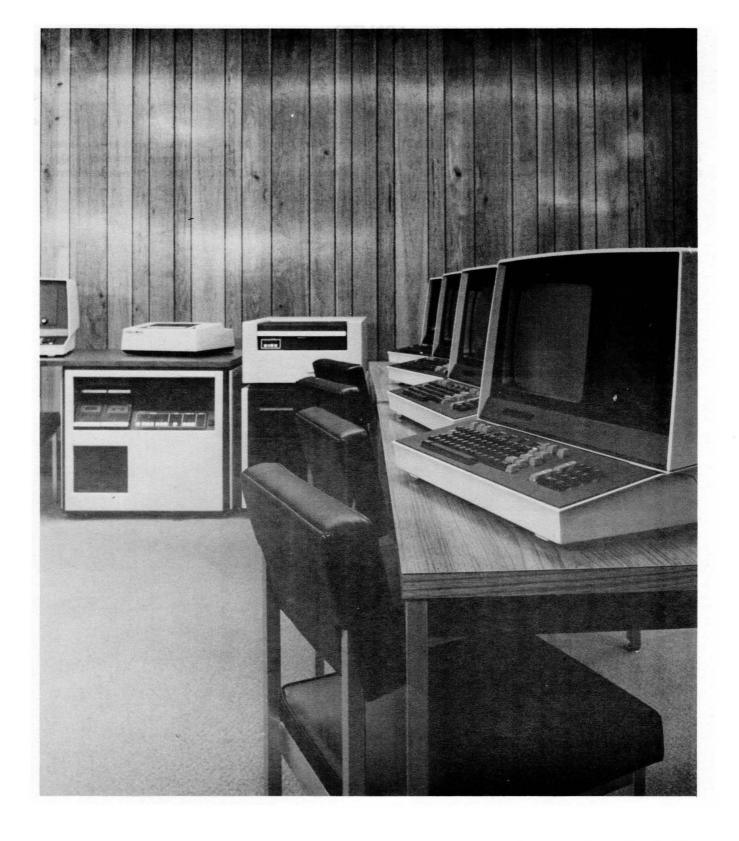

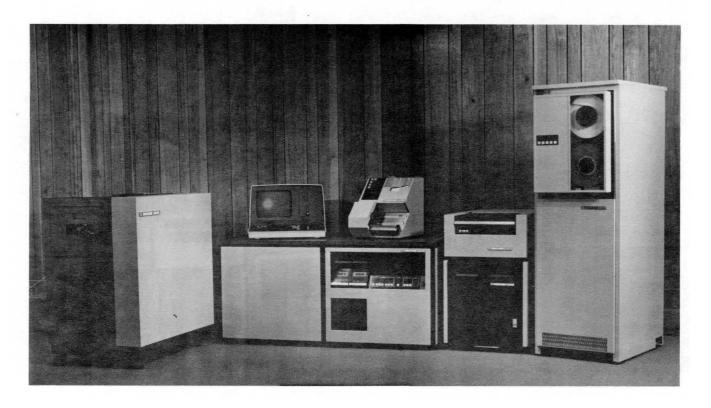

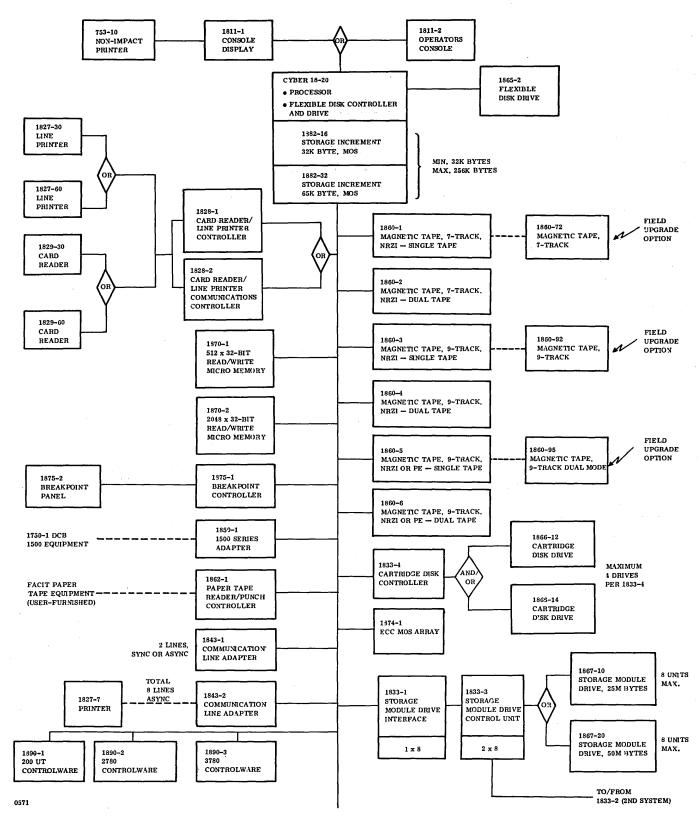

| 6-1        | Typical CYBER 18-20 Configuration                | 6-1        | 7-12 1860-5 Magnetic Tape Subsystem                | 7-7        |

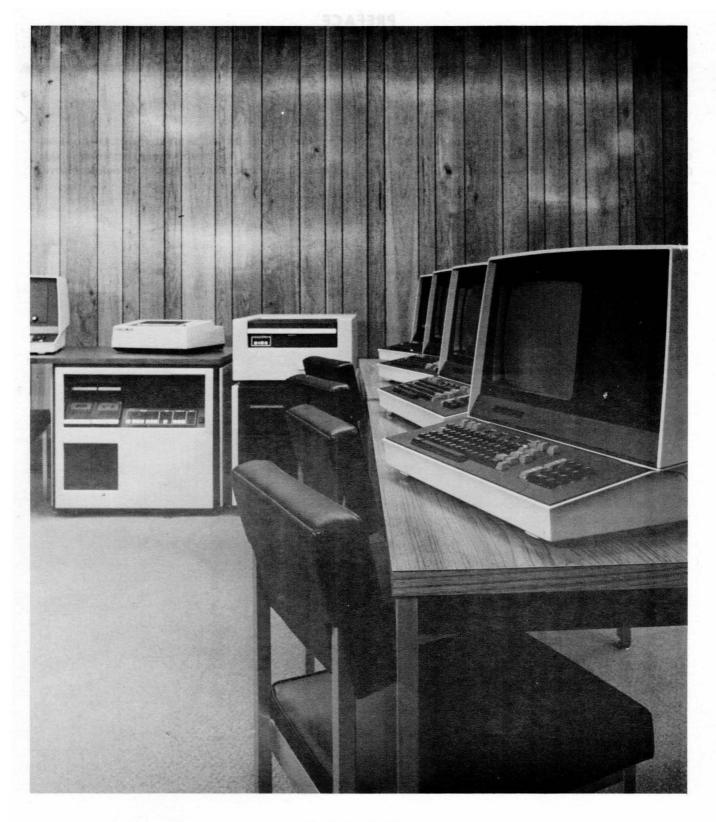

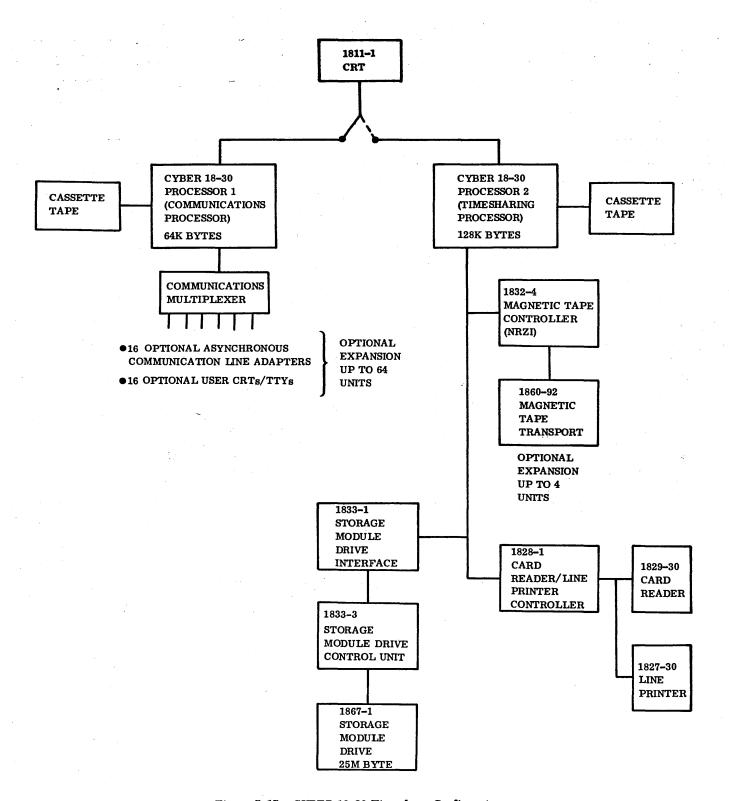

| 6-2        | Typical CYBER 18-30 Timeshare                    | c o        | 7-13 1860-6 Dual Magnetic Tape Subsystem           | 7-8        |

| <b>.</b>   | Configuration                                    | 6-2        | 7-14 CYBER 18-05 Configurator                      | 7-9        |

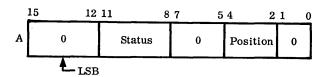

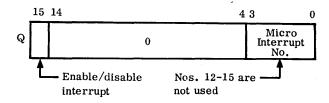

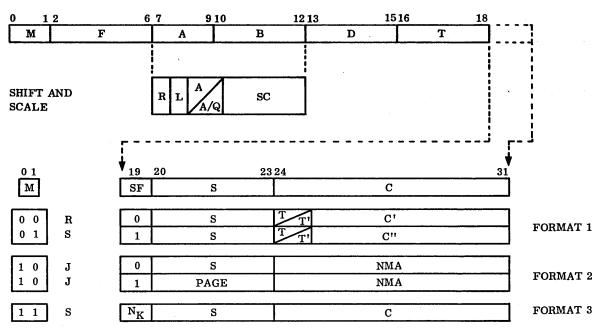

| 6-3        | Micro Instruction Formats                        | 6-4        | 7-15 CYBER 18-10M Configurator                     | 7-10       |

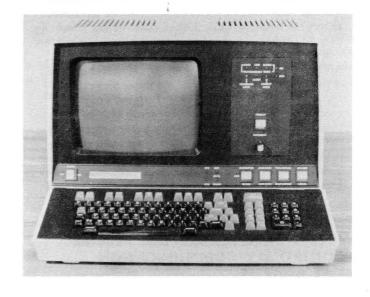

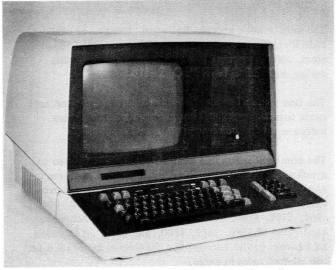

| 7-1        |                                                  | 7-1        | 7-16 CYBER 18-20 Configurator                      | 7-11       |

| 7-2        | 1811-2 Operators Console                         | 7-1        | 7-17 CYBER 18-30 Timeshare Configurator            | 7-12       |

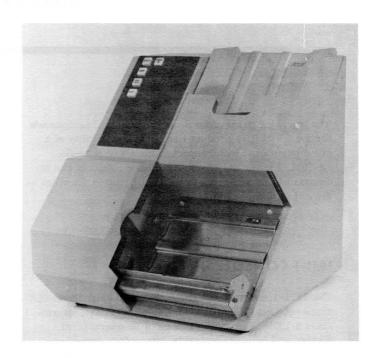

| 7-3        | 1829–30 Card Reader                              | 7-2        |                                                    |            |

|            |                                                  |            |                                                    |            |

|            |                                                  |            |                                                    |            |

|            |                                                  | TAI        |                                                    |            |

|            |                                                  | IAI        | BLES                                               |            |

|            | CVDED 10 Declarat Line Coursel                   |            |                                                    |            |

| 1-1        | CYBER 18 Product Line General                    |            | 5-3 Enhanced Storage Reference Instruction         | n          |

|            | Characteristics                                  | 1-2        | Addresses                                          | 5-11       |

| 5-1        | Mask Register/Interrupt Addresses                | 5-5        | 5-4 Interrupt State Definitions                    | 5-17       |

| 5-2        | Storage Reference Instruction Addressing         | 5-8        | <del>-</del>                                       |            |

vi

#### **PREFACE**

This manual provides general information on the CDC  $^{\circledR}$  CYBER 18 family of small computer systems. More detailed information on all aspects of the CYBER 18

product family (that is, hardware, software, maintenance, education, and customer support) are available through your local Control Data sales representative.

96767850 A

CYBER 18 SYSTEM

The CYBER 18 is a series of general-purpose microprogrammable processors designed for application to a broad range of requirements. One basic hardware design, made up of modular elements, serves a variety of functions, permitting a high degree of standardization.

The operation of the CYBER 18 is controlled by a "micro" program in semiconductor memory, referred to as micro memory. The micro program reads macro instructions from main memory and decodes them for execution in the micro processor. The semiconductor memory, which is several times faster than core memory, executes several micro instructions during a single main memory cycle. In the CYBER 18, special micro-programming techniques are used to emulate an enhanced CDC 1700 system for lower cost, smaller size, and equal or better speed.

Micro programming provides a number of long-range benefits. In contrast to the conventional computer, whose control is an irregular assembly of specially designed logic functions, the micro-programmed machine embeds the control logic in a high-speed read-only memory, reducing the amount of irregular logic in a processor and allowing greater use of MSI/LSI circuitry. This approach allows high-volume production of nearly identical processors that can be tuned to a specific application by including a selected instruction set in the micro memory, thus specifying a different virtual machine. The micro-programming technology provides the flexibility to offer new architectures for general-purpose computers with emulation capabilities and for controllers where emulation is not an important factor.

Growth is a most important feature of the CYBER 18. Growth is available via the micro-code expansion capability of the micro processor. New functions can be added as applications require, or operating system functions can be included as part of the micro sequence to improve overall system performance. This growth potential is available without sacrifice of hardware commonality, so a common logistic base is maintained.

Figure 1-1 presents an overall view of the CYBER 18 hardware and software products.

# 18-30 18-20 18-10M

#### **CHARACTERISTICS**

- 18-30 DUAL PROCESSOR

- 64K TO 512K BYTES, 18-BIT MOS

- FULL PERIPHERAL CAPABILITY

- ENHANCED 1700 MSOS SOFTWARE

- TYPICAL APPLICATION: EDUCATIONAL TIMESHARE

- 18-20 CPU

- 32K TO 256K BYTES, 18-BIT MOS

- FULL PERIPHERAL CAPABILITY

- ENHANCED 1700 MSOS SOFTWARE

- TYPICAL APPLICATION: ACCOUNTING AND MANAGEMENT CONTROL

- 18-10M CPU

- 32K TO 128K BYTES, 18-BIT MOS

- FULL PERIPHERAL CAPABILITY

- 1700 MSOS/RTOS SOFTWARE

- TYPICAL APPLICATIONS: INDUSTRIAL CONTROL SYSTEM ENTRY BUSINESS SYSTEM

- 18-05 CPU

- 16K BYTES, 18-BIT CORE

- LIMITED PERIPHERALS

- 200 UT, 2780, AND 3780 CONTROLWARE

- TYPICAL APPLICATION: BATCH SYSTEM

Figure 1-1. CYBER 18 Series Product Family

#### TABLE 1-1. CYBER 18 PRODUCT LINE GENERAL CHARACTERISTICS

| Basic | Configuration |

|-------|---------------|

Processor

Type

Organization

Word length

Micro-instruction word

Micro-memory type

Micro-memory size

Micro-memory access time

Arithmetic

Macro Memory

Requirement

Туре

Memory speed

Input/Output (I/O)

Interfaces

Mechanical

Construction

Dimensions

Weight

Register oriented or file oriented.

16 bits

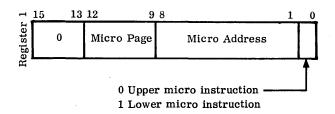

32-bit format; two micro instructions per micro-memory

General-purpose, micro-programmable digital processor

Semiconductor read/write memory (RAM) and/or read-

only memory (ROM)

512 words in 64-bit increments (on transform); maximum

of 4,096 additional words available.

70 nanoseconds

Binary with dynamic selection of ones or twos complement

Up to four parallel unrelated operations are possible in

one micro instruction

Variable, according to application

Core memory: Available in 16K byte stacks, with a maximum of

32K bytes (CYBER 18-05)

MOS memory: Available in 32K or 64K byte stacks, with a max-

imum of 128K bytes (CYBER 18-10M), 256K bytes (CYBER 18-20), or 512K bytes (CYBER 18-30)

Parity and protect bits are available in the standard stack.

750 nanoseconds average cycle

Display terminal (RS232-C compatible)

RETMA 19-inch, rack mountable

Logic Chassis:

Height - 18.5 inches (47 cm)

Width -17.5 inches (44.5 cm)

Depth - 16.0 inches (40.64 cm)

Power Supply Chassis:

Height - 8.75 inches (22.25 cm)

Width - 17.5 inches (44.5 cm)

Depth -16.0 inches (40.64 cm)

Logic Chassis: 40 pounds (approximately) (18 kg) Power Supply: 50 pounds (approximately) (45 kg)

TABLE 1-1. CYBER 18 PRODUCT LINE GENERAL CHARACTERISTICS (Continued)

|                        | Basic Configuration (Continued) |

|------------------------|---------------------------------|

| Mechanical (Continued) |                                 |

| Input power            | 115 volts, 50/60 Hz             |

| Miscellaneous Features |                                 |

|                        | Real-time clock                 |

|                        | Auto-data transfer              |

د, يا L., 1 () ريب

The hardware of the CYBER 18 product set is complemented with an extensive set of software products, comprising operating systems (including program debugging and development aids), micro and macro assemblers, application-oriented software, and FORTRAN, BASIC, RPG II, and PASCAL compilers.

#### OPERATING SYSTEMS

#### MASS STORAGE OPERATING SYSTEM (MSOS 5)

This operating system is the most recent in the development of a sequence of mass-storage-based operating systems for the 1700, 1714, 1774, and 1784 computers. It takes advantage of the enhanced instructions, additional registers, and firmware capabilities of the CYBER 18 Series of computers. MSOS 5 is designed for use on the CYBER 18-10M and 18-20, having random-access mass memory.

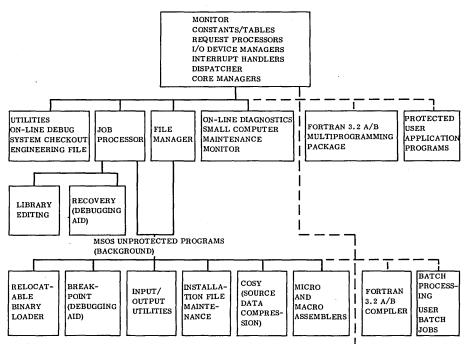

The component parts of MSOS 5 are shown in figure 2-1.

MSOS 5 is a multiprogramming system designed to support a variety of applications requiring dedicated system utilization, batch processing, and program checkout features in a real-time environment.

MSOS 5 regulates all multiprogramming on the basis of the priority level assigned to a particular operation, whether the operation is program execution or input/output. The system queues requests for I/O data transmission and program execution by priority level, with no restriction on the number of requests that may be queued at a given time. The program task with the highest priority level is selected for execution. It remains in execution until completed, unless a higher priority level interrupt is scheduled. The lower priority level task is then suspended until the higher priority interrupt task is completed.

#### MSOS PROTECTED PROGRAMS (FOREGROUND)

Figure 2-1. CYBER 18 Mass Storage Operating System (MSOS 5)

On interrupt, all eight registers of the CPU may be stored by a single command, making possible a very rapid change in the program environment as a result of interrupt.

Sixteen hardware interrupts are utilized to maximize input/output efficiency and to allow concurrent input/output and computation.

The program protect feature of the hardware segregates central memory into two functional entities — protected memory and unprotected memory.

- Protected memory (the foreground) is reserved for executing all parts of the operating monitor and the user's on-line high priority applications programs.

- Unprotected memory (the background) is used for execution of batch job processing and program checkout at low priority levels. MSOS 5 has the capability to swap (move) the contents of unprotected memory to mass storage and to make the area protected memory for use by foreground programs.

MSOS 5 is extremely modular in design and provides the user considerable flexibility to perform on-line system modification and update.

The MSOS 5 system features the following main capabilities:

- The monitor is the real-time executive for MSOS 5. It serves as the interface between the system programs and the peripheral hardware via input/output drivers. It is highly modular and may be parameterized for a large variety of hardware and software configurations. It contains request processors to allow for input/output, program scheduling, memory allocation, and background operation. MSOS 5 provides for the execution of instructions in 128K bytes of contiguous memory, with the ability to access data in up to 512K bytes of memory.

- The job processor is responsible for monitoring background programs running in unprotected memory. Interface is provided for batch stream unattended jobs or for interactive operatorcontrolled jobs. The job processor controls the FORTRAN compiler, the macro assember, and numerous background utility functions.

- The file manager is a general-purpose file management package. It creates and maintains both sequential and indexed files, and offers sequential, indexed, and direct methods of record retrieval, as well as variations of these. The file manager may be used by protected and unprotected programs and is FORTRAN-callable.

- The on-line diagnostics, in an on-line, real-time mode, have the capability of running peripheral hardware diagnostics, which facilitates problem detection and preventive maintenance.

The minimum hardware CYBER 18-20 requirements for MSOS 5 are:

- Computer with 32K bytes main memory

- Console device (teletypewriter, CRT)

- Input device (paper tape, cards, magnetic tape)

- Output device (paper tape, cards, magnetic tape)

- 1,024,000 bytes mass storage memory

#### MINIMUM OPERATING SYSTEM (RTOS 3)

The minimum operating system for the CYBER 18-10M is the Real-Time Operating System Version 3 (RTOS 3). It provides executive software and appropriate development tools in a minimum of main memory, without dependence on random-access mass memory.

RTOS 3 includes a monitor that is a compatible subset of MSOS 5. The monitor requires less than 3000 bytes of main memory, exclusive of peripheral-device drivers and optional features. Up to 16 program priority levels are provided, and input/output requests are also processed on a priority basis. The monitor is itself reentrant and minimizes the time for which interrupts are inhibited so as to provide very fast interrupt response times. It contains a request processor to handle the following standard requests:

READ WRITE FREAD FWRITE SCHDLE INDIR EXIT Optional request processors are available to process requests for:

TIMER

MOTION

SPACE

RELEASE

CORE

STATUS

EBCDIC

Other optional features include a protect processor for use while debugging user-written programs, a core allocator, an alternate device handler and a diagnostic timer.

All MSOS 5 drivers are compatible with RTOS 3.

An RTOS 3 system with a minimum of 16K bytes of main memory supports the Assembler, which is compatible with the MSOS assembler (except that macros may not be used). Previously compiled FORTRAN programs may be run under RTOS 3; however, FORTRAN programs may not be compiled under RTOS 3.

The minimum hardware requirements for RTOS 3 are:

- CYBER 18-10M with 16K bytes of main memory

- Console device (conversational display terminal)

- Input device (card reader, magnetic tape)

- Output device (magnetic tape) optional

#### LANGUAGES

#### MACRO ASSEMBLER

The macro assembler for the CYBER 18 Series provides a comprehensive instruction set that makes full use of the CPU capabilities and includes the ability to define, execute, and maintain a library of macro commands. A minimum system for execution of the macro assembler (under RTOS 3) requires 16K bytes of main memory.

#### CROSS ASSEMBLER (CLASS)

The CLASS cross assembler is designed for use on CYBER 170/70/6000/7000 computers. It duplicates all

the functions of the CYBER 18 macro assembler, producing listing output and relocatable binary output for input by the CYBER 18 relocatable binary loader.

#### MICRO ASSEMBLER

The micro assembler provides the ability for the user to develop his own micro program using appropriate alphabetic and numeric designations of operations to be performed. The micro assembler provides for cross micro assembly on large CYBER Series computer (CYBER 170/70/6000/7000). The micro assembler output is in binary relocatable format, compatible with the loader of the MSOS 5 or RTOS 3 operating system.

#### **FORTRAN**

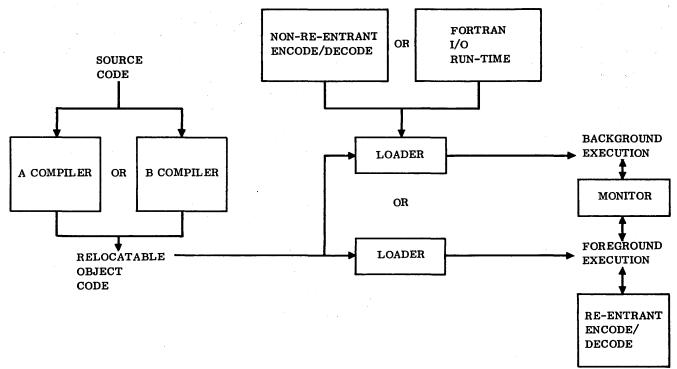

There are two FORTRAN compilers for the CYBER 18 Series. They provide the same run-time capability but differ in compilation speed and main memory requirements. The essential components and modes of operation are shown in figure 2-2.

The language is a subset of ANSI FORTRAN, so, most ANSI FORTRAN programs can be compiled with few changes; basic FORTRAN programs are immediately compiled.

As a product-set member of the CYBER 18 MSOS 5, Mass Storage FORTRAN offers a variety of compiletime options (such as run-anywhere code) and run-time packages.

CYBER 18 Mass Storage FORTRAN is a high-level language and, as such, is concise and provides data structuring capabilities and I/O independence. Increased program modularity and source code clarity also results.

The wide range of FORTRAN system configurations allows optimum usage of available storage resources for compilation and foreground/background execution.

Five basic elements comprise 1700 Mass Storage FOR-TRAN Version 3 — the A and B variations of the compiler and three run-time packages: re-entrant ENCODE/DECODE, non-re-entrant ENCODE/DECODE, and FOR-TRAN I/O.

The A variant compiler, having a larger number of overlays than the B variant, requires more compilation

Figure 2-2. CYBER 18 Mass Storage FORTRAN

time but less core memory (16K vs. 32K bytes). The source format for both variants is the same, while the object code produced by the two variants is nearly identical.

The re-entrant ENCODE/DECODE run-time package runs in the foreground (protected core) and is the FORTRAN multiprogramming interface. It allows FORTRAN routines to execute at multiple levels without interference, and provides a greatly enhanced interface capability to the MSOS monitor.

Although the formatted I/O is nonstandard, all I/O capabilities are provided through the monitor and ENCODE/DECODE package calls.

Given a list of variables and a FORMAT statement, ENCODE and DECODE translate the variables between internal hexadecimal format and ASCII. The other formatting routines do not use FORMAT statements, but translate either integer or floating-point variables. These formatting routines are as follows:

- HEXASC Hexadecimal to ASCII

- HEXDEC Hexadecimal to decimal ASCII

- ASCII ASCII to hexadecimal

- DECHEX Decimal ASCII to hexadecimal

- AFORM Packed ASCII to unpacked ASCII (leftjustified blank-filled)

- RFORM Packed ASCII to individual ASCII characters (right justified, zero filled)

- FLOATG Floating-point variable to ASCII

Monitor requests that are provided include Read/Write (extensive I/O capabilities), Scheduler/Timer (causes execution of another routine, optionally, after a specified time interval). Dispatcher (discontinue execution without terminating), and Release (return core allocated for execution).

10K bytes are required for the foreground ENCODE/DE-CODE package. If double-precision arithmetic is used, an additional 5K bytes are required.

Foreground programs can be checked out in the back-ground (unprotected core) via the (identical) interface provided by the non-re-entrant ENCODE/DECODE package, without interfering with the protected programs, including the monitor.

The FORTRAN I/O run-time package, which also runs in the background, provides standard FORTRAN I/O capabilities more extensive than those of the ENCODE/DE-CODE packages.

The efficiency of the produced object code is mainly due to the compiler's extensive optimizing features, which include:

- Common arithmetic subexpressions, including subscripts, are recognized within and between expressions and are computed only once

- Index registers are optimally assigned

- One-word relative addressing is used wherever possible

- Relative addressing is maximized by appropriate storage allocation: some constants, for instance, are duplicated, and some arrays are inserted between code segments

- Simple FORTRAN functions such as AND and IABS are provided in-line

- IF statements are extensively analyzed, such as a transfer made to the next statement or to a GO TO

- Expressions in logical IFs are analyzed for the method of least computation

- Arithmetic expressions are analyzed to minimize code production and execution time

- Division by a real constant generates code for multiplication by the constant's reciprocal

- Integer multiplication or division by a (constant) power of 2 is accomplished by shifting

The following standard statements are recognizable by the FORTRAN compiler:

> ASSIGN **FUNCTION** BACKSPACE GO TO INTEGER BLOCK DATA IF CALL COMMON OPEN CONTINUE PAUSE DIMENSION **PROGRAM** DO READ DOUBLE REAL **PRECISION** RETURN REWIND **END** ENDFILE SIGN SUBROUTINE **EQUIVALENCE** EXTERNAL STOP WRITE FORMAT

Extensions to the ANSI standard are as follows:

- ASSEM Allows inclusion of assembler statements in FORTRAN source code

- BYTE Assigns a name to a bit field within an integer variable or array

- DATA Enhanced to allow use of implied DO-loop to initialize arrays

- RELATIVE Specifies externals to be linked via relative addressing

- SIGNED BYTE Identical to BYTE but the highorder bit of the field is interpreted as a sign bit

The minimum main memory requirement for execution of the compiler (A or B version) on a CYBER 18-10M or a CYBER 18-20 is 64K bytes.

#### **PASCAL**

PASCAL is a compiler patterned after ALGOL 60. It is available as a cross compiler executing on large CYBER computers (170/70/6000/7000), producing relocatable binary output for loading and execution by a CYBER 18 machine.

PASCAL is a high-level, algorithmic type language retaining the attractive features of ALGOL 60. Thus, the grammar of PASCAL is essentially context-free. Its syntax is unambiguous and simple to define, properties that are greatly appreciated by programmers. The block-oriented structure of ALGOL 60, which is particularly adaptable to the use of structured programming techniques, has also been preserved.

The basic constituents of a PASCAL program are statements and declarations or definitions. Statements indicate the various actions that are to be carried out by a program, and declarations/definitions describe the meaning attached to the various identifiers used in a program.

PASCAL provides some noteworthy extensions to the capabilities of ALGOL 60. Within the domain of statement constructs, PASCAL supports a broad variety of structured statements. Thus, repetitive or conditional actions may be coded in a concise and natural manner. More significantly, the ALGOL 60 deficit in the area of structured data has been remedied by the introduction of a set of data structuring techniques. Another feature of PASCAL is the provision of pointer-type variables,

along with the ability to dynamically and explicitly allocate storage. These features extend the range of applicability of PASCAL, as compared with that of its more traditional ancestor.

PASCAL programs compiled on a CYBER 170/70/6000/7000 class of machine may be executed in a CYBER 18-10 under RTOS 3 with a minimum memory of 16K bytes.

#### BASIC

The BASIC compiler provided as a component of the CYBER 18 software product set meets the requirements of the proposed ANSI standard for minimal BASIC (ANSI-XJ32), and provides the following additional capabilities:

- Additional string manipulation functions

- Matrix operations

- Input/output formatting

- Binary and ASCII files

- Sequential and random (indexed) file accessing

The BASIC compiler is executed interactively under TIMESHARE 3 on a CYBER 18-30.

#### RPG II

The Report Program Generator II (RPG II) compiler provided as a member of the CYBER 18 software product set is closely compatible with IBM System 3/RPG II at the source language level. Differences from the System 3/RPG II primarily reflect differences in peripheral characteristics; the multifunction card reader, the dual tractor printer, bisync communication, card reader stacker selection, and inquiry mode are not supported by CYBER 18 RPG II.

RPG II provides a simple language by which a user can:

- Easily describe the formats, sources of input data, and destinations of output data

- Execute simple procedural programs with both conditional and unconditional statements

- Describe the formats and sources of data in an external file system

CYBER 18 RPG II requires a CYBER 18-10M or 18-20 for compilation under MSOS 5.

#### TIMESHARE 3

The TIMESHARE 3 system is designed to provide interactive computer capability for up to 64 concurrent users, together with communication with a remote large-scale CYBER system (70/170/6000/7000). TIMESHARE 3 requires the dual processor of the CYBER 18-30, one processor handling user programs, the other providing communication with a remote host machine and I/O for local peripherals. TIMESHARE 3 operates under MSOS 5.

The capabilities and characteristics of TIMESHARE 3 include:

- Up to 64 concurrent users on dedicated or dial-up lines

- Interactive execution of the BASIC compiler, with line-by-line syntax checking

- Log-in and sign-off procedures, with password security check

- A text editor for manipulation of user program and data files

- Simulation of a desk calculator, providing arithmetic operations with a minimum accuracy of six significant digits

- A formula calculator, where the user enters the algebraic formula and, under prompting by the computer, the values of independent variables

- A log of system events and file of system messages available to all terminal users

- Utility programs for use by the CYBER 18-30 operator for starting, stopping, and determining the status of the system, transmitting a message to all user terminals, establishing passwords, dumping, reloading, and auditing files.

- Ability to generate batch jobs at a remote terminal, for execution either by the CYBER 18-30 in batch mode or by the host processor (CYBER 170/70/ 6000/7000).

Minimum hardware requirements for TIMESHARE 3 are provided by the CYBER 18-30 Timeshare configuration and include:

- CYBER 18-30, the timeshare processor with 128K bytes and the communications processor with 64K bytes of main memory

- Asynchronous communications multiplexer, with facilities for both dial-up and dedicated lines

- Cassette tapes on both CPUs

- Storage module with 25M byte capacity

- Nine-track tape, card reader, and line printer on the timeshare CPU

#### Optional features include:

- Synchronous communication interface for host computer link

- Teletypewriter-compatible terminals

- Asynchronous communication line adapters

# MANUFACTURING INDUSTRY ACCOUNTING SYSTEM

This application software for the CYBER 18 is designed to provide a broad range of business data processing capabilities for manufacturing and distribution industries. The application software is supplied in modular form, facilitating the matching of system capabilities to a particular customer's requirements. The modules of the system are:

- Order entry and invoice preparation

- Purchase orders and accounts payable

- Inventory control and physical inventory

- Routing

- Bill of materials

- Material requirements planning

- Accounts receivable

- Payroll

- General ledger

- Sales analysis

The Manufacturing Industry Accounting System operates on a CYBER 18-10M or 18-20, supporting up to 16 local terminals operating on different tasks concurrently.

Minimum hardware requirements for the system are:

- CYBER 18-10M processor with 64K bytes of main memory (supporting two terminals), 96K bytes for up to six terminals, and 128K bytes for more than six terminals.

- Cartridge disk with 4.4M bytes of random-access mass storage

- Line printer

- Terminals with optional hard copy capability

# INTERACTIVE TERMINAL-ORIENTED SYSTEM

This application system, designed for use with the manufacturing applications programs, runs under MSOS 5. It consists of four major modules:

- Executive

- Terminal handler

- File/data manager

- Text editor/terminal utilities

#### **EXECUTIVE**

The executive controls execution of user jobs. It provides each job with a time slice, then queues the job until the next execution.

It controls the roll in/out of jobs to/from mass storage, typically when input/output is initiated. It also manages main and mass memory allocation to support multiple user job streams in main memory.

The executive isolates users from system software for system integrity. It supports serially re-entrant interpreters for multiple user access to common programs.

#### TERMINAL HANDLER

The terminal handler provides the interface between the system and the terminal operators.

Screen formatting and X-Y cursor positioning allow the user to reproduce his source data form. Data entry operations can be reduced to a simple fill-in-the-blanks operation. The cursor positioning corresponds to the automatic tabbing on a typewriter.

Corrections are made by backspacing, instead of deletion characters.

The handler supports variable operating modes: character, line, and block.

#### FILE/DATA MANAGER

Features of the file/data manager include:

- Files with up to 16 million  $(2^{24})$  records are supported. The maximum record size is 32,000  $(2^{15})$  bytes.

- The packs and cartridge are removable. Disk packs are labeled and file description information is maintained on the same volume as its associated files.

- Sequential, relative, and indexed sequential access methods are supported. Indexed sequential file key lengths are IBM standard, 29-character length.

- The initial release supports four primary level indexing keys so the user can select and sort file records with up to four different (not multilevel) keys; for example, a file of personnel records can be keyed by age, physical location, grade, and sex.

- Improved throughput is provided with techniques such as continuous file space allocation, optional sector aligned records, and mass memory overlap seek.

- Multiple users may access the same file because lockout is now at the record level

#### **TEXT EDITOR**

The source language text editor allows the user to enter, store, and retrieve text as a private or common file. Files may consist of:

- RPG II programs

- FORTRAN or Assembler programs to be batchprocessed at a later time

- Text and data files to be exchanged with a remote host processor

- Other data or text the user wishes to keep on file

The text editor supports the following commands:

| FILES  | List the names of all files belonging to the user         |

|--------|-----------------------------------------------------------|

| GET    | Retrieve a file                                           |

| SAVE   | Save a file                                               |

| BATCH  | Submit a file for batch processing                        |

| PURGE  | Discard a file                                            |

| LIST   | List a file                                               |

| AUTO   | Enter file create mode                                    |

| CLEAR  | Clear the working file                                    |

| DELETE | Delete the text line(s)                                   |

| SEARCH | Search for a text string                                  |

| CHANGE | Replace a text string                                     |

| MERGE  | Insert a named file into the text currently being editing |

| ALIGN  | Justifies text to RPG, FORTRAN, or Assembler format       |

| RESEQ  | Resequences line numbers                                  |

#### TERMINAL FILE UTILITIES

A variety of utilities is available for the manipulation of information files. These utilities are available from the interactive terminals as well as unit record equipment. The commands are:

| HELP | Print information about the command   |

|------|---------------------------------------|

| INIT | Initialize the volume on mass storage |

| STATUS Print the status of the specified file(s) RELOAD Reload a file onto mass storage from a sequential device.  DUMP Dump a file from mass storage to a sequential device  COPY Copy a file to another file  DELETE Delete a file and release storage space associated with it  CLEAR Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one specified |          |                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------|

| RELOAD Reload a file onto mass storage from a sequential device.  DUMP Dump a file from mass storage to a sequential device  COPY Copy a file to another file  DELETE Delete a file and release storage space associated with it  CLEAR Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                 | DEFINE   | Create a file on mass storage             |

| DUMP Dump a file from mass storage to a sequential device  COPY Copy a file to another file  DELETE Delete a file and release storage space associated with it  CLEAR Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                              | STATUS   | Print the status of the specified file(s) |

| COPY Copy a file to another file  DELETE Delete a file and release storage space associated with it  CLEAR Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                         | RELOAD   | 3                                         |

| DELETE Delete a file and release storage space associated with it  CLEAR Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                           | DUMP     | _                                         |

| Release all mass storage space of file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                    | COPY     | Copy a file to another file               |

| file(s) specified  LIST Print the file to the standard list device  RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                      | DELETE   | _                                         |

| RENAME Rename a specific file  COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                          | CLEAR    | <u> </u>                                  |

| COMMANDS List all file utility commands  EXIT Return to the executive  MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                         | LIST     |                                           |

| MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RENAME   | Rename a specific file                    |

| MOUNT The specified volume is available to the system  DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | COMMANDS | List all file utility commands            |

| DISMOUNT The specified volume is no longer available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EXIT     | Return to the executive                   |

| available to the system  SAVE Save the specified volume  RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MOUNT    |                                           |

| RESTORE Restore the specified volume  LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DISMOUNT | -                                         |

| LOAD Load the source data records to a file  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SAVE     | Save the specified volume                 |

| File  PURGE Release all files whose expiration dates have been exceeded  INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RESTORE  | Restore the specified volume              |

| INPUT Change the command inputting device to the one specified  COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LOAD     |                                           |

| COMPRES Delete the records marked and copy this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PURGE    | •                                         |

| this file into its existing location  OUTPUT Change the output device to the one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | INPUT    |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | COMPRES  |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OUTPUT   |                                           |

#### MODEL DESCRIPTION

Following is a brief description of the standard unit.

Descriptions of the optional peripherals are included in section 7. Standard Peripherals.

#### CYBER 18-05 BATCH TERMINAL CONTROLLER

The CYBER 18-05 batch terminal controller is a unit that can accommodate up to 32,768 eight-bit bytes (one protect and one parity bit for each two bytes) of core main memory with an effective read/write cycle time of 750 nanoseconds. The 18-05 emulates the basic as well as an enhanced 1700 instruction set. Basic features are: hardware multiply/divide, 16 levels each of micro and macro interrupts, auto-data transfer, a real-time clock, and deadstart facility from peripherals. The 18-05 supports only A/Q-type peripherals. It includes a cabinet, an operators panel, power supplies, an 1811-1 communications console, an I/O controller for the 1811-1, an I/O controller for a card reader and a line printer, a synchronous communications line adapter, and CDC 200 User Terminal batch controlware.

Feature options include:

- 300 or 600 card-per-minute card reader

- 300 or 600 line-per-minute line printer

- IBM 2780 or 3780 terminal batch controlware

#### BATCH TERMINAL CONTROLWARE

The CYBER 18-05 is a batch terminal with the ability to emulate a CDC 200 User Terminal or an IBM 2780 or 3780 terminal. This emulation is accomplished by software supplied in absolute binary form on card decks. A different deck is used for each emulation. The software is not intended to be accessible to the user for maintenance. The use of the term controlware reflects the "black-box" nature of the software.

The functions provided by the emulated terminals are described below.

#### CDC 200 USER TERMINAL EMULATION

The CDC 200 User Terminal provides the following features:

- Operator selection of Hollerith 026 or 029 card formats.

- CDC 200 User Terminal synchronous communication techniques, using modems conforming to RS232-C or CCITT-V24 specifications at rates from 1200 to 9600 baud.

- Half-duplex communication with a host computer, using a dedicated or dial-up line

- Compatibility with CDC CYBER 72, 73, 74, and 6000 Series computers using KRONOS with EXPORT/IMPORT or SCOPE with INTERCOM.

- Compatibility with CDC 3000 Series computers using MASTER with RESPOND-EXPORT/IMPORT, MARS III, or MCS III

- Operator selection of transmission-line code external or internal BCD or ASCII

- Display of operator-selected operating parameters on the CRT

- Automatic notification of line and terminal error conditions on the CRT

- Selection of input and output devices (keyboard, magnetic tape, card reader, or line printer)

- Off-line functions, providing for transfer of data between peripherals on the terminal

A selection card loaded with the controlware permits matching the controlware to the hardware configuration and to the operating modes required.

Diagnostics are provided through the Operational Diagnostic System (ODS), loaded as card decks distinct from the controlware.

The minimum hardware configuration is:

- CYBER 18-05 with 16K bytes of memory

- Card reader

- Line printer

- CRT display and keyboard

- Operator panel

#### IBM 2780 EMULATION

The IBM 2780 emulation in the batch controlware provides:

- Compatibility with IBM host computers capable of communicating with 2780 terminals

- Emulation of IBM bisync communication techniques, with equipment and capabilities similar to those of the emulated 200 User Terminal.

- Operator selection of EBCDIC or ASCII code, with transparent text mode

- Selection of number (up to 30) of retransmit attempts

- Selection of print-line length and of use of end-ofrecord feature to eliminate trailing blanks on card

- CRT display of emulated IBM 2780 status functions

- ASA vertical forms control

- Off-line processing similar to that provided under the 200 User Terminal emulation.

#### IBM 3780 EMULATION

The batch terminal controlware provides capabilities similar to those of the IBM 2780 emulation, with the addition of:

- Compatibility with IBM's Telecommunications Access Method (TCAM) under OS, and with BTAM under OS or DOS.

- Interruption of terminal operation by host CPU

- Vertical and horizontal formatting of printed data

- Restart of terminal by host CPU

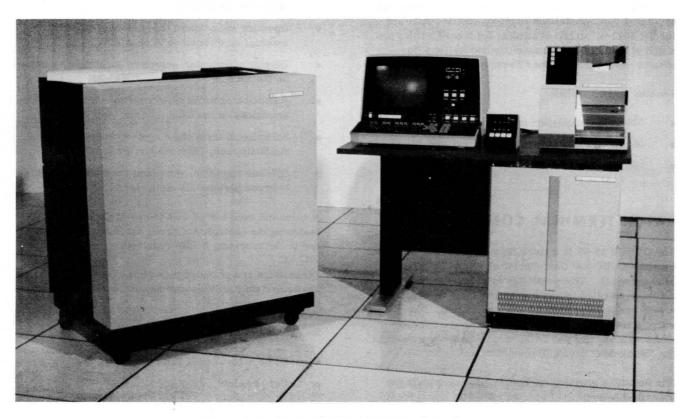

Figure 4-1. Typical CYBER 18-05 Configuration

#### MODEL DESCRIPTIONS

Following are brief descriptions of the standard units. Descriptions of optional peripherals are included in section 7, Standard Peripherals.

#### CYBER 18-10M PROCESSOR

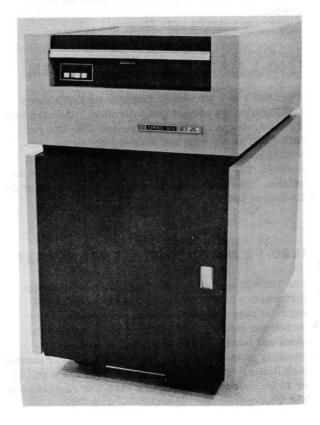

The CYBER 18-10M is a micro-programmable processor unit that accommodates from 32,768 to 131,072 eight-bit bytes (one protect and one parity for each two bytes) of MOS main memory, with an effective read/write cycle time of 750 nanoseconds. The 18-10M emulates the basic as well as the enhanced 1700 instruction set. Basic features of the processor include hardware multiply/divide, 16 levels each of micro and macro interrupts, auto-data transfer, a real-time clock. deadstart facility from peripherals, an A/Q I/O port that supports up to nine peripheral controllers, and a DMA I/O port that supports up to four DMA-type devices. Feature options are 512- through 4096-instruction read/ write micro memory with minimum instruction execution time of 168 nanoseconds for user micro programs, a programmable micro/macro breakpoint controller, and a breakpoint panel. The 18-10M includes a cabinet, operators panel, power supplies, an I/O controller to support the 1811-1 Console Display, and a flexible disk drive with controller. No main memory or read/write micro memory is included.

#### 1870-1 512 INSTRUCTION MICRO MEMORY

The 1870-1 micro memory provides storage for up to 512 32-bit micro control instructions for the processor. The memory is a read or write RAM (random-access memory) and can be loaded externally or under control of the micro program. It is designed for micro program storage in those applications that require that the processor be programmed at the micro level.

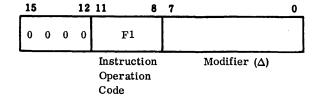

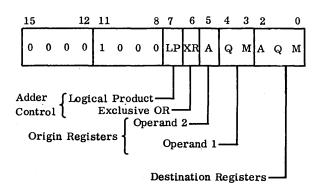

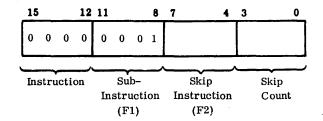

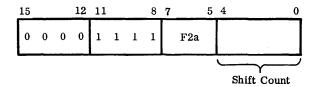

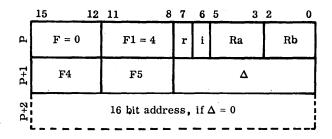

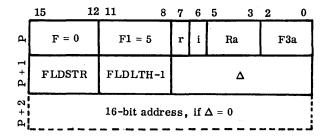

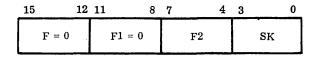

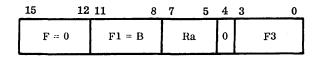

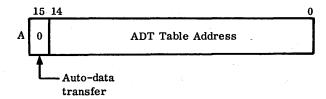

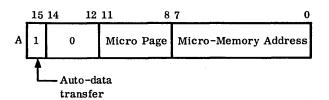

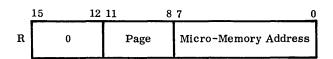

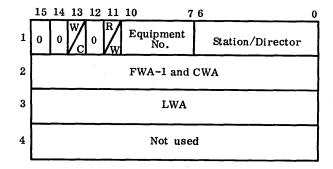

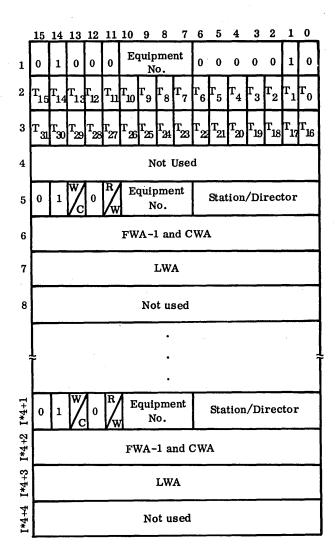

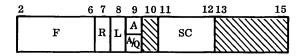

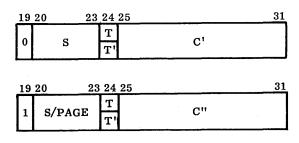

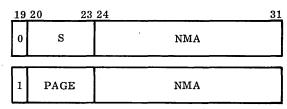

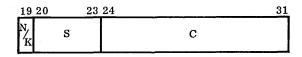

#### 1870-2 2048 INSTRUCTION MICRO MEMORY