# MACRO ASSEMBLER REFERENCE MANUAL

**CDC**®

MASS STORAGE OPERATING SYSTEM

INTERACTIVE TERMINAL-ORIENTED SYSTEM

|                                       | REVISION RECORD                                                                                            |

|---------------------------------------|------------------------------------------------------------------------------------------------------------|

| REVISION                              | DESCRIPTION                                                                                                |

| Α                                     | Original printing for Macro Assembler Version 3.0 and MSOS Version 4.0.                                    |

| (4/72)                                |                                                                                                            |

| В                                     | General revision and update for compatibility with MSOS 4.1. Appendix D added.                             |

| (3/74)                                |                                                                                                            |

| C                                     | Revised to add a new Chapter 5 and the Glossary and incorporate PSR changes 1950 and 3249.                 |

| (5/75)                                |                                                                                                            |

| D                                     | Revised to reflect MSOS 4.3 changes.                                                                       |

| (10/75)                               |                                                                                                            |

| E                                     | Revised to reflect MSOS 5 changes. Appendixes E and F added.                                               |

| (8/76)                                |                                                                                                            |

| F                                     | Manual updated to reflect correct publication numbers for related manuals.                                 |

| (1/77)                                |                                                                                                            |

| G                                     | Manual revised to reflect ITOS 2.0 release. The front cover, title page, and pages iii/iv and vi have been |

| (1/79)                                | revised.                                                                                                   |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

| <del></del>                           |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       | <u> </u>                                                                                                   |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

|                                       |                                                                                                            |

| · · · · · · · · · · · · · · · · · · · |                                                                                                            |

|                                       |                                                                                                            |

| iblication No.<br>60361900            |                                                                                                            |

Additional copies of this manual may be obtained from the nearest Control Data Corporation sales office.

© 1972, 1974, 1975, 1976, 1977, 1978 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Publications and Graphics Division

4455 Eastgate Mall

La Jolla, California 92037

or use Comment Sheet in the back of this manual.

# LIST OF EFFECTIVE PAGES

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

| PAGE                | REV | PAGE          | REV | PAGE | REV      | PAGE | REV | PAGE | REV |

|---------------------|-----|---------------|-----|------|----------|------|-----|------|-----|

| Cover               |     | 6-3 thru 6-6  | С   |      |          |      |     |      |     |

| Title Page          |     | Glossary-1    | E   |      |          |      |     |      |     |

| ii                  | G   | Glossary-2    | E   | ļ    |          |      |     |      |     |

| iii/iv              | G   | A-1           | E   |      |          |      | 1 1 |      | l i |

| v                   | E   | A-1<br>A-2    | A   |      |          |      |     |      |     |

| vi<br>vi            | G   | A-3           | В   |      |          |      | 1   |      | i   |

| vii thru ix         | E   | A-4 thru A-10 | E   |      |          | 1    |     |      |     |

| 1-1 thru 1-3        | E   | B-1           | E   | }    |          | 1    |     |      |     |

| 1-1 unu 1-3         | B   | C-1           | E   |      | l        | 1    |     |      |     |

| 1-5                 | A   | C-2 thru C-4  | A   |      |          | İ    | 1   |      |     |

| 1-6                 | A   | D-1           | В   |      |          |      |     |      |     |

| 1-7                 | D   | D-1<br>D-2    | В   |      |          | j    |     |      |     |

| 1-8                 | A   | E-1 thru E-3  | E   |      |          |      |     |      |     |

| 2-1                 | E   | F-1           | E   |      |          |      |     |      |     |

| 2-1 2-2             | E   | F-2           | E   |      |          |      |     | :    |     |

| 2-2<br>2-3 thru 2-5 | A   | Index-1 thru  |     |      |          |      |     |      |     |

| 2-6 thru 2-8        | В   | Index-4       | E   |      |          |      |     |      |     |

| 2-9 thru 2-27       | E   | Comment       | E   |      |          |      |     |      | 1   |

|                     |     | Sheet         | G   |      | 1 i      |      |     |      |     |

| 3-1                 | D   | I             |     |      |          |      |     |      |     |

| 3-2                 | В   | Cover         |     |      | <b> </b> |      |     |      | i i |

| 3-3                 | A   |               |     |      |          |      |     |      |     |

| 3-4                 | A   |               |     |      |          |      |     |      |     |

| 3-5                 | В   |               |     |      |          |      |     |      |     |

| 3-6                 | В   |               |     |      |          |      |     |      |     |

| 3-7                 | D   |               |     |      |          |      |     | · ·  |     |

| 3-8                 | D   |               |     |      |          |      |     | Į.   |     |

| 3-9 thru 3-12       | В   |               |     |      | 1        |      |     |      |     |

| 3-13                | C   |               |     |      |          |      | 1 1 |      |     |

| 3-14                | В   |               |     |      |          | }    | 1 1 |      | 1 1 |

| 3-15                | В   |               |     |      |          |      |     |      |     |

| 3-16                | A   |               | -   |      |          |      | 1 1 |      |     |

| 3-17                | D   |               |     |      | li       |      |     | }    |     |

| 3-18                | E   |               |     |      |          |      | 1 1 |      |     |

| 4-1                 | E   |               |     |      |          |      |     |      |     |

| 4-2                 | В   |               |     |      |          |      |     | 1    |     |

| 4-3                 | D   |               |     |      | }        |      |     |      |     |

| 4-4                 | D   |               |     |      |          |      | ]   |      |     |

| 4-5                 | A   |               |     |      |          |      |     |      |     |

| 4-6 thru 4-9        | В   |               |     |      |          |      |     |      |     |

| 4-10                | C   |               | ĺ   |      |          |      | ] ] |      |     |

| 5-1                 | E   | ]             |     |      |          |      |     |      |     |

| 5-2                 | E   |               |     |      |          |      | ]   |      |     |

| 5-2.1               | E   |               |     |      |          |      |     |      |     |

| 5-3 thru 5-6        | C   |               | ŀ   |      |          |      |     |      |     |

| 5-7                 | E   |               |     |      |          |      |     |      |     |

| 5-8                 | E   |               |     |      | 1        |      |     |      |     |

| 5-9 thru 5-15       | C   |               |     |      |          |      |     |      |     |

| 6-1                 | E   |               |     |      |          |      |     | 1    |     |

| 6-2                 | D   |               |     |      |          |      |     |      |     |

|                     |     | 1             |     | 1    | 1        | 1    | ı I | 1    | i i |

# **PREFACE**

The Macro Assembler for the CONTROL DATA® CYBER 18/1700 Computer Systems is a three-pass assembler that can convert source language input, including macro instructions, to relocatable output and generate list output. The source programs are written with symbolic machine, pseudo, and macro instructions.

Macro definitions may be defined by the user within the source program, or they may be placed on a separate macro library.

Input is from the standard input device, binary output is to the standard output device, and list output is to the standard list device.

The following describe functions occurring in each pass of the assembler.

#### Pass 1

Programmer-defined macros are processed, and appropriate tables are built. Whenever a macro instruction is encountered, the macro skeleton with actual parameters substituted is inserted into the source input on the mass storage device.

The source input is copied onto the mass storage device.

Sequence numbers of the input source images are checked.

#### Pass 2

Each source image on the mass storage device is read, and pass 2 errors are listed as they occur.

Conditional assembly pseudo instructions are processed.

Symbol and external tables are built.

#### Pass 3

Each image is read, and pass 3 errors are listed.

List and relocatable binary outputs are generated according to the input options.

#### TABLST

TABLST prints and punches the entry points and external images. The transfer image is punched.

An EOF image is output to the next load-and-go sector on mass storage.

A symbol table listing is given.

#### XREF

XREF creates and prints the cross-references lists.

This macro assembler operates under the Mass Storage Operating System (MSOS), Version 5, and the Interactive Terminal-Oriented System (ITOS), Version 2.

Refer to the Mass Storage Operating System (MSOS) 5 Reference Manual equipment configuration for the minimum hardware required by the Macro Assembler.

It is assumed that users of this manual are familiar with MSOS.

Following is a list of related publications.

| Description                                                                 | Publication No. |

|-----------------------------------------------------------------------------|-----------------|

| MSOS 5 Reference Manual                                                     | 96769400        |

| Mass Storage FORTRAN Version 3<br>A/B Reference Manual                      | 60362000        |

| 1700 Computer System Codes                                                  | 60163500        |

| Small Computer Maintenance Monitor<br>Reference Manual                      | 39520200        |

| MSOS 5 Instant                                                              | 96769430        |

| 1700 MSOS 5 File Manager Version 1<br>Reference Manual                      | 39520600        |

| MSOS 5 Release Bulletin                                                     | 96769440        |

| MSOS 5 Installation Handbook                                                | 96769410        |

| Small Computer Maintenance<br>Monitor Instant                               | 39521700        |

| MSOS 5 Ordering Bulletin                                                    | 96769490        |

| Interactive Terminal-Oriented System (ITOS) Version 2 Reference Manual      | 96769240        |

| Interactive Terminal-Oriented System (ITOS) Version 2 Installation Handbook | 60475200        |

This product is intended for use only as described in this document. Control Data cannot be responsible for the proper functioning of undescribed features or undefined parameters.

# **CONTENTS**

|           | PREFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | v                                                                                                      |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| CHAPTER 1 | INSTRUCTION FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-1                                                                                                    |

|           | 1.1 Source Program 1.2 Source Statement 1.2.1 Location Field 1.2.2 Remarks 1.2.3 Instruction 1.2.4 Address Field 1.2.5 Comment Field 1.2.6 Sequence Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2.1<br>1-8<br>1-8                                                 |

| CHAPTER 2 | MACHINE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-1                                                                                                    |

|           | 2.1 Storage Reference Instructions 2.1.1 Address Modes 2.1.2 Absolute Addressing 2.1.3 Relative Addressing 2.1.4 Constant Addressing 2.1.5 Data Transmission Instructions 2.1.6 Arithmetic Instructions 2.1.7 Logical Instructions 2.1.8 Jump Instructions 2.1.9 Type 2 Storage Reference 2.2 Register Reference Instructions 2.3 Inter-Register Instructions 2.3.1 Type 1 Inter-Register Instructions 2.3.2 Type 2 Inter-Register Instructions 2.5 Skip Instructions 2.5 Skip Instructions 2.5.1 Type 1 Skip Instructions 2.5.2 Type 2 Skip Instructions 2.5.3 Decrement and Repeat 2.7 Field Reference Instructions 2.8 Miscellaneous Instructions 2.9 Negative Zero/Overflow Set | 2-1 2-1 2-3 2-4 2-6 2-6 2-7 2-8 2-9 2-10 2-10.7 2-12 2-12 2-14 2-14 2-15 2-15 2-17 2-18 2-19 2-20 2-26 |

| CHAPTER 3 | PSEUDO INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-1                                                                                                    |

|           | 3.1 Subprogram Linkage 3.1.1 NAM 3.1.2 END 3.1.3 ENT 3.1.4 EXT/EXT*  3.2 Data Storage 3.2.1 BSS 3.2.2 BZS 3.2.3 COM 3.2.4 DAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1<br>3-1<br>3-1<br>3-2<br>3-2<br>3-4<br>3-4<br>3-4<br>3-5                                            |

$6\,036\,1\,900~\mathrm{E}$

|           | 3.3  | Constant Declarations 3.3.1 ADC/ADC*      | 3-7<br>3-7   |

|-----------|------|-------------------------------------------|--------------|

|           |      | 3.3.2 ALF                                 | 3-7          |

|           |      | 3.3.3 NUM                                 | 3-9          |

|           |      | 3.3.4 DEC                                 | 3-10         |

|           |      | 3.3.5 VFD                                 | 3-11         |

|           | 3.4  |                                           | 3-13         |

|           |      | 3.4.1 EQU                                 | 3-13         |

|           |      | 3.4.2 ORG/ORG*                            | 3-14         |

|           |      | 3.4.3 IFA                                 | 3-15         |

|           |      | 3.4.4 EIF                                 | 3-16         |

|           |      | 3.4.5 OPT                                 | 3-17         |

|           | 3.5  | 3.4.6 MON                                 | 3-17         |

|           | 3. 5 | Listing Control 3.5.1 NLS                 | 3-18         |

|           |      | 3.5.1 NLS<br>3.5.2 LST                    | 3-18         |

|           |      | 3.5.3 SPC                                 | 3-18<br>3-18 |

|           |      | 3.5.4 EJT                                 | 3-18<br>3-18 |

| CHAPTER 4 | MAC  | CROS                                      | 4-1          |

|           | 4.1  | Macro Pseudo Instructions                 | 4-1          |

|           | ** 1 | 4.1.1 MAC                                 | 4-1          |

|           |      | 4.1.2 EMC                                 | 4-2          |

|           |      | 4.1.3 LOC                                 | 4-2          |

|           |      | 4.1.4 IFC                                 | 4-2          |

|           | 4.2  | Macro Skeleton                            | 4-3          |

|           | 4.3  | Macro Instruction                         | 4-4          |

|           |      | 4.3.1 Parameters                          | 4-4          |

|           |      | 4.3.2 Examples                            | 4-6          |

| CHAPTER 5 | STA  | NDARD MACRO LIBRARY                       | 5-1          |

|           | 5.1  | Creating the Library                      | 5-1          |

|           | 5.2  | Modifying the Library                     | 5-2          |

|           | 5.3  | Programs in the Macro Library             | 5-2          |

|           |      | 5.3.1 Formatting Macros                   | 5-2          |

|           |      | 5.3.2 File Manager Macros                 | 5-3          |

|           |      | 5.3.3 Monitor Request Macros              | 5-8          |

|           |      | 5.3.4 Other Macros                        | 5-14         |

| CHAPTER 6 | ASSI | EMBLER OUTPUT                             | 6-1          |

|           | 6.1  | Control Options                           | 6-1          |

|           |      | 6.1.1 P Option                            | 6-1          |

|           |      | 6.1.2 X Option                            | 6-1          |

|           |      | 6.1.3 L Option                            | 6-1          |

|           |      | 6.1.4 C Option                            | 6-1          |

|           | 6 9  | 6.1.5 M Option                            | 6-2          |

|           | 6.2  | Assembly Listing                          | 6-2          |

|           |      | 6.2.1 Error Listing                       | 6-2          |

|           |      | 6.2.2 Cross-Reference Listing             | 6-3          |

|           |      | 6.2.3 Sample Program 6.2.4 Sample Listing | 6-4<br>6-4   |

|           |      |                                           | 6 = 4        |

viii

| GLOSSARY      |                                 | Glossary-1 |

|---------------|---------------------------------|------------|

| APPENDIX A    | MNEMONIC INSTRUCTIONS CODES     | A-1        |

| APPENDIX B    | PROGRAMMING CONSIDERATIONS      | B-1        |

| APPENDIX C    | ASCII CODES                     | C-1        |

| APPENDIX D    | MACRO ASSEMBLER ERRORS          | D-1        |

| APPENDIX E    | INSTRUCTION CODES               | E-1        |

| APPENDIX F    | MACRO LIBRARY                   | F-1        |

| INDEX         |                                 | Index-1    |

|               | TABLES                          |            |

|               |                                 |            |

| 2-1 Type 2 St | torage Addressing Relationships | 2-10.4     |

$60361900~\mathrm{E}$  ix

.....

#### 1.1 SOURCE PROGRAM

The number of independent subprograms comprising a source program is limited only by available space. Each subprogram may be assembled independently, or several may be assembled as a group. The main subprogram of a group is the one to which initial control is given; it need not be the first subprogram. The last subprogram of a group must be followed by the MON pseudo instruction indicating the end of assembly and return to the operating system.

Communication between subprograms is effected by the subprogram linkage pseudo instructions and by the use of common and data storage.

At execution time, the entry point named in the END pseudo instruction specifies the entry point to which initial control passes. A jump to the dispatcher or an exit request (see the MSOS reference manual) signals return of control to the operating system upon job completion. EXIT or a jump to the dispatcher must be the last statement to be executed.

# 1.2 SOURCE STATEMENT

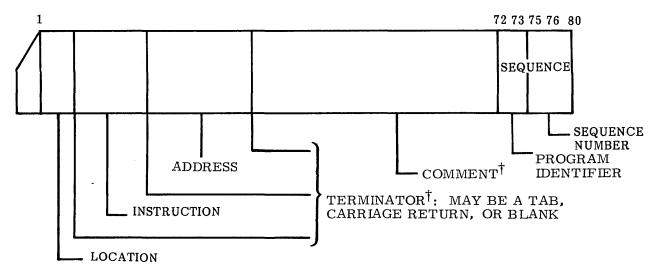

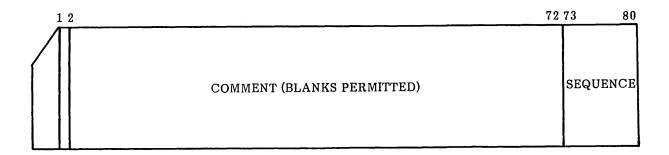

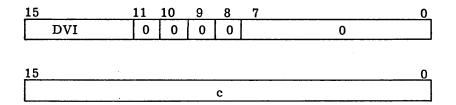

A source statement consists of location, instructions, address, remarks, and sequence fields (see figures 1-1 and 1-2). The first four fields may not exceed 72 characters; within that limitation they are free field. The sequence field is used when the source image is 80 characters; it is restricted to columns 73 through 80.

Each field is terminated by a tab (\$B; paper tape only), carriage return (end of statement mark) or blanks. Any number of blanks may separate fields. A carriage return is always the end-of-statement mark on paper tape.

<sup>†</sup>Blanks are permitted in remarks without terminating the field. It can be terminated only by a carriage return or by reading column 72.

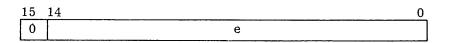

Figure 1-1. Normal Instruction, Free Field Format

Figure 1-2. Comment

#### 1.2.1 LOCATION FIELD

The location field of a source statement must begin in column 1.

This field is used to specify a labeled (label starting in column 1) or an unlabeled (blank or tab in column 1) statement.

The statement label is a symbolic name consisting of from one to six alphanumeric characters; the first must be alphabetic. Characters in excess of six are ignored. A two-character name makes the most efficient use of storage and assembly time.

#### Examples:

| LOOP1   | Legal                               |

|---------|-------------------------------------|

| 123456  | Illegal; first character is numeric |

| P1      | Legal                               |

| A123456 | Legal; only A12345 is processed     |

#### 1.2.2 REMARKS

An asterisk in column 1 of the location field specifies that the source statement is a remark. Comments, written in columns 2 through 72, are printed with the assembly list output but have no effect on the object program. An asterisk elsewhere in the location field is illegal. Remarks may also follow the address field of any instruction. There must be at least one blank separating the address field from the remarks.

#### 1.2.3 INSTRUCTION

This field begins to the right of the location field and must be separated from it by at least one blank character or a tab. If the location field contains no label (blank or tab on column 1), the operation code may begin in column 2.

The operation code field contains the three-letter instruction codes for machine and pseudo instructions, or it contains macro instructions which may be up to six characters. Certain instructions may be followed by a one-character terminator.

The mnemonic instruction codes are listed in appendix A.

#### 1.2.4 ADDRESS FIELD

The instruction field begins to the right of the operation code field, separated from it by at least one blank character or a tab. It is terminated by a blank or tab or by the 72nd character of the source statement. Exceptions are the macro instructions, which may have a continuation line, and the pseudo instruction ALF (section 3.3.2). The field may not necessarily contain an address (e.g., for some skip instructions it may contain a constant designating the number of words to be skipped).

This field contains an expression consisting of an operand or string of operands joined by arithmetic operators, or it may contain a series of operands separated by commas. An operand may be any of the following:

Symbolic name

Numeric constant

One of the special characters: \* A Q M 0 I B

#### Symbolic Operand

A symbolic name used as an operand in the address field must be defined in one of the following ways.

Label in the location field of any machine instruction

Label in the location field of any macro instruction

Label in the location field of constant declaration pseudo instructions: ADC, ALF, NUM, DEC, VFD  $\,$

Symbolic name in the address field of the pseudo instructions: EXT, COM, DAT, BSS, BZS, EQU

1-2.1

A defined symbolic name references a specific location in memory. It may be relocatable or absolute. A relocatable symbol refers to a location that may be relocated during loading.

Storage is divided into three areas: program, data, and common. These areas are defined at assembly time and the initial location of each is set to a relocation address of zero. The object code produced by the assembler contains addresses that are modified by a relocation factor to produce the actual address in memory.

A symbol is program relocatable if it references a location in the subprogram, data relocatable if it references a location in data storage, and common relocatable if it references a location in common storage. All other symbols are absolute. A symbol is made absolute by equating it to a number, an arithmetic expression, or another absolute symbol.

In all cases a symbolic label and a symbol defined by BSS or BZS take the relocation and value of the current location counter. The location counter of a program is originally program relocatable; however, its relocation may be changed by the ORG instruction.

An address expression that includes more than one operand must reference only one relocatable area. Terms of different relocation types must reduce to one relocatable area or to an absolute address. When the address mode of an instruction is made one-word relative by an asterisk terminator, the relocation type of the address expression must agree with the type of the current location counter.

A symbolic operand may be preceded by a plus or a minus sign. If preceded by a plus or no sign, the symbol refers to its associated value; if preceded by a minus, the symbol refers to the ones complement of its associated value. When an expression contains more than one symbol, the final sign of the expression is the algebraic sum of the operands.

#### Example:

RT=relocation type of current location counter: P=program relocatable, C=common relocatable, D=data relocatable, and A=absolute address.

| $\underline{\mathbf{RT}}$ | Label | Operation         | Address                                                            |

|---------------------------|-------|-------------------|--------------------------------------------------------------------|

|                           |       | COM<br>DAT<br>EQU | COM1, COM2<br>DAT1, DAT2<br>D(1), E(3), G(E-D), H(\$1000), F(DAT1) |

| P                         |       | BZS               | Α, Β, С                                                            |

| P                         |       | BZS               | J,K(10)                                                            |

The symbols D, E, G, and H are absolute; DAT1, DAT2, and F are data relocatable; COM1 and COM2 are common relocatable; A, B, C, J, and K are program relocatable.

| P | START | ADC  | 0     |         |

|---|-------|------|-------|---------|

| P |       | LDA* | START |         |

| P |       | STA* | DAT1  | (Error) |

| P |       | STA* | COM1  | (Error) |

60361900 E

The errors resulted because the relocation types of the symbols in the address field do not match that of the location counter, and the one-word relative address mode was requested by an asterisk terminator.

| $\underline{\text{RT}}$ | <u>Label</u> | Operation | Address        |

|-------------------------|--------------|-----------|----------------|

| P                       |              | LDA+      | (Not an error) |

Relocations need not match when mode is two-word absolute.

```

P LDA START (O.K., relocations match)

P LDA COM1 (Not an error)

```

Assembler changes this instruction to two-word absolute because relocations do not match, but no error is indicated.

P LDA COM2-DAT1+COM1-D+E-COM2+START-K+DAT2

This address expression results in a common relocation type; all other relocations cancel out (refer to address expressions).

ORG DAT1

ORG changes the relocation of the location counter to data.

| D | $\mathtt{LDA} *$ | START  | (Error) |

|---|------------------|--------|---------|

| D | STA*             | DAT2+9 |         |

|   | ORG*             |        |         |

ORG\* returns the location counter to original relocation.

| P | LDA*<br>ORG | START<br>H       | (Not an error) |

|---|-------------|------------------|----------------|

| A | LDA*        | $\mathtt{START}$ | (Error)        |

| A | STA*        | DAT1             | (Error)        |

| A | LDA*        | \$1001           |                |

| A | STA-        | В                |                |

|   | ORG*        |                  |                |

|   | END         |                  |                |

#### Numeric Operand

A numeric operand in the address field may be decimal or hexadecimal. A decimal number is represented by up to five decimal digits and must be within the range  $\pm 32767$ . A hexadecimal number is represented by a dollar sign and not more than four hexadecimal digits in the range  $\pm 7FFF$ . (Hexadecimal operands in the NUM pseudo instruction may be in the range  $\pm FFFF$ .)

Numeric operands in the address field may be preceded by a plus or a minus sign. If a plus or no sign is specified, the binary equivalent of the number is the value used; a minus means the one's complement of the binary equivalent is the value.

A numeric operand has no relocation type; it is always absolute.

#### Address Expression

An address expression may be a single operand or a string of operands joined by the following arithmetic operators.

- + Addition

- Subtraction

- \* Multiplication

- / Division

Arithmetic operators may not follow each other without an intervening operand. Parentheses are not permitted for grouping terms.

The asterisk has an additional meaning as an operand. When it is used as the multiplication operator (refer to special characters), it must be immediately preceded by an operand which may be another asterisk. When the asterisk is used as an operator, only one of its associated operands may be relocatable.

The slash, used as the division operator, must be between two operands. The operand which follows may not be zero or relocatable.

An external name may be used in an address expression only as a single operand. Arithmetic operators preceding or following an external operand are illegal.

# Example:

The first asterisk in the LDA instruction refers to the value of the current location counter.

The following instructions are illegal assuming the same pseudo instructions precede the START.

| START L | DA I | O-C**5+2 | *5 has no intervening operator  |

|---------|------|----------|---------------------------------|

| A.      | DD A | A-2/B    | Division by relocatable operand |

| A.      | DD I | Ī*F      | Both operands are relocatable   |

| S7      | ГА С | G+5      | An external must stand alone    |

The hierarchy for the evaluation of arithmetic expressions is:

/ or \* Evaluated first + or - Evaluated next

Expressions containing operators at the same level are evaluated from left to right. The expression

A/B+C\*D

is evaluated algrebraically as

A/B+(C)(D)

and not as any of the following:

$$\frac{(A)(D)}{B+C}$$

$\frac{A}{(B+C)(D)}$   $\frac{A}{B+(C)(D)}$

Parentheses may not be used for grouping operands. The algrebraic expression

$$(A-D)(B+C/E)$$

must be specified

$$A*B+A*C/E-D*B-D*C/E$$

The following expression is illegal.

$$(A-D)*(B+C/E)$$

Division in an address expression always yields a truncated result; thus, 11/3=3. The expression A\*B/C may result in a value different from B/C\*A. For example, if A=4, B=3, and C=2 then

All expressions are evaluated modulo  $2^{15}$ -1. An address expression consisting solely of numeric operands is absolute. If an expression contains symbolic operands, the final relocation for the expression is determined by the relocations of the symbolic operands. If the relocation of the operands is expressed by the following terms, the final relocation is the algebraic sum of the relocation terms.

- ±P Positive or negative program relocation

- ±C Positive or negative common relocation

- ±D Positive or negative data relocation

The relocation must reduce to one of the relocation terms or to zero. If zero, the location is absolute.

#### Example:

| Source | Statemer                                      | <u>nts</u>                                                                          | Relocation Formula                                                                                         |

|--------|-----------------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| STRT   | COM<br>DAT<br>EQU<br>LDA<br>LDA<br>LDA<br>LDA | A,B<br>C,D<br>E(1),F(D)<br>B+C-E*2-A-D<br>B+D-F+STRT-A-C<br>B+D-E+STRT-A-C<br>B-D-A | +C+D-C-D=0 (absolute)<br>+C+D-D+P-C-D=P-D (illegal)<br>+C+D+P-C-D=P (program)<br>+C-D-C=-D (negative data) |

#### Special Characters

Special characters may be used as operands in the address field of a source statement. Their definition may not be changed by the user. The three classes of special characters are storage, register, and index.

| Class    |   | Character        | Referenced Location                                                               |

|----------|---|------------------|-----------------------------------------------------------------------------------|

| Storage  | { | *<br>I           | Current location counter Location FF <sub>16</sub>                                |

| Register | { | A<br>Q<br>M<br>0 | A register<br>Q register<br>Mask register<br>Destination registers                |

| Index    | { | Q<br>I<br>B      | Index 1, Q register<br>Index 2, location FF <sub>16</sub><br>Index 1 plus index 2 |

Storage class characters (\*, I) reference storage locations. The asterisk refers to the location of the current instruction. For a two word instruction, an asterisk references the location of the first word. Special character I refers to value  $FF_{16}$ . I is the only indexing character that may stand alone as an operand with storage reference instructions. It may not be redefined in a program. It may be used anywhere the value  $FF_{16}$  is used.

The register class characters (A, Q, M, and 0) are used only with inter-register transfer instructions. They refer to the A, Q, and M (mask) registers. Character 0 sets the destination registers to zero (section 2.5).

#### Examples:

| Instruction | <u>Function</u>                                                  |

|-------------|------------------------------------------------------------------|

| SET A,Q,M   | Set A, Q, and mask registers to ones                             |

| TRA Q       | Transfer contents of A register to Q register                    |

| LAM M       | Transfer logical product of A and mask register to mask register |

Index class characters (Q, I, and B) are used in conjunction with an address expression to refer to the index registers. Any one character may follow an address expression; it is separated from the expression by a comma with no intervening blank. Indexing may be used only with storage reference instructions.

- Q Contents of Q register are added to contents of the expression to form the actual address

- I Contents of location FF<sub>16</sub> are added to contents of address expression to form the actual address

- B Contents of Q register are added to address expression and this sum is added to contents of FF<sub>16</sub> to produce the actual address

#### Examples:

| Address Field |         | <u>Function</u>                                                                                                                                           |

|---------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOC1, B       | Legal   | Contents of registers Q and FF16 and the contents of LOC1 are added to produce the actual address                                                         |

| ,,I           | Illegal | Character following first comma is assumed to be index character                                                                                          |

| TAG2,Q,I      | Illegal | Only one index notation allowed                                                                                                                           |

| Q             | Illegal | Unless Q has been previously defined as a location symbol or is being used with the inter-register transfer instruction, it must follow a location symbol |

| TAG3,I        | Legal   | Contents of ${\rm FF}_{16}$ and TAG3 are added to produce the actual address                                                                              |

#### 1.2.5 COMMENT FIELD

The address field is followed by the comment field which is used for remarks. Remarks do not affect the object code, but are printed as part of the list output. The comment field terminates at column 72, or with a carriage return (paper tape). Blanks are permitted in the comment field.

#### 1.2.6 SEQUENCE FIELD

When the input image is 80 characters, columns 73 through 80 are available for sequencing; 73 through 75 may be used for program identification, 76 through 80 for a sequence number.

Sequence numbers are checked for errors only if the input image is 80 characters. Each sequence number must be greater than or equal to the previous sequence number. The value of a character in the sequence number is in ASCII code except that a blank is treated as zero.

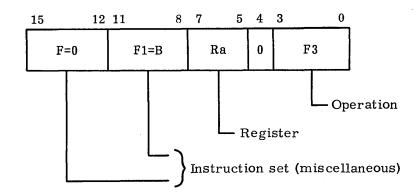

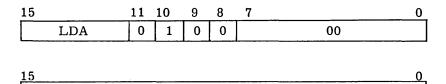

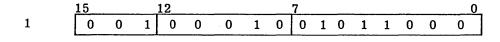

Machine instructions represented by a three-letter mnemonic code are divided into six basic classes and six additional classes of enhanced instructions.

#### BASIC CLASSES

Group A storage reference Shift

Group B storage reference Skip

Register reference Inter-register transfer

#### ENHANCED INSTRUCTION CLASSES

Type 2 storage reference Type 2 skip

Field reference Type 2 inter-register transfer

Decrement and repeat Miscellaneous

Storage reference instructions result in one or two machine words, depending on modification. Other machine instructions result in one machine word.

Appendix A lists the machine instructions in the order in which they are discussed in this chapter and also defines groups A and B storage reference instructions.

## 2.1 STORAGE REFERENCE INSTRUCTIONS

Group A and B storage reference instructions use storage addresses as operands or as operand addresses. Group B instructions include jump instructions and may not use the constant mode of addressing. Type 2 storage reference instructions use the enhanced two or three-word format. These may be 8- or 16-bit address.

#### 2.1.1 ADDRESS MODES

Group A storage reference instructions allow three modes of addressing: absolute, relative, and constant. Group B does not allow the use of the constant mode, but is otherwise the same as group A.

Special characters designate the mode of addressing, the number of words for the instruction, and indirect addressing.

| Character | Description                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------|

| *         | Asterisk as the last character of operation code specifies relative addressing in a one-word instruction |

| -         | Minus as the last character of operation code specifies absolute addressing in a one-word instruction    |

| +         | Plus as the last character of operation code specifies absolute addressing in a two-word instruction     |

#### Character

#### Description

Equal sign as the first character in address field preceding a constant indicates constant addressing; the instruction is always two words

() Parentheses enclosing the address expression indicate indirect addressing

If no character is specified as a terminator to the operation code, two-word relative addressing is assumed with the following exceptions.

- 1. If a constant is specified, the constant mode is assumed.

- 2. If the relocation type of the address expression differs from the relocation type of the location counter, two-word absolute addressing is assumed.

- 3. If a nonrelative external is referenced, absolute addressing is assumed.

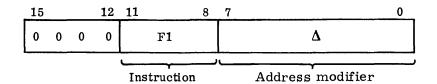

The machine language format resulting from a storage reference instruction is illustrated as follows.

First word:

| <u>1</u> 5 | 11_ | 10  | 9 | 8 | 7 0 |

|------------|-----|-----|---|---|-----|

| f          | r   | . d | q | i | Δ   |

- f 4-bit operation code is defined below

- r Specifies relative addressing

- d Specifies indirect addressing

- q Index register 1 flag; specifies adding contents of Q register to address

- δ 8-bit field; may be relative or absolute address for one-word instructions. When zero, indicates two-word instruction.

Second word (when used):

c 16-bit field for constant addressing or relative address. When it contains relative address, bit 15 is the sign.

- b Indirect address bit

- m Memory address

Address expressions are evaluated modulo 215-1.

#### 2.1.2 ABSOLUTE ADDRESSING

The value of the address expression of a one-word absolute instruction must be non-relocatable. The evaluated result is stored in 8 bits of the machine word. If this value is greater than 256, it is flagged as an error. If the 8-bit  $\Delta$  field is zero, two machine words are assumed regardless of the operation code terminator; no error message is printed. If the address expression is enclosed in parentheses for indirect addressing, bit 10 of the first word is set to 1.

Examples:

One Word, Direct

Instruction:

LDA-

Machine Word:

| 15  | 11 | 10 | 9 | 8 | 7 | ( | 0 |

|-----|----|----|---|---|---|---|---|

| LDA | 0  | 0  | 0 | 0 |   | e | ٦ |

One Word, Indirect

Instruction:

ADQ- (e)

Machine Word:

| 15  | 11 | 10 | 9 | 8 | 7 | 0_ |

|-----|----|----|---|---|---|----|

| ADQ | 0  | 1  | 0 | 0 | е |    |

The value of the address expression of a two-word absolute instruction is stored in the least significant bits of the second word. If the expression is enclosed in parentheses for indirect addressing, bit 15 of the second word is set to 1. The indirect address bit 10 in the first word is always set to 1 when two-word absolute addressing is specified whether the address expression is specified as indirect or direct. This indicates that the address expression is in the second word. The 8-bit  $\Delta$  field of the first word is set to zero for two-word instructions.

Examples:

Two Word, Direct

Instruction:

EOR+ e

Machine Words:

| 15  | 11 | 10 | 9 | 8 | 7  | 00_ |

|-----|----|----|---|---|----|-----|

| EOR | 0  | 1  | 0 | 0 | 00 |     |

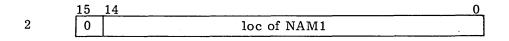

#### Two Word, Indirect

Instruction:

AND+ (e)

Machine Words:

| 15    | 1   | 1 | 10 | 9 | 8 | 7 |                                       | 0 |

|-------|-----|---|----|---|---|---|---------------------------------------|---|

| AN    | D ( | 0 | 1  | 0 | 0 |   | 00                                    |   |

| -     |     |   |    |   |   | · | · · · · · · · · · · · · · · · · · · · |   |

| 15 14 |     |   |    |   |   |   |                                       | 0 |

| 1     |     |   |    |   | е |   |                                       |   |

#### 2.1.3 RELATIVE ADDRESSING

When one-word relative addressing is specified, the value of the current location counter is subtracted (16-bit ones complement arithmetic) from the evaluated address expression. The result is placed in the 8-bit  $\Delta$  field. If the value of the result is outside the range  $\pm 7F_{16}$ , an error condition is flagged. An error condition is also flagged if the relocation type of the address expression differs from that of the location counter. If the 8-bit  $\Delta$  field is zero, two words are assumed regardless of the operation code terminator. No error message is printed for this condition.

#### Examples:

# One Word, Direct

Instruction:

AND\* €

Machine Word:

| 15  | 11 | 10 | 9 | 8 | 7 | 0   |

|-----|----|----|---|---|---|-----|

| AND | 1  | 0  | 0 | 0 |   | e-* |

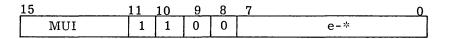

# One Word, Indirect

Instruction:

MUI\* (e)

Machine Word:

In the expression e-\* the asterisk indicates the value of the current location counter.

When a two-word instruction is specified, the value of the current location counter plus one is subtracted (using 16-bit 1's complement arithmetic) from the value of the address expression to obtain the 16-bit second word. If the relocation type of the address expression differs from that of the location counter and the address does not reference an external, the assembler forces a two-word absolute instruction. If the address expression is an external reference, the instruction is absolute or relative depending on the definition of the external.

#### Examples:

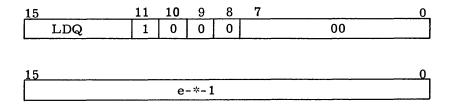

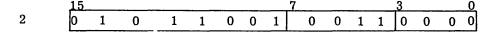

# Two Word, Direct

Instruction:

LDQ e

Machine Words:

# Two Word, Indirect

Instruction:

LDA (e)

Machine Words:

In the expression, e-\*-1, the asterisk indicates the value of the current location counter.

#### 2.1.4 CONSTANT ADDRESSING

Constant addressing may be used only for Group A storage reference instructions. Constants in the address field are preceded by an equal sign and a one-letter code. A constant may be one of the following:

|     | Code   | Type     | Meaning                                                           |

|-----|--------|----------|-------------------------------------------------------------------|

|     | Α      | aa       | 2 alphanumeric characters                                         |

|     | N      | ± ddddd  | 5-digit decimal number with or without a leading sign             |

|     | N      | ±\$hhhh  | 4-digit hexadecimal number preceded by \$, with or without a sign |

|     | X      | e        | Address expression evaluated modulo $2^{15}-1$                    |

|     | X      | (e)      | Address expression evaluated modulo $2^{15}$ -1, with bit 15 set  |

| Exa | mples: |          |                                                                   |

|     | DVI    | =N\$1000 | (Hexadecimal constant)                                            |

|     | ADD    | =N-12345 | (Decimal constant)                                                |

|     | LDA    | =AXY     | (ASCII constant)                                                  |

|     | AND    | =XTAG1+5 | (Address expression constant)                                     |

An instruction containing a constant in the address field results in two machine words.

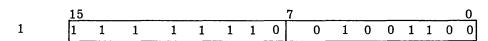

# Example:

#### Instruction:

DVI =nc

(n is the code, c is the constant)

Machine Words:

# 2.1.5 DATA TRANSMISSION INSTRUCTIONS

STQ (F=4) Store Q. Store the contents of the Q register in the storage location specified by the effective address. The contents of Q are not altered.

STA (F=6) Store A. Store the contents of the A register in the storage location specified by the effective address. The contents of A are not altered.

- SPA (F = 7) Store A, Parity to A. Store the contents of the A register in the storage location specified by the effective address. Clear A if the number of 1 bits in A is odd. Set A equal to 0001<sub>16</sub> if the number of 1 bits in A is even. The contents of A are not altered if the write into storage is aborted because of parity error or protect fault.

- LDA (F = C) Load A. Load the A register with the contents of the storage location specified by the effective address. The contents of the storage location are not altered.

- LDQ (F = E) Load Q. Load the Q register with the contents of the storage location specified by the effective address. The contents of the storage location are not altered.

#### 2.1.6 ARITHMETIC INSTRUCTIONS

All the following arithmetic operations use one's complement arithmetic.

- MUI (F = 2) Multiply Integer. Multiply the contents of the storage location, specified by the effective address, by the contents of the A register. The 32-bit product replaces the contents of Q and A, the most significant bits of the product in the Q register.

- DVI (F = 3) Divide Integer. Divide the combined contents of the Q and A registers by the contents of the effective address. The Q register contains the most significant bits before dividing. If a 16-bit dividend is loaded into A, the sign bit of A must be extended throughout Q. The quotient is in the A register and the remainder is in the Q register at the end of the divide operation.

The OVERFLOW indicator is set if the magnitude of the quotient is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

ADD (F = 8) Add to A. Add the contents of the storage location, specified by the effective address, to the contents of the A register.

The OVERFLOW indicator is set if the magnitude of the sum is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

- SUB (F = 9) Subtract From A. Subtract the contents of the storage location, specified by the effective address, from the contents of the A register. Operation on overflow is the same as for an Add to A instruction.

- RAO (F = D) Replace Add One in Storage. Add one to the contents of the storage location specified by the effective address. The contents of A are not altered. Operation on overflow is the same as for an Add to A instruction.

- ADQ (F = F) Add to Q. Add the contents of the storage location, specified by the effective address, to the contents of the Q register. Operation on overflow is the same as for an Add to A instruction.

60316900B 2-7

#### 2.1.7 LOGICAL INSTRUCTIONS

The AND (AND with A) instruction achieves its results by forming a logical product. A logical product is a bit-by-bit multiplication of two binary numbers according to the following rules:

$$0 \times 0 = 0$$

$1 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 1 = 1$

Example:

0011 Operand A

x 0101 Operand B

0001 Logical Product

A logical product is used, in many cases, to select only specific portions of an operand for use in some operation. For example, if only a specific portion of an operand in storage is to be entered into the A register, the operand is subjected to a mask in A. This mask is composed of a predetermined pattern of 0s and 1s. Executing the AND instruction causes the operand to retain its original contents only in those bits which have 1s in the mask in A.

The EOR (Exclusive OR with A) instruction achieves its result by forming an exclusive OR. Executing the EOR instruction causes the operand to complement its original contents only in those bits which have 1s in the mask in A. An exclusive OR is a bit-by-bit logical subtraction of two binary numbers according to the following rules:

#### Exclusive OR

| <u>A</u> | <u>B</u> | A 🕶 B |

|----------|----------|-------|

| 1        | 1        | 0     |

| 1        | 0        | 1     |

| 0        | 1        | 1     |

| 0        | 0        | 0     |

#### Example:

- AND (F = A) AND with A. Form the logical product, bit-by-bit, of the contents of the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.

- EOR (F = B) Exclusive OR with A. Form the logical difference (exclusive OR), bit-by-bit, of the contents of the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.

#### 2.1.8 JUMP INSTRUCTIONS

A Jump (JMP) instruction causes a current program sequence to terminate and initiates a new sequence at a different location in storage. The program address register, P, provides continuity between program instructions and always contains the storage location of the current instruction in the program.

When a Jump instruction occurs, P is cleared and a new address is entered. † In the Jump instruction, the effective address specifies the beginning address of the new program sequence. The word at the effective address is read from storage and interpreted as the first instruction of the new sequence.

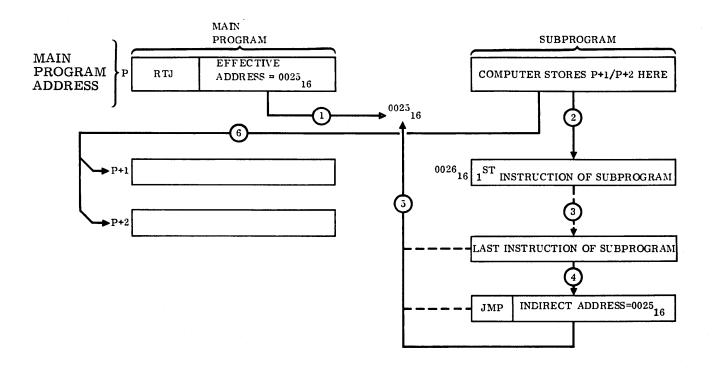

A Return Jump (RTJ) instruction enables the computer to leave the main program, jump to some subprogram, execute the subprogram, and return to the main program via another instruction. The Return Jump provides the computer with the necessary information to enable returning to the main program. Figure 2-1 shows how a Return Jump instruction can be used.

Figure 2-1. Program Using Return Jump Instruction

60361900 E 2-9

<sup>†</sup>Jumps or return jumps from unprotected to protected storage cause a fault, but the address that is saved in the trap location is the destination address (i.e., the address of the next sequential main program instruction).

An RTJ instruction is executed at main program address P. The computer jumps to effective address  $0025_{16}$  and stores P+1 or P+2 (depending on the address mode of RTJ) at this location. Then the program address counter P is set to  $0026_{16}$  and the computer starts executing the subprogram. At the end of the subprogram, the computer executes a jump instruction (JMP) with indirect addressing. This causes the computer to jump to the address specified by the subprogram address  $0025_{16}$  (P+1 or P+2 of the main program). Now main program execution continues at P+1 or P+2.

- JMP (F=1) Jump. Jump to the address specified by the effective addresses. This effectively replaces the contents of program address counter P with the effective address specified in the JMP instruction.

- RTJ (F = 5) Return Jump. Replace the contents of the storage location specified by the effective address with the address of the next consecutive instruction. The address stored in the effective address is P+1 or P+2, depending on the addressing mode of RTJ. The contents of P are then replaced with the effective address plus one.

#### 2.1.9 TYPE 2 STORAGE REFERENCE

#### NOTE

Instruction formats for enhancements to the instruction repertoire are upward-compatible with the existing 1704/14/84 computer

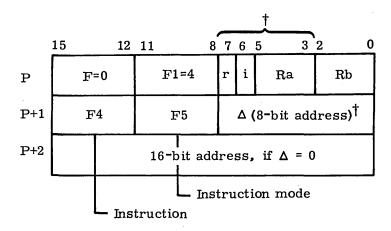

#### FORMAT:

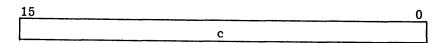

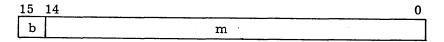

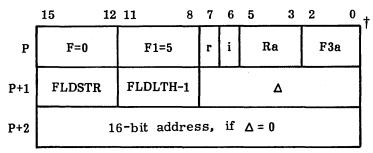

Type 2 storage reference instructions are identified by F field = 0, F1 = 4, and the r, i, Ra, and Rb fields are not all zero. (If these fields are all zero, the instruction is an EIN.) This instruction is made up of two words if  $\Delta \neq 0$  or three words otherwise. The type 2 storage reference instructions contain four parts: instruction field (F4), instruction mode field (F5), addressing mode fields (delta, r, i, and Ra), and the Rb register. From these, two operands (A and B) are specified for executing the instruction.

The F4 determines the instruction (e.g., add, subtract, etc.); F5 determines the instruction mode.

<sup>&</sup>lt;sup>†</sup>Addressing mode field

| $\mathbf{F5}$ | <u>Mode</u>                                |

|---------------|--------------------------------------------|

| 0             | word processing, register destination      |

| 1             | word processing, memory destination        |

| 2             | character processing, register destination |

| 3             | character processing, memory destination   |

F5 is not used for subroutine jumps and subroutine exit. The register/memory destination bit of F5 is not used for compare instructions.

The addressing mode requires four fields:

| Field | Addressing Mode                                                                                      | Addressing Mode |  |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Δ     | Eight or 16-bit address. $\Delta \neq 0$ , 8-bit; $\Delta = 0$ , 16-bit with the address in word P+2 | 1               |  |  |  |  |  |  |

| r     | Relative address                                                                                     |                 |  |  |  |  |  |  |

| i     | Indirect address                                                                                     |                 |  |  |  |  |  |  |

| Ra    | Index register                                                                                       |                 |  |  |  |  |  |  |

Type 1 storage instructions allow indexing by one or two registers (I and/or Q); type 2 allows indexing by any one of seven registers (1, 2, 3, 4, Q, A, or I).

The addressing mode fields determine the effective address for operand A; the Rb register and the instruction mode field (F5) determine the address for operand B. For character addressing, the effective address (operand A and the Rb register) are combined to generate the actual character effective address. Operand B is always the A register for character addressing.

#### **CAUTION**

For character addressing, a selection of absolute (r=0), no indirect (i=0), no index register (Ra=0), and no character register (Rb=0) results in an EIN instruction.

Unspecified combinations of F4, F5, and Rb are reserved for future expansion.

#### Addresses are defined below:

- Instruction address: The address of the instruction being executed, also called P

- Indirect address: A storage address that contains an address rather than an operand.

There is no multi-level indirect addressing for type 2 storage reference instructions.

- Base address: The operand address after all indirect addressing has been accomplished but before modification by an index register. The base address is the effective address if no indexing is specified.

- Effective address: The final address of the operand

- Indexing: If specified, the contents of the Ra register are added to the base address

to form the effective address. Indexing occurs after indirect addressing has been

completed.

The computer uses the 16-bit ones complement adder during indexing operations. Consequently, index register contents are treated as signed quantities (bit 15 is the sign bit).

Registers: The Ra and Rb registers are defined as follows:

| Register | <u>Value</u> |

|----------|--------------|

| None     | 0            |

| 1        | 1            |

| 2        | 2            |

| 3        | 3            |

| 4        | 4            |

| Q        | 5            |

| Å        | 6            |

| T        | 7            |

Type 2 storage reference instructions have eight types of addressing modes:

• Eight-bit absolute –  $(r=0, i=0, \Delta \neq 0)$

The base address equals delta. The sign bit of delta is not extended. The contents of index register Ra, when specified, are added to the base address to form the effective address.

• Eight-bit absolute indirect - (r=0, i=1,  $\Delta \neq 0$ )

The eight-bit value of delta is an indirect address. The sign bit of delta is not extended. The contents of this address in low core (addresses 0001 to 00FF) are the base address. The contents of index register Ra, when specified, are added to the base address to form the effective address.

• Eight-bit relative – (r=1, i=0,  $\Delta \neq 0$ )

The base address is equal to the instruction address plus one, P+1, plus the value of delta with sign extended. The contents of index register Ra, when specified, are added to the base address to form the effective address.

If no indexing takes place, the addresses that can be referenced in the eight-bit relative mode are restricted to the program area. Delta is eight bits long; thus the computer references a location between  $P^{-7}E_{16}$  and  $P^{+80}_{16}$  inclusive.

• Eight-bit relative indirect – (r=1, i=1,  $\Delta \neq 0$ )

The address of the second word of the instruction, P+1, plus the value of delta with sign extended is an indirect address. The contents of this address are the base address. The contents of index register Ra, when specified, are added to the base address to form the effective address.

• Absolute constant -  $(r=0, i=0, \Delta=0)$

The address of the third word of the instruction P+2, is the base address. The contents of the index register Ra, when specified, are added to the base address to form the effective address. Thus, when Ra is not specified, the contents of P+2 are the value of the operand.

Note that there is no immediate operand condition (i.e., indexing is specified and the instruction is read-operand type) as there is for type 1 storage reference addressing.

• Sixteen-bit absolute - (Storage) (r=0, i=1,  $\Delta$ =0)

The base address equals the contents of P+2 plus P+2. The contents of index register Ra, when specified, are added to the base address to form the effective address.

Sixteen-bit relative - (r=1, i=0,  $\Delta$ =0)

The base address equals the contents of P+2 plus P+2. The contents of index register Ra, when specified, are added to the base address to form the effective address.

• Sixteen-bit relative indirect -  $(r=1, i=1, \Delta=0)$

The address of the third word of the instruction, P+2, plus the contents of the third word of the instruction are an indirect address. The contents of this address are the base address. The contents of index register Ra, when specified, are added to the base address to form the effective address.

Table 2-1 summarizes the eight addressing modes.  $\Delta$ , r, i, and Ra are specified as is the effective address and the address of the next instruction.

SJE (F4=5, F5=0, Rb=0)

Subroutine/Jump Exit. The contents of P are replaced with the effective address. This instruction can be used as a jump or subroutine exit. For example, if  $\Delta$ =1, and Ra has been set up by a previous subroutine jump, control is returned following that subroutine jump. Subroutine jumps save the address of the last word of the instruction, rather than the next instruction so that the subroutine jump exit may be a two-word instruction ( $\Delta$  is nonzero) rather than three.

For example, the following program makes a subroutine jump at location 1000. The A register contains 1002 upon entry to subroutine SUB. Upon SUB's completion, it exits to location 1003.

| -    |              | _   |         |       |

|------|--------------|-----|---------|-------|

| 1000 | <b>044</b> 6 |     | SJA+    | SUB   |

| 1001 | 5000         |     |         |       |

| 1002 | 2000         |     |         |       |

| 1003 | 2000         |     |         |       |

| 1003 |              |     | •       |       |

|      |              |     | •       |       |

|      |              |     | •       |       |

| 2000 | • • •        | SUB | . • • • | • • • |

|      |              | _   | _       |       |

|      |              |     | •       |       |

|      |              |     | •       |       |

|      |              |     | •       |       |

| 2020 | 0430         |     | SJE-    | 1, A  |

| 2021 | 5001         |     |         | •     |

#### CAUTION

Since Rb=0, a selection of absolute (r=0), no indirect (i=0), and no index register (Ra=0) result in an EIN instruction.

#### NOTE

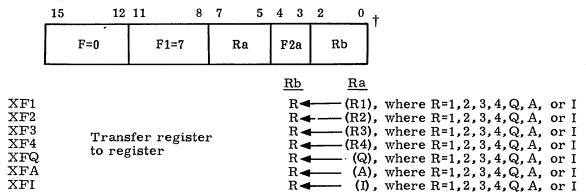

In the following instructions, Rb has the numeric value corresponding to the alphanumeric R:  $1 \longrightarrow 1$ ,  $2 \longrightarrow 2$ ,  $3 \longrightarrow 3$ ,  $4 \longrightarrow 4$ ,  $5 \longrightarrow Q$ ,  $6 \longrightarrow A$ ,  $7 \longrightarrow I$ .

SJr (F4=5, F5=0, Rb→r) Subroutine Jump. Loads the r register with the address of the last word of this instruction (i.e., P+1 for delta not zero; P+2 for delta zero). The contents of P are then replaced with the effective address.

TABLE 2-1. TYPE 2 STORAGE ADDRESSING RELATIONSHIPS

|                                      |            | !                               |                                 |                                      |                                                                                                                                                                          | Address of<br>Next                                   |

|--------------------------------------|------------|---------------------------------|---------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Addressing Modes                     | Delta      | r                               | i                               | Ra                                   | Effective Address (EA)                                                                                                                                                   | Instruction                                          |

| 8-Bit Absolute                       | <b>≠</b> 0 | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Δ<br>Δ+(1)<br>Δ+(2)<br>Δ+(3)<br>Δ+(4)<br>Δ+(Q)<br>Δ+(A)<br>Δ+(I)                                                                                                         | P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2 |

| 8-Bit Absolute Indirect              | <b>≠</b> 0 | 0<br>0<br>0<br>0<br>0<br>0      | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | (Δ)<br>(Δ)+(1)<br>(Δ)+(2)<br>(Δ)+(3)<br>(Δ)+(4)<br>(Δ)+(Q)<br>(Δ)+(A)<br>(Δ)+(I)                                                                                         | P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2 |

| 8-Bit Relative <sup>†</sup>          | <b>#</b> 0 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | $P+1+\Delta$ $P+1+\Delta+(1)$ $P+1+\Delta+(2)$ $P+1+\Delta+(3)$ $P+1+\Delta+(4)$ $P+1+\Delta+(Q)$ $P+1+\Delta+(A)$ $P+1+\Delta+(I)$                                      | P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2 |

| 8-Bit Relative Indirect <sup>†</sup> | <b>≠</b> 0 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>2<br>3<br>4<br>5<br>6      | $(P+1+\Delta)$<br>$(P+1+\Delta)+(1)$<br>$(P+1+\Delta)+(2)$<br>$(P+1+\Delta)+(3)$<br>$(P+1+\Delta)+(4)$<br>$(P+1+\Delta)+(Q)$<br>$(P+1+\Delta)+(A)$<br>$(P+1+\Delta)+(I)$ | P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2<br>P+2 |

| Absolute Constant                    | =0         | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | P+2<br>P+2+(1)<br>P+2+(2)<br>P+2+(3)<br>P+2+(4)<br>P+2+(Q)<br>P+2+(A)<br>P+2+(I)                                                                                         | P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3 |

NOTE: ( ) denotes contents of.

$<sup>\</sup>ensuremath{^{\dagger}} \ensuremath{\text{For these}}$  addressing modes, delta is sign extended.

TABLE 2-1. TYPE 2 STORAGE ADDRESSING RELATIONSHIPS (Continued)

| Addressing Modes             | Delta | r                          | i                               | Ra                                   | Effective Address (EA)                                                                                                                           | Address of<br>Next<br>Instruction                    |

|------------------------------|-------|----------------------------|---------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 16-Bit Absolute<br>(Storage) | =0    | 0 0 0 0 0 0 0              | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | (P+2)<br>(P+2)+(1)<br>(P+2)+(2)<br>(P+2)+(3)<br>(P+2)+(4)<br>(P+2)+(Q)<br>(P+2)+(A)<br>(P+2)+(I)                                                 | P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3 |

| 16-Bit Relative              | =0    | 1<br>1<br>1<br>1<br>1<br>1 | 0<br>0<br>0<br>0<br>0<br>0      | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | P+2+(P+2)<br>P+2+(P+2)+(1)<br>P+2+(P+2)+(2)<br>P+2+(P+2)+(3)<br>P+2+(P+2)+(4)<br>P+2+(P+2)+(Q)<br>P+2+(P+2)+(A)<br>P+2+(P+2)+(1)                 | P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3        |

| 16-Bit Relative<br>Indirect  | =0    | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1<br>1<br>1<br>1<br>1 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | (P+2+(P+2))<br>(P+2+(P+2))+(1)<br>(P+2+(P+2))+(2)<br>(P+2+(P+2))+(3)<br>(P+2+(P+2))+(4)<br>(P+2+(P+2))+(Q)<br>(P+2+(P+2))+(A)<br>(P+2+(P+2))+(I) | P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3<br>P+3 |

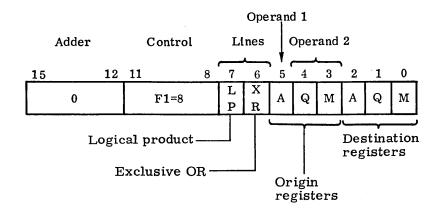

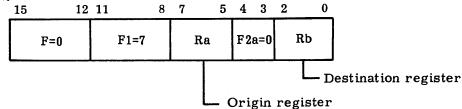

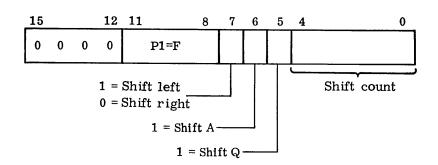

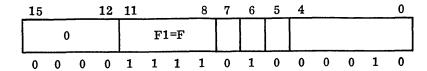

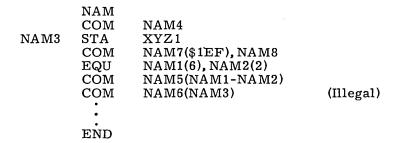

ARr (F4=8, F5=0, Rb→r)