# CONTROL DATA® 1700 COMPUTER SYSTEMS

1700 MSOS 4 MACRO ASSEMBLER REFERENCE MANUAL

|                           | REVISION RECORD                                                                |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------|--|--|--|--|

| REVISION                  | DESCRIPTION                                                                    |  |  |  |  |

| A                         | Original printing for Macro Assembler Version 3.0 and MSOS Version 4.0.        |  |  |  |  |

| (4/72)                    |                                                                                |  |  |  |  |

| В                         | General revision and update for compatibility with MSOS 4.1. Appendix D added. |  |  |  |  |

| (3/74)                    |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

|                           |                                                                                |  |  |  |  |

| ublication No<br>60361900 |                                                                                |  |  |  |  |

Additional copies of this manual may be obtained from the nearest Control Data Corporation sales office.

© 1972, 1974 by Control Data Corporation Printed in the United States of America Address comments concerning this manual to:

Control Data Corporation

Small Computer Development Division

4455 Eastgate Mall

La Jolla, California 92037

or use Comment Sheet in the back of this manual.

## PREFACE

The Macro Assembler for the CONTROL DATA $^{\circledR}$  1700 Computer System is a 3-pass assembler which can convert source language input including macro instructions to relocatable output and generate list output. The source programs are written with symbolic machine, pseudo, and macro instructions.

Macro definitions may be defined by the user within the source program, or they may be placed on a separate macro library.

Input is from the standard input device, binary output is to the standard output device, and list output is to the standard list device.

The following describe functions occurring in each pass of the assembler.

#### Pass 1

Programmer defined macros are processed and appropriate tables are built. Whenever a macro instruction is encountered, the macro skeleton with actual parameters substituted is inserted into the source input on the mass storage device.

The source input is copied onto the mass storage device.

Sequence numbers of the input source images are checked.

## Pass 2

Each source image on the mass storage device is read and pass  $2\ \mathrm{errors}$  are listed as they occur.

Conditional assembly pseudo instructions are processed.

Symbol and external tables are built.

#### Pass 3

Each image is read and pass 3 errors are listed.

List and relocatable binary output are generated according to the input options.

## TABLST

TABLST prints and punches the entry points and external images. The transfer image is punched.

An EOF image is output to the next load-and-go sector on mass storage.

A symbol table listing is given.

60361900A iii

## XREF

XREF creates and prints the cross-references lists.

Refer to the 1700 Mass Storage Operating System (MSOS) 4 Reference Manual equipment configuration for the minimum hardware required by the Macro Assembler.

It is assumed that users of this manual are familiar with the 1700 MSOS.

Following is a list of 1700 MSOS manuals.

| Description                                                        | Pub. No. |

|--------------------------------------------------------------------|----------|

| 1700 MSOS 4 Reference Manual                                       | 60361500 |

| 1700 MSOS 4 Mass Storage FORTRAN<br>Version 3 A/B Reference Manual | 60362000 |

| 1700 MSOS 4 Computer System Codes                                  | 60163500 |

| 1700 MSOS 4 Macro Assembler<br>General Information                 | 39519800 |

| 1700 MSOS 4 Mass Storage FORTRAN<br>General Information            | 39519900 |

| 1700 MSOS 4 Small Computer Maintenance<br>Monitor Reference Manual | 39520200 |

| 1700 MSOS 4 Instant                                                | 39520500 |

| 1700 MSOS 4 File Manager Version 1<br>Reference Manual             | 39520600 |

| 1700 MSOS 4 Release Bulletin                                       | 39520800 |

| 1700 MSOS 4 Installation Handbook                                  | 39520900 |

| 1700 MSOS 4 Small Computer Maintenance<br>Monitor Instant          | 39521700 |

| 1700 MSOS 4 Ordering Bulletin                                      | 39521900 |

| 1700 MSOS 4 General Information                                    | 39522400 |

# **CONTENTS**

|           | PREFACE                                                                                                                                                                                                                                                                                                                                                                                                                            | iii                                                                                                 |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| CHAPTER 1 | INSTRUCTION FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                     |  |

|           | 1.1 Source Program 1.2 Source Statement 1.2.1 Location Field 1.2.1 Remarks 1.2.3 Instruction 1.2.4 Address Field 1.2.5 Comment Field 1.2.6 Sequence Field                                                                                                                                                                                                                                                                          | 1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-8                                                       |  |

| CHAPTER 2 | MACHINE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                               | 2-1                                                                                                 |  |

|           | 2.1 Storage Reference Instructions 2.1.1 Address Modes 2.1.2 Absolute Addressing 2.1.3 Relative Addressing 2.1.4 Constant Addressing 2.1.5 Data Transmission Instructions 2.1.6 Arithmetic Instructions 2.1.7 Logical Instructions 2.1.8 Jump Instructions 2.1.8 Jump Instructions 2.2 Register Reference Instructions 2.3 Inter-Register Instructions 2.4 Shift Instructions 2.5 Skip Instructions 2.6 Negative Zero/Overflow Set | 2-1<br>2-1<br>3-3<br>2-4<br>2-6<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-12<br>2-14<br>2-15<br>2-16 |  |

| CHAPTER 3 | PSEUDO INSTRUCTIONS  3.1 Subprogram Linkage 3.1.1 NAM 3.1.2 END 3.1.3 ENT 3.1.4 EXT/EXT*                                                                                                                                                                                                                                                                                                                                           | 3-1<br>3-1<br>3-1<br>3-1<br>3-2<br>3-2                                                              |  |

|           | 3.2 Data Storage 3.2.1 BSS 3.2.2 BZS 3.2.3 COM                                                                                                                                                                                                                                                                                                                                                                                     | 3-4<br>3-4<br>3-4<br>3-5<br>3-6                                                                     |  |

|           | 3.3 Constant Declarations 3.3.1 ADC/ADC* 3.3.2 ALF 3.3.3 NUM 3.3.4 DEC 3.3.5 VFD                                                                                                                                                                                                                                                                                                                                                   | 3-7<br>3-7<br>3-7<br>3-9<br>3-10<br>3-11                                                            |  |

|           | 3.4 Assembler Control 3.4.1 EQU 3.4.2 ORG/ORG*                                                                                                                                                                                                                                                                                                                                                                                     | 3-13<br>3-13<br>3-14                                                                                |  |

60361900B v

|            | 3.4.3 IFA 3.4.4 EIF 3.4.5 OPT 3.4.6 MON 3.5 Listing Control 3.5.1 NLS 3.5.2 LST 3.5.3 SPC 3.5.4 EJT                                                                                              | 3-15<br>3-16<br>3-17<br>3-18<br>3-18<br>3-18<br>3-18<br>3-18       |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| CHAPTER 4  | MACROS                                                                                                                                                                                           | 4-1                                                                |

|            | 4.1 Macro Pseudo Instructions 4.1.1 MAC 4.1.2 EMC 4.1.3 LOC 4.1.4 IFC 4.2 Macro Skeleton 4.3 Macro Instruction 4.3.1 Parameters 4.4 Macro Library                                                | 4-1<br>4-1<br>4-2<br>4-2<br>4-2<br>4-3<br>4-4<br>4-4               |

| CHAPTER 5  | ASSEMBLER OUTPUT                                                                                                                                                                                 | 5-1                                                                |

|            | 5.1 Control Options 5.1.1 P Option 5.1.2 X Option 5.1.3 L Option 5.1.4 C Option 5.2 Assembly Listing 5.2.1 Error Listing 5.2.2 Cross-Reference Listing 5.2.3 Sample Program 5.2.4 Sample Listing | 5-1<br>5-1<br>5-1<br>5-1<br>5-1<br>5-2<br>5-2<br>5-3<br>5-4<br>5-4 |

| APPENDIX A | MNEMONIC INSTRUCTION CODES                                                                                                                                                                       | A - 1                                                              |

| APPENDIX B | PROGRAMMING CONSIDERATIONS                                                                                                                                                                       | B-1                                                                |

| APPENDIX C | ASCII CODES                                                                                                                                                                                      | C-1                                                                |

| APPENDIX D | MACRO ASSEMBLER ERRORS                                                                                                                                                                           | D-1                                                                |

60361900B

#### 1.1 SOURCE PROGRAM

The number of independent subprograms comprising a source program is limited only by available space. Each subprogram may be assembled independently, or several may be assembled as a group. The main subprogram of a group is the one to which initial control is given; it need not be the first subprogram. The last subprogram of a group must be followed by the MON pseudo instruction indicating the end of assembly and return to the operating system.

Communication between subprograms is effected by the subprogram linkage pseudo instructions and by the use of common and data storage.

At execution time, the entry point named in the END pseudo instruction specifies the entry point to which initial control passes. A jump to the dispatcher or an exit request (1700 MSOS Reference Manual) signals return of control to the operating system upon job completion. EXIT or a jump to the dispatcher must be the last statement to be executed.

## 1.2 SOURCE STATEMENT

A source statement consists of location, instructions, address, remarks, and sequence fields. The first four fields may not exceed 72 characters; within that limitation they are free field. The sequence field is used when the source image is 80 characters; it is restricted to columns 73 through 80.

Each field is terminated by a tab (\$B; paper tape only), carriage return (end of statement mark), or blanks. Any number of blanks may separate fields. A carriage return is always the end of statement mark on paper tape.

## 1.2.1 LOCATION FIELD

The location field of a source statement must begin in column 1.

This field is used to specify a labeled (label starting in column 1) or an unlabeled (blank or tab in column 1) statement.

The statement label is a symbolic name consisting of from 1 to 6 alphanumeric characters; the first must be alphabetic. Characters in excess of six are ignored. A 2-character name makes the most efficient use of storage and assembly time.

#### Examples:

| LOOP1    | Legal                               |

|----------|-------------------------------------|

| 123456   | Illegal; first character is numeric |

| P1       | Legal                               |

| A 123456 | Legal; only A12345 is processed     |

#### 1.2.2 REMARKS

An asterisk in column 1 of the location field specifies that the source statement is a remark. Comments, written in columns 2 through 72, are printed with the assembly list output but have no effect on the object program. An asterisk elsewhere in the location field is illegal. Remarks may also follow the address field of any instruction. There must be at least one blank separating the address field from the remarks.

#### 1.2.3 INSTRUCTION

This field begins to the right of the location field and must be separated from it by at least 1 blank character or a tab. If the location field contains no label (blank or tab on column 1), the operation code may begin in column 2.

The operation code field contains the three-letter instruction codes for machine and pseudo instructions; or it contains macro instructions which may be up to 6 characters. Certain instructions may be followed by a 1-character terminator.

The mnemonic instruction codes listed in Appendix A are described in the 1700 Computer Reference Manual.

#### 1.2.4 ADDRESS FIELD

The address field begins to the right of the operation code field, separated from it by at least 1 blank character or a tab. It is terminated by a blank or tab, or by the 72nd character of the source statement. Exceptions are the macro instructions which may have a continuation line and the pseudo instruction ALF (section 3.3.2).

This field contains an address expression consisting of an operand or string of operands joined by arithmetic operators; or it may contain a series of operands separated by commas. An operand may be any of the following:

Symbolic name

Numeric constant

One of the special characters: \* A Q M 0 I B

#### Symbolic Operand

A symbolic name used as an operand in the address field must be defined in one of the following ways.

Label in the location field of any machine instruction

Label in the location field of any macro instruction

Label in the location field of constant declaration pseudo instructions: ADC, ALF, NUM, DEC, VFD

Symbolic name in the address field of the pseudo instructions: EXT, COM, DAT, BSS, BZS, EQU

1-2 60361900B

A defined symbolic name references a specific location in memory. It may be relocatable or absolute. A relocatable symbol refers to a location that may be relocated during loading.

Storage is divided into three areas: program, data, and common. These areas are defined at assembly time and the initial location of each is set to a relocation address of zero. The object code produced by the assembler contains addresses which are modified by a relocation factor to produce the actual address in memory.

A symbol is program relocatable if it references a location in the subprogram, data relocatable if it references a location in data storage, and common relocatable if it references a location in common storage. All other symbols are absolute. A symbol is made absolute by equating it to a number, an arithmetic expression, or another absolute symbol.

In all cases a symbolic label and a symbol defined by BSS or BZS take the relocation and value of the current location counter. The location counter of a program is originally program relocatable, however, its relocation may be changed by the ORG instruction.

An address expression which includes more than one operand must reference only one relocatable area. Terms of different relocation types must reduce to one relocatable area or to an absolute address. When the address mode of an instruction is made one-word relative by an asterisk terminator, the relocation type of the address expression must agree with the type of the current location counter.

A symbolic operand may be preceded by a plus or a minus sign. If preceded by a plus or no sign, the symbol refers to its associated value; if preceded by a minus, the symbol refers to the ones complement of its associated value. When an expression contains more than one symbol, the final sign of the expression is the algebraic sum of the operands.

#### Example:

RT relocation type of current location counter: P program relocatable, C common relocatable, D data relocatable, and A absolute address.

| $\frac{RT}{}$ | <u>Label</u> | <u>Operation</u>  | Address                                                            |

|---------------|--------------|-------------------|--------------------------------------------------------------------|

|               |              | COM<br>DAT<br>EQU | COM1, COM2<br>DAT1, DAT2<br>D(1), E(3), G(E-D), H(\$1000), I(DAT1) |

| P             |              | BZS               | A, B, C                                                            |

| P             |              | BZS               | J, K(10)                                                           |

The symbols D, E, G, and H are absolute; DAT1, DAT2, and I are data relocatable; COM1 and COM2 are common relocatable; A, B, C, J, and K are program relocatable.

| P | START | ADC  | 0     |         |

|---|-------|------|-------|---------|

| P |       | LDA* | START |         |

| Р |       | STA* | DAT1  | (Error) |

| P |       | STA* | COM1  | (Error) |

60361900A 1-3

The errors resulted because the relocation types of the symbols in the address field do not match that of the location counter, and the one-word relative address mode was requested by an asterisk terminator.

| $\frac{RT}{}$ | <u>Label</u> | <u>Operation</u> | Address        |

|---------------|--------------|------------------|----------------|

| P             |              | LDA+             | (Not an error) |

Relocations need not match when mode is two-word absolute.

P LDA START (O.K., relocations match)

P LDA COM1 (Not an error)

Assembler changes this instruction to two-word absolute because relocations do not match, but no error is indicated.

P LDA COM2-DAT1+COM1-D+E-COM2+START-K+DAT2

This address expression results in a common relocation type; all other relocations cancel out (refer to address expressions).

ORG DAT1

ORG changes the relocation of the location counter to data.

D LDA\* START (Error)

D STA\* DAT2+9

ORG\*

ORG\* returns the location counter to original relocation.

| LDA*            | START                                       | (Not an error)                                     |

|-----------------|---------------------------------------------|----------------------------------------------------|

| ORG             | H                                           |                                                    |

| $\mathtt{LDA}*$ | START                                       | (Error)                                            |

| STA*            | DAT1                                        | (Error)                                            |

| LDA*            | \$1001                                      |                                                    |

| STA-            | В                                           |                                                    |

| ORG *           |                                             |                                                    |

| END             |                                             |                                                    |

|                 | ORG<br>LDA*<br>STA*<br>LDA*<br>STA-<br>ORG* | ORG H LDA* START STA* DAT1 LDA* \$1001 STA- B ORG* |

#### Numeric Operand

A numeric operand in the address field may be decimal or hexadecimal. A decimal number is represented by up to five decimal digits and must be within the range  $\pm 32767$ . A hexadecimal number is represented by a dollar sign and not more than four hexadecimal digits in the range  $\pm 7FFF$ . (Hexadecimal operands in the NUM pseudo instruction may be in the range  $\pm FFFF$ .)

Numeric operands in the address field may be preceded by a plus or a minus sign. If a plus or no sign is specified, the binary equivalent of the number is the value used; a minus means the one's complement of the binary equivalent is the value.

A numeric operand has no relocation type; it is always absolute.

## Address Expression

An address expression may be a single operand or a string of operands joined by the following arithmetic operators.

- + Addition

- Subtraction

- \* Multiplication

- / Division

Arithmetic operators may not follow each other without an intervening operand. Parentheses are not permitted for grouping terms.

The asterisk has an additional meaning as an operand. When it is used as the multiplication operator (refer to special characters), it must be immediately preceded by an operand which may be another asterisk. When the asterisk is used as an operator, only one of its associated operands may be relocatable.

The slash, used as the division operator, must be between two operands. The operand which follows may not be zero or relocatable.

An external name may be used in an address expression only as a single operand. Arithmetic operators preceding or following an external operand are illegal.

#### Example:

The first asterisk in the LDA instruction refers to the value of the current location counter.

The following instructions are illegal assuming the same pseudo instructions precede the START.

| START | LDA | D-C**5+2 | *5 has no intervening operator  |

|-------|-----|----------|---------------------------------|

|       | ADD | A-2/B    | Division by relocatable operand |

|       | ADD | E*F      | Both operands are relocatable   |

|       | STA | G+5      | An external must stand alone    |

60361900A 1-5

The hierarchy for the evaluation of arithmetic expressions is:

/ or \* Evaluated first + or - Evaluated next

Expressions containing operators at the same level are evaluated from left to right. The expression

A/B+C\*D

is evaluated algrebraically as

A/B+(C)(D)

and not as any of the following:

$$\frac{(A)(D)}{B+C}$$

$\frac{A}{(B+C)(D)}$   $\frac{A}{B+(C)(D)}$

Parentheses may not be used for grouping operands. The algrebraic expression

$$(A-D)(B+C/E)$$

must be specified

$$A*B+A*C/E-D*B-D*C/E$$

The following expression is illegal.

$$(A-D)*(B+C/E)$$

Division in an address expression always yields a truncated result; thus, 11/3=3. The expression A\*B/C may result in a value different from B/C\*A. For example, if A=4, B=3, and C=2 then

$$A*B/C=4*3/2=6$$

but

B/C\*A=3/2\*4=4

All expressions are evaluated modulo  $2^{15}$ -1. An address expression consisting solely of numeric operands is absolute. If an expression contains symbolic operands, the final relocation for the expression is determined by the relocations of the symbolic operands. If the relocation of the operands is expressed by the following terms, the final relocation is the algebraic sum of the relocation terms.

- ±P Positive or negative program relocation

- ±C Positive or negative common relocation

- ±D Positive or negative data relocation

The relocation must reduce to one of the relocation terms or to zero. If zero, the location is absolute.

1-6 60361900A

#### Example:

| Source Statements |                                  |                | Relocation Formula         |

|-------------------|----------------------------------|----------------|----------------------------|

|                   | COM                              | А, В           |                            |

|                   | DAT                              | C, D           |                            |

|                   | $\mathbf{E}\mathbf{Q}\mathbf{U}$ | E(1), F(D)     |                            |

| STRT              | LDA                              | B+C-E*2-A-D    | +C+D-C-D=0 (absolute)      |

|                   | LDA                              | B+D-F+STRT-A-C | +C+D-D+P-C-D=P-D (illegal) |

|                   | LDA                              | B+D-E+STRT-A-C | +C+D+P-C-D=P (program)     |

|                   | LDA                              | B-D-A          | +C-D-C=-D (negative data)  |

## Special Characters

Special characters may be used as operands in the address field of a source statement. Their definition may not be changed by the user. The three classes of special characters are storage, register, and index.

| Class    |   | Character        | Referenced Location                                                               |

|----------|---|------------------|-----------------------------------------------------------------------------------|

| Storage  | { | *<br>I           | Current location counter Location FF <sub>16</sub>                                |

| Register | { | A<br>Q<br>M<br>0 | A register<br>Q register<br>Mask register<br>Destination registers                |

| Index    | { | Q<br>I<br>B      | Index 1, Q register<br>Index 2, location FF <sub>16</sub><br>Index 1 plus index 2 |

Storage class characters (\*, I) reference storage locations. The asterisk refers to the location of the current instruction. For a word instruction, an asterisk references the location of the first word. Special character I refers to location  $FF_{16}$ . I is the only indexing character that may stand alone as an operand with storage reference instructions. It may not be defined as a location symbol in a program.

The register class characters (A, Q, M, and 0) are used only with inter-register transfer instructions. They refer to the A, Q, and M (mask) registers. Character 0 sets the destination registers to zero (section 2.5).

## Examples:

| Instruction | <u>Function</u>                                                  |

|-------------|------------------------------------------------------------------|

| SET A,Q,M   | Set A, Q, and mask registers to ones                             |

| TRA Q       | Transfer contents of A register to Q register                    |

| LAM M       | Transfer logical product of A and mask register to mask register |

60361900A 1-7

Index class characters (Q, I, and B) are used in conjunction with an address expression to refer to the index registers. Any one character may follow an address expression; it is separated from the expression by a comma with no intervening blank. Indexing may be used only with storage reference instructions.

- Q Contents of Q register are added to contents of the expression to form the actual address

- I Contents of location FF<sub>16</sub> are added to contents of address expression to form the actual address

- B Contents of Q register are added to address expression and this sum is added to contents of  $FF_{16}$  to produce the actual address

#### Examples:

| Address Field |         | <u>Function</u>                                                                                                                                             |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOC1, B       | Legal   | Contents of registers $Q$ and $FF_{16}$ and the contents of LOC1 are added to produce the actual address                                                    |

| ,,I           | Illegal | Character following first comma is assumed to be index character                                                                                            |

| TAG2,Q,I      | Illegal | Only one index notation allowed                                                                                                                             |

| Q             | Illegal | Unless $Q$ has been previously defined as a location symbol or is being used with the inter-register transfer instruction, it must follow a location symbol |

| TAG3,I        | Legal   | Contents of ${\rm FF}_{16}$ and ${\rm TAG}_3$ are added to produce the actual address                                                                       |

## 1.2.5 COMMENT FIELD

The address field is followed by the comment field which is used for remarks. Remarks do not affect the object code, but are printed as part of the list output. The comment field terminates at column 72, or with a carriage return (paper tape). Blanks are permitted in the comment field.

## 1.2.6 SEQUENCE FIELD

When the input image is 80 characters, columns 73 through 80 are available for sequencing; 73 through 75 may be used for program identification, 76 through 80 for a sequence number.

Sequence numbers are checked for errors only if the input image is 80 characters. Each sequence number must be greater than or equal to the previous sequence number. The value of a character in the sequence number is in ASCII code except that a blank is treated as zero.

Machine instructions represented by a three-letter mnemonic code are divided into six classes.

| Group A  | storage reference | Shift                   |

|----------|-------------------|-------------------------|

| Group B  | storage reference | Skip                    |

| Register | reference         | Inter-register transfer |

Storage reference instructions result in one or two machine words, depending on modification. Other machine instructions result in one machine word.

The function of each machine instruction is discussed in detail in the 1700 Computer Reference Manual. Appendix A lists the machine instructions in the order in which they are discussed in this chapter.

## 2.1 STORAGE REFERENCE INSTRUCTIONS

Group A and B storage reference instructions use storage addresses as operands or as operand addresses. Group B instructions include jump instructions and may not use the constant mode of addressing.

## 2.1.1 ADDRESS MODES

Group A storage reference instructions allow three modes of addressing: absolute, relative, and constant. Group B does not allow the use of the constant mode, but is otherwise the same as Group A.

Special characters designate the mode of addressing, the number of words for the instruction, and indirect addressing.

| Character | Description                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| *         | Asterisk as the last character of operation code specifies relative addressing in a one-word instruction                                   |

| -         | Minus as the last character of operation code specifies absolute addressing in a one-word instruction                                      |

| +         | Plus as the last character of operation code specifies absolute addressing in a two-word instruction                                       |

| =         | Equal sign as the first character in address field preceding a constant indicates constant addressing; the instruction is always two words |

| ()        | Parentheses enclosing the address expression indicate indirect addressing                                                                  |

If no character is specified as a terminator to the operation code, two-word relative addressing is assumed with the following exceptions.

- 1. If a constant is specified, the constant mode is assumed.

- 2. If the relocation type of the address expression differs from the relocation type of the location counter, two-word absolute addressing is assumed.

- 3. If a nonrelative external is referenced, absolute addressing is assumed.

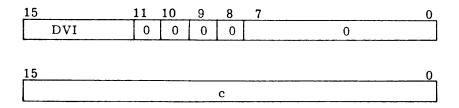

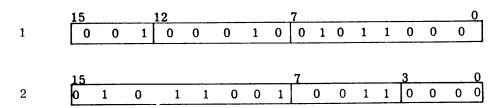

The machine language format resulting from a storage reference instruction is illustrated as follows.

#### First word:

| 15 | 11 | 10 | 9 | 8 | 7 | 0   |

|----|----|----|---|---|---|-----|

| f  | r  | d  | q | i | Δ | · ] |

- f 4-bit operation code is described in 1700 Computer Reference Manual

- r Specifies relative addressing

- d Specifies indirect addressing

- q Index register 1 flag; specifies adding contents of Q register to address

- i Index register 2 flag; specifies adding contents of storage register  ${\rm FF}_{16}$  to address

- $\Delta$  8-bit field; may be relative or absolute address for one-word instructions. When zero, indicates two-word instruction.

Second word (when used):

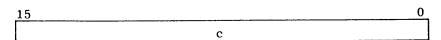

c 16-bit field for constant addressing or relative address. When it contains relative address, bit 15 is the sign.

- b Indirect address bit

- m Memory address

Address expressions are evaluated modulo  $2^{15}-1$ .

## 2.1.2 ABSOLUTE ADDRESSING

The value of the address expression of a one-word absolute instruction must be non-relocatable. The evaluated result is stored in 8 bits of the machine word. If this value is greater than 256, it is flagged as an error. If the 8-bit  $\Delta$  field is zero, two machine words are assumed regardless of the operation code terminator; no error message is printed. If the address expression is enclosed in parentheses for indirect addressing, bit 10 of the first word is set to 1.

Examples:

One Word, Direct

Instruction:

LDA-

Machine Word:

| 15  | 11 | 10 | 9 | 8 | 7 | ) |

|-----|----|----|---|---|---|---|

| LDA | 0  | 0  | 0 | 0 | е | ٦ |

One Word, Indirect

Instruction:

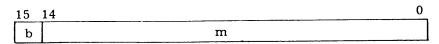

ADQ- (e)

Machine Word:

The value of the address expression of a two-word absolute instruction is stored in the least significant bits of the second word. If the expression is enclosed in parentheses for indirect addressing, bit 15 of the second word is set to 1. The indirect address bit 10 in the first word is always set to 1 when two-word absolute addressing is specified whether the address expression is specified as indirect or direct. This indicates that the address expression is in the second word. The 8-bit  $\triangle$  field of the first word is set to zero for two-word instructions.

Examples:

Two Word, Direct

Instruction:

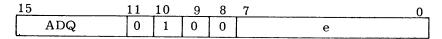

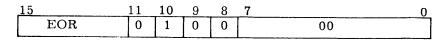

EOR+ e

Machine Words:

## Two Word, Indirect

Instruction:

AND+ (e)

Machine Words:

| 15  | 11 | 10 | 9 | 8 | 7  | 0 |

|-----|----|----|---|---|----|---|

| AND | 0  | 1  | 0 | 0 | 00 |   |

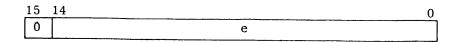

| 15 | 14 |   | 0_ |

|----|----|---|----|

| 1  |    | е |    |

## 2.1.3 RELATIVE ADDRESSING

When one-word relative addressing is specified, the value of the current location counter is subtracted (16-bit ones complement arithmetic) from the evaluated address expression. The result is placed in the 8-bit  $\Delta$  field. If the value of the result is outside the range  $\pm 7F_{16}$ , an error condition is flagged. An error condition is also flagged if the relocation type of the address expression differs from that of the location counter. If the 8-bit  $\Delta$  field is zero, two words are assumed regardless of the operation code terminator. No error message is printed for this condition.

## Examples:

#### One Word, Direct

Instruction:

AND\* e

Machine Word:

| 15  | 11 | 10 | 9 | 8 | 7 | 0,  |

|-----|----|----|---|---|---|-----|

| AND | 1  | 0  | 0 | 0 |   | e-* |

## One Word, Indirect

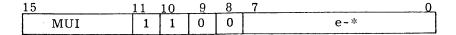

Instruction:

MUI\* (e)

Machine Word:

In the expression e-\* the asterisk indicates the value of the current location counter.

When a two-word instruction is specified, the value of the current location counter plus one is subtracted (using 16-bit 1's complement arithmetic) from the value of the address expression to obtain the 16-bit second word. If the relocation type of the address expression differs from that of the location counter and the address does not reference an external, the assembler forces a two-word absolute instruction. If the address expression is an external reference, the instruction is absolute or relative depending on the definition of the external.

#### Examples:

## Two Word, Direct

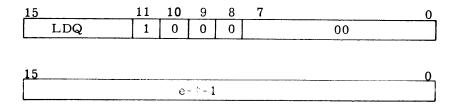

Instruction:

LDQ 6

Machine Words:

## Two Word, Indirect

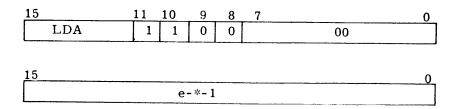

Instruction:

LDA (e)

Machine Words:

In the expression, e-\*-1, the asterisk indicates the value of the current location counter.

#### 2.1.4 CONSTANT ADDRESSING

Constant addressing may be used only for Group A storage reference instructions. Constants in the address field are preceded by an equal sign and a one-letter code. A constant may be one of the following:

|      | Code   | Type     | Meaning                                                             |

|------|--------|----------|---------------------------------------------------------------------|

|      | A      | aa       | 2 alphanumeric characters                                           |

|      | N      | ± ddddd  | 5-digit decimal number with or without a leading sign               |

|      | N      | ±\$hhhh  | 4-digit hexadecimal number preceded by $$$ , with or without a sign |

|      | X      | e        | Address expression evaluated modulo $2^{15}$ -1                     |

|      | X      | (e)      | Address expression evaluated modulo $2^{15}$ -1, with bit 15 set    |

| Exar | mples: |          |                                                                     |

|      | DVI    | =N\$1000 | (Hexadecimal constant)                                              |

|      | ADD    | =N-12345 | (Decimal constant)                                                  |

|      | LDA    | =AXY     | (ASCII constant)                                                    |

|      | AND    | =XTAG1+5 | (Address expression constant)                                       |

An instruction containing a constant in the address field results in two machine words.

## Example:

Instruction:

DVI =nc

(n is the code, c is the constant)

Machine Words:

## 2.1.5 DATA TRANSMISSION INSTRUCTIONS

STQ (F=4) Store Q. Store the contents of the Q register in the storage location specified by the effective address. The contents of Q are not altered.

STA (F=6) Store A. Store the contents of the A register in the storage location specified by the effective address. The contents of A are not altered.

- SPA (F = 7) Store A, Parity to A. Store the contents of the A register in the storage location specified by the effective address. Clear A if the number of 1 bits in A is odd. Set A equal to 0001<sub>16</sub> if the number of 1 bits in A is even. The contents of A are not altered if the write into storage is aborted because of parity error or protect fault.

- LDA (F = C) Load A. Load the A register with the contents of the storage location specified by the effective address. The contents of the storage location are not altered.

- LDQ (F = E) Load Q. Load the Q register with the contents of the storage location specified by the effective address. The contents of the storage location are not altered.

#### 2.1.6 ARITHMETIC INSTRUCTIONS

All the following arithmetic operations use one's complement arithmetic.

- MUI (F = 2) Multiply Integer. Multiply the contents of the storage location, specified by the effective address, by the contents of the A register. The 32-bit product replaces the contents of Q and A, the most significant bits of the product in the Q register.

- DVI (F = 3) Divide Integer. Divide the combined contents of the Q and A registers by the contents of the effective address. The Q register contains the most significant bits before fividing. If a 16-bit dividend is loaded into A, the sign bit of A must be extended throughout Q. The quotient is in the A register and the remainder is in the Q register at the end of the divide operation.

The OVERFLOW indicator is set if the magnitude of the quotient is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

ADD (F = 8)  $\frac{\text{Add to A.}}{\text{effective}}$  Add the contents of the storage location, specified by the

The OVERFLOW indicator is set if the magnitude of the sum is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

- SUB (F = 9) Subtract From A. Subtract the contents of the storage location, specified by the effective address, from the contents of the A register. Operation on overflow is the same as for an Add to A instruction.

- RAO (F = D) Replace Add One in Storage. Add one to the contents of the storage location specified by the effective address. The contents of A are not altered. Operation on overflow is the same as for an Add to A instruction.

- ADQ (F = F) Add to Q. Add the contents of the storage location, specified by the effective address, to the contents of the Q register. Operation on overflow is the same as for an Add to A instruction.

60316900B 2-7

#### 2.1.7 LOGICAL INSTRUCTIONS

The AND (AND with A) instruction achieves its results by forming a logical product. A logical product is a bit-by-bit multiplication of two binary numbers according to the following rules:

$$0 \times 0 = 0$$

$1 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 1 = 1$

Example:

0011 Operand A

x 0101 Operand B

0001 Logical Product

A logical product is used, in many cases, to select only specific portions of an operand for use in some operation. For example, if only a specific portion of an operand in storage is to be entered into the A register, the operand is subjected to a mask in A. This mask is composed of a predetermined pattern of 0s and 1s. Executing the AND instruction causes the operand to retain its original contents only in those bits which have 1s in the mask in A.

The EOR (Exclusive OR with A) instruction achieves its result by forming an exclusive OR. Executing the EOR instruction causes the operand to complement its original contents only in those bits which have 1s in the mask in A. An exclusive OR is a bit-by-bit logical subtraction of two binary numbers according to the following rules:

#### Exclusive OR

| <u>A</u> | $\mathbf{\underline{B}}$ | A <b>→</b> B |

|----------|--------------------------|--------------|

| 1        | 1                        | 0            |

| 1        | 0                        | 1            |

| 0        | 1                        | 1            |

| 0        | 0                        | 0            |

Example:

- AND (F = A)  $\frac{\text{AND with A.}}{\text{the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.$

- EOR (F = B) Exclusive OR with A. Form the logical difference (exclusive OR), bit-by-bit, of the contents of the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.

#### 2.1.8 JUMP INSTRUCTIONS

A Jump (JMP) instruction causes a current program sequence to terminate and initiates a new sequence at a different location in storage. The program address register, P, provides continuity between program instructions and always contains the storage location of the current instruction in the program.

When a Jump instruction occurs, P is cleared and a new address is entered.\* In the Jump instruction, the effective address specifies the beginning address of the new program sequence. The word at the effective address is read from storage and interpreted as the first instruction of the new sequence.

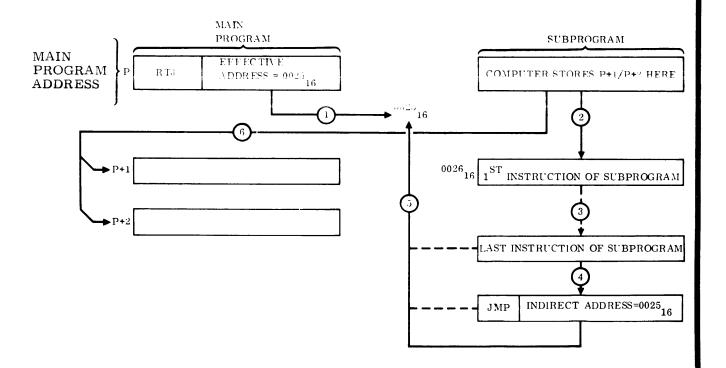

A Return Jump (RTJ) instruction enables the computer to leave the main program, jump to some subprogram, execute the subprogram, and return to the main program via another instruction. The Return Jump provides the computer with the necessary information to enable returning to the main program. Figure 2-1 shows how a Return Jump instruction can be used.

Figure 2-1. Program Using Return Jump Instruction

60361900B 2-9

<sup>\*</sup>Jumps or return jumps from unprotected to protected storage cause a fault, but the address that is saved in the trap location is the destination address (i.e., the address of the next sequential main program instruction).

A Return Jump instruction is executed at main program address P. The computer jumps to effective address  $0025_{16}$  and stores P+1 or P+2 (depending on the address mode of RTJ) at this location. Then the program address counter P is set to  $0026_{16}$  and the computer starts executing the subprogram. At the end of the subprogram, the computer executes a Jump instruction (JMP) with indirect addressing. This causes the computer to jump to the address specified by the subprogram address  $0025_{16}$  (P+1 or P+2 of the main program). Now main program execution continues at P+1 or P+2.

- JMP (F = 1) Jump. Jump to the address specified by the effective address. This effectively replaces the contents of program address counter P with the effective address specified in the Jump instruction.

- RTJ (F = 5) Return Jump. Replace the contents of the storage location specified by the effective address with the address of the next consecutive instruction. The address stored in the effective address is P + 1 or P + 2, depending on the addressing mode of RTJ. The contents of P are then replaced with the effective address plus one.

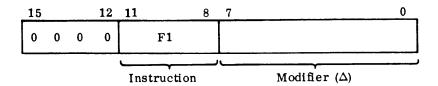

## 2.2 REGISTER REFERENCE INSTRUCTIONS

Register reference instructions use the address mode field for the operation code. Register reference instructions are identified when the upper four bits (15 through 12) of an instruction are 0s.

Format:

- SLS (F1=0) Selective Stop. Stops the computer if this instruction is executed when the selective stop switch is on. On restart, the computer executes the instruction at P+1. This becomes a Pass instruction when the selective stop switch is off.

- INP (F1=2) Input to A. Reads one word from an external device into the A register. The word in the Q register selects the sending device. If the device sends a Reply, the next instruction comes from P+1. If the device sends a Reject, the next instruction comes from P+1+ $\Delta$ , where delta is an eight-bit signed number. If an internal Reject occurs, the next instruction comes from P+ $\Delta$ . Refer to the 1700 Computer Reference Manual.

- OUT (F1=3) Output from A. Outputs one word from the A register to an external device. The word in the Q register selects the receiving device. If the device sends a Reply, the next instruction comes from P+1. If the device sends a Reject, the next instruction comes from P+1+  $\Delta$ , where delta is an eight-bit signed number. If an internal Reject occurs, the next instruction comes from P+ $\Delta$ . Refer to the 1700 Computer Reference Manual.

- INA (F1 = 9) Increase A. Replaces the contents of A with the sum of the initial contents of A and delta, where delta is treated as a signed number with the sign extended into the upper eight bits. Operation on overflow is the same as for an Add to A instruction.

- ENA (F1=A) Enter A. Replaces the contents of the A register with the eight-bit delta, sign extended.

- NOP (F1=B) No Operation. This is a Pass instruction (no operation is performed).  $\overline{\text{Compares to Selective Stop instruction with the STOP switch off.}$

- ENQ (F1=C) Enter Q. Replaces the contents of the Q register with the eight-bit delta, sign extended.

- INQ (F1=D) Increase Q. Replaces the contents of Q with the sum of the initial contents of Q and delta, where delta is treated as a signed number with the sign extended into the upper eight bits. Operation on overflow is the same as for an Add to A instruction.

The following instructions (F1 equals 4, 5, 6, 7, or E) are legal only if the program protect switch is off or if the instructions themselves are protected (refer to the 1700 Computer Reference Manual). If an instruction is illegal, it becomes a selective stop and an interrupt on program protect fault is possible (if selected).

- Protect switch on Selective stop unless instruction is protected

- Protect switch off Normal instruction execution (no program protection)

- EIN (F1=4) Enable Interrupt. Activates the interrupt system after one instruction following EIN has been executed. The interrupt system must be active and the appropriate mask bit set for an interrupt to be recognized.

- IIN (F1=5) Inhibit Interrupt. Deactivates the interrupt system. If interrupt occurs during execution of this instruction, the interrupt is not recognized until one instruction after the next EIN instruction is executed.

- SPB (F1=6) Set Program Protect Bit. Sets the program protect bit in the address specified by Q.

- CPB (F1=7) Clear Program Protect Bit. Clears the program protect bit in the address specified by Q.

- EXI(F1 = E)Exit Interrupt State. This instruction must be used to exit from any interrupt state. Delta defines the interrupt state from which the exit is taken (see 1700 Computer Reference Manual). At the time an interrupt occurs, the value of P is stored in the interrupt trap location assigned to that particular interrupt state. This value is called the return address as it enables return to the next unexecuted instruction after interrupt processing. The EXI instruction automatically reads the address containing the return address, then jumps to the return address. In addition, if the computer is in 32K mode, this instruction also sets the OVERFLOW indicator to the state of bit 15 in the return address. This bit records the state of the OVERFLOW indicator when the interrupt occurred. In 65K mode this instruction does not reset the OVERFLOW indicator. Refer to the 1700 Computer Reference Manual for an explanation of the overflow condition in 65K mode.

60361900B 2-11

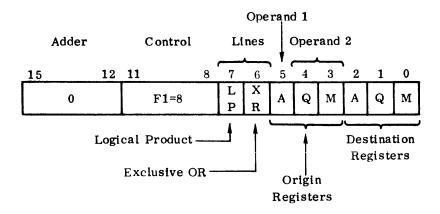

## 2.3 INTER-REGISTER INSTRUCTIONS

These instructions cause data from certain combinations of two origin registers to be sent through the adder to any combination of destination registers. Various operations, selected by the adder control lines, are performed on the data as it passes through the adder.

#### Format:

If bit 0 if an Inter-register instruction is set (M is the destination register) and the instruction is not protected, it is a program protect violation and becomes a non-protected Selective Stop instruction. The Program Protect Fault bit is set and interrupt occurs. See the 1700 Computer Reference Manual for additional information.

The origin registers are considered as operands. There are two kinds.

- Operand 1 may be:

- FFFF (bit 5 is 0) or

- The contents of A (bit 5 is 1)

- Operand 2 may be:

- FFFF (bit 4 is 0 and bit 3 is 0) or

- The contents of M (bit 4 is 0 and bit 3 is 1) or

- The contents of Q (bit 4 is 1 and bit 3 is 0) or

- The inclusive OR, bit-by-bit, of the contents of Q and M (bit 4 is 1 and bit 3 is 1)

The following operations are possible.

- Exclusive OR (LP = 0 and XR = 1) The data placed in the destination register(s) is the exclusive OR, bit-by-bit, of operand 1 and operand 2.

- Logical Product (LP = 1 and XR = 0) The data placed in the destination register(s) is the logical product, bit-by-bit, of operand 1 and operand 2.

- Complement Logical Product (LP = 1 and XR = 1) The data placed in the destination register(s) is the complement of the logical product, bit-by-bit, of operand 1 and operand 2.

2-12 60361900B

Arithmetic Sum (LP = 0 and XR = 0) - The data placed in the destination register(s) is the arithmetic sum of operand 1 and operand 2. The OVERFLOW indicator operates the same for an Add to A instruction.

#### INTER-REGISTER MNEMONICS

```

SET (F1 = 8, bits 7 through 3 = 10000)

Set to Ones

CLR (F1 = 8, bits 7 through 3 = 01000)

Clear to Zero

TRA (F1 = 8, bits 7 through 3 = 10100)

Transfer A*

TRM (F1 = 8, bits 7 through 3 = 10001)

Transfer M*

TRQ (F1 = 8, bits 7 through 3 = 10010)

Transfer Q*

TRB (F1 = 8, bits 7 through 3 = 10011)

Transfer Q + M*

TCA (F1 = 8, bits 7 through 3 = 01100)

Transfer Complement A*

TCM (F1 = 8, bits 7 through 3 = 01001)

Transfer Complement M*

TCQ (F1 = 8, bits 7 through 3 = 01010)

Transfer Complement Q*

TCB (F1 = 8, bits 7 through 3 = 01011)

Transfer Complement Q + M*

AAM (F1 = 8, bits 7 through 3 = 00101)

Transfer Arithmetic Sum A, M

AAQ (F1 = 8, bits 7 through 3 = 00110)

Transfer Arithmetic Sum A, Q

AAB (F1 = 8, bits 7 through 3 = 00111)

Transfer Arithmetic Sum A. Q + M

EAM (F1 = 8, bits 7 through 3 = 01101)

Transfer Exclusive OR A, M

EAQ (F1 = 8, bits 7 through 3 = 01110)

Transfer Exclusive OR A, Q

EAB (F1 = 8, bits 7 through 3 = 01111)

Transfer Exclusive OR A, Q + M

LAM (F1 = 8, bits 7 through 3 = 10101)

Transfer Logical Product A. M.

LAQ (F1 = 8, bits 7 through 3 = 10110)

Transfer Logical Product A, Q

LAB (F1 = 8, bits 7 through 3 = 10111)

Transfer Logical Product A, Q + M

CAM (F1 = 8, bits 7 through 3 = 11101)

Transfer Complement Logical Product A, M

CAQ (F1 = 8, bits 7 through 3 = 11110)

Transfer Complement Logical Product A. Q.

CAB (F1 = 8, bits 7 through 3 = 11111)

Transfer Complement Logical Product A, Q + M

```

Note: The "+" implies an inclusive OR.

60361900B 2-13

The use of bit 7 is optional; it may be a 1 or a 0. The assembler uses bit 7 = 0.

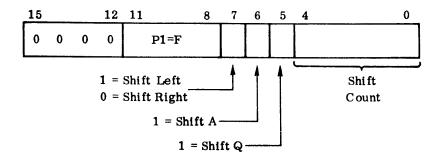

## 2.4 SHIFT INSTRUCTIONS

The Shift instructions shift A, Q, or QA left or right the number of places specified by the five-bit shift count. Right shifts are end-off with sign extension in the upper bits. Left shifts are end-around. The maximum long-right or long-left shift is 1F places.

Format:

Example: Shift A right two places - 0F42.

## SHIFT MNEMONICS

| ARS $(F1 = F, bits 7 through 5 = 010)$ A Right Shi | ARS | (F1 = | F. 1 | bits 7 | through | 5 = 010 | ) A | Right Shi |

|----------------------------------------------------|-----|-------|------|--------|---------|---------|-----|-----------|

|----------------------------------------------------|-----|-------|------|--------|---------|---------|-----|-----------|

ALS (F1 = F, bits 7 through

$$5 = 110$$

) A Left Shift

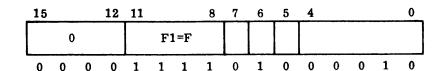

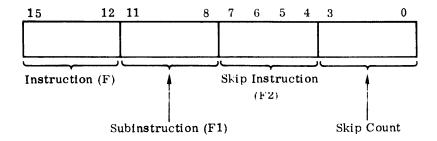

## 2.5 SKIP INSTRUCTIONS

Skip instructions result in one machine word: a 12-bit operation code and a 4-bit unsigned skip count. The first four bits of the operation code field are set to zero, the next four bits contain the skip instruction code 0001, and the last four bits contain a unique identifier, F2, for each skip instruction. The expression in the address field of the instruction is evaluated modulo  $2^{15}$ -1.

This expression may be absolute or relocatable. If absolute, the value of the expression is the skip count. If relocatable, the value of the skip count is obtained by subtracting (16-bit one's complement arithmetic) the value of the current location counter plus one from the expression. The skip count is then placed in the last four bits of the machine word. The final value of the skip count must not exceed four bits or an error message is printed. If the expression is relocatable, the relocation type of the expression must match the relocation type of the location counter or an error results.

#### Format:

When the skip condition is met, the skip count plus one is added to P to obtain the address of the next instruction (e.g., when the skip count is zero go to P+1). When the skip condition is not met, the address of the next instruction is P+1 (skip count ignored). The skip count does not have a sign bit.

| SAZ (F2 = 0) | Skip if A is positive zero (all bits are 0)         |

|--------------|-----------------------------------------------------|

| SAN (F2 = 1) | Skip if A is not positive zero (not all bits are 0) |

| SAP (F2 = 2) | Skip if A is positive (bit 15 is 0)                 |

| SAM (F2 = 3) | Skip is A is negative (bit 15 is 1)                 |

| SQZ (F2 = 4) | Skip if Q is positive zero (all bits are 0)         |

| SQN (F2 = 5) | Skip if Q is not positive zero (not all bits are 0) |

| SQP (F2 = 6) | Skip if Q is positive (bit 15 is 0)                 |

| SQM (F2 = 7) | Skip if Q is negative (bit 15 is 1)                 |

| SWS (F2 = 8) | Skip if selective skip switch is set                |

| SWN (F2 = 9) | Skip if selective skip switch is not set            |

60361900B 2-15

| SOV (I | F2 = A |

|--------|--------|

|--------|--------|

Skip on Overflow. This instructions skips if an overflow condition is sensed. This instruction clears the OVERFLOW indicator.

SNO (F2 = B)

Skip on No Overflow. This instruction skips if an overflow condition is not present. This instruction clears the OVERFLOW indicator.

SPE (F2 = C)

Skip on Storage Parity Error. This instruction skips if a storage parity error occurred; it clears the Storage Parity Error Interrupt signal and the PARITY FAULT indicator.

SNP (F2 = D)

Skip on No Storage Parity Error.

SPF (F2 = E)

Skip on Program Protect Fault. The program protect fault is set by:

- A nonprotected instruction attempting to write into an address that is protected.

- An attempt to execute a protected instruction immediately following a nonprotected instruction, unless an interrupt caused the instruction sequence.

- Execution of any nonprotected instruction affecting interrupt mask or enables.

The program protect fault is cleared when it is sensed by the SPF instruction. The program protect fault cannot be set if the program protect system is disabled. (Refer to the 1700 Computer Reference Manual.)

SNF (Fs = F)

Skip on No Program Protect Fault.

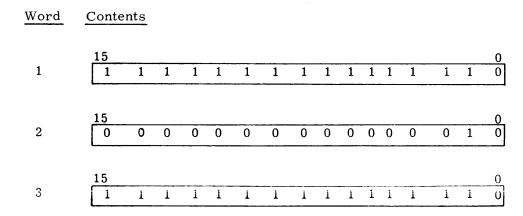

# 2.6 NEGATIVE ZERO/OVERFLOW SET

Negative zero and/or overflow set can be caused by two characteristics of the computer:

- The computer has a one's complement subtractive adder.

- Multiplication and division are done with positive numbers only. Therefore, a sign correction occurs, if required, before and after the multiplication or division symbols.

Arithmetic operation that produce a negative zero result and/or set overflow in the computer are:

Addition

$$(-0) + (-0) = (-0)$$

• Subtraction

$$(-0) - (+0) = (-0)$$

$$(+0) \times (-N) = (-0)$$

$$(-N) \times (+0) = (-0)$$

$$(-0) \times (+N) = (-0)$$

$$(+N) \times (-0) = (-0)$$

Where:

$$N \neq 0$$

$R = Remainder$

$$\frac{(+0)}{(-N)} = (-0), R = (+0)$$

$$\frac{(-0)}{(+N)} = (-0), R = (-0)$$

$$\frac{(-0)}{(-N)} = (+0), R = (-0)$$

$$\frac{(+N)}{(+0)}$$

= (-0), R = (+N) overflow set

$$\frac{(-N)}{(-0)}$$

= (-0), R = (-N) overflow set

$$\frac{(-2N)}{(+N)} = (-2), R = (-0)$$

$$\frac{(-2N)}{(-N)} = (+2), R = (-0)$$

$$\frac{(+0)}{(+0)}$$

= (-0), R = (+0) overflow set

$$\frac{(+0)}{(-0)}$$

= (+0), R = (+0) overflow set

$$\frac{(-0)}{(+0)}$$

= (+0), R = (-0) overflow set

$$\frac{(-0)}{(-0)}$$

= (-0), R = (-0) overflow set

Pseudo instructions control the assembler, provide subprogram linkage, control output listing, reserve storage, convert data, and so on.

Pseudo instructions may be placed anywhere in a source language subprogram. However, OPT or NAM must be the first statement of a subprogram and MON or END must be the last statement.

#### 3.1 SUBPROGRAM LINKAGE

These instructions identify and link subprograms; a symbolic name in the location field is ignored.

#### 3.1.1 NAM

NAM identifies a source language subprogram and must be the first statement of the subprogram. Only the assembler control pseudo instruction OPT (section 3.4.5) may precede it.

The format is

NAM s

s An optional symbolic name of the subprogram which is printed as part of the assembly list output.

#### 3.1.2 END

END must be the last statement of a source language subprogram. If END terminates a subprogram assembled separately or the last subprogram of a group, MON follows END. Otherwise END is followed by NAM or OPT.

The format is

END s

An optional symbolic name of an entry point to the first subprogram to be executed. If specified, s must be defined as an entry point in the subprogram to which control passes. This entry point may be in the same subprogram as the END statement or in a subprogram loaded at the same time.

#### Example:

END START

START is the location of the first statement to be executed.

60361900B 3-1

#### 3.1.3 ENT

The ENT instruction lists the symbolic names of entry points which may be referenced from other subprograms.

The format is

ENT

$$s_1, s_2, \ldots, s_n$$

s<sub>i</sub> Entry points listed in the address field of ENT and must be defined in the subprogram containing the ENT instruction. s<sub>i</sub> must not refer to to a location outside the subprogram, common storage, or data storage.

## Example:

## 3.1.4 EXT/EXT\*

The EXT instruction lists the symbolic names of entry points in external subprograms which may be referenced from this subprogram.

The format is

EXT

$$s_1, s_2, \ldots, s_n$$

Entry points in the address field of EXT, which must be symbols defined in the subprograms they reference.  $s_i$  must not refer to symbols in the same subprogram.

## Example 1:

|      | NAM                              |            | (7 1)                                 |

|------|----------------------------------|------------|---------------------------------------|

|      | $\mathbf{EXT}$                   | ENT1, ENT2 | (Legal)                               |

| ENT3 | LDA                              | XYZ        |                                       |

|      | COM                              | ENT5       |                                       |

|      | $\mathbf{E}\mathbf{X}\mathbf{T}$ | ENT3       | (Illegal; ENT3 is same subprogram)    |

|      | EXT                              | ENT4       | (Legal)                               |

|      | EXT                              | ENT5       | (Illegal; ENT5 in common storage)     |

|      | EXT                              | ENT1       | (Legal; defined in same way as above) |

|      | •                                | •          |                                       |

|      | •                                | •          |                                       |

|      | END                              | •          |                                       |

|      |                                  |            |                                       |

#### Example 2:

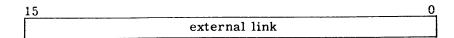

This reference to ENT1 results in the following two machine words.

| 15  | 11  | 10 | 9 | 8 | 7 |    | 0 |

|-----|-----|----|---|---|---|----|---|

| LDA | . 0 | 1  | 0 | 0 |   | 00 |   |

|     |     |    |   |   |   |    |   |

| 15  |     |    |   |   |   |    | 0 |

external link

External link is a pointer to the location of ENT1 used by the loader at load time.

The EXT\* instruction is the same as EXT except that  $\mathbf{s_i}$  are absolute locations in EXT and references to  $\mathbf{s_i}$  are made relative in EXT\*.

The format is

$$\text{EXT*} \quad s_1, s_2, \dots, s_n$$

The plus terminator cannot be used with an operation code when the address references a relative external entry point. It is also illegal to enclose an external in parentheses in the address field of an ADC instruction (section 3.3.1).

## Examples:

This reference to NAME1 results in the following two machine words.

| 15  | 11 | 10 | 9 | 8 | 7 0 |

|-----|----|----|---|---|-----|

| LDA | 1  | 0  | 0 | 0 | 00  |

External link is a pointer to the location of NAME1 used by the loader at load time.

#### 3.2 DATA STORAGE

The following instructions allocate data storage. BSS and BZS assign storage local to the subprogram in which they appear. COM and DAT assign data common to any number of subprograms. Symbolic names in the location fields of data storage instructions are ignored.

#### 3.2.1 BSS

The BSS instruction assigns symbolic names to segments of storage within the instruction sequence of the subprogram.

The format is

BSS

$$s_1(e_1), s_2(e_2), \dots, s_n(e_n)$$

Symbolic name which defines the first location of the name named segment.

When omitted from a subfield, a segment is assigned with omitted

the length e but no name is assigned to the segment.

Corresponding expressions of the symbolic name which expression  $e_i$

defines the length of the segment in words. Segments are assigned contiguously to form one block of data starting at location  $\mathbf{s}_1$ . The size of the block is equal to the sum of the sizes of the segments.  $e_i$  are evaluated modulo  $2^{15}$ -1 and must be absolute.

0 The associated symbolic name is assigned to the next

segment which in effect assigns two names to that segment.

omitted The length is assumed to be one computer word.

Must be previously defined; can be assigned by an EQU symbolic

name instruction.

#### 3.2.2 BZS

This statement functions in the same way as the BSS, except that the specified storage locations are set to zero.

The format is

BZS

$$s_1(e_1), s_2(e_2), ..., s_n(e_n)$$

# Example:

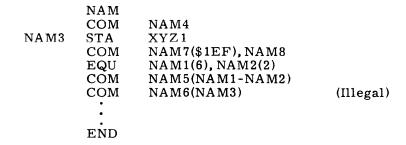

|      | NAM |                  |                                                            |

|------|-----|------------------|------------------------------------------------------------|

| NAM3 | LDA | XYZ1             |                                                            |

|      | BSS | NAM4(3)          | (Assign 3 words to NAM4)                                   |

|      | BZS | NAM5(5)          | (Assign 5 words, set to zero, to NAM5)                     |

|      | BSS | NAM1, NAM2(9)    | (Assign 1 word to NAM1; assign 9 words to NAM2)            |

|      | BSS | NAM3             | (Illegal; NAM3 already assigned)                           |

|      | BSS | NAM6, (4)        | (Assign 1 word to NAM6, assign 4 words to unnamed segment) |

|      | BSS | NAM7             | (Assign 1 word to NAM7)                                    |

|      | EQU | NAM8(4), NAM9(2) | (Assign I word to NAMI)                                    |

|      | BZS | NAM10(NAM8-NAM9) | (Assign 2 words, set to zero, to NAM10)                    |

|      | BSS | NAM8(NAM10-1)    | (Illegal; NAM8 already assigned)                           |

|      | BSS | LOC1(0), LOC2    | (Assign the same word to LOC1 and                          |

|      | •   | • • •            | LOC2)                                                      |

|      |     |                  |                                                            |

|      | •   |                  |                                                            |

|      | END |                  |                                                            |

## 3.2.3 COM

The COM instruction names and defines segments in a block of storage common to more than one subprogram.

The format is

| COM | s <sub>1</sub> (e <sub>1</sub> ), | $s_2(e_2), \ldots, s_n(e_n)$ |                                                                                                                                                                                                                                                                                                                                 |

|-----|-----------------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | $\mathbf{s_i}$                    | name                         | Symbolic name which defines the first location of the named segment.                                                                                                                                                                                                                                                            |

|     |                                   | omitted                      | When omitted from a subfield, a segment is assigned with the length e but no name is assigned to the segment.                                                                                                                                                                                                                   |

|     | e <sub>i</sub>                    | expression                   | Corresponding expressions of the symbolic name which defines the length of the segment in words. Segments are assigned contiguously to form one block of data starting at location $s_1$ . The size of the block is equal to the sum of the sizes of the segments. $e_i$ are evaluated modulo $2^{15}$ -1 and must be absolute. |

|     |                                   | 0                            | The associated symbolic name is assigned to the next segment which in effect assigns two names to that segment.                                                                                                                                                                                                                 |

|     |                                   | omitted                      | The length is assumed to be one computer word.                                                                                                                                                                                                                                                                                  |

|     |                                   | symbolic<br>name             | Must be previously defined; can be assigned by an $\mathrm{EQU}$ instruction.                                                                                                                                                                                                                                                   |

60361900B 3-5