# CONTROL DATA® SYSTEM 17

1784 COMPUTER REFERENCE MANUAL

|                 | REVISION RECORD                                                                     |  |  |  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| REVISION        | DESCRIPTION                                                                         |  |  |  |  |  |  |  |  |

| 01              | Preliminary release, published as CDC Publication Number 88830301.                  |  |  |  |  |  |  |  |  |

| 11/73           |                                                                                     |  |  |  |  |  |  |  |  |

| A               | Manual released; Publication Number 88830301 obsoleted.                             |  |  |  |  |  |  |  |  |

| 2/74            |                                                                                     |  |  |  |  |  |  |  |  |

| В               | Manual revised: address changes to Revision Record and Comment Sheet/Envelope only. |  |  |  |  |  |  |  |  |

| 9/74            |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

| <del> </del>    |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

|                 |                                                                                     |  |  |  |  |  |  |  |  |

| Publication No. |                                                                                     |  |  |  |  |  |  |  |  |

Address comments concerning this manual to:

Small Computer Development Division 4455 Eastgate Mall La Jolla, California 92037

or use Comment Sheet in the back of this manual.

89633400

# **CONTENTS**

| 1 | BASIC SYSTEM DESCRIPTION   |      |   | DSA Memory Protect Fault<br>Programming Requirements | 4-9<br>4-9 |

|---|----------------------------|------|---|------------------------------------------------------|------------|

|   | Basic 1784 Computer System | 1-2  |   | <b>.</b>                                             |            |

|   | Basic I/O Peripherals      | 1-2  | 5 | INPUT/OUTPUT                                         |            |

|   | Options                    | 1-3  |   |                                                      |            |

|   | Storage Options            | 1-4  |   | General Information                                  | 5-1        |

|   | I/O Options                | 1-5  |   | Basic Peripheral Equipment                           | 5-1        |

|   |                            |      |   | Data Storage                                         | 5-2        |

| 2 | STORAGE                    |      |   | Control Signals                                      | 5-2        |

|   |                            |      |   | Addressing                                           | 5-3        |

|   | Storage Word               | 2-1  |   | I/O Operations                                       | 5-5        |

|   | Storage Addressing         | 2-2  |   | Function                                             | 5-6        |

|   | Storage Access             | 2-2  |   | Director Function                                    | 5-6        |

|   |                            |      |   | Function Bit Definitions                             | 5-6        |

| 3 | CENTRAL COMPUTER           |      |   | Status                                               | 5-8        |

|   |                            |      |   | Director Status                                      | 5-8        |

|   | Arithmetic Section         | 3-1  |   | Status Bit Definitions                               | 5-8        |

|   | Control Section            | 3-3  |   | Interrupts                                           | 5-10       |

|   | Instruction Formats        | 3-3  |   | I/O on Basic Peripherals                             | 5-10       |

|   | Storage Reference          |      |   | Standard and Basic                                   |            |

|   | Instructions               | 3-4  |   | Peripheral s                                         | 5-11       |

|   | Register Reference         |      |   | 1711-4, 1711-5, 1713-4,                              |            |

|   | Instructions               | 3-13 |   | 1713-5 Teletypewriters                               | 5-11       |

|   | Skip Instructions          | 3-19 |   | 713-10 Conversational                                |            |

|   | Negative Zero/Overflow Set | 3-20 |   | Display Terminal                                     | 5-11       |

|   |                            |      |   | Basic Peripharal/                                    |            |

| 4 | INTERRUPT SYSTEM AND       |      |   | Computer Communication                               | 5-11       |

|   | PROGRAM PROTECTION         |      |   | Controls                                             | 5-18       |

|   |                            |      |   | Teletypewriter                                       | 5-18       |

|   | Interrupt System           | 4-1  |   | Conversational Display                               |            |

|   | Logical Description        | 4-1  |   | Terminal                                             | 5-19       |

|   | Programming and Operation  | 4-2  |   | Hard-Copy Printer                                    | 5-19       |

|   | Internal Interrupts        | 4-6  |   | Coding                                               | 5-20       |

|   | Program Protection         | 4-7  |   | Signal Coding                                        | 5-20       |

|   | Clearing/Setting the       |      |   |                                                      |            |

|   | Program Protect Bit        | 4-7  | 6 | CONSOLE CONTROLS AND                                 |            |

|   | Program Protect Switch     | 4-8  |   | INDICATORS                                           | 6-1        |

|   | Program Protect Violations | 4-8  |   |                                                      |            |

|   | Storage Parity Errors      |      | Α | 1784 COMPUTER INSTRUCTION                            |            |

|   | (Program Protect Enabled)  | 4-8  |   | TIMES                                                | A-1        |

|   | Peripheral Equipment       |      | В | 1784 INSTRUCTIONS                                    | B-1        |

|   | Protection                 | 4-8  |   |                                                      |            |

89633400 iii

# **FIGURES**

| 1-1 | Module Allocation of Typical<br>1784 Computer System Main |     | 3-2 | Program Using Return Jump<br>Instruction | 3-12 |

|-----|-----------------------------------------------------------|-----|-----|------------------------------------------|------|

|     | Enclosure                                                 | 1-4 | 5-1 | Peripheral Equipment Levels              | 5-4  |

| 1-2 | Module Allocation of Typical                              |     | 5-2 | A Graphic Presentation of                |      |

|     | 1783 Expansion Enclosure                                  | 1-5 |     | Typical Input/Output Devices             |      |

|     |                                                           |     |     | in 1784 Computer System                  | 5-13 |

| 3-1 | Block Diagram of the 1784                                 |     |     |                                          |      |

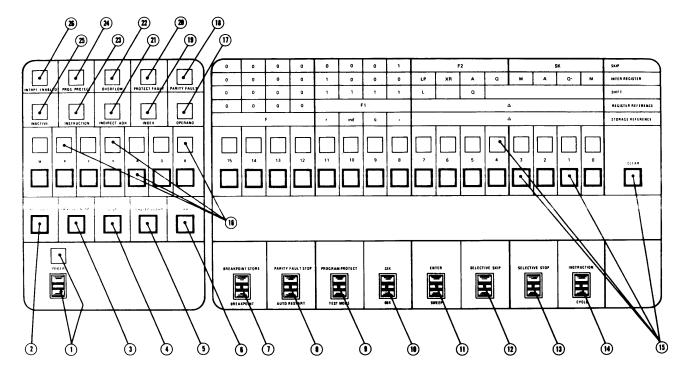

|     | Central Processing Unit                                   | 3-2 | 6-1 | 1784 Computer Console                    | 6-3  |

|     |                                                           |     |     |                                          |      |

|     |                                                           |     |     |                                          |      |

|     |                                                           |     |     |                                          |      |

|     |                                                           |     |     |                                          |      |

## **TABLES**

| 1-1 | Magnetic Tape Transport<br>Characteristics | 1-7 | 3-3 | Inter-register Instruction<br>Truth Table | 3-16 |

|-----|--------------------------------------------|-----|-----|-------------------------------------------|------|

| 1-2 | Cartridge Disk Drive                       |     | 4-1 | Interrupt State Definitions               | 4-3  |

|     | Characteristics                            | 1-8 |     |                                           |      |

|     |                                            |     | 5-1 | Use of Director                           | 5-5  |

| 2-1 | Storage Addressing Wrap-Around             | 2-3 |     |                                           |      |

| 3-1 | Decimal-Hexadecimal-Binary                 |     | 5-2 | ASCII (1968) Teletypewriter               |      |

| J-1 | Relationships                              | 3-4 |     | Codes                                     | 5-21 |

| 3-2 | Storage Addressing Relationships           | 3-5 | 5-3 | ASCII (1968) Control Signals              | 5_22 |

The CONTROL DATA<sup>®</sup> 1784 Computer is a stored program, parallel mode, digital computer. Miniaturized and compact, it is designed for high computation and input/output (I/O) rates. The program protection features of the 1784 Computer System and its high reliability under a wide range of environmental conditions make it suitable for many varied applications. The I/O interface of the 1784 Computer System is capable of accepting a great variety of peripheral devices, including 1700/SC1700 devices. SYSTEM 17 peripheral controllers are housed in the main computer enclosure.

The 1784 computer system has the following characteristics:

- It is a stored program, digital computer

- Medium and large scale integrated logic circuits

- Dynamic MOS memory cells

- Power cutoff and memory preserve battery

- Basic memory of 4096 18-bit words expandable to 65,536 words in 4096-word modules

- Two memory cycle times available:

- -900 nanosecond (1784-1 Computer)

- -600 nanosecond (1784-2 Computer)

- 18-bit storage word:

- -16 data or instruction bits

- 1 parity bit

- 1 program protect bit

- Program protect system

- Parity checking system

- Direct storage access for high-speed I/O transfer, rates up to 1.1 million (1784-1) or 1.6 million (1784-2) 18-bit words per second

- 16-level priority interrupt system

- Power failure/Autorestart

- Breakpoint

- Extensive repertoire of instructions, including arithmetic, logical, and inter-register operations

- 16-bit or 32-bit instruction

- Hardware multiply and divide

89633400

- Seven storage reference addressing modes, including multilevel indirect addressing

- Operator's console includes:

- -Register contents displayed in binary

- -Operating switches and indicators

- -Breakpoint selection

- -Manual interrupt

- Cabinet dimensions (approximate):

```

-Height -15-3/4 inches (40.0 cm)

```

- -Width 19 inches (48.3 cm)

- -Depth 19 inches (48.3 cm)

- Weight of basic 1784 Computer 80 lbs. (36.4 kg)

- Reliability (calculated) Approximately 17,000 hours mean time between failures for basic 1784 Computer

- Environment (operating):

- -Temperature 40°F to 120°F (5°C to 50°C)

- -Relative humidity 10% to 90% (non-condensing)

- Self-contained forced air cooling

- Built-in power supply unit

## **BASIC 1784 COMPUTER SYSTEM**

The 1784 Computer is the basic unit in the computer system. The 1784 performs arithmetic and logical operations required by the instructions of a stored program. The computer also generates the commands necessary to execute input/output operations. The basic 1784 contains one interrupt system with one internal and 15 external priority interrupt levels. It provides high-speed random-access main memory for 4096 18-bit words and includes an A/Qdata channel bus, a high-speed direct access (DSA) channel bus, and teletypewriter or conversational display terminal controller which can operate at 110, 300, 1200 and 9600 baud.

## BASIC I/O PERIPHERALS

The basic 1784 Computer may be equipped with a teletypewriter (TTY) or conversational display terminal (CDT) by utilizing the TTY/CDT controller, which is an integral part of the basic computer. Either the TTY or the CDT may be used with the controller, but not both simultaneously. The following types of teletypewriters and conversational display terminal can be used.

#### 1711-4 TELETYPEWRITER

The 1711-4 is a Model 33 KSR (keyboard send-receive) capable of data transmission at a rate of 110 bits per second. The KSR Teletype unit consists of a keyboard and printer.

1-2 89633400

#### 1711-5 TELETYPEWRITER

The 1711-5 is a heavy-duty Model 35 KSR capable of data transmission at a rate of 110 bits per second. The KSR Teletype unit consists of a keyboard and printer.

#### 1713-4 TELETYPEWRITER

The 1713-4 is a Model 33 ASR (automatic send-receive) which, in addition to the normal keyboard and printer, has its own paper tape reader and punch. Manual controls for the paper tape are provided.

#### 1713-5 TELETYPEWRITER

The 1713-5 is a heavy-duty Model 35 ASR which, in addition to the normal keyboard and printer, has its own paper tape reader and punch. Manual controls for the paper tape are provided.

## 713-10 CONVERSATIONAL DISPLAY TERMINAL

The 713-10 consists of video display with an image area for eight lines of 80 characters, or 16 lines of 80 characters with addition of the optional 711-100 Expanded Memory module. The terminal has an electronic data entry keyboard of standard teletypewriter layout and a 10-key numeric cluster. There are several control function keys which simplify message composition and communication operations. Facilities are provided for either character-by-character or multiple character message transmission. Communication transmission rates of 110 and 300 bits per second are selectable.

In addition, the 713-120 Printer can be used to provide "hard copy" of selected messages. This non-impact thermal printer prints 30 characters per second.

## **OPTIONS**

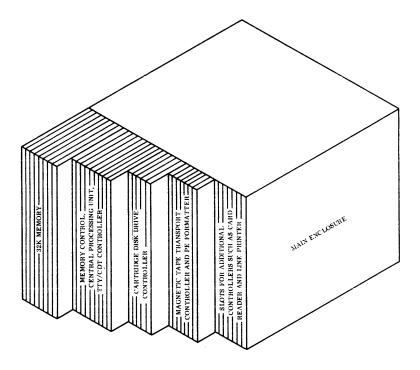

For greater system capability, the 1784 computer system may be expanded with storage and I/O options. Figure 1-1 shows a 1784 computer system with memory expanded to 32K words and some of the available peripheral controllers installed.

89633400 1-3

Figure 1-1. Module Allocation of Typical 1784 Computer System Main Enclosure

## STORAGE OPTIONS

## MEMORY INCREMENT MODULES

Memory increment modules of 4,096 words each may be added. The maximum central processor memory size of 65,536 words is achieved with the addition of 15 such memory increments to the basic 4096 words. The central processor memory is made up of dynamic MOS memory cells. For the 1784-1 Computer the 4096-word increment is the 1782-1 Memory Module (900-nanosecond memory cycle time). The 1782-2 Memory Module is for the 1784-2 Computer (600-nanosecond memory cycle time).

#### 1783-1 EXPANSION ENCLOSURE

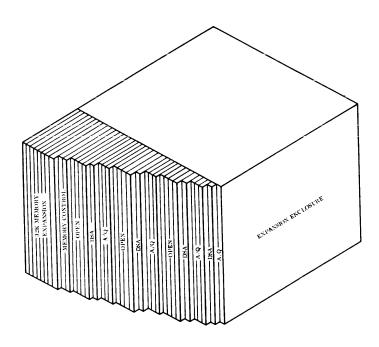

The 1783-1 is an enclosure to accommodate memory increment modules when main storage exceeds 32,768 words. It can be used for increments to either the 1784-1 or the 1784-2 Computers. The 1783-1 contains its own power supply unit. It also contains prewired slots for A/Q (10) and DSA (4) bus expansion to accommodate additional SYSTEM 17 peripheral controllers. See Figure 1-2. Programming of these controllers is identical in either enclosure.

1-4 89633400

Figure 1-2. Module Allocation of Typical 1783 Expansion Enclosure

## 1786-1 MEMORY EXPANSION CONTROLLER

This module is installed in the 1783-1 Expansion Enclosure to control the memory increment modules located in the 1783-1.

## 10297-1 MEMORY HOLD BATTERY

In the event of source power cutoff, this non-acid battery (when fully charged) provides power to preserve the contents of the 32K word memory bank for up to eight hours. Battery charging occurs during normal computer operation. (Maximum charge time is 32 hours for a fully discharged battery.) A memory hold battery can be accommodated in both the main computer and in the expansion enclosures, to preserve the contents of both memory banks.

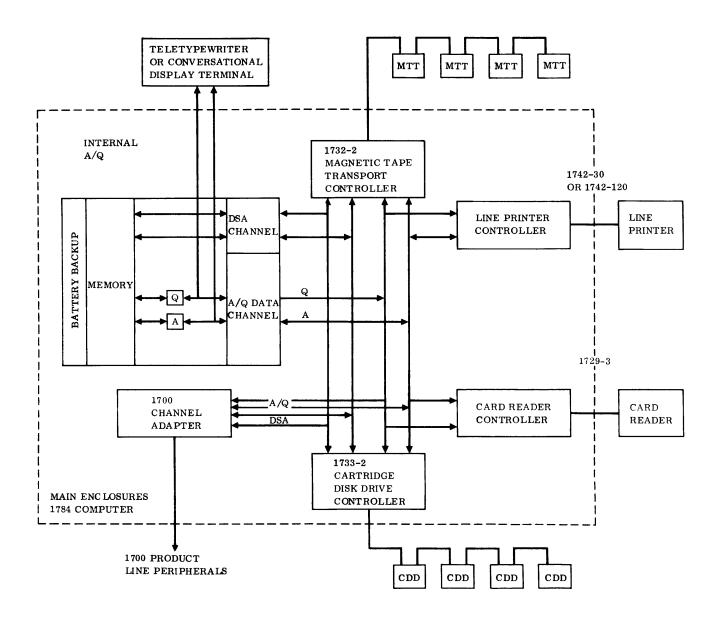

## I/O OPTIONS

The main and expansion enclosures of the 1784 computer system provide access to the standard A/Q and DSA data channels.\* In addition to the central processing unit, the main enclosure accommodates up to 32K words of memory, the associated memory controller, and certain peripheral controllers. These are the 1732-2 Magnetic Tape Transport Controller and the 1733-2 Cartridge Disk Drive Controller. Additional controllers, for the 1742-30 and 1742-120 Line Printers and 1729-3 Card Reader, can be accommodated in either the main or expansion enclosures.

89633400 1-5

<sup>\*</sup>See Section 5 for description of data channels.

## 1785-1 A/Q CHANNEL EXPANSION

The 1785-1 provides extension of the A/Q channel bus from the 1784 main enclosure to the 1783 expansion enclosure. The 1785-1 requires one of the 1783 A/Q slots plus one of the 1784 A/Q slots.

#### 1785-2 DSA CHANNEL EXPANSION

The 1785-2 provides extension of the DSA channel bus from the 1784 main enclosure to the 1783 expansion enclosure. The 1785-2 requires one of the 1783 DSA slots plus one of the 1784 DSA slots.

## 1785-3 1700 A/Q CHANNEL ADAPTER

The 1785-3 is an interface installed on a 1784 or 1783 which converts the A/Q voltage bus to a current mode channel. In essence, this conversion gives the 1784/1783 the same electrical I/O features as a 1704/1714/1774, so that standard 1700 unbuffered peripherals can be connected to the SYSTEM 17. Communication with these devices is exactly the same on the 1784/1783 as on the 1704/1714/1774. The 1785-3 requires two A/Q slots.

## 1785-4 1700 DSA CHANNEL ADAPTER

The 1785-4 is an interface installed on a 1785-3 and 1784 or 1783. Similar to the 1785-3, it converts the DSA voltage bus to current mode and allows standard 1700 buffered peripherals to be operated on the SYSTEM 17. The 1785-4 requires two DSA slots.

The following descriptions are of the major peripherals and controllers of the SYSTEM 17 product line that can form part of a 1784 computer system. See the appropriate product reference manuals for full details of the peripherals.

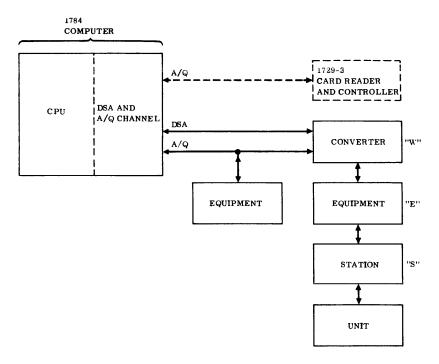

## 1729-3 CARD READER AND CONTROLLER

The card reader controller can be accommodated in either the main or expansion enclosures. The controller communicates with the peripheral unit via the A/Q channel. For every 1729-3 peripheral there must be an associated controller. The desk-top unit can read 80-column punched cards at a rate of 300 per minute.

The 1729-3 controller executes the following:

- Interprets central processing unit (CPU) function codes

- Controls the card reader operation

- Transfers data from the card reader to the CPU

- Detects operation and transmission errors

- Provides card reader status information to the CPU

## 1742-30 AND 1742-120 LINE PRINTERS AND CONTROLLER

The line printer controller can be accommodated in either the main or expansion enclosures. The controller communicates with one 1742-30 Line Printer or one 1742-120 Line Printer via the A/Q channel. Each additional line printer requires an additional controller. The 1742-30 Line Printer prints up to 300 lines per minute and the 1742-120 prints up to 1200 lines per minute. Both units print 136 columns per line.

The line printer controller executes the following:

- Interprets central processing unit (CPU) function codes

- Controls the line printer operation

- Transfers data from the CPU to the line printer

- Detects operation and transmission errors

- Provides the line printer status information to the CPU

## 1732-2 MAGNETIC TAPE TRANSPORT CONTROLLER

One 1732-2 Magnetic Tape Transport Controller may be accommodated in the 1784 Computer main enclosure. (Slots 14-8 are prewired to accept the 1732-2 and the 10300-1.) Up to four magnetic tape transports (MTTs) can be controlled by the 1732-2 controller. Any combination of 615-73 and 615-93 MTTs can be controlled. Table 1-1 gives the main characteristics of the MTTs.

Table 1-1. Magnetic Tape Transport Characteristics

| MAGNETIC<br>TAPE<br>TRANSPORT | NUMBER<br>OF<br>TRACKS | FORMAT* | DATA DENSITY<br>(BITS PER INCH) | DATA TRANSFER RATE (CHARACTERS PER SECOND) |

|-------------------------------|------------------------|---------|---------------------------------|--------------------------------------------|

|                               |                        |         | 556                             | 20.8K                                      |

| 615-73                        | 7                      | NRZI    | 800                             | 30.0K                                      |

|                               |                        | NRZI    | 800                             | 30.0K                                      |

| 615-93                        | 9                      | PE      | 1600                            | 60.0K                                      |

<sup>\*</sup>NRZ1: Non-Return to Zero, One's Complement

PE: Phase Encode (requires 10300-1)

The transports work at a speed of 37.5 inches per second. Reels containing up to 2400 feet of tape may be used.

The 1732-2 Magnetic Tape Transport Controller executes the following:

- Interprets CPU function codes

- Selects the MTT that the central processing unit (CPU) requires

- Controls the MTT operation

- Assembles, disassembles, and transfers data between the CPU and the MTT

- Detects operation and transmission errors

- Provides the MTT status information to the CPU

With the addition of the 10300-1 Phase Encoding Formatter, the 1732-2 controller will encode and decode PE data to and from the MTT.

Communication between the MTT controller and the CPU is via the A/Q channel for control functions and status information and non-buffered data transfer. Buffered data transfer is via the direct storage access (DSA) channel.

#### 1733-2 CARTRIDGE DISK DRIVE CONTROLLER

One 1733-2 Cartridge Disk Drive Controller may be accommodated in the 1784 Computer main enclosure (slots 19-15 are prewired to accept the 1733-2). Up to four cartridge disk drives (CDDs) can be controlled by the 1733-2 controller. Any combination of 856-2 and 856-4 CDDs can be controlled. The 856-2 and 856-4 CDDs have two disks, one fixed and one removable. Table 1-2 gives the main characteristics of the CDDs.

DATA TRANSFER TOTAL NUMBER OF TOTAL RATE (WORDS PER TRACKS CAPACITY CARTRIDGE NUMBER OF (WORDS) SECOND) DISK DRIVE SURFACES PER SURFACE 856-2 4 200 (+3 spares) 2.2 million 156K 4.4 million 156K 4 400 (+6 spares) 856-4

Table 1-2. Cartridge Disk Drive Characteristics

Each disk has two surfaces. All disks have 29 sectors per track and 96 words per sector. Average positioning time is 35 milliseconds.

The 1733-2 Cartridge Disk Drive Controller executes the following:

- Interprets CPU function codes

- Selects the CDD that the central processing unit (CPU) requires

- Controls the CDD operation

- Assembles, disassembles, and transfers data between the CPU and the CDD

- Detects operation and transmission errors

- Provides the CDD status information to the CPU

Communication between the CDD controller and the CPU is via the A/Q channel for control functions and status information. Buffered data transfer is via the direct storage access (DSA) channel.

The basic 1784 computer system provides high-speed, random-access memory for 4096 18-bit words. Dynamic LSI MOS memory cells are used. The memory capacity can be expanded from 4096 words to 65,536 words in 4096-word increments. When main enclosure memory (lower bank) exceeds 32K words, the additional memory (upper bank) is housed in an expansion enclosure. Two memory cycle times are available. The 1784-1 Computer has a 900-nanosecond memory cycle time, and the 1784-2 Computer has a 600-nanosecond memory cycle time. Memory cycle time is defined as the shortest possible interval between consecutive accesses in the lower or upper memory banks.

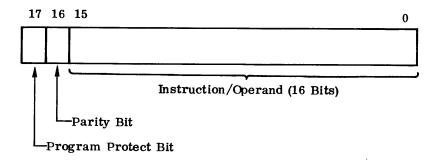

## STORAGE WORD

A storage word may be a 16-bit instruction, a 16-bit operand, or one-half of a 32-bit instruction. A parity bit and a program protect bit are appended to each 16-bit storage word; thus a storage word is 18 bits long.

#### Format:

Bit 16 is the parity bit. Odd parity is used. The parity bit takes on a value so that the total number of 1 bits in the word (including the program protect bit) is odd. For example, if all 16 data bits are 1s and the program protect bit is 0, the parity bit is a 1.

Bit 17 is the program protect bit. If it is a 1, it indicates the word is part of a protected program.

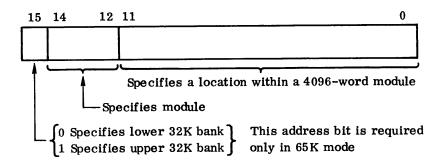

## STORAGE ADDRESSING

The location of each word in storage is identified by an assigned number (address). An address consists of 15 bits (00 through 14) in 32K mode and 16 bits when in 65K mode.

Format:

Bits 00 through 11 specify a location within a 4096-word storage module.

Bits 12 through 15 specify one of up to 16 storage modules.

A condition may arise in which the program references an address in a nonexistent storage module. In this case, the computer references the address specified by bits 00 through 11 in an existing storage module (storage addressing wrap-around). Table 2-1 lists the actual 1784 storage size, the storage module addressed, and the effective module addressed.

For example, if the computer has 16K (16,384) words of storage, the highest permissible address is  $3FFF_{16}$ .\* If the program attempts to address location  $5040_{16}$  (located in a nonexistent storage module 5), it actually references location  $1040_{16}$  in module 1.

## STORAGE ACCESS

There are two accesses to computer storage. One is internal from the central processing unit (CPU) and is used for all computation operations which reference storage. The other is the direct storage access (DSA), used to transfer buffered data to and from certain peripheral devices. Simultaneous memory references can occur in both the lower and upper memory banks when the storage exceeds 32K words, if one reference is a DSA memory reference and the other is a CPU reference.

<sup>\*</sup>Details of hexadecimal notation are given in Table 3-1.

Table 2-1. Storage Addressing Wrap-Around

| STORAGE SIZE<br>(K WORDS) | STORAGE MODULE ADDRESSED |   |   |   |   |   |   |   |   |   |   |   |              |              |              |   |

|---------------------------|--------------------------|---|---|---|---|---|---|---|---|---|---|---|--------------|--------------|--------------|---|

|                           | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | C            | D            | E            | F |

| 4                         | 0                        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0            | 0            | 0            | 0 |

| 8                         | 0                        | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0            | 1            | 0            | 1 |

| 12                        | 0                        | 1 | 2 | 2 | 0 | 1 | 2 | 2 | 0 | 1 | 2 | 2 | 0            | 1            | 2            | 2 |

| 16                        | 0                        | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0 | 1 | 2 | 3 | 0            | 1            | 2            | 3 |

| 20                        | 0                        | 1 | 2 | 3 | 4 | 4 | 4 | 4 | 0 | 1 | 2 | 3 | 4            | 4            | 4            | 4 |

| 24                        | 0                        | 1 | 2 | 3 | 4 | 5 | 4 | 5 | 0 | 1 | 2 | 3 | 4            | 5            | 4            | 5 |

| 28                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 6 | 0 | 1 | 2 | 3 | 4            | 5            | 6            | 6 |

| 32                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 0 | 1 | 2 | 3 | 4            | 5            | 6            | 7 |

| 36                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 8 | 8 | 8 | 8            | 8            | 8            | 8 |

| 40                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 8 | 9 | 8            | 9            | 8            | 9 |

| 44                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α | Α | 8            | 9            | Α            | Α |

| 48                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α | В | 8            | 9            | Α            | В |

| 52                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α | В | $\mathbf{C}$ | C            | $\mathbf{C}$ | C |

| 56                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | $\mathbf{C}$ | $\mathbf{D}$ | C            | D |

| 60                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | Α | В | C            | D            | E            | E |

| 65                        | 0                        | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | В | C            | D            | E            | F |

EFFECTIVE MODULE ADDRESSED The 1784 Computer performs calculations and processes data in a parallel, binary mode through the step-by-step execution of individual instructions. The instructions and data are stored in the main storage of the computer system.

Functionally, the computer may be divided into an arithmetic section and a control section.

## ARITHMETIC SECTION

P REGISTER

X REGISTER

Y REGISTER

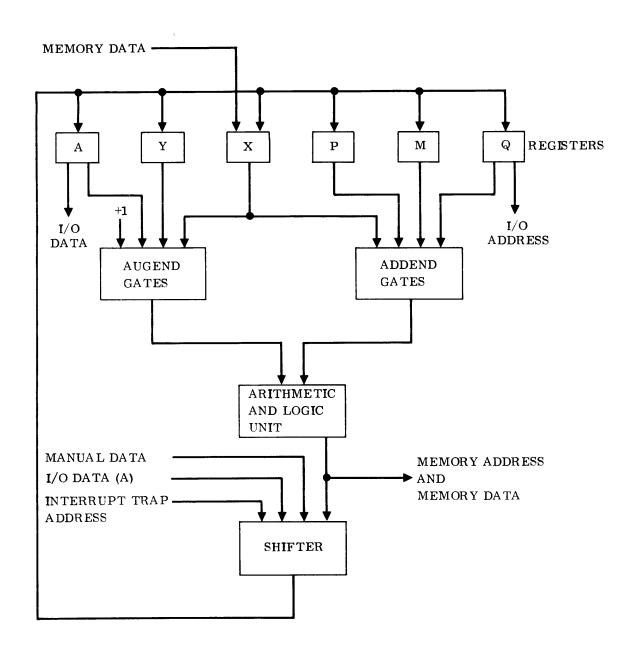

The arithmetic section performs the arithmetic and logical operations necessary for executing instructions. It consists primarily of several operational registers. In all discussions of registers, the rightmost bit is the least significant and is defined as bit 00. Figure 3-1 is a block diagram of the computer.

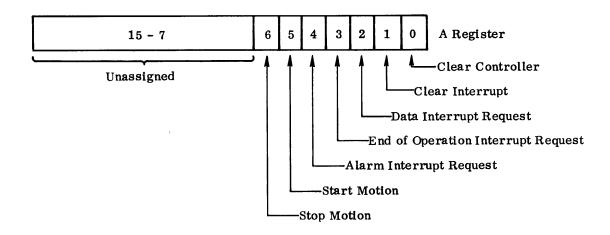

| A REGISTER | The A register is the principal arithmetic register; it contains 16 bits    |

|------------|-----------------------------------------------------------------------------|

|            | (15 through 00) of which bit 15 is the sign bit. The A register also serves |

|            | as the data interface during input/output (I/O) operations.                 |

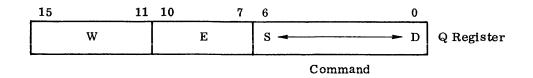

| Q REGISTER | The Q register is an auxiliary arithmetic register containing 16 bits (15       |  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

|            | through 00). This register is also used as an index register for instruc-       |  |  |  |  |  |  |

|            | tions requiring indexing. The Q register also holds the address of a peripheral |  |  |  |  |  |  |

|            | device during I/O operations.                                                   |  |  |  |  |  |  |

| The 16-bit P register (15 bits when in 32K mode) functions as a program      |

|------------------------------------------------------------------------------|

| address counter. The P register holds the address of each instruction.       |

| After the instruction at address P is executed, P is advanced to the address |

| of the next instruction. The amount by which P is advanced is determined by  |

| the type of instruction being executed.                                      |

Since the count in P is advanced by a 16-bit one's complement adder, P can generate storage address in sequence from  $0000_{16}$  to FFFE<sub>16</sub>. When a count of FFFE<sub>16</sub> is reached, the next count in P reduces its value to  $0000_{16}$ .

| The X register is an exchange register containing 16 bits (15 through 00). |

|----------------------------------------------------------------------------|

| This register holds data coming from storage. It also holds one of the     |

| parameters in most arithmetic operations.                                  |

The Y register is an address register containing 16 bits (15 through 00). In this register, storage addresses are formed and held for transfer during a storage reference. The Y register is also used as an auxiliary register during other operations.

89633400 3-1

Figure 3-1. Block Diagram of the 1784 Central Processing Unit

3-2 89633400

B REGISTER The breakpoint register contains 16 bits and holds the data for address

comparison during breakpoint mode of operation. This register can only

be entered manually via a control panel switch.

M REGISTER The M register is the mask register containing 16 bits. It is used in the

interrupt processing system and is described in detail in Section 4.

INDEX REGISTER 2 Storage location 00 FF16 acts as a second index register (in addition to the

Q register). The contents of this register can be used for address

modification.

## CONTROL SECTION

The control section of the computer directs the operations required to execute instructions and establishes the timing relationships needed to perform these operations in the proper sequence. It also controls interrupt processing, program protection, and operations involving I/O and storage.

The control section acquires an instruction from storage, interprets it, and sends the necessary commands to other sections. The program address counter, P, provides program continuity by generating in sequence the storage addresses which contain the individual instructions. The count in P is advanced to specify the address of the next instruction in the program. The amount by which P is advanced is determined by the type of instruction being executed.

## INSTRUCTION FORMATS

There are three types of instructions in the 1784 Computer: storage reference, register reference, and skip.

- Storage reference instructions reference storage for operands.

- Register reference instructions operate on the computer registers or control logic.

- Skip instructions sense the existence of specific conditions within the computer.

Five instruction formats are required, one for each type of instruction plus one for the Shift instructions and one for the Inter-register instructions, which are subgroups of the register reference instructions.

Hexadecimal notation is used in this computer for ease in expressing the four-bit groups which occur in the instruction format. Hexadecimal is base 16 and requires the additional characters A, B, C, D, E, and F. The relationships between binary, decimal, and hexadecimal are shown in Table 3-1.

89633400

Table 3-1. Decimal-Hexadecimal-Binary Relationships

| DECIMAL | HEXADECIMAL | BINARY | DECIMAL | HEXADECIMAL | BINARY |

|---------|-------------|--------|---------|-------------|--------|

| 0       | 0           | 0000   | 8       | 8           | 1000   |

| 1       | 1           | 0001   | 9       | 9           | 1001   |

| 2       | 2           | 0010   | 10      | A           | 1010   |

| 3       | 3           | 0011   | 11      | В           | 1011   |

| 4       | 4           | 0100   | 12      | C           | 1100   |

| 5       | 5           | 0101   | 13      | D           | 1101   |

| 6       | 6           | 0110   | 14      | E           | 1110   |

| 7       | 7           | 0111   | 15      | F           | 1111   |

#### STORAGE REFERENCE INSTRUCTIONS

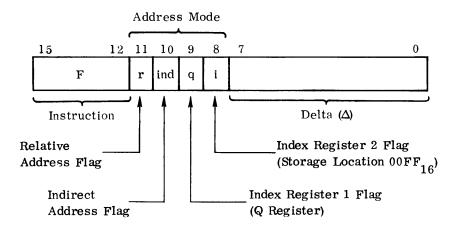

The storage reference instructions contain three fields: instruction, address mode, and delta.

The instruction field contains the four-bit operation code, F. The address mode contains four flags for indexing, indirect addressing, and relative addressing. The sign bit of delta is extended in all cases except those noted.

#### Format:

The following definitions apply to the description of addressing modes.

- Instruction Address: The address of the instruction being executed, also called P.

- <u>Indirect Address</u>: A storage address which contains an address rather than an operand.

- <u>Base Address</u>: The operand address after all indirect addressing but before modification by index registers. The base address is the effective address if no indexing is specified.

- Effective Address: The final address of the operand. In certain cases, the effective address equals the operand for read-operand-type instructions. These cases are noted in Table 3-2.

3-4 89633400

Table 3-2. Storage Addressing Relationships

|                                                             | ADDRESS I                       |        |                                              |                                                                                  | ADDRESS<br>OF NEXT<br>INSTRUC- |

|-------------------------------------------------------------|---------------------------------|--------|----------------------------------------------|----------------------------------------------------------------------------------|--------------------------------|

| MODE                                                        | BINARY                          | HEX.   | DELTA                                        | EFFECTIVE ADDRESS                                                                | TION                           |

| Absolute<br>Constant                                        | 0000                            | 0      | $\Delta \neq 0$ $\Delta = 0$                 | Δ<br>P + 1                                                                       | P + 1<br>P + 2                 |

| Absolute<br>Constant                                        | 0001                            | 1      | $ \Delta \neq 0 \\ \Delta = 0 $              | Δ+ (00FF)<br>(P + 1) + (00FF)*                                                   | P + 1<br>P + 2                 |

| Absolute<br>Constant                                        | 0010                            | 2      | $ \Delta \neq 0 \\ \Delta = 0 $              | $\Delta + (Q)$<br>(P + 1) + (Q)*                                                 | P + 1<br>P + 2                 |

| Absolute<br>Constant                                        | 0011                            | 3      | $\Delta \neq 0$ $\Delta = 0$                 | $\Delta$ + (Q) + (00FF)<br>(P + 1) + (Q) + (00FF)*                               | P + 1<br>P + 2                 |

| Indirect<br>Storage                                         | 0100                            | 4      | $ \Delta \neq 0 \\ \Delta = 0 $              | (Δ)<br>(P + 1)                                                                   | P + 1<br>P + 2                 |

| Indirect<br>Storage                                         | 0101                            | 5      | $ \Delta \neq 0 \\ \Delta = 0 $              | (Δ) + (00FF)<br>(P + 1) + (00FF)                                                 | P + 1<br>P + 2                 |

| Indirect<br>Storage                                         | 0110                            | 6      | $ \Delta \neq 0 \\ \Delta = 0 $              | (Δ) + (Q)<br>(P + 1) + (Q)                                                       | P + 1<br>P + 2                 |

| Indirect<br>Storage                                         | 0111                            | 7      | $ \Delta \neq 0 \\ \Delta = 0 $              | (Δ) + (Q) + (00FF)<br>(P + 1) + (Q) + (00FF)                                     | P + 1<br>P + 2                 |

| Relative<br>16-Bit Relative                                 | 1000                            | 8      | $ \Delta \neq 0 \\ \Delta = 0 $              | P + Δ<br>P + 1 + (P + 1)                                                         | P + 1<br>P + 2                 |

| Relative<br>16-Bit Relative                                 | 1001                            | 9      | $ \Delta \neq 0 \\ \Delta = 0 $              | $P + \Delta + (00FF)$<br>P + 1 + (P + 1) + (00FF)                                | P + 1<br>P + 2                 |

| Relative<br>16-Bit Relative                                 | 1010                            | A      | $ \Delta \neq 0 \\ \Delta = 0 $              | $P + \Delta + (Q)$<br>P + 1 + (P + 1) + (Q)                                      | P + 1<br>P + 2                 |

| Relative<br>16-Bit Relative                                 | 1011                            | В      | $ \Delta \neq 0 \\ \Delta = 0 $              | $P + \Delta + (Q) + (00FF)$<br>P + 1 + (P + 1) + (Q) + (00FF)                    | P + 1<br>P + 2                 |

| Relative Indirect<br>Relative Indirect                      | 1100                            | С      | $ \Delta \neq 0 \\ \Delta = 0 $              | $(P + \Delta)$<br>[P + 1 + (P + 1)]                                              | P + 1<br>P + 2                 |

| Relative Indirect Relative Indirect                         | 1101                            | D      | $\Delta \neq 0$ $\Delta = 0$                 | $(P + \Delta) + (00FF)$<br>[P + 1 + (P + 1)] + (00FF)                            | P + 1<br>P + 2<br>P + 1        |

| Relative Indirect<br>Relative Indirect<br>Relative Indirect | 1110<br>1111                    | E<br>F | $ \Delta \neq 0  \Delta = 0  \Delta \neq 0 $ | $(P + \Delta) + (Q)$<br>[P + 1 + (P + 1)] + (Q)<br>$(P + \Delta) + (Q) + (00FF)$ | P + 1<br>P + 2<br>P + 1        |

| Relative Indirect                                           | r <sup>j</sup> j L <sub>1</sub> |        | $\Delta = 0$                                 | [P+1+(P+1)]+(Q)+(00FF)                                                           | P + 2                          |

<sup>\*</sup>Effective address is the operand for read-operand-type instructions Note: () and [] denote "contents of."

89633400 3-5

Indexing: The computer has two index registers. Index register 1 is the Q register, and index register 2 is storage location 00FF<sub>16</sub>. The base address may be modified by either one or both of the index registers. If the index register 1 flag is set, the contents of the Q register are added to the base address to form the effective address. If the index register 2 flag is set, the contents of storage location 00FF<sub>16</sub> are added to the base address to form the effective address. If both index register flags are set, the contents of Q and the contents of 00FF<sub>16</sub> are added to the base address to form the effective address. Indexing occurs after indirect addressing has been completed.

The computer uses the 16-bit one's complement adder during indexing operations. Consequently, index register contents are treated as signed quantities (bit 15 is the sign bit).

Storage reference instructions have seven different types of addressing modes. They are:

1. Absolute (address mode bits equal 0, 1, 2, or 3). Relative and indirect flags are both 0 and delta does not equal zero. The base address equals delta. The sign bit of delta is not extended. The contents of the index registers, when specified, are added to the base address to form the effective address.

If no indexing takes place, the addresses which can be referenced in the absolute mode are restricted to the lower memory bank. Delta can be only two hexadecimal characters and thus the computer references a location between 0000 and 00FF (address 00FF is one of the index registers).

#### Example:

Load A register with the contents of the absolute address specified by delta. C010 loads the contents of address 0010 into A. If an index register is used, the contents of either 00FF or the Q register are added to the absolute address to specify the effective address.

The command C110 adds the contents of 00FF to delta and from location 0015 loads the A register with 1234.

- 2. Constant (address mode bits equal 0, 1, 2, or 3). Relative and indirect flags are both 0 and delta is 0.

- a. When the address mode bits are 0, P + 1 is the effective address.

- b. When the address mode bits equal 1, 2, or 3, the contents of P + 1 plus the contents of one or both index registers form the effective address. The effective address is taken as the operand for read-operand-type instructions.

## Example:

$$P = C000$$

$P + 1 = 03E8$

The computer loads the A register with the contents of P+1 (i.e., 03E8 is in the register). If indexing is specified, the index register is added to form the constant.

$$P = C200$$

$P + 1 = 03E8$   $Q = 0001$

The A register is loaded with 03E9 because the Q register contained 0001.

3A. 32K Mode Indirect (address mode bits equal 4, 5, 6, or 7). Relative address flag is 0, indirect flag is 1, and delta does not equal zero. The eight-bit value of delta is an indirect address. Delta is a magnitude quantity for this operation (no sign bit).

The computer goes to the base address in the lower memory bank (addresses 0000 through 00FF) and treats the contents of this address as the effective address of the operand unless indexing is specified. Indexing takes place after indirect addressing is completed. If the sign bit of an indirect address (bit 15) is set and the computer is in 32K mode, the address is another indirect address. Indirect addressing continues until the sign bit of a word is not set, resulting in multilevel indirect addressing.

#### Example:

$$P = C4FD$$

$00FD = 0500$   $0500 = 1234$

The computer examines the contents of location 00FD and finds that the sign bit is not set. It then loads the contents of location 0500 into the A register. If indexing had been specified, the indexing quantity would have been added to the contents of address 00FD to reach the effective address. The program continues at P + 1. If address 00FD had contained 8500, the computer would have accepted 1234 in location 0500 as another indirect address and loaded the A register with the contents of address 1234.

Both absolute and indirect modes of addressing reference the lower memory bank locations, 0000 through 00FF. The difference is that absolute loads the A register with the contents of the address in the lower memory bank and indirect uses this location as the address of the operand.

- 3B. 65K Mode Indirect (address mode bits equal 4, 5, 6, or 7). Operates the same as 32K mode indirect with the following exception: If the sign bit of an indirect address (bit 15) is set and the computer is in 65K mode, the address equals an address in high core (banks 8-F). No multilevel indirect addressing is possible.

- 4. Storage (address mode bits equal 4, 5, 6, or 7). Relative address flag is 0, indirect flag is 1, and delta is 0. The contents of location P + 1 is an indirect address. When the base address is formed (indirect addressing complete), the contents of one or both index registers, if specified, are added to form the effective address.

This mode of addressing is very similar to indirect, but instead of the lower memory bank references, the indirect address is found in P+1. In 32K mode, indirect addressing continues as long as the sign bit is set.

89633400 3-7

Example:

$$P = C400$$

$P + 1 = 8500$   $0500 = 1234$

The computer examines P + 1 and finds that the upper bit is set. It accepts the contents of location 0500 as another indirect address and loads A with the contents of address 1234.

In 65K mode the instruction would load A with the contents of location 8500.

5. Relative (address mode bits equal 8, 9, A, or B). The relative flag is 1, indirect address flag is 0, and delta does not equal zero. The base address is equal to the instruction address, P, plus the value of delta with sign extended. The contents of the index registers, when specified, are added to the base address to form the effective address.

The address referenced by this mode is located forward or backward relative to the P in the program. The delta portion of the instruction is evaluated with a sign extension which makes it possible to subtract from the current address.

Example:

$$P = C805$$

$P + 5 = 1234$

The instruction address, P, is augmented by 0005, and the computer loads A with 1234.

$$P(0100) = C883$$

In this case, the quantity delta is negative (bit 7 is set) so that P (0100) plus FF83 is 0084. The A register is then loaded with the contents of location 0084.

One or both index registers can be added to the base address to form the effective address.

6. <u>16-Bit Relative</u> (address mode bits equal 8, 9, A, or B). The relative address flag is 1, the indirect address flag is 0, and delta is 0. If no indexing is specified, the instruction address P + 1 plus the contents of location P + 1 form the base address, which in this case equals the effective address. If indexing is specified, the contents of the specified index register(s) are added to the base address to form the effective address.

This mode is very similar to relative except the base address is formed from P+1+(P+1) instead of  $P+\Delta$ .

Example:

$$P(010E) = C800$$

$P + 1 (010F) = 0011$

Effective Address (0120) = 1234

The contents of P+1 are added to P+1 resulting in an effective address of 0120, and 1234 is loaded into the A register. Since the address referenced is relative to P+1, a program can be relocated easily.

- 7. Relative Indirect (address mode bits equal C, D, E, or F). Both relative and indirect flags are 1.

- a. Delta does not equal zero. The value of instruction address P plus the value of delta with sign extended is an indirect address. If bit 15 of this indirect address is 0, this indirect address is the base address. If bit 15 is a 1, and the computer is in 32K mode, the contents of the indirect address is another indirect address. In 65K mode all 16 bits of the first indirect address is the base address, and indirect addressing does not continue. However, in 32K mode indirect addressing continues until bit 15 of the indirect address is 0. The contents of the index registers, when specified, are then added to the base address to form the effective address.

#### 32K Mode Example:

The Load A instruction forms  $P + \Delta (0100 + FFAB)$  which is 00AC. The contents of address 00AC is 8102. Since the sign bit is set, the next indirect address referenced is 0102. The effective address at location 0102 is 00AB. The computer loads 8103 from this location into the A register. The program continues at 0101.

b. Delta equals zero. If bit 15 of [P+1+(P+1)] is a 1, and the computer is in 32K mode, [P+1+(P+1)] is an indirect address. Indirect addressing continues until bit 15 of the contents of an indirect address is 0. Then the contents of the index registers, when specified, are added to the base address to form the effective address. Note that in 65K mode, [P+1+(P+1)] is the base address.

#### 32K Mode Example:

0100 = CC00 0101 = FFFE 4C00 = 0101

The Load A instruction adds P + 1 (0101) to the contents of this address, FFFE, and obtains 0100. This address is referenced; the CC00 indicates that another indirect addressing cycle is necessary (bit 15 is set). Indirect addressing is repeated at 4C00 and produces an effective address of 0101. The A register is loaded with FFFE from this location. The binary bits of C are 1100 and the computer disregards the sign bit to determine the indirect address. For this reason, 4C00 (binary 4 is 0100) is referenced and not location CC00.

## DATA TRANSMISSION

- STQ (F = 4) Store Q. Store the contents of the Q register in the storage location specified by the  $\frac{1}{1}$  effective address. The contents of Q are not altered.

- STA (F = 6) Store A. Store the contents of the A register in the storage location specified by the effective address. The contents of A are not altered.

- SPA (F = 7) Store A, Parity to A. Store the contents of the A register in the storage location specified by the effective address. Clear A if the number of 1 bits in A is odd. Set A equal to  $0001_{16}$  if the number of 1 bits in A is even. The contents of A are not altered if the write into storage is aborted because of parity error or protect fault.

- LDA (F = C) Load A. Load the A register with the contents of the storage location specified by the effective address. The contents of the storage location are not altered.

- LDQ (F = E)  $\frac{\text{Load Q}}{\text{the effective address}}$ . Load the Q register with the contents of the storage location specified by

## ARITHMETIC

All the following arithmetic operations use one's complement arithmetic.

- MUI (F = 2) Multiply Integer. Multiply the contents of the storage location, specified by the effective address, by the contents of the A register. The 32-bit product replaces the contents of Q and A, the most significant bits of the product in the Q register.

- DVI (F = 3) Divide Integer. Divide the combined contents of the Q and A registers by the contents of the effective address. The Q register contains the most significant bits before dividing. If a 16-bit dividend is loaded into A, the sign bit of A must be extended throughout Q. The quotient is in the A register and the remainder is in the Q register at the end of the divide operation.

The OVERFLOW indicator is set if the magnitude of the quotient is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

ADD (F = 8) Add to A. Add the contents of the storage location specified by the effective address to the contents of the A register.

The OVERFLOW indicator is set if the magnitude of the sum is greater than the capacity of the A register. Once set, the OVERFLOW indicator remains set until a Skip On Overflow (SOV) or Skip On No Overflow (SNO) instruction is executed.

- SUB (F = 9) Subtract From A. Subtract the contents of the storage location specified by the effective address from the contents of the A register. Operation on overflow is the same as for an Add to A instruction.

- RAO (F = D)

Replace Add One in Storage. Add one to the contents of the storage location specified by the effective address. The contents of A are not altered. Operation on overflow is the same as for an Add to A instruction.

- ADQ (F = F)

Add to Q. Add the contents of the storage location specified by the effective address to the contents of the Q register. Operation on overflow is the same as for an Add to A instruction.

3-10 89633400

## LOGICAL

The AND (AND with A) instruction achieves its result by forming a logical product is a bit-by-bit multiplication of two binary numbers according to the following rules:

$$0 \times 0 = 0$$

$1 \times 0 = 0$   $0 \times 1 = 0$   $1 \times 1 = 1$

Example:

0001 Logical Product

A logical product is used, in many cases, to select only specific portions of an operand for use in some operation. For example, if only a specific portion of an operand in storage is to be entered into the A register, the operand is subjected to a mask in A. This mask is composed of a predetermined pattern of 0s and 1s. Executing the AND instruction causes the operand to retain its original contents only in those bits which have 1s in the mask in A.

The EOR (Exclusive OR with A) instruction achieves its result by forming an exclusive OR. Executing the EOR instruction causes the operand to complement its original contents only in those bits which have 1s in the mask in A. An exclusive OR is a bit-by-bit logical subtraction of two binary numbers according to the following rules:

#### Exclusive OR

| <u>A</u> | <u>B</u> | <u>A <del>-&gt;-</del> B</u> |

|----------|----------|------------------------------|

| 1        | 1        | 0                            |

| 1        | 0        | 1                            |

| 0        | 1        | 1                            |

| 0        | 0        | 0                            |

|          |          |                              |

Example:

0011 Operand A 0101 Operand B

0110 Exclusive OR

- AND (F = A) AND with A. Form the logical product, bit by bit, of the contents of the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.

- EOR (F = B) Exclusive OR with A. Form the logical difference (exclusive OR), bit by bit, of the contents of the storage location specified by the effective address and the contents of the A register. The result replaces the contents of A. The contents of storage are not altered.

## **JUMPS**

A Jump (JMP) instruction causes a current program sequence to terminate and initiates a new sequence at a different location in storage. The program address register, P, provides continuity between program instructions and always contains the storage location of the current instruction in the program.

When a Jump instruction occurs, P is cleared and a new address is entered.\* In the Jump instruction, the effective address specifies the beginning address of the new program sequence. The word at the effective address is read from storage and interpreted as the first instruction of the new sequence.

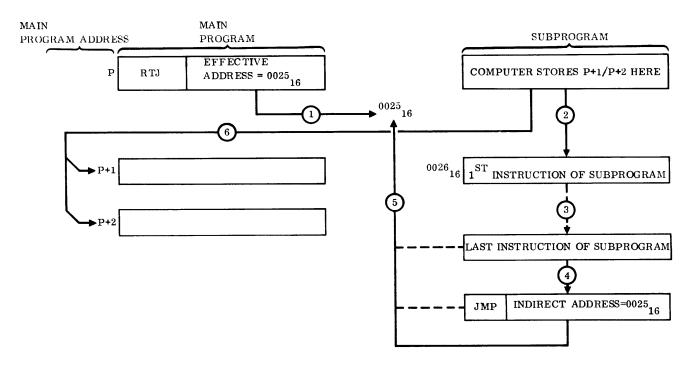

A Return Jump (RTJ) instruction enables the computer to leave the main program, jump to some subprogram, execute the subprogram, and return to the main program via another instruction. The Return Jump provides the computer with the necessary information to enable returning to the main program. Figure 3-2 shows how a Return Jump instruction can be used.

Figure 3-2. Program Using Return Jump Instruction

3-12 89633400

<sup>\*</sup>Jumps or return jumps from unprotected to protected storage cause a fault, but the address that is saved in the trap location is the destination address (i.e., the address of the next sequential main program instruction). See Programming Requirements in Section 4.

A Return Jump instruction is executed at main program address P. The computer jumps to effective address  $0025_{16}$  and stores P + 1 or P + 2 (depending on the address mode of RTJ) at this location. Then the program address counter P is set to  $0026_{16}$  and the computer starts executing the subprogram. At the end of the subprogram, the computer executes a Jump instruction (JMP) with indirect addressing. This causes the computer to jump to the address specified by the subprogram address  $0025_{16}$  (P + 1 or P + 2 of the main program). Now main program execution continues at P + 1 or P + 2.

- JMP (F = 1) Jump. Jump to the address specified by the effective address. This effectively replaces the contents of program address counter P with the effective address specified in the Jump instruction.

- RTJ (F = 5) Return Jump. Replace the contents of the storage location specified by the effective address with the address of the next consecutive instruction. The address stored in the effective address is P + 1 or P + 2, depending on the addressing mode of RTJ. The contents of P are then replaced with the effective address plus one.

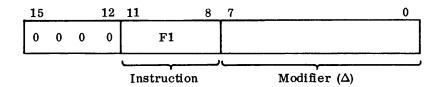

#### REGISTER REFERENCE INSTRUCTIONS

Register reference instructions use the address mode field for the operation code. Register reference instructions are identified when the upper four bits (15 through 12) of an instruction are 0s.

Format:

- SLS (F1 = 0) Selective Stop. Stops the computer if this instruction is executed when the selective stop switch is on. On restart, the computer executes the instruction at P + 1. This becomes a Pass instruction when the selective stop switch is off.

- INP (F1 = 2) Input to A. Reads one word from an external device into the A register. The word in the Q register selects the sending device. If the device sends a Reply, the next instruction comes from P + 1. If the device sends a Reject, the next instruction comes from P + 1 +  $\Delta$ , where delta is an eight-bit signed number. If an internal Reject occurs, the next instruction comes from P +  $\Delta$ . Refer to Section 5, Input/Output.

- OUT (F1 = 3) Output from A. Outputs one word from the A register to an external device. The word in the Q register selects the receiving device. If the device sends a Reply, the next instruction comes from P+1. If the device sends a Reject, the next instruction comes from  $P+1+\Delta$ , where delta is an eight-bit signed number. If an internal Reject occurs, the next instruction comes from  $P+\Delta$ . Refer to Section 5, Input/Output.

89633400 3-13

- INA (F1 = 9) Increase A. Replaces the contents of A with the sum of the initial contents of A and delta, where delta is treated as a signed number with the sign extended into the upper eight bits. Operation on overflow is the same as for an Add to A instruction.

- ENA (F1 = A) Enter A. Replaces the contents of the A register with the eight-bit delta, sign extended.

- NOP (F1 = B) No Operation. This is a Pass instruction (no operation is performed). Compares to Selective Stop instruction with the STOP switch off.

- ENQ (F1 = C) Enter Q. Replaces the contents of the Q register with the eight-bit delta, sign extended.

- INQ (F1 = D) Increase Q. Replaces the contents of Q with the sum of the initial contents of Q and delta, where delta is treated as a signed number with the sign extended into the upper eight bits. Operation on overflow is the same as for an Add to A instruction.

The following instructions (F1 equals 4, 5, 6, 7, or E) are legal only if the program protect switch is off or if the instructions themselves are protected (refer to Section 4). If an instruction is illegal, it becomes a selective stop and an interrupt on program protect fault is possible (if selected).

- -Protect switch on: Selective stop unless instruction is protected.

- -Protect switch off: Normal instruction execution (no program protection)

- EIN (F1 = 4) Enable Interrupt. Activates the interrupt system after one instruction following EIN has been executed. The interrupt system must be active and the appropriate mask bit set for an interrupt to be recognized.

- IIN (F1 = 5) Inhibit Interrupt. Deactivates the interrupt system. If interrupt occurs during execution of this instruction, the interrupt is not recognized until one instruction after the next EIN instruction is executed.

- SPB (F1 = 6) Set Program Protect Bit. Sets the program protect bit in the address specified by Q.

- CPB (F1 = 7) Clear Program Protect Bit. Clears the program protect bit in the address specified by Q.

- EXI (F1 = E) Exit Interrupt State. This instruction must be used to exit from any interrupt state.

Delta defines the interrupt state from which the exit is taken (see Table 4-1). This instruction automatically reads the address containing the return address, then jumps to the return address. In addition, if the computer is in 32K mode, this instruction also sets the OVERFLOW indicator to the state of bit 15 in the return address. This bit records the state of the OVERFLOW indicator when the interrupt occurred. In 65K mode this instruction does not reset the OVERFLOW indicator. Refer to the section on Programming and Operation of the Interrupt System for an explanation of the overflow condition in 65K mode.

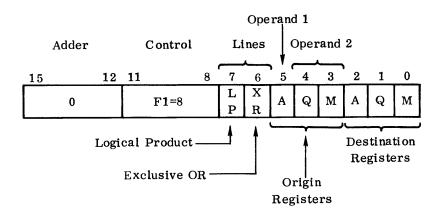

#### INTER-REGISTER

These instructions cause data from certain combinations of two origin registers to be sent through the adder to any combination of destination registers. Various operations, selected by the adder control lines, are performed on the data as it passes through the adder.

#### Format:

If bit 0 of an Inter-register instruction is set (M is the destination register) and the instruction is not protected it is a program protect violation and becomes a non-protected Selective Stop instruction. The program protect fault bit is set and interrupt occurs if selected. See Section 4 for additional information.

The origin registers are considered as operands. There are two kinds, defined as follows:

- Operand 1 may be:

- -FFFF (bit 5 is 0) or

- -The contents of A (bit 5 is 1)

- Operand 2 may be:

- -FFFF (bit 4 is 0 and bit 3 is 0) or

- -The contents of M (bit 4 is 0 and bit 3 is 1) or

- -The contents of Q (bit 4 is 1 and bit 3 is 0) or

- -The inclusive OR, bit by bit, of the contents of Q and M (bit 4 is 1 and bit 3 is 1)

The following operations are possible (see Table 3-3):

- Exclusive OR (LP = 0 and XR = 1). The data placed in the destination register(s) is the exclusive OR, bit by bit, of operand 1 and operand 2.

- Logical Product (LP = 1 and XR = 0). The data placed in the destination register(s) is the logical product, bit by bit, of operand 1 and operand 2.

- Complement Logical Product (LP = 1 and XR = 1). The data placed in the destination register(s) is the complement of the logical product, bit by bit, of operand 1 and operand 2.

- Arithmetic Sum (LP = 0 and XR = 0). The data placed in the destination register(s) is the arithmetic sum of operand 1 and operand 2. The OVERFLOW indicator operates the same for an Add to A instruction.

Table 3-3. Inter-register Instruction Truth Table

| OPERAND<br>1 | OPERAND<br>2 | EXCLUSIVE<br>OR<br>LP = 0<br>XR = 1 | LOGICAL<br>PRODUCT<br>LP = 1<br>XR = 0 | COMPLEMENT LOGICAL PRODUCT LP = 1 XR = 1 | LP = 0<br>XR = 0 |

|--------------|--------------|-------------------------------------|----------------------------------------|------------------------------------------|------------------|

| 0            | 0            | 0                                   | 0                                      | 1                                        |                  |

| 0            | 1            | 1                                   | 0                                      | 1                                        | Arithmetic       |

| 1            | 0            | 1                                   | 0                                      | 1                                        | Sum              |

| 1            | 1            | 0                                   | 1                                      | 0                                        |                  |

## Notes:

- a. Register transfers can be accomplished by setting LP and XR to 0 and either operand 1 or operand 2 to  ${\tt FFFF}_{16}$ .

- b. Magnitude comparisons can be made without destroying either operand by setting LP and XR to 0, selecting no destination register, and then testing the OVERFLOW indicator.

Assume we wish to test a set of operands, N, to exceed the value of one operand, M, The test value to be used is that number, P, which when added to M produces a sum which exceeds the register capacity by one bit, causing overflow. If the sum of N and P causes overflow:

$$N \ge M \text{ if } M > 0$$

and  $N \le M \text{ if } M < 0$ .

c. Registers can be complemented by setting LP to 0, XR to 1, and either operand 1 or operand 2 to FFFF<sub>16</sub>.

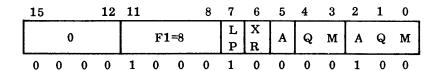

Destination register bits must be determined and the whole instruction written out.

## Example:

Set A to Ones is 0884 since bits 7 and 2 are 1 and all others from 0 through 7 are 0.

## INTER-REGISTER MNEMONICS

| SET (F1 = 8, bits 7 through 3 = 10000)    | Set To Ones                                  |

|-------------------------------------------|----------------------------------------------|

| CLR (F1 = 8, bits 7 through 3 = 01000)    | Clear to Zero                                |

| TRA (F1 = 8, bits 7 through 3 = 10100)    | Transfer A*                                  |

| TRM (F1 = 8, bits 7 through $3 = 10001$ ) | Transfer M*                                  |

| TRQ (F1 = 8, bits 7 through $3 = 10010$ ) | Transfer Q*                                  |

| TRB (F1 = 8, bits 7 through 3 = 10011)    | Transfer Q + M*                              |

| TCA (F1 = 8, bits 7 through $3 = 01100$ ) | Transfer Complement A*                       |

| TCM (F1 = 8, bits 7 through $3 = 01001$ ) | Transfer Complement M*                       |

| TCQ (F1 = 8, bits 7 through 3 = 01010)    | Transfer Complement Q*                       |

| TCB (F1 = 8, bits 7 through $3 = 01011$ ) | Transfer Complement Q + M*                   |

| AAM (F1 = 8, bits 7 through $3 = 00101$ ) | Transfer Arithmetic Sum A, M                 |

| AAQ (F1 = 8, bits 7 through $3 = 00110$ ) | Transfer Arithmetic Sum A, Q                 |

| AAB (F1 = 8, bits 7 through 3 = 00111)    | Transfer Arithmetic Sum A, Q + M             |

| EAM (F1 = 8, bits 7 through $3 = 01101$ ) | Transfer Exclusive OR A, M                   |

| EAQ (F1 = 8, bits 7 through $3 = 01110$ ) | Transfer Exclusive OR A, Q                   |

| EAB (F1 = 8, bits 7 through 3 = 01111)    | Transfer Exclusive OR A, Q + M               |

| LAM (F1 = 8, bits 7 through $3 = 10101$ ) | Transfer Logical Product A, M                |

| LAQ (F1 = 8, bits 7 through $3 = 10110$ ) | Transfer Logical Product A, Q                |

| LAB (F1 = 8, bits 7 through 3 = 10111)    | Transfer Logical Product A, Q + M            |

| CAM (F1 = 8, bits 7 through 3 = 11101)    | Transfer Complement Logical Product A, M     |

| CAQ (F1 = 8, bits 7 through 3 = 11110)    | Transfer Complement Logical Product A, Q     |

| CAB (F1 = 8, bits 7 through 3 = 11111)    | Transfer Complement Logical Product A, Q + M |

Note: "+" symbol implies an inclusive OR.

89633400 3-17

<sup>\*</sup>The use of bit 7 is optional; it may be a 1 or a 0. The assembler uses bit 7 = 0.

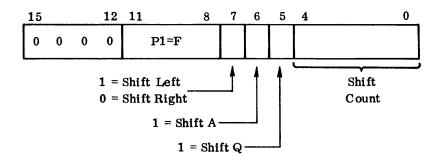

## **SHIFTS**

The Shift instructions shift A, Q, or QA left or right the number of places specified by the five-bit shift count. Right shifts are end-off with sign extension in the upper bits. Left shifts are end-around. The maximum long-right or long-left shift is 1F places.

#### Format:

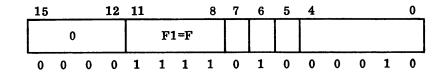

Bit configurations must be determined for each instruction.

Example: Shift A right two places is 0F42.

## SHIFT MNEMONICS

| ARS (F1 = F, bits 7 through $5 = 010$ ) | A Right Shift         |

|-----------------------------------------|-----------------------|

| QRS (F1 = F, bits 7 through $5 = 001$ ) | Q Right Shift         |

| LRS (F1 = F, bits 7 through 5 = 011)    | Long Right Shift (QA) |

| ALS (F1 = F, bits 7 through $5 = 110$ ) | A Left Shift          |

| QLS (F1 = F, bits 7 through $5 = 101$ ) | Q Left Shift          |

| LLS (F1 = F, bits 7 through 5 = 111)    | Long Left Shift (QA)  |

3-18 89633400

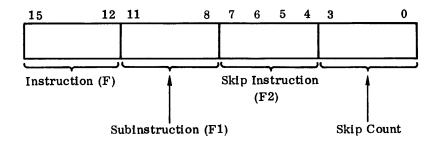

## SKIP INSTRUCTIONS

Skip instructions are identified when the instruction mode field is zero and the subinstruction mode field is one.

## Format:

When the skip condition is met, the skip count plus one is added to P to obtain the address of the next instruction (e.g., when the skip count is zero, go to P+1). When the skip condition is not met, the address of the next instruction is P+1 (skip count ignored). The skip count does not have a sign bit.

| SAZ (F2 = 0)   | Skip if A is positive zero (all bits are 0)                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| SAN $(F2 = 1)$ | Skip if A is not positive zero (not all bits are 0)                                                                                  |

| SAP $(F2 = 2)$ | Skip if A is positive (bit 15 is 0)                                                                                                  |

| SAM (F2 = 3)   | Skip if A is negative (bit 15 is 1)                                                                                                  |

| SQZ (F2 = 4)   | Skip if Q is positive zero (all bits are 0)                                                                                          |

| SQN (F2 = 5)   | Skip if Q is not positive zero (all bits are not 0)                                                                                  |

| SQP (F2 = 6)   | Skip if Q is positive (bit 15 is 0)                                                                                                  |

| SQM (F2 = 7)   | Skip if Q is negative (bit 15 is 1)                                                                                                  |

| SWS (F2 = 8)   | Skip if selective skip switch is set                                                                                                 |

| SWN (F2 = 9)   | Skip if selective skip switch is not set                                                                                             |

| SOV $(F2 = A)$ | Skip on Overflow. This instruction skips if an overflow condition is sensed. This instruction clears the OVERFLOW indicator.         |

| SNO $(F2 = B)$ | Skip on No Overflow. This instruction skips if an overflow condition is not present. This instruction clears the OVERFLOW indicator. |

89633400 3-19

| SPE | (F2 | = | CI |

|-----|-----|---|----|

|     |     |   |    |

Skip on Storage Parity Error. This instruction skips if a storage parity error occurred; it clears the Storage Parity Error Interrupt signal and the PARITY FAULT indicator.

SNP (F2 = D)

Skip on No Storage Parity Error.

SPF (F2 = E)

Skip on Program Protect Fault. Program protect fault is set by:

- A nonprotected instruction attempting to write into an address which is protected.

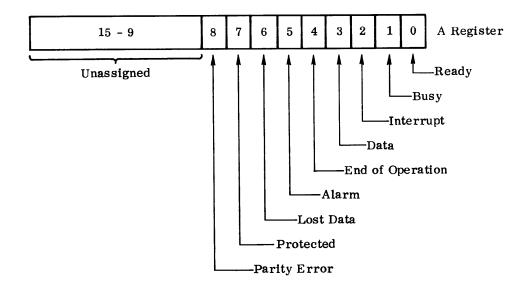

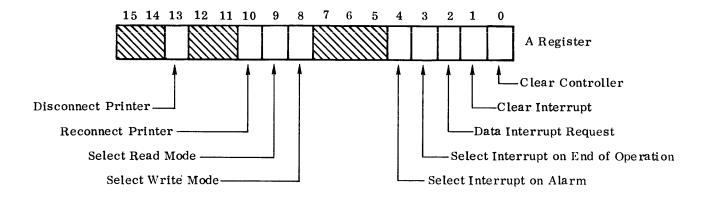

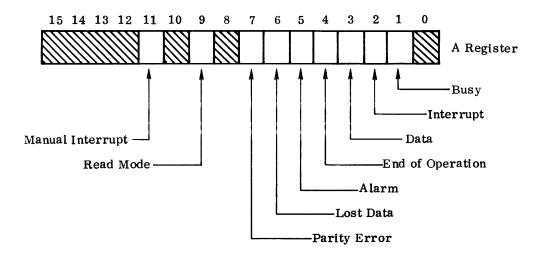

- An attempt to execute a protected instruction immediately following a nonprotected instruction unless an interrupt caused the instruction sequence.