CONTROL DATA CORPORATION

Development Division - Applications

# THE DEAD START PROCESS AND THE SYSTEM LOADER

Chippewa Operating System

# THE DEAD START PROCESS AND THE SYSTEM LOADER

# INTRODUCTION

The dead start process requires that a short program (up to 12 instructions) be set up on the matrix of toggle switches on the dead start panel. When the dead start switch is toggled, this dead start program is transmitted to peripheral processor zero's memory and executed. The dead start program in turn transmits a bootstrap program to another peripheral processor. This bootstrap program brings in the system loader from the library tape and transfers control to it. The system loader transfers a resident program to each peripheral processor, causes the Display and Monitor programs to be loaded, loads the central memory resident, library, and tables, and places the remaining library programs on the disk. It then inititates execution of the Display and Monitor programs.

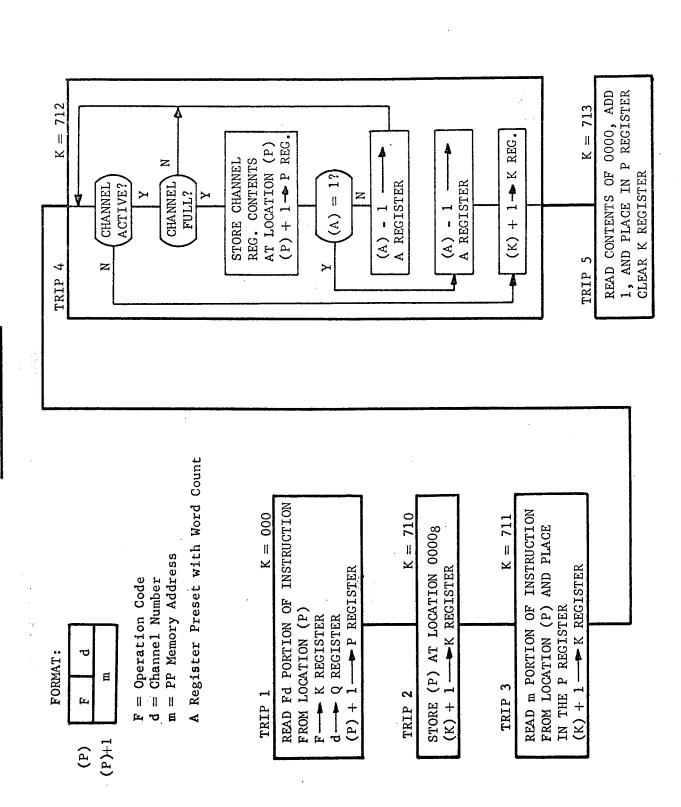

# THE IAM INSTRUCTION

A detailed understanding of the dead start loading process requires some familiarity with the functioning of the IAM instruction. The IAM instruction is a 24-bit instruction: the d portion of the instruction holds the channel number and the m portion of the instruction contains the address in peripheral processor memory where the first data word is to be stored. The A register is assumed to contain the number of words to be read. The functioning of the IAM instruction is shown in figure 1. Note the following points:

• During execution of the IAM instruction, the contents of the P register are stored in location 0, and the P register used to hold the memory address for the next word to be stored. At the time the contents of the P register are stored, P holds the address of the second word (m

- portion) of the IAM instruction. Before exiting the instruction, the contents of location 0 are read, incremented by one, and placed in the P register to provide the address of the next instruction.

- The IAM instruction tests the word count in the A register to see if it has been reduced to one: if so, (A) is reduced by one and the instruction exited. Therefore, if the IAM instruction is entered with the contents of the A register equal to zero, the word count is effectively 777778.

- The IAM instruction may be exited in one of two ways: (1) because the word count has been reduced to zero or (2) because the channel has become inactive. If the word count has not been reduced to zero and the channel is active, exit will not take place even though no data is being read: the processor will idle in trip 4, waiting for the channel to become full.

### THE DEAD START SEQUENCE

When the dead start switch is toggled, the following sequence is initiated:

- The Master Clear signal is generated

- The A register of each peripheral processor is set to 100008: the P register of each peripheral processor is set to zero

- The K register of each peripheral processor is set to 712 (trip 4 of an IAM instruction)

- All channels are set to empty and active

- All peripheral processors are connected to their respective channels (i.e., PPO to channel 0, PPI to channel 1, etc.) by setting the appropriate channel number in each processor's Q register

- The first synchronizer on each channel is selected: the first unit on that synchronizer is selected

- The dead start synchronizer is selected on channel 0

- The program on the dead start panel is transferred to PPO memory: first, a zero byte is transmitted (stored in location 0); next, the 12 bytes from the panel switches are transmitted (stored in location 1 14); finally, another zero byte is transmitted (stored in location 15)

• The dead start synchronizer disconnects channel 0, initiating the execution of the dead start program

Peripheral processor zero treats the data sent by the dead start synchronizer as it would data arriving from any other controller. When the dead start synchronizer disconnects from channel zero, peripheral processor zero exits from the IAM instruction. In exiting, the contents of location 0 are incremented by 1 and used as the address of the next instruction. Since this location was cleared to 0 by the dead start process, the address of the next instruction is 0001: this location holds the first instruction of the program sent by the dead start synchronizer from the dead start panel.

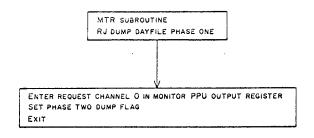

# THE DEAD START PROGRAM

The dead start program is shown in figure 2. The purpose of the dead start program is to transmit a bootstrap program to peripheral processor xx (PPxx), where xx is the channel number of the controller on which the system tape is mounted. The dead start program begins by transmitting a block of 8 words on channel xx. PPxx is connected to this channel and is idling in trip 4 of an IAM instruction: it will therefore read in these 8 words and store them in its memory beginning at location 0. PPxx will not, however, begin execution yet, since the channel is still active and the word count has not been reduced to zero.

The dead start program next disconnects channel xx: when channel xx becomes inactive, PPxx exits from the IAM instruction and begins execution of the bootstrap program. In exiting from the IAM instruction, the contents of location 0 are read, incremented by 1, and used as the address of the next instruction. Since the first word of the 8-word block sent by PPO was equal to zero, this address is equal to 0001, and the instruction at this address is read and executed.

The dead start program then issues an input instruction for channel 13: since

# THE DEAD START PROGRAM

$\mathbf{x}\mathbf{x} = \mathbf{CHANNEL}$  NUMBER FOR CONTROLLER ON WHICH SYSTEM TAPE IS MOUNTED

| FUNCTION                               | SET THE A REGISTER TO 108  OUTPUT 8 WORDS BEGINNING AT LOCATION 0006 ON CHANNEL xx (PROCESSOR xx WILL STORE THESE INTO ITS MEMORY BEGINNING AT LOCATION 0)  DISCONNECT CHANNEL xx (THIS PERMITS PROCESSOR xx TO EXIT FROM THE IAM INSTRUCTION AND BEGIN EXECUTION OF THE PROGRAM IT HAS RECEIVED) |              | SET PPO TO INPUT FROM CHANNEL 13 (CHANNEL 13 | INSTRUCTION UNTIL CHANNEL 13 BECOMES FULL) |      |      |             |                                    |                         |      | CLEARED DURING DEAD START             |      |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------|--------------------------------------------|------|------|-------------|------------------------------------|-------------------------|------|---------------------------------------|------|

| ≅ <b> </b>                             |                                                                                                                                                                                                                                                                                                   |              |                                              |                                            |      |      |             |                                    | ·                       |      |                                       | •    |

| INSTRUCTION                            | 1410                                                                                                                                                                                                                                                                                              | 73××<br>0006 | 75xx                                         | 7113                                       | 0000 | 77xx | 2060        | 77xx                               | 2020                    | 74xx | 71xx                                  | 0000 |

| PPO MEMORY<br>LOCATION                 | 0001                                                                                                                                                                                                                                                                                              | 0002         | 0004                                         | 0005                                       | 9000 | 2000 | 0010        | 0011                               | 0012                    | 0013 | 0014                                  | 0015 |

| <u>р</u> . Г                           | $\uparrow$                                                                                                                                                                                                                                                                                        |              |                                              |                                            |      |      | <del></del> | ·                                  | ·                       |      | · · · · · · · · · · · · · · · · · · · |      |

| THESE INSTRUCTIONS ARE EXECUTED IN PPO |                                                                                                                                                                                                                                                                                                   |              |                                              |                                            |      |      | •           | THESE INSTRUCTIONS ARE TRANSFERRED | TO AND EXECUTED IN PPxx |      |                                       |      |

channel 13 is empty and active, PPO will idle in trip 4 of this instruction waiting for channel 13 to become full.

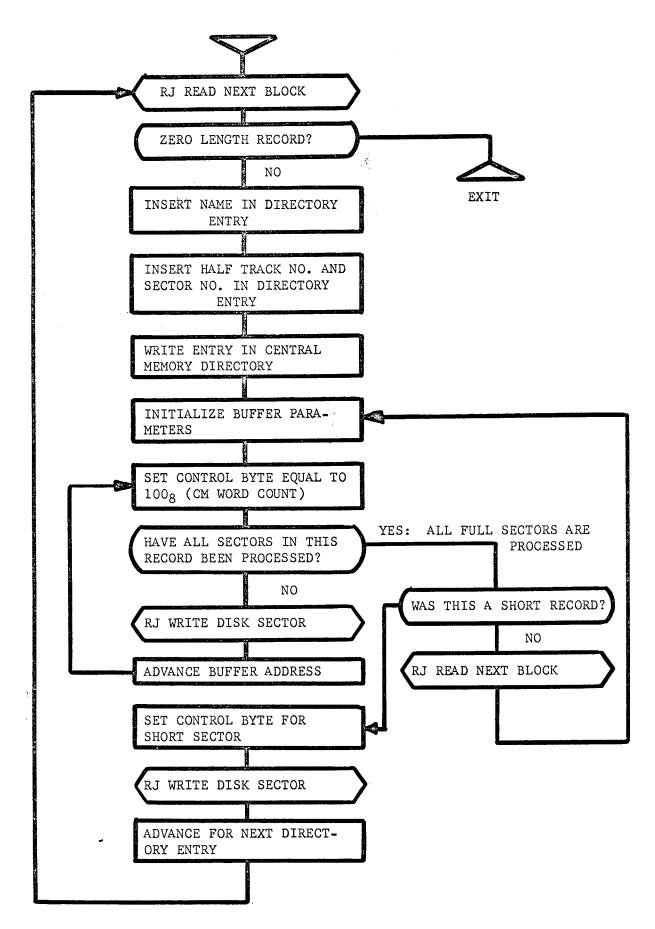

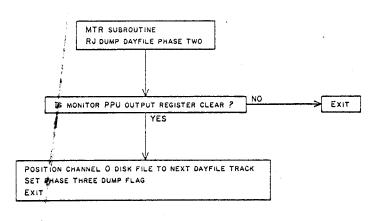

# THE LOADER BOOTSTRAP

The bootstrap program (figure 3) in PPxx issues the necessary function, activate, and input instructions to read the first record on the system tape into its memory beginning at location 0. When this record, which contains the loader program, has been read, PPxx will exit the IAM instruction when the controller disconnects the channel upon detecting the end-of-record gap. PPxx, in exiting the IAM instruction, reads the contents of location 0, adds 1 to it, and uses this as the address of the next instruction. Location 0 contains the first word of the record read from tape: thus, this word supplies the address of the first instruction of the loader program.

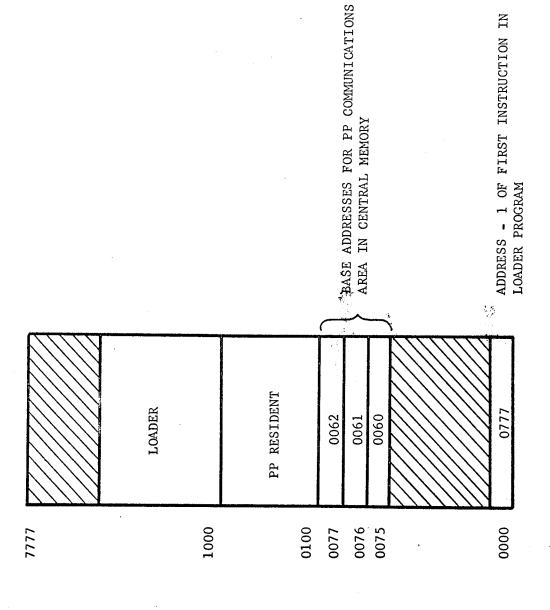

# THE LOADER PROGRAM

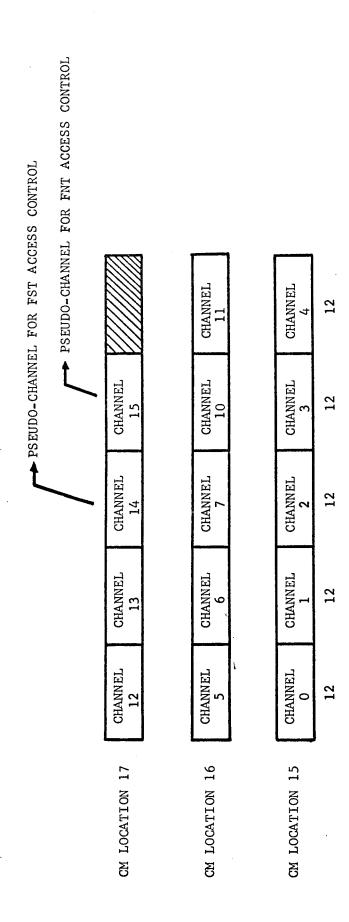

The layout of the loader program in PPxx is shown in figure 4. As mentioned earlier, the first word of the loader program (location 0) contains the address - 1 of the first instruction of the loader. The loader program also contains a peripheral processor resident package in locations 0001 - 07778. This package is transmitted by the loader to each of the other peripheral processors. The resident program is contained in locations 0100 - 07778: locations 75, 76, and 778 contain the values 60, 61, and 62, respectively. These values are the central memory addresses of the Input Register, the Output Register, and the Message Buffer for PP1, and must be modified when the resident package is transmitted to processors other than PP1.

At the time the loader program begins execution, all channels except the channel corresponding to the processor containing the loader program (PPxx) are active and empty: their corresponding processors are idling in an IAM instruction, waiting for input. Channel xx, however, was disconnected by the tape controller

# THE DEAD START PROGRAM

# LOADER BOOTSTRAP

| FUNCTION             | NOT EXECUTED (ADDRESS - 1 OF FIRST INSTRUCTION) | ISSUE FUNCTION CODE: SELECT REWIND | ISSUE FUNCTION CODE: SELECT BINARY READ | ACTIVATE CHANNEL xx (xx DISCONNECTED BY PPO PROGRAM) | <pre>INPUT (A) WORDS FROM CHANNEL xx BEGINNING AT LOCATION 0000 (THE A REGISTER HAS NOT BEEN USED AND STILL CONTAINS 0)</pre> |

|----------------------|-------------------------------------------------|------------------------------------|-----------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| INSTRUCTION          | 0000                                            | 77xx<br>2060                       | 77××<br>2020                            | 74xx                                                 | <b>71xx</b> 0000                                                                                                              |

| PPxx MEMORY LOCATION | 0000                                            | 0001<br>0002                       | 0003                                    | 0005                                                 | 9000                                                                                                                          |

- THE TAPE CONTROLLER WILL DISCONNECT THE CHANNEL WHEN THE END-OF-RECORD GAP IS DETECTED AND THUS CAUSE THE PROCESSOR TO EXIT FROM THE 71 INSTRUCTION.

- THE FIRST WORD FROM TAPE WILL BE READ INTO LOCATION O: ON EXIT FROM THE IAM INSTRUCTION, THE CONTENTS OF LOCATION O ARE READ, INCREMENTED BY 1, AND USED AS THE ADDRESS OF THE NEXT INSTRUCTION.

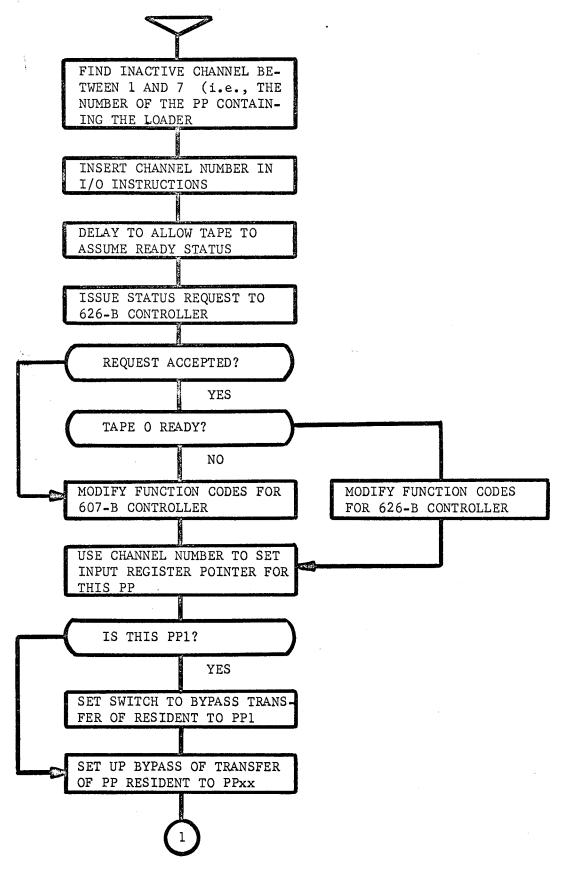

when the end-of-record gap following the loader program was detected, and is therefore inactive. The loader program searches for an inactive channel in order to determine which processor it resides in: it also inserts this channel number in the appropriate I/O instructions.

The loader program then proceeds to determine if the system tape is mounted on a 607-B unit or a 626-B unit, and modifies the function codes accordingly. Transfer of the resident package to each of the other processors then takes place. The loader first outputs a single word to the receiving processor, which stores it in its memory at location zero. Since the receiving processor is in trip 4 of an IAM instruction, it will, upon exiting this instruction, use the contents of location 0 as the address - 1 of the next instruction it is to execute. For processors 1 - 8, this address is  $77_8$ : the address - 1 of the first instruction of the resident program. For processors 0 and 9, this address is  $777_8$ : the address - 1 of the first instruction of the MTR and DSD programs, respectively. After transmitting this single word, the loader then transmits the resident package, which the receiving processor stores in its memory beginning at location 0001. The receiving processor does not exit the IAM instruction at this time, however, since the conditions for exiting (either word count reduced to zero or channel inactive) have not been met. As the transfer of each resident takes place, the loader program modifies the Input Register, Output Register, and Message Buffer pointers to the proper values for each processor.

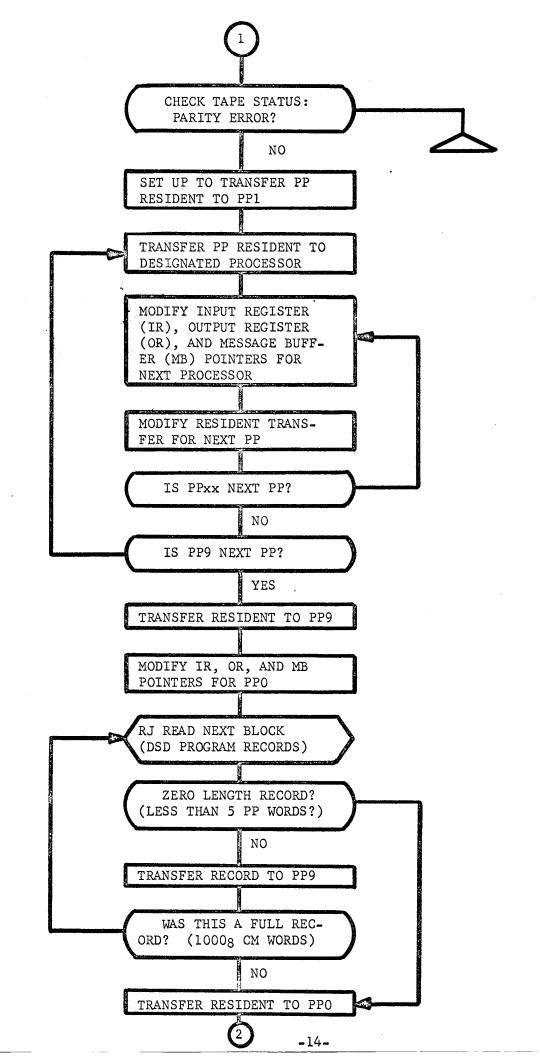

When all processors have been loaded with the resident package, the loader program then proceeds to load the MTR and DSD programs from the system tape into processors 0 and 9, respectively.

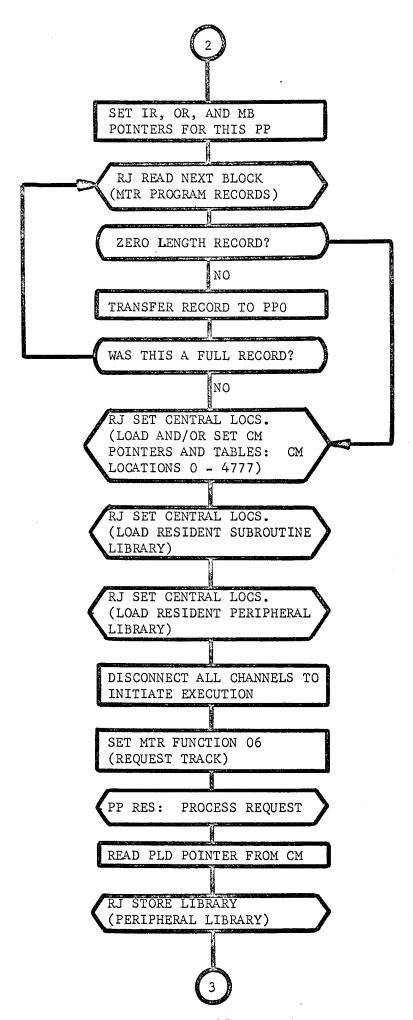

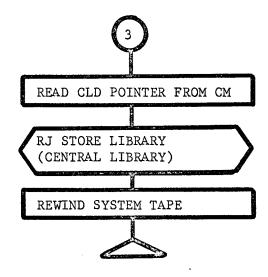

The format of the system tape is illustrated in figure 5. The tape contains a single file of binary records: a full physical record contains  $1000_8$  CM words. A logical record, such as the MTR program or the CM resident, may be composed of more than one physical record: the last physical record for a specific program may be a short record of less than  $1000_8$  CM words. The end of a logical record is indicated when a short physical record is processed or when a zero length record

LOADER PROGRAM LAYOUT IN PPxx

(RECORD 1 ON SYSTEM TAPE)

(4 PP words) is detected, except for the disk library routines: the end of each disk library routine is indicated by a short record only. The end of a library is indicated by a zero length record.

The loader reads the records comprising the DSD program, transferring each record as it is read to PP9: when a short record is processed or a zero length record is detected, loading of the DSD program is complete. This process is repeated for the MTR program records.

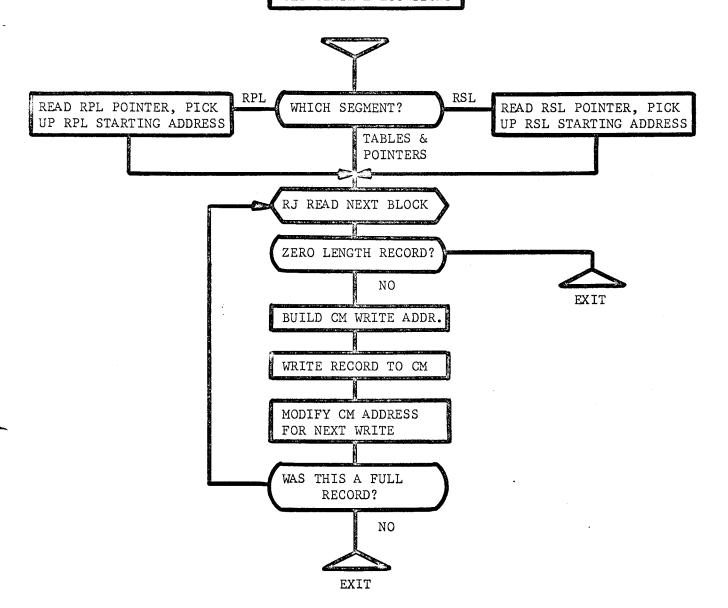

The CM Resident is loaded next. This resident contains table pointers and initial values for certain tables, such as the track reservation tables. The resident subroutine library is loaded using the RSL pointer from the CM Resident to provide the starting address: the resident peripheral library (RPL) is similarly loaded. In all three cases (CM Resident, RSL, and RPL), records are read and transferred to central memory until either a zero length record is detected or a short record is processed.

The loader program then disconnects the channels for each of the other processors, permitting these processors to exit from the IAM instruction and begin execution

of their programs. Now that MTR is executing, the loader program can utilize the

assistance of MTR in loading the libraries on the disk.

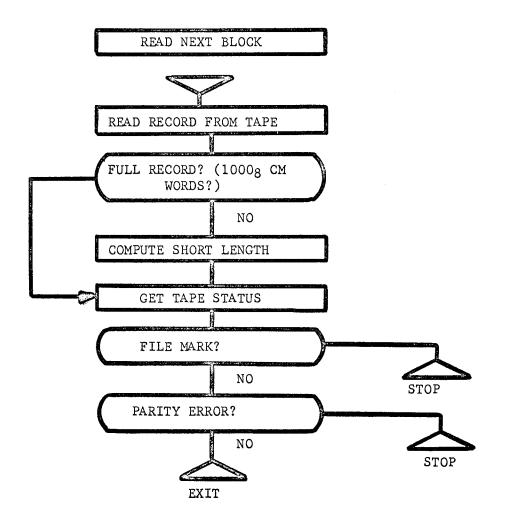

The loader requests a track from MTR via its resident, and picks up the Peripheral Library Directory pointer from central memory in order to obtain the starting address of the directory. It then reads a record from the system tape, builds the PLD entry and writes it in the directory, and transfers the record to the disk. The next record is then read from tape and written to the disk: this process continues until a short record is processed, indicating that a complete program has been transferred. The next record is read from tape, the directory entry constructed and written in the directory, and the process of reading records from tape and transferring them to the disk repeated. The end of a library is indicated by the detection of a zero length record.

When the peripheral library has been transferred to the disk, the transfer of the central library to the disk is initiated and executed in the same manner.

| CENTRAL LIBRARY ERO LENGTH RECORD ERO LENGTH RECORD LIBRARY LIBRARY LIBRARY LIBRARY CM RESIDENT CM RESIDENT  RESIDENT RESIDENT RESIDENT CM RESIDENT  RESIDENT CM RESIDENT  RESIDENT SYSTEM DISPLAY) SYSTEM LOADER | 41 |                    |  |                       | T        |                                |   |                           |  |                  |  |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------------|--|-----------------------|----------|--------------------------------|---|---------------------------|--|------------------|--|---|

|                                                                                                                                                                                                                   | 1  | CENTRAL<br>LIBRARY |  | PERIPHERAL<br>LIBRARY | RESIDENT | ${f PERIPHERAL} \ {f LIBRARY}$ | , | RESIDENT<br>SUBR, LIBRARY |  | MTR<br>(MONITOR) |  | i |

- SYSTEM TAPE CONTAINS A SINGLE FILE OF BINARY RECORDS

- A FULL PHYSICAL RECORD IS A BLOCK OF 10008 CM WORDS

- A LOGICAL RECORD (i.e., MTR, RPL, etc.) MAY BE COMPOSED OF A NUMBER OF PHYSICAL RECORDS

- THE END OF A LOGICAL RECORD IS INDICATED WHEN A SHORT RECORD IS PROCESSED OR WHEN A ZERO LENGTH RECORD (4 BYTES) IS DETECTED THE END OF PERIPHERAL LIBRARY OR CENTRAL LIBRARY ROUTINES IS INDICATED BY A SHORT RECORD ONLY: THE END OF THE LIBRARY IS INDICATED BY A ZERO LENGTH RECORD

BEGINNING OF TAPE

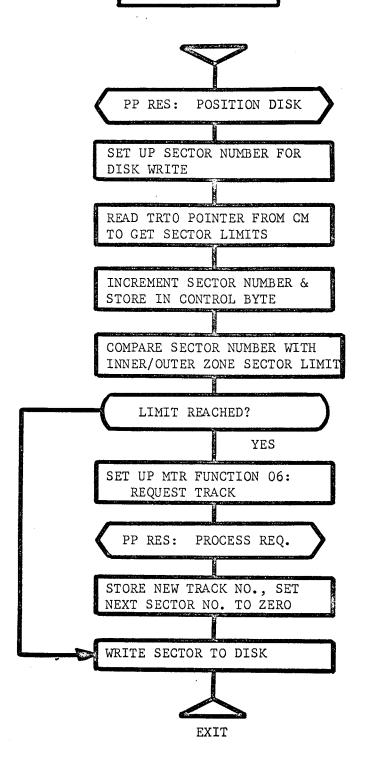

When a half track is filled during library transfers to the disk, the loader program requests a new half track from MTR via its (the loader's) resident program. The resident's POSITION DISK routine is used to position the disk to the new half track position.

When the transfer of the central library to the disk is completed, the loader program exits to the idle loop of its resident.

# Notes:

- 1. For the loading process described, the system tape should be mounted on unit zero of the first controller on channel xx. If channel xx has both 607-B and 626-B controllers, the unused controller's unit zero should be made not ready. The channel xx may be any channel from 1 to 9.

- 2. In addition to the bootstrap routine described, a variety of others are in use. Many of these use a one-card loader.

-15-

EXIT TO PPxx RESIDENT IDLE LOOP

# SET CENTRAL LOCATIONS

# CONTROL DATA CORPORATION Development Division - Applications

# POOL PROCESSORS AND PERIPHERAL PROCESSOR RESIDENTS

Chippewa Operating System

# POOL PROCESSORS AND PERIPHERAL PROCESSOR RESIDENTS

# INTRODUCTION

In the Chippewa Operating System, the System Display program (DSD) and the Monitor program (MTR) permanently reside in two of the ten peripheral processors. MTR and DSD reside in processors 0 and 9, respectively. The remaining processors, 1 - 8, form a pool of processors to which MTR may assign tasks as required. These pool processors have no fixed assignments: any processor may be assigned to the execution of any system routine, and it is possible that more than one processor may be executing the same routine at the same time. All ten processors contain a small resident program which handles the communications between pool processor programs and the Monitor, and initiates the execution of these programs as directed by MTR.

### POOL PROCESSOR STRUCTURE

The structure of a pool processor is illustrated in figure 1. The resident program is contained in locations 0100 - 0772: locations 75, 76, and 77 contain pointers to the Input Register, the Output Register, and Message Buffer in central memory. When directed to do so by MTR, the resident loads a program into its memory and executes it: since that program remains in that processor only for the period of time required to perform its function, it is called a transient program. Transient programs occupy locations 0773 - 1772, although the first instruction is at location 1000. Transient programs generally load overlays to perform specific tasks. For example, CIO, which is a transient program, calls various overlays depending on the task (read, write, backspace) and the equipment (disk, tape, etc.) specified. Overlays are loaded into memory beginning

POOL PROCESSORS & PP RESIDENT

at location 1773: the first instruction falls at location 2000. Overlays are generally entered via a return jump. Transient programs have names beginning with a letter (CIO, EXU) or the numeral 1 (1BJ, 1LT): overlays have names beginning with the numeral 2 (2WD, 2BP, etc.).

Both transient and overlay programs, as well as the resident program, make extensive use of the low core locations 01 - 74.

# THE RESIDENT

The peripheral processor resident program has two main functions to perform:

- all communication between MTR and the transient or overlay programs is handled by the resident;

- the resident, when directed by MTR, loads transient programs from either the RPL or the disk library and initiates the execution of these programs.

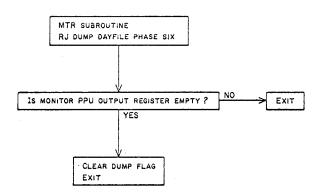

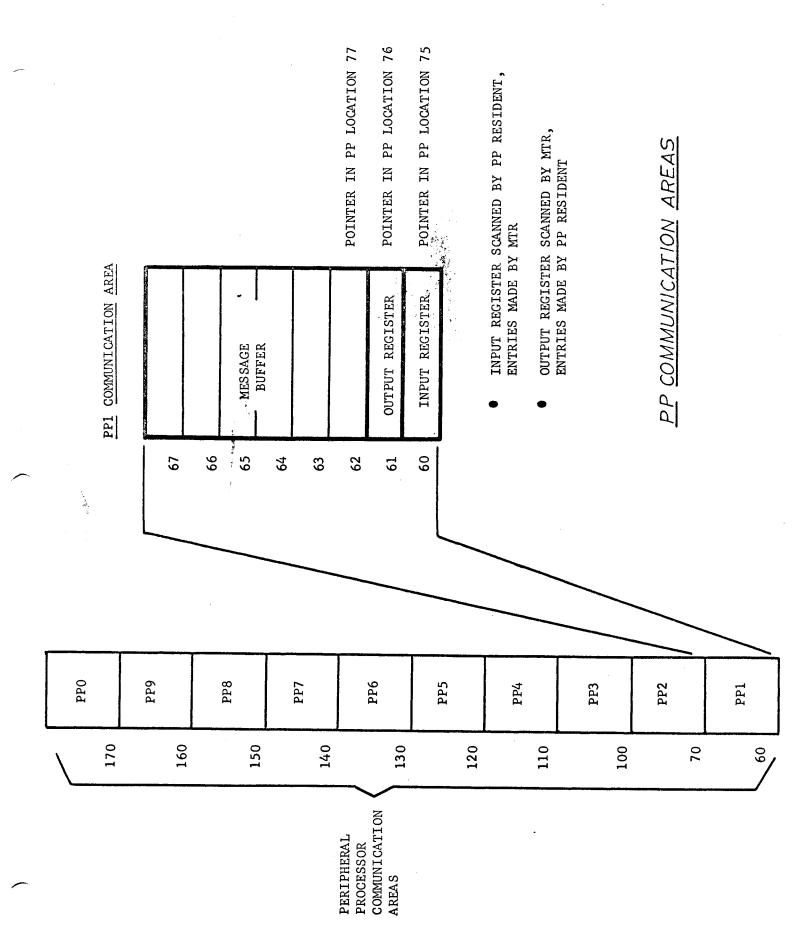

Communication between MTR and the resident programs is carried out through the use of ten communication areas in central memory, one for each processor.

(Note: MTR on occasion communicates with itself by this means.) Each communication area consists of a one-word Input Register, a one-word Output Register, and a six-word Message Buffer. Pool processors address these areas by means of pointers in locations 75 - 77.

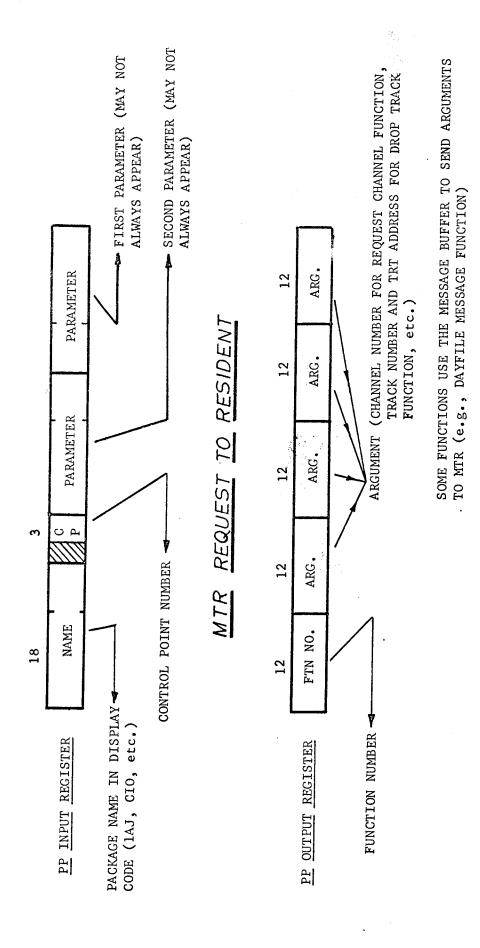

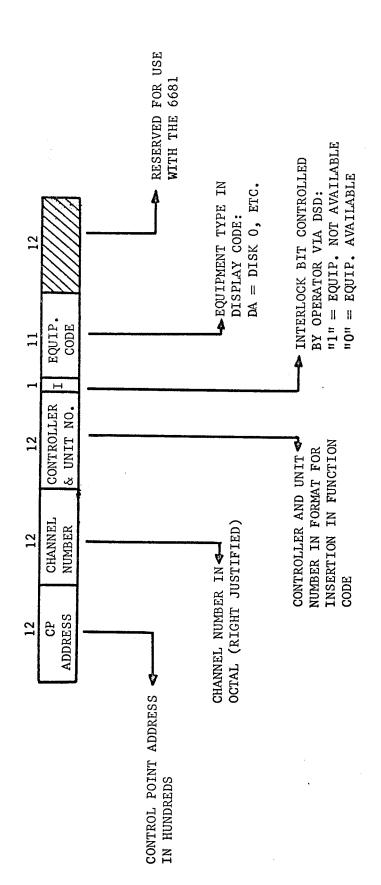

MTR assigns a task to a pool processor by placing the request in the processor's Input Register. The format of the request is shown in figure 2. The name of

the program package which is to be loaded and executed appears in the high-order

18 bits of the Input Register. This name consists of three display code characters, such as IAJ, CIO, etc. The number of the control point to which this package

is assigned appears in the low-order three bits of byte 2 of the Input Register.

Package parameters, such as the address of arguments required by the package,

appear in the low-order 36 bits of the Input Register. The request remains in the

Input Register until the task is completed. On completion of a task, the transient

program requests MTR to release the processor: MTR then clears the processor's

RESIDENT REQUEST TO MTR

Input Register. The Input Register of a pool processor is thus clear only when the processor is idle. When MTR needs a pool processor to assign to a task, it searches the communication areas for a cleared Input Register: when one is found, the corresponding processor is assigned to the task.

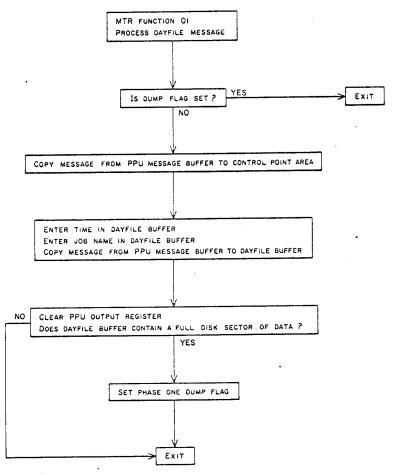

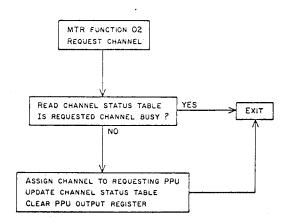

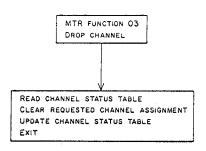

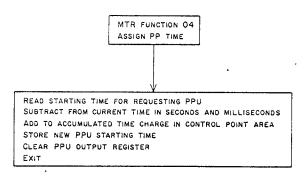

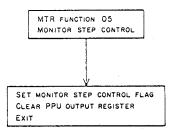

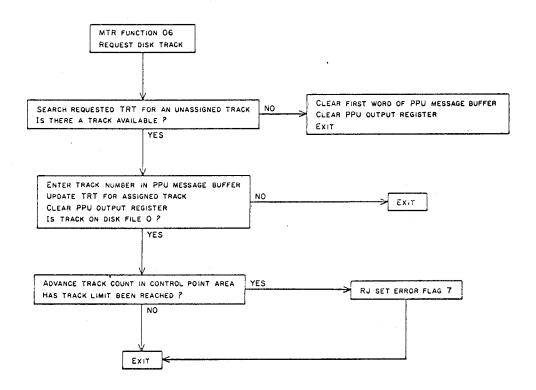

All communication between the Monitor and the transient and overlay programs is handled by the resident program. MTR performs a variety of functions, each of which is identified by a function code of one or two octal digits.

Some of these functions are listed below:

| Code | Function                |

|------|-------------------------|

| 1    | Process Dayfile Message |

| 2    | Request Channel         |

| 7    | Drop Track              |

| 12   | Release PP              |

| 33   | Assign Equipment        |

To transmit a request to MTR, the resident places the request in its Output Register. The format of this request is illustrated in figure 2. Byte 1 of the Output Register contains the function code in the low-order bit positions. Bytes 2 - 5 are used for arguments: the number of argument bytes depends on the particular function. Thus, for a Request Channel function (function number 2), the channel number is placed in byte 2. For a Drop Track function, byte 2 contains the address of the Track Reservation Table and byte 3 contains the half track number. For some functions, the function arguments are placed in the Message Buffer and only the function code appears in the Output Register.

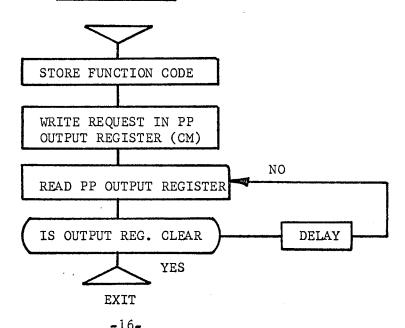

MTR regularly scans the Output Register of each processor to determine if a request is present. When the request has been detected, analyzed, and processed, MTR clears the Output Register. The resident, after placing the request in the Output Register, waits for the Output Register to be cleared before proceeding.

Some functions require that information be returned by MTR to the requesting program: for example, the Request Track function (function number 6) returns

a half track number to the requestor. MTR places any information to be sent to

the requestor in the Message Buffer. The resident returns control to the requesting transient or overlay program when it detects that the Output Register has

been cleared by MTR: the requesting program then reads the Message Buffer to

obtain the required information.

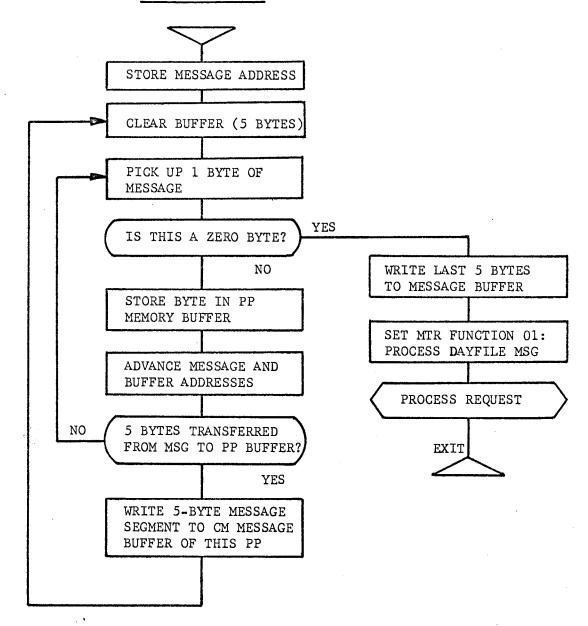

The resident contains a routine called Process Request which handles the transmission of function requests to MTR. The Process Request routine uses locations 10 - 14 in peripheral processor memory as temporary storage for the request to be written in the Output Register. A peripheral processor program may utilize this routine by placing the arguments for the function in bytes 11 and 12, setting the A register with the function number, and executing a return jump to the Process Request routine at location 761. The Process Request routine will enter the function number in location 10 and write the contents of locations 10 - 14 in the Output Register. Control will be returned to the requesting program upon MTR's clearing the Output Register.

# THE RESIDENT PROGRAM

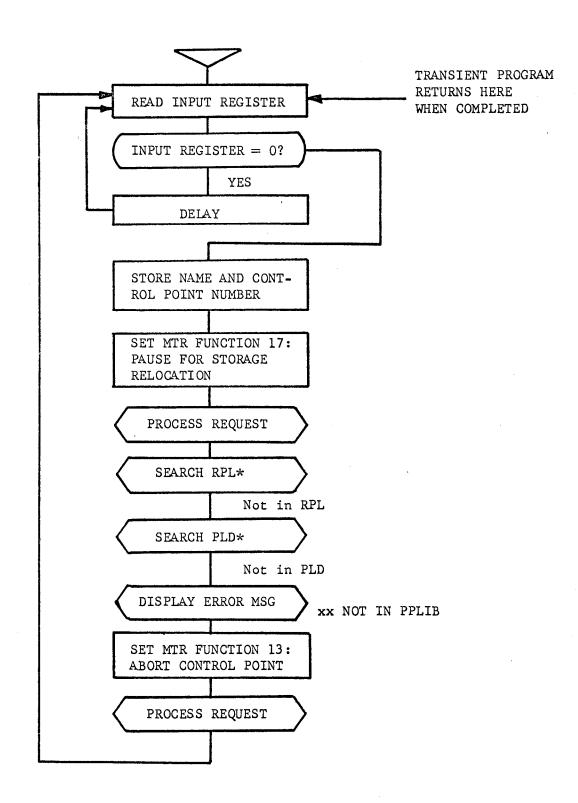

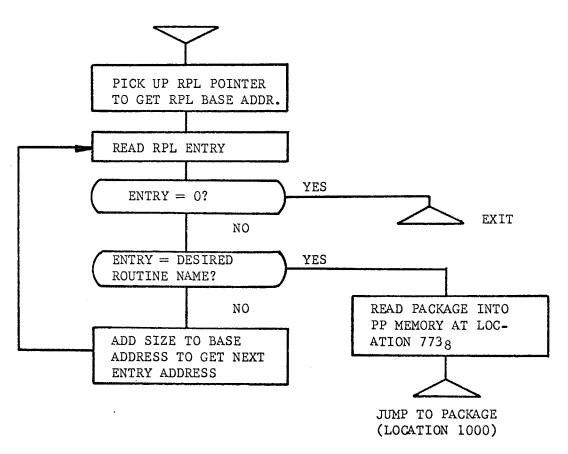

When a pool processor program completes execution, it exits to location 100, which is the address of the resident idle loop. In this idle loop, the processor's Input Register is scanned at intervals of slightly greater than 125 microseconds until a request is found in the Input Register. The delay between successive scans avoids unnecessary memory and read pyramid conflicts. When a request is detected, the resident stores the routine name and the control point number. It then sends function code 17, Pause for Storage Relocation, to MTR and waits for MTR to clear the Output Register before continuing. Should MTR be in the process of relocating the storage assigned to this control point, the Output Register clear will be delayed until relocation is

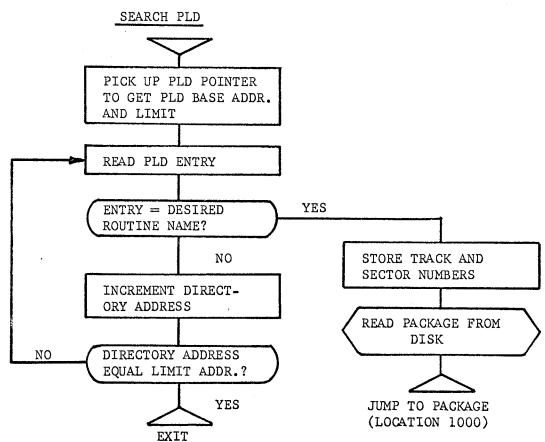

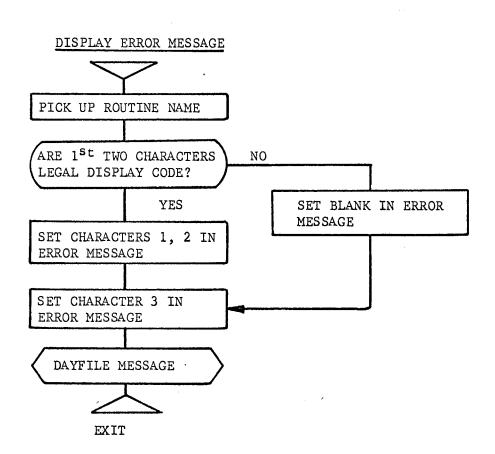

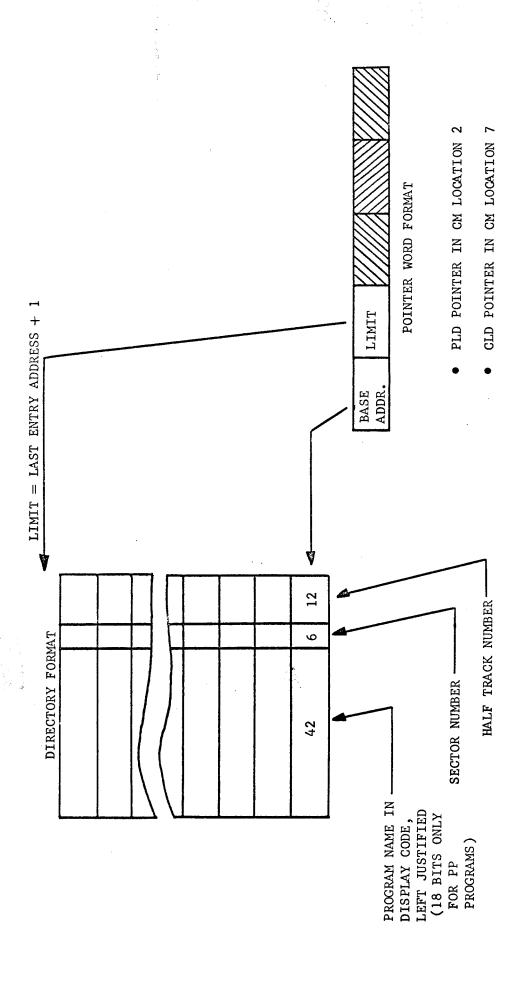

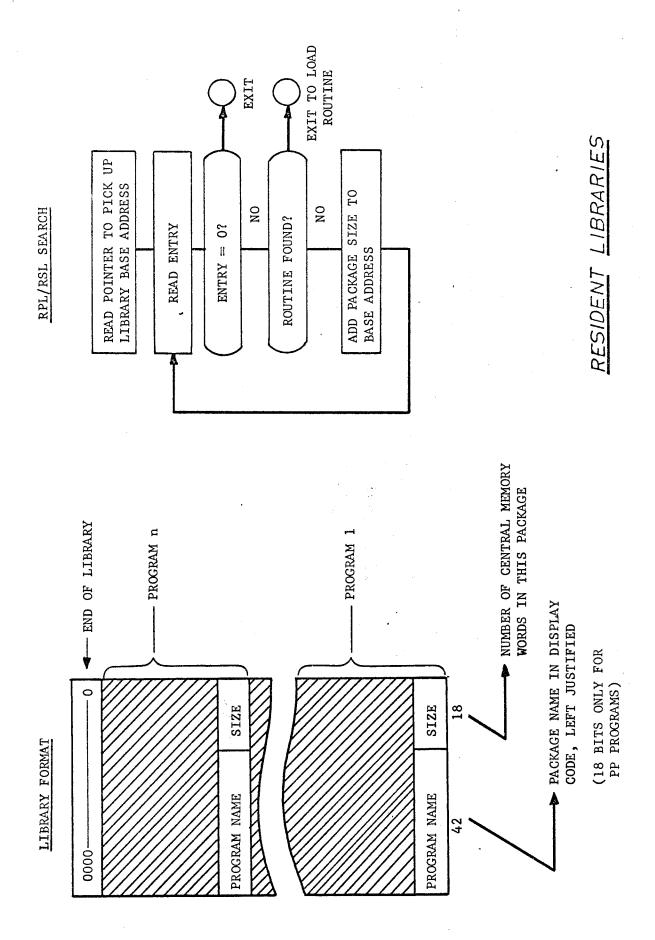

complete. The resident then searches the RPL for the requested routine: if found, the package is read from the resident library into the processor's memory beginning at location 773, and resident turns control over to this routine by jumping to location 1000. If the routine name was not found in the RPL, resident then initiates a search of the PLD. If the routine is in the disk library, the resident loads it from the disk into its memory at location 773, and jumps to it to begin execution. If the routine is not found in the PLD, the resident enters the message "XXX NOT IN PPLIB" in the dayfile, and requests MTR to abort the job which called the routine. The resident then returns to its idle loop.

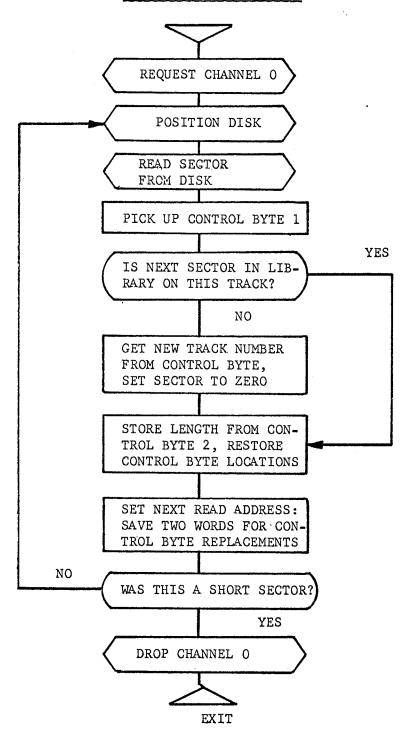

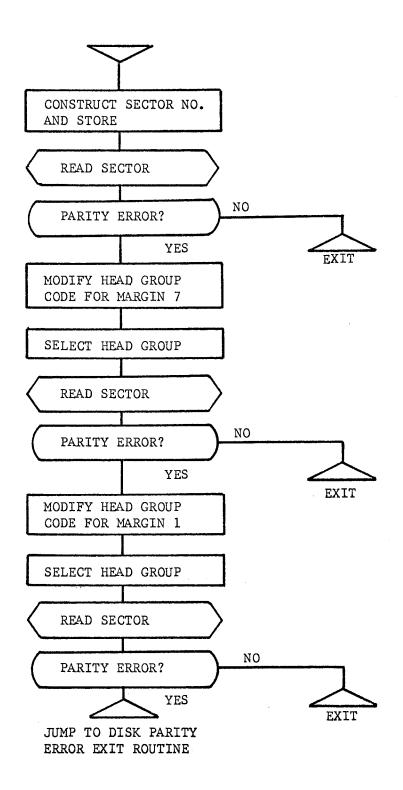

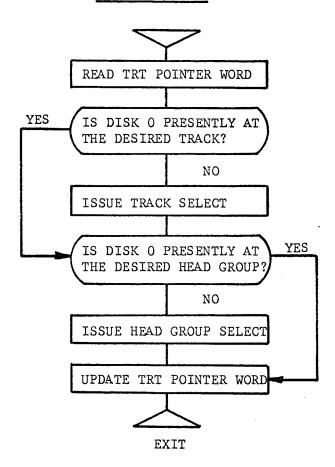

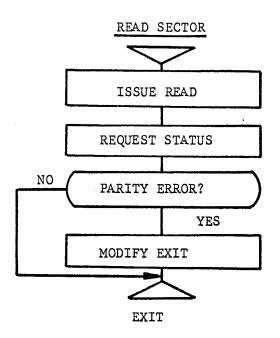

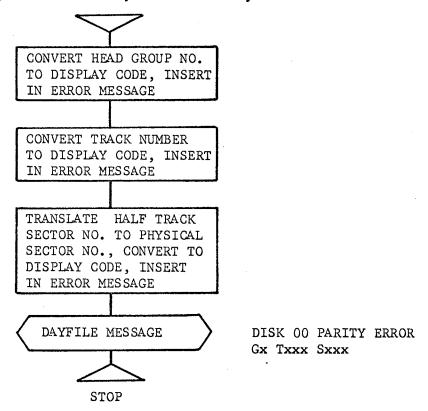

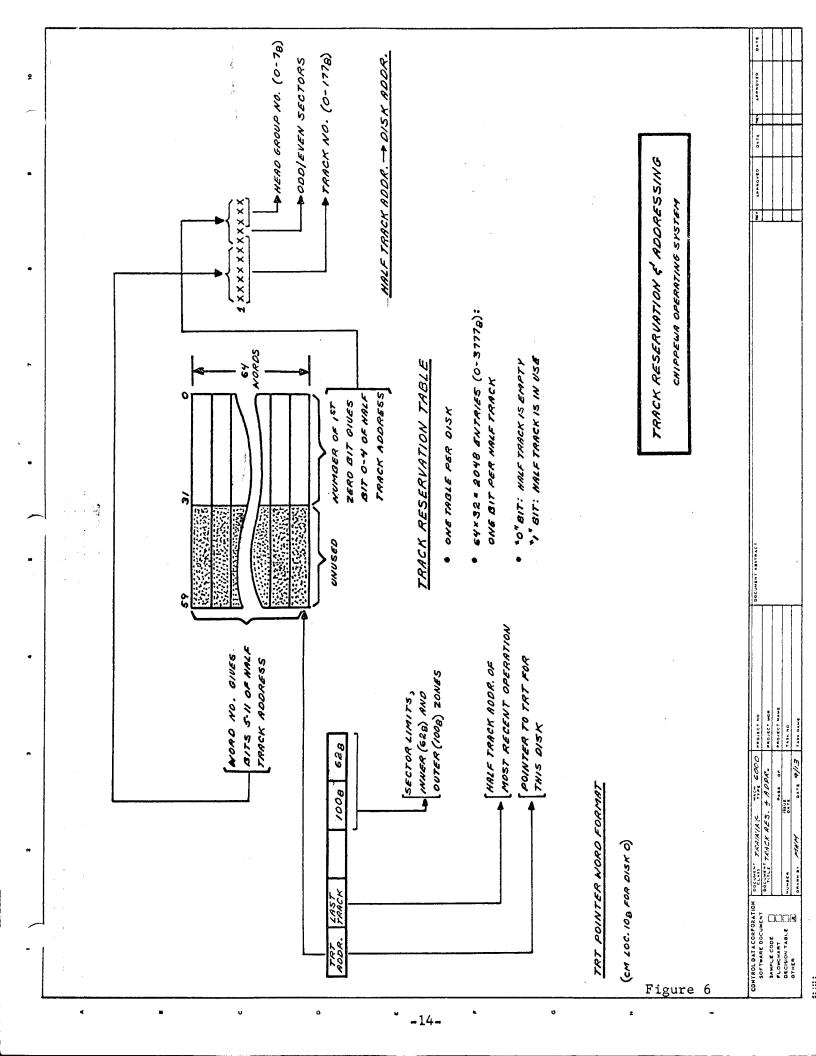

In loading a program from the disk, resident begins by reserving channel 0 via the appropriate MTR function request. Next, resident compares the track number of the requested routine with the current position of the disk as contained in the TRT pointer word for disk 0. Repositioning and/or head group switching is done only if necessary. Once the disk has been properly positioned, the sectors composing the desired routine are read into peripheral processor memory. The end of the routine is indicated when a short record (less than 100g central memory words) is read. If a parity error is detected, the sector in which the error occurred is reread twice, each time at a different clipping level. Should these reads also fail, the resident enters the message "DISK 0 PARITY ERROR Gx Txxx Sxxx" in the dayfile and then stops (via a UJN 0 instruction). A dead start load is necessary to renew systems operation.

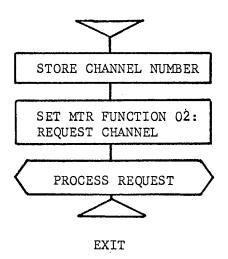

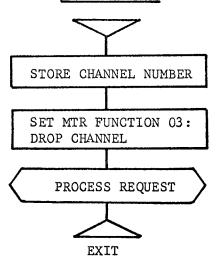

Several resident routines are used by transient and overlay programs.

These routines are described below.

| Address | Routine         | Entry Conditions              | Description                                                                                                                                 |

|---------|-----------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 761     | Process Request | Function number in A register | Enters function number in location 10, and writes locations 10 - 14 to the Output Register. Exits when the Output Register has been cleared |

| Address | Routine                     | Entry Conditions                                                                         | Description                                                                                                                                             |

|---------|-----------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 741     | Request Channel             | Channel number in<br>A register                                                          | Stores channel number in location 11, sets function code 2 in A register, and jumps to Process Request                                                  |

| 751     | Drop Channel                | Channel number in<br>A register                                                          | Stores channel number in location 11, sets function code 3 in A register, and jumps to Process Request                                                  |

| 531     | Dayfile Message             | Message address<br>in A register                                                         | Write message (less than 6 CM words, terminated by a zero byte) in Message Buffer, sets function code 1 in the A register, and jumps to Process Request |

| 701     | Position Disk*              | Half track num-<br>ber in A register                                                     | Repositions heads and/or switches head groups as necessary (for disk 0 only)                                                                            |

| 200     | Disk Parity Error Exit*     | Half track num-<br>ber in location<br>6, sector number<br>in location 7                  | Enters error message in the dayfile and halts                                                                                                           |

| 401     | Read Sector from Disk<br>0* | Read address in A register, half track number in location 6, sector number in location 7 | Reads one sector from disk 0 into memory at the designated address. Jumps to Disk Parity Error Exit if an error occurs.                                 |

\* Not a MTR function

All of the foregoing routines are entered via a return jump instruction to the specified address except the Disk Parity Error Exit, which is entered via a long jump instruction.

\* IF FOUND, LOAD PROGRAM AND JUMP TO IT

# SEARCH RPL

# READ PACKAGE FROM DISK

# POSITION DISK

# DISK PARITY ERROR EXIT Used by transient programs and overlays as well as by PP Resident

# DAYFILE MESSAGE

## REQUEST CHANNEL

## DROP CHANNEL

## PROCESS REQUEST

## CONTROL DATA CORPORATION

Development Division - Applications

THE SYSTEM MONITOR, MTR

Chippewa Operating System

# THE SYSTEM MONITOR, MTR

## CONTENTS

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| INTRODUCTION                                                         | . 1  |

| THE CONTROL POINT CONCEPT                                            | . 1  |

| DEAD START HOUSEKEEPING, THE CP IDLE PROGRAM, AND CONTROL POINT ZERO | . 5  |

| USE OF LOW CORE LOCATIONS                                            | 6    |

| MASTER LOOP                                                          | 9    |

| JOB INITIATION                                                       | 17   |

| JOB STATUS AND THE CONTROL POINT STACK                               | 19   |

| EXCHANGE PACKAGE SWITCHING                                           | 25   |

| PP RECALL PROCESSING                                                 | 29   |

| NORMAL AND ABNORMAL JOB TERMINATION                                  | 31   |

| STORAGE ALLOCATION AND RELOCATION                                    | 35   |

| TIME ACCOUNTING                                                      | 39   |

| DAYFILE                                                              | 44   |

| APPENDIX A: MTR FLOW CHARTS                                          |      |

| A PPENDIY R. STODACE MOVE DROCDAM                                    |      |

## THE SYSTEM MONITOR, MTR

### INTRODUCTION

The monitor, or executive, of the Chippewa Operating System is the MTR program, which permanently resides in peripheral processor 0. Among the functions performed by MTR is the allocation of the physical components of the system to various users. The components controlled by MTR include:

- pool processors

- peripheral equipment tapes, printers, card readers, etc.

- data channels

- disk tracks

- central memory

MTR directs the loading and initiates the execution of central processor programs, monitors central processor programs for I/O requests and assigns these requests to available peripheral processors, and monitors peripheral processor programs for function requests. MTR maintains the time accounting in the system and is responsible for the maintenance of the dayfile.

## THE CONTROL POINT CONCEPT

In a multiprogrammed multiprocessor such as the 6600 system, central memory is shared by a number of users. In addition to the active and inactive central processor programs residing in central memory, many peripheral processor programs require central memory buffers. The allocation of central storage to these various users is a function which the operating system can handle in one of two ways:

1. Storage can be allocated to a number of users limited only by

the amount of memory available. This assures the maximum utilization of central memory, but requires an elaborate bookkeeping system. In particular, the manipulation of the variable length tables required, and the relocation of storage to avoid arriving at a "patchquilt" of unallocated memory locations as jobs complete, present interesting design problems.

2. Storage can be allocated to a fixed number of users. If the limit is properly selected, losses in memory utilization efficiency will be minimal. In this method, control of storage allocation and relocation is greatly simplified.

For many job mixes, system throughput is not materially affected by the use of one or the other of the above methods.

The Chippewa Operating System uses the second method described. In the Chippewa Operating System, central memory may be simultaneously shared by up to seven users. For each of the seven users sharing central memory, there is an area in the central memory resident called the control point area. As each user is assigned storage, pertinent information about the user is entered in the control point area: as execution proceeds, entries are made in the control point area to reflect the current status of the user.

The seven control point areas are each 200<sub>8</sub> central memory locations in length, and occupy a portion of the central memory resident between locations 0200 and 1777. The control point areas are numbered one through seven in accordance with their relative (to one another) locations in central memory resident: control point 1 refers to the control point area in locations 0200 - 0377, control point 2 refers to the control point area in locations 0400 - 0577, and so forth. If the information about a user is contained in a given control point area, the user is said to be assigned to that control point.

The user assigned to a control point may be a peripheral processor program, a central processor program, or both: the last case occurs when a central processor program employs a peripheral processor program to perform an input-output operation. Control point assignments are required not only for external users (i.e., jobs) but for many of the operating system programs as well. Thus, the system program which transfers jobs from the card reader to the disk (1LJ) must be assigned to a control point, since a central memory buffer is required.

In many instances, the system packages READ and PRINT will each be assigned to a control point (usually to control points one and two). The READ package loads a job from the card reader and places it on the disk, and the PRINT package prints the output of a job. Each of these packages requires central memory space: the total space required by both packages is  $10,000_8$  locations. These two packages plus the central memory resident occupy  $24,000_8$  locations or about  $10,200_{10}$  locations. This leaves approximately  $120,000_{10}$  locations to be shared by users assigned to the remaining five control points, which should provide ample storage for a wide variety of jobs. If necessary, the READ and PRINT packages can be dropped to rpovide more capacity.

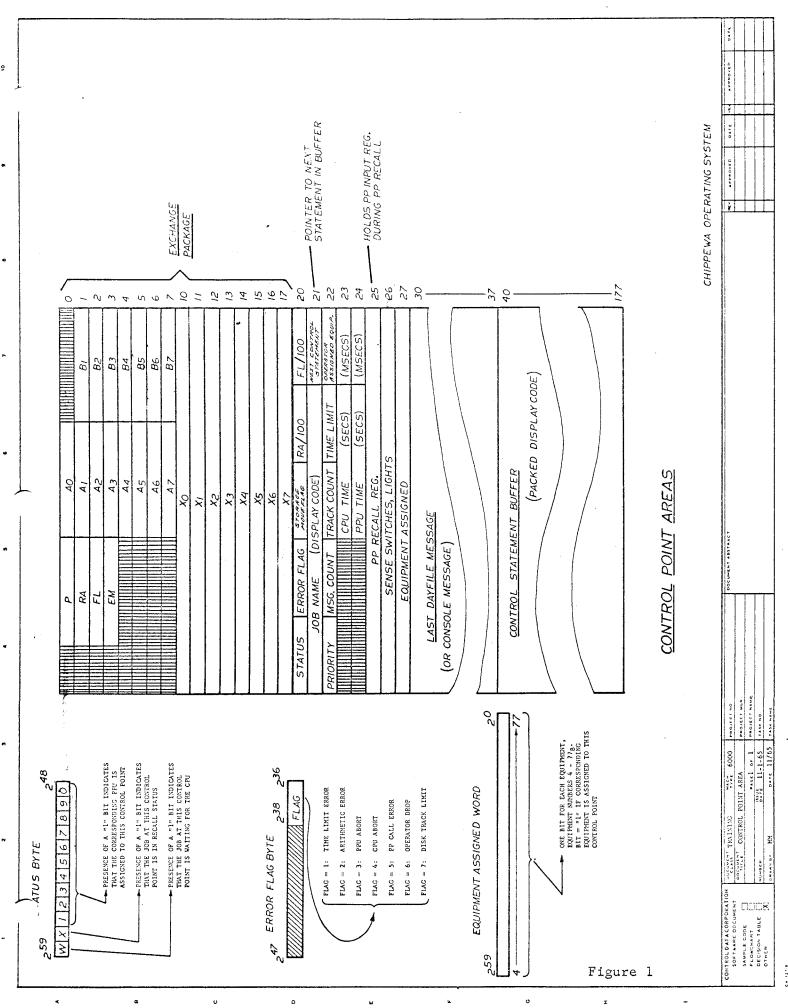

The control point area is illustrated in figure 1. The first sixteen words of the control point area contain the exchange jump package. If the user assigned to the control point is a peripheral processor program, no use is made of this exchange jump package insofar as this user is concerned. If the user assigned to this control point is a central processor program, this package is set with the appropriate values of P, RA, FL and EM when the program is initiated: as central processor programs are interrupted and restarted, the exchange jump packages for other central processor programs appear here.

Regardless of whether the user assigned to this control point is a central processor program or a peripheral processor program, the storage allocated

is always defined by the values of RA and FL in bytes 4 and 5, respectively, of location 20g within the control point area. Note that these values are in hundreds (upper 12 bits of an 18-bit address).

The control point number is often maintained in the low-order three bits of a byte. On many occasions, the system derives the control point area address by shifting the control point number left 7 places from its low-order bit positions. For example, a routine might pick up a byte containing the number of control point 2, which would appear as 0002: shifting this left 7 places, we obtain 0400, the beginning address of the control point 2 area.

# MTR: DEAD START HOUSEKEEPING, THE CP IDLE PROGRAM, AND CONTROL POINT O

During the loading of the system tape, the lower portion of the central memory resident is initialized by reading a series of records totalling 50008 CM words into central memory beginning at location 0. This initialization process sets the first entry in the FNT/FST with the file name DAYFILE and the file type COMMON.

When the loader releases peripheral processor zero to MTR, MTR obtains the next available track number from the Track Reservation Table for disk 0. This half track number is set in the Beginning Track (byte 2) and Current Track (byte 3) bytes of the FST entry for the dayfile. Byte 1, the Equipment Number, is set to zero as is byte 4, the Current Sector byte. The Buffer Status byte (byte 5) is set to 1, indicating that this file is not reserved.

Once the FNT/FST entry for the dayfile has been completed, MTR issues an exchange jump to the central processor idle program. This idle program executes a jump to relative location 2, which contains a stop instruction, and thus halts the central processor with  $P \neq 0$ . The function of the idle program is to keep  $P \neq 0$  in all cases except in the case of an error exit from a central processor program.

The idle program is a central processor program, and as such must be

assigned to a control point. A pseudo control point, called control point zero, is used for this purpose. Referring to the control point area illustration (figure 1), note that relative locations 218 and 208 contain, respectively, the job name and the job status. The control point area for control point zero is assumed to start at location 0 in central memory: central memory locations 218 and 208 (absolute) contain the job name and the job status for control point zero. These are the only locations in this portion of the resident which are actually a part of the control point zero area: the exchange jump package for the idle program begins at location 2040. Location 218 contains MONITOR as the job name. Byte 1 of location 208 contains the job status: the low order bits of this byte are used to indicate the assignment of peripheral processors to a control point. For control point zero, the status byte contains 0003, indicating that processor 0 (MTR) and processor 9 (DSD) are assigned to this control point.

The use of the pseudo control point zero is a mechanism simplifying the manner in which MTR controls the assignment of jobs to the central processor. The reason for using location 0 as the start of the control point area for control point zero is evident when we remember that the address of a control point may be obtained from its control point number by shifting the control point number left seven places.

After initiating the central processor idle program, MTR enters its master loop.

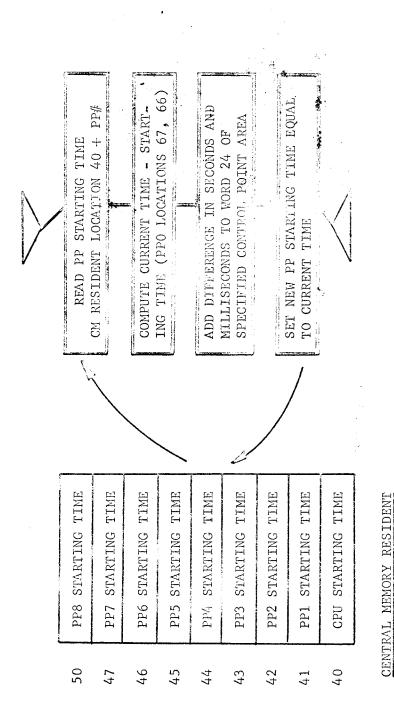

## MTR: USE OF LOW CORE LOCATIONS

MTR uses low core locations 26 - 77 to maintain various flags, pointers, and special-purpose buffers: these are illustrated in figure 2. Locations 75 - 77 contain the Input Register, Output Register, and Message Buffer pointers for the peripheral processor zero communication area. A five-byte area

| 76<br>77<br>77<br>77<br>60<br>60<br>60<br>61<br>61<br>61<br>63<br>64<br>64<br>64<br>64<br>64<br>64<br>65<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67<br>67 | MESSAGE BUFFER POINTER  INPUT REGISTER POINTER  BATE LINE BUFFER  CLOCK PHASE  DAYFILE DUMP FLAG  LAST SECOND COUNT  NEXT PP INPUT ADDRESS  COMPLETE DAYFILE FLAG  ACTIVE CONTROL POINT ADDR.  CONTROL POINT STACK  TEMPORARY  TEMPORARY  CHANNEL STATUS BUFFER | THE CENTRAL PROCESSOR AND THE SYSTEM TIME FROM CM LOCATION 30  PROCESSOR - ZERO IF NONE AVAILABLE  PROCESSOR - ZERO IF NONE AVAILABLE  PROCESSOR - ZERO IF NONE AVAILABLE  THE CENTRAL PROCESSOR IS ASSIGNED (FOP OF STACK)  THE CENTRAL PROCESSOR IS ASSIGNED (FOP OF STACK)  FOR THE CENTRAL PROCESSOR  ADDRESS BETWEEN MTR ROUTINES  ADDRESS BETWEEN MTR ROUTINES  ADDRESS BETWEEN MTR ROUTINES  ADDRESS BETWEEN MTR ROUTINES  STATUS TABLE  STATUS TABLE |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                      | CP ADVANCE COUNTER                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                      | ,                                                                                                                                                                                                                                                               | MACO WINTOU TOURING CINTERIAL INT AUGUS                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                      | NEXT CP NUMBER                                                                                                                                                                                                                                                  | USED IN ADVANCING CONTROL POINT SCAN                                                                                                                                                                                                                                                                                                                                                                                                                         |

Figure 2

consisting of locations 70 through 74 is used to buffer the time line from the time-date area in central memory locations 30 - 37. This central memory area contains the time and, optionally, the date: it is initialized via the DSD keyboard entry "TIME". The first word of this central resident area contains the time: this word is read into locations 70 - 74 whenever the time is to be advanced or entered in a dayfile message. Locations 63, 65, 66, and 67 contain counts used in advancing the clock and in computing time charges to a control point.

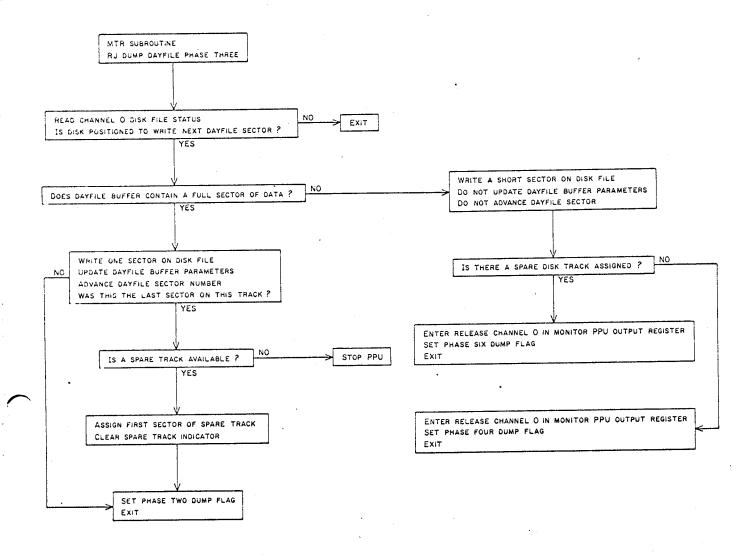

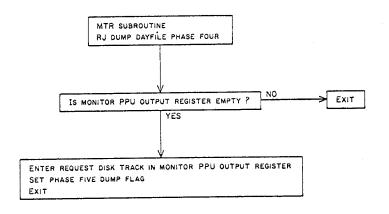

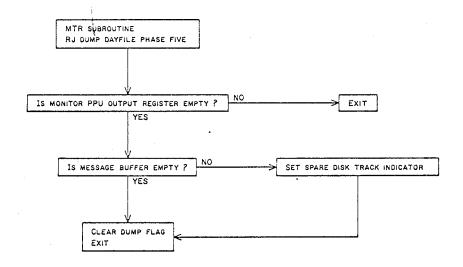

Location 64 contains the Dayfile Dump Flag, which, when set, indicates that the data in the dayfile buffer is being dumped to the disk, and also indicates which phase of the dumping process is to be executed next. Location 61 contains another dayfile related flag, the Complete Dayfile Flag, which is used in insuring that dayfile messages for a specific job are dumped to the disk at the end of a job.

Location 62 contains the address of the Input Register of a free pool processor: this processor will be assigned by MTR to the next peripheral processor task. If all pool processors are busy, this location contains zero.

Locations 60 and 52 - 57 hold the control point stack. Location 60 represents the top of the stack and contains the address of the control point area for the program currently being executed by the central processor: if this location contains zero, the central processor is unassigned (i.e., is assigned to pseudo control point zero, the control point for the idle program). Control points representing programs waiting for the central processor are stacked in locations 52 - 57.

Location 51 contains a Move Storage Flag, used when storage is being reallocated to control points. Location 50 is a temporary storage area: it is often used to transmit the Output Register address of a peripheral processor between MTR routines.

Locations 30 - 46 provide a buffer used by MTR in updating the Channel Status Table. Locations 26 and 27 are used by MTR in advancing the control point scan: location 27 contains a count used in determining the time interval between successive scans, and location 26 contains the number of the control point to be processed on the next scan.

The remaining low core locations, 01 - 25, are used for a variety of temporary storage needs. For example, locations 10 - 14 are used at various times to hold a peripheral processor's Output Register, the status word from a control point area, a TRT pointer, and a variety of other quantities.

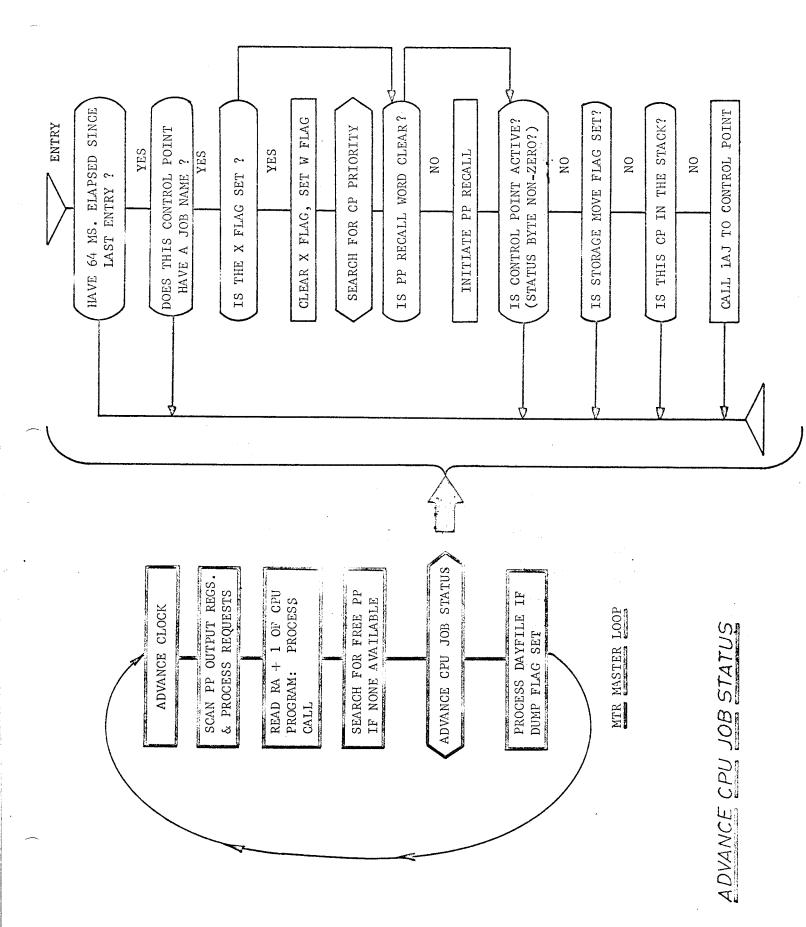

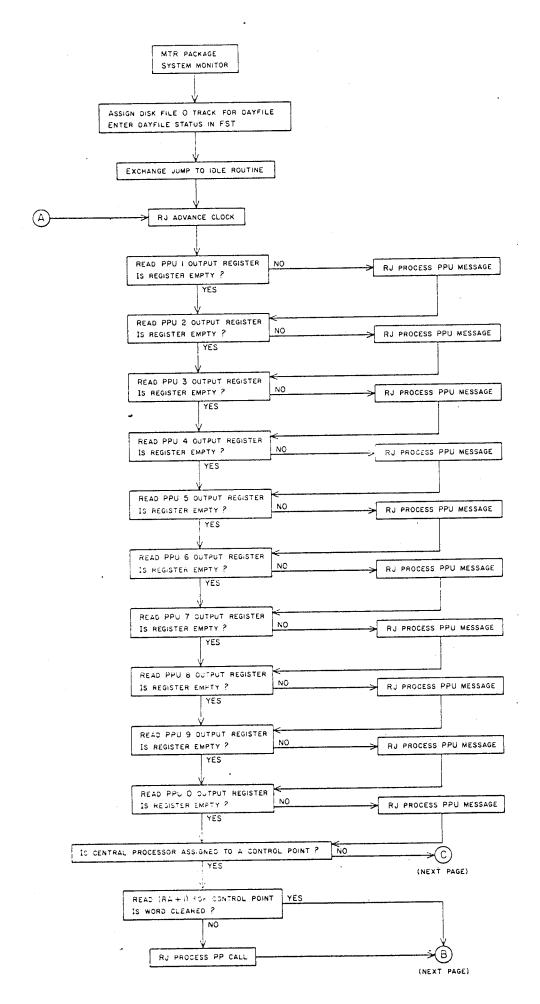

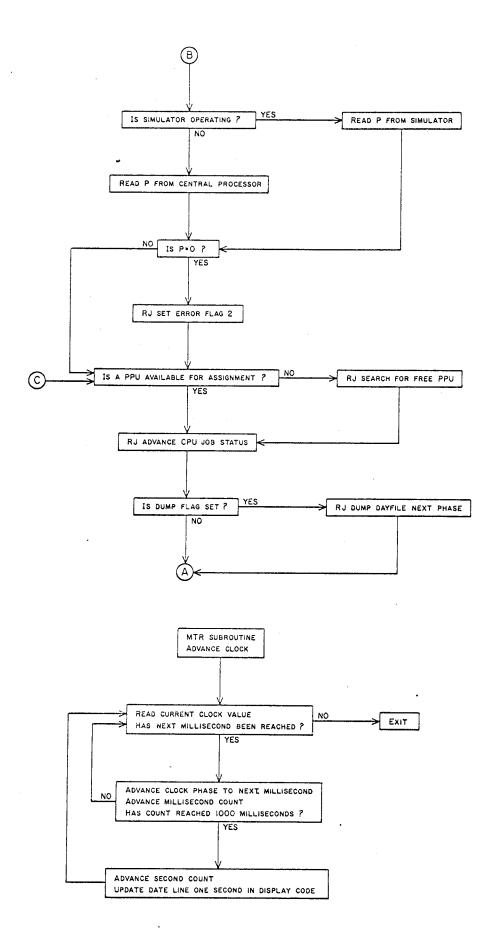

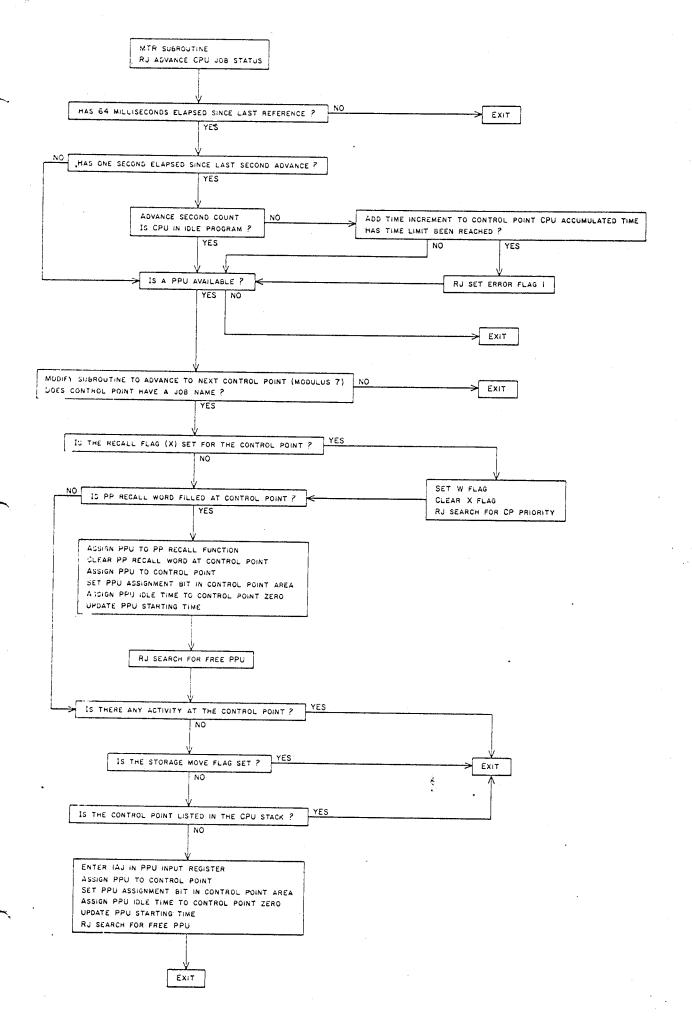

## MTR: MASTER LOOP

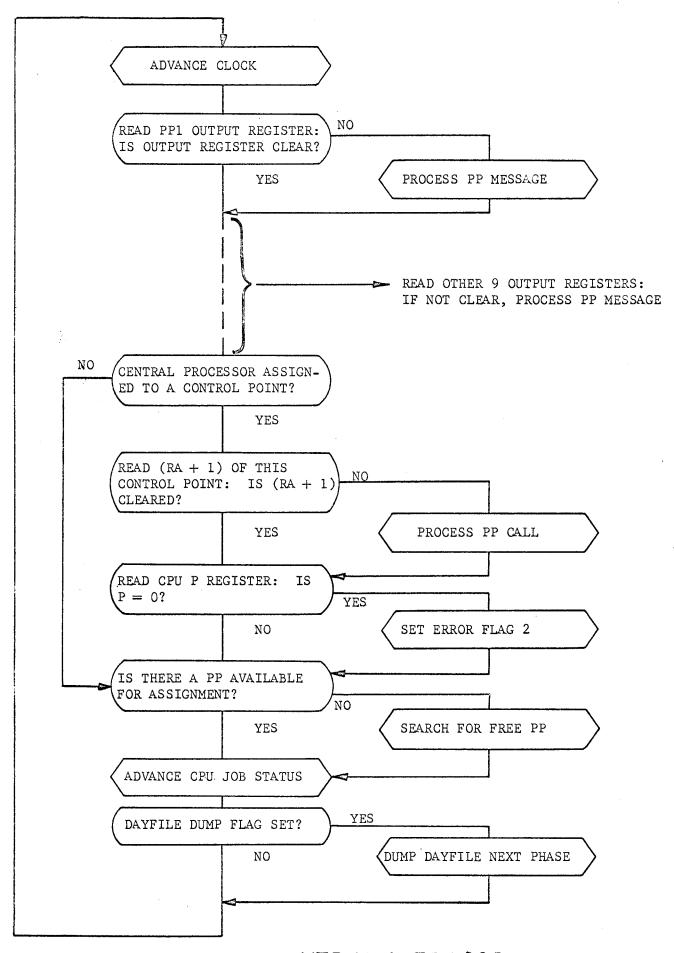

The MTR Master Loop is illustrated in figure 3. This loop, from which all MTR routines are entered (either directly or indirectly), performs the following four major functions:

- Advances the system clock

- Monitors peripheral processors for function requests

- Monitors the central processor program currently being executed for I/O requests and normal or abnormal exit conditions

- Examines one of the seven control points for PP or CP recall status and may initiate another central processor program: if the control point is inactive, the IAJ routine is called to bring a job from the disk to this control point.

The time between successive scans is primarily a function of the number and type of requests serviced during a scan. In any case, the fourth function mentioned above (Advance CPU Job Status) is performed at intervals of no less than 64 milliseconds.

The Advance Clock routine updates the system clock, which is stored in location 30 in central memory resident. This word generally has the format

MTR MASTER LOOP

"sp HR . MN . SC .", where HR, MN, and SC are each two display code digits representing, respectively, hours, minutes, and seconds.

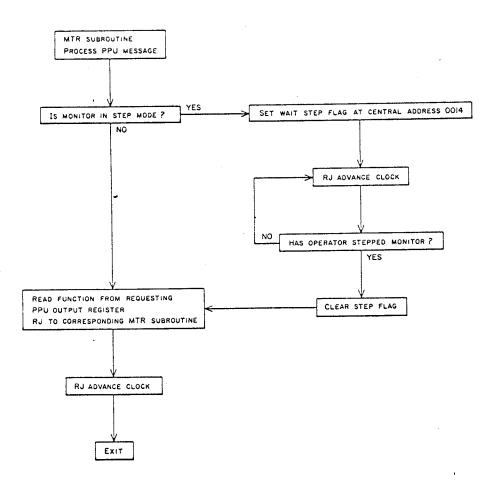

On each pass through the loop, MTR reads the Output Register of each peripheral processor, including its own. All requests to MTR from peripheral processor programs are transmitted in the form of function codes placed in the requesting processor's Output Register. When MTR finds a request in an Output Register (i.e., Output Register not cleared), it performs a table look-up for the routine corresponding to the function number, and jumps to that routine. If the request can be executed, the routine clears the Output Register before exiting back to the master loop: if the request cannot be executed, the routine exits to the master loop without clearing the Output Register. In the latter case, MTR will pick up the request again on its next trip through the master loop, and attempt to execute the request once again.

The functions performed by MTR for peripheral processor programs are listed below. The flow chart page numbers refer to the attached flow charts: memory addresses refer to the version of MTR dated 10/15/64.

| Function<br>Number | Starting<br>Address | Flow Chart<br>Page No. | Function                |  |

|--------------------|---------------------|------------------------|-------------------------|--|

| 1                  | 1500                | A-3                    | Process Dayfile Message |  |

| 2                  | 2000                | A-4                    | Request Channel         |  |

| 3                  | 2040                | A-4                    | Drop Channel            |  |

| 4                  | 2440                | A-4                    | Assign PP Time          |  |

| 5                  | 1560                | A-5                    | Monitor Step Control    |  |

| 6                  | 2200                | A-5                    | Request Disk Track      |  |

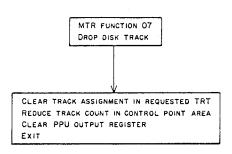

| 7                  | 2300                | A-5                    | Drop Disk Track         |  |

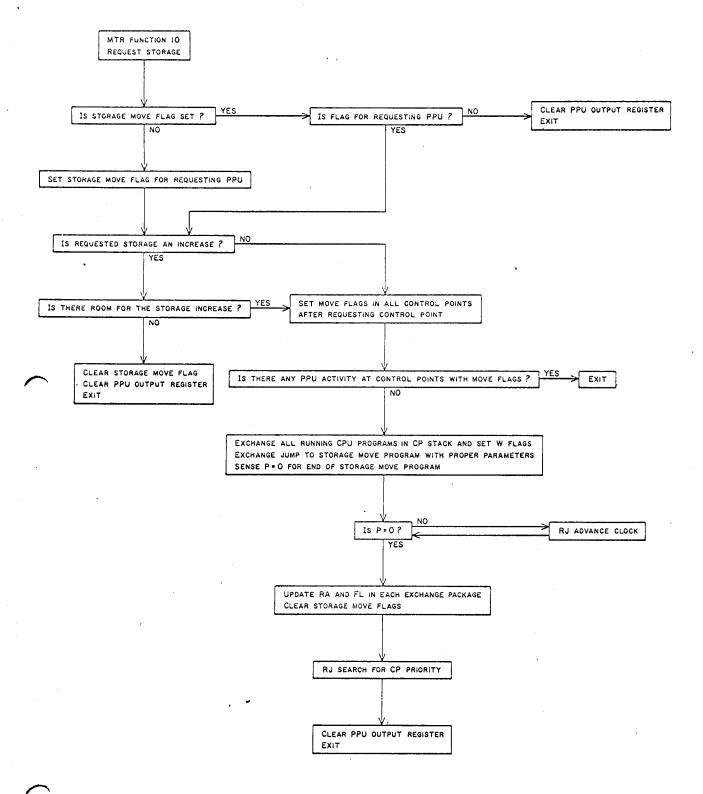

| 10                 | 4300                | A-6                    | Request Storage         |  |

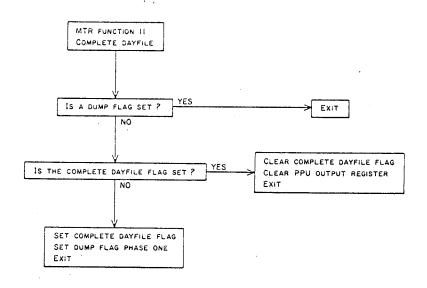

| 11                 | 1300                | A-7                    | Complete Dayfile        |  |

| Function<br>Number | Starting<br>Address | Flow Chart<br>Page No. | Function                     |  |

|--------------------|---------------------|------------------------|------------------------------|--|

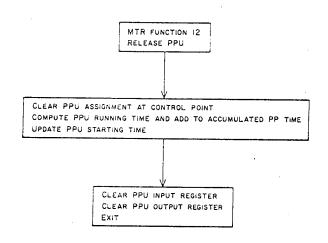

| 12                 | 3730                | A-7                    | Release PP                   |  |

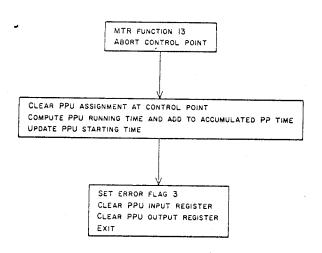

| 13                 | 4040                | A-7                    | Abort Control Point          |  |

| 14                 | 3600                | A-8                    | Enter New Time Limit         |  |

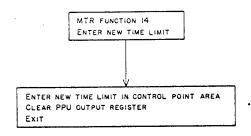

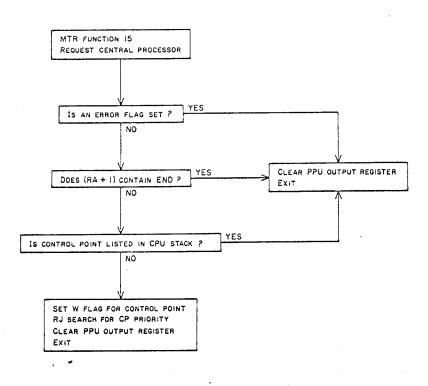

| 15                 | 2600                | A-8                    | Request Central Processor    |  |

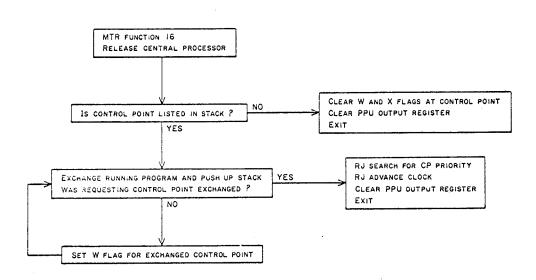

| 16                 | 3760                | A-8                    | Release Central Processor    |  |

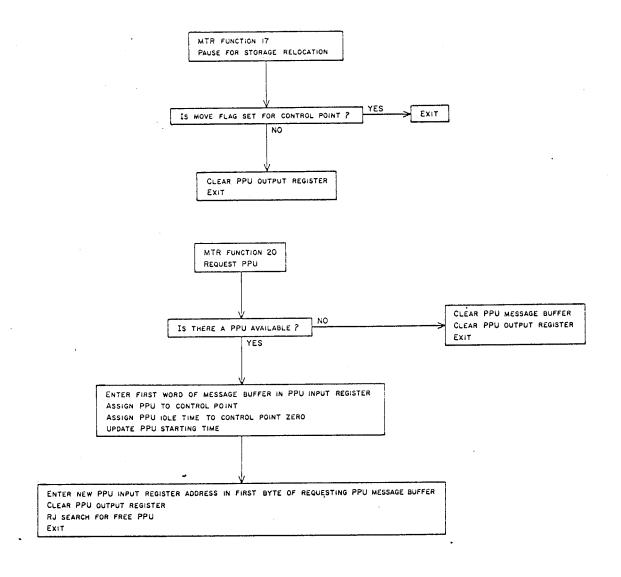

| 17                 | 5200                | A-9                    | Pause for Storage Relocation |  |

| 20                 | 4640                | A-9                    | Request Peripheral Processor |  |

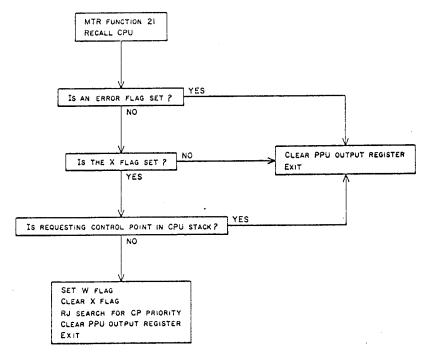

| 21                 | 2750                | A-9                    | Recall Central Processor     |  |

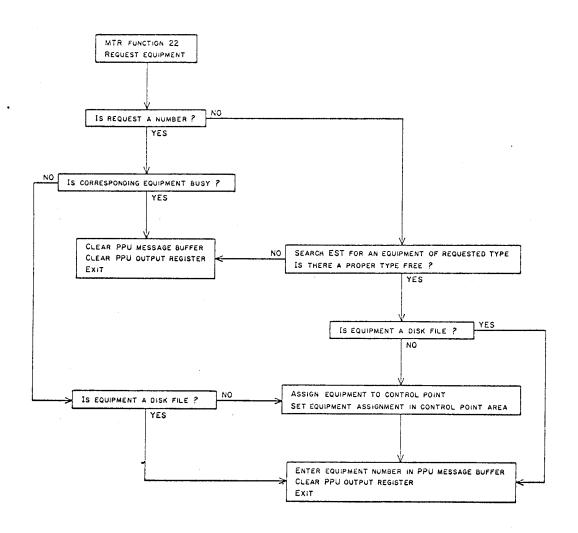

| 22                 | 5600                | A-10                   | Request Equipment            |  |

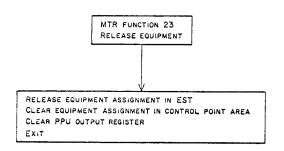

| 23                 | 5240                | A-10                   | Drop Equipment               |  |

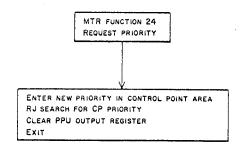

| .24                | 3240                | A-10                   | Request Priority             |  |

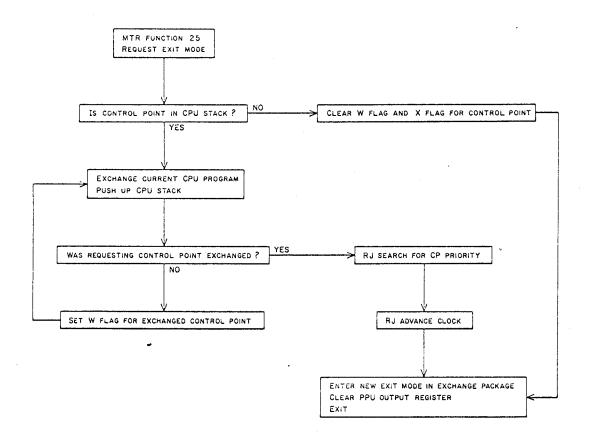

| 25                 | 3630                | A-11                   | Request Exit Mode            |  |

| 26                 | 3030                | -                      | Reserved for Future Use      |  |

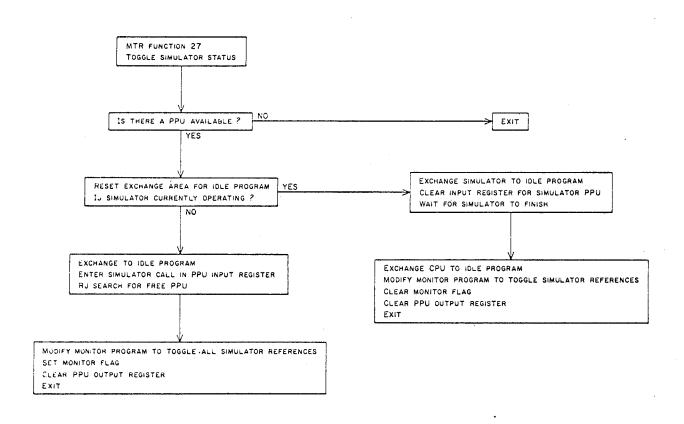

| 27                 | 3100                | A-11                   | Toggle Simulator             |  |

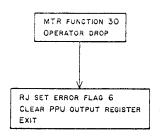

| 30                 | 2160                | A-12                   | Operator Drop                |  |

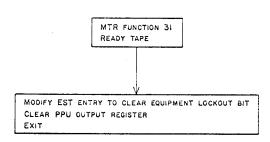

| 31                 | 4200                | A-12                   | Ready Tape                   |  |

| 32                 | 4240                | A-12                   | Drop Tape                    |  |

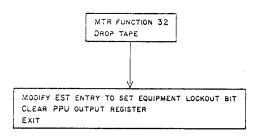

| 33                 | 6100                | A-12                   | Assign Equipment             |  |

| 34 - 37            | 3030                | -                      | Reserved for Future Use      |  |

After servicing any peripheral processor requests which may have been present, MTR proceeds to determine if any action is required by the central processor. To determine if the central processor is executing a program, MTR looks at the top of the control point stack (location 60 in processor 0's memory). If this location contains zero, the central processor is idle: if the contents of this location are non-zero, then the central processor is currently executing a program. The entries in the stack are control point

addresses: thus, location 60 contains the address of the control point area for the program currently being executed by the central processor. MTR adds 208 to this address to form the address of the Status word in the control point area (see figure 1), reads the Status word and extracts byte 4, which contains the reference address in hundreds. MTR then reads the contents of RA + 1 to determine if the central processor program has issued a request.

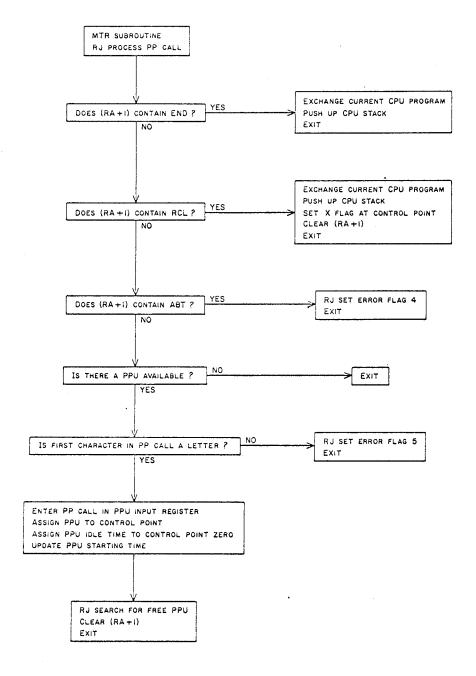

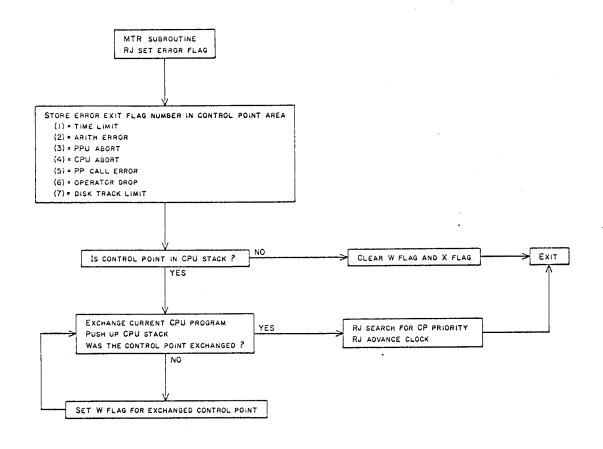

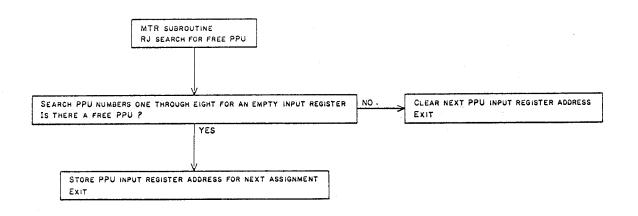

If the contents of RA + 1 are not zero, MTR jumps to a routine to process the request. If RA + 1 contains END or RCL, another central processor program is initiated in place of the current one: if RA + 1 contains ABT or if the request in RA + 1 does not begin with a letter, the appropriate error flag is set in byte 2, location  $20_8$ , of the control point area. If RA  $+\ l$ contains a legitimate PP call, MTR places the call and the control point number of the requestor in the Input Register of an available pool processor and assigns the processor to this control point by setting the appropriate bit in byte one of the Status word. After processing the call, (RA + 1) is cleared to inform the central processor that the request has been processed, and control is then returned to the master loop. If the call was END, ABT, or illegal, or if the request could not be processed at this time (no free pool processor), the routine exits to the master loop without clearing  $RA \, + \, 1$ . The subroutine which processes central processor requests for peripheral programs is entitled "Process PP Call". Its starting address is 2700, and it appears on page A-14 of the attached flow charts.

After processing the central processor program request, MTR reads the central processor P register. If P contains zero, it is assumed that an error exit has occurred, and MTR sets the appropriate error flag in byte 2 of the Status word in location 20g of the control point area.

MTR then looks at location 62 in its memory to see if it has a pool processor available for assignment. If this location contains zero (no

processor available), MTR scans the Input Registers of processors 1 - 8 and writes the address of the first cleared Input Register in location 62.

MTR next examines one of the seven control points and determines if the control point is in recall status. If it is, then this program may be reinitiated by MTR, depending upon its priority. If the control point is inactive, MTR directs the loading of another job at this control point. MTR scans only one control point on each pass through the master loop: the number of the control point most recently scanned is maintained in location 26 of MTR's memory. The MTR subroutine which performs this processing is entitled "Advance CPU Job Status" and is shown on page A-13 of the attached flow charts. This subroutine will be discussed at greater length during the description of the control point stack.

If dayfile dumping is not in process, MTR returns to the beginning of the loop and begins its scan once more.

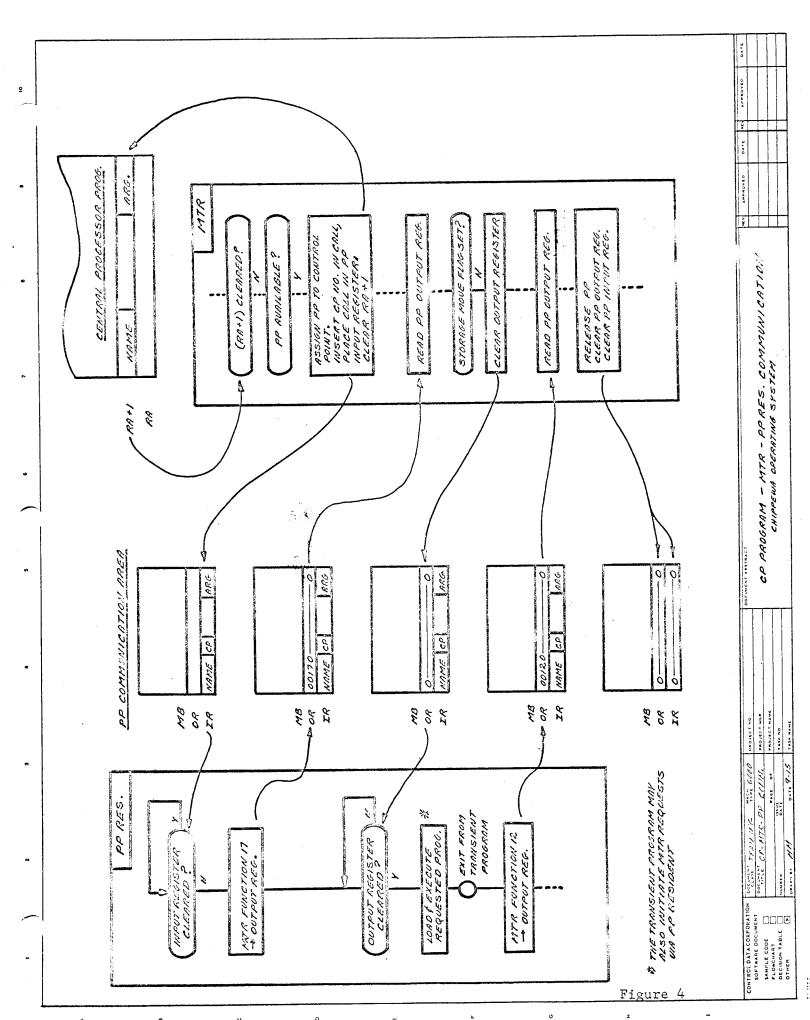

As a review of CPU - MTR - PP communication, the sequence which takes place when a central processor program requests that a task be performed by a peripheral processor program is described below. (Refer to figure 4.)

- 1. The central processor program requests a peripheral processor by writing the routine name (three display code characters), left-justified, in location 1 of its program. The address of any parameters required are written in the low-order bits of this location.

- 2. MTR examines the contents of RA + 1 during its master loop: if (RA + 1) is non-zero, MTR jumps to a subroutine to process the call. This subroutine inserts the control point number of the requesting job in the low-order three bits of byte 2 of the word read from RA + 1 and then writes this word in the Input Register of a free pool processor. The routine also sets the bit corresponding to the processor in byte 1 of word 208 in the control point area.

- 3. When the peripheral processor resident finds the routine name in its Input Register, it asks MTR if the storage assigned to this control point is to be relocated by issuing the appropriate function request (function code 17).

- 4. If the storage assigned to this control point is to be relocated, MTR will delay the execution of the requested transient program by not clearing the Output Register of the peripheral processor until relocation is completed. If no storage relocation is to be done, MTR clears the Output Register immediately upon recognizing the function request.

- 5. When the Output Register has been cleared by MTR, the resident proceeds to load the requested program either from the resident library or the disk library, and then transfers control to it.

- 6. The transient program and any overlays it may use may also communicate with MTR by using the resident subroutines to transmit function requests to MTR. These programs may also communicate directly with the central program by adding the parameter address (held in the Input Register) to the value of RA from the control point area in order to obtain the absolute address of information within the central processor program.

- 7. When the transient program completes execution, it sends (via peripheral resident) a Release PP function request (function code 12) to MTR. MTR clears the processor's Input Register and Output Register, and clears the bit in byte 1 of the Status word (control point area, location 20<sub>8</sub>) corresponding to this processor.

## MTR: JOB INITIATION

Once the system loader has released control of the peripheral processors to their respective programs, the pool processors begin spinning in their idle loops while MTR and DSD, after performing some initial housekeeping, enter their master loops. To initiate job loading and execution in the system, the operator may use the DSD keyboard entry "AUTO.". This assigns routines to control points as follows:

| Control Point |     | Routine |

|---------------|-----|---------|

| 1             | 1LJ | (READ)  |

| 2             | 1DJ | (PRINT) |

| 3             | 1BJ | (NEXT)  |

| 4             | 1BJ | (NEXT)  |

| 5             | 1BJ | (NEXT)  |

| 6             | 1BJ | (NEXT)  |

DSD accomplishes this assignment by placing the routine name and control point number in the first two bytes of its Message Buffer and (via peripheral resident) issuing a Request PP function (function code 20) to MTR. MTR assigns a processor to the control point by writing the routine name and control point number in the Input Register of a free pool processor, and then setting the appropriate bit in byte one of the control point area status word.

The READ package (1LJ and its overlays) brings jobs in from the card reader and places them on the disk. It enters the job name as the file name in the FNT/FST table, inserts the priority from the job card in the FNT entry, and sets the file type to INPUT.

The NEXT package (1BJ and its overlays) loads a job from the disk to the control point to which it (NEXT) is assigned. 1BJ searches the FNT for the highest priority unassigned file of type INPUT. The file name (job name from the job card) is entered as the job name in the control point area. The file name is changed to INPUT, the file type changed to LOCAL, and the file assigned to this control point. The priority is placed in the control point area by

1BJ via an MTR function request (function code 24). 1BJ then calls overlays to read the first record from the file into the control statement buffer in the control point area. This record, which may be up to 95 words in length, contains the control cards for this job. The Next Control Statement pointer in the control point area is then initialized.

An overlay is called to complete job card translation. The time and the field length from the job card are inserted in the control point area by 1BJ via MTR function requests 10 and 14, respectively. (When 1BJ was initiated, it requested storage from MTR, who set the values of RA and FL in the control point area. Central storage is used by 1BJ for a buffer area: when the job is brought from the disk to the control point, the storage required by the job is requested by 1BJ. This storage is considered by MTR to be a replacement for, and not an addition to, the storage originally assigned to the control point.) In processing the storage request, MTR may have to relocate storage assigned to other (higher) control points. After this relocation is performed, MTR sets the value of FL in the control point area, both in byte 4 of location 20 and in the exchange jump package.

When IBJ has completed its function, it requests MTR to release the peripheral processor. MTR then clears the processor's Input and Output Registers, and clears the appropriate bit in byte 1 of the status word in the control point area. This byte then contains zero. The processing performed by IBJ has resulted in the control point area being set as follows:

- the job name, time limit, priority, and field length have been set.

- the pointer to the next control statement has been set to address whatever control card followed the job card.

- byte 1 of the Status word (location 20<sub>8</sub> of the control point area is zero.

(Note; the control point areas are cleared during loading of the system and are also cleared each time a job is dropped from a control point.)

Once 1BJ has brought a job to a control point, further action concerning that job is initiated by MTR. This action will be described shortly: first we shall discuss the status of a job relative to the central processor.

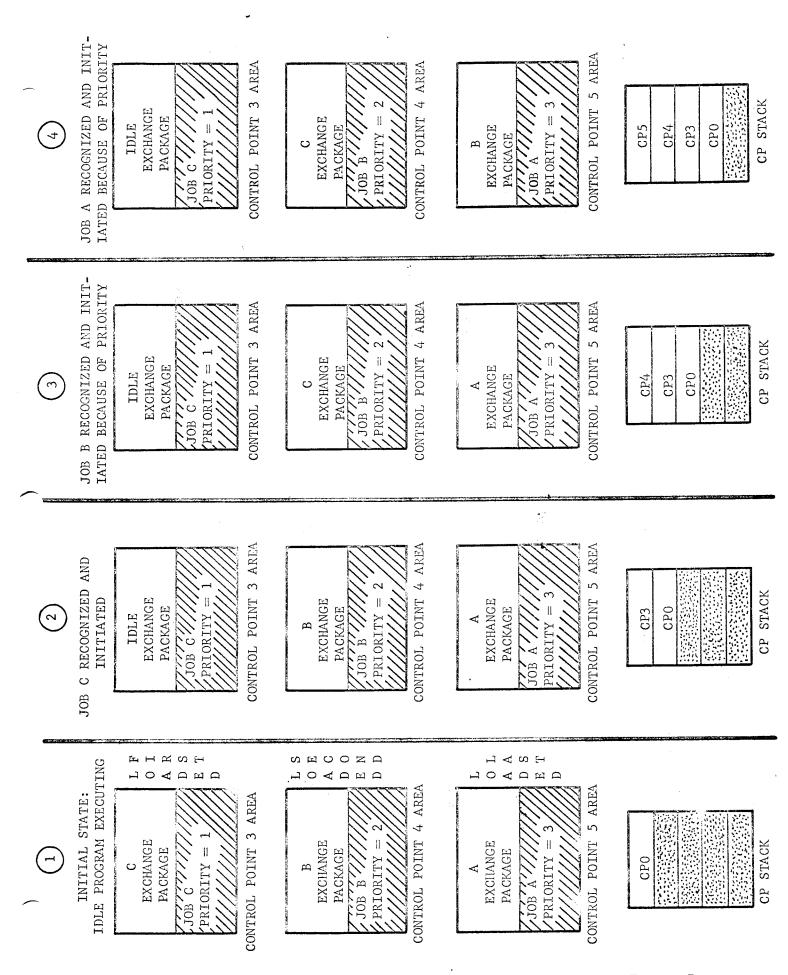

## MTR: JOB STATUS AND THE CONTROL POINT STACK

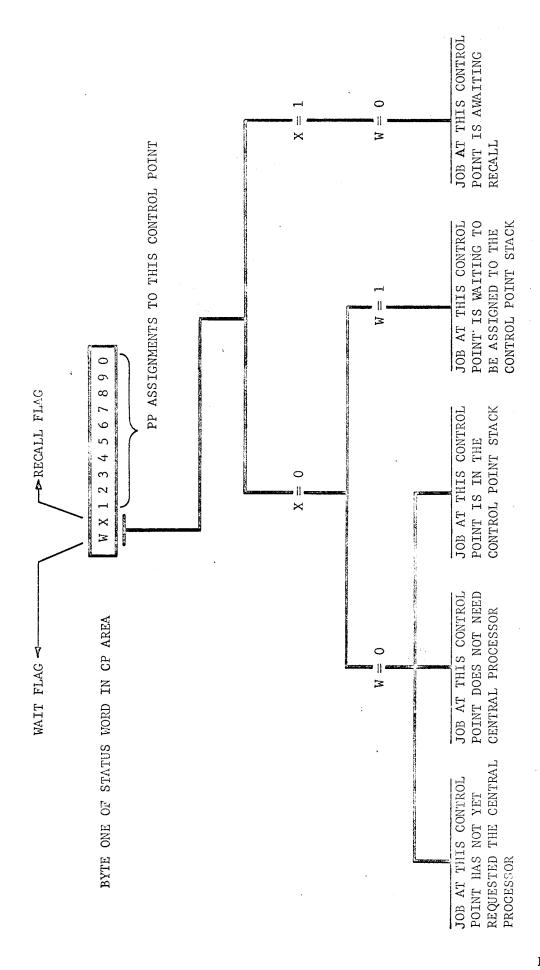

The status of a job is defined by the setting of bits 2<sup>11</sup> and 2<sup>10</sup> in byte one of the control point status word, and by the presence or absence in the control point stack of the control point address for the job. The 2<sup>10</sup> bit is the X, or recall, flag. This flag is set when MTR detects RCL in RA + 1 of the program being executed by the central processor. The 2<sup>11</sup> bit is the W, or wait, flag. This flag is set by various MTR routines to indicate that the job at the associated control point is waiting for the central processor. We may have two queues of jobs waiting for the central processor: one queue consists of jobs in the control point stack, and the other consists of jobs in W status. The top of the control point stack (location 60 in PPO memory) represents the job currently being executed by the central processor. The remaining entries in the stack represent jobs interrupted because of the entry of a higher priority job into the system.

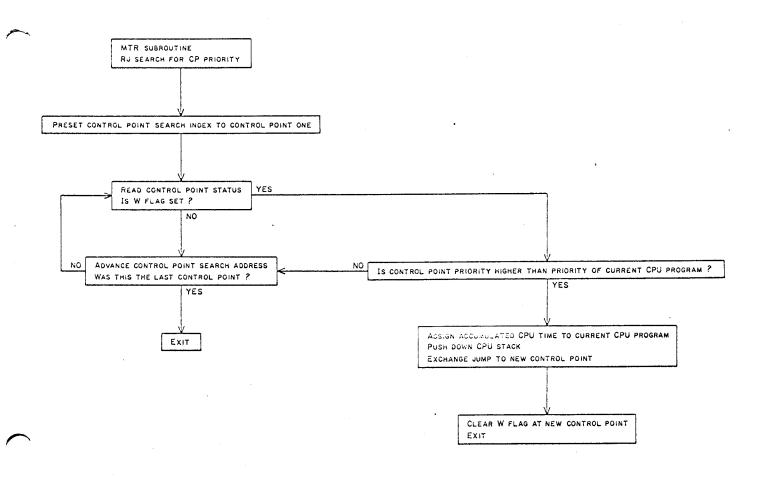

Whenever MTR sets the W flag for a job at a control point, a subroutine called Search for CP Priority is called. The flow chart for this subroutine appears on page A-16 of the attached flow charts. This subroutine checks the status of control points beginning with control point one. If the W flag at a control point is set, MTR compares the priority of this job with the priority of the job currently being executed by the central processor. If the job at the control point with the W flag set (i.e., the first control point found in wait status) has a higher priority than the job currently being executed, the routine pushes down the stack and inserts the control point address of the new job at the top of the stack, clears the W flag in the control point area, and

CP STATUS FLAGS

issues an exchange jump to interrupt the current program and initiate the new job. If the priority of the job currently being executed is higher than the priorities of any job which is in wait status (W flag set), then the routine leaves the flag set. This priority search is repeated on an aperiodic basis.

When a central processor program issues a recall request (by placing RCL in RA + 1), MTR processes this by interrupting this program and initiating the next program in the stack, and then setting the X flag in the control point area of the interrupted program. At an interval of time after the X flag is set, MTR will switch the control point from X status to W status and call the Search for CP Priority routine to re-initiate the job.

If the X flag is set, then, the job at the associated control point is awaiting recall. If the W flag is set, the job is waiting to enter the stack. The stack is always entered at the top: a job always enters the stack by taking control of the central processor. Note that the W flag and the X flag are never both set at the same time. If the W and X flags are both cleared, there are three possibilities:

- the job at the associated control point is in the stack

- the job at the associated control point does not require the central processor

- the job at the associated control point is inactive or has not yet requested the central processor

The interpretation of the X and W flag settings is charted in figure 5.

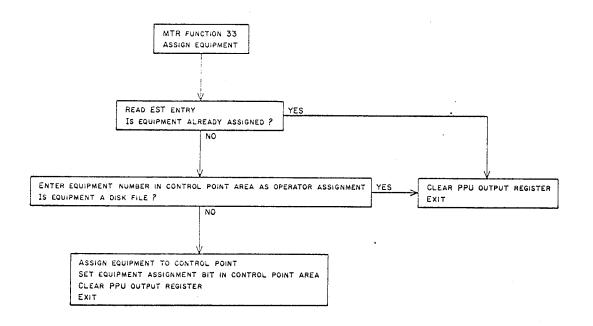

The status of each control point is examined by a MTR subroutine called Advance CPU Job Status. This routine is called each time MTR makes a pass through its master loop: however, unless 64 milliseconds or longer has passed since the routine was last entered, control is immediately returned to the master loop. This routine examines only one control point on each entry:

thus, a minimum interval of  $7 \times 64 = 448$  milliseconds elapses between successive scans of the same control point. The Advance CPU Job Status subroutine and its relationship to the MTR master loop are illustrated in figure 6. (See page A-13 of the attached flow charts for a more detailed flow chart of this routine.)

Upon entering the routine (if the 64 ms. interval has elapsed) the pointer for the control point to be scanned is advanced. This pointer is maintained in location 26 of peripheral processor zero's memory. The X flag for the control point is then examined: if this flag is set, the W flag is set and the X flag cleared. The subroutine Search for CP Priority is then called to re-initiate the program. If this program's priority is higher than the priority of the program currently being executed, the running program will be interrupted and its control point address pushed down in the stack: the higher priority program will be initiated, its control point address placed at the top of the stack, and its W flag cleared.

After processing the central processor recall flag, the Advance CPU Job Status routine examines the PP recall word in location 25<sub>8</sub> of the control point area. If this word is non-zero, a peripheral processor is assigned to complete execution of the recalled task.

The routine next examines byte one of location 20<sub>8</sub> in the control point area: if this byte is non-zero, then the W flag or the X flag at this control point is set, and/or a peripheral processor is performing a task for the job at this control point. If this byte is non-zero, then, the job at this control point is active (although perhaps not in execution at the moment): the routine therefore exits back to the master loop.

If the storage move flag in byte three of location  $20_8$  in the control point area is set, the storage assigned to this control point is to be or is being relocated. The routine exits back to the master loop, thus delaying further action until this relocation is completed.

Figure 6

It is possible for byte one of the status word (control point area, location 20<sub>8</sub>) to be zero and for the program at that control point nevertheless to be active. For example, the non-executing programs in the stack will have zero status (i.e., byte one of the status word = 0), and the running program will also have zero status if it is not using a peripheral processor. Therefore, in addition to determining that the program has zero status, the routine must also determine if the job is in the control point stack before it can be ascertained that all activity associated with the control point has stopped. If it is found that this is the case, the routine assigns a peripheral processor to the control point and calls the lAJ routine to that processor. The lAJ routine promptly calls the statement translator, 2TS, to interpret the next control statement. (Note: although not shown in the simplified flow chart of figure 6, the Advance CPU Job Status routine also checks to see if the running program has exceeded its time limit; if so, the appropriate error flag is set.)

Now let us return for a moment to an earlier point in our discussion. After 1BJ has brought a job to its control point, the job name, time limit, priority, and field length have been set in the control point area. Also, byte one of the status word is zero. Further action involving the control point is initiated by the MTR subroutine Advance CPU Job Status. When this routine scans the control point to which the job was brought by 1BJ, it finds that the job has zero status (byte one of location 20<sub>8</sub> = 0) and that the job's control point address is not listed in the stack. Thus, there is no activity at this control point. The Advance CPU Job Status routine therefore assigns a pool processor to this control point and calls 1AJ to that processor (by setting the name in the processor's Input Register). 1AJ in turn calls an overlay, 2TS, to process the next control statement from the control statement buffer. If this is a statement such as ASSIGN, RELEASE, COMMON, etc., the statement translator, 2TS, processes the control statement, moves the next control statement pointer (byte 5 of location 21<sub>8</sub> in the control point area) to point

to the next control statement in the buffer, and releases the processor. This ends the activity at the control point temporarily: the Advance CPU Job Status routine will recognize this inactivity, and call IAJ to advance the job at this control point again. This process repeats until a statement not recognized as a control point statement - a program card - is processed by 2TS. When 2TS processes a program card, it searches the FNT, the CLD, and the PLD, in that order, for the program. If the program is found in the FNT, 2TS proceeds to read the program from disk 0 into central memory beginning at location RA. Upon reaching the end of record (or upon detecting the end of the storage assigned to the job), 2TS sets the proper value of P in the exchange area, sets the field length in AO, transfers the arguments from the program card to the program area beginning at RA + 2, and clears RA and RA + 1. The value of P is obtained by adding 3 to the number of arguments: the latter quantity is supplied by the low-order six bits of the second word in the program record. The field length is set in  $A_0$  so that the program can determine the upper limit of its memory area. The remainder of the exchange area is cleared.

When 2TS has completed setting up the control point area and the program area, it requests the central processor for the job by sending function code 15 (Request Central Processor) to MTR. MTR sets the W flag in the control point area, and calls the Search for CP Priority subroutine to initiate the job. This subroutine will compare the priority of the new job with the priority of the running job, initiating the execution of the new job if it is higher in priority.

#### MTR: EXCHANGE PACKAGE SWITCHING .

As jobs are brought into the system or are recalled from X status, the running program may be interrupted to permit a higher priority program to take the central processor: when this occurs, an exchange jump is issued which results in the exchange package of the interrupted job being stored in

the control point area of the newly initiated job. Also, the stack is pushed down and the control point address of the newly initiated job is placed at the top of the stack. Each control point in the stack contains the exchange package for the control point immediately below it in the stack. An example will help to illustrate how this comes about. Assume that IBJ routines at control points 3, 4, and 5 bring jobs C, B, and A, respectively, to their control points. Job C has a priority of 1, job B has a priority of 2, and job A has a priority of 3. At the time the jobs are loaded, the central processor is executing the idle program. Figure 7 illustrates a possible sequence of events involving these jobs:

- 1 lBJ has brought jobs C, B, and A to control points 3, 4, and 5. The central processor is executing the idle program and thus the top of the stack contains zero the address of the control point area for pseudo control point zero.

- The Advance CPU Job Status routine has recognized the presence of the job at control point 3 and called lAJ to advance the job. lAJ's overlay, 2TS, has loaded the program into memory and, via a MTR request, requested that the job be executed. The MTR subroutine which processed this request called the Search for CP Priority routine. Since job C has a higher priority than the running program, the latter routine issued an exchange jump to job C which resulted in the idle program's exchange package being stored in control point three's exchange area, and then, after pushing down the stack, placed the address of control point three at the top of the stack.