CONTROL DATA®

CYBER 70

MODELS 71, 72, 73, 74

COMPUTER SYSTEMS

Volume 2 of 3

INSTRUCTION DESCRIPTIONS

HARDWARE REFERENCE MANUAL

## INSTRUCTION INDEX

## INSTRUCTION INDEX

#### CENTRAL PROCESSOR

| CENTRA         | AL PROCESSOR                                                                     |              |              |                                                               |                                             |

|----------------|----------------------------------------------------------------------------------|--------------|--------------|---------------------------------------------------------------|---------------------------------------------|

| 00XXX          | Error exit to MA or Program Stop                                                 | 3-3          | 72ijK        | Set Xi to (Xj) + K                                            | 2 9.0                                       |

|                | J t                                                                              |              | 73 i jk      | Set Xi to $(X_j) + (B_k)$                                     | 3-26<br>3-26                                |

| 0100K          | Return jump to K                                                                 | 3-3          | 74ijk        | Set Xi to (Aj) + (Bk)                                         | 3-26                                        |

| 011jK          | Read extended core storage                                                       | 3-6          | 75ijk        | Set Xi to (Aj) - (Bk)                                         | 3-26                                        |

| 012jK          | Write extended core storage                                                      | 3-6          | 76ijk        | Set Xi to (Bj) + (Bk)                                         | 3-26                                        |

| 013jK          | Central exchange jump                                                            | 3-6          | 77ijk        | Set Xi to (Bj) - (Bk)                                         | 3-26                                        |

| 02iXk          | Jump to (Bi) + K                                                                 | 3-4          | PERIPH       | IERAL PROCESSORS                                              |                                             |

| 030jK          | Jump to K if $(Xj) = 0$                                                          | 3-4          | 0000         | Pass                                                          | 4-4                                         |

| 031jK          | Jump to K if $(Xj) \neq 0$                                                       | 3-4          | 01dm         | Long jump to m + (d)                                          | 4-5                                         |

| 032jK          | Jump to K if (Xj) positive                                                       | 3-4          | 02dm         | Return jump to m + (d)                                        | 4-5                                         |

| 033jK<br>034jK | Jump to K if (Xj) negative                                                       | 3-4          | 03d<br>04d   | Unconditional jump d                                          | 4-5                                         |

| 034jK<br>035jK | Jump to K if (Xj) in range Jump to K if (Xj) out of range                        | 3-4<br>3-4   | 05d          | Zero jump d<br>Nonzero jump d                                 | 4-6                                         |

| 036jK          | Jump to K if (Xj) definite                                                       | 3-4          | 06d          | Plus jump d                                                   | 4-6                                         |

| 037jK          | Jump to K if (Xj) indefinite                                                     | 3-4          | 07d          | Minus jump d                                                  | 4-6<br>4-7                                  |

| 04ijK          | Jump to K if (Bi) = (Bj)                                                         | 3-5          | 10d          | Shift d                                                       |                                             |

| 05ijK          | Jump to K if (Bi) $\neq$ (Bj)                                                    | 3-5          | 11 d         | Logical difference d                                          | 4-7<br>4-7                                  |

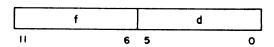

| 06ijK          | Jump to K if (Bi) > (Bj)                                                         | 3-5          | 12d          | Logical product d                                             | 4-7                                         |

| 07i K          | Jump to K if (Bi) $\leq$ (Bj)                                                    | 3-5          | 13d          | Selective clear d                                             | 4-8                                         |

|                | •                                                                                |              | 14d          | Load d                                                        | 4-9                                         |

| 10i            | Transmit (Xj) to Xi                                                              | 3-7          | 15d          | Load complement d                                             | 4 - 10                                      |

| 11i,k          | Logical product of (Xj) and (Xk) to Xi                                           | 3-7          | 16d          | Add d                                                         | 4 - 12                                      |

| 12i k          | Logical sum of (Xj) and Xk) to Xi                                                | 3-7          | 17d          | Subtract d                                                    | 4-12                                        |

| 13ijk<br>14i0k | Logical difference of (Xj) and (Xk) to Xi                                        | 3-8          | 20dm         | I and due                                                     |                                             |

| 15ijk          | Transmit complement of (Xk) to Xi                                                | 3-8<br>3-8   | 21dm         | Load dm<br>Add dm                                             | 4-10                                        |

| 16ijk          | Logical product of (Xj) and comp (Xk) to Xi Logical sum (Xj) and comp (Xk) to Xi | 3-9          | 22dm         | Logical product dm                                            | 4-12                                        |

| 17ijk          | Logical difference of (Xj) and comp (Xk) to Xi                                   | 3-9          | 23dm         | Logical difference dm                                         | 4-8<br>4-8                                  |

| 3              |                                                                                  |              | 2400         | Pass                                                          | 4-4                                         |

| 20ijk          | Left shift (Xi) by jk                                                            | 3-9          | 2500         | Pass                                                          | 4-4                                         |

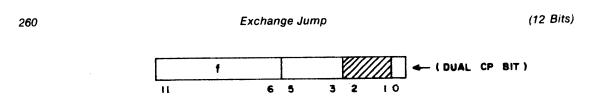

| 21ijk          | Right shift (Xj) by jk                                                           | 3-10         | 260X         | Exchange jump                                                 | 4-14                                        |

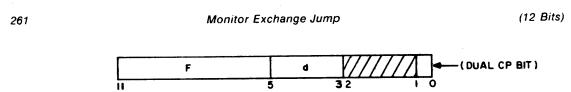

| 22ijk          | Left shift (Xk) nominally (Bj) places to Xi                                      | 3-10         | $261 \times$ | Monitor exchange jump                                         | 4-14                                        |

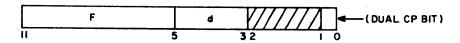

| 23ijk          | Right shift (Xk) nominally (Bj) places to Xi                                     | 3-10         | 262X         | Monitor exchange jump to MA                                   | 4-15                                        |

| 24ijk          | Normalize (Xk) to Xi and Bj                                                      | 3-11         | 27X          | Read program address                                          | 4-15                                        |

| 25ijk<br>26ijk | Round and normalize (Xk) to Xi and Bj                                            | 3-11         | 30d          | Load (d)                                                      |                                             |

| 27ijk          | Unpack (Xk) to Xi and Bj Pack Xi from (Xk) and Bj)                               | 3-12<br>3-12 | 31 d         | Load (d)<br>Add (d)                                           | 4-10                                        |

| J. 2,112       | ruck 21 from (22k) and DJ)                                                       | 3-12         | 32d          | Subtract (d)                                                  | 4-12                                        |

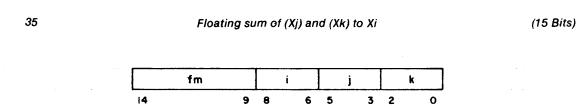

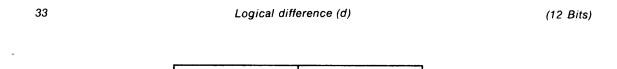

| 30ijk          | Floating sum of (Xj) and Xk) to Xi                                               | 3-13         | 33d          | Logical difference (d)                                        | 4-13<br>4-9                                 |

| 31ijk          | Floating difference of (Xj) and (Xk) to Xi                                       | 3-14         | 34d          | Store d                                                       | 4-10                                        |

| \$2ijk         | Floating DP sum of (Xj) and (Xk) to Xi                                           | 3-14         | 35d          | Replace add (d)                                               | 4-17                                        |

| 3ijk           | Floating DP difference of (Xj) and (Xk) to Xi                                    | 3-14         | 3 <b>6</b> d | Replace add one (d)                                           | 4-18                                        |

| 34ijk          | Round floating sum of (Xj) and (Xk) to Xi                                        | 3-15         | 37d          | Replace subtract one (d)                                      | 4-18                                        |

| 35ijk          | Round floating difference of (Xj) and (Xk) to Xi                                 | 3-15         | 40d          | T 4 ((4))                                                     |                                             |

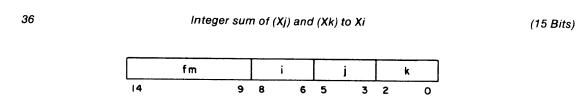

| 36ijk<br>37ijk | Integer sum of (Xj) and (Xk) to Xi                                               | 3-19         | 40d<br>41d   | Load ((d))<br>Add ((d))                                       | 4-11                                        |

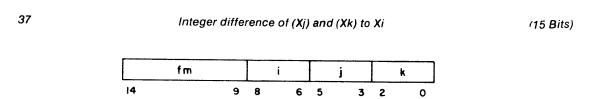

| orijk          | Integer difference of (Xj) and (Xk) to Xi                                        | 3-19         | 42d          | Subtract ((d))                                                | 4-13                                        |

| 40ijk          | Floating product of (Xj) and (Xk) to Xi                                          | 3-16         | 43d          | Logical difference ((d))                                      | 4 13<br>4-9                                 |

| 41ijk          | Round floating product of (Xj) and (Xk) to Xi                                    | 3-17         | 44d          | Store ((d))                                                   | 4-11                                        |

| 42ijk          | Floating DP product of (Xj) and (Xk) to Xi                                       | 3-17         | 45d          | Replace add ((d))                                             | 4-18                                        |

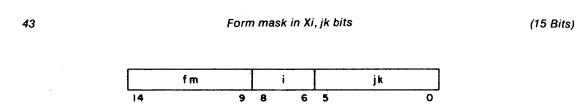

| 43ijk          | Form mask in Xi, jk bits                                                         | 3-13         | <b>46</b> d  | Replace add one ((d))                                         | 4-18                                        |

| 44ijk          | Floating divide (Xj) by (Xk) to Xi                                               | 3-18         | 47d          | Replace subtract one ((d))                                    | 4-i9                                        |

| 45ijk          | Round floating divide (Xj) by (Xk) to Xi                                         | 3-18         |              | ,                                                             |                                             |

| 46000          | No operation (pass)                                                              | 3-20         | 50dm         | Load $(m + (d))$                                              | 4-11                                        |

| 464jk          | Move indirect                                                                    | 3-21         | 51dm<br>52dm | Add (m + (d))                                                 | 4-13                                        |

| 465jk<br>466ik | Move direct                                                                      | 3-22         | 53dm         | Subtract (m + (d))                                            | 4-14                                        |

| 466jk<br>467jk | Compare collated Compare uncollated                                              | 3-22         | 54dm         | Logical difference (m + (d))<br>Store (m + (d))               | 4-9                                         |

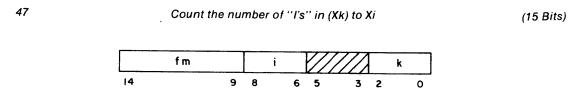

| 47iXk          | Count the numbers or "1's" in (Xk) to Xi                                         | 3-23<br>3-19 | 55dm         | Replace add (m + (d))                                         | 4-11<br>4-19                                |

| - 122311       | count the numbers of 15 in (22k) to 21                                           | 3-13         | 56dm         | Replace add one (m + (d))                                     | 4-19                                        |

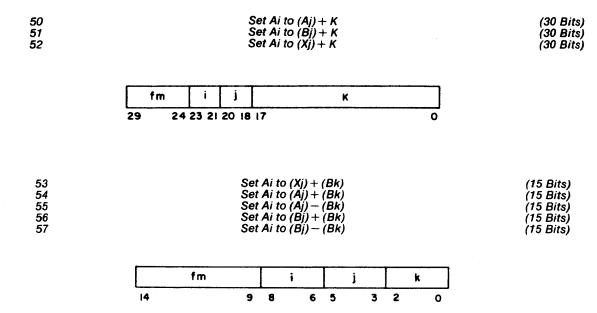

| 50ijK          | Set Ai to (Aj) + K                                                               | 3-24         | 57dm         | Replace subtract one (m + (d))                                | 4-20                                        |

| 51ijK          | Set Ai to (Bj) + K                                                               | 3-24         |              |                                                               |                                             |

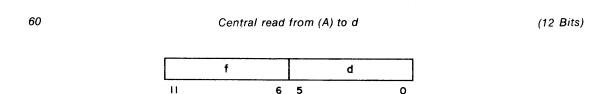

| 52ijK          | Set Ai to (Xj) + K                                                               | 3-24         | <b>60</b> d  | Central read from (A) to d                                    | 4-15                                        |

| 53ijk          | Set Ai to (Xj) + (Bk)                                                            | 3-24         | 61dm         | Central read (d) words to (A) from m                          | 4-16                                        |

| 54ijk          | Set Ai to (Aj) + (Bk)                                                            | 3-24         | 62d          | Central write to (A) from d                                   | 4-16                                        |

| 55ijk          | Set Ai to (Aj) - (Bk)                                                            | 3-24         | 63dm<br>64dm | Central write (d) words to (A) from m                         | 4-17                                        |

| 56ijk<br>57ijk | Set Ai to (Bj) + (Bk)                                                            | 3-24         | 65dm         | Jump to m if channel d active Jump to m if channel d inactive | 4-20                                        |

| 0.17           | Set Ai to (Bj) - (Bk)                                                            | 3-24         | 66dm         | Jump to m if channel d full                                   | $\begin{array}{c} 4-20 \\ 4-21 \end{array}$ |

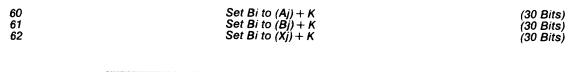

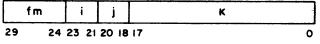

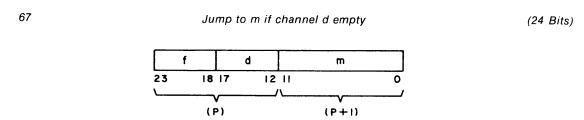

| 60ijK          | Set Bi to (Aj) + K                                                               | 3-25         | 67dm         | Jump to m if channel d empty                                  | 4-21                                        |

| 61ijK          | Set Bi to (Bj) + K                                                               | 3-25         |              |                                                               | 7.61                                        |

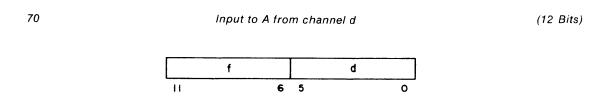

| 62ijK          | Set Bi to (Xj) + K                                                               | 3-25         | 70d          | Input to A from channel d                                     | 4-21                                        |

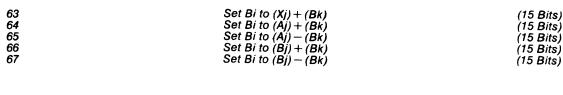

| 63ijk          | Set Bi to (Xj) + (Bk)                                                            | 3-25         | 71dm         | Input (A) words to m from channel d                           | 4-22                                        |

| 64ijk          | Set Bi to (Aj) + (Bk)                                                            | 3-25         | 72d          | Output from A on channel d                                    | 4-22                                        |

| 65ijk          | Set Bi to (Aj) - (Bk)                                                            | 3-25         | 73dm         | Output (A) words from m on channel d                          | 4-23                                        |

| 66ijk          | Set Bi to (Bj) + (Bk)                                                            | 3-25         | 74d          | Activate channel d                                            | 4-23                                        |

| 67ijk          | Set Bi to (Bj) - (Bk)                                                            | 3-25         | 75d          | Disconnect channel d                                          | 4-24                                        |

| 70ijK<br>71ijK | Set Xi to (Aj) + K                                                               | 3-26         | 76d          | Function (A) on channel d                                     | 4-24                                        |

| 71ijK          | Set Xi to (Bj) + K                                                               | 3-26         | 77dm         | Function m on channel d                                       | 4-24                                        |

|                |                                                                                  |              |              |                                                               |                                             |

New features, as well as changes, deletions, and additions to information in this manual, are indicated by bars in the margins or by a dot near the page number if the entire page is affected. A bar by the page number indicates pagination rather than content has changed.

|                        | REVISION RECORD                                                                                    |

|------------------------|----------------------------------------------------------------------------------------------------|

| REVISION               | DESCRIPTION                                                                                        |

| Α                      | Manual Released.                                                                                   |

| (2-22-71)              |                                                                                                    |

| В                      | Manual revised, editorial corrections.                                                             |

| (3-1-71)               |                                                                                                    |

| С                      | Revise move, compare instructions and integer multiply instruction. ECO 27834.                     |

| (7-71)                 |                                                                                                    |

| D                      | Manual revised; includes Engineering Change 31589. Pages iii, v, 3-3, 3-7, 3-12, 3-13, 3-20, 3-21, |

| (4-27-72)              | 3-22,3-23,4-14,4-15 are revised. Pages 4-25,4-26,4-27,4-28,4-29, and 4-30 are added.               |

| E                      | Manual revised; includes Engineering Change Order 30639. Page 3-17 is revised.                     |

| (3-13-73)              |                                                                                                    |

| F                      | Manual revised; includes Engineering Change Order 33110. Inside Front Cover and pages 3-1,         |

| (3-13-73)              | 3-21, 4-21, 4-22, 4-24 are revised.                                                                |

| G                      | Manual revised; includes Engineering Change Order 33534. Pages 3-20, 4-23, and 4-24 are            |

| (4-1-74)               | revised.                                                                                           |

| H                      | Manual revised; includes Field Change Order 34719. Pages 4-15, 4-16, and 4-17 are revised.         |

| (6-26-74)              | Manual 10715cu, included 11014 Change Order 017107 1 ages 1 20, 1 20, una 1 17 az 0 10712047       |

| J                      | Manual revised; includes Engineering Change Order 35678. Page 3-17 is revised.                     |

| (12-5-74)              |                                                                                                    |

| K .                    | Manual revised; includes Engineering Change Order 36469. Pages 3-10 and 4-25 are revised.          |

| (8-15-75)              | )                                                                                                  |

| L<br>L                 | Manual revised; includes Engineering Change Order 37244. Front cover, title page, ii, iii, and     |

| (5-3-76)               | 3-20 are revised.                                                                                  |

| M                      | Manual revised; includes Engineering Change Order 37148. Page 4-21 and 4-22 are revised.           |

| (5-3-76)               |                                                                                                    |

| N N                    | Manual revised; includes Engineering Change Order 37836. Pages iii and 4-2 are revised.            |

| (6-15 <del>-</del> 77) | Walluar revised, includes mighter mg change order 5,000. Tagos III and 1 2 are 10,000.             |

| (0 13 11)              |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

|                        |                                                                                                    |

REVISION LETTERS I, O, Q AND X ARE NOT USED

© 1971, 1972, 1973, 1974, 1975, 1976, 1977 by Control Data Corporation

Printed in the United States of America

Address comments concerning this manual to:

Control Data Corporation Publications and Graphics Division 4201 North Lexington Avenue St. Paul, Minnesota 55112 or use Comment Sheet in the back of this manual,

## **PREFACE**

The CONTROL DATA® CYBER 70 series reference manuals are published in a series of three volumes. This manual is volume 2 of the series and contains the instruction descriptions.

Volume 1 of the series contains the detailed system description/programming information. (Use the appropriate manual from the following list.)

| CDC Publication   | Publication Number |

|-------------------|--------------------|

| CYBER 70/Model 71 | 60453300           |

| CYBER 70/Model 72 | 60347000           |

| CYBER 70/Model 73 | 60347200           |

| CYBER 70/Model 74 | 60347400           |

Volume 3 of the series contains information about the Extended Core Storage (ECS), publication number 60347100.

These publications are available through the nearest Control Data sales office.

# **CONTENTS**

| 3.   | CENTRAL PROCESSOR INSTRUCT                   | CIONS |     | No Address Mode                                 | 4-1  |

|------|----------------------------------------------|-------|-----|-------------------------------------------------|------|

| Inst | ruction Formats                              | 3-1   |     | Direct Address Mode                             | 4-2  |

|      | Monitor, Stop                                | 3-3   |     | Indirect Address Mode                           | 4-2  |

|      | Branch                                       | 3-3   | Des | cription of Instructions                        | 4-3  |

|      | Extended Core Storage                        |       |     | No Operation                                    | 4-4  |

|      | Communication                                | 3-5   |     | Branch                                          | 4-5  |

|      | Central Exchange Jump                        | 3-6   |     | Shift                                           | 4-7  |

|      | Logical                                      | 3-7   |     | Logical                                         | 4-7  |

|      | Shift                                        | 3-9   |     | Data Transmission                               | 4-9  |

|      | Floating Point Arithmetic                    | 3-13  |     | Arithmetic                                      | 4-12 |

|      | Fixed Point Arithmetic                       | 3-19  |     | Central Processor and Central                   |      |

|      | Pass                                         | 3-20  |     | Memory Communications                           | 4-14 |

|      | Move, Compare Data Handling                  | 3-20  |     | Replace                                         | 4-17 |

|      | Increment                                    | 3-24  |     | Input/Output                                    | 4-20 |

| _    |                                              |       |     | Console Programming                             | 4-25 |

| 4.   | PERIPHERAL PROCESSOR<br>INSTRUCTIONS         |       |     | •.                                              |      |

| Inst | ruction Formats                              | 4-1   |     |                                                 |      |

| Add  | ress Modes                                   | 4-1   |     |                                                 |      |

|      |                                              | FIG   | URE | S                                               |      |

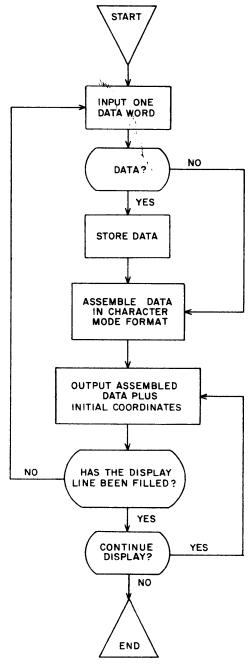

| 4-1  | Console Output Function Codes                | 4-27  | 4-3 | Character Data Word                             | 4-27 |

| 4-2  | Coordinate Data Word                         | 4-27  | 4-4 | Receive and Display Program Flow Chart          | 4-29 |

|      |                                              |       |     |                                                 |      |

|      |                                              | TAB   | LES |                                                 |      |

| 3-1  | Central Processor Instruction<br>Designators | 3-2   | 4-2 | Peripheral Processor<br>Instruction Designators | 4-4  |

| 4-1  | Addressing Modes for Peripheral              |       | 4-3 | Keyboard Character Codes                        | 4-25 |

|      | Processor Instructions                       | 4-3   | 4-4 | Display Character Codes                         | 4-26 |

60347300 D

## INSTRUCTION FORMATS

This section describes the Central Processor instructions. The CPU instructions tend to fall into two categories: those causing computation and those causing storage references or program branching. The instructions causing only computation are generally executed in a fixed amount of time after they have been issued. Instructions involving storage references for operands or program branching require variable amounts of time and cannot be precisely timed.

Careful coding of critical program loops can produce substantial improvements in execution time. Detailed timing information is provided in the applicable CYBER 70 series System Description Reference Manual, which is volume 1 of the series.

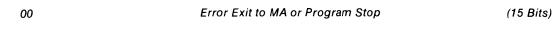

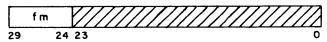

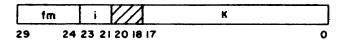

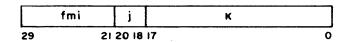

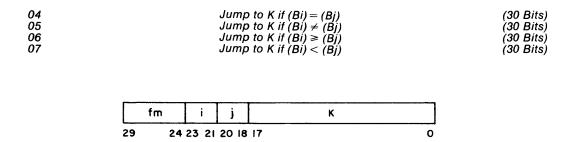

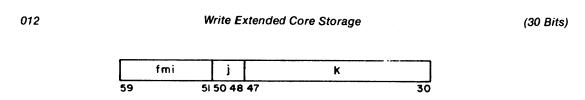

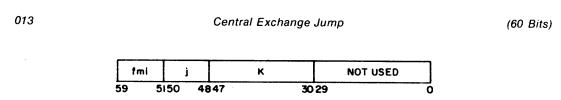

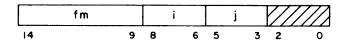

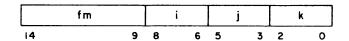

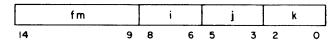

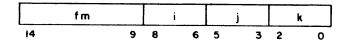

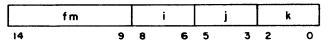

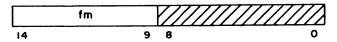

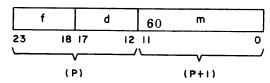

Preceding the description of each instruction is the octal code, the instruction name, the number of bits in the instruction, and a diagram showing the instruction format. Slanted parallel lines within a format diagram indicate unused bit positions. Table 3-1 defines the Central Processor instruction designators.

60347300 F 3-1

TABLE 3-1. CENTRAL PROCESSOR INSTRUCTION DESIGNATORS

| Designator | Use                                                                                                                                                                      |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A          | Specifies one of eight 18-bit address registers.                                                                                                                         |

| В          | Specifies one of eight 18-bit index registers; B0 is fixed and equal to zero.                                                                                            |

| C1         | The offset (character address) of the first character in the first word of the source field.                                                                             |

| C2         | The character address of the first character in the first word of the result field.                                                                                      |

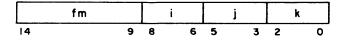

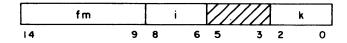

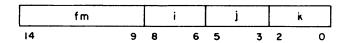

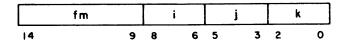

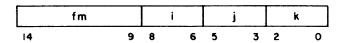

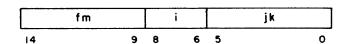

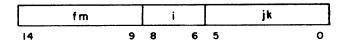

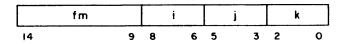

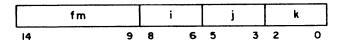

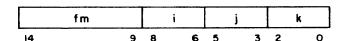

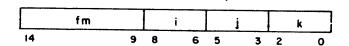

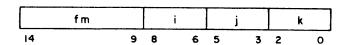

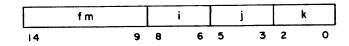

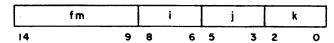

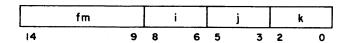

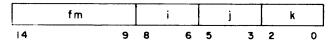

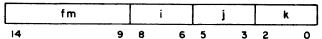

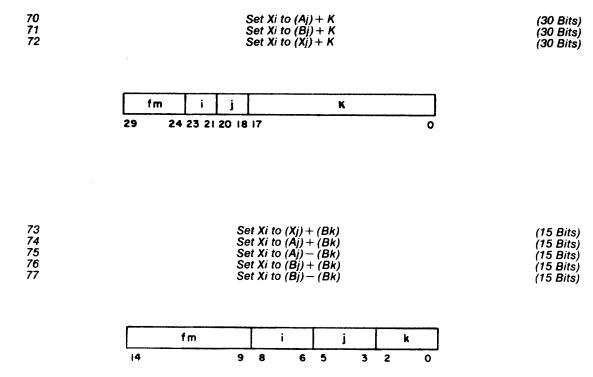

| fm         | A 6-bit instruction code.                                                                                                                                                |

| i          | A 3-bit code specifying one of eight designated registers (e.g., Ai).                                                                                                    |

| j          | A 3-bit code specifying one of eight designated registers (e.g., Bj).                                                                                                    |

| jk         | A 6-bit constant, indicating the number of shifts to be taken.                                                                                                           |

| k          | A 3-bit code specifying one of eight designated registers (e.g., Bk).                                                                                                    |

| К          | An 18-bit constant, used as an operand or as a branch destination (address).                                                                                             |

| K1         | An 18-bit address indicating the memory location of the first (left-most) character of the source field.                                                                 |

| K2         | An 18-bit address indicating the memory location of the first (left-most) character of the result field.                                                                 |

| LL         | The lower 4 bits of the field length (character count) of a move or compare instruction. Used with LU to specify field length.                                           |

| LU         | The upper 9 bits of the field length (character count) for indirect move instruction or the upper 3 bits for direct instructions.  Used with LL to specify field length. |

| X          | Specifies one of eight 60-bit operand registers.                                                                                                                         |

#### MONITOR, STOP

A panel switch labeled CEJ/MEJ determines which of the functions this instruction can perform. In the DISABLE position, the system has no central exchange (or monitor exchange) jump capability so the central processor stops. In the ENABLE position, the system has the jump capability so the 00 causes an exchange jump to the monitor address (MA) in the exchange jump package if the monitor flag is clear. It then sets the monitor flag. If the flag is already set, this instruction stops the central processor.

#### BRANCH

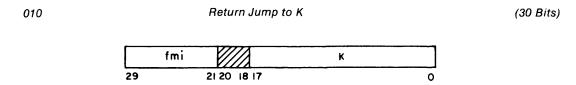

The instruction stores an 04 unconditional jump and the current address plus one [(P) + 1] in the upper half of address K, then branches to K + 1 for the next instruction. Note that this instruction is always out of the instruction stack, thus voiding the stack.

The octal word at K after the instruction appears as follows:

A jump to address K at the end of the branch routine returns the program to the original sequence.

60347300 D

This instruction adds the contents of increment register Bi to K and branches to the address specified by the sum. The branch address is K when i = 0. Addition is performed modulo  $2^{18}$ -1.

Note that this instruction is always out of the instruction stack, thus voiding the stack. For an unindexed, unconditional jump, the 04 instruction with i = j = 0 is a better choice. Thus, if this instruction is contained in a tight loop, the instruction at K can be obtained from the stack, if possible.

| <b>0</b> 30 | Jump to K if $(X_i) = 0$               | (30 Bits) |

|-------------|----------------------------------------|-----------|

| 031         | Jump to K if $(X_i) \neq 0$            | (30 Bits) |

| 032         | Jump to K if $(X_i) = plus$ (positive) | (30 Bits) |

| 033         | Jump to K if (Xi) = negative           | (30 Bits) |

| 034         | Jump to K if (Xj) is in range          | (30 Bits) |

| 035         | Jump to K if (Xj) is out of range      | (30 Bits) |

| 036         | Jump to K if (Xį́) is definite         | (30 Bits) |

| 037         | Jump to K if (Xi) is indefinite        | (30 Bits) |

These instructions branch to K when the 60-bit word in operand register  $X_j$  meets the condition specified by the i digit. The instruction allows zero, sign, and indefinite forms tests for fixed or floating point words.

The following applies to tests made in this instruction group:

- a) The 030 and 031 operations test the full 60-bit word in Xj. The words 000...000 and 777...777 are treated as zero. All other words are non-zero.

- b) The 032 and 033 operations examine only the sign bit (2<sup>59</sup>) of Nj. If the sign bit is zero, the word is positive; if the sign bit is one, the word is negative. Thus, the sign test is valid for fixed point words or for coefficient in floating point words.

c) The 034 and 035 operations examine the upper-order 12 bits of Xj. Both plus and minus infinity are detected:

3777XX...XX and 4000XX...XX are out of range; all other words are in range.

d) The 036 and 037 operations examine the upper-order 12 bits of Xj. Both plus and minus indefinite forms are detected:

1777XX...XX and 6000XX...XX are indefinite; all other words are definite.

These instructions test an 18-bit word from register Bi against an 18-bit word from register Bj (both words signed quantities) for the condition specified and branch to address K on a successful test. All tests against zero (all zeros) can be made by setting Bj = B0.

The following rules apply in the tests made by these instructions:

- a) Positive zero is recognized as unequal to negative zero, and

- b) Positive zero is recognized as greater than negative zero, and

- c) A positive number is recognized as greater than a negative number.

Note that the 06 and 07 instructions first perform a sign test on Bi and Bj and the Branch/ No Branch determination is based on the above rules. If Bi and Bj are of the same sign, a subtract test is performed (in the Increment Unit) and the sign of the result (Bi-Bj) determines whether a Branch is made.

#### EXTENDED CORE STORAGE COMMUNICATION

This category of instructions provides the ability to communicate with Extended Core Storage (ECS). This section describes Extended Core Storage instructions. A more detailed description of the instructions can be found in the Extended Core Storage volume of the Reference Manual (volume 3, Pub. No. 60347100).

These instructions must be located in the upper order position of the instruction word. If they are not, any attempt at execution will cause an exit to  $RA_{CM}$  regardless of the error mode bits. This will also happen if the instructions are used in a system that does not have ECS.

This instruction initiates a Read operation to transfer [(Bj) + K] 60-bit words from Extended Core Storage to Central Memory. The initial Extended Core Storage address is [(X0) +  $RA_{ECS}$ ]; the initial Central Memory address is [(A0) +  $RA_{CM}$ ].

This instruction initiates a Write operation to transfer [(Bj) + K] 60-bit words from Central Memory to Extended Core Storage. The initial Central Memory address is [(A0) +  $RA_{CM}$ ]; the initial Extended Core Storage address is [(X0) +  $RA_{ECS}$ ].

#### CENTRAL EXCHANGE JUMP

This instruction is enabled or disabled by a panel switch labeled CEJ/MEJ. If the switch is at ENABLE position, this instruction unconditionally exchange jumps the Central Processor, regardless of the state of the Monitor Flag bit. Instruction action differs, however, depending on whether the Monitor Flag bit is set or clear. Operation is as follows:

a) Monitor Flag bit clear. The starting address for the exchange is taken from the 18-bit Monitor Address register. Note that this starting address is an absolute address. During the exchange, the Monitor Flag bit is set.

- b) Monitor Flag bit set. The starting address for the exchange is the 18-bit result formed by adding K to the contents of register Bj. Note that this starting address is an absolute address. During the exchange, the Monitor Flag bit is cleared. If the CEJ/MEJ switch is at the DISABLE position, this instruction is illegal. P is cleared, P+1 is stored at RA, and the central processor is stopped.

- c) In dual central processor machines, when one CPU is in monitor mode, the other CPU cannot jump and will wait until the first CPU's monitor flag is cleared.

#### LOGICAL

10 Transmit (Xj) to Xi (15 Bits)

This instruction transfers a 60-bit word from operand register Xj to operand register Xi.

11 Logical product of (Xj) and (Xk) to Xi (15 Bits)

This instruction forms the logical product (AND function) of 60-bit words from operand registers Xj and Xk and places the product in operand register Xi. Bits of register Xi are set to "1" when the corresponding bits of the Xj and Xk registers are "1" as in the following example:

$$(Xj) = 0101$$

$(Xk) = 1100$

$Xi = 0100$

12 Logical sum of (Xj) and (Xk) to Xi (15 Bits)

This instruction forms the logical sum (inclusive OR) of 60-bit words from operand registers Xj and Xk and places the sum in operand register Xi. Bits of register Xi are set to "1" if the corresponding bit of the Xj or Xk register is a "1" as in the following example:

$$(Xj) = 0101$$

$(Xk) = 1100$

$$Xi = 1101$$

13

### Logical difference of (Xj) and (Xk) to Xi

(15 Bits)

This instruction forms the logical difference (exclusive OR) of 60-bit words from operand registers Xj and Xk and places the difference in operand register Xi. Bits of register Xi are set to "1" if the corresponding bits in the Xj and Xk registers are unlike as in the following example:

$$(Xj) = 0101$$

$(Xk) = 1100$

$Xi = 1001$

14

## Transmit the complement of (Xk) to Xi

(15 Bits)

This instruction extracts the 60-bit word from operand register Nk, complements it, and transmits this complemented quantity to operand register Ni.

15

Logical product of (Xj) and complement of (Xk) to Xi

(15 Bits)

This instruction forms the logical product (AND function) of the 60-bit quantity from operand register Xj and the complement of the 60-bit quantity from operand register Xk, and places the result in operand register Xi. Thus, bits of Xi are set to "1" when the corresponding bits of the Xj register and the complement of the Xk register are "1" as in the following example:

$$(Xj) = 0101$$

Complemented  $(Xk) = 0011$

$Xj = 0001$

(15 Bits)

16

This instruction forms the logical sum (inclusive OR) of the 60-bit quantity from operand register Xj and the complement of the 60-bit word from operand register Xk, and places the result in operand register Xi. Thus, bits of Xi are set to "1" if the corresponding bit of the Xj register or complement of the Xk register is a "1" as in the following example:

$$(Xj) = 0101$$

Complemented  $(Xk) = 0011$

$$Xi = 0111$$

17 Logical difference of (Xj) and complement of (Xk) to Xi

(15 Bits)

This instruction forms the logical difference (exclusive OR) of the quantity from operand register Xj and the complement of the 60-bit word from operand register Xk, and places the result in operand register Xi. Thus, bits of Xi are set to "1" if the corresponding bits of register Xj and the complement of register Xk are unlike as in the following example:

$$(Xj) = 0101$$

Complemented (Xk) =  $0011$

$$Xi = 0110$$

SHIFT

20 Left shift (Xi), jk places (15 Bits)

This instruction shifts the 60-bit word in operand register Xi left circular jk places. Bits shifted off the left end of operand register Xi replace those from the right end.

The 6-bit shift count jk allows a complete circular shift of register Xi.

21

#### Arithmetic right shift (Xi), jk places

(15 Bits)

This instruction shifts the 60-bit word in operand register Xi right jk places. The right-most bits of Xi are discarded and the sign bit is extended.

22

#### Left shift (Xk) nominally (Bj) places to Xi

(15 Bits)

This instruction shifts the 60-bit quantity from operand register Xk the number of places specified by the quantity in increment register Bj and places the result in operand register Xi.

- 1) If Bj is positive (i.e., bit 17 of Bj = 0), the quantity from Xk is shifted left-circular. (The low order six bits of Bj specify the shift count.)

- 2) If Bj is negative (i.e., bit 17 of Bj = 1), the quantity from Xk is shifted right (end off with sign extension). (The one's complement of the low order eleven bits of Bj specify the shift count.) If any of bits 2<sup>6</sup>-2<sup>10</sup>, after complementing, are "1's", the shift is not performed and the result register Xi is cleared to all zeros.

23

## Right shift (Xk) nominally (Bj) places to Xi

(15 Bits)

This instruction shifts the 60-bit quantity from operand register Xk the number of places specified by the quantity in increment register Bj and places the result in operand register Xi.

- If Bj is positive (i.e., bit 17 of Bj = 0), the quantity from register Xk is shifted right (end-off with sign extension). (The low order eleven bits of Bj specify the shift count.) If any of bits  $2^6-2^{10}$  are "1's", the shift is not performed and the result register Xi is cleared to all zeros.

- 2) If Bj is negative (i.e., bit 17 of Bj = 1), the quantity from register Xk is shifted left circular. (The complement of the lower order six bits of Bj specify the shift count.)

This instruction normalizes the floating point quantity from operand register Xk and places it in operand register Xi. The number of left shifts necessary to normalize the quantity is entered in increment register Bj. A Normalize operation may cause underflow which will clear Xi to all zeros regardless of the original sign of Xk. Normalizing either a plus or minus zero coefficient sets the shift count (Bj) to  $48_{10}$  and clears Xi to all zeros.

If Xk contains an infinite quantity (3777X...X or 4000X...X) or an indefinite quantity (1777X...X or 6000X...X), no shift takes place. The contents of Xk are copied into Xi and Bj is set equal to zero. Optional error exits do occur.

25

#### Round and normalize (Xk) to Xi and Bj

(15 Bits)

This instruction performs the same operation as instruction 24 except that the quantity from operand register Xk is rounded before it is normalized. Rounding is accomplished by placing a "1" round bit immediately to the right of the least significant coefficient bit. Normalizing a zero coefficient places the round bit in bit 47 and reduces the exponent by 48. Note that the same rules apply for underflow.

If Nk contains an infinite quantity (3777X...X or 4000X...X) or an indefinite quantity (1777X...X or 6000X...X), no shift takes place. The contents of Nk are copied into Ni and Bj is set equal to zero. Optional error exits do occur.

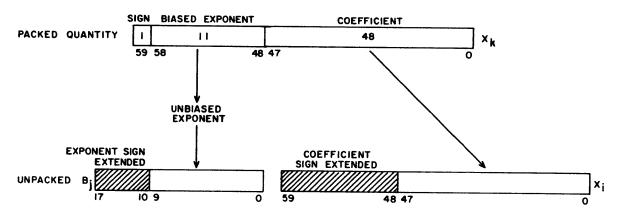

This instruction unpacks the floating point quantity from operand register Xk and sends the 48-bit coefficient to operand register Xi and the 11-bit exponent to increment register Bj. The exponent bias is removed during Unpack so that the quantity in Bj is the one's complement representation of the true exponent.

The exponent and coefficient are sent to the low-order bits of the respective registers as shown below:

27

Pack Xi from (Xk) and (Bj)

(15 Bits)

This instruction packs a floating point number in operand register Xi. The coefficient of the number is obtained from operand register Xk and the exponent from increment register Bj. Bias is added to the exponent during the Pack operation. The instruction does not normalize the coefficient.

Exponent and coefficient are obtained from the proper low-order bits of the respective registers and packed as shown in the illustration for the Unpack (26) instruction. Thus, bits 48 to 58 of Xk and bits 11 to 17 of Bj are ignored. There is no test for overflow or underflow.

Note that if Xk is positive, the packed exponent occupying positions 48 to 58 of Xi is obtained from bits 0 to 10 of Bj by complementing bit 10; if Xk is negative, bit 10 is not complemented but bits 0 to 9 are.

This instruction forms a mask in operand register Xi. The 6-bit quantity jk defines the number of "1's" in the mask as counted from the highest order bit in Xi.

The contents of operand register i = 0 when jk = 0.

#### FLOATING POINT ARITHMETIC

This instruction forms the sum of the floating point quantities from operand registers Xj and Xk and packs the result in operand register Xi. The packed result is the upper half of a double precision sum.

At the start both arguments are unpacked, and the coefficient of the argument with the smaller exponent is entered into the upper half of a 96-bit accumulator. The coefficient is shifted right by the difference of the exponents. The other coefficient is then added into the upper half of the accumulator. If overflow occurs, the sum is right-shifted one place and the exponent of the result increased by one. The upper half of the accumulator holds the coefficient of the sum, which is not necessarily in normalized form. The exponent and upper coefficient are then repacked in operand register Xi.

If both exponents are zero  $(2000_8)$  and no overflow occurs, the instruction causes an ordinary integer addition. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

60347300 D

(15 Bits)

31

This instruction forms the difference of the floating point quantities from operand registers Xj and Xk and packs the result in operand register Xi. Alignment and overflow operations are similar to the Floating Sum (30) instruction, and the difference is not necessarily normalized. The packed result is the upper half of a double precision difference.

An ordinary integer subtraction is performed when the exponents are zero. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

32

#### Floating DP sum of (Xj) and (Xk) to Xi

(15 Bits)

This instruction forms the sum of two floating point numbers as in the Floating Sum (30) instruction, but packs the lower half of the double precision sum with an exponent 48 less than the upper sum. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

33

Floating DP difference of (Xj) and (Xk) to Xi

(15 Bits)

This instruction forms the difference of two floating point numbers as in the Floating Difference (31) instruction, but packs the lower half of the double precision difference with an exponent of 48 less than the upper sum. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

This instruction forms the round sum of the floating point quantities from operand registers Xj and Xk and packs the upper sum of the double precision result in operand register Xi. The sum is formed in the same manner as the Floating Sum instruction but the operands are rounded before the addition, as shown below, to produce a round sum.

- 1) A round bit is attached at the right end of both operands if:

- a) both operands are normalized, or

- b) the operands have unlike signs.

- 2) A round bit is attached at the right end of the operand with the larger exponent for all other cases.

- 3) In the event that the operands have equal exponents, a round bit is attached to the coefficient for only one of the operands.

For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

Round floating difference of (Xj) and (Xk) to Xi

(15 Bits)

This instruction forms the round difference of the floating point quantities from operand registers Xj and Xk and packs the upper difference of the double precision result in operand register Xi. The difference is formed in the same manner as the Floating Difference (31) instruction but the operands are rounded before the subtraction, as shown below, to produce a round difference.

- 1) A round bit is attached at the right end of both operands if:

- a) both operands are normalized, or

- b) the operands have like signs.

- 2) A round bit is attached at the right end of the operand with the larger exponent for all other cases.

- 3) In the event that the operands have equal exponents, a round bit is attached to the coefficient for only one of the operands.

For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

40

### Floating product of (Xj) and (Xk) to Xi

(15 Bits)

This instruction multiplies two floating point quantities obtained from operand registers Xj (multiplier) and Xk (multiplicand) and packs the upper product result in operand register Xi.

The two 48-bit coefficients are multiplied together to form a 96-bit product. The upper 48 bits of the product (bits 48-95) are then packed together with the resulting exponent. Note that when using unnormalized quantities, the entire result could lie in the lower-order 48 bits of the product; hence, this result would be lost when packing occurs.

The result is a normalized quantity only when both operands are normalized; the exponent in this case is the sum of the exponents plus 47 (or 48).

The result is unnormalized when either or both operands are unnormalized; the exponent in this case is the sum of the exponents plus 48. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

This instruction is not meant for integer multiplication, however it can be used to indicate overflow resulting from operands too large for integer multiplication. Any non-zero resultant from an attempted integer multiply indicates overflow.

This instruction multiplies the floating point number from operand register Xk (multiplicand), by the floating point number from operand register Xj. The upper product result is packed in operand register Xi. (No lower product available.) The multiply operation is identical to that of instruction 40 with the following exception:

Before the left shift of the final product and during the merge operation to form the final product, a "1" bit is added to bit  $2^{46}$ . The following rounded result is the net effect of this action:

- for products  $> 2^{95}$ , round is by one-fourth

- for all other products, round is by one-half

- when one or both operands are unnormalized, round is by one-fourth.

The result is a normalized quantity only when both operands are normalized; the exponent in this case is the sum of the exponents plus 47 (or 48).

The result is unnormalized when either or both operands are unnormalized; the exponent in this case is the sum of the exponents plus 48. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

42

Floating DP product of (Xi) and (Xk) to Xi

(15 Bits)

This instruction multiplies two floating point quantities obtained from operand registers Xj and Xk and packs the lower product in operand register Xi. The two 48-bit coefficients are multiplied together to form a 96-bit product. The lower-order 48 bits of this product (bits 47-00) are then packed together with the resulting exponent. The result is not necessarily a normalized quantity. The exponent of this result is 48 less than the exponent resulting from a 40 instruction using the same operands. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

#### INTEGER MULTIPLY

The 42 code performs short word integer multiplication of 47-bit operands if the 12 upper bits (exponents) of both operands are sign extended and one or both of the operands are not normalized. The 48 bit result is entered into Xi with sign extension. To ensure a resultant integer of 48 bits or less, the sum of the non-sign bits in the two operands should not exceed 48 bits. To detect overflow, see the 40 instruction description. Both operands normalized cause underflow results to be reported.

44

#### Floating divide (Xj) by (Xk) to Xi

(15 Bits)

This instruction divides two normalized floating point quantities obtained from operand registers Xj (dividend) and Xk (divisor) and packs the quotient in operand register Xi.

The exponent of the result in a no-overflow case is the difference of the dividend and divisor exponents minus 48.

A one-bit overflow is compensated for by adjusting the exponent and right shifting the quotient one place. In this case the exponent is the difference of the dividend and divisor exponents minus 47.

The result is a normalized quantity when both the dividend and the divisor are normalized. A divide fault occurs when the coefficient of the dividend is two or more times as large as the coefficient of the divisor. This forces an indefinite result (17770...0). To avoid this, normalize both operands before executing this instruction. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

45

#### Round floating divide (Xj) by (Xk) to Xi

(15 Bits)

This instruction divides the floating quantity from operand register j (dividend) by the floating point quantity from operand register Xk (divisor) and packs the round quotient in operand register Xi. Rounding is accomplished by adding one-third during the division process. In effect, the quantity "2525....25258" resides immediately to the right of the dividend binary point prior to starting the divide operation. On the first iteration, a "1" is added to the least significant bit of the dividend. After each iteration (subtraction of divisor from partial dividend) a two-place left shift occurs and a "1" is again added to the least significant bit of the partial dividend. Thus, successive iterations gradually bring in the one-third round "quantity" (25....258).

The result exponent in a no-overflow case is the difference of the dividend and divisor exponents minus 48.

A one-bit overflow is compensated for by adjusting the exponent and right shifting the quotient one place; in this case the exponent is the difference of the dividend and divisor exponents minus 47.

The result is a normalized quantity when both the dividend and the divisor are normalized. A divide fault occurs when the coefficient of the dividend is two or more times as large as the coefficient of the divisor. This forces an indefinite result (17770...0). To avoid this, normalize both operands before executing this instruction. For treatment of special operands and/or indefinite forms, refer to the programming information in volume 1.

#### FIXED POINT ARITHMETIC

This instruction forms a 60-bit one's complement sum of the quantities from operand registers Xj and Xk and stores the result in operand register Xi. An overflow condition is ignored.

This instruction forms the 60-bit one's complement difference of the quantities from operand registers Xj (minuend) and Xk (subtrahend) and stores the result in operand register Xi. An overflow condition is ignored.

This instruction counts the number of "1's" in operand register Nk and stores the count in the lower order 6 bits of operand register Ni. Bits 6 through 59 are cleared to zero.

46

#### No operation (Pass)

(15 Bits)

This is a pass instruction for Models 71 and 74 machines. It is also a pass instruction for Models 72 and 73 except for the move and compare instruction codes (464-467) when any of them is in parcel 0. The example shows a typical use for this code.

#### EXAMPLE:

| :     | 59       |       |          |          |       | 0 |

|-------|----------|-------|----------|----------|-------|---|

| P     | 30 - BIT | INST. | 15 - BIT | INST.    | PASS  |   |

| P + 1 | 30-BIT   | INST. |          | 30 - BIT | INST. |   |

In this example, a Pass instruction is used to pad the remainder of the word at P. Since the next instruction is 30 bits, it cannot fit in P and must be placed in P + 1.

# MOVE, COMPARE DATA HANDLING (Applicable only to Models 72 and 73)

These instructions are present on CDC CYBER Models 72 and 73 only. The instructions must be located in parcel 0 of the 60-bit instruction word or they will be interpreted as Pass instructions. These instructions are treated as illegal instructions in CDC CYBER Models 71 and 74.

Data fields consisting of 6-bit characters may start or end with any character position (offset) of the 10 6-bit positions in each word. The character positions are designated as follows:

| 0          | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 |

|------------|---|---|---|---|---|---|---|---|---|

| <b>5</b> 9 |   |   |   |   |   |   |   |   | 0 |

For Move instructions the designator K1 specifies which storage word contains the first character of the source data field and designator C1 specifies the character position (offset) of the first character. Designator K2 specifies the storage location in which the first character of the result data field will be placed and designator C2 specifies the first character position. For Compare instructions, both data field addresses specify source fields.

#### EXAMPLE:

If the instruction were K1=1000 and C1=3, the first character of the source field is at position 3 of location 1000.

|      |     | _     | _   | •  | _  | •  | 6  | •  | •  | •  |

|------|-----|-------|-----|----|----|----|----|----|----|----|

| 1000 | 1// | ///// | 111 | 71 | 72 | 73 | 74 | 75 | 76 | 77 |

The first character of the source field is thus 71.

An address is out-of-range if: C1 or C2 is greater than 9<sub>10</sub>, K1+N1 is greater than the relative address plus the program field length (RA+FL) (N1 = number of memory references made to the source data field starting at K1), K2+N2 is greater than (RA+FL) (N2 = number of memory references made to the result data field starting at K2). The address out-of-range condition is not predicted. When the condition occurs, some unpredictable part of the operation will be performed. The amount of the operation performed does not necessarily repeat on an identical out-of-range condition.

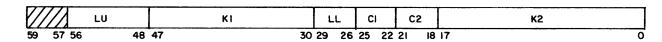

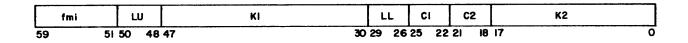

LL is the lower 4 bits and LU the upper 9 bits of the field length designator in numbers of characters. The maximum length of the data fields for the Move Direct and the Compare instructions is 177<sub>8</sub> (127<sub>10</sub>) characters. The maximum data field length for the Move Indirect instruction is 1777<sub>8</sub> (8191<sub>10</sub>) characters. If L (LU and LL combined) is zero, the instruction becomes a pass.

For overlapping Move instructions, the address of the source field (K1) must be greater than the address of the result field (K2) to provide proper field overlap. If K1 is less than K2, part of the source field will be changed during execution, with amount of change determined by the number of memory conflicts encountered. Overlapping fields should not contain more than 377<sub>8</sub> characters, because an exchange jump interrupts any compare/move operation having a decremented field length greater than 377<sub>9</sub>.

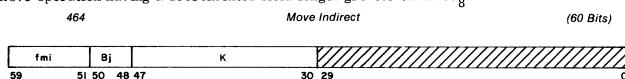

This instruction moves the source field to the result field as specified by the descriptor. The quantity Bj + K is the address of the descriptor. Any instructions located in bit positions 0-29 will not be executed.

60-Bit Descriptor Word

The move is from left to right through the field. Register X0 is cleared at the end of execution.

3 - 21

465 Move Direct (60 Bits)

This instruction moves the source field to the result field as specified by the instruction. The field length is limited to a 7 bit count.

466

Compare Collated

(60 Bits)

fmi

LU

KI

LL

CI

C2

K2

59

51 50 48 47

30 29 26 25 22 21 18 17

0

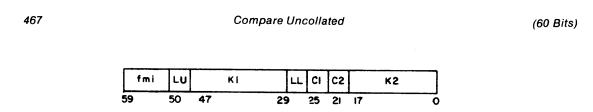

This instruction compares the field designated by K1, C1 with the field designated by K2, C2 and sets X0 as follows then terminates:

If (field K1) is greater than (field K2), set X0 to 00 - 0XXX

If (field K1) is equal to (field K2), set X0 to 00 - 000

If (field K1) is less than (field K2), set X0 to 77 - 7YYY where YYY is the complement of XXX

The compare is made left to right through the fields until two unequal characters are found. These two characters are then collated (looked up in the collating table beginning at address A0). If the table values found for the two unequal characters is the same, the compare continues until another pair of characters are unequal or until the field length is exhausted. If the table values found for the two unequal characters are unequal, X0 is set according to the rules shown above.

The value of the three octal numbers XXX, stored in X0 is determined by the equation L - N = XXX, where L is the length of the field and N is the number of pairs of characters that were collated equal, prior to instruction termination. In other words XXX is the number of pairs of characters not yet compared plus one.

3-22 60347300 D

Register A0 contains the starting word address of an 8 word, 64 character, collating table. This table must have been previously stored in consecutive memory locations.

| Address | Colla | ating | Chara | acter | Loca | tions |    |    |                 |                |

|---------|-------|-------|-------|-------|------|-------|----|----|-----------------|----------------|

| A0      | 00    | 01    | 02    | 03    | 04   | 05    | 06 | 07 |                 | <u> </u>       |

| A0+1    | 10    | 11    | 12    | 13    | 14   | 15    | 16 | 17 | <i>X</i> ////// | <i>\\\\\\\</i> |

| A0+2    | 20    | 21    | 22    | 23    | 24   | 25    | 26 | 27 | MINI            |                |

| A0+3    | 30    | 31    | 32    | 33    | 34   | 35    | 36 | 37 | <i>IIIIII</i>   |                |

| A0+4    | 40    | 41    | 42    | 43    | 44   | 45    | 46 | 47 | MININ           |                |

| A0+5    | 50    | 51    | 52    | 53    | 54   | 55    | 56 | 57 | MIIII           | WWW            |

| A0+6    | 60    | 61    | 62    | 63    | 64   | 65    | 66 | 67 | XIIIIIX         | <i>\\\\\\\</i> |

| A0+7    | 70    | 71    | 72    | 73    | 74   | 75    | 76 | 77 | MMM             |                |

|         | 59    |       |       |       |      |       |    | 12 | 11              | 0              |

The collated value of a character is found by examining the collating table. The upper three bits of the character to be collated are added to the contents of register A0 to obtain the relative address of the word containing the collated value. The lower three bits of the character to be collated specify the character address of the collated value.

#### EXAMPLE:

Suppose the character under examination were an octal 63. The 6 would be added to the contents of register A0 to form the word address and the 3 would be used to pick the correct character from that word. The value of 63 is 63 in the collating table.

This instruction is identical to the Compare Collated instruction with one exception. The collating table is not used. X0 is set when the first pair of unequal characters is encountered or when the field length is exhausted.

#### INCREMENT

These instructions perform one's complement addition and subtraction of 18-bit operands and store an 18-bit result in address register Ai. Overflow, in itself, is ignored, but an address range fault may result from overflow in this set of instructions.

Operands are obtained from address (A), increment (B), and operand (X) registers as well as the instruction itself (K = 18-bit signed constant). Operands obtained from an Xj operand register are the truncated lower 18 bits of the 60-bit word.

Note that an immediate memory reference is performed to the address specified by the final content of address registers A1 - A7. The operand read from memory address specified by A1 - A5 is sent to the corresponding operand register X1 - X5. When A6 or A7 is referenced, the operand from the corresponding X6 or X7 operand register is stored at the address specified by A6 or A7.

#### NOTE

If, in this category of instructions, the result placed in address register Ai is an address out of range, the following occurs: (Note that this action is independent of an Exit selection on Address Out of Range.)

If i = 1-5: Operand register Xi is loaded with the contents of absolute address zero and the contents of memory location (Ai) are unchanged.

If i = 6 or 7: Operand register Xi retains its original contents and the contents of memory location (Ai) are unchanged.

## EXAMPLE: (For system with 131K central memory)

50

$$SAi = Aj + K$$

$i = 4$

$$SA_4 = A_6 + K j = 6$$

$$SA_4 = 032100_8 + 234567_8$$

$$SA_4 = 266667_8$$

## Initial Quantities

$A_6 = 032100_8$

x<sub>4</sub> - 00..... 00<sub>8</sub>

Storage location  $266667 = 7 \dots 75342104600_{8}$

# Final Quantities:

$A_4 = 266667_8$   $A_6 = 032100_8$   $X_4 = 7 \dots 75342104600_8$

These instructions perform one's complement addition and subtraction of 18-bit operands and store an 18-bit result in increment register Bi. An overflow condition is ignored.

Operands are obtained from address (A), increment (B), and operand (X) registers as well as the instruction itself (K = 18-bit signed constant). Operands obtained from an Xj operand register are the truncated lower 18 bits of the 60-bit word.

These instructions perform one's complement addition and subtraction of 18-bit operands and store an 18-bit result into the lower 18 bits of operand register Xi. The sign of the result is extended to the upper 42 bits of operand register Xi. An overflow condition is ignored.

Operands are obtained from address (A), increment (B), and operand (X) registers as well as the instruction itself (K = 18-bit signed constant). Operands obtained from an Xj operand register are the truncated lower 18 bits of the 60-bit word.

## EXAMPLE:

73 SXi Xj + Bk i = 2

$$X_2 = 0 \dots 0745321402_8$$

SX<sub>2</sub>  $X_3 + B_1$  j = 3, k = 1  $X_3 = 0 \dots 0652224310_8$

SX<sub>2</sub> = 0 \dots 0652224310<sub>8</sub> + 511245<sub>8</sub>  $B_1 = 511245_8$

SX<sub>2</sub> = 7 \dots 7777735555<sub>8</sub>

# Initial Quantities:

$$X_2 = 0 \dots 0745321402_8$$

$X_3 = 0 \dots 0652224310_8$

$B_1 = 511245_8$

# Final Quantities:

$$X_2 = 7 \dots 7777735555_8$$

$X_3 = 0 \dots 0652224310_8$

$B_1 = 511245_8$

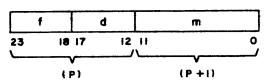

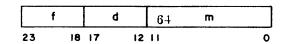

## INSTRUCTION FORMATS

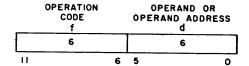

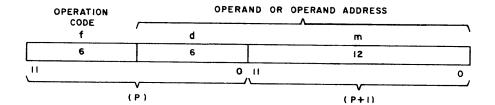

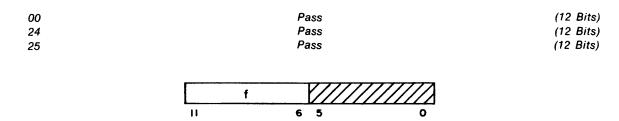

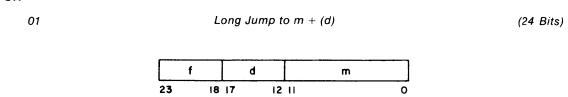

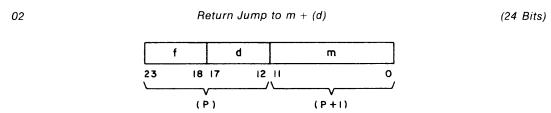

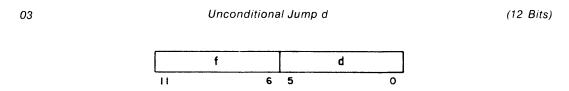

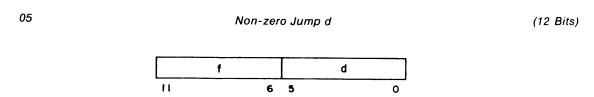

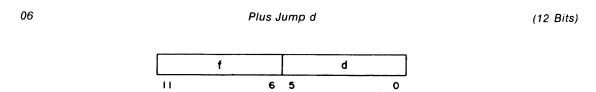

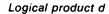

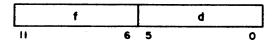

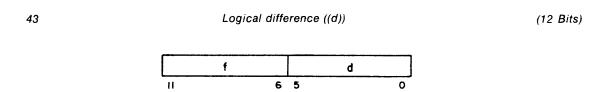

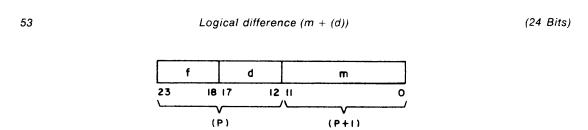

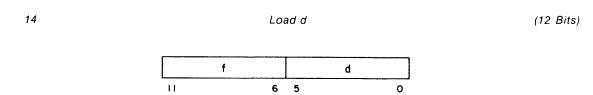

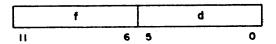

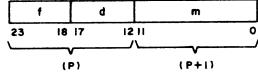

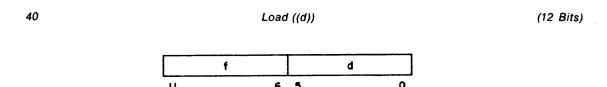

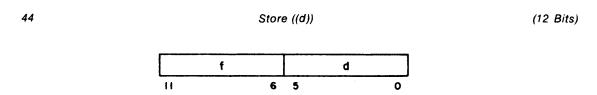

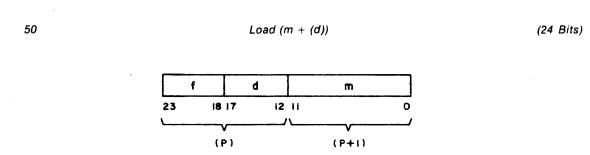

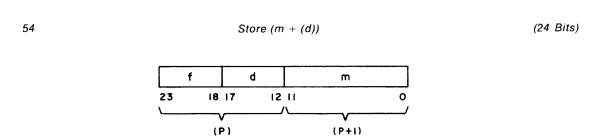

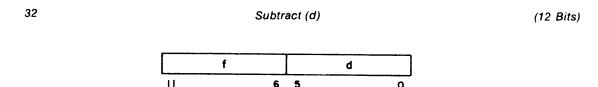

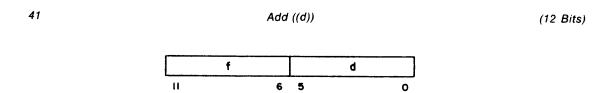

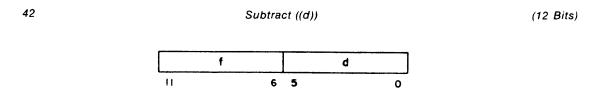

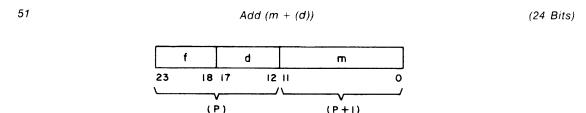

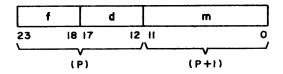

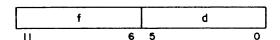

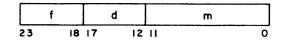

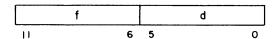

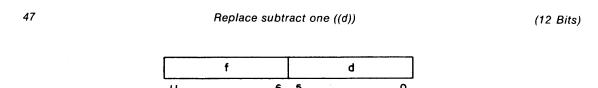

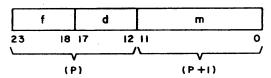

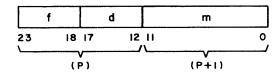

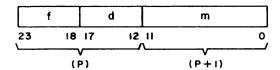

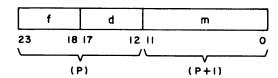

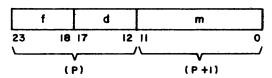

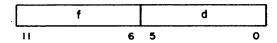

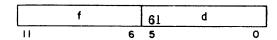

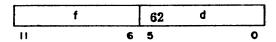

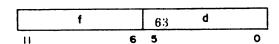

Two formats are used; 12-bit and 24-bit. The 12-bit format has a 6-bit operation code f and a 6-bit operand or operand address d.

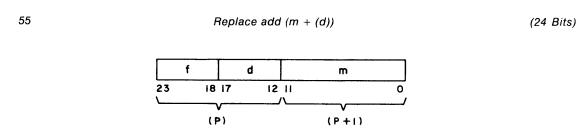

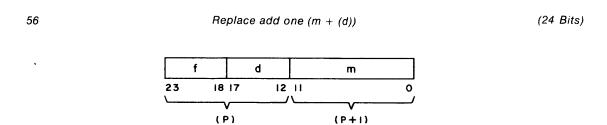

The 24-bit format uses the 12-bit quantity m, the contents of the next program address (P+1), with d to form an 18-bit operand or operand address.

## **ADDRESS MODES**

Program indexing is accomplished and operands are manipulated in several modes. The two instruction formats provide for 6-bit or 18-bit operands and 6-bit, 12-bit or 18-bit addresses.

## NO ADDRESS MODE

In this mode d or dm is used as an operand. This mode eliminates the need for storing constants. The d quantity is considered a 12-bit number, the upper six bits of which are zero. The dm quantity has d as the upper six bits and m as the lower 12 bits.

60347300 C

#### **DIRECT ADDRESS MODE**

In this mode, d or m + (d) is used as the address of the operand. The d quantity specifies one of the first 64 addresses in memory  $(0000-0077_8)$ . The m + (d) quantity generates a 12-bit address for referencing all possible peripheral memory locations  $(0000-7777_8)$ . If d ≠ 0, the content of address d is added to m to produce an operand address (indexed addressing). If d = 0, m is taken as the operand address. If m =  $7777_8$ , the address is 0. Address  $7777_8$  is only accessible if the value of d is  $7777_8$  and m =  $7777_8$ .

EXAMPLE: Address Modes

Given: d = 25m = 100

contents of location 25 = 0150 contents of location 150 = 7776 contents of location 250 = 1234

Then:

| MODE             | INSTRUCTION | A REGISTER      |

|------------------|-------------|-----------------|

| No Address       | 14          | 000025          |

|                  | 20          | 250100          |

| Direct Address   | 30<br>50    | 000150 $001234$ |

|                  | . •         | 007776          |

| Indirect Address | 40          | 001110          |

#### INDIRECT ADDRESS MODE

In this mode, d specifies an address which contains the address of the desired operand. Thus the operand is indirectly obtained. Indirect addressing and indexed addressing require an additional memory reference beyond that required by direct addressing. Address  $7777_8$  is accessible if the desired operand address is  $7777_8$ .

The description of instructions uses the expression (d) to define the contents of memory location d. An expression with double parentheses ((d)) refers to indirect addressing. The expression (m + (d)) refers to direct addressing when d = 0 and to indexed direct addressing when  $d \neq 0$ . Table 4-1 summarizes the addressing modes used for the Peripheral Processor instructions.

TABLE 4-1. ADDRESSING MODES FOR PERIPHERAL PROCESSOR INSTRUCTIONS

| To red our of the co | Address Mode    |    |            |  |

|----------------------|-----------------|----|------------|--|

| Instruction<br>Type  | Direct Indirect |    | No Address |  |

| Load                 | 30, 50          | 40 | 14, 20     |  |

| Add                  | 31, 51          | 41 | 16, 21     |  |

| Subtract             | 32, 52          | 42 | 17         |  |

| Logical Difference   | 33, 53          | 43 | 11, 23     |  |

| Store                | 34, 54          | 44 |            |  |

| Replace Add          | 35, 55          | 45 |            |  |

| Replace Add One      | 36, 56          | 46 |            |  |

| Replace Subtract One | 37, 57          | 47 |            |  |

| Long Jump            | 01              |    |            |  |

| Return Jump          | 02              |    |            |  |

| Unconditional Jump   |                 |    | 03         |  |

| Zero Jump            |                 |    | 04         |  |

| Non-Zero Jump        |                 |    | 05         |  |

| Positive Jump        |                 |    | 06         |  |

| Minus Jump           |                 |    | 07         |  |

| Shift                |                 |    | 10         |  |

| Logical Product      |                 |    | 12, 22     |  |

| Selective Clear      |                 |    | 13         |  |

| Load Complement      |                 |    | 15         |  |

# **DESCRIPTION OF INSTRUCTIONS**

This section describes the Peripheral Processor instructions. Table 4-2 lists designators used throughout the section.

TABLE 4-2. PERIPHERAL PROCESSOR INSTRUCTION DESIGNATORS

| Designator | Use                                                                         |

|------------|-----------------------------------------------------------------------------|

| A          | The A register.                                                             |

| d          | A 6-bit operand or operand address.                                         |

| f          | A 6-bit instruction code.                                                   |

| m          | A 12-bit quantity used with d to form an 18-bit operand or operand address. |

| P          | The Program Address register.                                               |

| Q          | The Q register.                                                             |

| ()         | Contents of a register or location                                          |

| ( () )     | Refers to indirect addressing.                                              |

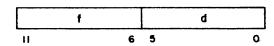

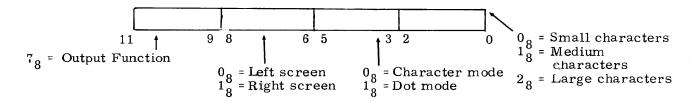

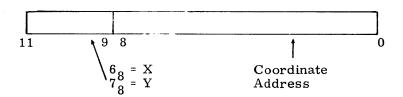

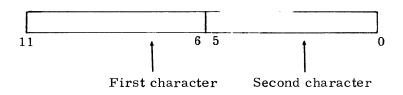

Preceding the description of each instruction is the octal code, the instruction name and instruction length.

# EXAMPLE:

Instruction formats are also given; hashed lines within a format indicate bits which are not used in the operation.

# NO OPERATION

These instructions specify that no operation be performed. They provide the means for padding out a program.

#### BRANCH

This instruction jumps to the sequence beginning at the address given by m + (d). If d = 0, then m is not modified.

This instruction jumps to the sequence beginning at the address given by m + (d). If d = 0 then m is not modified. The current program address (P) plus two is stored at the jump address. The new program commences at the jump address plus one. This program should end with a long jump to, or normal sequencing into, the jump address minus one, which should in turn contain a long jump, 0100. The latter returns the original program address plus two to the P register.

This instruction provides an unconditional jump to any instruction up to 31 steps forward or backward from the current program address. The value of d is added to the current program address. If d is positive (01 - 37), then 0001 (+1) - 0037 (+31) is added and the jump is forward. If d is negative (40 - 76) then 7740 (-31) - 7776 (-1) is added and the jump is backward. The program stops (a Dead Start is necessary to restart the machine) when d = 00 or 77.

O4 Zero Jump d (12 Bits)

This instruction provides a conditional jump to any instruction up to 31 steps forward or backward from the current program address. If the content of the A register is zero, the jump is taken. If the content of A is non-zero, the next instruction is executed. Negative zero (777777) is treated as non-zero. For interpretation of d see instruction 03.

This instruction provides a conditional jump to any instruction up to 31 steps forward or backward from the current program address. If the content of the A register is nonzero, the jump is taken. If A is zero, the next instruction is executed. Negative zero (777777) is treated as nonzero. For interpretation of d see instruction 03.

This instruction provides a conditional jump to any instruction up to 31 steps forward or backward from the current program address. If the content of the A register is positive, the jump is taken. If A is negative, the next instruction is executed. Positive zero is treated as a positive quantity; negative zero is treated as a negative quantity. For interpretation of d see instruction 03.

07

(12 Bits)