NO. 5241.0600 DATE 10/15/69 PAGE 1 OF 84 REV. 01

COMPUTER DEVELOPMENT

# SPECIFICATION BUFFER CONTROLLER {FR]0]}

#### LOG OF REVISION DATES PRIOR TO REVISION D1

| DATE OF ISSUE | DESCRIPTION OF ISSUE                |

|---------------|-------------------------------------|

| 5/13/68       | Rough Draft {Original Issue}        |

| 6/17/68       | Design-To-Requirements Draft        |

| 5/30/69       | Update Prior to Restricted Release  |

| 10/15/69      | Update Prior to Design Verification |

NO. 52410600 DATE 10/15/69 PAGE 2 REV. 01

#### COMPUTER DEVELOPMENT

|                                                                                                                                                                 | TABLE OF CONTENTS                                                                                                                             | Page No.                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| h • 0<br>c <sup>2</sup> • 0<br>d • 0                                                                                                                            | SCOPE<br>APPLICABLE DOCUMENTS<br>PERFORMANCE REQUIREMENTS                                                                                     | 8<br>8<br>8                      |

| 1 - 1 <sub>1</sub> 3 - 1 <sub>1</sub> - 1 <sub>1</sub> 4 - 1 <sub>1</sub> - 1 <sup>2</sup> 4 - 1 <sub>1</sub> - 4 3 - 1 <sub>1</sub> - 5 4 - 1 <sub>1</sub> - 6 | General Description Control Section Arithmetic Section Storage Interface Normal Channel Interface Coupler Interface Station Control Interface | 75<br>77<br>77<br>70<br>70       |

| 3 - 2 - 1 - 2<br>3 - 2 - 1 - 1<br>3 - 2 - 1 - 2                                                                                                                 | Performance Characteristics Instruction Formats Instruction Format 1 Instruction Format 2                                                     | 73<br>73<br>73<br>73             |

| 1.2.1.2.1<br>3.2.1.2.3<br>3.2.1.2.3<br>3.2.1.2.4<br>3.2.1.2.5<br>4.2.1.2.5<br>4.2.1.2.8                                                                         | Direct Address Index Bl Index B2 Relative Forward Indirect Address Indirect/Index Bl Indirect/Index B2 Relative Backward                      | 14<br>14<br>14<br>14<br>14<br>15 |

| 4.5.5.5<br>3.5.6.1<br>3.5.5                                                                                                                                     | Data Formats<br>Word Format<br>Byte Format                                                                                                    | 15<br>15<br>15                   |

| 3.2.3<br>3.2.3.1<br>4.2.3.2                                                                                                                                     | Internal Flags<br>Condition Bit<br>Adder Generate Bit                                                                                         | 16<br>16                         |

| 3.2.4<br>3.2.4.1<br>3.2.4.2<br>3.2.4.3                                                                                                                          | Instruction Tables Format 1: Hexadecimal Format 2: Hexadecimal Instruction Execution Times                                                    | 17<br>17<br>17<br>17             |

NO. 52410600 DATE 10/15/69 PAGE 3 REV. 01

COMPUTER DEVELOPMENT

#### CONTENTS {cont d}

|                                                          |                                                                                                                                                 | Page                       | No-         |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|

|                                                          |                                                                                                                                                 |                            |             |

| 1-2-5<br>1-2-5-1<br>1-2-5-2<br>1-2-5-3<br>1-2-5-4        | Instruction Descriptions Selective Stop Selective Set Bit t of A Selective Clear Bit t of A Selective Complement Bit t of A                     | 55<br>55<br>55<br>57       |             |

| 1.2.5.5<br>3.2.5.6<br>3.2.5.7<br>3.2.5.8                 | Count of Leading Zeroes in A; to Af<br>Shift A Right, t Places<br>Transfer A to Bl<br>Transfer A to B2                                          | 23<br>23<br>23<br>23       |             |

| 3-2-5-9<br>3-2-5-10<br>3-2-5-11<br>3-2-5-12              | Set Condition Equal: Internal Tests Set Condition Equal: Bit t of Channel s Selective Set Bit t of Channel s Selective Clear Bit t of Channel s | 24<br>24<br>25<br>25       |             |

| 3.2.5.13<br>3.2.5.14<br>3.2.5.15<br>3.2.5.16             | Input to A from Channel s<br>Set Channel s for Ones in A<br>Clear Channel s for Zeroes in A<br>Transfer A to Channel s                          | 26<br>26<br>27<br>27       |             |

| 3.2.5.17<br>3.2.5.18<br>3.2.5.19<br>3.2.5.20             | Add No Address<br>Subtract No Address<br>Exclusive Or No Address<br>Logical Product No Address                                                  | 28<br>28<br>28             |             |

| 3.2.5.21<br>3.2.5.22                                     | Test Index Bl No Address<br>Test Index B2 No Address                                                                                            | 5 '                        |             |

| 3-2-5-23<br>3-2-5-24<br>3-2-5-25<br>3-2-5-26<br>3-2-5-27 | Load A Complement No Address Load From {A} Enter A With Address Enter B] With Address Enter B2 With Address                                     | 25<br>25<br>26<br>30<br>30 | ]<br>]<br>] |

| 3.2.5.2 <b>8</b><br>3.2.5.29                             | Test Index Bl<br>Test Index B2                                                                                                                  | 31<br>31                   |             |

NO. DATE PAGE REV. 01 52410600 1**0/15/**69

COMPUTER DEVELOPMENT

|                                                                                     | CONTENTS                                                                                                                                          | {Cont'd}                    |     | Page No.                               |

|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|----------------------------------------|

| 3.2.5.32                                                                            | Load A<br>Load A Complement<br>Load Left-most Byte<br>Load Right-most Byte                                                                        |                             |     | 31<br>31<br>31                         |

| 3-2-5-34<br>3-2-5-35<br>3-2-5-36<br>3-2-5-37                                        | Add<br>Subtract<br>Exclusive Or<br>Logical Product                                                                                                |                             |     | 32<br>32<br>32                         |

| 3-2-5-38<br>3-2-5-39<br>3-2-5-40<br>3-2-5-41                                        |                                                                                                                                                   |                             | et. | 33<br>33<br>33                         |

| 3-2-5-42<br>3-2-5-43<br>3-2-5-44                                                    | Store Zeros                                                                                                                                       |                             |     | 33<br>33                               |

|                                                                                     | Jump Instructions<br>Unconditional Jump                                                                                                           |                             |     | 34<br>34                               |

| 3.2.5.45.4<br>3.2.5.45.4<br>3.2.5.45.5<br>3.2.5.45.6                                | A Zero Jump A Nonzero Jump A Positive Jump A Negative Jump Condition True Jump Condition False Jump                                               |                             |     | 34<br>34<br>34<br>34<br>34             |

| 3.2.5.46<br>3.2.5.47                                                                | Input Block Transfer<br>Output Block Transfer                                                                                                     |                             |     | 35<br>36                               |

| 3.2.6.1<br>3.2.6.1.1<br>3.2.6.1.2<br>3.2.6.1.3<br>3.2.6.2<br>3.2.6.3.1<br>3.2.6.3.2 | Storage Interface Storage Control Signals Access Command Write Command Master Clear Storage Address Storage Data Read Data Lines Write Data Lines |                             |     | 37<br>37<br>37<br>37<br>37<br>38<br>38 |

| 3 • 2 • 6 • 4<br>4 • 2 • 6 • 4 • 1<br>3 • 2 • 6 • 4 • 2<br>4 • 2 • 6 • 4 • 3        | Special Storage Controls<br>Crystal Input and Feedba<br>End of Access/Cycle Input<br>End of Access/Cycle Outp                                     | ack Controls<br>ut Controls |     | 39<br>39<br>39<br>39                   |

NO. 52410600 DATE 10/15/69 PAGE 5 REV.01

### COMPUTER DEVELOPMENT

### CONTENTS {Contrd}

| 3.2.7.1<br>3.2.7.1<br>3.2.7.1.1<br>3.2.7.1.2                                      | Normal Channel Interfaces Normal Output Channel Control Signals Set Channel Commands Clear Channel Commands                                                                                                              | 41<br>41<br>41                               |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 3.2.7.2<br>3.2.7.3<br>3.2.7.3.1<br>3.2.7.3.2                                      | Channel Select Signals<br>Normal Channel Data<br>Normal Input Channel Data<br>Normal Output Channel Data                                                                                                                 | 42<br>42<br>42<br>43                         |

| 3.2.8.1.1<br>3.2.8.1.1<br>3.2.8.1.2<br>3.2.8.1.3<br>3.2.8.1.4                     | Coupler Interface Controls to the Coupler Output Ready Input Request Parity Strobe Master Clear                                                                                                                          | 46<br>46<br>46<br>46<br>46                   |

| 3.2.8.2.3<br>3.2.8.2.3<br>3.2.8.2.3                                               | Controls from the Coupler Ready Reply Terminate                                                                                                                                                                          | 47<br>47<br>47<br>47                         |

| 3.2.8.3.1<br>3.2.8.3.2<br>3.2.8.4<br>3.2.9.1<br>3.2.9.1<br>3.2.9.1.2<br>3.2.9.1.3 | Coupler Data Interface Coupler Input Data Coupler Output Data Coupler Interface Data Rate Station Control Interface Pluggable Station Control Signals A Register Entry P Register Entry Adder Display P Register Display | 48<br>48<br>50<br>51<br>52<br>52<br>52<br>52 |

| 3.2.9.1.5<br>3.2.9.1.7<br>3.2.9.1.8<br>3.2.9.1.9<br>3.2.9.1.10<br>3.2.9.1.11      | Vt Designator Select Not Vt Designator Select                                                                                                                                                                            | 53<br>53<br>53<br>53<br>53<br>53<br>53       |

| 3.2.9.1.14<br>3.2.9.1.15                                                          | Breakpoint Instruction Select                                                                                                                                                                                            | 5 4<br>54<br>5L                              |

NO. 52410600 DATE 10/15/69 PAGE 6 **REV.** 01

#### COMPUTER DEVELOPMENT -

|                                                                    | COMPUTER DEVELOPMENT -                                                                                        |                                  |

|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                    | CONTENTS {CONT'D.}                                                                                            | Page No.                         |

| 3-2-9-1-17<br>3-2-9-1-18<br>3-2-9-1-19                             | Parity Error<br>Parity Error Clear<br>Stop on Parity Error Select                                             | 55<br>55<br>55                   |

| 05.1.P.5.E<br>15.1.P.5.E<br>55.1.P.5.E                             | Go Switch Inputs<br>Stop Switch<br>Master Clear <b>Sw</b> itch                                                | 56<br>56<br>56                   |

| 3.2.9.1.23<br>3.2.9.1.24<br>3.2.9.1.25<br>3.2.9.1.26               | Instruction Step<br>Cycle Step<br>Enter Mode<br>Sweep Mode                                                    | 57<br>57<br>57<br>57             |

| 3.2.9.1.27<br>3.2.9.1.28<br>3.2.9.1.29                             | Selective Stop<br>Clear Channel<br>Timing Margins                                                             | 58<br>58<br>58                   |

| 3.2.9.1.30<br>3.2.9.1.31<br>3.2.9.1.32<br>3.2.9.1.33<br>3.2.9.1.34 | Not Running Status<br>RNI Status<br>RADR Status<br>ROP Status<br>STO Status<br>Jump Condition Met Status      | 59<br>59<br>59<br>59<br>59<br>59 |

| 3.2.9.2<br>3.2.9.2.1<br>3.2.9.2.2<br>3.2.9.2.3                     | Non-Pluggable Station Control Signals<br>Not Go<br>Not Stop<br>Not Master Clear                               | PO<br>PO<br>PO                   |

| 3.2.9.2.4<br>3.2.9.2.5<br>3.2.9.2.6<br>3.2.9.2.7                   | Enable Storage Write<br>Not Force Function<br>Force Function Select<br>End of Block Transfer Status           | PS<br>PJ<br>PO                   |

| 3.3.1.2<br>3.3.1.2                                                 | Physical Requirements<br>Backpanel/50-PAKs<br>Materials/workmanship<br>Interchangeability                     | P3<br>P3<br>P3                   |

| 3.3.2<br>3.3.2.1<br>3.3.2.2<br>3.3.2.3                             | Interfaces<br>Storage Interface<br>Coupler Interface<br>Normal Channel Interface<br>Station Control Interface | 6 4<br>6 4<br>6 4<br>6 4         |

| 3.4<br>3.5<br>3.6<br>3.7<br>3.8                                    | Power<br>Environmental Requirements<br>MTBF<br>MTTR<br>Useful Life                                            | 65<br>65<br>65<br>65             |

| 4.0                                                                | TEST REQUIREMENTS                                                                                             | PP                               |

| 5 • D                                                              | PREPARATION FOR DELIVERY                                                                                      | 66 PRINTED IN U.S.A.             |

|                                                                    |                                                                                                               |                                  |

NO. 52410600 DATE 10/15/69 PAGE 7 REV.01

#### COMPUTER DEVELOPMENT

|                                                                  | _          |

|------------------------------------------------------------------|------------|

| CONTENTS {CONT'D.}                                               | Page No.   |

| Table 1: Hexadecimal Codes for Format 1 Instructions             | 18         |

| Table 2: Hexadecimal Codes for Format 2 Instructions             | 19         |

| Table 3: Instruction Times in Number of Storage Reference Cycles | - 20       |

| Table 4: Storage Interface POL                                   | 67         |

| Table 5: Storage Interface PD2                                   | P8         |

| Table 5: Coupler Interface, Output                               | 69         |

| Table 6A: Coupler Interface, Input                               | 70         |

| Table 7: Normal Channel Interface, Input □→7                     | 71         |

| Table 7A: Normal Channel Interface, Output $\square 	o 7$        | 72         |

| Table 7B: Normal Channel Interface, Output □→7, Daisy-Chained    | 73         |

| Table 8: Normal Channel Interface, Input 8->F                    | 74         |

| Table 8A: Normal Channel Interface, Output 8-                    | 75         |

| Table 9: Station Control Interface, JOL                          | 7 <b>L</b> |

| Table 10: Station Control Interface, JO2                         | 77         |

| Table 11: Station Control Interface, JO3                         | 78         |

| Table 12: Station Control Interface, JO4                         | 79         |

| Table 13: Non-Pluggable Station Control Interface                | 80         |

| Table 14: Non-Pluggable Storage Interface Signals                | 80         |

|                                                                  |            |

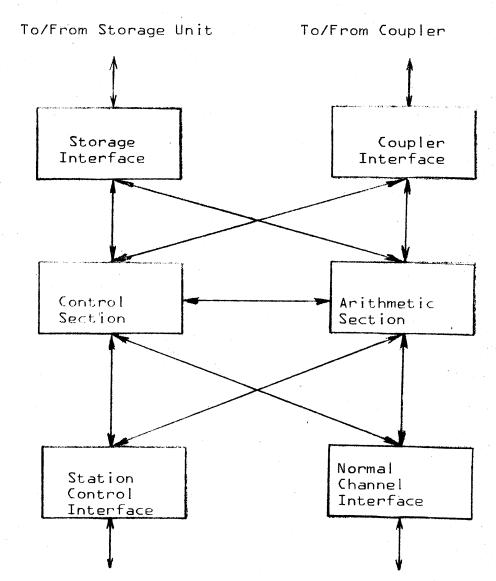

| Figure 1: Buffer Controller Block Diagram                        | 9          |

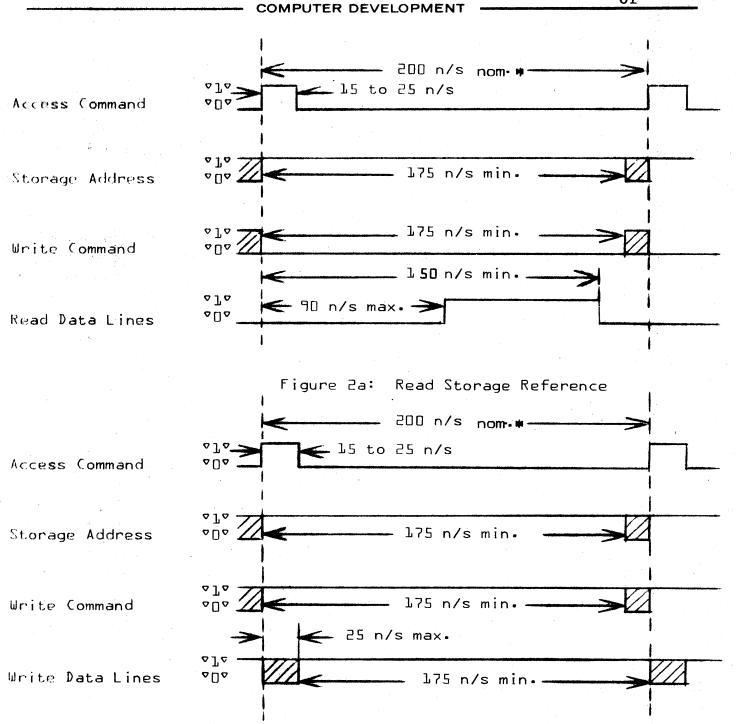

| Figures 2a and 2b: Storage Reference Timing                      | 40         |

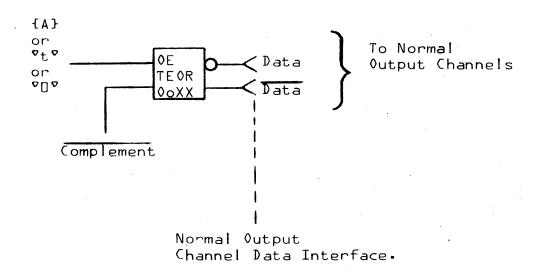

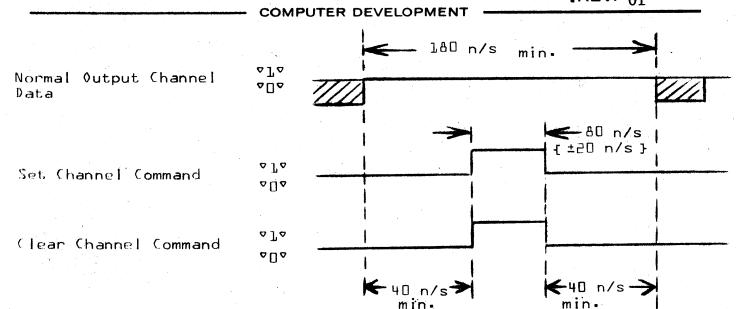

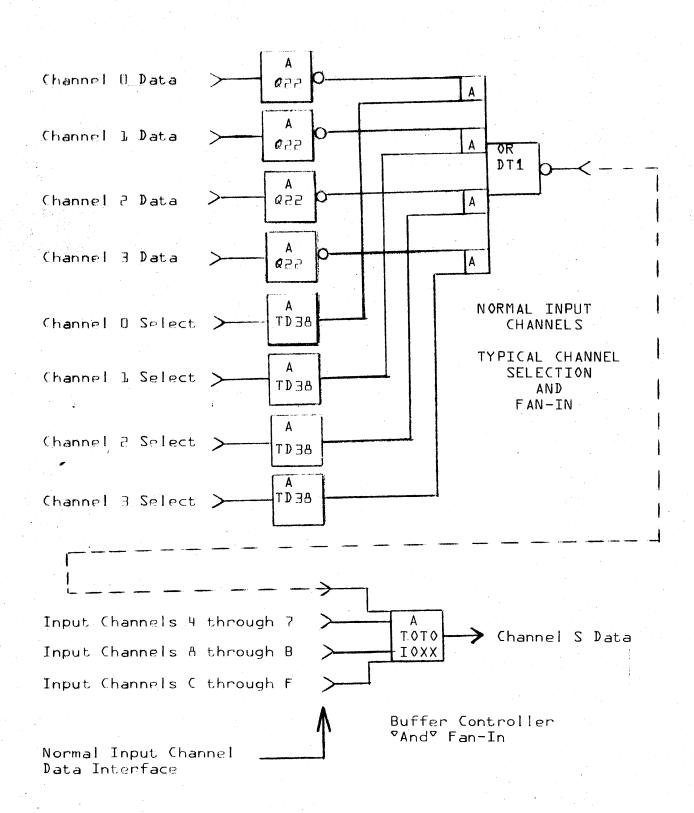

| Figures 3a and 3b: Normal Channel Timing                         | 44.        |

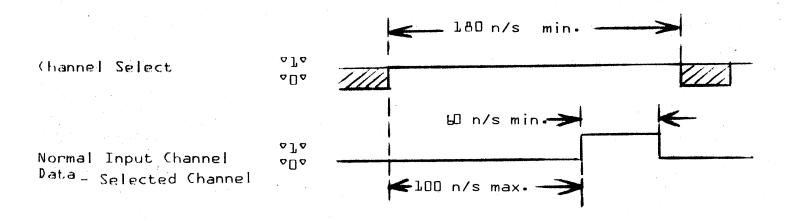

| Figure 4: Typical Normal Input Channel Configuration             | 45 .       |

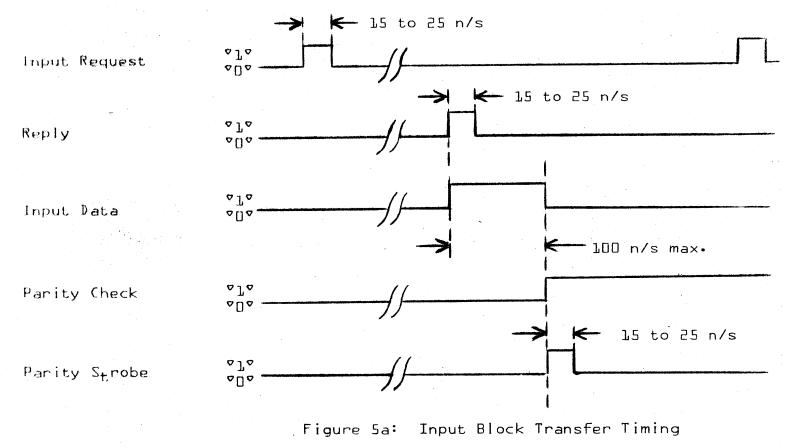

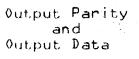

| Figures 5a and 5b: Coupler Interface Timing                      | 49         |

| Figure 5: Buffer Controller Backpanel                            | 81         |

| figure 7: A Row Ground Assignments                               | 82         |

| Figure 8: B Row Ground Assignments                               | 83         |

|                                                                  |            |

NO. 52410600 DATE10/15/69 PAGEA REV. 01

COMPUTER DEVELOPMENT

#### 1.- II SCOPE

This specification describes the Buffer Controller which serves as the data processing and/or master control element in a peripheral equipment and/or peripheral processing configuration.

Although the properties of the Buffer Controller are described in detail, an equally detailed description of their implementation in a peripheral environment, {Station}, is not within the scope of this specification.

#### applicable Documents

Engineering Standard 1.30.011

Engr. Spec. 20278200, High Speed 4096 word, 18-bit Memory

Engr. Spec. 52410700, Buffer (ontroller Normal Channels

Engr. Spec. 52410800, Buffer Controller Block Transfer Coupler

Engr. Spec. 11834700, TCS Gate - TOTO

Engr. Spec. 58018900, Buffer Controller Maintenance Console

Engr. Spec. 52319800, 1.1 u/s, 4096 word, 18 Bit Memory

Engr. Spec. 20277200, Three-layer Printed Circuit Board

Engr. Spec. 11828700, General Quality Spec. for ICs.

Engr. Spec. 11845900, Workmanship Spec. for CDC Mfg. ICs.

Engr. Spec. 52302000, Performance Spec for Connector Plates

CDC Spec. 10120300, General Quality Requirements

#### H-D PERFORMANCE REQUIREMENTS

#### 3.1 General Description

The Buffer Controller is an internally programmed, parallel mode, digital device intended to control a wide variety of peripheral devices. The Buffer Controller consists of six main sections as shown in the Block Diagram (Figure 1, page 9).

In order to achieve its intended functions as a programmable device, the Buffer Controller {Equipment FR101} requires as a minimal addition, a Storage Unit which meets the interface requirements as described in Section 3.2.6. Although the Buffer Controller described by this Specification is actually a processor only, with a Storage Unit established as an absolute requirement, the term Buffer Controller is used in place of Buffer Controller Processor.

NO. 52410600 DATE 10/15/69 PAGE 9 REV. 01

COMPUTER DEVELOPMENT

To/From Station Controls

To/From Normal Channels

Buffer Controller Block Diagram

FIGURE 1

NO. 52410600 DATE 10/15/69 PAGE 10

**REV.** 01

COMPUTER DEVELOPMENT

#### 3.1.1 Control Section

The Control Section processes all instructions. In addition to sequencing arithmetic operations, this section issues timing and control signals to the Storage, Normal Channel, Coupler, and Station Control Interfaces.

The 16-bit Program Address Register is contained within this section and is referred to as the P Register throughout the remainder of this specification. The P Register is incremented within the Arithmetic section in 2's complement mode.

#### 3.1.2 Arithmetic Section

The Arithmetic Section performs all arithmetic operations in 2's complement mode including those which form storage addresses. In addition to a 16-bit adder, this section contains the 16-bit Accumulator Register and two 16-bit Index Registers. These directly addressable registers are referred to as A, B1 and B2, respectively, throughout the remainder of this specification. All logical operations are performed within the Arithmetic Section.

The 16-bit adder includes a 17th output bit used to record the generation of a carry out of the adder during arithmetic operations involving the A Register. See section 3.2.3.2.

A parallel Shift Network provides the capability of right-shifting the contents of the A Register a maximum of 15 binary positions under the control of a 4-bit Shift Count. The Shift Network and Shift Count are referred to as SN and SC, respectively, throughout the remainder of this specification.

Note: Section 3.2 contains detailed information on the characteristics of both the Control and Arithmetic Sections.

NO.52410600 DATE10/15/69 PAGE 11 REV. 01

- COMPUTER DEVELOPMENT

#### 1.1.3 Storage Interface

Although the Buffer Controller requires a Storage unit in order to achieve its intended functions as a programmable controller. Storage is treated as a separate equipment and is described in Engineering Specification 20278200.

Critical properties of the Storage unit which can be generally described as requirements at the Storage Interface of the Buffer Controller include:

200 n/s cycle, 90 n/s access times, {Optimum}. L8-bit read and write date interfaces L6-bit {maximum} address interface

Note: Throughout this specification, descriptions of the Storage Interface are based on a 200 n/s storage cycle time since the design of the Buffer Controller must be optimized for 200 n/s cycles.

Section 3.2.6 provides detailed information on the Storage Interface.

#### 3.1.4 Normal Channel Interface

The Normal Channel Interface provides the Buffer Controller with the means for utilizing an input/output facility with programmable "Ready/Resume" controls. As a result, the Normal Channel Interface is oriented toward a one-for-one correspondence between Buffer Controller instructions and input/output transfers through the Normal Channel Interface. The general properties of this interface include the ability to uniquely select one of sixteen Normal Input Channels; and the ability to uniquely select one of sixteen Normal Output Channels for "ones" and/or "zeros" transfer. Normal Channel data transfers involve the A Register for 16-bit parallel operations or an instruction designated bit for bit addressable operations.

Section 3.2.7 provides detailed information on the Normal Channel Interface.

The description of DTL Normal Channels designed for attachment to the Buffer Controller Normal Channel Interface can be found in Engineering Specification 52410700.

NO. 52410600 DATE 10/15 /69 PAGE 12 REV. 01

COMPUTER DEVELOPMENT

#### J.1.5 Coupler Interface

The Coupler Interface provides the Buffer Controller with the means for utilizing an input/output facility with hardware \*Ready/Resume\* controls. As a result, I/O operations are oriented toward consecutive data transfers between the Buffer Controller and a Coupler via the Coupler Interface.

During Block Transfer Instructions the Buffer Controller references consecutive storage locations on the basis of external {Coupler} demands. The A Register is utilized for word count control and the transfer of data is terminated when the contents of the A Register become zero or upon the occurrence of an external terminate signal.

Section 3.2.8 provides detailed information on the Coupler Interface.

The description of a Coupler designed for attachment to the Buffer Controller Block Transfer Channel can be found in Engineering Specification 52410800.

#### 3.1.6 Station Control Interface

The Station Control Interface provides facilities for controlling and monitoring Buffer Controller Operations. Certain input controls on this interface, such as °GO°, °STOP°, and °Master Clear°, are required for basic operational control of the Buffer Controller. Other control inputs and status outputs on this interface, such as Breakpoint, Register Entry, Register Readout, Instruction Step, Timing Margins, etc., are facilities which may be externally exercised for hardware/software checkout and/or maintenance purposes.

Section 3.2.9 provides detailed information on the Station Control Interface.

NO. 5243,0600 DATE 10/15/69 PAGE 13 REV 01

COMPUTER DEVELOPMENT

- Performance Characteristics 3.2

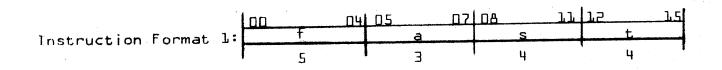

- Instruction Formats 3.0.1

- Instruction Format 1 {No Address} 3.2.1.1

| nn 04 | 05 07 | 08 11 | 12 15 |

|-------|-------|-------|-------|

| f     | а     | S     | t     |

| 5     | . 3   | ц     | 4     |

- f, function code

- a, sub-function code

- s. channel designator, instruction condition designator, or left-most 4 bits of an 8-bit immediate operand

- t. bit designator, right-shift count, or right-most 4 bits of an A-bit immediate operand

Format 1 instructions are considered to be No Address mode. No execution address is associated with these instructions since they perform control operations. contain an immediate operand, or perform operations involving only directly addressable registers.

The single exception to the preceding definition is the \*LOAD from [A] instruction in which the A Register initially contains the execution address. See section 3.2.5.24.

Instruction Format 2 {Single Address} 3.2.1.2

| loo |   | 04 | 05 | 06 | 07       | OA | 15 |

|-----|---|----|----|----|----------|----|----|

|     | f |    | i  | r  | `        |    | m  |

|     | 5 |    | 1  | ē  | <u> </u> |    | В  |

- f, function code

- i and r. addressing mode designators

- m, base address

Addressing modes for Format 2 instructions are described with respect to the formation of an execution address. M. Parentheses are used to indicate of the contents of a register or storage location. Where the right-most & bits of an instruction, m, are used directly or arithmetically to form a 16-bit address, zeros are appendended to m in the left-most bit positions, OO through O7. All address arithmetic is performed 2's complement mode and does not alter the state of the Adder Generate Bit.

NO. 52410600 DATE 10/15/69 PAGE 14 REV. 01

COMPUTER DEVELOPMENT

1.0.1.2.1 Direct Address: i = 0. r = 002

A direct address is formed by using only the right-most & bits of the instruction word. This addressing mode provides direct access to the first 25610 storage locations.

M = m

3.0.1.2.2 Index Bl: i = 0. r = 012

An Index Bl modified address is formed by adding the contents of the Bl Register to the right-most & bits of the instruction word.

$M = \{B\}\} + m$

3.2.1.2.3 Index B2: i = 0, r = 102

An Index B2 modified address is formed by adding the contents of the B2 Register to the right-most & bits of the instruction word.

$M = \{B2\} + m$

3.2.1.2.4 Relative Forward: i = 0, r = 112

A Relative Forward address is formed by adding the contents of the P Register to the right-most & bits of the instruction word.

$M = \{P\} + m$

3.2.1.2.5 Indirect Address: i = 1, r = 002

An Indirect address is formed by reading the contents of the storage location designated by the right-most & bits of the instruction word.

$M = \{m\}$

3.2.1.2.6 Indirect/Index Bl: i = 1. r = 012

An Indirect/Index Bl modified address is formed by reading the contents of the storage location designated by the right-most 8 bits of the instruction word and adding the contents of the Bl Register.

$M = \{m\} + \{B\}\}$

NO. 52410600 DATE 10/15/69 PAGE REV. 01

COMPUTER DEVELOPMENT

3.2.1.2.7 Indirect/Index B2:

i = 1, r = 102

An Indirect/Index B2 modified address is formed by reading the contents of the storage location designated by the right-most A bits of the instruction word and adding the contents of the B2 Register.

$M = \{m\} + \{B2\}$

3.2.1.2.8 Relative Backward;

i = 1, r = 11<sub>p</sub>

A Relative Backward address is formed by subtracting the right-most & bits of the instruction word from the contents of the P Register.

$M = \{P\} - m$

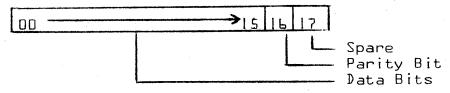

3.2.2 Data Formats

Data within the Storage and Arithmetic Sections of the Buffer Controller may be treated as 16-bit words or 8-bit bytes.

3.2.2.1 Word Format

Registers and Storage locations contain 16-bit words with the following bit designations:

| laa | υī | 02 | 03 | 04 | 05 | 0 <b>b</b> | 07 | 08 | 09 | 10 | 11 | 75 | 13 | 14 | 15 |

|-----|----|----|----|----|----|------------|----|----|----|----|----|----|----|----|----|

|     | _  |    |    |    |    |            |    |    |    |    |    |    |    |    |    |

Bit OD is the left-most bit. For signed quantities, the vone state denotes a negative 2's complement quantity; the vzero state denotes a positive quantity.

Bit 15 is the right-most bit.

3.2.2.2 Byte Format

Registers and Storage locations contain two 8-bit bytes within each 16-bit word with the following designations:

00 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 Left-most Byte Right-most Byte

The left-most byte occupies the left-most bit positions. On through O7.

The right-most byte occupies the right-most bit positions,  $\square A$  through  $\square S$ .

NO. 52410600 DATE 10/15 /69 PAGE 16 **REV.** 01

Page

COMPUTER DEVELOPMENT -

Internal Flags 3.2.3

Condition Bit 7.2.3.1

> The Condition Bit is an internal flag that may be altered and sensed by program means. In the set or Yone state this flag is referred to as Condition True. In the clear or "zero" state this flag is referred to as Condition False. The following instructions are capable of altering the state of the Condition Bit:

| Instruction                                                                 | Page     |

|-----------------------------------------------------------------------------|----------|

| Set Condition Equal: Internal Tests Set Condition Equal: Bit t of Channel s | 24<br>24 |

| Test Index Bl No Address<br>Test Index B2 No Address                        | 29<br>29 |

| Test Index Bl<br>Test Index B2                                              | 37<br>31 |

| Input Block Transfer<br>Output Block Transfer                               | 3P       |

#### Adder Generate Bit 3.2.3.2

The Adder Generate Bit constitutes the 17th output bit of the adder and reflects the generation of an end-off carry following operand arithmetic for the following instructions:

| Page     |

|----------|

| 28<br>28 |

| 32<br>32 |

| 33<br>33 |

|          |

The Adder Generate Bit is not intended to convey any information concerning what is conventionally referred to as Arithmetic Overflow.

During multiple precision arithmetic operations the Adder Generate Bit provides an indication of Register Overflow by its presence when adding like-signed operands and by its absence when subtracting unlike-signed operands.

NO. 52410600 DATE 10/15/69 PAGE 17 REV 01

COMPUTER DEVELOPMENT

Instruction Tables 7.7.4

Format 1: Hexadecimal 7.2.4.1

> Table 1 on page 14 provides the hexadecimal codes for the  $\Pf^{\nabla}$  and  $\Pa^{\nabla}$  portions of all Format 1 instructions. In addition, the  $\Ps^{\nabla}$  and  $\Pt^{\nabla}$  fields are designated by an X when used and by a O when unused. Explicit information with respect to these fields is contained within the detailed instruction descriptions in Section 3.2.5.

Format 2: Hexadecimal 3.2.4.2

> Table 2 on page 19 provides the hexadecimal codes for the ofo, vio and oro portions of all Format 2 instructions. Designation of the address field, omo, has been omitted from the table since its participation in address formation has been previously described in Section 3.2.1.2.

Instruction Execution Times 3.2.4.3

> Table 3 on page 20 provides instruction execution times in number of storage reference cycles required for each instruction. The storage unit described in Engineering Specification 20278200 provides the Buffer Controller with a storage reference cycle of 200 n/s. 1±.005%.

The following characteristics indicated by Table 3 deserve mention:

- All Format 1 instructions require a single storage reference cycle with the exception of Load from {A}♥.

- Indexing of an address does not impose a penalty 2. on instruction execution time.

- The execution time for Block Transfer instructions 3. is dependent upon the number of transfers to be performed as well as the time required for each transfer.

In Table 3:  $k = n\{1+c\}$

Where:

n = number of transfers,

1 = one storage reference

cycle.

- c = a constant determined by the characteristics of the Coupler attached to the Block Transfer Channel.

- ч. Indirect Conditional Jumps require only a single storage reference cycle, {RNI}, when the jump condition is not satisfied.

NO. 52410600 DATE 10/15 /69 PAGE 18 REV. 01

COMPUTER DEVELOPMENT

|                                                                                                                                                 |                      | 5                     | , ' <i>y</i> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------|--------------|

| INSTRUCTION DESCRIPTION                                                                                                                         | - ( )                | 200                   |              |

| Selective Stop Selective Set Bit t of A Selective Clear Bit t of A Selective Complement Bit t of A                                              | 03<br>05<br>01<br>00 | 0X<br>0X<br>0X        |              |

| Count of Leading Zeroes in A; to Af Shift A Right, t Places Transfer A to Bl: {A} + °s° °t° → Bl Transfer A to B2: {A} + °s° °t° → B2           | 04<br>05<br>06<br>07 | 00<br>XX<br>XX<br>XX  |              |

| Set Condition Equal: Internal Tests Set Condition Equal: Bit t of Channel s Selective Set Bit t of Channel s Selective Clear Bit t of Channel s | 08<br>09<br>0A<br>0B | XX<br>XX<br>XX<br>XX  |              |

| Input to A From Channel s Set Channel s from A Clear Channel s from A Transfer A to Channel s                                                   | 0C<br>0D<br>0E<br>0F | X D<br>XX<br>XX<br>XX |              |

| Add No Address Subtract No Address Exclusive or No Address Logical Product No Address                                                           | 73<br>75<br>77<br>70 | XX<br>XX<br>XX        |              |

| Test Index Bl No Address Test Index B2 No Address Load A Complement No Address Load From {A}                                                    | 14<br>15<br>16<br>17 | XX<br>XX<br>XX        |              |

Table 1: Hexadecimal Codes for Format 1 Instructions

NO. 52410600 DATE 10/15/69 PAGE19 REV. 01

COMPUTER DEVELOPMENT

Instruction Format 2:

| - 1 | nn <b>0</b> 4 | 05 | 06 07 | O8 15 |   |

|-----|---------------|----|-------|-------|---|

|     | f f           | i  | r     | m     | l |

|     | 5             | 1  | 2     | a a   | l |

|                                             |                |                | / ,                 | / ,                 |                | / 30           |            | e <sup>+</sup>                                    |

|---------------------------------------------|----------------|----------------|---------------------|---------------------|----------------|----------------|------------|---------------------------------------------------|

|                                             | ,              | 12000          | ( \s\)              |                     | 20 /           |                |            | 15 8 15 20 15 15 15 15 15 15 15 15 15 15 15 15 15 |

| INSTRUCTION DESCRIPTION                     |                |                | 1.80 <sup>+</sup> / | , se <sup>+</sup> / |                |                | 120, /     |                                                   |

| See Table 1                                 | 00<br>08<br>10 | 01<br>09<br>11 | 75<br>0V<br>05      | 08<br>13            | 04<br>00<br>14 | 05<br>0D<br>15 | 7P<br>OE   | 07<br>0F<br>17                                    |

| Enter A with Address                        | 18             | 19             | ЪΑ                  | 1B                  | 1C             | ],D            | <u>ι</u> Ε | <u>1</u> F                                        |

| Enter Bl with Address Enter B2 with Address | 30             | 21             | 22                  | 23                  | 24             | 25             | 3P         | 27                                                |

|                                             | 28             | 21             | 2A                  | 2B                  | 2C             | 2 <b>D</b>     | 5E         | 2F                                                |

|                                             | 20             | 21             | 52                  | 33                  | 34             | 35             | 5P         | 37                                                |

| Test Index Bl<br>Test Index B2              | 38             | 39             | 3A                  | 3B                  | 3.0            | 3D             | 3E         | 3F                                                |

| Load A                                      | 40             | 4]             | 42                  | 43                  | 44             | 45             | 46         | 47                                                |

| Load A Complement                           | 48             | 49             | 4A                  | 4B                  | 4C             | 4D             | 4E         | 4F                                                |

| Load Left-most Byte                         | 50             | 51             | 52                  | 53                  | 54             | 55             | 56         | 57                                                |

| Load Right-most Byte                        | 58             | 59             | 5 A                 | 5B                  | 5C             | 5D             | 5E         | 5F                                                |

| Add                                         | P8             | 61             | P V                 | 63                  | Ь4             | 65             | PE         | 67                                                |

| Subtract                                    |                | 69             | P S                 | 68                  | ЬС             | 6D             | PE         | 6F                                                |

| Exclusive Or                                | 70             | 71             | 72                  | 73                  | 74             | 75             | 76         | 77                                                |

| Logical Product                             | 78             | 79             | 7A                  | 7B                  | 7C             | 7D             | 7E         | 7F                                                |

| Replace Add                                 | 88             | 81             | 82                  | 83                  | 84             | 85             | &E         | 87                                                |

| Replace Add One                             | 88             | 89             | A8                  | 8B                  | 80             | 8D             | &E         | 8F                                                |

| Replace Left-most Byte                      | 90             | 9 <u>1</u>     | SP                  | 93                  | 94             | 95             | 96         | 97                                                |

| Replace Right-most Byte                     | 98             | 99             | AP                  | 98                  | 90             | 9D             | 9E         | 9F                                                |

| Store                                       | AD             | A L            | AA                  | A3                  | A4             | A5             | AE         | A7                                                |

| Store Zeroes                                | AB             | PA             | AA                  | AB                  | AC             | AD             | AE         | AF                                                |

| Destructive Load                            | BD             | B1             | B2                  | B3                  | B4             | B5             | BE         | B7                                                |

| Unconditional Jump                          | BB             | B9             | BA                  | BB                  | BC             | BD             | BE         | BF                                                |

| A Zero Jump<br>A Nonzero Jump               | C B            | C1<br>C9       | CA                  | CB                  | C4<br>CC       | C5<br>CD       | CE         | C7<br>CF                                          |

| A Positive Jump                             | DO             | D L            | D A                 | DB                  | D4             | D5             | DE         | D7                                                |

| A Negative Jump                             | DA             | D P            |                     | D3                  | DC             | DD             | DE         | DF                                                |

| Condition True Jump                         | E0             | E1             | E A                 | E3                  | E4             | E5             | EE         | E7                                                |

| Condition False Jump                        | E8             | E9             |                     | EB                  | EC             | ED             | EE         | EF                                                |

| Input Block Transfer                        | FO             | F]             | F2                  | F3                  | F4             | F5             | FE         | F7                                                |

| Output Block Transfer                       | FA             | F9             | FA                  | FB                  | FC             | FD             | FE         | FF                                                |

Table 2: Hexadecimal Codes for Format 2 Instructions

NO. 52410600 DATE 10/15/69 PAGE 20

REV. 01

COMPUTER DEVELOPMENT

|                                                                                                                                                                                                                                  |          |                |          |               |                   |                                        |             | -/       |                                          |    |       |   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------|----------|---------------|-------------------|----------------------------------------|-------------|----------|------------------------------------------|----|-------|---|

|                                                                                                                                                                                                                                  |          |                | -        | /             | / .               | / '                                    |             |          |                                          |    |       |   |

|                                                                                                                                                                                                                                  |          |                |          |               |                   |                                        | ره/         |          | 10 10 10 10 10 10 10 10 10 10 10 10 10 1 | &V | Wat C |   |

|                                                                                                                                                                                                                                  |          | ,              | / /      | / ,           | / ,               | C. tys                                 | /           | , de     | not the                                  |    |       |   |

| en de la companya de<br>La companya de la co |          |                |          | . / .         |                   |                                        | ٧/ رخ       | .\\\\;   |                                          | r/ |       |   |

|                                                                                                                                                                                                                                  |          | 1 1 2 X        | idet .   | **            |                   | 87                                     | Sit?        | 8156     |                                          |    |       |   |

| THE TANK BESCHTETAN                                                                                                                                                                                                              |          | \$ <b>`</b> /^ | S/\      | 1.80 ×        | Fe/               | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |             |          | */                                       |    |       | • |

| INSTRUCTION DESCRIPTION                                                                                                                                                                                                          |          |                |          |               |                   |                                        |             |          | •                                        |    |       |   |

| See Table 1                                                                                                                                                                                                                      | 1        | 1              | 1        | <u>l</u><br>1 | 1                 | <u>l</u>                               | 1           |          |                                          |    |       |   |

|                                                                                                                                                                                                                                  | <u>1</u> | 1 1            | <u>l</u> | 1             | 1 1               | 7                                      | 1 1         | 5⋈<br>7  |                                          |    |       |   |

| Enter A with Address                                                                                                                                                                                                             | 1        | l l            | J.       | l l           | 2                 | 2                                      | 2           | l l      |                                          |    |       |   |

| Enter Bl with Address                                                                                                                                                                                                            | ľ        | ľ              | J.       | l l           | 5                 | 2                                      | 5           | 1        |                                          |    |       |   |

| Enter B2 with Address Test Index B1                                                                                                                                                                                              | 5<br>7   | <u>1</u>       | <u> </u> | <u>1</u>      | 3                 | 3                                      | 3           | <u> </u> |                                          |    |       |   |

| Test Index 82                                                                                                                                                                                                                    | 5        | 5              | 2        | 5             | 3                 | 3                                      | 3           | ē        |                                          |    |       |   |

| Load A                                                                                                                                                                                                                           | 5        | 5              | 5        | 2             | 3                 | 3                                      | 3           | 2        |                                          |    |       |   |

| Load A Complement                                                                                                                                                                                                                | 2        | 5              | 2        | 2             | 3                 | 3                                      | 3           |          | •                                        |    |       |   |

| Load Left-most Byte<br>Load Right-most Byte                                                                                                                                                                                      | 5        | ט ט            | 5        | ח ח           | ш<br>П            | ש ש                                    | ы<br>Б      | ص<br>ح   |                                          |    |       |   |

|                                                                                                                                                                                                                                  | 5        | 5              | 5        | 2             | 3                 | 3                                      | 3           | 2        |                                          |    |       |   |

| Add<br>Subtract                                                                                                                                                                                                                  | 5        | ם ט            | 5        | 2             | ח                 | ח ר                                    | 3           | 2        |                                          |    |       |   |

| Exclusive Or                                                                                                                                                                                                                     | 5        | 5              | 5        | 5             | 3                 | 3                                      | 3           | 5        |                                          |    |       |   |

| Logical Product                                                                                                                                                                                                                  | 2        | 2              | 2        | 2             | 3                 | 3                                      | 3           | 2        |                                          |    |       |   |

| Replace Add                                                                                                                                                                                                                      | 3<br>3   | m<br>m         | 3        | <u>.</u>      | 4                 | 4                                      | 4           | חח       |                                          |    |       |   |

| Replace Add One Replace Left-most Byte                                                                                                                                                                                           | 3        | 3              | 3        | 3             | 4                 | 4                                      | 4           | 3        |                                          |    |       |   |

| Replace Right-most byte                                                                                                                                                                                                          | 3        | 3              | 3        | 3             | 4                 | 4                                      | 4           | 3        | •                                        |    |       | • |

| Store                                                                                                                                                                                                                            | 2        | 2              | 5        | 2             | 3                 | 3                                      | 3           | 2        |                                          |    |       |   |

| Store Zeroes                                                                                                                                                                                                                     | 3        | 3              | 3        | 2             | 3                 | 3                                      | 3           | 3        |                                          | ,  |       |   |

| Destructive Load Unconditional Jump                                                                                                                                                                                              | ī        | ī              | ī        | ī             | ė                 | ż                                      | 2           | ī        |                                          |    |       |   |

| A Zero Jump                                                                                                                                                                                                                      | 1        | 1              | 1        | l.            | .—                |                                        | 5 M M       | 1        | ŀ                                        |    |       |   |

| A Nonzero Jump                                                                                                                                                                                                                   | 1        | 1              | 1        | 1             |                   |                                        | <b>5</b> MM |          | ł                                        |    |       |   |

| A Positive Jump<br>A Negative Jump                                                                                                                                                                                               | 7        | 1              | 7        | 7 7           | 5 m m             | l                                      | ı           |          |                                          |    |       |   |

| Condition True Jump                                                                                                                                                                                                              | ı        | 1              | ı        | 1             | Бим               | БММ                                    | Бии         | l.       | 1                                        |    |       |   |

| Condition False Jump                                                                                                                                                                                                             | 11       | 1              | 1        | l l           |                   |                                        | SMM         | 1        |                                          |    |       |   |

| Input Block Transfer<br>Output Block Transfer                                                                                                                                                                                    |          |                |          |               | 2+k<br><b>2+k</b> |                                        |             |          |                                          |    |       | • |

| vutput block iransier                                                                                                                                                                                                            | 1 HTK    | 1 JTK          | TALK     | 1111          | LETK              | LETK                                   | LLTK        | 17,6     | 1                                        |    |       |   |

<sup>■</sup> Load from {A}

Table 3: Instruction Times in Number of Storage Reference Cycles

k is defined in 3.2.4.3

WM Only 1 cycle is required for these instructions when the jump condition is not satisfied.

NO. 5,49,06.00 DATE 10/15/69 PAGE 21 REV. 01

COMPUTER DEVELOPMENT

#### 3.2.5 Instruction Descriptions

Each detailed instruction description begins with a heading that includes the instruction name and the associated hexadecimal code or range of codes.

The instruction descriptions make extensive use of abbreviations that have been previously defined in the preceding sections of this specification. In addition, the subscripts i and f are used to denote finitial and final, respectively, and refer to the contents of registers or storage locations.

Instructions which perform Input/Output are described to the extent that the Normal Channel and Coupler Interfaces may be meaningfully defined in sections 3.2.7 and 3.2.8, respectively. More precise information regarding Normal Channel and Coupler characteristics must be obtained from the appropriate Reference Documents listed in section 2.0.

Instructions which serve no purpose other than to increment the {P} by one are referred to as resulting in no operation.

Instruction words in which bit positions are unused, must have those bits in the zero state. Where unused bits in an instruction word are in the one state, the results of the instruction are undefined. As previous stated, each instruction heading provides the defined decimal code or range of codes.

NOTE: In the case of the Selective Stop Instruction, {DDXX} described in Section 3.2.5.1, since the °s° and °t° fields are unused to the extent that they do not participate in the execution of this instruction, they may be non-zero and are defined as having no effect. Subsequently these fields may be used in this instruction for identification, temporary storage or other program purposes.

NO. 52910600 DATE10/15/69 PAGE 22 REV.01

COMPUTER DEVELOPMENT

### 1.2.5.1 Selective Stop OO XX

The execution of this instruction is dependent on the state of the  $\P NOP-DDP$  signal, a Selective Stop control input on the Station Control Interface defined in Section 3.2.9.

With the "NOP-DD" signal equal to a "one" this instruction results in no operation.

With the "NOP-DD" signal equal to a "zero" this instruction results in an immediate halt of program execution.

Once halted Buffer Controller program execution may be resumed, with the reading of the next instruction at P+1, through the use of additional control input facilities on the Station Control Interface. See section 3.2.9.

### 3.2.5.2 Selective Set Bit t of A Ol OX

This instruction unconditionally sets bit t of A, where the 4-bit designator t specifies one of the sixteen bit positions in A. The remaining fifteen bits of A are left unchanged.

If bit t of A; was already in the set state, then the instruction effectively results in no operation.

### J.2.5.3. Selective Clear Bit t of A D2 DX

This instruction unconditionally clears bit t of A, where the 4-bit designator t specifies one of the 16-bit positions in A. The remaining fifteen bits of A are left unchanged.

If bit t of A; was already in the clear state, then the instruction effectively results in no operation.

### 3.0.5.4 Selective Complement Bit t of A DB DX

This instruction complements bit t of A. where the 4-bit designator t specifies one of the sixteen bit positions in A. The remaining fifteen bits of A are left unchanged.

The complement operation is performed so that: When bit t of  $A_i$  is set, bit t of  $A_f$  is clear; When bit t of  $A_i$  is clear, bit t of  $A_f$  is set.

NO. 52410600 DATE 10/15/69 PAGE 23 REV.01

- COMPUTER DEVELOPMENT

3.2.5.5 Count of Leading Zeroes in A; to Af 04 00

This instruction scans the contents of A; from left to right and transfers the count of leading zeroes into A; as a 5-bit, right-justified quantity. The left-most 11 bits of A; are cleared.

3.2.5.6 Shift A Right, t Places D5 DX and D58X

This instruction shifts the {A} right, t bit positions where t is a 4-bit shift count, SC.

The shift may be circular or end-off. When bit DA of the instruction is a one, the shift is circular with right-most bits shifted end-around into left-most bit positions. When bit DA of the instruction is a zero, the shift is end-off with zeroes inserted into left-most bit positions.

When t = 0 the instruction effectively results in no operation.

1.2.5.7 Transfer A to Bl: {A} + ♥s♥ ♥t♥→Bl Ob XX

This instruction adds the right-most & bits of the instruction word, with zeroes extended to the {A} and transfers the sum to B1.

The state of the Adder Generate Bit is unaltered by the execution of this instruction.

3.2.5.8 Transfer A to B2: {A} + ♥s♥ ♥t♥→B2 □7 XX

This instruction adds the right-most 8 bits of the instruction word, with zeroes extended, to the {A} and transfers the sum to B2.

The state of the Adder Generate Bit is unaltered by the execution of this instruction.

NO. 52410600 DATE 10/15/69 PAGE 24 REV. 01

COMPUTER DEVELOPMENT

1.2.5.9

Set Condition Equal: Internal Tests

DB DX through DB 7X

This instruction forces the state of the Condition Bit to reflect the state of the selected internal test(s).

When bit 09 of the instruction word is a one, the Condition Bit is forced True if the A Register contains an odd number of one bits, or

When bit 10 of the instruction word is a one, the Condition Bit is forced True if the Adder Generate Bit is a one, or

When bit 11 of the instruction word is a one, the Condition Bit is forced True if the right-most bit at the output of the Shift Network, SN15, is a one.

Since the {A} are statically enabled to the input of the Shift Network, the 4-bit Shift Count, t, determines the bit in A which is right shifted to emerge at SN15. The following table provides the hexadecimal values of t with the corresponding bit positions of A which are tested when bit 11 of the instruction word is a one.

| t A  | t A         | t | A  | t | Α    |

|------|-------------|---|----|---|------|

| 0 15 | 4 11        | В | 07 | C | 03   |

| 1 14 | 5 10        | 9 | 06 | D | 02 - |

| 2 13 | <b>6</b> 09 | Α | 05 | Ε | 01   |

| 3 12 | 7 08        | В | 04 | F | 00   |

Since the selected internal tests will force the Condition Bit True on an Vinclusive or basis, all of the selected tests must be zero in order to force the Condition Bit False. Likewise, if bits 19, 10 and 11 of the instruction word are zeroes, the Condition Bit is forced False.

3.2.5.10

Set Condition Equal: Bit t, Channel s 09 XX

This instruction forces the state of the Condition Bit to reflect the state of the selected bit on the selected Normal Input Channel.

Force the Condition Bit True if bit t of Normal Input Channel s is a one; Force the Condition Bit False if bit t of Normal Input Channel s is a zero.

The 4-bit designator s specifies one of sixteen possible Normal Input Channels and the 4-bit designator t specifies one of the sixteen-bit positions to be tested within that channel. If the designated Input Channel is not physically present, the Condition Bit is forced True.

NO. 52410600 DATE 10/15/69 PAGE 25 REV. 01

COMPUTER DEVELOPMENT

#### 3.2.5.11

Selective Set Bit t of Channel s

□A XX

This instruction unconditionally sets bit t of Normal Output Channel s.

The 4-bit designator s specifies one of sixteen possible Normal Output Channels and the 4-bit designator t specifies one of the sixteen bit positions to be set within that channel. The remaining fifteen bits of the channel are left unchanged.

If bit t of channel s was initially in the set state or if Normal Output Channel s is not physically present, the instruction effectively results in no operation.

#### 3.2.5.12

Selective (lear Bit t of Channel s

OB XX

This instruction unconditionally clears bit t of Normal Output Channel s.

The 4-bit designator s specifies one of sixteen possible Normal Output Channels and the 4-bit designator t specifies one of the sixteen bit positions to be cleared within that channel.

If bit t of channel s was initially in the clear state or if Normal Output Channel s is not physically present, the instruction effectively results in no operation.

NO. 52410600 DATE 10/15/69 PAGE <sup>26</sup> REV. 01

COMPUTER DEVELOPMENT

3.2.5.13

Input To A From Channel s

DC XD

This instruction transfers a word from Normal Input Channel s to A.

The 4-bit designator s specifies one of sixteen possible Normal Input Channels.

If Normal Input Channel s is not physically present, {A<sub>f</sub>} will consist of all ones; FFFF<sub>16</sub>.

3.2.5.14

Set Channel s From A

DD XD or DD X8

This instruction sets bits on Normal Output Channel s according to the [A].

When bit 12 of the instruction word is a zero, this instruction sets bits on Normal Output Channel s where corresponding ones are present in A. Where zeros are present in A. corresponding bits on the Normal Output Channel are left unchanged.

When Bit 12 of the instruction word is a one, this instruction sets bits on Normal Output Channel's where corresponding zeros are present in A. Where ones are present in A. corresponding bits on the Normal Output Channel are left unchanged.

The 4-bit designator s specifies one of sixteen possible Normal Output Channels.

If Normal Output Channel s is not physically present, the instruction results in no operation.

NO. 52410600 DATE 10/15/69 PAGE 27 REV. 01

COMPUTER DEVELOPMENT

1.2.5.15

#### Clear Channel s From A

DE XD or DE X8

This instruction clears bits on Normal Output Channel s according to {A}.

When bit 12 of the instruction word is a zero, this instruction clears bits on Normal Output Channel s where corresponding zeros are present in A. Where ones are present in A. corresponding bits on the Normal Output Channel are left unchanged.

When bit 12 of the instruction word is a one, this instruction clears bits on Normal Output Channel s where corresponding ones are present in A. Where zeros are present in A. corresponding bits on the Normal Channel are left unchanged.

The 4-bit designator s specifies one of sixteen possible Normal Output Channels.

If Normal Output Channel s is not physically present, the instruction results in no operation.

3.2.5.16

#### Transfer A to Channel s

OF XD or OF X&

This instruction transfers the {A} directly or in one's complement mode to Normal Output Channel s.

When bit 12 of the instruction word is a zero, this instruction force transfers the {A} directly to Normal Output Channel s.

When bit 12 of the instruction word is a one, this instruction force transfers the one's complement of [A] to Normal Output Channel s.

The 4-bit designator s specifies one of sixteen possible Normal Output Channels.

If Normal Output Channel s is not physically present, the instruction results in no operation.

NO. 52410600 DATE<sup>10</sup>/15/69 PAGE <sup>28</sup> REV. 01

COMPUTER DEVELOPMENT

1.0.5.17 Add No Address

JO XX

This instruction adds the right-most 8 bits of the instruction word, with zeroes extended, to the {A}  $_i$  and transfers the sum to A  $_f$

The Adder Generate bit receives the end-off carry from the adder at the time the result is transferred to A.

3.2.5.18

Subtract No Address

ll XX

This instruction subtracts the right-most A bits of the instruction word, with zeroes extended, from the  $\{A\}_i$  and transfers the difference to  $A_f$ .

The Adder Generate bit receives the end-off carry from the adder at the time the result is transferred to A.

3.2.5.19

Exclusive Or No Address

75 XX

This instruction performs an exclusive or with the right-most & bits of the instruction word and the right-most & bits of Ai and places the result in Af. The left-most & bits of Ai remain unchanged.

The exclusive or operation is performed for the following truth table:

| Bit n of Ai | Bit n of the<br>Immediate Operand | Bit n of A <sub>f</sub> |

|-------------|-----------------------------------|-------------------------|

|             |                                   |                         |

|             | 0                                 |                         |

| 0           | l.                                | <u> </u>                |

| L           | 0                                 | <u>l</u>                |

| 1           | l.                                |                         |

n = 08 through 15

3.2.5.20

Logical Product No Address

T3 XX

This instruction performs the logical product with the right-most & bits of the instruction word and the right-most &-bits of A; and places the result in Af. The left-most & bits of Af are cleared.

The logical product operation is performed for the following truth table:

| Bit n of Ai | Bit n of the<br>Immediate Operand | Bit n of A <sub>f</sub> |

|-------------|-----------------------------------|-------------------------|

| Ω           | 0                                 | 0                       |

|             | 1                                 | 0                       |

| 1           | 0                                 | 0                       |

| <u>l</u>    | 1                                 |                         |

n = 08 through 15

## SPECIFICATION

NO. 52410600 DATE 10/15/69 PAGE 29 REV. 01

COMPUTER DEVELOPMENT

3.2.5.21

Test Index Bl No Address

]4 XX

This instruction compares the right-most & bits of the instruction word with the right-most & bits initially contained in Bl.

If the quantities are equal, the Condition Bit is forced True and the {Bl}; are left unchanged.

If the quantities are not equal, the Condition Bit is forced False and the {Bl}; are increased by one; {Bl};  $+1 \rightarrow Blf$ .

1.2.5.22

Test Index B2 No Address

15 XX

This instruction compares the right-most & bits of the instruction word with the right-most & bits initially contained in B2.

If the quantities are equal, the Condition Bit is forced True and the {B2}; are left unchanged.

If the quantities are not equal, the Condition Bit is forced false and the {B2}; are increased by one; {B2}; +  $1 \rightarrow B2$ f.

3.2.5.23

Load A Complement No Address

JP XX

This instruction performs the 2's complement of the rightmost 8 bits of the instruction word, with zeroes extended, and transfers the result to A.

3.2.5.24

Load From {A}; {{A;} + oso oto} -> Af

ъ7 XX

This instruction transfers the {M} to A.

The execution address, M. is formed by adding the right-most 8 bits of the instruction word to the {A};.

3.2.5.25

Enter A With Address

la XX through lfXX

This instruction transfers M to A.

As a result of using the execution address as an operand, four variations of this instruction become noteworthy:

When M = m, the instruction performs what is conventionally described as Enter A.

When  $M = \{BL\} + m$  and m = DD, the instruction performs an inter-register transfer from BL to A.

When  $M = \{B2\} + m$  and m = DD, the instruction performs an inter-register transfer from B2 to A.

When  $M = \{P\} \pm m$  and m = 00, the instruction performs an inter-register transfer from P to A.

NO. 52410600 DATE 10/15/69 PAGE <sup>30</sup> REV. 01

COMPUTER DEVELOPMENT

1.2.5.26

Enter Bl With Address

20 XX through 27 XX

This instruction transfers M to Bl.

As a result of using the execution address as an operand, six variations of this instruction become noteworthy:

When M = m, the instruction performs what is conventionally described as Enter Index.

When M = {Bl} + m, the instruction performs what is conventionally described as Increase Index.

When  $M = \{B2\} + m$  and m = DD, the instruction performs an inter-register transfer from B2 to B1.

When  $M = \{P\} \pm m$  and m = DD, the instruction performs an inter-register transfer from P to Bl.

When M = {m}, the instruction performs what is conventionally described as Load Index.

When  $M = \{BL\} + \{m\}$ , the instruction performs an Add to Index operation.

#### 1.2.5.27

#### Enter B2 With Address

28 XX through 2F XX

This instruction transfers M to B2.

As a result of using the execution address as an operand, six variations of this instruction become noteworthy:

When M = m, the instruction performs what is conventionally described as Enter Index.

When M = {B2} + m, the instruction performs what is conventionally described as Increase Index.

When  $M = \{BL\} + m$  and m = DD, the instruction performs an inter-register transfer from BL to B2.

When  $M = \{P\} \pm m$  and m = DD, the instruction performs an inter-register transfer from P to B2.

When M = {m}, the instruction performs what is conventionally described as Load Index.

When  $M = \{B2\} + \{m\}$ , the instruction performs an Add to Index operation.

NO. 52410500 DATE10/15/59 PAGE 31 REV. 01

COMPUTER DEVELOPMENT

1.0.5.28

Test Index Bl

30 XX through 37 XX

This instruction compares the {M} to the {BL}; .

If the quantities are equal, the Condition Bit is forced True and the {Bl}; are left unchanged.

If the quantities are not equal, the Condition Bit is forced False and the {Bl}; are increased by one; {Bl}; +1->Blf.

1.2.5.29

Test Index B2

38 XX through 3F XX

This instruction compares the  $\{M\}$  to the  $\{B2\}_i$ .

If the quantities are equal, the Condition Bit is forced True and the {B2}; are left unchanged.

If the quantities are not equal, the Condition Bit is forced False and the {B2}; are increased by one; {B2}; +1 $\rightarrow$ B2<sub>f</sub>.

3.2.5.30

Load A

40 XX through 47 XX

This instruction transfers the {M} to A.

3.2.5.31

Load A Complement

48 XX through 4F XX