# CONTROL DATA® 9730 MINI MODULE DRIVE (MMD)

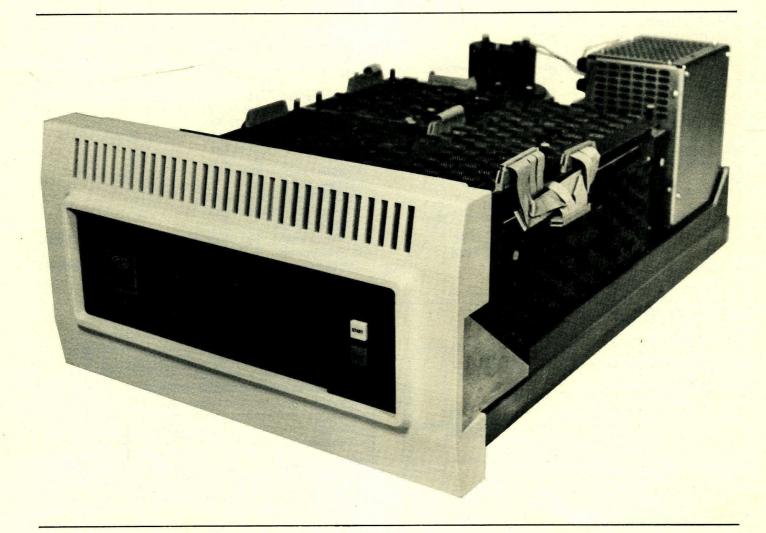

The CONTROL DATA Mini Module Drives (MMD) are random-access storage devices which utilize fixed-sealed modules for the storage medium.

The Mini Module Drive family consists of the 9730-12 (12 MB), 9730-24 (24 MB) and 9730-48 (48 MB).

The basic drive includes a frame where the following components are mounted: drive motor, power supply, electronics, front panel, and sealed module. The sealed module contains the spindle, media, rotary actuator, and heads. Optionally, a head-per-track shoe can also be mounted within the sealed module.

The CDC® Mini Module Drive family is designed for applications demanding high reliability, low maintenance, and environmental tolerance. The sealed module protects the entire recording environment from external contaminants. The fixed media concept significantly improves device reliability and eliminates the need for performing costly head alignments. The circuit packaging approach offers easy accessibility and fast trouble shooting with replaceable modules.

The Mini Module Drive is both format and interface compatible with CDC's Storage Module Drive family.

# **FEATURES**

- Interface and format compatibility to SMD

- Write protect

- Daisy chaining of up to 16 drives

- Power sequencing

- Power supply

- I/O connectors suitable for flat cable

- · Variable or fixed sectoring

- Phase-locked oscillator/data separator

- NRZ to MFM data encoder with write compensation

## **OPTIONS**

- Head per track

- Rack mount slides

- Dual channel

# **SPECIFICATIONS**

# DATA ORGANIZATION – UNFORMATTED CAPACITIES GIVEN

|                          | 9730-12 | 9730-24 | 9730-48 |

|--------------------------|---------|---------|---------|

| 8 Bit bytes per spindle  | 12M     | 24M     | 48M     |

| Optional head per track  | 00      | 00      | 00      |

| (48 heads)               | .96     | .96     | .96     |

| Cylinders per surface    | 320     | 320     | 640     |

| Bytes per track          |         | 20,160  |         |

| Data heads per surface   | 2       | 2       | 2       |

| Data surfaces            |         | 2       | 2       |

| Disks                    | 1       | 2       | 2       |

| Servo and head per track |         |         |         |

| surface                  | 1       | 1       | 1       |

| Track density-TPI        | 300     | 300     | 600     |

#### Performance

Data transfer rate: 1.2 megabytes

Spindle speed: 3600 RPM Bit density: 6220 BPI

Access time

Max. full stroke: 60 MSEC Average: 40 MSEC Min. one track: 14 MSEC

Latency time

Maximum: 16.7 milliseconds Average: 8.3 milliseconds

Media-14" diameter, magnetic oxide coated, lubricated

Heads - Contact start/stop

#### Power requirements

| Frequency | Voltages        |  |  |

|-----------|-----------------|--|--|

| 60 Hz     | 100,120         |  |  |

| 50 Hz     | 100,220,240,250 |  |  |

Phase-single

Maximum inrush current—14 AMPS Heat Dissipation—1050 BTU/Hour

Power Input - 300 Watts

Input pwr. conn. - Nema type 5-15P for 110V, 60 Hz

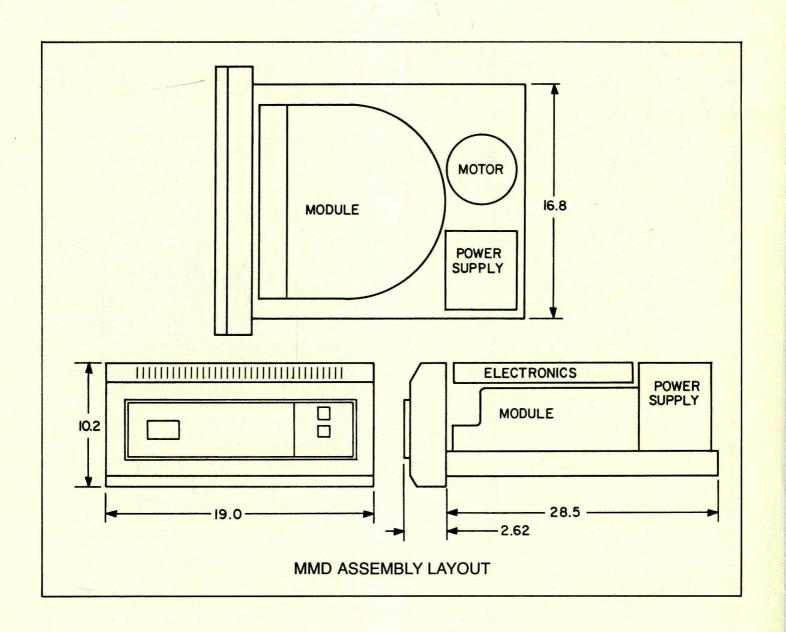

Physical characteristics

Height - in/mm 10.2/259.1

Depth - in/mm 30/762

Width -in/mm 16.75/425.5

Weight-Ibs/kg 85/38.6

#### Environmental

Operating temperature - 50°F to 95°F

Humidity - 20% to 80% RH

Non-operating temperature - 40°F to 158°F

Humidity-5% to 95% RH

# Reliability and service

MTBF: 8000 hours

MTTR: Less than 1.0 hour Service life: 36,000 hours

Data error rate-

Recoverable: Not more than one error in 1010 bits

transferred

No scheduled maintenance required other than periodic

coarse filter cleaning.

#### OPERATOR CONTROL PANEL

Ready indicator

Fault clear switch with fault status indicator

#### MAINTENANCE FEATURES

- · No head alignment required

- · No read/write adjustments

- · Fault trap indicators to isolate problems quickly

- Field test unit available for off-line maintenance

- Module is easily removed as a sealed unit

- Functionally organized logic modules with easy access

#### INTERFACE HARDWARE

#### I/O Circuits

Industry Standard 75110 balanced line drivers or equivalent.

Industry Standard 75108 balanced line receivers or

equivalent.

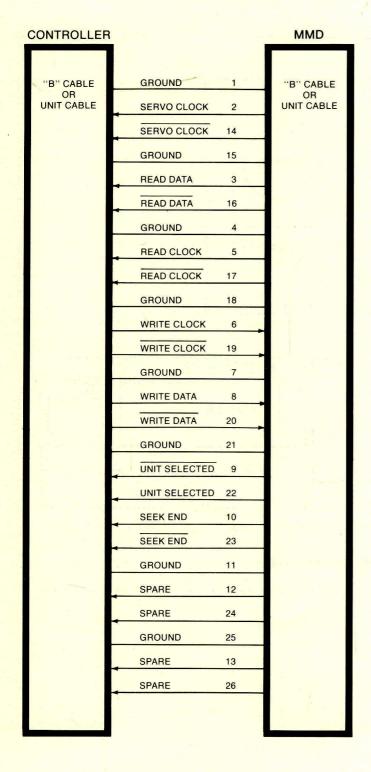

## I/O Connectors

"A" Cable (60 pin) Amp P/N 88012-2

"B" Cable (26 pin) Amp P/N 86905-2, 3M P/N 3399-3000, Ansley 609-2601M

Cable

"A" Cable-30 twisted pair, flat cable 100 ±10 ← characteristic impedance maximum length-100 ft. Used in daisy chain mode.

Spectra strip 3CT-6028-7B-05-100

"B" Cable - 26 conductor, flat cable with ground plane, 130 ±15

characteristic impedance, 50 ft. maximum length, 3M P/N 3476/26. Used in radial mode as unit cable.

INTERFACE SIGNALS Input Signals from Controller

UNIT SELECT TAG - Leading edge samples the unit select bit lines for storage. The remaining true level enables the unit to stay selected.

UNIT SELECT 20-23 - Carry binary logical address of the unit to be selected.

CYLINDER SELECT TAG 1 - Leading edge loads the absolute address from the 10 bit bus lines and the trailing edge initiates the seek.

HEAD SELECT TAG 2-Leading edge loads the head address from the 10 bit bus lines.

CONTROL SELECT TAG 3-Used as gate enable which provides control information from the 10 bit bus lines and must be true for the entire control operation. The bus lines contain the following control information:

BIT 0 WRITE GATE - Enables the write driver.

BIT 1 READ GATE-Enables digital read data on the transmission lines. Leading edge of Read Gate triggers the read chain to synchronize on all-zeros pattern.

NOTE: The Data Strobe and Servo Offset signals are intended to be an aid in recovering marginal data. BIT 2 SERVO OFFSET PLUS - Actuator offset from the nominal on Cylinder position towards the spindle.

BIT 3 SERVO OFFSET MINUS-Actuator offset from nominal On Cylinder position away from the spindle. BIT 4 FAULT CLEAR - Will clear the fault flip-flop if the fault condition no longer exists.

BIT 5 AM ENABLE - Address Mark Enable line, in conjunction with Write Gate or Read Gate, allows the writing or recovering of Address Marks. When AM Enable is true while Write Gate is true, the writer stops toggling and erases the data, creating an Address Mark. Write Fault detection in the unit is inhibited by this signal. When AM Enable is true while Read Gate is true, an analog voltage comparator detects the absence of read signal. If the duration of the erased area is greater than 16 bits, an Address Mark Found signal will be issued. BIT 6 RTZ-Pulse sent to the SMD will cause the actuator to seek to track 0, reset the Head Register and clear the Seek Error flip-flop. This seek is significantly longer than a normal seek to track 0, and should only be used for recalibration and not data acquisition.

BIT 7 DATA STROBE EARLY-SMD PLO Data Separator will strobe the data at a time earlier than nominal.

BIT 8 DATA STROBE LATE-SMD PLO Data Separator will strobe the data at a time later than nominal.

| CONTROLLER                |                   | HI, LO     | MMD                 |

|---------------------------|-------------------|------------|---------------------|

|                           | UNIT SELECT TAG   | 22, 52     |                     |

| "A" CABLE                 | UNIT SELECT 2º    | 23, 53     | "A" CABLE           |

| DAISY CHAIN               | UNIT SELECT 21    | 24, 54     | DAISY CHAIN         |

|                           | UNIT SELECT 22    | 26, 56     |                     |

|                           | UNIT SELECT 23    | 27, 57     |                     |

|                           | TAG 1             | 1, 31      |                     |

|                           | TAG 2             | 2, 32      |                     |

|                           | TAG 3             | 3, 33      |                     |

|                           | BIT 0             | 4, 34      |                     |

|                           | BIT 1             | 5, 35      |                     |

|                           | BIT 2             | 6, 36      |                     |

|                           | BIT 3             | 7, 37      |                     |

|                           | BIT 4             | 8, 38      |                     |

|                           | BIT 5             | 9, 39      |                     |

|                           | BIT 6             | 10, 40     |                     |

|                           | BIT 7             | 11, 41     |                     |

|                           | BIT 8             | 12, 42     |                     |

|                           | BIT 9             | 13, 43     |                     |

|                           | OPEN CABLE DETECT | TOR 14, 44 |                     |

|                           | INDEX             | 18, 48     |                     |

|                           | SECTOR            | 25, 55     | A-                  |

|                           | FAULT             | 15, 45     |                     |

|                           | SEEK ERROR        | 16, 46     |                     |

| NOTE: 60                  | ON CYLINDER       | 17, 47     |                     |

| POSITION<br>28 AWG.       | UNIT READY        | 19, 49     |                     |

| 30 PAIR<br>TWISTED-       | ADDRESS MARK FOU  | ND 20, 50  |                     |

| STRAIGHT<br>FLAT<br>CABLE | WRITE PROTECTED   | 28, 58     |                     |

| MAXIMUM<br>LENGTH-        | POWER SEQUENCE F  | PICK 29    | ONE TWICTED         |

| 100 FT.                   | POWER SEQUENCE H  | HOLD 59    | ONE TWISTED<br>PAIR |

|                           | BUSY              | 21, 51     |                     |

|                           | NOT USED (SPARE)  | 30, 60     |                     |

|                           |                   |            |                     |

|                           |                   |            |                     |

POWER SEQUENCING—Internally switch-selectable feature. When a ground is applied to the P.S. pick line, the SMD is allowed to power-up in the daisy chain order. After this unit is up to speed, it will apply ground to next unit to continue sequence. This is used after a power interruption of first power-up.

OPEN CABLE DETECTOR—Inhibits control functions from taking place when not a true signal, as in the case of a disconnected "A" cable.

Output Signals to Controller

UNIT READY-Heads are loaded; no fault, and unit is up to speed.

ON CYLINDER – Indicates that heads are on track. The unit is ready to seek, read, or write.

FAULT—One of the following faults exists: D.C. power fault, head select fault, write fault, write or read and not On Cylinder, or both read and write at the same time. The fault inhibits the writer. If the fault was transient, this status may be cleared by control select clear, operator panel clear, or master clear in the logic chassis.

SEEK ERROR—Unit was not able to complete a seek within 500 ms, carriage has moved off position, or there was an attempted illegal seek. A return-to-zero (RTZ) will clear the seek Error Status and return heads to track zero.

INDEX – This pulse occurs once per revolution. Its leading edge defines the start of each track or sector zero.

SECTOR – Sector marks as well as the index mark are derived from the servo track. Number of sectors is switch selectable within the SMD.

ADDRESS MARK FOUND—Sent during Address Mark Search when there is at least 16 missing transitions detected on the disk. After receipt, AM Enable should be dropped and valid data will be present on the I/O.

WRITE PROTECTED—Status which says the writer is inhibited because write protect switch is set "on" or during a fault.

SEEK END—On Cylinder or Seek Error except for an illegal seek. Indicates when a seek operation has ended. UNIT SELECTED—Occurs when the four unit select lines compare with the logic plug decode on the control panel and the unit select tag is true. Allows physical identification of logical unit.

READ CLOCK-9.67 MHz clock derived from the MFM data recorded on the disk. The leading edge is used by the controller to sample the Read Data line.

READ DATA-PLO separated NRZ data with 103 ns cell time.

SERVO CLOCK - Phased-locked 9.67 MHz clock generated from the servo track dibits.

WRITE DATA-NRZ data with 103 ns cell time to be converted within the drive to MFM and written on the disk.

WRITE CLOCK-9.67 MHz clock which is Servo Clock turned around at controller and in phase such that the leading edge falls in the center of the 103 ns cell of write data.

BUSY-Status for dual channel units only.

Specifications are subject to change without notice.

Detailed design specifications are available upon request.

CONTROL DATA SALES OFFICES ARE LOCATED IN PRINCIPAL CITIES THROUGHOUT THE WORLD PERIPHERAL PRODUCTS SALES

BOX 0, MINNEAPOLIS, MINNESOTA 55440

TELEPHONE: (612) 853-3617 • TWX: 910-576-2978