**SPEC** 77738076

CD 7

REV D2

DATE Nov. 1984

**PAGE** 1 of 93

# ENHANCED SMALL DEVICE INTERFACE SPECIFICATION

## COPYRIGHT © 1984 by MAGNETIC PERIPHERALS INC. ALL RIGHTS RESERVED

Printed in the United States of America

This publication may contain application, high technology, or product specification data, or any combination thereof, is considered advance technical information by the producer, and is subject to change without prior notice.

SPECIFICATION

## TABLE OF CONTENTS

| SECTION            |                                                | PAGE                            |

|--------------------|------------------------------------------------|---------------------------------|

| 1.0                | SCOPE                                          | . 1                             |

| 1.0                |                                                |                                 |

| 2.0                | GENERAL DESCRIPTION                            | . 2                             |

| 3.0                | ELECTRICAL INTERFACE                           | . 2                             |

| 3.1                | Control Signal Drivers and Receivers           | . 4                             |

| 3.2                | Data Line Drivers and Receivers                | . 4                             |

| 4.0                | PHYSICAL INTERFACE                             | . 5                             |

| 4.1                | J1/P1 Connectors                               |                                 |

| 4.2                | J2/P2 Connectors                               |                                 |

| 4.3                | J3/P3 Connectors                               | . 6                             |

| 4.4                | J4/P4 Frame Ground Connector                   | . 0                             |

| 5.0                | DISK DRIVE IMPLEMENTATION - SERIAL MODE        | . 8                             |

| 5.1                | Control Input Lines                            | . 8                             |

| 5.1.1              | Drive Select                                   | . 8                             |

| 5.1.2              | Drive Select 20, 21, 22, 23                    | . 11                            |

| 5.1.3              | Write Gate                                     | . 11                            |

| 5.1.4              | Read Gate                                      | . 12                            |

| 5.1.5<br>5.1.5.1   | Command Data Bits 15 thru 12 decode definition | . 14                            |

| 5.1.6              | Transfer Request                               |                                 |

| 5.1.7              | Address Mark Enable                            | . 18                            |

| 5.2                | Control Output Lines                           | . 19                            |

| 5.2.1              | Drive Selected                                 | . 19                            |

| 5.2.2              | Ready                                          | . 19                            |

| 5.2.3              | Configuration-Status Data                      | . 19                            |

| 5.2.3.1            | Configuration Response Bits                    | . 20                            |

| 5.2.3.2            | Status Response Bits                           | . 21<br>. 23                    |

| 5.2.4<br>5.2.5     | Attention                                      |                                 |

| 5.2.6              | Index                                          | _                               |

| 5.2.7              | Sector/Byte Clock/Address Mark Found           | . 23                            |

| 5.2.7.1            | Sector                                         |                                 |

| 5.2.7.2<br>5.2.7.3 | Byte Clock                                     | <ul><li>25</li><li>26</li></ul> |

| 5.2.8              | Command Complete                               |                                 |

|                    |                                                |                                 |

| SECTION                                                        |                                                                                                                                                                                       | PAGE #                                 |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4                        | Data Transfer Lines  NRZ Write Data  NRZ Read Data  Read/Reference Clock Write Clock                                                                                                  | 27<br>27<br>27                         |

| 5.4                                                            | Read, Write, and Format Parameters                                                                                                                                                    | 29                                     |

| 5.4.1<br>5.4.2<br>5.4.3                                        | General Summary of Critical Read Timing Parameters<br>General Summary of Critical Write Timing Parameters<br>Fixed Sector Implementation                                              | 30                                     |

| 5.4.3.1<br>5.4.3.2<br>5.4.3.3<br>5.4.3.4<br>5.4.3.5<br>5.4.3.6 | Format Rules (Fixed Sector) Intersector Gap (ISG) Address Area Data Area Format Speed Tolerance Gap Fixed Sector Adr Mark, Write Gate, PLO Sync Format Timing.                        | 33<br>33<br>35<br>36                   |

| 5.4.4                                                          | Address Mark Implementation                                                                                                                                                           | 38                                     |

| 5.4.4.1<br>5.4.4.2<br>5.4.4.3<br>5.4.4.4<br>5.4.4.5<br>5.4.4.6 | Format Rules (Soft Sector) Soft Sector Format Address Mark Field Address Mark Pad InterSector Gap (ISG) Speed Tolerance Gap Soft Sector Adr Mark, Write Gate, PLO Sync Format Timing. | 38<br>38<br>39<br>39<br>39             |

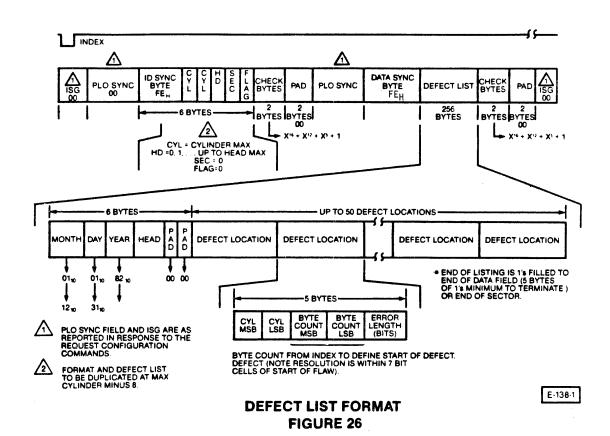

| 5.5                                                            | Defect List Option                                                                                                                                                                    | 41                                     |

| 6.0                                                            | DISK DRIVE IMPLEMENTATION - STEP MODE                                                                                                                                                 | 43                                     |

| 5.1                                                            | Control Input Lines                                                                                                                                                                   | 43                                     |

| 5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7    | Drive Select Head Select 2 <sup>0</sup> , 2 <sup>1</sup> , 2 <sup>2</sup> , 2 <sup>3</sup> ,/Change Cartridge Write Gate Read Gate Direction In Step Address Mark Enable              | 43<br>46<br>46<br>47<br>47<br>48<br>49 |

| SECTION                                                                                                        |                                                                                                                                                                                                                                                                                                                    | PAGE                                                     |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 6.2                                                                                                            | Control Output Lines                                                                                                                                                                                                                                                                                               | 50                                                       |

| 6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7<br>6.2.7.1<br>6.2.7.2<br>6.2.7.3<br>6.2.8<br>6.2.9 | Drive Selected Ready Seek Complete Track 0000 Write Fault Index Sector/Byte Clock/Address Mark Found Sector Byte Clock Address Mark Found Write Protected Cartridge Changed                                                                                                                                        | 50<br>50<br>51<br>51<br>52<br>52<br>52<br>53<br>54<br>54 |

| 6.3                                                                                                            | Data Transfer Lines                                                                                                                                                                                                                                                                                                | 55                                                       |

| 6.3.1<br>6.3.2<br>6.3.3<br>6.3.4                                                                               | NRZ Write Data                                                                                                                                                                                                                                                                                                     | 55<br>55                                                 |

| 6.4                                                                                                            | Read, Write, and Format Parameters                                                                                                                                                                                                                                                                                 | 57                                                       |

| 6.4.1<br>6.4.2<br>6.4.3<br>6.4.3.1<br>6.4.3.2<br>6.4.3.3<br>6.4.3.4<br>6.4.3.5                                 | General Summary of Critical Read-Function Timing Parameters General Summary of Critical Write-Function Timing Parameters Fixed Sector Implementation Format Rules (Fixed Sector) Intersector Gap (ISG) Address Area Data Area Format Speed Tolerance Gap Fixed Sector Adr Mark, Write Gate, PLO Sync Format Timing | 57<br>58<br>60<br>60<br>61<br>61<br>63<br>64<br>64       |

| 6.4.4                                                                                                          | Address Mark Implementation                                                                                                                                                                                                                                                                                        | 66                                                       |

| 6.4.4.1<br>6.4.4.2<br>6.4.4.3<br>6.4.4.4                                                                       | Format Rules (Soft Sector)                                                                                                                                                                                                                                                                                         | 66<br>66<br>67<br>67                                     |

| <b>6.</b> 5                                                                                                    | Defect List Option                                                                                                                                                                                                                                                                                                 | 69                                                       |

| SECTION                                                                                    |                                                                                                                                                    | PAGE                                         |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

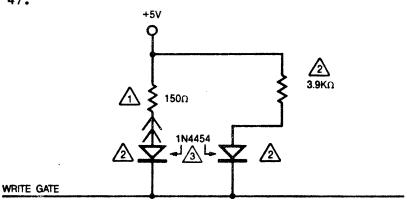

| 7.0                                                                                        | TAPE DRIVE IMPLEMENTATION - SERIAL MODE                                                                                                            | 71                                           |

| 7.1<br>7.2<br>7.3<br>7.4                                                                   | General Description                                                                                                                                | 71<br>72<br>72<br>75                         |

| 7.4.1<br>7.4.2<br>7.4.3<br>7.4.4<br>7.4.5<br>7.4.6<br>7.4.7<br>7.4.8                       | Head Select Write Gate Read Gate Command Data Command Data Bits 15 thru 12 Decode Definitions Transfer Request Address Mark Enable Data Write Gate | 75<br>75<br>76<br>76<br>78<br>84<br>84<br>84 |

| 7.5                                                                                        | Control Output Lines                                                                                                                               | 85                                           |

| 7.5.1<br>7.5.2<br>7.5.3<br>7.5.3.1<br>7.5.3.2<br>7.5.4<br>7.5.5<br>7.5.6<br>7.5.7<br>7.5.8 | Drive Selected                                                                                                                                     | 85<br>85<br>86<br>87<br>88<br>88<br>88<br>99 |

| 7.6                                                                                        | Data Transfer Lines                                                                                                                                | 90                                           |

| 7.6.1<br>7.6.2<br>7.6.3<br>7.6.4<br>7.6.5                                                  | NRZ Write Data  NRZ Read Data  Read Clock  Write Clock  Write Reference Clock                                                                      | 90<br>91<br>91<br>91<br>91                   |

| <b>7</b> 7                                                                                 | Format Pules                                                                                                                                       | 93                                           |

## FIGURES

| Figure |                                                            | Page # |

|--------|------------------------------------------------------------|--------|

| 1      | Typical Connection, Multiple Drive System                  | . 3    |

| 2      | Control Signals, Driver/Receiver Combination               | . 4    |

| 3      | Data Line Driver/Receiver Combination                      | . 4    |

| 4      | J1 Connector Dimensions                                    | . 5    |

| 5      | J2 Connector Dimensions                                    | . 6    |

| 6      | J3 Connector                                               | . 7    |

| 7      | Typical PCB Connector Orientation                          | . 7    |

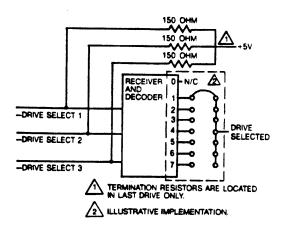

| 8      | Drive Select Termination                                   | . 8    |

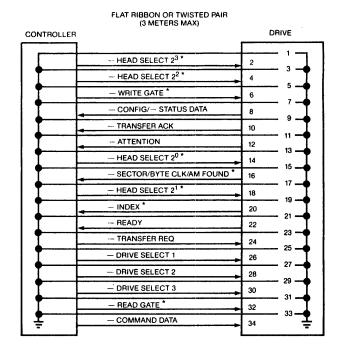

| 9      | Control Cable (J1/P1) Signals (Disk Drive - Serial Mode) . | . 9    |

| 10     | Data Cable (J2/P2) Signals (Disk Drive - Serial Mode)      | . 10   |

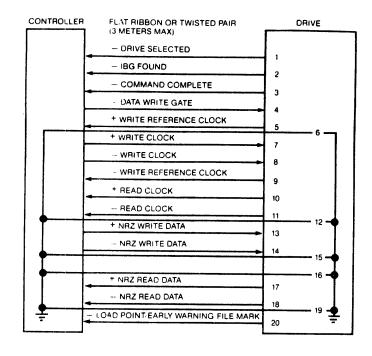

| 11     | Write Gate Termination                                     | . 11   |

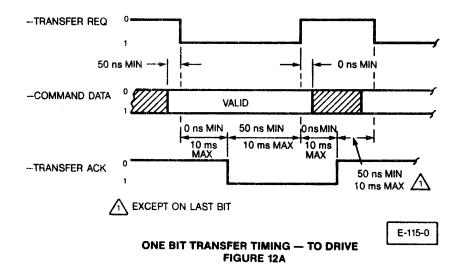

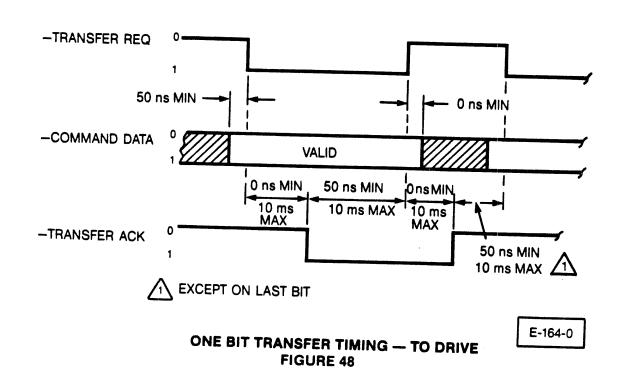

| 12A    | One Bit Transfer Timing To Drive                           | . 12   |

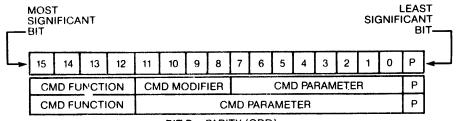

| 12B    | Command Data Word Structure (Disk Drive)                   | . 13   |

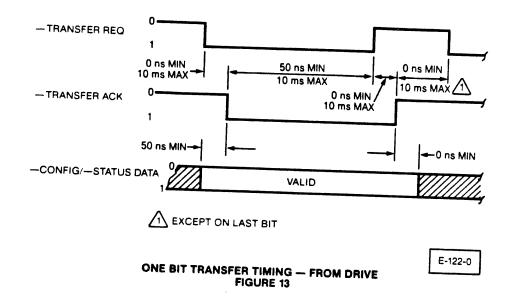

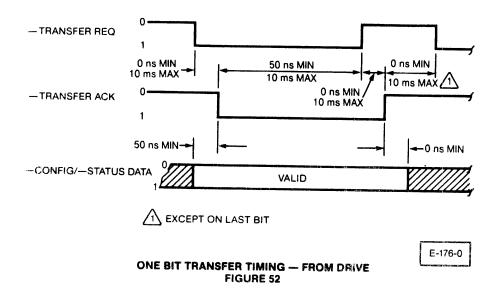

| 13     | One Bit Transfer Timing From Drive                         | . 17   |

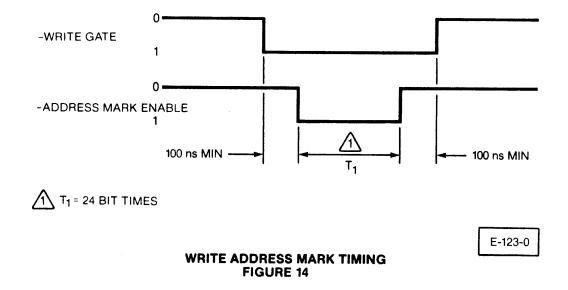

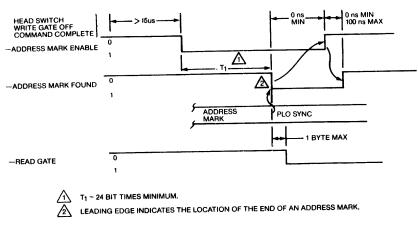

| 14     | Write Address Mark Timing                                  | . 18   |

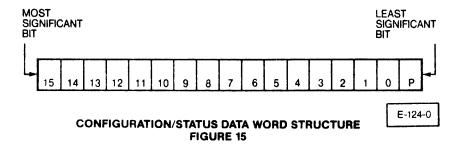

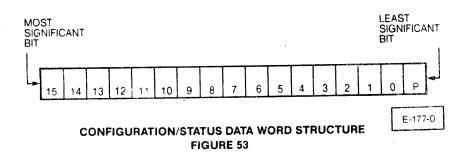

| 15     | Configuration/Status Data Word Structure                   | . 19   |

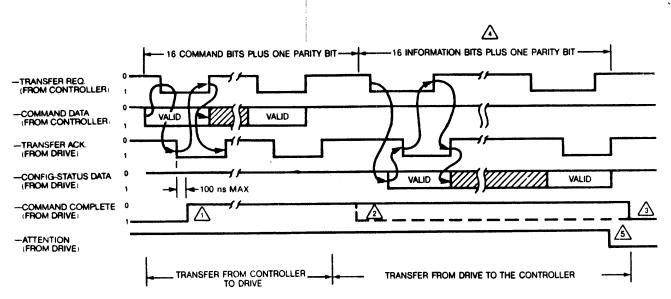

| 16     | Typical Serial Operation(s)                                | . 22   |

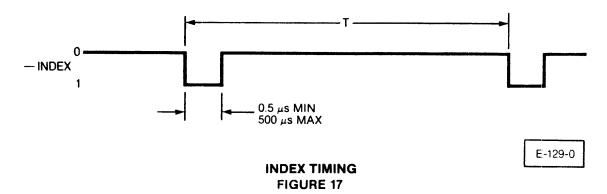

| 17     | Index Timing                                               | . 23   |

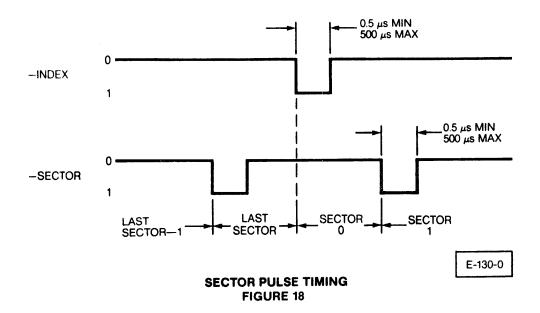

| 18     | Sector Pulse Timing                                        | . 24   |

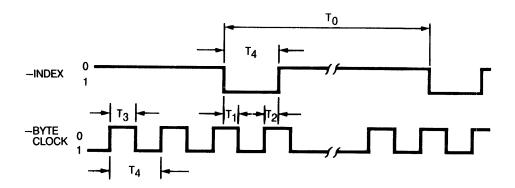

| 19     | Index and Byte Clock Relationship                          | . 25   |

| 20     | Read Address Mark Timing                                   | . 26   |

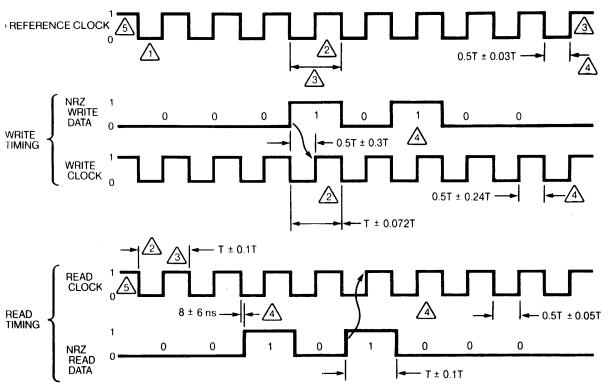

| 21     | NRZ Read/Write Data Timings                                | . 28   |

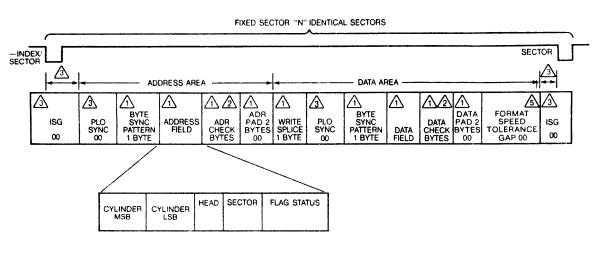

| 22     | Fixed Sector Format (Serial Mode)                          | . 32   |

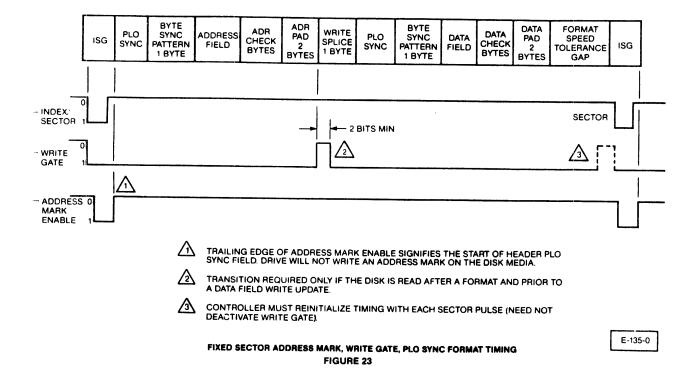

| 23     | Fixed Sector Adr Mark, Write Gate, PLO Sync Field Timing . |        |

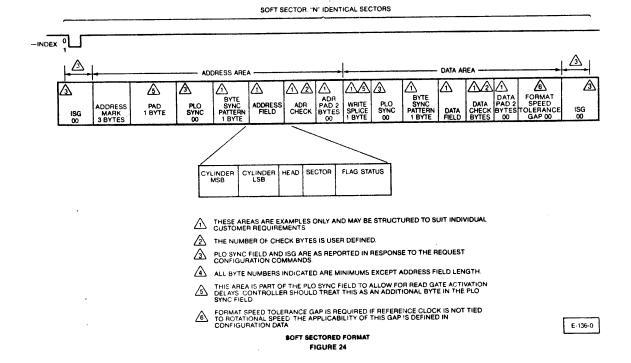

| 24     | Soft Sector Format (Serial Mode)                           |        |

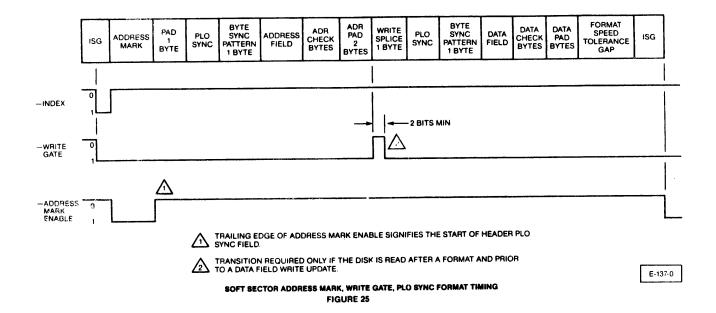

| 25     | Soft Sector Adr Mark, Write Gate, PLO Sync Format Timing . | . 40   |

| 26     | Defect List Format                                         | . 42   |

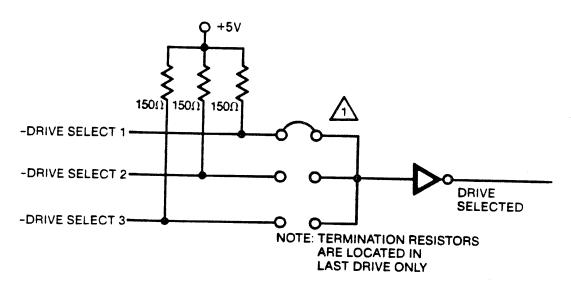

| 27     | Drive Select Termination (Step Mode)                       |        |

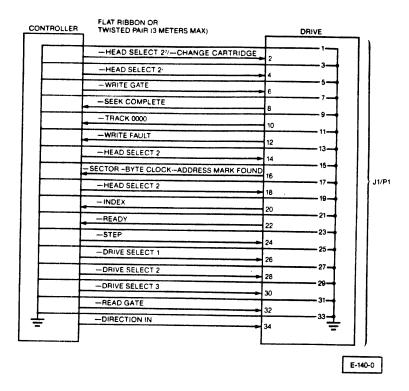

| 28     | Control Cable (J1/P1) Signals (Disk Drive-Step Mode)       |        |

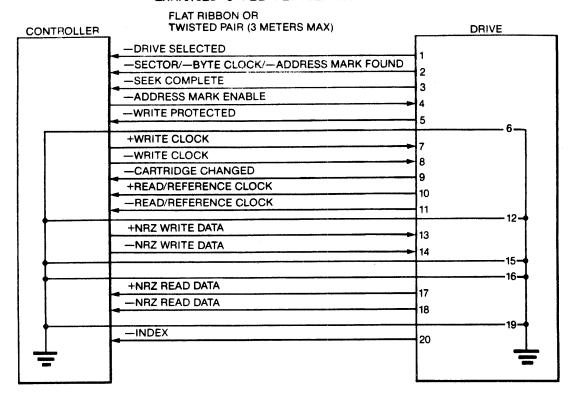

| 29     | Data Cable (J2/P2) Signals (Disk Drive-Step Mode)          |        |

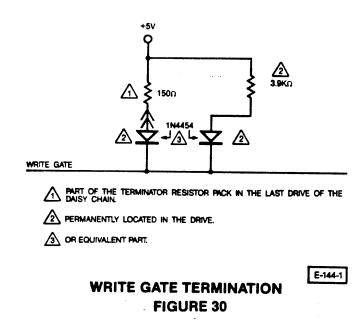

| 30     | Write Gate Termination                                     |        |

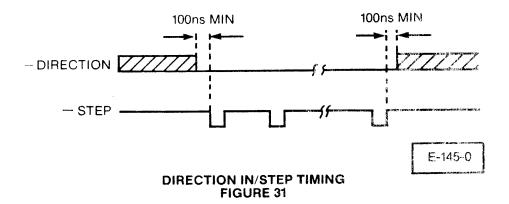

| 31     | Direction In/Step Timing                                   | . 47   |

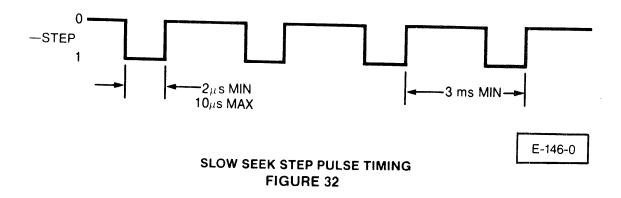

| 32     | Slow Seek Step Pulse Timing                                | . 48   |

|        |                                                            |        |

## **FIGURES**

| Figure | #                                                          | Page # |

|--------|------------------------------------------------------------|--------|

|        |                                                            |        |

| 33     | Buffered Seek Step Pulse Timing                            | . 48   |

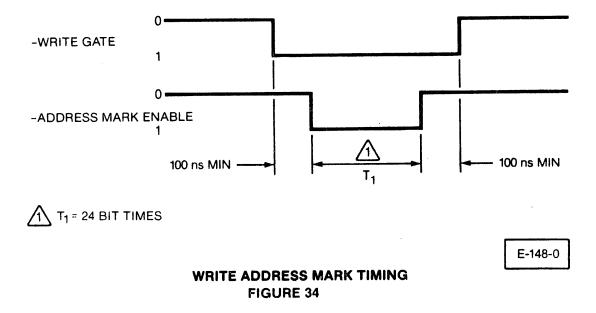

| 34     | Write Address Mark Timing                                  | . 49   |

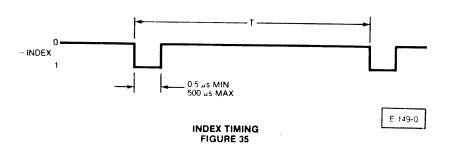

| 35     | Index Timing                                               | . 52   |

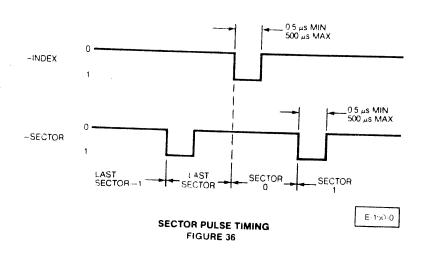

| 36     | Sector Pulse Timing                                        | . 52   |

| 37     | Index and Byte Clock Relationship                          | . 53   |

| 38     | Read Address Mark Timing                                   | . 54   |

| 39     | NRZ Read/Write Data Timing Relationship                    | . 56   |

| 40     | Fixed Sector Format (Step Mode)                            | . 60   |

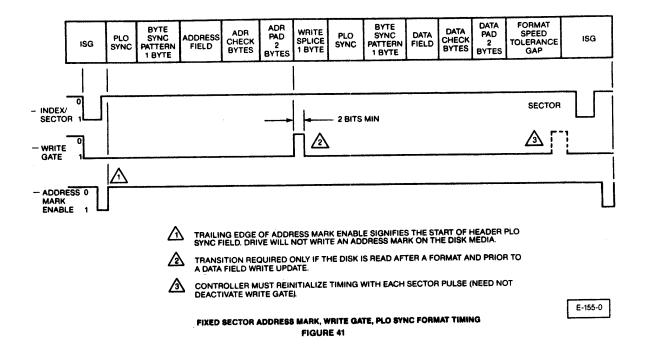

| 41     | Fixed Sector Adr Mark, Write Gate, PLO Sync Field Timing . | . 65   |

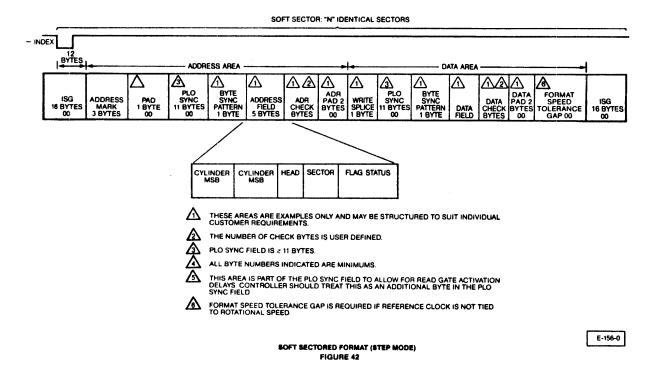

| 42     | Soft Sectored Format (Step Mode)                           | . 66   |

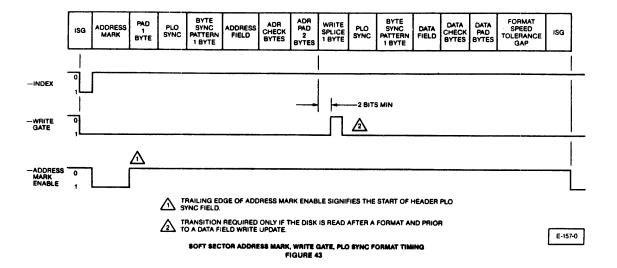

| 43     | Soft Sector Adr Mark, Write Gate, PLO Sync Format Timing . | . 68   |

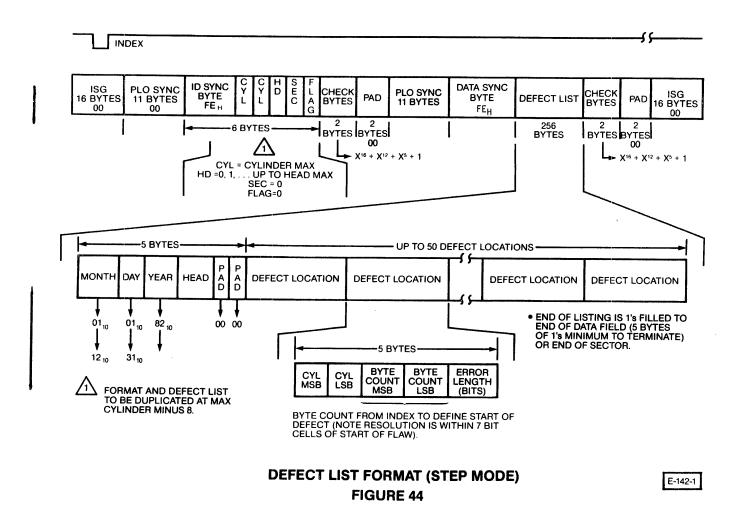

| 44     | Defect List Format (Step Mode)                             | . 70   |

| 45     | Control Cable (J1/P1) Signals (Tape Drive)                 | . 73   |

| 46     | Data Cable (J2/P2) Signals (Tape Drive)                    | . 74   |

| 47     | Write Gate Termination                                     | . 75   |

| 48     | One Bit Transfer Timing - To Drive                         | . 76   |

| 49     | Command Data Word Structure (Tape Drive)                   | 77     |

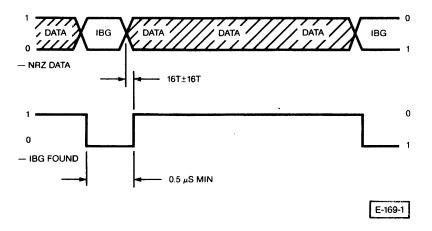

| 50     | Read Data and IBG Detection                                | 80     |

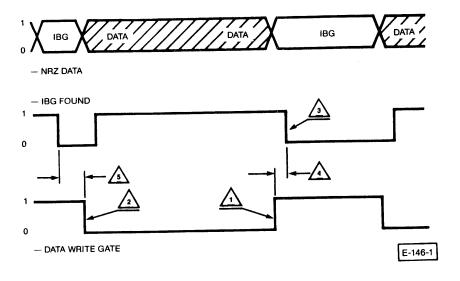

| 51     | Write Data and IBG Timing                                  | 83     |

| 52     | One Bit Transfer Timing - From Drive                       | 84     |

| 53     | Configuration/Status Data Word Structure                   | 85     |

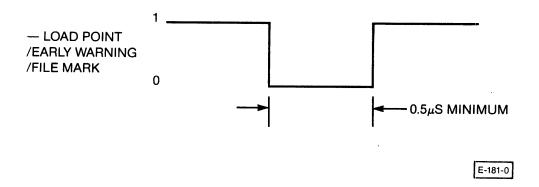

| 54     | Load Point/Early Warning Timing                            | 88     |

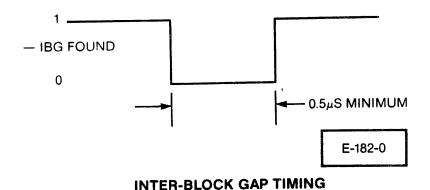

| 55     | Inter-Block Gap Timing                                     | 89     |

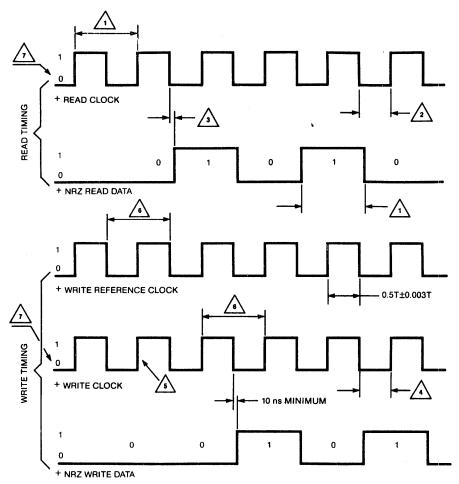

| 56     | NRZ Read/Write Data Timings                                | 92     |

| 57     | Required Base Format                                       | 93     |

### **TABLES**

| Table | #                                                               | Page i |

|-------|-----------------------------------------------------------------|--------|

| 1     | J3 Connector Pin Assignments                                    | 7      |

| 2     | Drive Selection Matrix (Serial Mode)                            |        |

| 3     | Control Cable (J1/P1) Pin Assignments (Disk Drive-Serial Mode). | 9      |

| 4     | Data Cable (J2/P2) Pin Assignments (Disk Drive-Serial Mode)     | 10     |

| 5     | Command (CMD) Data Definition                                   | 13     |

| 6     | Request Configuration Modifier Bits (Disk Drive)                | . 14   |

| 7     | Control Command Modifier Bits (Disk Drive)                      |        |

| 8     | Data Strobe Command Modifier Bits (Disk Drive)                  | . 15   |

| 9     | Track Offset Command Modifier Bits (Disk Drive)                 | . 16   |

| 10    | General Configuration Response Bits (Disk Drive)                | . 20   |

| 11    | Specific Configuration Response Bits (Disk Drive)               | . 20   |

| 12    | Standard Status Response Bits (Disk Drive)                      | . 21   |

| 13    | Control Cable (J1/P1) Pin Assignments (Disk Drive-Step Mode)    | . 44   |

| 14    | Data Cable (J2/P2) Pin Assignments (Disk Drive-Step Mode)       | . 45   |

| 15    | Control Cable (J1/P1) Pin Assignments (Tape Drive)              | . 73   |

| 16    | Data Cable (J2/P2) Pin Assignments (Tape Drive)                 | . 74   |

| 17    | Command (CMD) Data Definition (Tape Drive)                      | . 77   |

| 18    | Request Configuration Modifier Bits (Tape Drive)                | . 79   |

| 19    | Deck Control Command Modifier Bits (Tape Drive)                 | . 79   |

| 20    | Read Command Modifier Bits (Tape Drive)                         | . 80   |

| 21    | Space Froward/Reverse Command Modifier Bits (Tape Drive)        |        |

| 22    | Fast Position EOT/BOT Command Modifier Bits (Tape Drive)        | . 82   |

| 23    | Write Command Modifier Bits (Tape Drive)                        | . 82   |

| 24    | Erase Fixed Length Command Modifier Bits (Tape Drive)           | . 83   |

| 25    | General Configuration Response Bits (Tape Drive)                | . 86   |

| 26    | Standard Status Response Bits (Tape Drive)                      | . 87   |

#### 1.0 SCOPE

This document defines the Enhanced Small <u>Device</u> Interface (ESDI) specification. It represents the merging of the the Enhanced Small Disk Interface specification and the Enhanced Small Tape Interface specification.

The general portions covering electrical and physical interfacing can be found in sections 2.0 through 4.0. Specific information concerning interfacing of disk drives can be found in Section 5.0 mode implementation) and Section 6.0 (Step mode implementation) while specific information concerning interfacing of tape drives can be found in Section 7.0. Either Section 5.0, 6.0, or 7.0 may be implemented independently of the other or combined if so desired.

The primary objectives in developing this specifications was to:

- (1) provide a low cost, high performance interface definition suitable for the smaller, high performance memory devices currently being produced,

- (2) develop a standard which could support higher data transfer rates as well as provide for additional performance features that are desireable on higher performance systems.

- (3) provide a single interface definition which could effectively support both disk and tape drives on the same controller.

In order to accommodate a number of product types, the specification defines several alternatives.

For the disk portion, two implementations are possible: Serial (Section 5.0) and Step (Section 6.0).

The Serial mode of operation utilizes NRZ data transfer along with serial commands and serial configuration and status reporting across the command cable (J1).

The Step mode implementation utilizes the same NRZ data transfer; however, the STEP and DIRECTION lines are used to cause actuator motion. Hence, configuration and status reporting are unavailable over the interface.

This specification does not require that both of these modes be available on any drive; rather, it is the choice of the disk drive manufacturer which mode to implement. If desired, both modes may be offered with a selection method provided by the manufacturer.

### **COMMENTS**

This specification describes the Industry Standard ESDI (Enhanced Small Disk Interface) and is reproduced in it's original form as developed by the ESDI Committee.

Reference by Control Data to the ESDI specifies the parameters outlined in this document. CDC Products supporting the ESDI are designed to this specification. Any variation from this specification by a CDC ESDI Product will be noted in detail by the respective Product Specification.

Section 7.0 of the specification provides for the attachment of either streaming or start/stop tape drives to the same ESDI controller. Because of the characteristics of tape devices, only a serial mode of implementation is supported.

Both the physical and logical interface characteristics of tape and disk drives have been included in these specifications. Certain design considerations were made to allow optimized operation of the disk drive with a tape device. For exmaple, simultaneous disk and tape access is possible allowing direct disk-to-tape transfers to occur without host intervention. Provision for multiple radial data channels has been provided to enhance the intra-device data transfer rates. This specification supports cable lengths of up to three meters (9.8 feet).

#### 2.0 GENERAL DESCRIPTION

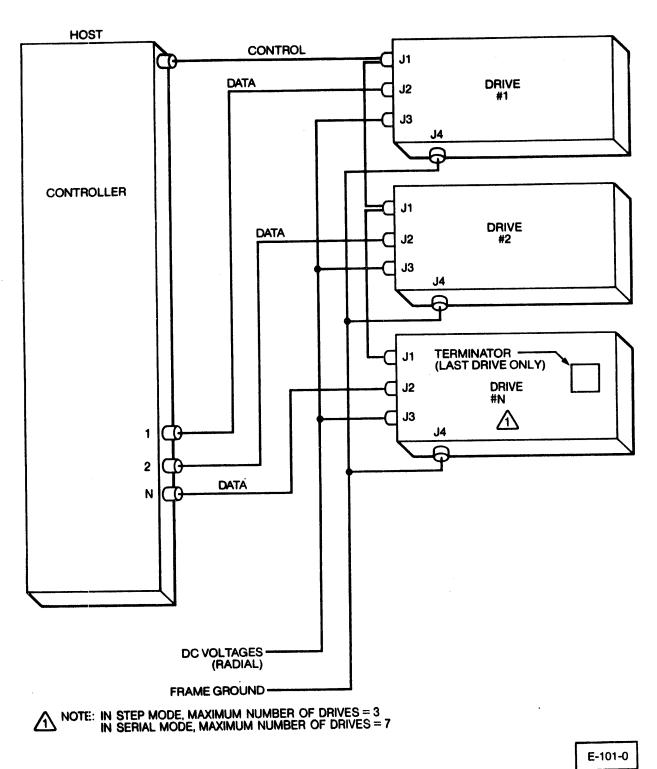

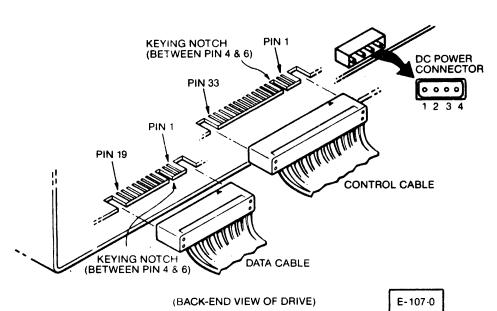

The Enhanced Small Device Interface consists of a control cable and a data cable. The control cable allows for a daisy chain connection of up to three disk drives (in STEP mode) and up to seven disk and tape drives (in SERIAL mode) with only the last drive being terminated. See Figure 1. The data cable must be attached in a radial configuration.

#### 3.0 **ELECTRICAL INTERFACE**

The Enhanced Small Device Interface can be divided into three categories, each of which is physically separated.

- 1. Control signals.

- 2. Data signals

- 3. DC power.

All control lines are digital in nature (open collector TTL) and either provide signals to the drive (input) or signals to the host (output). The data transfer signals are differential in nature and provide data either to (write) or from (read) the drive.

TYPICAL CONNECTION, MULTIPLE DRIVE SYSTEM FIGURE 1

APRIL 18, 1984

#### 3.1 Control Signal Drivers and Receivers

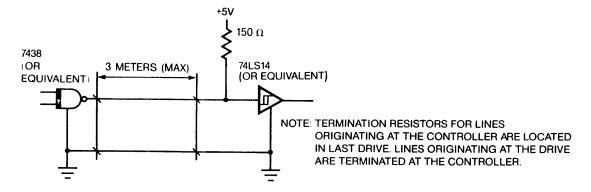

The drivers have the following electrical specifications. Refer to Figure 2 for the recommended circuit.

TRUE/ACTIVE: 0.0 VDC to 0.4 VDC @ I= -48mA (Max)

FALSE/DEACTIVE: 2.5 VDC to 5.25 VDC @ I= +250 uA (Open Collector)

CONTROL SIGNALS

DRIVER/RECEIVER COMBINATION

FIGURE 2

#### 3.2 Data Line Drivers and Receivers

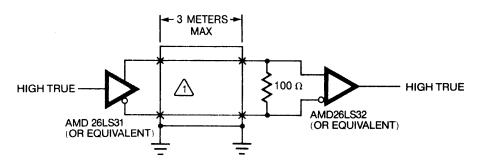

The data drivers and receivers are differential in nature. The recommended circuit is shown in Figure 3.

$Z = 105~\Omega$  FLAT RIBBON OR TWISTED PAIR

E-102-1

E-103-0

## DATA LINE DRIVER/RECEIVER COMBINATION FIGURE 3

REVISION D

Γ 4 7

APRIL 18, 1984

#### 4.0 PHYSICAL INTERFACE

The electrical interface between the drive and the host controller is via four connectors:

- J1 Control signals (multiplexed)

- 2. J2 Read/write signals (radial)

- 3. J3 DC power input

- 4. J4 Frame ground

#### 4.1 J1/P1 Connector

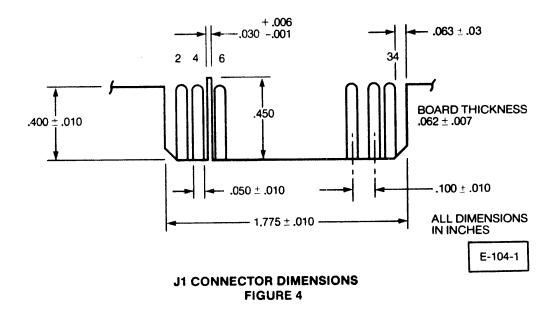

Connection to J1 is via a 34 pin PCB edge connector. The dimensions for this connector are shown in Figure 4. The pins are numbered 1 through 34 with the even pins located on one side of the PCB. A key slot is provided between pins 4 and 6. The recommended mating connector for P1 is AMP ribbon connector P/N 88373-3 or equivalent. See Figure 7 for connector orientation.

#### 4.2 J2/P2 Connector

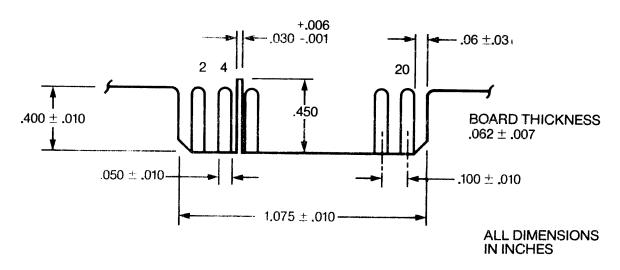

Connection of J2 is via a 20 pin PCB edge connector. The dimensions for the connector are shown in Figure 5. The pins are numbered 1 through 20 with the even pins located on one side of the PCB. The recommended mating connector for P2 is AMP ribbon connector P/N 88373-6 or equivalent. A key slot is provided between pins 4 and 6. See Figure 7 for orientation.

E-105-1

#### J2 CONNECTOR DIMENSIONS FIGURE 5

#### 4.3 J3/P3 Connector

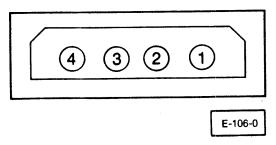

The DC power connector (J3), is a 4 pin AMP MATE-N-LOCK connector P/N 350543-1. An alternate connector is AMP MATE-N-LOCK P/N 641737-1 (right angle). The recommended mating connector (P3) is AMP P/N 1-480424-0 utilizing AMP pins P/N 350078-4 (strip) or P/N 61173-4 (loose piece). Equivalents of these part numbers are permissible. J3 pins are numbered as shown in Figure 6. Pin assignments are shown in Table 1. See Figure 7 for connector orientation.

#### 4.4 J4/P4 Frame Ground Connector

The frame ground connection is a Faston type connection, AMP P/N 61761-2 or equivalent. The recommended mating connection is AMP 62187-1 or equivalent. If wire is used, the hole in J4 will accommodate a wire size of 18AWG maximum.

REVISION D

J3 CONNECTOR FIGURE 6

| J3 CONNECTOR PIN | VOLTAGE      |

|------------------|--------------|

| 1                | +12V DC ±5%  |

| 2                | 12V RETURN   |

| 3                | 5V RETURN    |

| . 4              | + 5V DC + 5% |

E-106-0

#### J3 CONNECTOR PIN ASSIGNMENTS TABLE 1

TYPICAL PCB CONNECTOR ORIENTATION FIGURE 7

APRIL 18, 1984

#### 5.0 DISK DRIVE IMPLEMENTATION -- SERIAL MODE

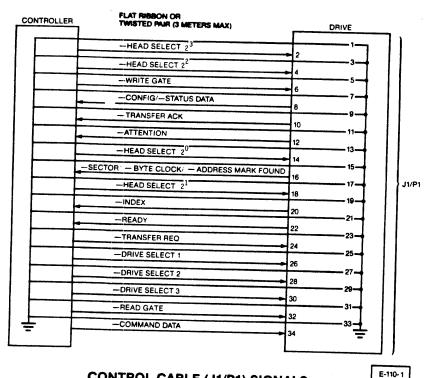

This section describes the interface lines, hardware, and interface protocols necessary to implement the SERIAL mode disk drive version of the ESDI. Pin assignments for connectors J1 and J2 are shown in Figures 9 and 10 along with Tables 3 and 4.

#### 5.1 Control Input Lines

The control input signals are of two types: those to be multiplexed in a multiple drive system and those intended to do the multiplexing. The control input signals to be multiplexed are WRITE GATE, READ GATE, HEAD SELECT  $2^0$ , HEAD SELECT  $2^0$ , HEAD SELECT  $2^0$ , HEAD SELECT  $2^0$ , TRANSFER REQ and COMMAND DATA. The signals to do the multiplexing are DRIVE SELECT 1, DRIVE SELECT 2, and DRIVE SELECT 3.

ADDRESS MARK ENABLE is a control input in the radial cable. It is not multiplexed.

NOTE: Any lines not used should be terminated.

#### 5.1.1 Drive Select

The three DRIVE SELECT lines are to be decoded for drive select. Decode 000 shall be a no select. See Figure 8 and Table 2.

|                                   | E-108-0 |

|-----------------------------------|---------|

| DRIVE SELECT TERMINATION FIGURE 8 |         |

| DRIVE<br>SELECTED                  | DRIVE<br>SELECT<br>3  | DRIVE<br>SELECT<br>2  | DRIVE<br>SELECT<br>1  |

|------------------------------------|-----------------------|-----------------------|-----------------------|

| NONE<br>1<br>2<br>3<br>4<br>5<br>6 | 0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>0<br>0 | 0<br>1<br>0<br>1<br>0 |

DRIVE SELECTION MATRIX

TABLE 2

CONTROL CABLE (J1/P1) SIGNALS (DISK IMPLEMENTATION - SERIAL MODE) FIGURE 9

| SIGNAL NAME                             | SIGNAL<br>PIN | GROUND |

|-----------------------------------------|---------------|--------|

| -HEAD SELECT 2 <sup>3</sup>             | 2             |        |

| -HEAD SELECT 2 <sup>2</sup>             | _             | 1      |

| -WRITE GATE                             | 4             | 3      |

| -CONFIG/-STATUS DATA                    | 6             | 5      |

| -TRANSFER ACK                           | 8             | 7      |

| -ATTENTION                              | 10            | 9      |

| -HEAD SELECT 20                         | 12            | 11     |

| -SECTOR/-BYTE CLOCK/-ADDRESS MARK FOUND | 14            | 13     |

| -HEAD SELECT 21                         | 16            | 15     |

| -INDEX                                  | 18            | 17     |

| -READY                                  | 20            | 19     |

| -TRANSFER REQ                           | 22            | 21     |

| -DRIVE SELECT 1                         | 24            | 23     |

|                                         | 26            | 25     |

| -DRIVE SELECT 2                         | 28            | 27     |

| -DRIVE SELECT 3                         | 30            | 29     |

| —READ GATE                              | 32            | 31     |

| COMMAND DATA                            | 34            | 33     |

|                                         |               | ~      |

|                                         |               |        |

CONTROL CABLE (J1/P1) PIN ASSIGNMENTS (DISK IMPLEMENTATION - SERIAL MODE) TABLE 3

E-111-1

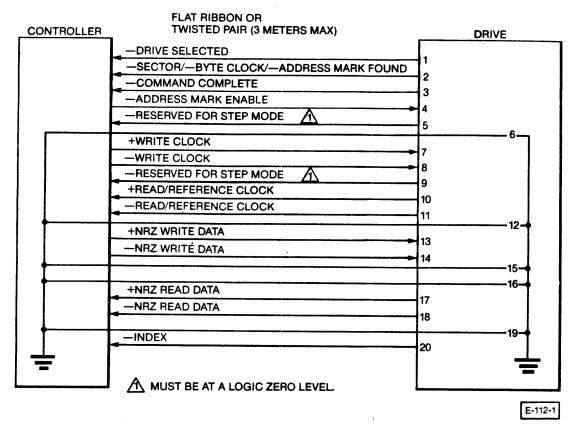

#### DATA CABLE (J2/P2) SIGNALS (DISK IMPLEMENTATION - SERIAL MODE) FIGURE 10

| SIGNAL NAME                           | SIGNAL<br>PIN | GROUND   |

|---------------------------------------|---------------|----------|

| DRIVE SELECTED                        | 1             |          |

| -SECTOR-BYTE CLOCK-ADDRESS MARK FOUND | 2             |          |

| -SEEK COMPLETE                        | 3             |          |

| -ADDRESS MARK ENABLE                  | 4             |          |

| -RESERVED FOR STEP MODE               | 5             | 6        |

| +/WRITE CLOCK                         | 7/8           |          |

| RESERVED FOR STEP MODE                | 9             |          |

| +/—READ REF CLOCK                     | 10/11         | 12       |

| +/—NRZ WRITE DATA                     | 13/14         | 15/16    |

| +/—NRZ READ DATA                      | 17/18         | 19       |

| —INDEX                                | 20            |          |

|                                       |               | E-113- 1 |

# DATA CABLE (J2/P2) PIN ASSIGNMENTS (DISK IMPLEMENTATION - SERIAL MODE) TABLE 4

## 5.1.2 <u>Head Select 2<sup>0</sup>, 2<sup>1</sup>, 2<sup>2</sup>, and 2<sup>3</sup></u>

These four lines allow selection of each individual read/write head in a binary coded sequence. HEAD SELECT 20 is the least significant line. Heads are numbered 0 through 15. When all HEAD SELECT lines are high (inactive), head 0 will be selected. Addressing more than 16 heads is allowed by use of the SELECT HEAD GROUP command.

Head addressing is continuous from 0 through both removeable and fixed drives. If removeable drive is present, head 0 will be on the removeable media drive.

Addressing more heads than contained in the drive will result in a write fault when attempting to perform a write operation.

A 150 OHM resistor pack allows for line termination.

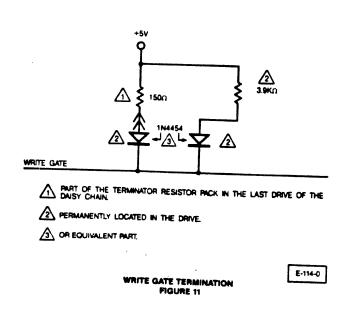

#### 5.1.3 Write Gate

The active state of this signal, or low level, enables write data to be written on the disk.

The high to low transition of this signal creates a write splice and initiates the writing of the data PLO Sync field by the drive. See Figures 23 and 25. When formatting, WRITE GATE should be deactivated for 2 bit times minimum between the address area and the data area to identify to the drive the beginning of the data PLO sync field.

This line shall be protected from terminator power loss by implementation of the circuit shown in Figure 11.

#### 5.1.4 Read Gate

The active state of this signal, or low level, enables data to be read from the disk. This signal should become active only during a PLO sync field and at least the number of bytes defined by the drive prior to the ID or Data Sync Bytes. The PLO sync field length is determined by the response to the REQUEST PLO SYNC FIELD LENGTH command. Read gate must be false when passing over a write splice area.

A 150 OHM resistor pack allows for line termination.

#### 5.1.5 Command Data

When presenting a command, 16 information bits of serial data, plus parity, will be presented on this line. This data is to be controlled by the handshake protocol with signals TRANSFER REQ and TRANSFER ACK. Upon receipt of this serial data, the drive will perform the required function as specified by the bit configuration. Data is transmitted MSB first. See Table 5 for the meaning of the various bit combinations. See Figure 12A for timing.

The parity utilized in all commands shall be odd. The parity bit shall be a "1" when the number of "1's" in a 16 bit command is an even number. The number of "1" bits in the command, plus parity, shall be an odd number.

No communications should be attempted unless the COMMAND COMPLETE line is true. Note: This line must be at a logic 0 when not in use.

A 150 OHM resistor pack allows for line termination.

MOST SIGNIFICANT BIT LEAST SIGNIFICANT

| 15 | 14           | 13   | 12 | 11 | 10           | 9  | 8    | 7    | 6  | 5         | 4 | 3 | 2 | 1 | 0 | Р |

|----|--------------|------|----|----|--------------|----|------|------|----|-----------|---|---|---|---|---|---|

| CN | CMD FUNCTION |      |    |    | CMD MODIFIER |    |      |      |    | ALL ZEROS |   |   |   |   |   | Р |

| CN | 1D FU        | NCTI |    |    |              | CI | MD I | PARA | ME | ΓER       |   |   |   |   | Ρ |   |

BIT P: PARITY (ODD)

#### COMMAND DATA WORD STRUCTURE FIGURE 12B

E-116-0

| CMD<br>FUNCTION<br>BIT 15 14 13 12                                        | CMD<br>FUNCTION<br>DEFINITION                                                                      | CMD<br>MODIFIER<br>APPLICABLE<br>(BITS 11-8) | CMD<br>PARAMETER<br>APPLICABLE<br>(BITS 11-0) | STATUS/CONFIGURATION DATA<br>RETURNED TO CONTROLLER |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------|-----------------------------------------------------|

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1<br>0 1 0 0                       | SEEK RECALIBRATE REQUEST STATUS REQUEST CONFIGURATION SELECT HEAD GROUP (OPTIONAL)                 | NO<br>NO<br>YES<br>YES<br>NO                 | YES<br>NO<br>NO<br>NO<br>YES                  | NO<br>NO<br>YES<br>YES<br>NO                        |

| 0 1 0 1<br>0 1 1 0<br>0 1 1 1<br>1 0 0 0                                  | CONTROL DATA STROBE OFFSET TRACK OFFSET INITIATE DIAGNOSTICS (OPTIONAL)                            | YES<br>YES<br>YES<br>NO                      | 20<br>20<br>20<br>20<br>20<br>20              | NO<br>NO<br>NO<br>NO                                |

| 1 0 0 1<br>1 0 1 0<br>1 0 1 1<br>1 1 0 0<br>1 1 0 1<br>1 1 1 0<br>1 1 1 1 | RESERVED | NO<br><br><br><br><br>                       | YES                                           | NO                                                  |

NOTES: 1. ALL UNUSED OR NOT APPLICABLE LOWER ORDER BITS MUST BE ZERO.

2. ANY "RESERVED" OR COMMAND FUNCTION RECEIVED SHALL BE TREATED AS AN INVALID COMMAND.

3. SIMULTANEOUS DATA STROBE AND TRACK OFFSETS ARE ALLOWED BY MULTIPLE COMMANDS.

E-117-0

**COMMAND (CMD) DATA DEFINITION** TABLE 5

REVISION D [ 13 ]

#### 5.1.5.1 Command Data bits 15 thru 12 decode definition

<u>SEEK (0000):</u> This command causes the drive to seek to the cylinder indicated in Bits 0 thru 11. A SEEK command will restore data strobe and track offsets to zero.

RECALIBRATE (0001): This command causes the actuator to return to cylinder 0000. A RECALIBRATE command will restore data strobe and track offsets to zero.

REQUEST STATUS (0010): This command causes the drive to send 16 bits (see Table 12, page 21) of standard or vendor unique status information to the controller as determined by the command modifier bits. The parity utilized in all status responses shall be odd.

Request Standard Status: When the command modifier bits (11-8) of the REQUEST STATUS command is 0000, the drive will respond with 16 bits of standard status. Bits 15-12 of this status are defined as state bits which do not cause ATTENTION to be asserted. Bits 11-0 of this status are fault or change of status bits that cause ATTENTION to be asserted each time one is set. See section 5.2.3.2 for response protocol and format of the status response from the drive.

Request Vendor Unique Status: When the command modifier bits (11-8) of the REQUEST STATUS command is 0001 through 1111, the drive responds with vendor unique status (undefined in this specification). The number of words available is specified by configuration data. Each word of vendor unique status is requested using a different command modifier configuration. This command modifier for the first word is 0001 and subsequent words are requested by incrementing the command modifier.

REQUEST CONFIGURATION (0011): This command causes the drive to send 16 bits (Table 10 and 11, page 20) of configuration data to the controller. The parity utilized in all configuration responses shall be odd. The specific configuration requested is specified by bits 11-8 of the command as shown below in Table 6:

| COMM | COMMAND MODIFIER BITS |   |   | FUNCTION                                          |

|------|-----------------------|---|---|---------------------------------------------------|

| 11   | 10                    | 9 | 8 |                                                   |

| 0    | 0                     | 0 | 0 | GENERAL CONFIGURATION OF DRIVE AND FORMAT         |

| 0    | 0                     | 0 | 1 | NUMBER OF CYLINDERS, FIXED                        |

| 0    | 0                     | 1 | 0 | NUMBER OF CYLINDERS, REMOVABLE                    |

| 0    | 0                     | 1 | 1 | NUMBER OF HEADS                                   |

| 0    | 1                     | 0 | 0 | MINIMUM UNFORMATTED BYTES PER TRACK               |

| 0    | 1                     | 0 | 1 | UNFORMATTED BYTES PER SECTOR (HARD SECTOR ONLY)   |

| 0    | 1                     | 1 | 0 | SECTORS PER TRACK (HARD SECTOR ONLY)              |

| 0    | 1                     | 1 | 1 | MINIMUM BYTES IN ISG FIELD*                       |

| 1    | 0                     | 0 | 0 | MINIMUM BYTES PER PLO SYNC FIELD                  |

| 1    | 0                     | 0 | 1 | NUMBER OF WORDS OF VENDOR UNIQUE STATUS AVAILABLE |

<sup>\*</sup>NOT INCLUDING INTERSECTOR SPEED TOLERANCE

E-118-0

## REQUEST CONFIGURATION MODIFIER BITS TABLE 6

SELECT HEAD GROUP (0100): This optional command causes the drive to select a group of 16 heads. Heads 0-15 are considered as group 0. Bits 7-4 are used to indicate the group to be selected. Bit 4, if a one, causes head group 1 (heads 16-31) to be selected. Bit 5 will cause head group 2 to be selected. The individual head selected within each group is controlled by the four head select lines.

<u>CONTROL (0101)</u>: This command causes the control operations specified by bits 11-8 to be performed as shown below in Table 7:

| COMM | COMMAND MODIFIER BITS |   |   | FUNCTION                                                   |

|------|-----------------------|---|---|------------------------------------------------------------|

| 11   | 10                    | 9 | 8 |                                                            |

| 0    | 0                     | 0 | 0 | RESET INTERFACE ATTENTION AND STANDARD STATUS (BITS 0- 11) |

| 0    | 0                     | 0 | 1 | RESERVED                                                   |

| 0    | 0                     | 1 | 0 | STOP SPINDLE MOTOR (OPTIONAL)                              |

| 0    | 0                     | 1 | 1 | START SPINDLE MOTOR (OPTIONAL)                             |

| 0    | 1                     | 0 | 0 | RESERVED                                                   |

| 0    | 1                     | 0 | 1 | RESERVED                                                   |

| 0    | 1                     | 1 | 0 | RESERVED                                                   |

| 0    | 1                     | 1 | 1 | RESERVED                                                   |

| 1    | ×                     | × | X | RESERVED                                                   |

E-119-1

## CONTROL COMMAND MODIFIER BITS TABLE 7

<u>DATA STROBE OFFSET (0110):</u> This optional command causes the drive to offset the data strobe in the direction and amount specified by Bits 11-8 as shown below in Table 8:

| COMM | IAND M | ODIFIE | R BITS | FUNCTION            |

|------|--------|--------|--------|---------------------|

| 11   | 10     | 9      | 8      |                     |

| 0    | 0      | 0      | 0      | RESTORE OFFSET TO 0 |

| 0    | 0      | 0      | 1      | RESTORE OFFSET TO 0 |

| 0    | 0      | 1      | 0      | EARLY OFFSET 1      |

| 0    | 0      | 1      | 1      | LATE OFFSET 1       |

| 0    | 1      | 0      | 0      | EARLY OFFSET 2      |

| 0    | 1      | O      | 1 1    | LATE OFFSET 2       |

| 0    | 1      | 1      | 0      | EARLY OFFSET 3      |

| 0    | 1      | 1      | 1      | LATE OFFSET 3       |

| 1    | ×      | ×      | X      | RESERVED            |

## DATA STROBE COMMAND MODIFIER BITS TABLE 8

E-120-0

Seek or recalibrate commands restore offsets to zero. Simultaneous Data Strobe and Track offsets are allowed by use of multiple commands.

REVISION D

[ 15 ]

TRACK OFFSET (0111): This optional command causes the drive to perform a track offset in the direction and amount specified by Bits 11-8 as shown below in Table 9:

| COMM        | AAND N           | IODIFI      | R BITS           | FUNCTION                                                                                                        |

|-------------|------------------|-------------|------------------|-----------------------------------------------------------------------------------------------------------------|

| 11          | 10               | 9           | 8                |                                                                                                                 |

| 0 0 0 0     | 0<br>0<br>0<br>1 | 0 0 1 1 0 0 | 0<br>1<br>0<br>1 | RESTORE OFFSET TO 0 RESTORE OFFSET TO 0 POSITIVE OFFSET 1 NEGATIVE OFFSET 1 POSITIVE OFFSET 2 NEGATIVE OFFSET 2 |

| 0<br>0<br>1 | 1<br>1<br>X      | 1<br>1<br>X | 0<br>1<br>X      | POSITIVE OFFSET 3 NEGATIVE OFFSET 3 RESERVED                                                                    |

## TRACK OFFSET COMMAND MODIFIER BITS TABLE 9

E-121-1

Seek and recalibrate commands restore offsets to zero. Simultaneous Track and Data Strobe offsets are allowed by use of multiple commands.

Drives that implement only one value of offset, Data Strobe or Track, shall respond to unimplemented offset commands as a legal offset function.

INITIATE DIAGNOSTICS (1000): This optional command causes the drive to perform internal diagnostics. COMMAND COMPLETE indicates the completion of the diagnostics. ATTENTION with COMMAND COMPLETE indicates that a fault was encountered and status should be requested to determine the proper course of action.

<u>SET UNFORMATTED BYTES PER SECTOR (1001)</u>: This optional command causes the drive to set the number of unformatted bytes per sector indicated in bits 11-0 (if implemented). This command is valid only if the drive is configured to be in the drive hard sectored mode. This command is used only if the drive uses a settable counter for the number of bytes per sector and that counter is controllable from the interface.

CODES 1010 THRU 1111: Codes reserved for future definition.

## 5.1.6 <u>Transfer Request</u> (Transfer Req)

This line functions as a handshake signal in conjunction with TRANSFER ACK during command and configuration/status transfers. See Figures 12A, page 12, and Figure 13, page 17 for timing.

#### 5.1.7 Address Mark Enable

This signal, when active with Write Gate, causes an Address Mark to be written. ADDRESS MARK ENABLE shall be active for 24 bit times. See Figure 14 for timing. The address mark written shall be left to the drive manufacturer's discretion.

ADDRESS MARK ENABLE, when active without WRITE GATE or READ GATE, causes a search for Address Marks. If WRITE GATE is true, the low to high transition, or deassertion, of this signal causes the drive to begin writing the ID PLO Sync field. See Figures 23, page 37, and Figure 25, page 40.

This line must be permanently terminated in the drive. See figure 2.

In fixed sector drives, ADDRESS MARK ENABLE does not cause an Address Mark to be written on the media. The trailing edge of ADDRESS MARK ENABLE with WRITE GATE true initiates the writing of the header PLO sync field.

#### 5.2 Control Output Lines

The output control signals are driven with an open collector output stage capable of sinking a maximum of 48mA at low level or true state with maximum voltage of 0.4V measured at the driver. When the line driver is in the high level or false state, the driver transistor is off and collector leakage current is a maximum of 250uA.

All J1 output lines are enabled by their respective DRIVE SELECT decodes.

Figure 2 shows the recommended circuit.

#### 5.2.1 Drive Selected

A status line provided at the J2/P2 connector to inform the host system of the selection status of the drive. The DRIVE SELECTED line is driven by a TTL open collector driver as shown in Figure 2. This signal will go active only when the drive is selected as defined in section 5.1.1. (page 8). The DRIVE SELECT lines at J1/PI are activated by the host system.

#### 5.2.2 Ready

This signal indicates that the spindle is up to speed. This interface signal when true, together with COMMAND COMPLETE indicates that the drive is ready to read, write or, seek. When the line is false, all writing and seeking is inhibited.

#### 5.2.3 Configuration/Status Data (Config/Status)

The drive presents serial data on this line upon request from the controller. See Figure 16 for typical operation. This config-status serial data will be presented to the interface and transferred using the handshake protocol with signals TRANSFER REQ and TRANSFER ACK. See Figure 13. Once initiated, 16 bits plus parity will be transmitted MSB first. The parity utilized shall be odd.

REVISION D [ 19 ] APRIL 18, 1984

#### 5.2.3.1 Configuration Response Bits

In response to the REQUEST CONFIGURATION command (see section 5.1.5.1 page 14) 16 bits of configuration information is returned to the controller.

If the command modifier bits (11-8) were 0000, the general configuration status information shown below is returned.

| BIT<br>POSITION | FUNCTION                                 |

|-----------------|------------------------------------------|

| 15              | TAPE DRIVÉ                               |

| 14              | FORMAT SPEED TOLERANCE GAP REQUIRED      |

| 13              | TRACK OFFSET OPTION AVAILABLE            |

| 12              | DATA STROBE OFFSET OPTION AVAILABLE      |

| 11              | ROTATIONAL SPEED TOLERANCE IS >0.5%      |

| 10              | TRANSFER RATE > 10MHz                    |

| 9               | TRANSFER RATE >5MHz ≤10MHz               |

| 8               | TRANSFER RATE ≤5MHz                      |

| 7               | REMOVABLE CARTRIDGE DRIVE                |

| 6               | FIXED DRIVE                              |

| 5               | SPINDLE MOTOR CONTROL OPTION IMPLEMENTED |

| 4               | HEAD SWITCH TIME >15μs*                  |

| 3               | RLL ENCODED (NOT MFM)                    |

| 2               | CONTROLLER SOFT SECTORED (ADR MARK)      |

| 1               | DRIVE HARD SECTORED (SECTOR PULSES)      |

| 0               | CONTROLLER HARD SECTORED (BYTE CLOCK)    |

<sup>\*</sup>COMMAND COMPLETE MUST BE DEACTIVATED WITHIN 15µsec OF A HEAD CHANGE

## GENERAL CONFIGURATION RESPONSE BITS TABLE 10

E-125-1

If other command modifier bits were used, the specific configuration information shown below is returned for each CONFIGURATION command with those modifiers.

| COMM | COMMAND MODIFIER BITS |   |   | CONFIGURATION RESPONSE                                                                                                                                  |

|------|-----------------------|---|---|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | 10                    | 9 | 8 |                                                                                                                                                         |

| 0    | 0                     | 0 | 1 | NUMBER OF CYLINDERS, FIXED                                                                                                                              |

| 0    | 0                     | 1 | 0 | NUMBER OF CYLINDERS, REMOVABLE (ZERO IF NOT REMOVABLE MEDIA DRIVE)                                                                                      |

| 0    | 0                     | 1 | 1 | NUMBER OF HEADS BIT\$ 15-8: REMOVABLE DRIVE HEADS BIT\$ 7-0: FIXED HEADS                                                                                |

| 0    | 1                     | 0 | 0 | MINIMUM UNFORMATTED BYTES PER TRACK                                                                                                                     |

| 0    | 1                     | 0 | 1 | UNFORMATTED BYTES PER SECTOR (HARD SECTOR ONLY)                                                                                                         |

| 0    | 1                     | 1 | 0 | SECTORS PER TRACK (DRIVE HARD SECTOR ONLY) BITS 15-8: SPARE BITS 7-0: SECTORS PER TRACK                                                                 |

| 0    | 1                     | 1 | 1 | MINIMUM BYTES IN ISG FIELD (NOT INCLUDING INTERSECTOR SPEED TOLERANCE)  BIT\$ 15-8: ISG BYTES AFTER INDEX                                               |

|      | 1                     | 1 | i | BITS 7-0: BYTES PER ISG                                                                                                                                 |

| 1    | 0                     | 0 | 0 | MINIMÜM BYTES PER PLO SYNC FIELD BITS 15-8: SPARE                                                                                                       |

| 1    | 0                     | 0 | 1 | BIT\$ 7-0: BYTES PER PLO SYNC FIELD NUMBER OF WORDS OF VENDOR UNIQUE STATUS AVAILABLE BIT\$ 15-4: SPARE BIT\$ 3-0: NUMBER OF VENDOR UNIQUE STATUS WORDS |

E-126-1

## SPECIFIC CONFIGURATION RESPONSE BITS TABLE 11

REVISION D [ 20 ] APRIL 18, 1984

#### 5.2.3.2 Status Response Bits

In response to the REQUEST STATUS command (See section 5.1.5.1, page 14) 16 bits of status information is returned to the controller.

Bits 15-12 of the status are defined as state bits which do not cause ATTENTION to be asserted. Bits 11-0 are fault or change of status bits that cause ATTENTION to be asserted.

| BIT<br>POSITION | FUNCTION                                         |

|-----------------|--------------------------------------------------|

| 15              | RESERVED                                         |

| 14              | REMOVABLE MEDIA NOT PRESENT                      |

| 13              | WRITE PROTECTED, REMOVABLE MEDIA                 |

| 12              | WRITE PROTECTED, FIXED MEDIA                     |

| 11              | RESERVED                                         |

| 10              | RESERVED                                         |

| 9               | SPINDLE MOTOR STOPPED*                           |

| 8               | POWER ON RESET CONDITIONS EXIST (RECONFIGURATION |

|                 | OR START SPINDLE MOTOR COMMAND MAY BE REQUIRED   |

| 7               | COMMAND DATA PARITY FAULT                        |

| 6               | INTERFACE FAULT                                  |

| 5               | INVALID OR UNIMPLEMENTED COMMAND FAULT           |

| 4               | SEEK SAULT                                       |

| 3               | WRITE GATE WITH TRACK OFFSET FAULT               |

| 2               | VENDOR UNIQUE STATUS AVAILABLE                   |

| 1               | WRITE FAULT **                                   |

| 0               | REMOVABLE MEDIA CHANGED (REMOVABLE MEDIA         |

|                 | HAS BEEN CHANGED SINCE LAST STATUS REQ)          |

<sup>\*</sup>SPINDLE MOTOR IS STOPPED DUE TO PREVIOUS COMMAND TO STOP OR THE DRIVE IS IN POWER ON RESET CONDITION.

- a. Write current in a head without WRITE GATE active or no write current with WRITE GATE active and the drive selected.

- $t. \ \mbox{Multiple}$  heads selected, no head selected, or improperly selected with WRITE GATE active.

- c. WRITE GATE active to a write protected drive.

- d. Simultaneous activation of READ GATE and WRITE GATE.

E-127-1

## STANDARD STATUS RESPONSE BITS TABLE 12

<sup>\*\*</sup> CONDITIONS THAT CAN CAUSE WRITE FAULT ARE:

COMMAND COMPLETE IS DEACTIVATED FOR ALL COMMANDS TO THE DRIVE.

COMMAND COMPLETE IS ACTIVATED TO SIGNIFY COMPLETION OF EXECUTION OF A COMMAND. APPLICABLE FOR ALL COMMANDS.

COMMAND COMPLETE IS ACTIVATED TO SIGNIFY COMPLETION OF THE REQUESTED CONFIGURATION/STATUS TRANSFER.

APPLICABLE FOR ALL REQUEST STATUS AND CONFIGURATION COMMANDS.

IF AN ERROR WAS ENCOUNTERED DURING THE CURRENT COMMAND, ATTENTION MUST BE ACTIVATED AT LEAST 100 ns BEFORE COMMAND COMPLETE IS ACTIVATED.

E-128-0

TYPICAL SERIAL OPERATION(S)

FIGURE 16

#### 5.2.4 <u>Transfer Acknowledge (Transfer Ack)</u>

This signal functions as a handshake signal along with TRANSFER REQ during COMMAND and CONFIGURATION-STATUS transfers. See Figures 12A and 13.

#### 5.2.5 Attention

This output is asserted when the drive wants the controller to request its standard status. Generally, this is a result of a fault condition or a change of status. Writing is inhibited when ATTENTION is asserted. ATTENTION is deactivated by the Reset Interface Attention command (section 5.1.5.1).

#### 5.2.6 <u>Index</u>

This pulse is provided by the drive once each revolution to indicate the beginning of a track. Normally, this signal is high and makes the transition to low to indicate INDEX. Only the transition at the leading edge of the pulse is accurately controlled. The period (T) of this signal is the reciprocal of the rotational speed, Figure 17. This signal is available on the command cable J1/P1 (gated) and on the data cable J2/P2 (ungated).

#### 5.2.7 Sector/Byte Clock/Address Mark Found

These three signals are mutually exclusive and therefore may share this line. The signal that is used is determined by the NRZ data transfer control implementation. These signals are available on the command cable J1/P1 (gated) and on the data cable J2/P2 (ungated). One of these three signals must be implemented by the drive manufacturer.

#### 5.2.7.1 Sector (Drive Hard Sector)

This optional interface signal indicates the start of a sector. No short sectors are allowed. The leading edge of the sector pulses is the only edge that is accurately controlled. The index pulse indicates sector zero. See Figure 18.

#### 5.2.7.2 Byte Clock (Controller Hard Sector)

This signal occurs once per every eight Reference clock periods. This signal is provided for the controller to count the desired number of Byte Clocks to determine the sector size and beginning sector locations. The inter-relationship of INDEX and BYTE CLOCK is shown in Figure 19. This signal is continuously transmitted if the disk is up to speed and the heads are positioned over the recording zone of the This clock does not have a fixed phase relationship to the recorded data.

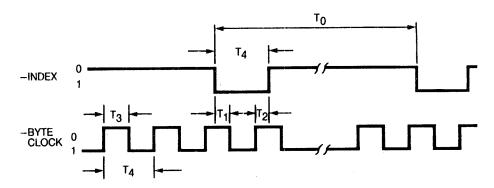

T<sub>0</sub> = DISK ROTATIONAL PERIOD = INVERSE OF DISK REVOLUTIONS PER SECOND

$T_1 = (0.16) \times (T_4) \text{ TO } (0.25) \times (T_4)$

$T_2 = (0.25) \times (T_4) \text{ TO } (0.33) \times (T_4)$   $T_3 = (0.40) \times (T_4) \text{ TO } (0.6) \times (T_4)$   $T_4 = 8 \text{ TIMES THE REFERENCE CLOCK PERIOD } (T)$

NOTE: TIMING IS NOMINAL AND MAY VARY DUE TO SPEED VARIATIONS.

E-131-1

#### INDEX AND BYTE CLOCK RELATIONSHIP FIGURE 19

# 5.2.7.3 Address Mark Found (Controller Soft Sector)

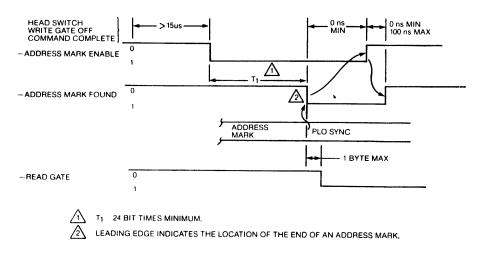

This signal indicates the detection of the end of an address mark. See Figure 20 for timing.

### READ ADDRESS MARK TIMING FIGURE 20

E-132-1

# 5.2.8 Command Complete

A status line provided at the J2/P2 connector. This is an ungated output from the drive which allows the host to monitor the drive's COMMAND COMPLETE status, during overlapped commands, without selecting the drive. This signal line will go false in the following cases:

- A recalibration sequence is initiated (by drive logic) at power on, if the R/W heads are not over track zero.

- 2. Upon receipt of the first Command Data bit. COMMAND COMPLETE will stay false during the entire command sequence.

- 3. Within 15 usec from a head select change if head selection time is >15usec as indicated in CONFIGURATION DATA.

This signal is driven by an open collector driver as shown in Figure 2.

#### 5.3 Data Transfer Lines

All lines associated with the transfer of data between the drive and the host system are differential in nature and may not be multiplexed. These lines are provided at the J2/P2 connectors on all drives.

Four pair of balanced signals are used for the transfer of data and clock: NRZ WRITE DATA, NRZ READ DATA, WRITE CLOCK, and READ/REFERENCE CLOCK. Figure 3 illustrates the recommended driver/receiver circuit.

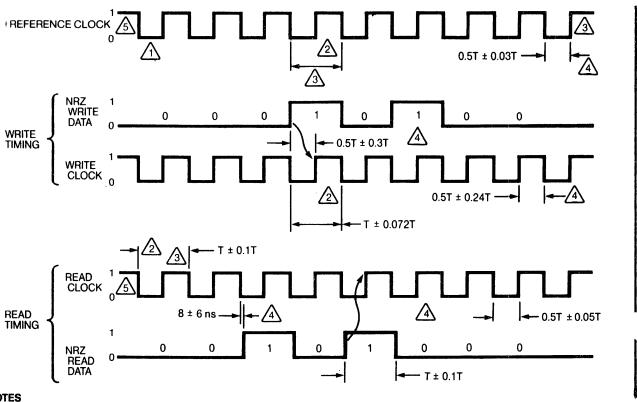

# 5.3.1 NRZ Write Data

This is a differential pair that defines the data to be written on the track. This data will be clocked by the WRITE CLOCK signal. See Figure 21 for timing.

#### 5.3.2 NRZ Read Data

The data recovered by reading previously written information is transmitted to the host system via the differential pair of NRZ READ DATA lines. This data is clocked by the READ CLOCK signal. See Figure 21 for timing. These lines must be held at a zero level until PLO sync has been obtained and data is valid.

#### 5.3.3 Read/Reference Clock

The timing diagram as shown in Figure 21 depicts the necessary sequence of events (with associated timing restrictions for proper read/write operation of the drive). The REFERENCE CLOCK signal from the drive will determine the data transfer rate. The transitions from REFERENCE CLOCK to READ CLOCK must be performed without glitches. Two missing clock cycles are permissible.

All controllers which meet the ESDI specification must be able to operate at a minimum of 10Mbits/second data transfer rate.

#### 5.3.4 Write Clock

WRITE CLOCK is provided by the controller and must be at the bit data rate. This clock frequency shall be dictated by the READ/REFERENCE CLOCK during the write operation. See Figure 21 for timing.

WRITE CLOCK need not be continuously supplied to the drive. WRITE CLOCK should be supplied before beginning a write operation and should last for the duration of the write operation.

#### **NOTES**

- ALL TIMES IN NS MEASURED AT I/O CONNECTOR OF THE DRIVE. T IS THE PERIOD OF THE CLOCK SIGNALS AND IS THE INVERSE OF THE REFERENCE OR READ CLOCK FREQUENCY.

- SIMILAR PERIOD SYMMETRY SHALL BE IN ± 4ns BETWEEN ANY TWO ADJACENT CYCLES DURING READING OR WRITING.

- EXCEPT DURING A HEAD CHANGE OR PLO SYNCHRONIZATION THE CLOCK VARIANCES FOR SPINDLE SPEED AND CIRCUIT TOLERANCES SHALL NOT VARY MORE THAN -5.5% to +5.0%. PHASE RELATIONSHIP BETWEEN REFERENCE CLOCK AND NRZ WRITE DATA OR WRITE CLOCK IS NOT DEFINED.

- TIMING APPLICABLE DURING READING OR WRITING.

- REFERENCE CLOCK IS VALID WHEN READ GATE IS INACTIVE. READ CLOCK IS VALID WHEN READ GATE IS ACTIVE AND PLO SYNCHRONIZATION HAS BEEN ESTABLISHED.

- $\stackrel{\frown}{6}$  SEE FIGURE 3 FOR DEFINITION OF Ø AND 1 ON THESE DIFFERENTIAL SIGNAL LINES.

E-133-1

#### NRZ READ/WRITE DATA TIMINGS FIGURE 21

# 5.4 Read. Write, and Format Parameters

# 5.4.1 General Summary of Critical Read-Function Timing Parameters

Controller variations of the read timing are allowed if the following drive-dependent parameters are met:

#### a. Read Initialization Time.

A read operation may not be initiated until 15 us following a head change. Drives not able to meet 15 us must drop COMMAND COMPLETE upon a head switch.

#### b. Read-Gate Timing

Read Gate may not be enabled or true during a Write Splice area (Read Gate must be deactivated one bit time minimum before a Write Splice area and may be enabled one bit time minimum after a Write Splice area.)

# c. Read Propagation Delay

Data (read) at the interface is delayed by up to 9 bit times from the data recorded on the disk media. See specific drive product specification for exact value.

#### d. Read Clock Timing

Read Clock and Read Data are valid within the number of PLO sync field bytes specified by the drive configuration after Read Enable and a PLO sync field is encountered The Interface Read/Reference Clock line may contain no transitions for up to two Reference Clock periods for transitions between reference and read clocks. The transition period will also be one-half of a Reference Clock period minimum with no shortened pulse widths.

#### 5.4.2 General Summary of Critical Write-Function Parameters

Controller timing variations in the record-update function are allowed if the following drive-dependent write (and interrelated read) timing parameters are met:

#### a. Read-to-Write Recovery Time

Assuming head selection is stabilized, the time lapse from deactivating Read Gate to activiting Write Gate shall be five Reference Clock periods minimum.

#### b. Write Clock-to-Write Gate Timing

Write Clocks must precede Write Gate by a minimum of two and a half Reference Clock periods.

#### c. Write Driver Plus Data-Encoder Turn-On From Write Gate

The write driver plus data-encoder turn-on time (write splice width) is between 3 and 7 Reference Clock periods.

### d. Write-Driver Turn-Off from Write Gate

To account for data-encoding delays, Write Gate must be held on for at least two byte times after the last bit of the information to be recorded.

#### e. Write-to-Read Recovery Time

The time lapse before READ GATE or ADDRESS MARK ENABLE can be activated after deactivating the Write Gate is 10us.

#### f. Head Switching Time

Write Gate must be deactivated at least 1 us before a head change.

Write Gate may not be activated until 15 us after a head change or COMMAND COMPLETE is true.

#### g. Reference Clocks Valid Time

The Read/Reference Clock lines will contain valid Reference Clocks within two Reference Clock periods after the deactivation of Read Gate. Pulse widths will not be shortened during the transition time but clock transitions may not occur for up to two Reference Clock periods.

#### h. Read Clocks Valid Time

The Read/Reference Clock line will contain valid Read clocks within two Clock periods after PLO synchronization is established. Pulse widths will not be shortened during the REFERENCE CLOCK to READ CLOCK transition time, but missing clocks may occur for up to two clock periods.

#### i. Write Propagation Delay

Write Data Received at the I/O connector will be delayed by the Write Data Encoder by up to 8 bit times maximum prior to being recorded on the media.

#### 5.4.3 Fixed Sector Implementation (Controller or Drive Hard Sectored)

This section is included as an example of a fixed sector format to give meaning to the definitions given.

#### 5.4.3.1 Format Rules (Fixed Sector)

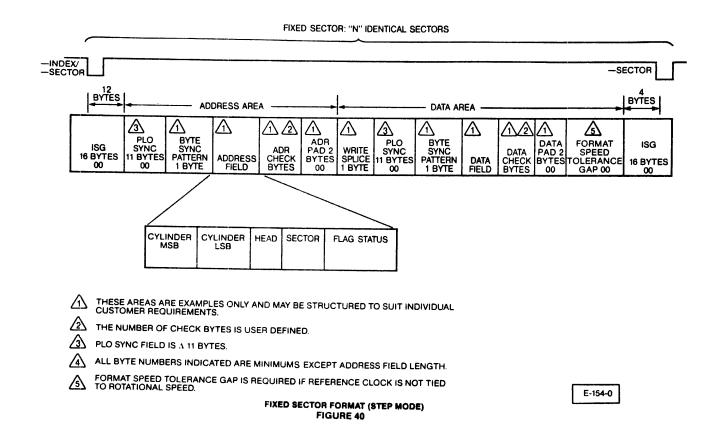

The record format on the disk is under control of the controller. The Index pulse and BYTE CLOCKS or INDEX and SECTOR pulses are available for use by the controller to indicate the beginning of a track and allow the controller to define the beginning of a sector. A suggested format for fixed data records is shown in Figure 22.

The format presented in Figure 22 consists of four functional areas; Intersector Gap, Address, Data, and Format Speed Tolerance Gap. The Data area is used to record the system's data files. The Address area is used to locate and verify the track and sector location on the Disk where the Data areas are to be recorded. This section refers to a SECTOR pulse which is generated internal to the controller from the BYTE CLOCK, or SECTOR pulses available from the drive to ease the format description.

THESE AREAS ARE EXAMPLES ONLY AND MAY BE STRUCTURED TO SUIT INDIVIDUAL CUSTOMER REQUIREMENTS.

THE NUMBER OF CHECK BYTES IS USER DEFINED.

PLO SYNC FIELD AND ISG ARE AS REPORTED IN RESPONSE TO THE REQUEST CONFIGURATION COMMANDS.

ALL BYTE NUMBERS INDICATED ARE MINIMUMS EXCEPT ADDRESS FIELD LENGTH.

FORMAT SPEED TOLERANCE GAP IS REQUIRED IF REFERENCE CLOCK IS NOT TIED TO ROTATIONAL SPEED. THE APPLICABILITY OF THIS GAP IS DEFINED IN THE CONFIGURATION DATA.

FIXED SECTOR FORMAT FIGURE 22 E-134-0

# 5.4.3.2 Intersector Gap (ISG)

The minimum Intersector Gap size is determined from the configuration data. The Intersector Gap provides a separation between each sector. The gap size is chosen to provide for:

- a. Drive required write-to-read recovery time (minimum time between deassertion of WRITE GATE and assertion of READ GATE).

- b. Drive required head switching time.

- c. Control decision making time between sectors.

- d. Other drive required ISG times.

- e. Variations in detecting INDEX and SECTOR.

# 5.4.3.3 Address Area

The address area (Figure 22) provides a positive indication of the track and sector locations. The address area is normally read by the controller and the address bytes verified prior to a data area read or write. The address area is normally only written by the controller during a format function and thereafter only read to provide a positive indication of the sector location and establish the boundaries of the data area. The address area consists of the following bytes.

#### a. PLO Sync Field

These bytes are required by the drive to allow the drive's read-data phase-locked oscillator to become phase and frequency synchronized with the data bits recorded on the media. The controller should send 00's during this time.

# b. Byte Sync Pattern (one byte minimum)

This byte establishes byte synchronization (i.e. the ability to partition this ensuing serial bit stream into meaningful information groupings, such as bytes) and indicates to the controller the beginning of the address field information. It is recommended that the Byte Sync Pattern contain more than a single one bit for a greater confidence level of detection.

#### c. Address Field

These bytes are user-defined and interpreted by the user's controller. A suggested format consists of five bytes, which allows two bytes to define the cylinder address, one byte to define the head address, one byte to define the sector address, and one byte to define flag status.

### d. ADR Check Bytes - (Address Field Check Codes)

An appropriate error-detection mechanism is generated by the controller and applied to the address for file-integrity purposes. These codes are written on the media during formatting. Data integrity is maintained by the controller recalculating and verifying the address-field check codes when the address field is read. ADR check bytes are user defined.

#### e. ADR Pad (two bytes minimum) - (Address Field Pad)

The Address Field Pad bytes must be written by the controller and are required by the drive to ensure proper recording and recovery of the last bits of the address-field check codes. These pad bytes should be 00's

#### 5.4.3.4 <u>Data Area</u>

The Data Area (Figure 22) is used to record data fields. The contents of the data fields within the Data Area are specified by the host system. The remaining parts of the Data Area are specified and interpreted by the disk controller to recover the data fields and ensure their integrity. The Data Area consists of:

# a. Write Splice (one byte minimum)

This byte area is required by the drive to allow time for the write drivers to turn on and reach recording amplitude sufficient to ensure data recovery. This byte should be allowed for in the format and the controller should send 00's during this byte time.

# b. PLO Sync bytes

These bytes are required when reading to allow the drive's phase-locked oscillator to become phase and frequency synchronized with the data bits recorded in the media. The controller should send 00's during these byte times.

# c. Byte Sync Pattern (one byte minimum)

This byte establishes byte synchronization and indicates, to the controller, the beginning of the data field. It is recommended that this byte contain more than a single one bit.

#### d. Data Field

The data field contains the host system's data files.

# e. <u>Data Check Bytes - (Data-Field Check Codes)</u>

The Data Check or Error Check Code bytes are generated by the controller and written on the media at the end of the Data Field. Data integrity is maintained by the controller recalculating and verifying the Data Field Check Codes or applying error correction algorithyms if applicable when the Data Field is read. The Data Check Field is user defined.

# f. Data Pad (two bytes minimum) - (Data Field Pad)

The Data Field Pad bytes must be issued by the controller and is required by the drive to ensure proper recording and recovery of the last bits of the data field check codes. The controller should send 00's during these byte times.

#### 5.4.3.5 Format Speed Tolerance Gap

This gap is required if bit 14 of the configuration respones flag is activated. If this gap is required, the size is determined by the controller and is:

Unformatted sector length X .01 (if configuration flag bit 11 is 0)

or

Unformatted sector length X .02 (if configuration flag bit 11 is 1)

This gap, if required, should be between each sector. The byte pattern in this gap should be 00's.

# 5.4.3.6 Fixed Sector, Address Mark, Write Gate, PLO Sync Format Timing

This timing is mainly to support drives that utilize unique encoding for PLO sync fields. The beginning of each PLO sync field must be specified by the controller. For compatability with Controller Soft Sector mode of operation, the beginning of the Header PLO Sync Field will be specified by the trailing edge of the ADDRESS MARK ENABLE signal when WRITE GATE is true. See Figure 23.

#### 5.4.4 Address Mark Implementation (Controller Soft Sectored)

This section is included as an example to give meaning to the definitions given.

#### 5.4.4.1 Format Rules (Soft Sector)

The purpose of a format is to organize a data track into smaller sequentially numbered blocks of data called sectors.

#### 5.4.4.2 Soft Sectored Format

The format shown below in Figure 24 is similar to the format commonly used for hard sectored disk drives and indicates minimum requirements.

This format is a soft sectored type of sector which means that the beginning of each sector is defined by an ID Address Mark followed by a prewritten identification (ID) field which contains the logical sector address plus cylinder and head information. The ID field is then followed by a user supplied data field.

The definitions of the functional areas shown in the soft sectored format are identical to those described for the hard sectored format. There are some additional fields in this format and they are the Address Mark field, Address Mark Pad, and ISG speed tolerance gap.

# 5.4.4.3 Address Mark Field

The address mark field is a field 3 bytes long and is found before the PLO sync field in the address area. The contents of this 3 byte field is drive dependent and is written by the drive when so commanded by WRITE GATE and ADDRESS MARK ENABLE active simultaneously.

Detection of Address Mark indicates the location of the beginning of a sector.

# 5.4.4.4 Address Mark Pad