Printed Circuit Manual

VOLUME 1

**CONTROL DATA**

CORPORATION

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in back of this manual.

| 60042900                                            | Record of Revisions                                      |  |  |  |  |  |  |

|-----------------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| REVISION                                            | NOTES                                                    |  |  |  |  |  |  |

| A                                                   | Corrections                                              |  |  |  |  |  |  |

| В                                                   | 1604 Inverter Ground Rules and Hammer Storage Card       |  |  |  |  |  |  |

|                                                     | 91 pages added.                                          |  |  |  |  |  |  |

| C                                                   | Long Line Driver and Receiver Cards CA98 and HA26        |  |  |  |  |  |  |

|                                                     | pages added.                                             |  |  |  |  |  |  |

| D                                                   | Corrections to card type C64 and C65.                    |  |  |  |  |  |  |

| E                                                   | Add index tabs, chapter headings, new Table of Contents  |  |  |  |  |  |  |

|                                                     | addition to Appendix, type "E" and 1604 cards; and       |  |  |  |  |  |  |

|                                                     | Delay Card P13A.                                         |  |  |  |  |  |  |

| F                                                   | Replace the following pages: 3-HA18-1 and 2; 4-C62 and   |  |  |  |  |  |  |

|                                                     | C-61-5 and 6; Appendix pages 5 thru 10. Add pages 4-60,  |  |  |  |  |  |  |

| 60A, 62 and 67-1 thru 3; 4-79A-1, 5-97-1 and 2, 5-E |                                                          |  |  |  |  |  |  |

| Replace page 4-E12-1.                               |                                                          |  |  |  |  |  |  |

| G                                                   | 6600 Info and Circuit Module Schematics added as Vol. 3. |  |  |  |  |  |  |

| H Vol. 1, addition of revised Record of Rev. Vol. 2 |                                                          |  |  |  |  |  |  |

|                                                     | of Record of Rev. Replace the following revised page:    |  |  |  |  |  |  |

| Chapter 4 contents page, 4-C62 and C61-1, 4-C62 a   |                                                          |  |  |  |  |  |  |

|                                                     | C61-2, 4-C62 and C61-3, 4-C62 and C61-5, 4-C62 and       |  |  |  |  |  |  |

|                                                     | C61-6, 4-C62 and C61-7, 4-P14A & P16A-3, 5-C94-3.        |  |  |  |  |  |  |

| J                                                   | Vol. 1, page 2-3600 Inv-3 revised, Vol. 2, Chapter 5,    |  |  |  |  |  |  |

|                                                     | second page of contents revised, removed pages 5-PED-1   |  |  |  |  |  |  |

|                                                     | thru 5-PED-22. Chapter 6 added and Appendix 1, pages     |  |  |  |  |  |  |

|                                                     | 16, 17 and 18 removed and new pages added.               |  |  |  |  |  |  |

| K                                                   | Publications Change Order 11170. Record of Rev. for      |  |  |  |  |  |  |

|                                                     | Vol's, 1 and 2 revised. Removed pages 15 thru 31 of vol. |  |  |  |  |  |  |

|                                                     | 2, Appendix 1 and replaced with revised pages.           |  |  |  |  |  |  |

| L                                                   |                                                          |  |  |  |  |  |  |

| (10-5-65)                                           | volume 1 revised. Chapter 4 contents page, 4-HA19-3,     |  |  |  |  |  |  |

|                                                     | 4-HA37 & HA43-10, 4-P14C & P16A-1, 4-P14C & P16A-2,      |  |  |  |  |  |  |

|                                                     | 4-P14C & P16A-3, chapter 5 contents pages, 5-C84-1,      |  |  |  |  |  |  |

| 5-C84-2, 5-C84-3 (new page), 3, 4, 7 & 8 (appendix  |                                                          |  |  |  |  |  |  |

| 60042900                                     | Record of Revisions                                      |  |  |  |  |  |  |

|----------------------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| REVISION                                     | NOTES                                                    |  |  |  |  |  |  |

| L (Cont'd)                                   | revised. Pages 5-C60-1, 5-C60-2, 5-C60-3, 5-C97-1,       |  |  |  |  |  |  |

| (10-5-65)                                    | 5-C97-2, and 5-C97-3 added. Pages 5-HA27 & 5-HA28-1      |  |  |  |  |  |  |

|                                              | and 5-HA27 & 5-HA28-2 revised.                           |  |  |  |  |  |  |

| M                                            | Change Order 12131. Appendix 1: pages 16 through 31      |  |  |  |  |  |  |

| (12-13-65)                                   | revised and pages 32 through 47 added.                   |  |  |  |  |  |  |

| N                                            | Publication Change Order 12940. New Peripheral           |  |  |  |  |  |  |

| <b>(</b> 5-13-66 <b>)</b>                    | Equipment cards added to Chapter 6: ADH, ITA/ITB/ITC,    |  |  |  |  |  |  |

|                                              | ITD, IYA, OJB, OYA and UJB. Revised text for page:       |  |  |  |  |  |  |

|                                              | 6-OHA-1. Revised schematic for page 6-IAA, IAB-2.        |  |  |  |  |  |  |

|                                              | Appendix 1 revised. This revision obsoletes all editions |  |  |  |  |  |  |

|                                              | of Pin Assignments - 1604 & 3600 - Printed Circuit       |  |  |  |  |  |  |

|                                              | Cards, Pub. No. 60106200, which is now included in       |  |  |  |  |  |  |

|                                              | this revision.                                           |  |  |  |  |  |  |

| P                                            | Publication Change Order 13632. Pages 6-ISC-1 of         |  |  |  |  |  |  |

| <b>(</b> 5-13-66 <b>)</b>                    | chapter 6 is revised. The following new cards are        |  |  |  |  |  |  |

| added to chapter 6: ALA, AMF, AMG, AMH, AMI, |                                                          |  |  |  |  |  |  |

|                                              | ANB, ANC, AND, AUA, EUA, EUC, EVB, FCA, FCB,             |  |  |  |  |  |  |

|                                              | FDA, FGA, FHA, FIA, FJA, FKA, FLA, FLB, FMA,             |  |  |  |  |  |  |

|                                              | FNA, FPA, FRA, FSA, FTA, FUA, FVA, FWA, FYA,             |  |  |  |  |  |  |

|                                              | JBA, JCA, JDA, and OTA.                                  |  |  |  |  |  |  |

| R                                            | Publications Change Order 15800. The following new       |  |  |  |  |  |  |

| (2-13-67)                                    | cards added to Chapter 6: AIB, AKA, AOA, ATA, ATB,       |  |  |  |  |  |  |

|                                              | AVA, AYA, BAA, BAB, BBA, BCA, EEG, EEH, EWA,             |  |  |  |  |  |  |

|                                              | EWB, EZA, FAB, FOA, FOB, FRB, FRC, FRD, FSB,             |  |  |  |  |  |  |

|                                              | FUB, FWB, FXB, GAA, GBA, GCA, GCB, GCC, GCD,             |  |  |  |  |  |  |

|                                              | IOB, IOC, IOD, JEB, JEC, ONA, OUA, OVA, UEA,             |  |  |  |  |  |  |

|                                              | UHB, UIA, UJC, UKA, and UKB.                             |  |  |  |  |  |  |

|                                              |                                                          |  |  |  |  |  |  |

|                                              |                                                          |  |  |  |  |  |  |

|                                              |                                                          |  |  |  |  |  |  |

|                                              |                                                          |  |  |  |  |  |  |

#### PREFACE

This manual is for use by design engineers, maintenance personnel, and others who need detailed characteristics of CONTROL DATA\* Printed Circuit Cards. A separate manual is available for those interested in schematics only. THE SCHEMATICS INCLUDED IN THIS MANUAL DO NOT NECESSARILY REFLECT THE LATEST REVISIONS.

The descriptions and schematics presented in chapters 2 through 5 are representative of the various types of circuits. Any user who desires more information about a given circuit may order a print of the schematic drawing from the cognizant division, using the drawing number from one of the tables in the appendix section. The schematic drawing bears the name of the designer, who may be contacted for first-hand information.

The appendix section of this manual contains tables listing all printed circuit cards produced by Control Data Corporation. Further up-to-date listings may be obtained by ordering the Standard Printed Circuit Card Index, available from Engineering Services, Computer Division.

Page numbering system used in this manual provides modularity so that additional circuit descriptions may be inserted without affecting the sequential order of page numbers. Additional descriptions may be obtained from the Technical Publications Department as they become available.

Every effort will be made to keep this manual current. Users are requested to notify the Technical Publications Department of any errors or suggestions for improvement.

<sup>\*</sup> Registered trademark of Control Data Corporation

## CONTENTS

Chapter 1. Elements of Control Data Logic

Appendix. Table of Card Types, Pin Assignments and Schematic Drawing Numbers.

Chapters 2, 3, 4, and 5. Circuit Descriptions

Chapter 6. Peripheral Equipment Cards, Group Logic Card Index.

| CARD TYPE |                      | CHAPTER | CARD TYPE |                           | CHAPTER |  |

|-----------|----------------------|---------|-----------|---------------------------|---------|--|

|           | 1604 Inverter        | 2       | 66        | Punch Puller              | 5       |  |

|           | 3600 Inverter        | 2       | 67        | Output (L)                | 4       |  |

| 00        | Clock Disconnect     | 5       | 70B       | Read Amplifier            | 5       |  |

| 01        | Oscillator           | 5       | 73        | Delay Capacitor           | 5       |  |

| 01A       | Oscillator           | 5       | 73A       | Delay Capacitor           | 5       |  |

| 02A       | Oscillator           | 5       | 74        | Current Source            | 3       |  |

| 06        | Oscillator Amplifier | 5       | 75        | Reader Level Amplifier    | 5       |  |

| 50        | Capacitor            | 5       | 75A       | Reader Level Amplifier    | 5       |  |

| 51        | Drive Generator      | 3       | 76A       | Reader Brake-Clutch Driv  | er 5    |  |

| 51A       | Drive Generator      | 3       | 77        | Delay Capacitor           | 5       |  |

| 52        | Diverter             | 3       | 79A       | Output                    | 4       |  |

| 52A       | Diverter             | 3       | 82        | Delay Capacitor           | 5       |  |

| 53        | Selector             | 3       | 86        | Punch Puller              | 5       |  |

| 54        | Current Source       | 3       | 87        | Input (M)                 | 4       |  |

| 55        | Inhibit Generator    | 3       | 91        | Hammer Storage            | 5       |  |

| 55A       | Inhibit Generator    | 3       | 97A       | Delay                     | 5       |  |

| 56        | Sense Amplifier      | 3       | C00       | Even Plane Inhibit Driver | 3       |  |

| 57        | Sense Amplifier      | 3       | C01       | Clock Oscillator-Amplifie | er 5    |  |

| 58        | Inhibit Generator    | 3       | C02       | Clamp                     | 5       |  |

| 58A       | Inhibit Generator    | 3       | C03       | Line Driver               | 3       |  |

| 59        | Inhibit Generator    | 3       | C04       | Odd Plane Inhibit Driver  | 3       |  |

| 59A       | Inhibit Generator    | 3       | C05       | Gate                      | 3       |  |

| 60        | Output (L)           | 4       | C06       | Sense Amplifier           | 3       |  |

| 60A       | Output (L)           | 4       | C070      | C Emitter Follower        | 5       |  |

| 61        | Input (M)            | 4       | C08       | Delay Line Driver         | 5       |  |

| 62        | Output (L)           | 4       | C09       | Inhibit Compensator       | 3       |  |

| 65        | Speaker Driver       | 5       | C10       | Drive Line Transformer    | 3       |  |

|           | -                    |         | C60.      | A Switch                  | 5       |  |

| CARD TYPE |                        | CHAPTER | CARD TYPE    |                          | CHAPTER |  |

|-----------|------------------------|---------|--------------|--------------------------|---------|--|

| C61       | Receiver               | 4       | E02A         | Crosspoint Module        | 5       |  |

| C61B      | Receiver               | 4       | E03A         | Crosspoint Control Modul | e 5     |  |

| C62A      | Transmitter            | 4       | E04A         | Crosspoint Control Modul | .e 5    |  |

| C64A      | Resync Circuit         | 5       | E <b>0</b> 5 | Decoder                  | 5       |  |

| C65A      | Resync Circuit         | 5       | E06          | Terminator               | 5       |  |

| C66A      | Resync Circuit         | 5       | E07          | Terminator               | 5       |  |

| C67       | Capacitive Delay       | 5       | E08          | Single Pulser            | 5       |  |

| C68       | Capacitive Delay       | 5       | E10          | Integrator               | 5       |  |

| C69       | Capacitive Delay       | 5       | E11          | Delay                    | 5       |  |

| C70C      | Capacitive Delay       | 5       | E12          | Line Driver              | 4       |  |

| C71       | Capacitive Delay       | 5       | E13          | Line Receiver            | 4       |  |

| C75       | Modified M Input       | 4       | E14          | Variable Clock           | 5       |  |

| C75B      | Modified M Input       | 4       | E15          | Line Driver              | 4       |  |

| C76       | Modified L Output      | 4       | E19          | Terminator               | 5       |  |

| C76A      | Modified L Output      | 4       | E20          | Resistor Assembly        | 5       |  |

| C77       | Priority Circuit       | 5       | E61A         | Line Receiver            | 4       |  |

| C78B      | Priority Circuit       | 5       | E62B         | Line Driver              | 4       |  |

| C79A      | Priority Circuit       | 5       | E67A         | Line Driver              | 4       |  |

| C80       | Delay Line, 1 usec     | 5       | H10A         | Console Interface        | 5       |  |

| C81       | Crystal Oscillator     | 5       | H11A         | Receiver                 | 4       |  |

| C82       | Crystal Oscillator     | 5       | H12          | Delay Line Amplifier     | 5       |  |

| C83       | Crystal Oscillator     | 5       | H14          | Digit Driver             | 3       |  |

| C84       | Relay Driver           | 5       | H15          | Digit Compensator        | 3       |  |

| C85       | Strobe Shaper          | 5       | H16          | Sense Amplifier          | 3       |  |

| C86       | I/O Sense Amplifier    | 3       | H17          | Filter                   | 5       |  |

| C87       | I/O Memory Driver      | 3       | H18          | Sense Amplifier          | 3       |  |

| C88       | I/O Memory Diverter    | 3       | H19          | Transmitter              | 4       |  |

| C89       | Amplifier - Shaper     | 5       | H20          | Light Driver             | 5       |  |

| C90       | I/O Emitter Follower   | 3       | H26          | Long Line Receiver       | 4       |  |

| C91       | Reader Level Amplifier | 5       | H27          | Keyboard Translator      | 5       |  |

| C94       | Overload Protector     | 5       | H28          | Keyboard Translator      | 5       |  |

| C97       | Channel Disable        | 5       | H31          | Level Translator         | 4       |  |

| C98       | Long Line Driver       | 4       | H32A         | Line Driver              | 4       |  |

| E00       | Jumper                 | 5       | H35          | Delay Line, 0.1 usec     | 5       |  |

| E01A      | Crosspoint Module      | 5       |              |                          |         |  |

Rev. L vi

| CARD TYPE   |                                | CHAPTER  |                | CARD TYPE CHAI               | PTER |

|-------------|--------------------------------|----------|----------------|------------------------------|------|

| H37         | Transmitter, 1000-foot         | 4        | AFA            | Multiple Time Delay          | 6    |

| H38         | Diode                          | 5        | AFB            | Multiple Time Delay          | 6    |

| H39         | Line Terminator                | 5        | AGA            | Enable Amplifier             | 6    |

| H43         | Transmitter, 1000-foot         | 4        | AHA            | Flip-Flop Driver             | 6    |

| K67         | Capacitive Delay               | 5        | AIA            | Driver                       | 6    |

| K71         | Capacitive Delay               | 5        | EDA            | Read Level Detector          | 6    |

| P13A        | Delay, 0.15 usec               | 5        | EEA            | Resistor Termination         | 6    |

| P14C        | Transmitter                    | 4        | EEB            | Capacitor Termination        | 6    |

| P16A        | Receiver                       | 4        | EEC            | Capacitor Termination        | 6    |

| P51         | Memory Driver                  | 3        | EED            | Resistor Termination         | 6    |

| P52         | Memory Diverter                | 3        | EEE            | Capacitor Termination        | 6    |

| P54         | Power Supply Filter and        | 5        | $\mathbf{EEF}$ | Resistor Termination         | 6    |

| -           | Jumper                         |          | EFA            | Clock Amplifier              | 6    |

| P55         | Power Supply Filter and Jumper | 5        | EGA            | Read Level Detector          | 6    |

| P56         | Sense Amplifier                | 3        | EHA            | Read Preamplifier            | 6    |

| P91         | Hammer Driver                  | 5        | EHB            | Read Preamplifier            | 6    |

| P92         | Hammer Driver                  | 5        | EHC            | Read Preamplifier            | 6    |

| P93         | Pulse Shaper                   | 5        | ΕIA            | Read Level Detector          | 6    |

| P94         | Ribbon Advance                 | 5        | EIB            | Read Level Detector          | 6    |

| <b>P</b> 95 | Brake-Clutch One-Shot          | 5        | EID            | Read Level Detector          | 6    |

| P96         | Ribbon Drive and Hold          | 5        | $\mathbf{EIE}$ | Read Level Detector          | 6    |

| P97         | Hammer Driver One-Shot         | t 5      | EPA            | Potentiometer                | 6    |

| <b>P</b> 99 | Brake-Clutch One-Shot          | 5        | ERA            | Solenoid Driver              | 6    |

|             |                                |          | ESA            | Delay Control Potentiometers | 6    |

| P           | . E. D Special Purpose of      | Circuits | IAA            | Relay Puller                 | 6    |

| ABA         | Relay Puller                   | 6        | IAB            | Relay Puller                 | 6    |

| ACA         | Photo - Diode Bias and         | 6        | IBA            | Power Emitter Follower       | 6    |

|             | Preamplifier                   |          | ICA            | Dual Driver                  | 6    |

| ADA         | Hammer Driver                  | 6        | IIA            | Write Driver                 | 6    |

| ADB         | Hammer Driver                  | 6        | IJA            | Flip-Flop Write Driver       | 6    |

| ADC         | Hammer Driver                  | 6        | IKA            | Output Amplifier             | 6    |

| ADD         | Hammer Driver                  | 6        | ILA            | Voice Coil Driver            | 6    |

| ADE         | Hammer Driver                  | 6        | INA            | Output Amplifier             | 6    |

| AEB         | Output Driver                  | 6        | IPA            | Output Amplifier             | 6    |

vii Rev. L

| C   | ARD TYPE                         | CHAPTER |     | CARD TYPE                               | CHAPTER |

|-----|----------------------------------|---------|-----|-----------------------------------------|---------|

| IQA | Output Amplifier                 | 6       | OPA | Input Amplifier                         | 6       |

| ISC | Output Amplifier                 | 6       | OQA | Input Amplifier                         | 6       |

| ITA | Pulse Delay and Output           | 6       | ORA | Comparator and Readou                   | t 6     |

|     | Amplifier                        |         | OSA | Input Amplifier                         | 6       |

| OAA | Photocell Amplifier              | 6       | OSB | Input Amplifier                         | 6       |

| OCA | Dual Photocell Amplifier         | 6       | UAA | - •                                     | 6       |

| ODA | Read Peak Detector               | 6       | UAB | •                                       | 6       |

| OFA | Input Amplifier                  | 6       | UBA | <b>33</b>                               | 6       |

| OGA | Peak Detector                    | 6       | UCB |                                         | 6       |

| OGB | Peak Detector                    | 6       | UFA | •                                       | -       |

| OGC | Peak Detector                    | 6       |     | • • • • • • • • • • • • • • • • • • • • |         |

| ОНА | Peak Detector                    | 6       | UFB |                                         | •       |

| OIA | Input Amplifier                  | 6       | UGA | Voltage Controlled Puls Delay           | е 6     |

|     | Input Amplifier                  | 6       | XKA | •                                       |         |

|     | •                                |         |     |                                         | 6       |

| OLA | Flyback Verify Flip-Flop         | 6       | XKC | Pulse Shaper                            | 6       |

| OMA | Input Amplifier, High<br>Fan-Out | 6       |     |                                         |         |

Rev. L viii

## CHAPTER 1. ELEMENTS OF CONTROL DATA LOGIC

| Printed Circuit Cards                | 1-1  |

|--------------------------------------|------|

| Inverter                             | 1-1  |

| Flip-Flop (FF)                       | 1-2  |

| Control Delay                        | 1-2  |

| Definition of a Clock Phase Time     | 1-2  |

| Description                          | 1-3  |

| Circuit Operation                    | 1-4  |

| Logical Equations of a Control Delay | 1-7  |

| Logical AND                          | 1-8  |

| Logical OR                           | 1-8  |

| Basic Three-Stage Counter            | 1-8  |

| Capacitive Delay                     | 1-11 |

| Pulse Forming Networks               | 1-13 |

| Timing Chain Pulse Generator         | 1-15 |

The basic logic element in Control Data computers and peripheral devices is a transistor inverter circuit. A flip-flop (FF) is a combination of two inverters; a control delay is three inverters with clocked inputs. The major portion of a digital computer is built by interconnecting these circuits. Connections of inverters, flip-flops, and control delays form the various units of a digital computer, e.g., registers, counters, adders, complementers, and comparators. To facilitate the diagrammatic representation of these circuits the logic diagram technique is used. This technique emphasizes the functional aspect of a digital computer rather than the electronic aspect.

As a general rule, a digital computer has four main sections: Control, Arithmetic, Storage, and Input/Output. The Control and Arithmetic sections can be grouped under Logic section. Accordingly, the descriptions of the circuits in this manual are presented in four groups: Logic, Storage, Input/Output, and Special Purpose, (Chapters 2, 3, 4, and 5).

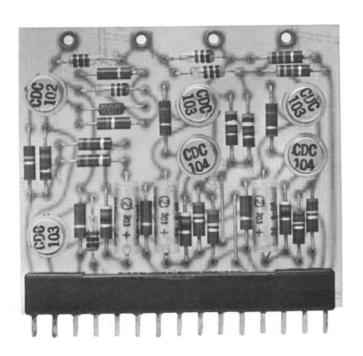

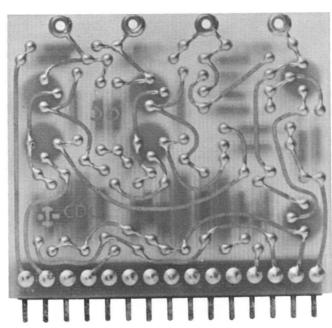

#### PRINTED CIRCUIT CARDS

Control Data electronic circuits are mounted on printed circuit cards (frontispiece). Each card is equipped with a 15 pin male connector for plugging into the equipment chassis. The printed circuit card technique has the advantages of ease of design and maintenance, use of solid state components, greater reliability, and modular construction.

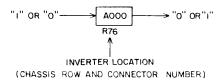

#### INVERTER

The basic logic building block is an inverter circuit, represented by a rectangle as shown in figure 1-1. This circuit employs a  $180^{\circ}$  electrical phase shift to produce an inversion; a "1" input results in a "0" output, and vice versa. In addition to use as an inverter, combinations of this basic logic element form bi-stable flip-flops and control delays.

Figure 1-1. Conventional Inverter Symbol

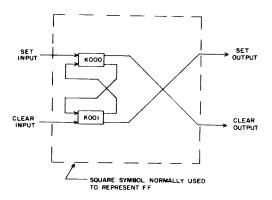

#### FLIP-FLOP (FF)

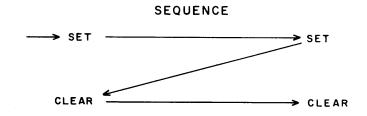

A FF is two inverter circuits interconnected as shown in figure 1-2. Each rectangle represents a single inverter. One of the inverters is the set side of the FF; the other, the clear side. The FF is placed in the "1" (set) state by a "1" signal on the set input. Conversely, it is placed in the "0" (cleared) state by a "1" signal on the clear input.

The storage capability of a FF means that the FF remains in the state in which it was placed by the last "1" input. Specifically, if a "1" signal is present at the set input, then the output of inverter K000 (figure 1-2) becomes "0". This output is applied as an input to K001 and its output then becomes "1". The output of K001 is fed back to K000. Thus, when the set input drops to "0", the feedback connection between K000 and K001 permits the storage of the state to which the "1" signal on the set input forced the FF. Should the clear input later receive a "1" signal the output of K001 becomes "0", and the feedback input to K000 is "0". Consequently, K000 furnishes a "1" output which is returned to K001 and replaces the "1" signal at the clear input.

When the FF is set, K001 has a "1" output and K000 has a "0" output. Conversely, when the FF is cleared, K001 has a "0" output, and K000 has a "1" output.

The conventional square or box symbol for a FF is used in figure 1-2 to show the relationship between it and the inverter configuration which forms the FF. The square which represents the FF encompasses the crossover of the outputs.

#### CONTROL DELAY

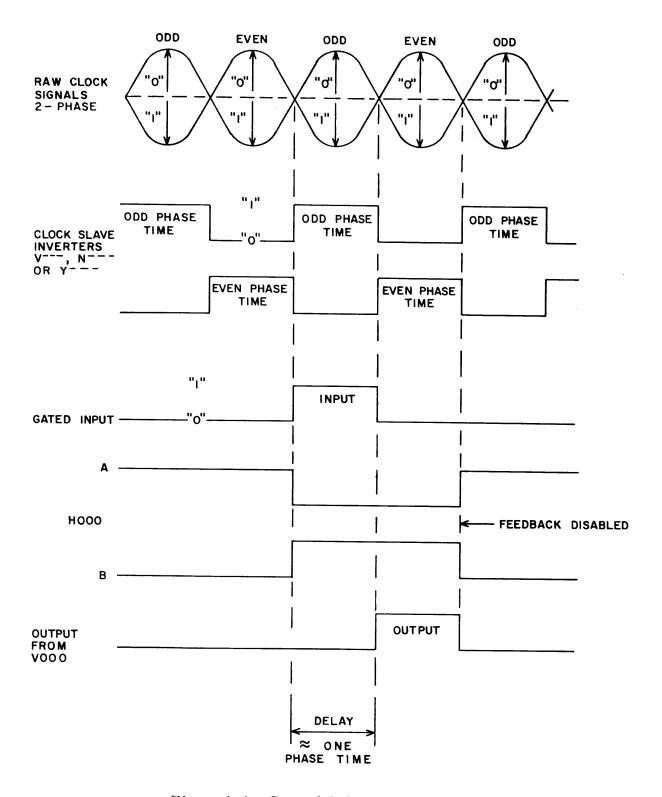

The function of the control delay is to synchronize a sequence of logic operations within the computer with the two-phase master clock. Logical "1" inputs are received during one phase time, either odd or even, and "1" outputs are provided during the next phase time, either even or odd. The phase time of the output is opposite the phase time of the input.

#### DEFINITION OF A CLOCK PHASE TIME

A clock phase time is the time during which an inverter driven by that phase has a "1" output. The input to the inverter is the raw clock signal received directly from the clock card. Thus during a clock phase time, the raw clock signal from that phase is a logical "0".

NOTE: INPUTS AND OUTPUTS EXIST AS SHOWN WHEN FF IS "SET"

Figure 1-2. Conventional Flip-Flop Symbol

The response time of the inverter is approximately 1/4 to 1/2 a phase time. Thus the clock phase time always lags behind the raw clock signal, due to the delay of the inverter. However, this delay is not shown in the timing diagram of figure 1-4.

#### DESCRIPTION

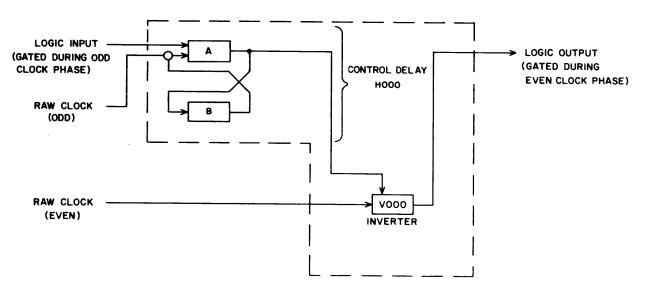

The control delay consists of a FF having its feedback ANDed with a raw clock signal, and one or more inverters with two OR inputs each, which are driven by the A section of the FF and by a raw clock signal. The raw clock signal which enables the FF feedback is the phase opposite that which drives the inverter or inverters.

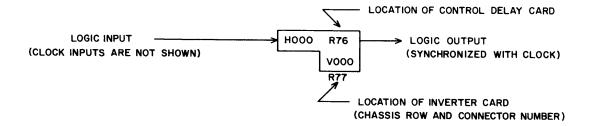

A diagram of a control delay symbol and the circuits encompassed by it is shown in figure 1-3. Figure 1-4 shows the timing of its operation.

The clock inputs to a control delay are ordinarily not shown on a drawing. It is understood that the output occurs during the odd or even phase time, while the corresponding raw clock signal is a "0", depending upon whether the third superscript digit is odd or even. For example, control delay  $\rm H100/V100$  would have its output during an even clock phase time, while  $\rm H101/V101$  would have its output during an odd clock phase time.

The logic input to a control delay is gated by the external circuitry. Normally, the input drops to "0" shortly after the output appears, and is not repeated. If the input does not drop, then the output of the control delay is a series of pulses from the inverter, since it is driven by the raw clock signal.

## CIRCUIT OPERATION

Figure 1-3 shows that the gated logic input goes directly into the A section of H000. This forces the output of A to "0", resulting in a "1" output from B. The input to A is gated during the odd clock phase time; thus during this time, the odd raw clock signal is "0". When the odd raw clock signal becomes "1", the logic input to A drops, but the feedback path from B to A is enabled so that A continues to have a "0" output until the next odd clock phase time.

Inverter V000 is gated both by the output of A and by the even raw clock signal. With a "0" input from A, inverter V000 provides a "1" output during the even clock phase time, since the even raw clock signal is a "0". The "1" output from V000 continues until the next odd clock phase time disables the FF feedback, and the control delay returns to initial conditions.

#### NOTE:

INVERTER MAY BE REPRESENTED BY EITHER V---, N---, OR Y---.

## NOTE:

LOGIC INPUT IS GATED INTO CONTROL DELAY WHILE ODD CLOCK PHASE IS "I". THE INPUT DROPS WHEN ODD PHASE BECOMES "O" AND IS NOT REPEATED.

Figure 1-3. Conventional Control Delay Symbol

Figure 1-4. Control Delay Timing Diagram

## LOGICAL EQUATIONS OF A CONTROL DELAY

A control delay may be represented by a minimum of two logical equations: one equation for the H--- term, and one equation for each V---, N---, or Y--- term. The symbol on the left of the equal sign is the subject term, and the expression on the right describes the configuration of its inputs.

All raw clock and gated logic inputs to a control delay are represented in its equations. The H--- term requires a logic input gated during a clock phase, and a raw clock signal which gates the FF feedback. The V--- term requires a raw clock signal to gate its output, and a logic input from the H--- term. These conditions are covered by the following basic rules:

- 1. Every input term of an H--- equation must contain one, and only one, clocked symbol such as V---, N---, or Y---.

- 2. The last term of an H--- equation must be a C--- (raw clock).

- 3. At least one input term of a V---, N---, or Y--- equation must contain an H--- symbol.

- 4. The last term of a V---, N---, or Y--- equation must be a C--- (raw clock) symbol.

A set of equations for control delay which would have an output during an even phase time could be written as follows:

H000 = Z024 W005 N001 + C001 V000 = H000 + C000

The symbols in the above equations refer to the following:

- H000 A circuit on a control delay card which receives its input during an odd phase time, since the third superscript digit is even.

- Z024 A logic input.

- W005 A logic input.

- N001 A clock slave inverter which provides a "1" input enabling the 3-way AND during an odd clock phase time.

- C001 A raw clock signal which is a "0" during odd clock phase times; it is received at the control delay card and gates the FF feedback.

- V000 The inverter portion of the control delay which provides a "1" output during an even clock phase time only.

- C000 A raw clock signal which is "0" during even clock phase times and drives the control delay inverter.

#### LOGICAL "AND"

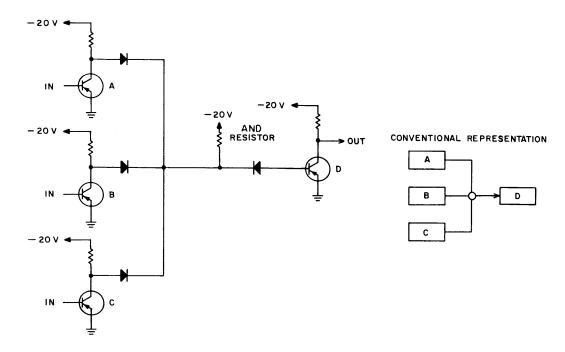

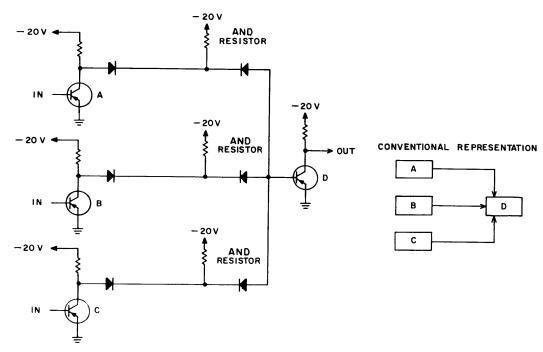

A three-input AND circuit is shown in figure 1-5. The small circle and connections used to represent this circuit on a logic diagram are also shown.

The AND gate requires that all inputs must be a "1" simultaneously. If any one of the AND inputs is a "0", then a "1" on another input is not sensed.

Thus, if the transistors A, B, and C are not conducting, their output diodes are biased in the reverse direction, and the resulting output signals are at the logical "1" level. This condition allows the -20v through the AND resistor to place a negative voltage on the base of transistor D, so that it conducts.

However, if any one of transistors A, B, or C is conducting, its collector goes to approximately ground potential. Its output diode is biased in the forward direction from the -20v through the AND resistor. This prevents the -20v source from applying drive current to transistor D, and transistor D is held in the non-conducting state.

## LOGICAL "OR"

A three-input OR circuit is shown in figure 1-6 (the conventional logic diagram representation is also shown). An OR gate allows a "1" signal on any input to be sensed, although a "0" signal may simultaneously appear on another input.

Figure 1-6 shows three single-input ANDs connected to produce three logical OR inputs to transistor D. The input lines are separated by diodes, so that a "1" signal is not nullified by a "0" signal on another input line. Thus, if any one of transistors A, B. or C is not conducting so that it has a "1" output, the -20v through the respective AND resistor applies a negative voltage to the base of transistor D, causing it to conduct.

#### BASIC THREE-STAGE COUNTER

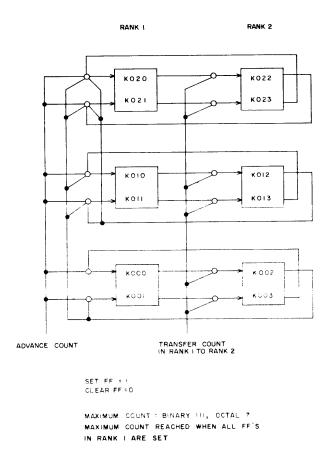

A counter is essentially a double rank register which increases or decreases the quantity stored, an increment at a time. The three-stage counter circuit shown in figure 1-7 is additive from binary 000 through 111.

A count is stored in two steps:

1. A "1" input on the Advance line sets a FF in rank 1. This occurs in consecutive order and when all three are set, the next

Figure 1-5. Logical AND

Figure 1-6. Logical OR

input clears them.

2. A "1" input on the Transfer line causes the FFs in rank two to assume the identical states as their corresponding FFs in rank 1.

To analyze the operation of the counter, assume that both ranks are initially cleared, so the count stored is zero. The first Advance command finds the AND gate to K000 enabled and therefore enters the count 001 (octal 1) into rank 1. This partially enables the AND gate to K002 so that the Transfer command enters the count 001 into rank two. The next Advance command finds the AND gate to K001 and K010 enabled and thus enters the count 010 (octal 2) into rank 1. The operation continues in this manner as shown in table 1-1 until the count reaches 111 (octal 7), which is the highest possible count in a three-stage counter. This is followed by a command sequence which returns both ranks to the count 000.

Figure 1-7. Basic Three-Stage Counter

TABLE 1-1. COUNTING SEQUENCE FOR THREE-STAGE COUNTER

|  | Command               | Quantity          | Rank 1 |        |        | Rank 2 |        |        |

|--|-----------------------|-------------------|--------|--------|--------|--------|--------|--------|

|  |                       | Stored<br>(Octal) | K02-   | K01-   | K00-   | K02-   | K01-   | K00-   |

|  | Initial<br>conditions | 0                 | 0      | 0      | 0      | 0      | 0      | 0      |

|  | Advance<br>Transfer   | 1                 | 0      | 0      | 1      | 0      | 0      | 0<br>1 |

|  | Advance<br>Transfer   | 2                 | 0      | 1<br>1 | 0<br>0 | 0      | 0<br>1 | 1      |

|  | Advance<br>Transfer   | 3                 | 0      | 1<br>1 | 1<br>1 | 0      | 1      | 0<br>1 |

|  | Advance<br>Transfer   | 4                 | 1      | 0      | 0<br>0 | 0<br>1 | 1      | 1      |

|  | Advance<br>Transfer   | 5                 | 1      | 0      | 1      | 1      | 0<br>0 | 0<br>1 |

|  | Advance<br>Transfer   | 6                 | 1      | 1      | 0<br>0 | 1      | 0<br>1 | 1 0    |

|  | Advance<br>Transfer   | 7                 | 1      | 1      | 1<br>1 | 1      | 1      | 0<br>1 |

|  | Advance<br>Transfer   | 0(or8)            | 0      | 0<br>0 | 0<br>0 | 1<br>0 | 1<br>0 | 1<br>0 |

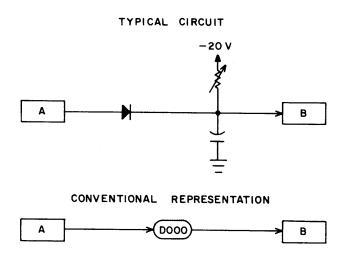

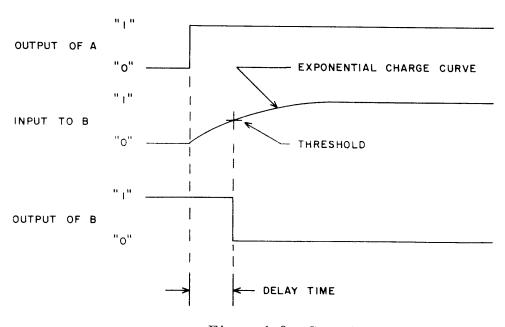

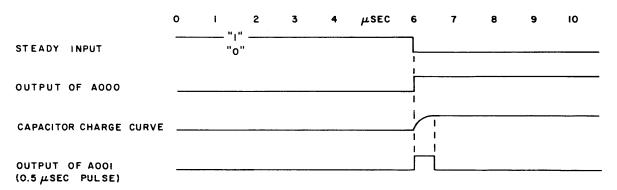

#### CAPACITIVE DELAY

Capacitive delay circuits are constructed by placing a capacitor from the signal line to ground. The delay time is the time required to charge the capacitor when a "1" signal appears on the line. A "0" signal is delayed approximately one tenth as long as a "1". The method of connecting a delay between two logic cards, and the symbols used to represent this connection on a logic diagram are shown in figure 1-8.

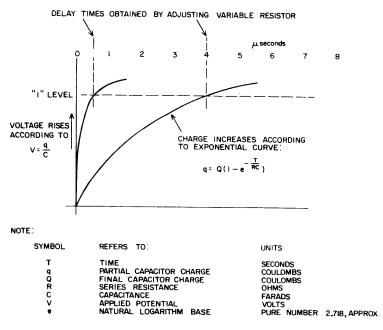

Figure 1-8 shows that when the transistor on card A is conducting, its collector is almost at ground potential. Hence, the voltage across the delay capacitor is quite low and it contains very little charge. However, when the output of card A switches to "1" and its transistor stops conducting, the circuitry attempts to bias the input line at the "1" level. Initially this voltage is absorbed by the uncharged delay capacitor, which gradually obtains a charge as shown in figure 1-9.

Two factors govern the delay time: the size of the capacitor and the rate at which it receives charging current. Generally, the larger the capacitor, the longer the delay time. The delay time may be adjusted by varying the resistance in series with the capacitor. Increasing the resistance decreases current flow to the capacitor, increasing the delay time.

Figure 1-8. Capacitive Delay

Figure 1-9. Capacitor Charge Curve

#### PULSE FORMING NETWORKS

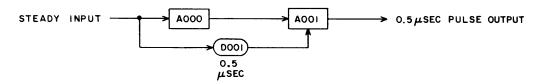

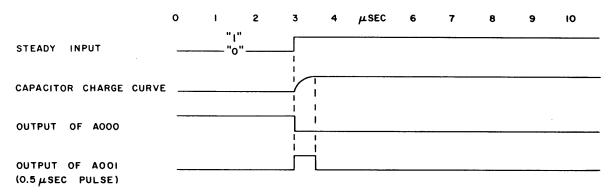

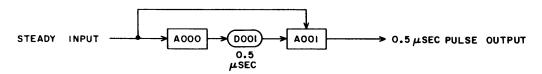

Many circuits contain pulse forming networks, consisting of two inverters and a capacitive delay, for the purpose of reshaping a steady "1" signal into a short "1" pulse. There are two types: those which produce a pulse upon receipt of a "1" signal and those which produce a pulse when the "1" signal ends. These types are known respectively as "leading edge" and "trailing edge" networks, and are presented in figure 1-10.

When a "1" input is received by a leading edge network, an immediate double inversion occurs, producing a "1" output. However, as soon as the capacitor is sufficiently charged, a "1" is sent directly into A001, and the output of inverter A001 switches to "0".

In the case of a trailing edge network, the steady input signal is fed directly into both inverters. Thus, when this signal goes to "0", the output of both inverters switches to "1". However, the "1" output of A000 does not reach A001 until the capacitor has charged sufficiently; at that time the output of A001 switches to "0".

#### LEADING EDGE NETWORK

## TIMING CHART

## TRAILING EDGE NETWORK

#### TIMING CHART

Figure 1-10. Pulse Forming Networks

## TIMING CHAIN PULSE GENERATOR

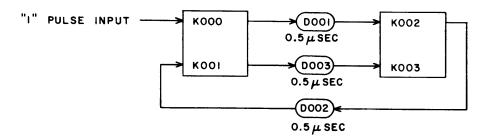

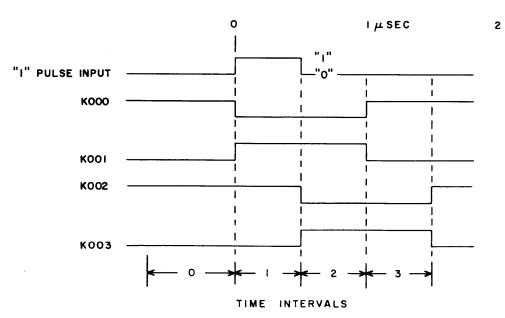

A convenient method of obtaining a series of sequential pulses using flip-flops and delays is shown in figure 1-11.

The two FFs exhibit four distinct sets of conditions at successive time intervals. Initially both are in the clear state. A "1" pulse input to K000 sets K000/001, so that K001 has a "1" output. After a brief delay, this signal sets K002/003. K003 then sends a "1" through a delay to K001, so that K000/001 is cleared. This causes K000 to send a "1" through the third delay to K003, so that K002/003 is also cleared and initial conditions prevail.

These four conditions and the times at which they occur are as follows:

|               | K000/K001 | K002/K003 |

|---------------|-----------|-----------|

| Time 0        | Clear     | Clear     |

| Time 1        | Set       | Clear     |

| Time 2        | Set       | Set       |

| Time 3        | Clear     | Set       |

| Time 0 (or 4) | Clear     | Clear     |

The lengths of these time intervals are dependent upon the value of the capacitive delays. In the example shown, all of the times are 0.5 us. However, these may be varied in any manner desired.

## . TIMING CHAIN PULSE GENERATOR

## TIMING CHART

Figure 1-11. Timing Chain

## CHAPTER 2. LOGIC CARDS

1604 Inverter Circuit and Ground Rules3600 Inverter Circuit and Ground Rules

# INVERTER CIRCUIT 1604 TYPE

The two signal levels in 1604 type logic are: -3.0v, logical "1", and -0.5v, logical "0". The single inverter inverts these signal levels: a -3.0v input becomes a -0.5v output, and vice versa.

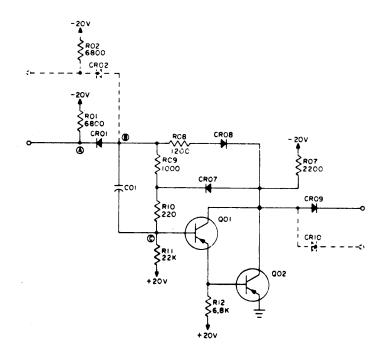

In the standard inverter circuit shown, transistor Q01 is connected as an emitter-follower; Q02, as an amplifier. The collector circuits of the transistors have two feedback loops which prevent the transistors from being driven to cutoff or saturation. As a result, switching from one state to the other is accomplished in from 50 to 100 nano-seconds.

An input signal is applied via isolation diodes CR01 or CR02 to a voltage divider network composed of resistors R07, R08, R09, R10 and R11. An input signal of -0.5v (point A) results in -1.5v at point B and 0.8v at the base of Q01 (point C). CR01 is biased 1v in the backward direction to provide for noise suppression at the input of the inverter. Capacitor C01, between CR01 and the base of Q01, provides rapid coupling of input signal changes to Q01, improving the switching time of the circuit.

Transistors Q01 and Q02 each provide beta\* current gains of approximately 100; loop gain of the two transistors is in the order of 10<sup>4</sup>. The collector current of Q01 and Q02 develops the output voltage across resistor R07. Output diode CR09 isolates the output line from the other output line connected to CR10.

Diodes CR07 and CR08 form the feedback loops which prevent transistors Q01 and Q02 from being driven to cutoff or saturation. The positive-going limit allows a maximum transistor conduction that is less than saturation; the negative-going limit fixes a minimum conduction for the transistors. When the transistors approach cutoff, their collectors approach -3.0v. The collector potential is coupled back to the base of Q01 through CR08, R09 and R10. As a consequence the base of Q01 always is held at a sufficiently negative voltage to permit some minimum conduction of Q01 and thus Q02.

<sup>\*</sup>The beta current gain is the ratio of collector current to base current.

When the transistors approach saturation, the collectors approach 0v. The collector potential is coupled back to the base of Q01 through CR07 and R10. The base of Q01 is thus prevented from becoming so negative that saturation occurs.

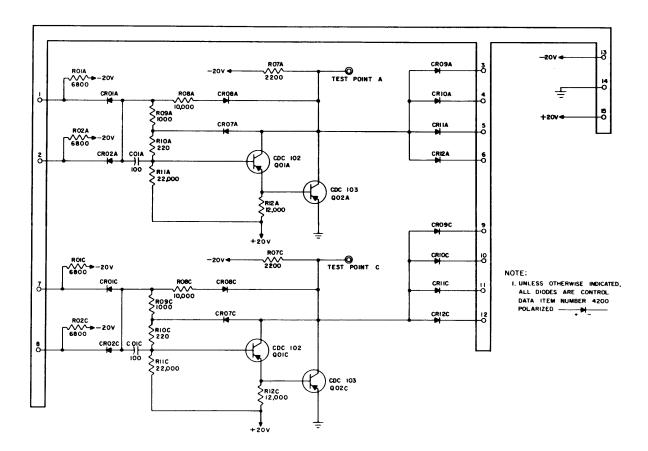

Schematic Diagram of 1604 Type Inverter Circuit

#### GROUND RULES

The following ground rules for usage of the basic 1604 inverter circuit are intended as guidelines in obtaining optimum performance. They are not intended to be excessively restrictive, because it is often found that a circuit will operate satisfactorily in a configuration which may deviate considerably from one or more of the ground rules. Decisions as to when a ground rule may be violated must be based upon various electronic and timing considerations, and are the responsibility of the designer.

- 1) A maximum of eight outputs may be taken from a single inverter.

- 2) An inverter will drive a maximum of six simultaneously gated AND loads.

- 3) The total number of inputs and outputs of a single inverter must not exceed 12.

- 4) The number of OR inputs to an inverter is limited to a maximum of six.

- 5) For high speed operation, the number of AND connections which can be made to a single OR input should be limited to four. If timing is not critical, the maximum number of AND connections can be increased to six.

- 6) All unused input pins must be grounded.

- 7) The minimum switching time for a mesa transistor inverter driving one load is approximately 30 nanoseconds. This will increase to about 75 nanoseconds as additional loads are added.

- 8) The minimum switching time for a drift transistor inverter driving one load is approximately 50 nanoseconds. This will increase to about 100 nanoseconds as additional loads are added.

- 9) An inverter will drive a load having 0.015 uf of capacitance. This may be increased at the discretion of the designer; however, long capacitive delays (greater than 10 usec) should be constructed using card type 97.

- 10) A capacitive delay should not be driven directly by a flip-flop, especially a flip-flop using mesa transistors, unless the discharge time of the capacitance is appreciably shorter than the duration of the input to the flip-flop.

## 3600 INVERTER CIRCUIT

#### NOTE

Type CA cards having OR inputs have been discontinued and should not be used for new design.

### AVAILABLE CARD TYPES

Three series of printed circuit cards have been produced during development of the 3600 family of computing systems. The initial prototype series was designated Type C. Later, after the design had been approved, the physical size of the phenolic board was increased slightly and the cards went into production as the Type CA series. Except for the addition of more test points, there was no change in the circuit.

As shown in figure 1, logical OR inputs on Type CA inverters consist of only the OR diode without any connection to -20 volts. This was intended to eliminate the requirement for grounding unused OR inputs, since an open OR input will not drive the circuit output to "0". In actual practice, however, it was found that the distributed capacitance of large numbers of open OR inputs could result in a delay in switching time. In addition, since OR inputs did not provide the clamping action of AND inputs, the circuits tended to respond excessively to transients on the signal line. These conditions brought about the development of two new series of cards, called Type HA and Type K. Both of these have the same basic inverter circuit as the Type CA inverter, but the inputs are modified. The logical AND and OR input configuration of a Type K card is identical to the corresponding Type CA number, but all OR's have been converted to single-way AND's including the feedback of flip-flops. Cards in the Type HA series are built with a limited number of inputs, e.g., an HA 07 card contains two inverters with each having only one single-way AND input. Type CA cards have since been discontinued and should not be used in new design.

#### BASIC INVERTER CIRCUIT

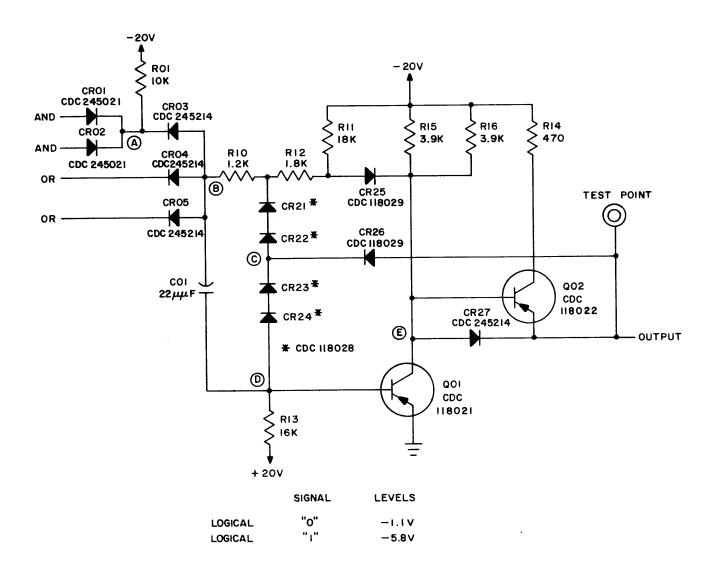

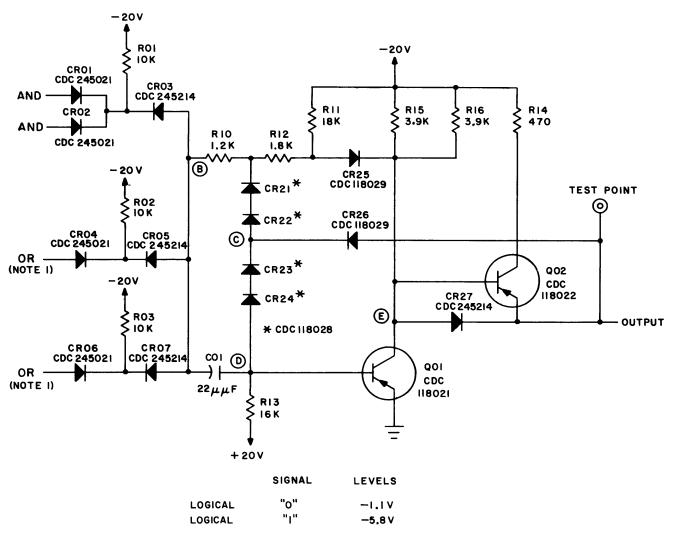

The basic inverter circuit consists of two transistor stages, as shown in figures 1 and 2. Transistor Q01 is a grounded emitter stage which supplies AND current to the load, and transistor Q02 is an emitter follower stage which supplies OR current to the load.

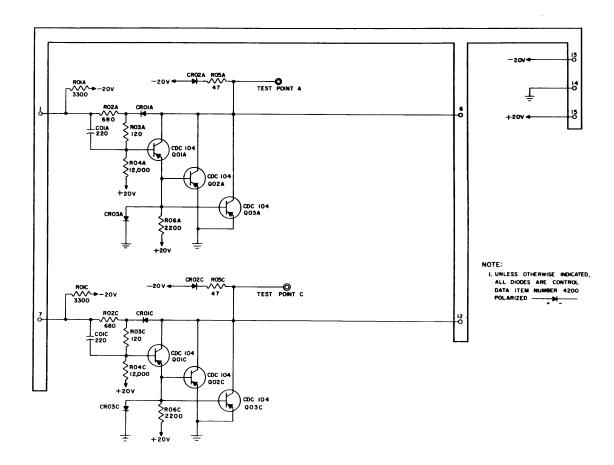

Figure 1. Schematic Diagram Type CA Inverter Circuit (Not to be used for new design)

The input to the circuit consists of two levels of diode logic. The maximum number of inputs is limited by the number of available input pins on a circuit card; however, the maximum number of individual inputs to any single AND cannot exceed 6.

NOTE I. THESE "OR" INPUTS ARE SINGLE-WAY "AND'S" AND MUST BE GROUNDED IF NOT USED.

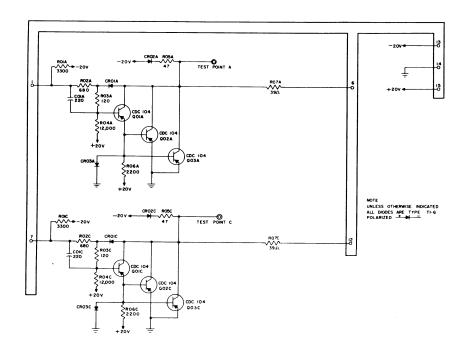

Figure 2. Schematic Diagram of Type K and Type HA Inverter Circuit

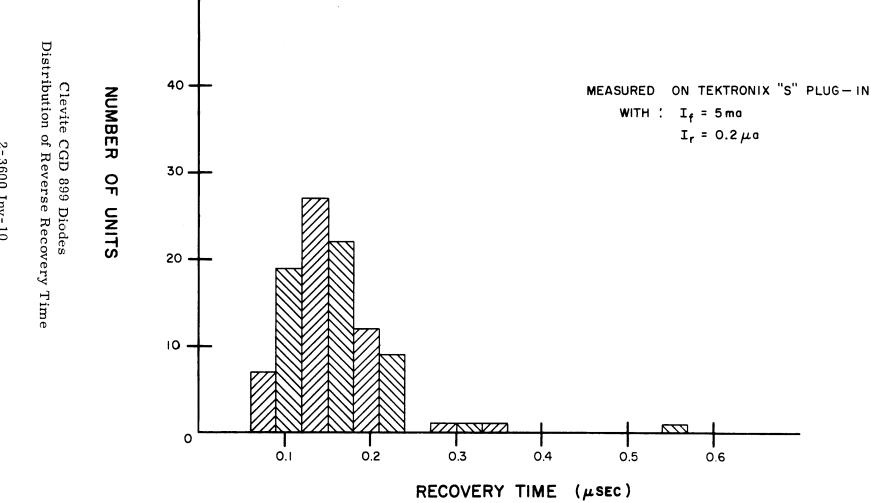

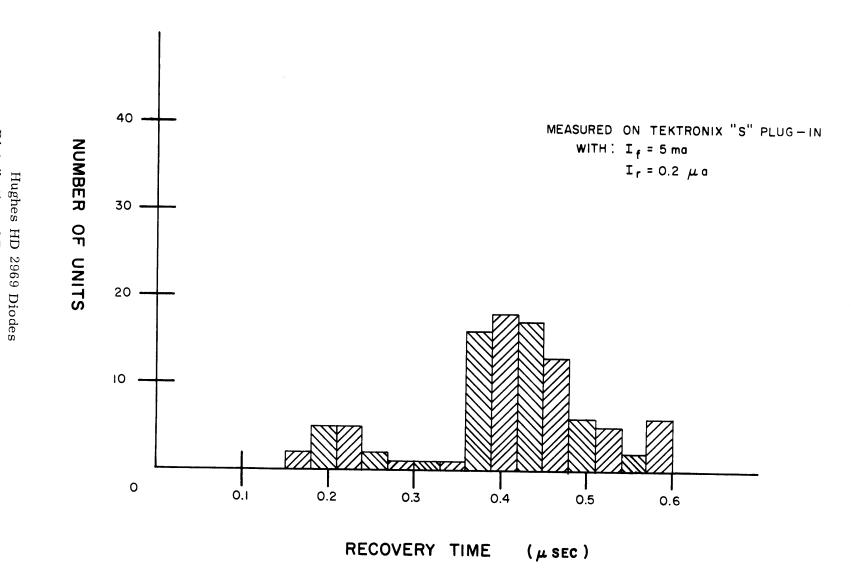

The input logic diodes are medium speed germanium devices. Initially, Hughes HD2969 diodes were used, and a set of graphs is included in this report which show the comparative recovery time of these diodes.

The response of an AND input is a function of the time constant of the AND resistor R01, shunt circuit capacitance at point (A) and the recovery speed of the input diodes. Because additional AND diode inputs increase the shunt capacitance, it is necessary to decrease the size of the AND resistor a proportionate amount as the number of inputs to the AND increases beyond 3.

The transition speed of the AND circuit varies inversely with the recovery speed of the AND diodes. Slow diodes allow additional recovery current to be drawn. This, in effect, allows a larger turn-on current in the first transistor stage.

The input resistor and diode network of transistor Q01 establishes the clamping levels for the output signal. This network also provides feedback to the base of Q01 which stabilizes the two quiescent values of the output voltage.

The input network establishes an input threshold level of approximately -3 volts. Thus, the input signal must be more negative than -3 volts before transistor Q01 turn-on current is allowed to flow. Silicon forward drop diodes CR21 through CR24 are used in the input network to obtain a constant d-c level for signal threshold. These diodes also have a low dynamic impedance which causes little attenuation of the input signal current.

The 22 uuf speed-up capacitor C01 on the input of the first stage bypasses the 1.2 k resistor R10 and the diode network during the initial rise or fall of the input signal. This provides additional drive to the base of Q01 during the input signal transition, thereby speeding the switching of this stage.

Feedback is accomplished through two high speed silicon diodes, CR25 and CR26, which have very low stored charge characteristics. If these diodes were capable of storing excessive charge, there would be additional delay in switching. By using diodes with very low storage, the initial switching speed is greatly improved.

When the grounded emitter stage Q01 is turned on, collector current flows out of the circuit through the series diode CR27. In this state, Q01 can supply current to 8 AND loads. Transistor Q01 is clamped out of saturation by the silicon feedback diode CR26, and the output voltage settles at a nominal value of -1.1 volt. The voltage drop across diode CR27 insures a back bias being applied to the base-emitter junction of Q02, thereby keeping this stage turned off.

When Q01 turns off, the collector voltage starts to rise toward -20 volts. Since the voltage across the load cannot change as quickly as the collector voltage of Q01, the series output diode CR27 is back biased and the output emitter follower stage Q02 is turned on.

The turn-on current is applied to the base of Q02 at the rate at which Q01 turns off. The turn-on current is the current that is drawn through the first stage collector resistors R15 and R16. This current is available to turn on the output stage only as fast as it is turned off in the first stage.

Transistor Q02 in the on state proceeds to drive the output voltage negative. At about -5.8 volts, the output is fed back to the input of the first stage by diode CR25 to start the clamping action. Since this process has delay associated with it, the output signal overshoots the -5.8 volt mark and may carry as far as -8 volts. The circuit then settles the voltage back to the -5.8 volt level. In this state, transistor Q02 provides a low impedance path to the -20 volt supply.

#### GROUND RULES

#### (Effective November 21, 1963)

The following ground rules for usage of the basic 3600 inverter circuit are the result of tests performed by the Special Projects Department, Government Systems Division of Control Data Corporation. Inquiries concerning these ground rules should be addressed to the above department.

The ground rules are intended as guidelines in obtaining optimum circuit performance. They should not be considered as being excessively restrictive, because it is often found that a circuit will operate satisfactorily in a less than optimum configuration which may deviate considerably from one or more of the ground rules. Decisions as to when a ground rule may be violated must be based upon various electronic considerations, and are the responsibility of the designer.

## Definition: Minimum Usage Inverter

The minimum usage inverter referred to in the following rules is defined to be an inverter driving one load and having one input. The inverter which drives the minimum usage inverter must drive no other loads. All wire lengths are kept as short as possible, voltages are adjusted to proper levels, and temperatures are allowed to stabilize.

## LOADING

Any single input to a recipient inverter, regardless of whether it is a part of a 1, 2, 3, 4, 5, or 6 input AND or an OR input, is considered to be one load.

- 1) An inverter may simultaneously drive eight AND loads, eight OR loads, or any combination up to eight loads total.

- 2) A flip-flop or a control delay may drive only seven loads, because it is required to provide its own feedback which constitutes one load.

## Exception to Rule

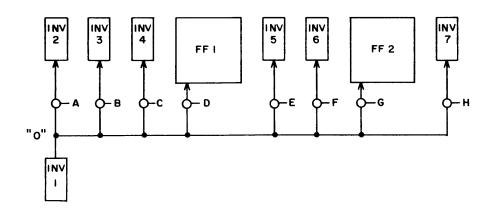

Inverter 1 is normally capable of maintaining a logical "0" on eight input AND gates. However, there is one exception when all the points, A through H, are driven to a "1" simultaneously. The current demand on inverter 1 is of such magnitude that the "0" condition is lost momentarily, allowing runt pulses to occasionally set a flip-flop or be amplified through an inverter. This condition can be avoided by limiting the inverter to a total of six loads as opposed to the usual eight loads.

#### UNUSED INPUTS

- In case an entire AND input group is unused, at least one of the inputs must be grounded.

- 4) All unused OR inputs must be grounded, if using type C or CA cards.

- 5) All unused single-way AND inputs must be grounded.

## NOISE SUPPRESSION

- 6) When a noise condition cannot be alleviated by the following suggestions or if an interconnecting lead is over 80 inches in length use logic level clamp card CA02.

- a) Maintain wire runs as short as possible.

- b) When possible, drive heavily loaded inverters from a lightly loaded source.

- c) When possible, use cards with 1, 2, 3, or 4 input AND gates as opposed to 5 and 6 input AND gates.

- d) Avoid using OR inputs unless the OR is a single-way AND.

- 7) All drive lines from H--- terms to N---, V---, and Y--- terms must be clamped, regardless of length, and must enter the recipient N---, V---, and Y--- terms through AND inputs.

- 8) N---, V---, and Y--- terms having a clock signal on an AND input must use one of the special card types numbered K72, CA73, K74, K92, K93, and HA06.

The clock input must be on the following pins:

| Card Type | Inverter A | Inverter B |

|-----------|------------|------------|

| CA72      | 5 or 6     | 13 or 14   |

| K72       | 2,5,or6    | 10,13,or14 |

| CA73      | 2 or 3     | 10 or 11   |

| CA74      | 5 or 6     | 13 or 14   |

| K74       | 5 or 6     | 13 or 14   |

| K92       | 2          |            |

| K93       | 2 or 3     |            |

| HA06      | 5 or 6     | 13 or 14   |

|           |            |            |

## Exception to Rule

- a) A clock input must come in on an AND; if the listed pins do not lend themselves to conditions, another AND input can be used.

- b) The restriction of using only the above card types may be violated in applications where the logic circuits are heavily loaded.

## PROPAGATION DELAYS AND TIMING ALLOWANCES

- 9) Allow  $17 \times 10^{-9}$  seconds To switch from "0" to "1" any minimum usage inverter using any type input.

- 10) Allow 11 x 10<sup>-9</sup> seconds To switch from "1" to "0" any minimum usage inverter using a 1, 2, 3, or 4-way AND input.

- 11) Allow 8 x 10<sup>-9</sup> seconds To switch from "1" to "0" minimum usage inverters where equal numbers of AND and OR inputs are involved in a string of inverters.

- 12) Allow 6 x 10<sup>-9</sup> seconds To switch from "1" to "0" any minimum usage inverters using a 5 or 6-way AND input.

- 13) Allow  $5 \times 10^{-9}$  seconds To switch from "1" to "0" any minimum usage inverters using OR inputs.

- 14) Allow 2 x 10<sup>-9</sup> seconds For propagation time from point to point per foot through all lengths of wire.

- 15) Add 1 x 10<sup>-9</sup> seconds To each inverter switching time for each additional load beyond one.

- 16) Add 2 x 10<sup>-9</sup> seconds To each inverter switching time for each foot of wire attached to the output.

- 17) The transition times from -1.1v "0" to -5.8v "1" and from -5.8v "1" to -1.1v "0" range from  $20 \times 10^{-9}$  to  $50 \times 10^{-9}$  seconds and  $15 \times 10^{-9}$  to  $35 \times 10^{-9}$  seconds, respectively. These times are highly influenced by loading effects.

- 18) If two inverters are cross coupled to perform as a flip-flop and the load on either side of the flip-flop is two loads or less, the cross-coupling must come into AND inputs.

- 19) The length of cross-coupling leads of inverters to be used as a flip-flop must not exceed six inches.

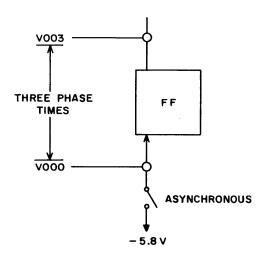

- 20) In applications where an asynchronous signal forms an AND gate with an N---, V---, or Y--- term, allow a minimum of three clock-phase times (187.5 x 10<sup>-9</sup> sec) before probing the flip-flop output for reliable information.

## TEST RESULTS

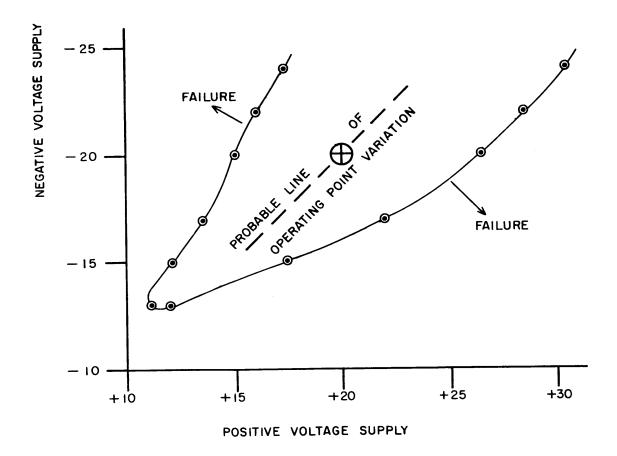

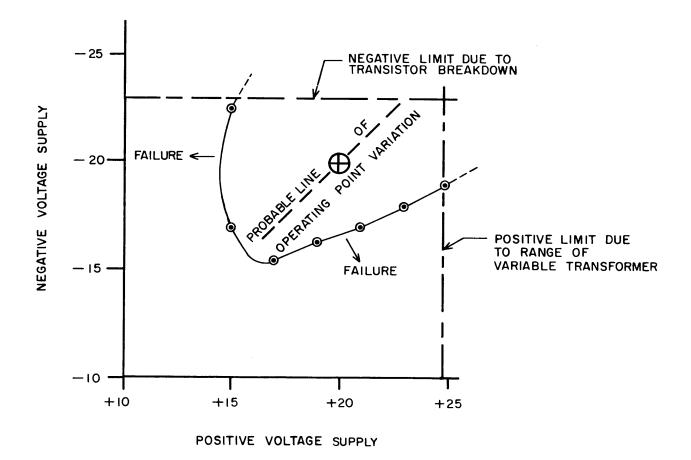

The following pages contain graphs showing the comparative recovery time of the logic diodes and the margins over which the +20v and -20v supplies may vary.

The voltage margin tests were made by varying the supply voltage of an entire chassis until failure occurred. The final version of the inverter circuit was tested in a chassis composed of 1170 cards which contained 2046 inverters.

Distribution of Reverse Recovery Time

## 8 mc "P" COUNTER CONTAINING 43 CARDS LOGIC DIODES HD 1804

Voltage Margins

2-3600 Inv-12

Voltage Margins

## CHAPTER 3. STORAGE CARDS

| Drive Generator           | 51, 51A                   |

|---------------------------|---------------------------|

| Diverter                  | 52, 52A                   |

| Selector                  | 53                        |

| Current Source            | 54, 74                    |

| Inhibit Generator         | 55, 55A, 58, 58A, 59, 59A |

| Sense Amplifier           | 56                        |

| Sense Amplifier           | 57                        |

| Even Plane Inhibit Driver | C00                       |

| Line Driver               | C03                       |

| Odd Plane Inhibit Driver  | C04                       |

| Gate                      | C05                       |

| Sense Amplifier           | C06                       |

| Inhibit Compensator       | C09                       |

| Drive Line Transformer    | C10                       |

| I/O Sense Amplifier       | C86                       |

| I/O Memory Driver         | C87                       |

| I/O Memory Diverter       | C88                       |

| I/O Emitter Follower      | C90                       |

| Digit Driver              | H14                       |

| Digit Compensator         | H15                       |

| Sense Amplifier           | H16                       |

| Sense Amplifier           | H18                       |

| Memory Driver             | P51                       |

| Memory Diverter           | P52                       |

| Sense Amplifier           | P56                       |

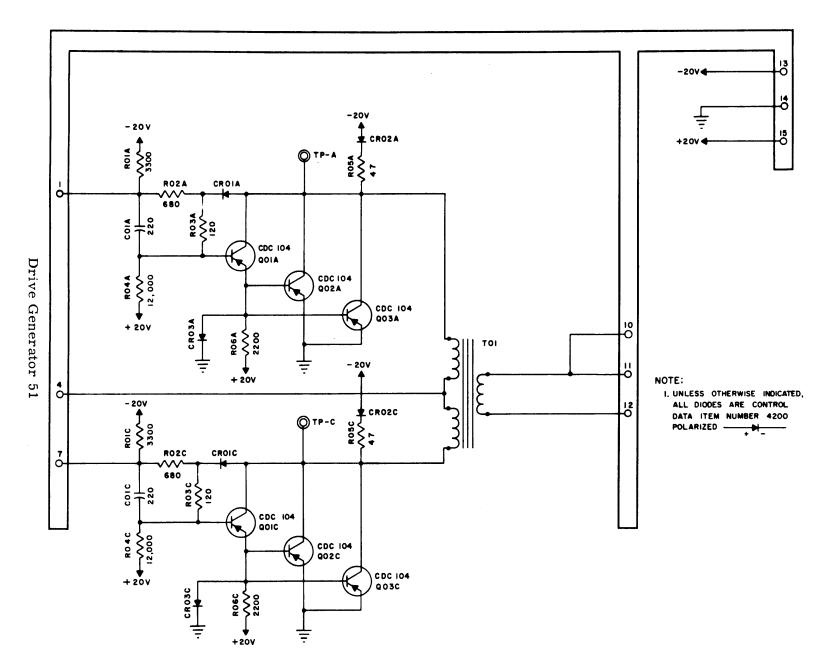

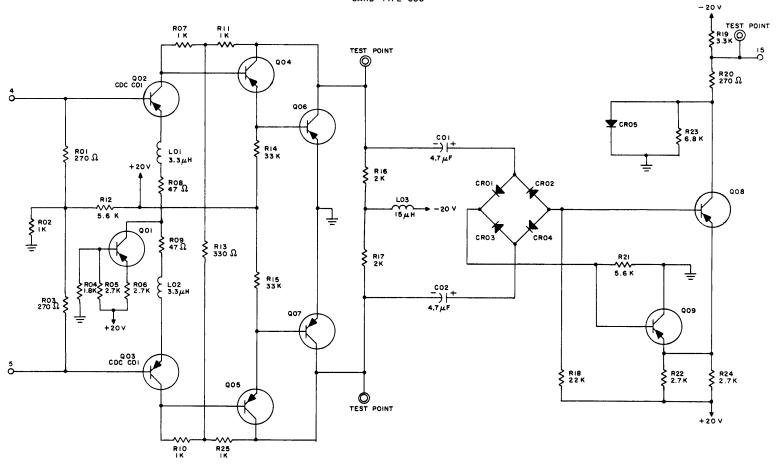

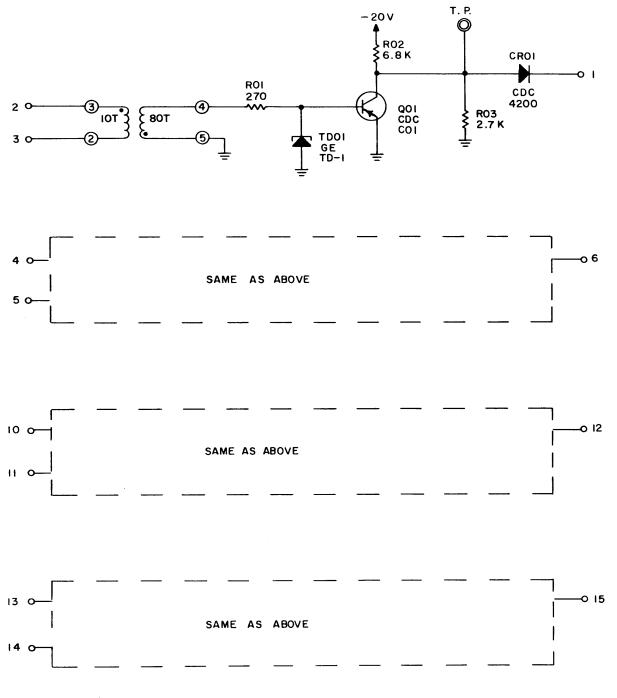

# DRIVE GENERATOR Card Types 51 and 51A

The driver generator (page 3-51-2) develops the R/W current which is applied to the memory drive lines selected (designated H and V in the 1604 computer). Two identical channels feed opposite ends of the primary winding of transformer T01. Each channel consists of transistor Q01, connected as an emitter-follower, and transistors Q02 and Q03, connected in parallel as amplifiers. The input signal is an AND combination of two selector (card type 53) outputs. A -1v input results in approximately 0v at the base of Q01. The emitter of Q01 is clamped to ground by CR03, so neither Q02 nor Q03 conducts. Consequently, no current flows in the primary of T01.

Note: Transistor Q03 is not used on card type 51A.

A -12v input signal causes Q01 to conduct; however, the conduction is held below saturation by feedback diode CR01. The negative voltage developed across R06 is applied to the bases of Q02 and Q03, causing these transistors to conduct. Current flows from the current sources through the emitters of Q02 and Q03 to the collectors, through the primary of T01, to the current sources. The current pulse from the secondary of T01, amplified by the step-down action of T01, is applied to the drive line of the memory plane assembly. It then flows through the selected diverter and back to the secondary of T01.

The polarity of the output current from T01 is determined by the direction of the current flow in the primary. The direction of current flow, in turn, is determined by the selected channel. For example, if channel A receives a -12v input, a read pulse is generated; a channel B input generates a write pulse. Acceptable switching times are as follows:

Negative to positive ≤ 0.15usec Positive to negative ≤ 0.2 usec

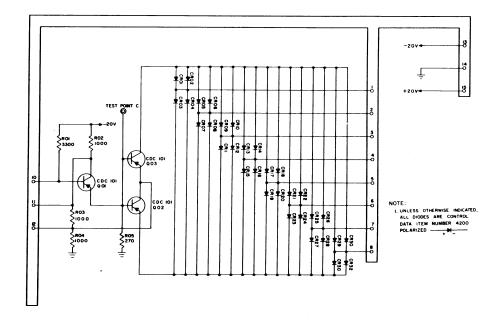

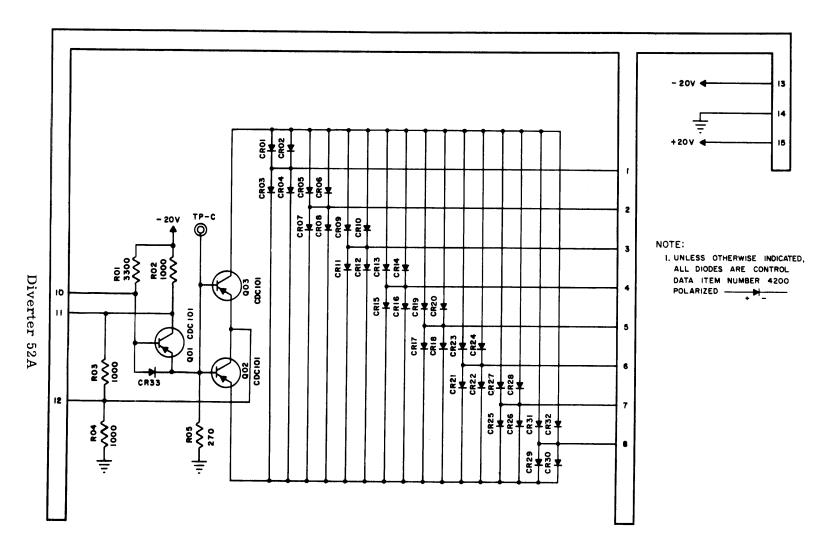

# DIVERTER Card Types 52 and 52A

## DIVERTER (Type 52)

The diverter circuit serves as an electronic switch in series with a drive line of the memory plane assembly. Transistor Q01 is connected as an emitter follower, and transistors Q02 and Q03 as switches. A -3v input causes Q01 to conduct; the negative signal from Q01 enables Q02 and Q03. One or the other transistor passes the current pulse on the drive line to which the diverter is connected.

A positive pulse passes one of the pairs of diodes CR03/CR04, CR07/CR08, CR11/CR12, etc., depending upon the driver selection, and passes Q02. A negative pulse passes one of the pairs of diodes CR01/CR02, CR05/CR06, etc., and passes Q03. In either case, the current pulse is returned to the R/W driver. The bleeder networks of all diverters are connected in parallel via terminals 11 and 12 to equalize the current flow through the bleeders and reduce heating.

Diverter 52

## SELECTOR Card Type 53

Each selector card consists of two identical circuits designed to feed a drive generator circuit. A selector circuit is similar to the 1604 type inverter except that the resistance results in output signal levels of -1v and -12v. Each selector circuit has two input diodes CR01/CR02 and four output diodes CR09/CR10/CR11/CR12.

Selector 53

## CURRENT SOURCE Card Types 54 and 74

A current source card consists of banks of parallel resistors, each of which connects an output pin and the -20v supply. The function of this card is to provide the resistances needed to hold memory drive and inhibit currents to the desired amplitude.

The available resistances are as follows:

Card Type 54

pins 1, 3, 5, 7

pin 9

Card Type 74

pins 1, 3, 5, 7

pin 9

257 ohms

303 ohms

Current Source 54

## INHIBIT GENERATOR

Card Types 55, 55A, 58, 58A, 59, 59A

Note: Transistor Q03 is not used on card types 55A, 58A, and 59A.

Each inhibit generator card has two generator circuits which are similar to the type 51 drive generator channels except for the absence of an output transformer. The output of each channel is independently connected to a terminal of the card.

A -12v input signal to either generator of a type 58 card causes Q01 to conduct and thus enable Q02 and Q03. Current from the external source connects to the generator via terminal 6 or 12 and passes through Q02 and Q03 to ground.

Inhibit Generator 55

Inhibit Generator 58

Inhibit Generator 59

3-55,58 and 59-2

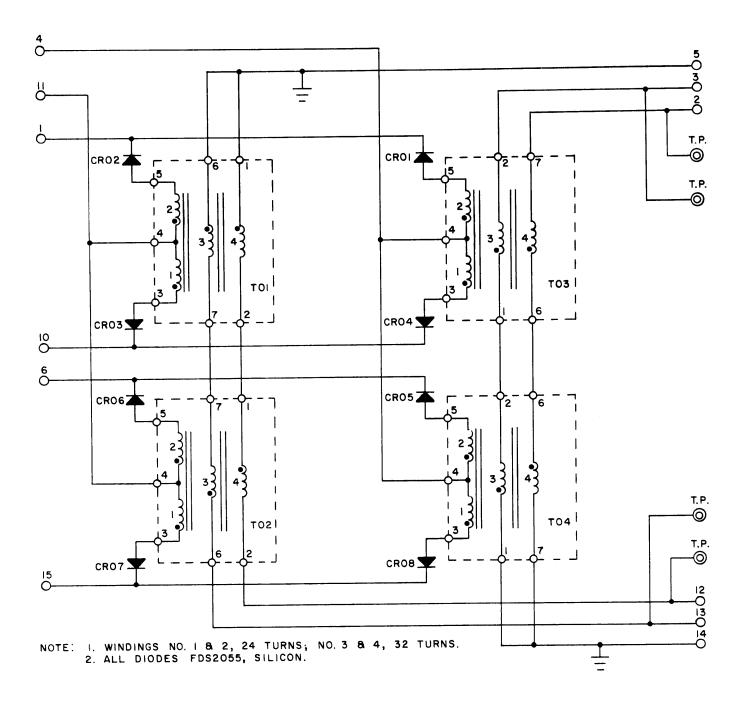

## SENSE AMPLIFIER Type 56

The 56 card amplifies the signals from a memory plane as the result of a read pulse, and produces a "0" output when a core switches. Transistors Q01 to Q04 are connected in a differential amplifier circuit. The signals from either end of the sense windings are applied to Q01 and Q03. The emitters are held at the difference voltage by a difference network composed of R04 and C01; noise voltages on the sense line are cancelled.

Capacitors C02 and C03, in the collector circuits of Q02 and Q04, provide d-c stabilization. Diodes CR01 and CR02 pass the negative-going components of the signals from Q02 and Q04, and serve as clippers. The bias across these diodes, and thus the clipping level, is adjustable by the Margin Switch on the operator's console. When the switch is up, +20v is applied to the junction of R14 and R15 raising the reference voltage across the input diodes to the last stage. When the switch is down, -20v is applied to R14 and R15 making the circuit more sensitive to the signal from the sense line which tends to make spurious pulses look like "1's". Transistors Q05 and Q06 are connected in an amplifier-inverter circuit. The output, a signal from CR05, as a result of a "1" signal from the sense wire, is -0.5v.

Sense Amplifier 56

# SENSE AMPLIFIER Type 57

The sense amplifier below amplifies the signal from a memory plane (pins 2 and 4) as the result of a read pulse, and produces a "0" output when a core switches. Transistors Q01, Q02, Q03, and Q04 form a differential amplifier which feeds T1 through coupling capacitors C02 and C03. The secondary of T1 is connected to a bridge detector so that the signal polarity at (A) is always the same. The Q05 network is a standard inverter circuit providing normal output logic levels of -3.0v and -0.5v.

Gain from the differential amplifier for the common mode component of the input signal is about 2; for the differential mode component, across R06 - C01, gain is about 100. Detector bias is determined by the Margin switch on the console. With the switch at HI, the +20v applied to pin 1 raises the reference level of the detector making it less sensitive; weak signals tend to be dropped. With the switch at LO, -20v appears at pin 1 and the detector is more sensitive to spurious pulses. No connection to pin 1 is made when the switch is in the normal, center position. Pin 6 is connected to the diverter bus (-7.0v) to provide bias for input transistors Q01, Q02. The output from Q05, as the result of a "1" signal on the sense lines, is -0.5v.

Sense Amplifier 57

Tape Current Source 74

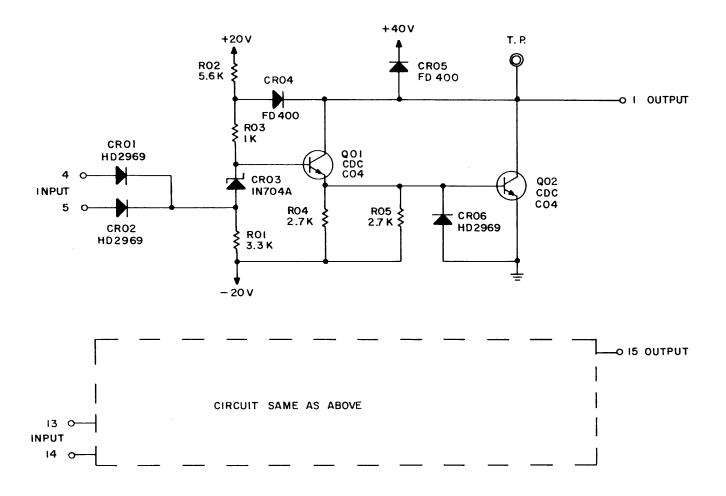

# EVEN PLANE INHIBIT DRIVER Card Type C00

## **FUNCTION**

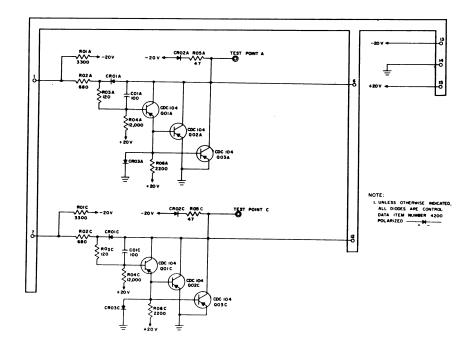

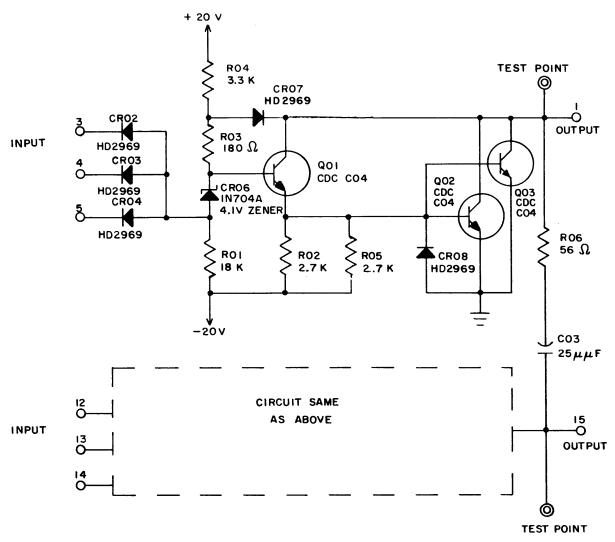

The function of the circuits on this card is to allow a 340 ma inhibit current to flow from the +40v source at pin 6 to the inhibit winding at pin 1 or pin 15. This occurs whenever all inputs to the respective circuit are at the logical "1" level of -5.8v. The inhibit circuit contains a series 120-ohm resistor so that the resulting current is approximately 340 ma.

## **OPERATION**

Each circuit has a three-way logical AND input, meaning that all inputs must be at the -5.8v "1" level in order for an input to be sensed. A -1.1v "0" signal on any input disables the AND. An unused input acts as a steady "1" if left open, or as a steady "0" if grounded.

A level-shifting action is provided to the base of Q01 by resistors R01, R02, R03, and the 4.1v zener diode CR05. The zener diode CR05 is reverse biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

When a -1. 1v "0" signal appears at an input, the zener diode CR05 places a forward bias on the base of Q01. Transistor Q01 then switches to a state of heavy conduction. It is held out of saturation by the feedback diode CR06 and its collector voltage is approximately +0.4v. The low collector voltage of Q01 is also the base voltage of Q02, which is connected as an emitter follower. The emitter voltage of Q02 is equal to its +0.4v base voltage minus its base-emitter junction drop, and is approximately -0.3v. This provides sufficient forward bias so that a minimum conduction is maintained through Q02. Transistor Q03 is connected as an emitter follower with the inhibit winding load in series with the emitter. The emitter of Q03 is connected to ground through the inhibit line. The base-emitter junction is therefore reverse biased by the -0.3v input, so that Q03 is cut off. This disables the current path from the +40v supply to the inhibit winding.

With the AND input satisfied by -5.8v "1" signals, the base of Q01 is biased at approximately -1.5v and Q01 is cut off. The collector voltage of Q01 rises to approximately +38.5v (40v minus the IR drop across R03 and R04). This provides drive to the

## NOTES:

- I. EACH CIRCUIT HAS THREE "AND" INPUTS.

- 2. TRANSISTORS QO2 & QO3 CONDUCT WHEN ALL INPUTS ARE -5.8 V "I".

- 3. ALL DIODES ARE HD2969 UNLESS OTHERWISE INDICATED.

## **EVEN PLANE**

Inhibit Driver C00

base-emitter junction of Q02. Transistor Q02 is connected as an emitter follower; thus its emitter voltage becomes approximately +38v. This provides a strong forward bias to the base of Q03, causing Q03 to conduct heavily. The voltage applied to the inhibit line is the emitter voltage of Q03 and is approximately +37.5v. The 340 ma inhibit current is also the emitter current of Q03, and is allowed to flow when Q03 switches to the conduction state.

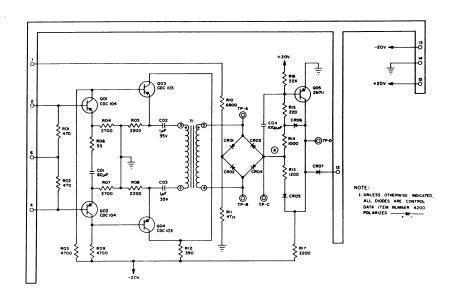

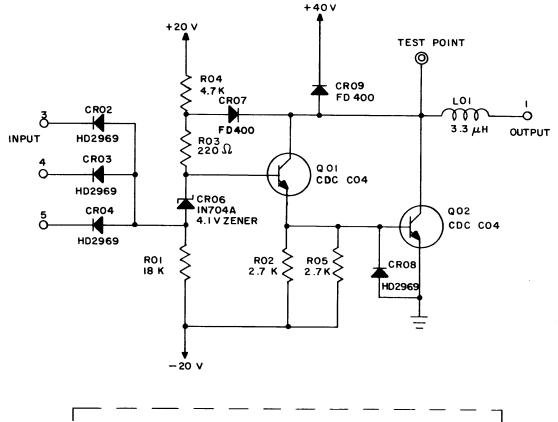

## LINE DRIVER

## Card Type C03

#### **FUNCTION**

The function of the circuits on this card is to enable 450 ma of positive current to flow from the output pins 1 or 15 to ground, whenever all inputs to the respective circuit are at the logical "0" level of -1. lv. Pins 1 and 15 connect to the two ends of the primary windings of eight memory driver transformers. During the memory cycle, one transformer will be center-tapped to +20v; thus current flow in either direction may be obtained by selecting one of the circuits on the C03 card.

The output pins 1 and 15 are connected as shown on page 3-C03-2 by capacitor C03 and resistor R06, which form a series differentiating network. This connection transmits only those signals having a high rate of change, such as a sharp noise spike, and blocks entirely a steady d-c voltage. Thus, a noise spike appearing at pin 1 also appears at pin 15, and their total effect is to cancel each other. However, the d-c levels of pins 1 and 15 are completely separated if either circuit switches to the conduction state while the other remains cut off.

## **OPERATION**

The two circuits on the card are identical and are labeled A and B. The following discussion of operation applies to either circuit; however, the component numbers mentioned are those appearing in circuit A.

A level shifting action is provided to the base and emitter of Q01 by resistors R01, R03, R04, and the 4.1v zener diode CR06. The zener diode CR06 is reverse biased so that its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

Each circuit has three logical OR inputs, meaning that a -5.8v "1" signal on any input is sensed, although a -1.1v "0" signal may be present simultaneously at another input. Any unused input acts as a steady "0", regardless whether it is grounded or left open.

When a -5.8v "1" signal appears at an input, the base of Q01 is biased at about -1v and it is cut off. The bases of Q02 and Q03 are held at approximately -0.3v by the forward drop of diode CR08, and they are likewise cut off. Thus, except for negligible leakage effects, pin 1 is completely isolated from ground and rises to a high positive voltage. Diode CR07 therefore provides a blocking action, preventing current from flowing

## NOTES:

- I. EACH CIRCUIT HAS 3 "OR" INPUTS.

- 2.TRANSISTORS SWITCH TO CONDUCTION STATE WHEN ALL INPUTS ARE  $-\ \text{I.I.V}$  "0".

Line Driver C03

through the transformer primary into pin 1.

If all of the circuit inputs are at the -1.1v "0" level, zener diode CR06 holds the base of Q01 at a positive voltage. This forward bias is sufficient so that Q01 conducts heavily, but it is held out of deep saturation by diode CR07 and resistor R03. Transistor Q01 in its conduction state allows the +20v source, which connects to pin 1 through the transformer primary, to bias the bases of Q02 and Q03 at a positive potential. Thus they also conduct heavily, and positive current is allowed to flow from pin 1 to ground with only a drop of approximately 1v across Q02 and Q03.

Transistors Q02 and Q03 are grounded emitter stages driven by the emitter follower stage Q01. Their base drive is taken directly from the emitter of Q01; thus the input to Q02 and Q03 follows the input to Q01 and is increased by the gain of Q01. When Q01 switches on, it attempts to bias the bases of Q02 and Q03 well into the positive voltage domain, so that they also switch on and conduct heavily. Likewise, when Q01 switches off, Q02 and Q03 also switch off, and the voltage drop across diode CR08 applies a reverse bias of approximately 0. 3v to the base-emitter junctions of Q02 and Q03 so that they are well into the cut off region.

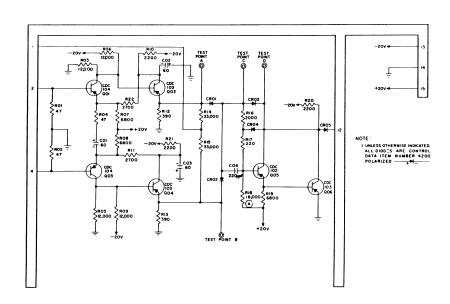

# ODD PLANE INHIBIT DRIVER Card Type C04

## FUNCTION

The function of the circuits on this card is to allow a 340 ma inhibit current to flow from pin 1 or 15 to ground, whenever all inputs to the respective circuit are at the logical "0" level of -1.1v. The inhibit wires are energized by a source of +40v, and each inhibit circuit contains a series 120-ohm resistor so the resulting current is approximately 340 ma. The odd plane inhibit wires terminate at either pin 1 or pin 15 of a C04 card, and the path is completed to ground allowing current to flow, if the respective inhibit generator circuit switches to its conduction state.

### **OPERATION**

The two circuits contained on the card are identical and are labeled A and B. The following discussion of operation applies to either circuit but the component numbers mentioned are those appearing in circuit A.

A level-shifting action is provided to the base and emitter of Q01 by resistors R01, R03, R04, and the 4.1v zener diode CR06. The zener diode CR06 is reverse biased so its operating point is beyond the knee of the breakdown region; thus the cathode remains approximately 4.1v positive with respect to the anode, regardless of current fluctuations.

Each circuit has three logical OR inputs, meaning that a -5.8v "1" signal on any input is sensed, although a -1.1v "0" signal may be present simultaneously at another input. Any unused input acts as a steady "0", regardless whether it is grounded or left open.

When a -5.8v "1" signal appears at an input, the base of Q01 is biased at about -1v and Q01 is cut off. The base of Q02 is held at approximately -0.3v by the forward drop of diode CR08, and Q02 is also cut off. Thus, except for negligible leakage effects, pin 1 is completely isolated from ground and rises to a high positive voltage. Diode CR07 therefore provides a blocking action, preventing current from flowing through the inhibit wire into pin 1.

If all of the circuit inputs are at the -1.1v "0" level, zener diode CR06 holds the base of Q01 at a sufficiently positive voltage so Q01 conducts heavily. In this state, diode

3-C04-1

REV. A

#### NOTES:

- I. EACH CIRCUIT HAS THREE "OR" INPUTS.

- 2.A CIRCUIT WILL SWITCH TO ITS CONDUCTION STATE WHEN ALL INPUTS ARE  $-1.1\,\mathrm{V}$  "O".

## ODD PLANE

Inhibit Driver C04

CR07 holds Q01 out of saturation. Transistor Q01 in its conduction state allows the +40v source, which connects through the inhibit wire to pin 1, to bias the base of Q02 at a positive level. Thus transistor Q02 also conducts heavily, and positive current is allowed to flow from pin 1 to ground with only a drop of 1v across Q02.

Transistor Q02 is a grounded emitter stage driven by the emitter follower stage Q01. The base drive for Q02 is taken directly from the emitter of Q01; thus the input to Q02 follows the input to Q01 and is increased by the gain of Q01. When Q01 switches on, it attempts to bias the base of Q02 well into the positive voltage domain, so Q02 also switches on and conducts heavily. Likewise, when Q01 switches off, Q02 also switches off, and the voltage drop across diode CR08 applies a reverse bias of approximately 0. 3v to the base-emitter junction of Q02 so it is well into the cut off region.