# PRELIMINARY COPY

I

I

ſ

I

I

CIP/2200 COMPUTER REFERENCE MANUAL 7 000 0076MA

December, 1972

The information contained in this manual is the property of Cincinnati Milacron and is furnished for customer use only. It is not an authorization to furnish this information to others.

# CIP/2200 Computer Reference Manual

Publication 7 000 0076MA

Errata Sheet

Page 16 Direct relative

The mode designator, bit 8, should be a 'l' instead of a '0'.

Line 4. After "--- 2's complement" add the word 'signed'.

Indirect relative

Line 3. Insert the word 'signed' between "complement" and "dis-placement".

Page 39 Line 3. "LDX/" should read "LDX=".

- Page 44 In "LRA Logical Right A" the shifting diagram should show register A and not B.

- Page 75 "MVL Move character string left" should have an op-code of 5C and not 5A.

- Page 76 "MVR Move character string right" should have an op-code of 5D and not 5B.

- Page 112 Add the words "and clear high" to the comments of the two 13XX instructions.

# Table of Contents

| 1.0 | INTRODUCTION                               | 4   |

|-----|--------------------------------------------|-----|

| 2.0 | GENERAL CHARACTERISTICS                    | 6   |

| 2.1 | Basic Machine Architecture                 | 6   |

| 2.2 | Information Formats                        | 9   |

| 2.3 | Memory Addressing                          | 15  |

| 2.4 | Interrupt Structure                        | 19  |

| 2.5 | Input/Output Facilities                    | 21  |

| 2.6 | Control Stack Facility                     | 24  |

| 3.0 | MACHINE INSTRUCTIONS                       | 27  |

| 3.1 | Binary Arithmetic and Logical Instructions | 27  |

| 3.2 | Shift Instructions                         | 41  |

| 3.3 | Variable Word Length Instructions          | 47  |

| 3.4 | Memory Immediate Instructions              | 56  |

| 3.5 | Memory to Memory Instructions              | 60  |

| 3.6 | Transfer of Control Instructions           | 81  |

| 3.7 | Control Instructions                       | 90  |

| 3.8 | Input/Output Instructions                  | 95  |

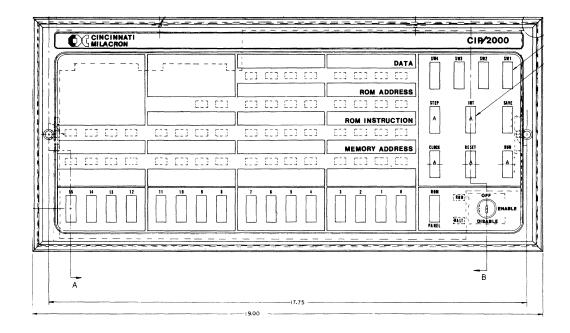

| 4.0 | COMPUTER OPERATION                         | 104 |

| 4.1 | Front Panel                                | 104 |

| 4.2 | Basic Panel Operation                      | 105 |

| 4.3 | System Panel Operation                     | 109 |

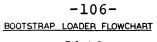

| 4.4 | Bootstrap Loader                           | 114 |

| 4.5 | Disk IPL Option                            | 115 |

I

I

.

Į,

hai

**1** 1

1717) Maria

I

I

I

I

I

I

I

I

I

I

I

# APPENDIXES

| Α. | Instructions Listed Numerically by Opcode | 117 |

|----|-------------------------------------------|-----|

| Β. | Instructions Listed Alphabetically        | 122 |

| С. | Instruction Execution Times               | 127 |

| D. | Power Fail/Auto Restart Programming       | 133 |

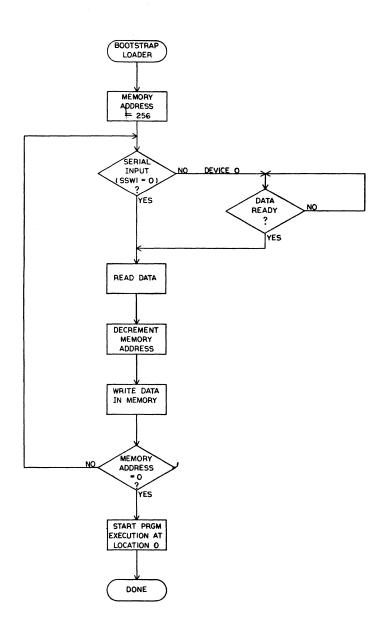

| Ε. | DMA Channel Programming                   | 135 |

| F. | Firmware Extension Procedures             | 138 |

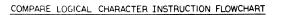

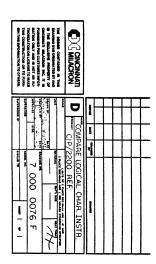

| G. | Instruction Flowcharts                    | 142 |

| Н. | Dedicated Memory Locations                | 147 |

| Ι. | Internal Codes                            | 149 |

:

-3-

**1**

ľ

## 1.0 INTRODUCTION

The CIP/2200 is a general purpose byte oriented minicomputer designed primarily for dedicated system applications. The CIP/2200 has an extensive instruction set including binary and decimal arithmetic capability, character string and bit manipulation instructions.

The CIP/2200 has an 8 bit hardware data path and memory. The CPU registers, however are 16 bits in length. The instruction set includes a complete set of 16 bit register to memory and register to register binary arithmetic instructions. In addition to the 16 bit word instructions, the CIP/2200 includes a variable length binary arithmetic capability, allowing binary arithmetic to be performed on 8, 16, 24, or 32 bit data without resorting to multiple precision software routines. A third group of instructions provides memory to memory decimal arithmetic on ANSCII format character strings up to 16 digits in length. Other memory to memory operations include character string move and compare, code conversion, and decimal editing.

Main memory consists of 8 bit/byte or 9 bit/byte core memory with a 1.1 microsecond full cycle time. Memory is expandable in 8k byte modules from a minimum of 8k bytes to a maximum memory size of 32k bytes. Memory parity protection is available as an option on systems with 9 bit/byte memory.

The CIP/2200 I/O structure consists of a microprogrammed serial I/O interface, a byte I/O facility, firmware supported Direct Memory Channel concurrent transfers, and the capability of attaching up to two independent Direct Memory Access (DMA) processors. The serial I/O interface is a microprogram for controlling serial data transfers, normally used to control a teletype or other similar terminal device. The byte I/Ofacility is used for transmission of 8 bit data between any one of up to 32 peripheral devices and either an accumulator register or main memory under program control. Associated with the byte I/O facility is the external priority interrupt system. The CIP/2200 has a capacity for up to 64 external priority interrupts. Byte I/O interfaces normally contain the logic for data transfer related interrupts. Non device-related interrupts may be added in groups of 8 for a total of 64 interrupts.

The Direct Memory Channel feature (DMC) allows microprogram controlled, high speed data transfer to occur concurrently with program execution. The maximum DMC transfer rate is 86,000 bytes per second for asynchronous devices and 25,000 bytes per second for synchronous devices. Requirements for faster operation (up to 910,000 bytes per second) may be filled with a hardware Direct Memory Access processor. The Direct Memory Access unit is an independent hardware controller which competes with the CPU for use of main memory time.

The CIP/2200 is a microprogrammed general purpose minicomputer based on the CIP/2000 Computer. The use of microprogramming has allowed instructions of considerable power and flexibility to be implemented at modest cost. Microprogramming offers the user the added power of features such as a bootstrap loader, an integral serial I/O facility, a high speed Direct Memory Channel, and complex instructions such as "Edit and Mark" and "Translate and Test under Mask" in a low cost system. The CIP/2200 provides special instructions to allow transfer of control to special user written application microprograms for greater flexibility in meeting specific system requirements.

#### .0 GENERAL CHARACTERISTICS

#### .1 Basic Machine Architecture

#### Registers

The CIP/2200 has three programmable registers, the accumulator (A), the accumulator extension (B), and the index register (X). Two other registers, the program counter (P) and the status register (S) are also of importance to the programmer.

The A register is the 16 bit main accumulator register. It is an operand source for all binary arithmetic and logical instructions, and receives the result of all binary operations except store. Serial and byte mode I/O operations may transfer data to or from the low 8 bits of the A register.

The B register is also 16 bits in length and serves as an accumulator extension for variable length binary arithmetic and logical operations. Byte mode I/O operations may transfer data to or from the low 8 bits of the B register.

The index register (X) is a 16 bit register used for address modification and base relative addressing. Several specialized instructions are provided for index value modification.

The P register (program counter) contains the address of the next machine instruction to be executed. The P register contents are stored by the subroutine transfer instruction (RTJ) and are altered by transfer of control instructions (jump, skips, etc.). When an instruction modifies the P register contents, the address of the next machine instruction to be executed is determined by the contents of the P register after it has been modified.

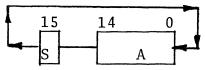

The status register (S) is an 8 bit register containing the CIP/2200 internal status indicators. The indicators are stored as shown in the illustration below. The meaning of each indicator is described in Figure 2-1.

| 7                                          | 6   | 5   | 4                               | 3                             | 2                                               | 1   | 0                     |  |

|--------------------------------------------|-----|-----|---------------------------------|-------------------------------|-------------------------------------------------|-----|-----------------------|--|

| PF                                         | E/Z | L/Ø | H/M                             | INT                           | ØV                                              | WL  |                       |  |

|                                            |     |     |                                 |                               |                                                 |     | -                     |  |

| MNEMON                                     | IC  |     | NAM                             | E                             |                                                 |     |                       |  |

| PF<br>E/Z<br>L/Ø<br>H/M<br>INT<br>ØV<br>WL |     |     | Equ<br>Low<br>Hig<br>Int<br>Ove | al/Zerc<br>/Ones R<br>h/Mixed | os Resu<br>Result<br>I Resu<br>System<br>Indica | tor | icato<br>tor<br>catoi |  |

Figure 2-1. CIP/2200 Status Register

Power Failure (PF)

The power failure indicator reports the status of the computer's electrical power supply. The power fail/ automatic restart option monitors the power supply and generates an internal interrupt whenever the input power line voltage becomes insufficient for reliable operation. The firmware detects the interrupt, sets the power failure indicator, and causes the CIP/2200 program to transfer to a user programmed power failure interrupt service routine. When normal power supply voltage is restored, the power fail/automatic restart option causes another internal interrupt. The firmware, in response to the power restart indication, resets the power failure indicator and transfers to the user written power restart routine. If the power fail/automatic restart option is not installed, the power failure indicator is set to zero by a RESET and is not changed by the hardware.

Arithmetic and Logical Indicators  $(E/Z, L/\emptyset, H/M)$

The indicators represented by bits 4-6 of the status register are collectively called the arithmetic and logical indicators (ALI). These three bits are used to save information about the results of the memory to memory and memory immediate arithmetic and logical instructions. Only one indicator will be set at any given time. The "E/Z" (Equal/Zeros result) indicator is set when the operands of a compare are equal or when the result of an arithmetic or logical operation is zero. The "L/Ø" (Low/Ones result) indicator is set when the source of a compare is lower (more negative) than the target, when the result of an arithmetic operation is negative, or when the result of a logical operation contains all ones. The "H/M" (High/Mixed result) indicator is set when the source of a compare is higher (more positive) than the target, when the result of an arithmetic operation is positive, or when the result of a logical operation contains mixed ones and zeros.

The meaning of the individual indicators depends upon the type of operation which caused them to be set. For example, an arithmetic operation which produces a negative (low)result will cause bit 5, the Low/Ones indicator, to be set. Similarly, a logical operation which causes all bits of the result to be ones will also set the Low/Ones indicator. Note that the arithmetic and logical indicators are set only by the memory to memory and memory immediate instructions and are not altered by binary arithmetic and logical instructions. The indicators may be tested with a conditional branch instruction; testing does not cause the indicators to be reset.

Interrupt System Disabled Indicator (INT)

The INT indicator reports the external interrupt system status. The INT indicator is zero when external interrupts are enabled and one when they are disabled or masked. The INT indicator is meaningless in systems which do not have the interrupt enable/disable option installed.

#### Overflow Indicator (ØV)

The overflow indicator is set when an arithmetic overflow is detected during a binary or decimal arithmetic operation. The overflow indicator may be tested and reset by conditional skip instructions or tested without resetting by a conditional branch instruction. Instructions are also provided to set and reset the overflow indicator without testing.

The overflow indicator is not reset by binary arithmetic operations. Thus, an overflow test over multiple binary operations may be achieved by resetting the indicator before the sequence of instructions to be tested and testing after the last operation. If one or more of the instructions caused an overflow, the indicator will be set.

An arithmetic overflow occurs when the result of an operation is too large to be contained in the receiving field or register. For decimal operations this occurs whenever the target field is shorter than the source field, or when a carry occurs when operating on the leftmost target digit. For example, when 10 is added to 995 in a three digit field, an overflow occurs. A binary overflow occurs whenever the result of the operation is too large to be contained by the receiving register. This condition is detected by comparing the carry into and out of the sign bit (left-most bit) of the register; if these carries are not the same an overflow has occurred.

Word Length Indicator (WL)

The word length indicator defines the word length currently in effect for variable length binary operations. Variable length data may be from 1-4 bytes long. Values of  $00_2$  to 112 in the two bit word length indicator correspond to variable data sizes of 1 to 4 bytes, respectively. The word length value is set programmatically with control instructions. A system reset causes the word length to be set to 1 byte (WL = 002).

#### System Save Area

The system save area is a 16 byte area of memory reserved for use by the CIP/2200 firmware. The system save area is located immediately after the external interrupt locations, from  $180_{16}$  to  $18F_{16}$ .

# 2.2 Information Formats

The 8 bit byte is the basic data element from which all data, addresses, and instructions are formed. The bits within the byte are numbered from 7 to 0 from left to right.

An optional 9th bit may be added to each byte in memory to provide a memory parity check. This 9th bit is used only to detect memory malfunctions and is set, reset, and checked in hardware by the memory parity check option. The CPU cannot alter or sense the parity bit.

Three basic types of information are used by the CIP/2200: data, addresses, and instructions. Data are items of information acted upon by the computer as directed by the program, and may have several forms. Addresses are information items containing the location of other items in memory. An address may be either part of an instruction or a separate item. In the latter case, the address is often referred to as a "pointer" since the address "points to" the location of some other item. Instructions are the information items which control the action of the computer.

#### Data Formats

Data may be stored and processed in several forms by the CIP/2200. The form chosen depends upon the nature of the data and the operations to be performed. Numerical data may be represented in either 2's complement notation binary (base 2) or sign and magnitude notation decimal (base 10) form. Logical data are represented as unsigned binary items. Alphanumeric data (text) are represented as strings of bytes, each byte being the ANSCII code for a single character.

| Halfword                        | 7<br>S              | 0  |                  |    |               |          |                                       |                        |    |

|---------------------------------|---------------------|----|------------------|----|---------------|----------|---------------------------------------|------------------------|----|

| Fullword or Word                | 15<br>S             | 8  | 7                | 0  |               |          |                                       |                        |    |

| Extended Word                   | 23<br>S             | 16 | 15               | 8  | 7             | 0        | -                                     |                        |    |

|                                 | 31                  | 24 | 23               | 16 | 15            | 8        | 7                                     | 0                      |    |

| Double Word                     | S                   |    |                  |    |               |          |                                       |                        |    |

| Data Format                     | Assembler<br>Coding |    | Size             |    | Range         |          |                                       |                        |    |

| Halfword<br>Fullword<br>or Word | H'n'<br>F'n'        |    | 1 byte<br>2 byte | S  | -128<br>-3276 | 8        | n <u>&lt;</u> 1<br><u>&lt; n &lt;</u> | 27<br>327              | 67 |

| Extended Word                   | E'n'                |    | 3 byte           | S  | -8,38         | 8,<br>88 | $\frac{608}{607}$                     | n                      |    |

| Double word                     | D'n'                |    | 4 byte           | S  | <pre></pre>   | 7,<br>47 | 483,6<br>,483,                        | 48<br>647 <sup>≤</sup> | n  |

Figure 2-2 Binary Data

Binary data may be stored and processed in either 2 byte (16 bit) words or in variable length byte strings up to 4 bytes ( $\overline{32}$  bits) in length. The address of a data item is the address of the leftmost (most significant) byte. The lower order bytes occupy higher addressed bytes in memory. The various binary data formats, the range of values representable in each format, and the assembly language specification for each are shown in Figure 2-2.

Decimal numbers are represented within the CIP/2200 as strings of ANSCII decimal digit characters in memory. Decimal numbers may vary in length from 1 to 16 digits. Each digit is represented in memory as one byte containing an ANSCII zoned decimal digit. The low four bits (bits 3-0) of the byte contain the binary equivalent of the decimal digit. The high four bits (bits 7-4, the zone bits) of a decimal operand digit contain the ANSCII decimal digit zone, 10112, with the exception of the low order digit (highest addressed byte) of a decimal number. The zone bits of the low order digit of a number contain the sign of the decimal number. A minus sign is represented by zeros in the zone of the low order bits; a plus sign by a zone of 10112 ( $B_{16}$ ).

The illustration in Figure 2-3 shows typical decimal numbers as they appear in memory. The leftmost byte is the addressed byte; the remainder of the number occupies successively higher locations in memory.

| Assembler Coding | Ma  | chine | Repr | esent | ation | (hex | <u>;)</u>   |

|------------------|-----|-------|------|-------|-------|------|-------------|

| Z'123456'        |     | B 1   | B 2  | B 3   | B 4   | B 5  | B 6<br>Sign |

| Z'-0123456'      | B 0 | B 1   | B 2  | B 3   | B 4   | B 5  | 06<br>Sign  |

Figure 2-3 Decimal Data

Logical data is represented as either 2 byte words or variable length byte strings of from 1 to 4 bytes. The representation is similar to binary data, except that logical data is unsigned.

Alphanumeric data (text) and other character string data are represented in the CIP/2200 as variable length byte strings in memory. The individual bytes are treated as unsigned 8 bit logical items. Byte strings of from one to 256 bytes may be operated upon by memory to memory instructions. The standard internal code used by the CIP/2200 is ANSCII with bit 7 set to a 1 (See Appendix I), but other codes (e.g., EBCDIC) may be used as desired by the programmer. The CIP/2200 CPU is insensitive to the choice of code except for decimal number representation and certain characters used for editing. I/O devices and system software, however, are code sensitive and usually require ANSCII code.

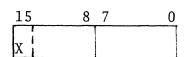

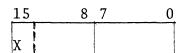

Addresses are represented in several forms within the various instructions. Addresses not part of an instruction (pointers) are always represented in memory as 2 byte words as shown below. The memory address appears as

| 15 | 8 | 7 | 0 |

|----|---|---|---|

| x  |   |   |   |

a 15 bit positive integer in bits 14-0 of the address word; an address word can therefore address 32,768 different bytes. Since negative addresses are not used, the sign

bit (bit 15) of an <u>address</u> is always zero and is not needed. The sign bit of an <u>address word</u> is therefore available to specify indexing. A 1 in bit 15 of an address word in memory is used to indicate that the effective address is the sum of the index register contents and the address contained in bits 14-0 of the address word. If bit 15 is a 0, the effective address is simply the value stored in bits 14-0 of the address word.

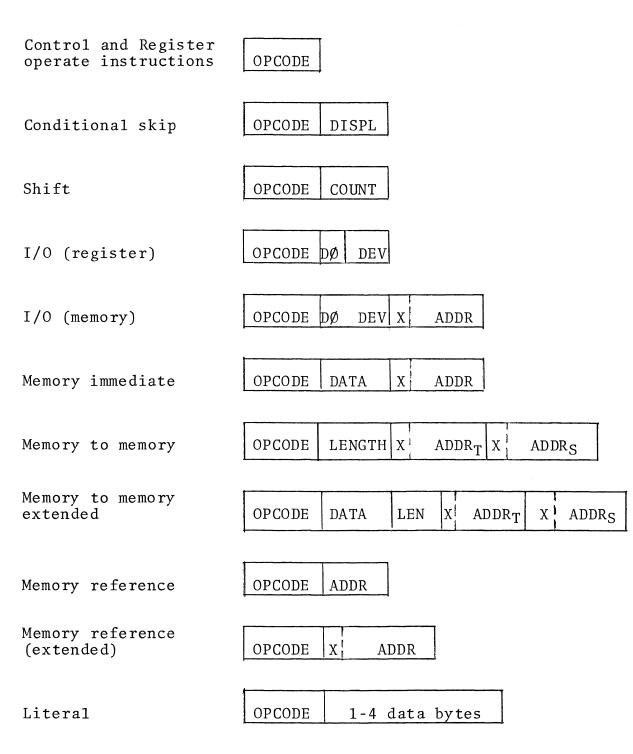

Instructions

CIP/2200 instructions vary in length from one to eight bytes depending upon the number of memory addresses required, the addressing modes specified, and the other information contained in the instruction. Variable instruction length permits efficient utilization of memory while permitting a wide range of instruction types. In all cases the first byte of the instruction contains a code indicating the operation to be performed. The second byte of less frequently used instructions contains an extended operation code. The basic instruction formats are shown in Figure 2-4.

The control and register operate instructions do not refer to memory and consist of a one or two byte operation code Conditional skip instructions allow the program to only. test various machine conditions and alter the execution path of the program depending upon the result. Conditional skips have a one byte displacement address allowing control to be transferred to instructions within + 128 bytes of the conditional skip. Shift instructions also use the two byte format; the first byte contains the operation and the second byte contains the count of bit positions to be shifted. Input and output (I/0) instructions require either two bytes (for transfers to or from a register) or four bytes (for transfers to or from memory). Memory immediate instructions occupy four bytes and provide various operations between a data byte in the instruction itself and a byte in memory. The memory to memory format is used for decimal arithmetic and byte string operations.

The memory reference, extended memory reference, and literal formats are used by most binary arithmetic, logical, and transfer of control instructions. Eight addressing modes allow considerable flexibility and power while conserving memory.

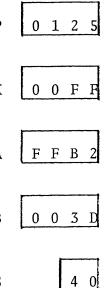

The CIP/2200 provides a control stack mechanism to aid the programmer in saving the machine state when entering subroutines or interrupt service routines. The machine state saved on the stack by the save instruction consists of the contents of the program counter (P), the machine status register (S), and the B, A, and X registers as shown below.

Ρ S В А Х

The status register contains the most recent arithmetic or logical indicator setting, the overflow indicator, the external interrupt enable state, the word length currently in effect, and the state of the power fail detector. The full machine state may be saved on the stack or returned to the active registers by the save and return instructions.

Figure 2-4 CIP/2200 Instruction Formats

# 2.3 Memory Addressing

The CIP/2200 has the capability of addressing up to 32,768 bytes of memory. The basic addressing mode, extended addressing, utilizes a 16 bit address word. The low 15 bits contain the binary value of the address. Bit 15 is used to request indexing. Indexing may be specified for any memory reference using extended addressing. A single

level of indirect addressing is provided for certain memory referencing instructions. When indirect addressing is used, the address word specified by the

instruction may be indexed.

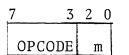

In addition to extended addressing, many memory reference type instructions have seven other addressing modes, for a total of eight modes. These additional addressing modes include various short (1 byte) address types, literal address ing, and indirect addressing. The low three bits of the operation code byte of these instructions contain a three bit addressing mode, m, as shown below. The remainder of

the instruction consists of from zero to four bytes depending on the addressing mode selected. The operation specified in bits 3-7 of the instruction is performed on the data located at the <u>effective</u>

address (EA), the memory location specified by the result of the indicated address computation.

The individual addressing modes are discussed in the following paragraphs. Modes 2 and 3, (and mode 7 for JMP and RTJ) specify indirect addressing. In all three cases the effective address is the location specified by an address word. The effective address is the contents of bits 14-0 of the address word if bit 15 is 0. A one in bit 15 causes the

address specified by bits 14-0 of the address pointer to be modified by addition of the contents of the index register.

Direct page 0 (m=0) EA = ADDR

| 15   | 11 | 10 | ) | 8 | 7 |      | 0 |

|------|----|----|---|---|---|------|---|

| OPCC | DE | 0  | 0 | 0 |   | ADDR |   |

The effective address is given by the second byte of the instruction. This mode allows a short, fast

means for accessing data in the first 256 locations in memory. Direct page zero addressing is commonly used for sharing data between programs. Considerable savings in program size can result from placing commonly used data (such as system parameters) on page zero. Direct relative (m=1) EA = (P) + DISPL

| 1 | 5 11   | L   | 1( | ) | 8 | 7 | 6 |       | 0 |

|---|--------|-----|----|---|---|---|---|-------|---|

|   | OPCODI | 111 | 0  | 0 | 0 | s |   | DISPL |   |

The effective address is given by the sum of the program counter (P) and the 2's complement

eight bit displacement contained in the second byte of the instruction. The program counter contains the address of the first byte of the next instruction when the address computation is performed. A displacement of zero, therefore, addresses the next instruction. This mode provides a savings in memory required when addressing the 256 byte area of memory around the current instruction, from 127 bytes ahead to 128 bytes behind the first byte of the next instruction. Since programs tend to refer most frequently to nearby locations, this mode allows considerable economy of storage. Note that this mode is identical to the addressing mode of the conditional skip instructions.

Indirect page 0 (m=2) EA = (ADDR)

| 15  | 11   | 1( | ) | 8 | 7 |      | 0 |

|-----|------|----|---|---|---|------|---|

| OPC | CODE | 0  | 1 | 0 |   | ADDR |   |

The second byte of mode 2 instructions contains an 8 bit absolute address specifying a location in

page zero. The two byte address word at the specified location is used to obtain the effective address as explained above for indirect addressing. Indexing may be specified by the indirect address word. This mode provides a convenient means of using shared address pointers.

Programming Note: A series of page zero pointers (a transfer vector) may be used to provide dynamically alterable linkage between subroutines.

Indirect relative (m=3) EA = ((P) + DISPL)

| 15 11  | 1 | 0 | 8 | 7 | 6 0   |

|--------|---|---|---|---|-------|

| OPCODE | 0 | 1 | 1 | s | DISPL |

The sum of the contents of the program counter and the 8 bit 2's complement displacement gives the address

of an address word. The address word is evaluated to form the effective address. This mode provides a means of sharing address words located within a section of a program. Indirect relative addressing also provides a means of returning from a subroutine by an indirect jump. Programming Note: Indirect relative addressing can be used to save memory by sharing address words when multiple instructions located close together refer to a distant location. One reference is made to the desired datum using extended addressing (mode 6). All other references within relative range can be made indirect relative using the extended address word portion of the mode 6 instruction as a pointer.

Base addressing (m=4) EA = (X)

7 3 2 0 OPCODE 1 0 0 This mode provides a fast, one byte instruction format. The effective address is the contents of the index register (X). Mode 4 addressing is

particularly useful for string processing or table procassing where the index register is used to point to the byte in the string or entry in the table currently being processed.

Base plus displacement addressing (m=5) EA = (X) + DISPL

| 15 1   | 1 | _1( | ) | 8            | 7 |       | 0 |

|--------|---|-----|---|--------------|---|-------|---|

| OPCODI | G | 1   | 0 | 1            |   | DISPL |   |

|        | G | L T | U | - <b>T</b> ] |   | DISPL | 1 |

The effective address is given by the sum of the contents of the index register and the 8 bit

unsigned displacement contained in the second byte of the instruction. This mode may be regarded as an indexed page zero address (for page zero data tables) or as a base plus displacement mode where the index register contains the address of the datum.

Extended addressing (m=6) EA = ADDR or ADDR + (X)

| 23 19  | 1 | 8 | 16 | 15 | 0    |

|--------|---|---|----|----|------|

| OPCODE | 1 | 1 | 0  | x  | ADDR |

This mode is the basic addressing mode discussed

in the beginning of this section. If indexing is not specified, the effective address is contained in the low 15 bits of the second and third bytes of the instruction. If indexing is specified, the effective address is the sum of the contents of the ADDR field and the index register. This mode allows addressing of all of a fully expanded 32,768 byte memory. Literal addressing (m=7) EA = 2nd byte of instruction

|              |                  | Literal       |

|--------------|------------------|---------------|

|              |                  | addressing    |

| OPCODE 1 1 1 | DATA (1-4 bytes) | provides a    |

|              |                  | means of cod- |

ing data in the instruction itself, thus saving the memory otherwise required to specify the address of the data. The length of the data may vary from one to four bytes depending upon the requirements of the opcode.

Extended indirect addressing (m=7, jump and return jump only) EA = (ADDR or ADDR + (X))

| I |        |   |   |   | · · |      |

|---|--------|---|---|---|-----|------|

|   | OPCODE | 1 | 1 | 1 | Х   | ADDR |

| _ |        |   |   |   |     |      |

bytes of the instruction is evaluated as described for mode 6. The result specifies the location of an address word, which is evaluated to form the effective address of the instruction. This mode is provided in lieu of literal addressing for the jump and return jump (subroutine transfer) instructions. Extended indirect addressing provides a means of utilizing transfer vectors (jump tables) outside of page zero.

The assembly language coding of the various addressing modes is shown below.

| ADDR    | modes 0,1                    | (direct page zero and direct                                          |

|---------|------------------------------|-----------------------------------------------------------------------|

|         |                              | relative)                                                             |

| ADDR    | modes 2,3                    | (indirect page zero and in-                                           |

|         |                              | direct relative)                                                      |

|         | mode 4                       | (base addressing)                                                     |

| Ν       | mode 5                       | (base plus displacement)                                              |

| ADDR(X) | mode 6                       | (extended addressing)                                                 |

| DATA    | mode 7                       | (literal addressing)                                                  |

| ADDR(X) | mode 7                       | (extended indirect addressing                                         |

|         |                              | for JMP and RTJ only)                                                 |

|         | ADDR<br>N<br>ADDR(X)<br>DATA | ADDR modes 2,3<br>mode 4<br>N mode 5<br>ADDR(X) mode 6<br>DATA mode 7 |

Figure 2-5 Address Mode Assembly Language Coding

The address word located in the second and third

#### 2.4 Interrupt Structure

#### Basic Interrupt Action

The CIP/2200 interrupt system is responsive to two types of interrupts. <u>Internal interrupts</u> are generated by the computer on the occurrence of an operational fault, a console interrupt, or by the interval timer. <u>External</u> <u>interrupts</u> are generated by an I/O device or another <u>externally</u> supplied signal. Each interrupt is assigned an address word in main memory called an interrupt transfer location. These assignments are shown in Fig. 2-6.

The interrupt transfer location specifies the address of a software routine which will be executed whenever the associated interrupt is recognized. When an interrupt occurs, the computer responds by executing a subroutine transfer of control to the address specified by the interrupt transfer location. This mechanism for interrupting the execution of one program and starting execution of another program allows the computer to respond to external events and execute the appropriate portions of the program on a priority basis.

| Location                                                                                        | Assignment                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 080-081<br>082-083<br>086-087<br>08A-08B<br>08C-08D<br>08E-08F<br>090-091<br>100-101<br>102-103 | Console Interrupt<br>DMA Channel Interrupt<br>Interval Timer Interrupt<br>Memory Parity Error Interrupt<br>Control Stack Under/Overflow Interrup<br>Power Fail Interrupt<br>Power Restart Interrupt<br>External Interrupt 0<br>External Interrupt 1 |

| 17E-17F                                                                                         | External Interrupt 63                                                                                                                                                                                                                               |

Figure 2-6 Interrupt Transfer Locations

#### Internal Interrupts

The internal interrupts are used to report computer operation faults or the occurrence of events with a high priority. Internal interrupts are generated by the console interrupt switch or a trap instruction, the DMA channel, the interval timer, the memory parity option hardware, a control stack under/overflow, and the power fail/restart option hardware.

The console interrupt is generated by depressing the console interrupt switch on the computer front panel or by executing a trap instruction.

The DMA channel interrupt is generated by the DMA processor at the end of a DMA transfer. If a system has more than one DMA processor, both interrupts will occur through the same interrupt transfer location. A status check on one of the DMA processors must be used to determine which one interrupted. For details of operation of the DMA channel, refer to the DMA processor manual and Appendix E.

The interval timer interrupt occurs when the interval timer counter value reaches zero. The interval timer counter in memory locations 84 - 85<sub>16</sub> is incremented by the interval timer (real time clock) option on the processor option board. The rate at which the timer is incremented is selected by jumpers on the processor option board. The board is supplied with the jumpers set for a 1 millisecond interval, but other intervals may be obtained by changing the jumpers as described in the Processor Option Board Manual (publication #7 000 0052MA). The EIT and DIT instructions are used to start and stop the interval timer.

The memory parity failure interrupt occurs when a parity failure (an odd number of bits in a byte) is detected by the memory parity check option hardware. The memory parity check option consists of a 9 bit memory and the parity check option on the processor option board. If the memory parity check option is not supplied, the interrupt will not be generated.

The control stack under/overflow interrupt is caused when the control stack cannot hold or supply sufficient data. This interrupt can only occur as a result of execution of a save or return instruction (SAV, RET, or RTN; see Section 2.6). The power failure interrupt occurs when the primary power supply voltage becomes insufficient for reliable computer operation. The power restart interrupt occurs when the power supply is restored to the computer after a power failure. Certain requirements must be met by the power failure interrupt service routine if the contents of memory and the machine state are to be preserved. Refer to Appendix A for notes on the design of this program. The power fail and automatic restart interrupts are set by the power fail/automatic restart option on the processor option board, and will not occur unless that option is installed.

#### External Interrupts

External interrupts may be generated by I/O device controllers or other external hardware devices. The CIP/2200 has provision for a total of 64 external interrupts. The external interrupt system may be disabled (masked) to defer recognition of interrupt requests if the interrupt enable/disable option is installed.

# 2.5 Input/Output Facilities

The CIP/2200 provides four basic types of I/O transfers ranging from bit serial transfers at 10 characters per second to Direct Memory Access (DMA) byte transfers at 910,000 bytes per second. The serial I/O facility is a low speed interface suitable for operating a low speed terminal device. Byte I/O provides either program loop or interrupt I/O capabilities for medium speed devices. The Direct Memory Channel (concurrent I/O) facility provides a firmware managed high speed data transfer at a rate of up to 86,000 bytes per second concurrent with and transparent to normal program execution. Direct Memory Access I/O utilizes a separate hardware channel into memory to provide extremely fast I/O at the maximum memory rate of 910,000 bytes per second.

#### Serial I/O

The serial I/O interface provides a simple, inexpensive means for communicating with a teletype or other similar terminal device. The serial I/O interface is a microprogram which controls the transfer of bit serial data between the computer and a serial I/O device. Serial mode transfers always use the low 8 bits of the A register as the output source or input target. The data transfer rate is 110 bits per second. Program execution and detection of all interrupts is suspended during a serial I/O transfer.

#### Byte I/O

The CIP/2200 byte I/O facility provides for program controlled data transfers over the byte I/O bus. Each byte of data transferred to or from an I/O device controller requires the execution of an I/O instruction. The byte I/O bus is also used to transfer status information from devices to the computer and to transmit function bytes containing control information to the devices. The byte I/O facility is related to the external interrupt facility in that device controllers are able to cause an interrupt when ready for a data transfer or when an error is detected. The interrupt service routine then uses the byte I/O instructions to test the device status and to take appropriate action. This allows I/O transfers to be overlapped with background (non-interrupt) program execution.

The byte I/O facility may also be used without interrupts by testing the device status continually until the device is found to be ready to accept or send data. The upper limit of the byte I/O transfer rate is approximately 10,000 bytes per second.

The byte I/O facility offers considerable flexibility to the programmer. Data and status or control information can be transferred between external devices and the A or B register or memory. Up to 32 device controllers may be connected to the byte I/O bus.

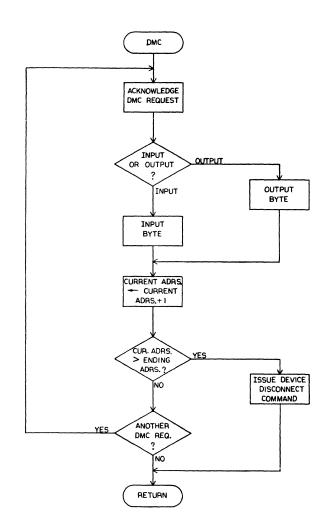

Direct Memory Channel (DMC)

The Direct Memory Channel (concurrent I/O) facility allows automatic block data transfers between devices attached to the byte I/O bus and memory. DMC transfers are firmware controlled and occur concurrently with normal program execution.

Concurrent operation of I/O and program execution is accomplished by assigning higher priority to DMC data transfers than to instruction execution. Before each instruction is executed, a firmware check is made for pending DMC transfers. All such data transfers for DMC operations are finished before an instruction is executed. A DMC transfer may also force short breaks in the execution of long instructions.

The maximum rate at which DMC transfers can occur is determined by the time between the arrival of a data transfer request and the servicing of that request by the micro-The microprogram tests for pending DMC requests program. at discrete intervals. The longest interval possible between the occurrence of a DMC transfer request by the highest priority DMC controller and the answering data transfer is 40 microseconds. The CIP/2200 can therefore support a 25,000 byte/second transfer rate for a single synchronous device. (A synchronous device is a device which requires data transfers at a fixed rate determined by the device itself, for example, a magnetic tape drive.) When multiple devices are simultaneously transferring data, the maximum time between a request and the transfer is 40 microseconds for the highest priority device, 52 microseconds for the second highest priority device 64 microseconds for the third highest priority device, and The maximum aggregate data transfer rate for the so on. DMC channel is approximately 86,000 bytes/second. This rate can be maintained only if requests arrive at less than 12 microsecond intervals. Since service for these requests can only be guaranteed at a rate of 25,000 bytes/second, rates of more than 25,000 bytes/second can only be supported on asynchronous devices (devices with variable transfer rate, i.e., devices which can operate at rates slower than the maximum such as a tape perforator).

The location and amount of data transferred during a DMC block transfer operation is determined by a four byte DMC descriptor. A two word (4 byte) dedicated page zero location is reserved for the DMC descriptor for each I/O The address of this descriptor is calculated device. by multiplying the device number by 4. The descriptor contains two address words, a current address and an ending address. The current address word contains the address of the next byte to be transferred by the I/OThe ending address word contains the address operation. of the last byte to be transferred. The current address is incremented after each byte transfer. When the current address becomes greater than the ending address, the DMC operation is terminated.

DMC operations are started by initializing the descriptor and executing the appropriate byte I/O instruction. After a DMC I/O operation is initiated by a processor instruction, byte transfers proceed automatically until the last byte of the block is transferred. An interrupt may be triggered at the end of a DMC transfer if the programmer so requests. If termination with interrupt is used, the interrupt occurs through the interrupt transfer location assigned to that I/O device. The address of the device interrupt location is twice the device address plus  $100_{16}$ . If termination without an interrupt is desired, the program must check the device status word to determine the state of the DMC transfer.

# DMA Operations

The DMA processor may be used for high speed data transfer directly to memory at a maximum rate of 910,000 bytes per second. The DMA processor is an independent hardware device which is attached directly to the main memory address, data, and control busses. Data transfers performed by the DMA processor are completely independent from operation of the main computer except that both devices use the same memory. The DMA processor takes precedence over the CIP/2200 CPU for memory operations. Programming for DMA transfers is described in Appendix E.

.6 Control Stack Facility

The CIP/2200 control stack facility provides a method for saving and restoring the computer state information. The implementation of state switching using a control stack greatly increases programming ease and flexibility, particularly in an interrupt environment.

#### Computer State Information

The computer state information uniquely defines the internal state of the computer at a given point in a program. The CIP/2200 state information consists of the contents of the A, B, and X registers, the location of the next instruction to be executed (P), and all status indicators (S). This information is reloaded into the computer registers when the machine state is restored. The machine state must be saved by a subroutine or an interrupt service routine to allow the programmer to use registers, change word length, or alter other status indicators freely in the subroutine or interrupt service routine without affecting the values stored in the computer registers during the execution of other programs. State saving is essential for interrupt service routines since the interrupted program must be able to continue as before when the interrupt service routine returns.

## Stack Operations

A stack is a data storage element containing a varying number of entries. Data is entered and removed from the stack in a Last In-First Out ("LIFØ") manner. LIFØ operation means that when data is removed from the stack, the information removed first is that which was entered into the stack most recently. Entry of data into a stack is called "pushing" and data removal is known as "popping".

#### Control Stack Use

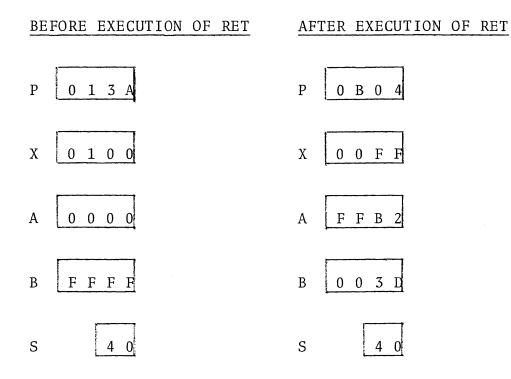

The control stack is used to save the computer state. Each entry in the CIP/2200 control stack consists of a complete set of state information. The most recently saved machine state is on the "top" of the stack, the oldest machine state on the "bottom". In normal use each subroutine saves the machine state immediately after being called. The subroutine returns the state information by using the RET or RTN instruction to "pop" the old machine state from the stack. When multi-level subroutine calls are used, the control stack will contain more than one entry during execution of the lower level subroutines. As each subroutine terminates, one more entry is removed from the stack. When control returns to the original calling routine, the control stack will be empty. Uniform use of a save and restore convention greatly enhances the reliability of programs, especially in an interrupt environment.

Control stack operations are performed by the SAV, RET, and RTN instructions. The location of the control stack is defined by the <u>control stack pointer</u> which occupies a dedicated page zero location - 92 - 93<sub>16</sub>. The control stack pointer always contains the address of the first (lowest addressed) byte of the most recently stacked machine state information. The control stack occupies the 256 byte memory page indicated by the control stack pointer. The control stack pointer cannot be made to cross a page boundary without generating a control stack under/overflow interrupt. The length of the control stack area used by a program is determined by the number of levels of subroutines and interrupts allowed. For example, a program having a four level subroutine structure (where at most four subroutines are simultaneously in use - A calls B which calls C which calls D) requires 36 bytes for its control stack (9 bytes per SAV) regardless of the total number of subroutines in the program. Additional control stack space must be reserved for interrupt processing because interrupts can, in general, occur at any time. Each interrupt requires a minimum of 9 additional bytes of reserved control stack space. Interrupt service routines may also require further control stack space for subroutines.

# 3.0 MACHINE INSTRUCTIONS

This section describes the operation of the CIP/2200 machine instructions. The instructions are grouped by logical type into several subsections. Details of memory addressing are given in section 2.3 and are not repeated for each instruction. The instruction descriptions include the format of the instruction as it appears in memory and the CIP/2200 assembly language coding. An asterisk to the right of the machine instruction format diagram indicates that the eight addressing modes discussed in section 2.3 apply. The assembly language coding for those cases assumes extended addressing (mode 6).

The abbreviations used in this chapter are shown below.

- ALI Arithmetic and logical indicators

- E/Z Equal/zero indicator

- $L/\emptyset$  Low/ones indicator

- H/M High/mixed indicator

- INT Interrupt system disabled indicator

- ØV Arithmetic overflow indicator

- WL Word length indicator

- PF Power fail indicator

- A A register (accumulator)

- B B register (extended accumulator)

- X Index register

- P Program counter

## 3.1 Binary Arithmetic and Logical Instructions

The instructions in the binary arithmetic and logical instruction group perform binary arithmetic operations on fixed length 16 bit 2's complement numbers or perform logical operations on 16 bit unsigned binary data. In general, one operand resides in a register, usually the A register, and the other is in memory. Instructions are provided for moving data between registers; transferring data between registers and memory; and for adding, subtracting, counting, masking, and inverting 16 bit data. Special instructions are provided to assist in implementing binary multiplication and division. Binary arithmetic is provided both for general computation and for address and index computation. Since the binary arithmetic operand length is consistent with the CIP/2200 address word size, the full arithmetic and logical capabilities of the instruction set may be used for address computation.

The two fixed length binary data formats are shown below. Some of the instructions in this group also use 8 bit immediate data. When a shorter field is added to a 16 bit integer the sign of the short field is extended to provide 16 data bits. Note that when zero is complemented in 2's complement notation no change occurs.

| 15  | 0       |    |

|-----|---------|----|

|     | INTEGER | 07 |

| 131 | INTEGER | ar |

arithmetic data

logical data

The results of all arithmetic instructions are tested for an overflow (result greater than  $2^{15}$ -1 or less than  $-2^{15}$ ). The overflow indicator is set if an overflow occurs but it remains unchanged if no overflow occurs.

Instructions in the variable length arithmetic group (Section 3.3) and in the shift group (Section 3.2) supplement the fixed length arithmetic and logical capabilities of the CIP/2200. When mixing fixed and variable length instructions, care must be taken to ensure that the registers are used consistently.

The binary arithmetic and logical instruction group is shown in Figure 3-1. The table lists the name, the assembler mnemonic, the operands in assembler notation, the indicators affected, and the machine operation code in hexadecimal notation. Those instructions allowing eight addressing modes are indicated by an asterisk following the operation code.

| NAME                   | MNEMONIC | OPERANDS | INDICATORS | OPCODE                    |

|------------------------|----------|----------|------------|---------------------------|

| Load A                 | LDA      | ADDR(X)  |            | E0-E7*                    |

| Load B                 | LDB      | ADDR(X)  |            | C0-C7*                    |

| Load X                 | LDX      | ADDR(X)  |            | 80-87*                    |

| Store A                | STA      | ADDR(X)  |            | F0-F7*                    |

| Store B                | STB      | ADDR(X)  |            | C8-CF*                    |

| Store X                | STX      | ADDR(X)  |            | 88-8F*                    |

| Transfer A<br>to B     | TAB      |          |            | 2 B                       |

| Transfer B<br>to A     | TBA      |          |            | 2 F                       |

| Transfer A<br>to X     | TAX      |          |            | 4 C                       |

| Transfer X<br>to A     | TXA      |          |            | 4 E                       |

| Transfer B<br>to X     | TBX      |          |            | 4 D                       |

| Transfer X<br>to B     | TXB      |          |            | 4 F                       |

| Interchange<br>A and B | IAB      |          |            | 03                        |

| Interchange<br>A and X | IAX      |          |            | 35                        |

| Interchange<br>B and X | IBX      |          |            | 36                        |

| Add to A               | ADA      | ADDR(X)  | ØV         | A0 - A7*                  |

| Subtract<br>from A     | SBA      | ADDR(X)  | øv         | B <b>0 -</b> B <b>7 *</b> |

| Increment A            | INA      |          | ØV         | 48                        |

| Increment B            | INB      |          | ØV         | 49                        |

ľ

I

C

l

I

ľ

I

I

I

| NAME                        | MNEMONIC | OPERANDS  | INDICATORS | OPCODE   |

|-----------------------------|----------|-----------|------------|----------|

| Increment X                 | INX      |           | ØV         | 44       |

| Decrement A                 | DCA      |           | ØV         | 23       |

| Decrement B                 | DCB      |           | ØV         | 27       |

| Decrement X                 | DCX      |           | ØV         | 4 5      |

| Add to Index<br>Immediate   | AXI      | I         | ØV         | 5F02     |

| Ones Comple-<br>ment A      | ØCA      |           |            | 4 A      |

| Ones Comple-<br>ment B      | ØCB      |           |            | 4 B      |

| Multiply Step               | MST      | ADDR(X)   |            | 90-97*   |

| Divide Step                 | DST      | ADDR(X)   |            | 98-9F*   |

| Increment Word<br>in Memory | IWM      | ADDR(X)   | ØV,ALI     | 70-77*   |

| Decrement Word<br>in Memory | DWM      | ADDR(X)   | ØV,ALI     | 78-7F*   |

| Add to Word<br>Immediate    | AWI      | I,ADDR(X) | ØV,ALI     | 50       |

| And Memory<br>with A        | ANA      | ADDR(X)   |            | D0 - D7* |

| OR B to A                   | ØRA      |           |            | 40       |

| OR A to B                   | ØRB      |           |            | 42       |

| Exclusive OR<br>B to A      | XRA      |           |            | 41       |

| Exclusive OR<br>A to B      | XRB      |           |            | 43       |

Figure 3-1. Binary Arithmetic and Logical Instructions

Ι

I

I

I

I

I

Ľ

L

I

I

I

I

I

| LDA - Load A                                            |   |  |  |  |  |  |

|---------------------------------------------------------|---|--|--|--|--|--|

| 23 16 15 0 *                                            |   |  |  |  |  |  |

| EO-E7 X ADDR                                            |   |  |  |  |  |  |

| LDB - Load B                                            |   |  |  |  |  |  |

| 23 16 15 0 *                                            |   |  |  |  |  |  |

| CO-C7 X ADDR                                            |   |  |  |  |  |  |

| LDX - Load X                                            |   |  |  |  |  |  |

| 23 16 15 0                                              |   |  |  |  |  |  |

| 80-87 X ADDR                                            |   |  |  |  |  |  |

| Indicators Affected: none.<br>Assembly Lanugage Coding: | L |  |  |  |  |  |

|                                                         |   |  |  |  |  |  |

The two byte operand located at the effective address replaces the contents of the register specified by the operation code. The operand in memory is not changed.

LDA/

STA - Store A

$\gamma_{\rm eff}$

| 23  | 16 | 15 | (    | ) | * |

|-----|----|----|------|---|---|

| F0- | F7 | x  | ADDR |   |   |

0. \* 23 16 15 C8-CF Х ADDR

STX - Store X

Indicators Affected: none. Assembly Language Coding:

The operand contained in the register specified by the operation code replaces the contents of the 16 bit word located at the effective address. The operand in the register is not changed.

ADDR(X)

STA/ ADDR(X) TAB - Transfer A to B

TBA - Transfer B to A

7 0 2F The contents of the source register (specified by the second character of the mnemonic operation code) replace the contents of the target register (specified by the last character). The source register contents are not changed.

TAX - Transfer A to X

TXA - Transfer X to A

TBX - Transfer B to X

TXB - Transfer X to B

7 0 4F

Indicators Affected: none Assembly Language Coding:

TXA

IAB - Interchange A and B

| 7  | 0 |

|----|---|

| 03 |   |

The contents of the registers specified by the opcode are interchanged.

IAX - Interchange A and X

| 7 |    | 0 |

|---|----|---|

|   | 35 |   |

IBX - Interchange B and X

7 0 36

Indicators Affected: none. Assembly Language Coding:

IAB

ADA - Add to A

| 23 1    | 6 | 15 |      | 0 | * |

|---------|---|----|------|---|---|

| A0 - A7 | 7 | x  | ADDR |   |   |

The 16 bit operand at the effective address is added to the contents of the A register; the sum replaces

register; the sum replaces the contents of the A register. If the result cannot be contained in 16 bits the arithmetic overflow indicator is set. The operand in memory is not changed.

Indicators Affected: ØV Assembly Language Coding:

ADA/ ADDR(X)

SBA - Subtract from A

| 23 16   | 15 | 5 0  | * |

|---------|----|------|---|

| B0 - B7 | x  | ADDR |   |

The 16 bit operand at the effective address is sub tracted from the contents of the A register; the

difference is placed in the A register. The operand in memory is unchanged. The overflow indicator is set if the result cannot be represented in 16 bits.

Indicators Affected: ØV Assembly Language Coding:

SBA / ADDR(X)

INA - Increment A

INB - Increment B

INX - Increment X

Indicators Affected: ØV Assembly Language Coding:

INA

DCA - Decrement A

DCB - Decrement B

7 0

The operand in the register specified by the operation code is decremented by one; the decremented operand is placed in the register. An arithmetic overflow results if the register contains  $-2^{15}$  (8000<sub>16</sub>) before the decrement instruction is executed.

The operand in the register specified by the operation code is incremented by one; the incremented operand is placed in the register. An arithmetic overflow results if the register contains  $2^{15}-1$  (7FFF<sub>16</sub>) before the increment instruction is executed. DCX - Decrement X

7 0 45

Indicators Affected: ØV Assembly Language Coding:

DCX

AXI - Add to Index Immediate

| 23 | 16 | 15 | 8 | 7 |   | 0 |

|----|----|----|---|---|---|---|

| 5  | F  | 02 | 2 | S | Ι |   |

The contents of the immediate data byte located in bits 7-0 of the instruction are added to the contents of the index d in the index register. The

register; the sum is placed in the index register. The imemdiate data is treated as a signed 8 bit number. If the sum cannot be contained in the 16 bit index register the overflow indicator is set.

Indicators Affected: ØV Assembly Language Coding:

AXI I

ØCA - Ones Complement A

ØCB - Ones Complement B

7 0 4 B

Indicators Affected: none. Assembly Language Coding:

The operand located in the specified register is inverted. The operation is performed on a bit by bit basis. Each 0 bit in the register is replaced by a 1, each 1 by a 0.

ØCA

Programming Note:

The 2's complement of a number held in either the A or B register may be obtained by taking the 1's complement and incrementing the result. For example, the sequence:

ØCA INA

will give the negative of the contents of the A register in 2's complement notation.

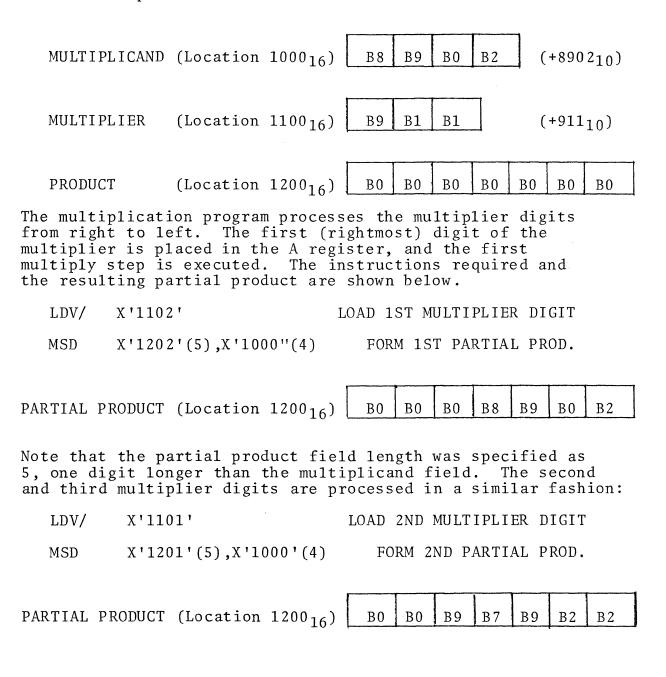

MST - Multiply Step

| 23   | 16  | 15 |      | 0 | * |

|------|-----|----|------|---|---|

| 90 - | -97 | X  | ADDR |   |   |

The multiply step instruction is designed to assist in the multiplication of 2's complement binary integers. Each

execution of the multiply step instruction uses a single multiplier bit and generates a new partial product; the multiply step instruction must be executed once for each bit in the multiplier to perform a complete multiplication. Multiplication uses both the A and B registers. A multiply operation is performed by setting the A register to zero, loading the B register with the multiplier, and executing the Multiply Step instruction once for each bit of the multiplier.

The multiply step instruction tests the low order bit of the B register (multiplier). If the tested bit is a 1, the addressed operand (multiplicand) is added to the partial product (A); if the bit is a zero, no add is performed. The A and B registers are then shifted one place to the right, thus discarding the multiplier bit just used and positioning the partial product one place to the right.

When all of the multiplier bits have been processed the product is in the A register and the high order bits of B. Note that the number of bits in the product is equal to the number of bits in the multiplicand plus the number of bits in the multiplier.

The method of multiplication supported by this instruction requires that the multiplier be a positive number. The multiplier must therefore be complemented if negative, and the sign of the product must be adjusted after the multiplication process.

The example below illustrates binary multiplication using the multiply step instruction. For brevity, all operands as well as the A and B registers are assumed to be 4 bits long instead of their actual length of 16 bits.

| Multipl      | icand:                                                             | $2_{10}^{10} = 0010_2^2$                                |               |  |

|--------------|--------------------------------------------------------------------|---------------------------------------------------------|---------------|--|

| Step         | А                                                                  | В                                                       |               |  |

| 1            | 0000<br>+0010                                                      | 0101                                                    |               |  |

|              | $\frac{0010}{0001}$                                                | $\begin{array}{c} 0101 \\ 0010 \end{array}$             | (after shift) |  |

| 2            | $\begin{array}{c} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 $ | $\begin{array}{c} 0010\\ 100\overline{1} \end{array}$   | (after shift) |  |

| 3            | 0000<br>+0010                                                      | 100 <u>1</u>                                            |               |  |

|              | $\frac{0010}{0010}$                                                | $\begin{array}{c} 1  0  0  1 \\ 0  1  0  0 \end{array}$ | (after shift) |  |

| 4<br>AN SWER | $\begin{array}{c} 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 $ | $\begin{array}{c} 0100\\ 101\overline{0} \end{array}$   | (after shift) |  |

Indicators Affected: none Assembly Language Coding:

Multiplier:  $5_{10} = 0101_2$

MST/ ADDR(X)

Programming Note:

The following code will multiply two positive 16 bit numbers.

| LDA= | F'0'   |                        |

|------|--------|------------------------|

| LDB/ | MPLIER |                        |

| LDX= | F'16'  |                        |

| MST/ | MCAND  |                        |

| DCX  |        | DECREMENT BIT COUNT    |

| NXZ  | *-4    | SKIP BACK IF COUNT ≠ 0 |

DST - Divide Step

| 23 1  | 6 | 15 | 0    | * |

|-------|---|----|------|---|

| 98-9F |   | X  | ADDR |   |

The divide step instruction is designed to aid in implementing a fixed point binary divide routine. To perform

a complete division the divide step instruction is executed once for each quotient bit desired. Before the division is started the dividend is loaded into the A and B registers; the divisor is located at the effective address in memory. Both the divisor and the dividend are positive binary numbers. The sign of the quotient must be determined using the rules of algebra, and the quotient complemented if necessary after division. The dividend may have a maximum length of 30 magnitude bits, and is right justified in the A-B register pair with a double sign bit in bits 15 and 14 of the A register. The quotient bits are shifted into the low order position (bit 0) of the B register as they are formed. When the divide is complete the B register contains the quotient right justified, and the A register contains the remainder.

The divide step instruction performs the following operations.

- The A-B register is shifted left one position. A zero is shifted into the low bit of the B register.

- 2. The divisor is subtracted from the contents of the A register. A zero or positive result causes the low bit of the B register to be set to 1. If the result was negative, the divisor is added to the A register and the low bit of the B register is left zero.

Indicators Affected: none. Assembly Language Coding:

DST/ ADDR(X)

Programming Note:

The divide step instruction may be used to implement a full division as shown. The example assumes a 30 bit positive dividend and a 16 bit positive divisor.

| R04  |        |                         |

|------|--------|-------------------------|

| LDV/ | DIVDND |                         |

| LDX/ | F'16'  | LOAD QUOTIENT BIT COUNT |

| DST/ | DIVISR |                         |

| DC X |        | DECREMENT BIT COUNT     |

| NXZ  | * - 4  |                         |

|      |        |                         |

IWM - Increment Word in Memory

| 23 16   | 15 | (    | ) | * |

|---------|----|------|---|---|

| 70 - 77 | x  | ADDR |   |   |

The two byte operand located at the effective address is incremented by one. If the operand contains  $2^{15}-1$

$(7FFF_{16})$  before the execution of the IWM instruction an arithmetic overflow will result and the overflow indicator will be set. The arithmetic and logical indicators are set by this instruction.

Indicators Affected: ØV, ALI Assembly Language Coding:

\*

IWM/ ADDR(X)

DWM - Decrement Word in Memory

| 23 | 16   | 1! | 5    | 0 |

|----|------|----|------|---|

| 70 | 7 17 | v  |      |   |

| /8 | -7F  | X  | ADDR |   |

The two byte operand located at the effective address is decremented by one. If the operand contains  $-2^{15}$  (8000<sub>16</sub>)

before the execution of the DWM instruction an arithmetic overflow will result and the overflow indicator will be set. The arithmetic and logical indicators are set according to the sign and value of the result.

Indicators Affected: ØV, ALI Assembly Language Coding: DWM/

ADDR(X)

AWI - Add to Word Immediate

| 31 | 24 | 23 | 16 | 15 | 5     | 0 | * |

|----|----|----|----|----|-------|---|---|

| 5  | 0  | S  | I  | x  | AD DR |   |   |

The immediate data in the second byte of the instruction is added as a signed 8-bit number

to the contents of the two byte operand at the effective address; the result replaces the operand in memory. Ιf

the result is greater than  $2^{15}$ -1 or less than  $-2^{15}$ , an arithmetic overflow will occur and the overflow indicator will be set. The arithmetic and logical indicators are set according to the result.

Indicators Affected: ØV, ALI Assembly Language Coding:

AWI/ I,ADDR(X)

ANA - AND Memory with A

| 23     | 16 | 15 | 0    | * |

|--------|----|----|------|---|

| D0 - D | )7 | X  | ADDR |   |

The two byte operand indicated by the effective address is ANDed with the contents of the A register. The result re-

places the contents of the A register. The operation is performed on a bit by bit basis. The resulting bit is a one if both bits are one, zero otherwise.

Indicators Affected: none. Assembly Language Coding:

ANA/ ADDR(X)

ØRA - ØR B to A

The contents of the source register (the register not named in the mnemonic operation code) is  $\emptyset$ Red with the target register (specified in the mnemonic operation code); the result is placed in the target register. For example,  $\emptyset$ RA replaces A with the result of the operation (A)  $\emptyset$ R (B). The source register (B in the example is not changed. The operation is performed on a bit by bit basis. If both bits are zeros, the resulting bit is a zero; otherwise the result is a one.

Indicators Affected: none. Assembly Language Coding:

ØRA

XRA - Exclusive ØR B to A

XRB - Exclusive  $\emptyset R$  A to B

The contents of the register not indicated in the mnemonic opcode are Exclusive ØRed with the contents of the register indicated by the last character of the mnemonic. The result is placed into the named target register. For example, XRA replaces the A register contents with the result of the exclusive  $\emptyset R$ operation. The source register (B in the example) is not changed. The operation is performed on a bit by bit basis. If both bits are alike (both zeros or both ones), the resulting bit is a zero; otherwise the resulting bit is a one.

Indicators Affected: none. Assembly Language Coding:

XRA

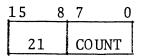

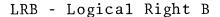

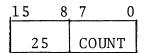

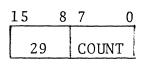

## 3.2 Shift Instructions

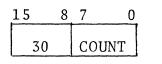

| 15    | 8  | 7     | 0 |

|-------|----|-------|---|

|       |    |       |   |

| OPCO. | DE | COUNT |   |

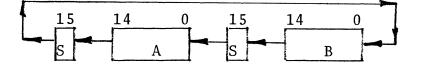

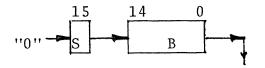

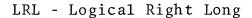

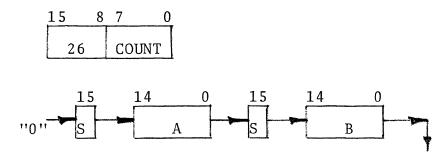

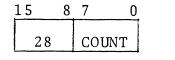

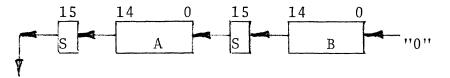

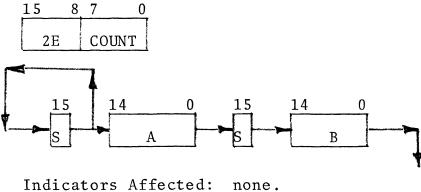

The shift group includes arithmetic and logical shifts and a rotate for the A register, the B register, and the linked A-B register pair. The shift

instructions are two bytes long. The operation code determines the type of shift operation. The second byte contains an 8 bit 2's complement count which specifies the number of bit positions to be shifted. If the shift count is negative, no operation is performed. Figure 3-2 is a summary of the shift instructions. The "long" shifts operate on the linked A-B register pair. Bits shifted out of bit 0 of the A register by a long right shift are shifted into bit 15 of the B register. Similarly, bits shifted out of bit 15 of the B register by a long left shift are shifted into bit 0 of the A register. The assembly language operand "N" in Figure 3-2 specifies the shift count in all cases.

| INSTRUCTION              | MNEMONIC | OPERAND | INDICATORS | OPCODE |

|--------------------------|----------|---------|------------|--------|

| Rotate Left<br>A         | RLA      | Ν       |            | 20     |

| Rotate Left<br>B         | RLB      | Ν       |            | 21     |

| Rotate Left<br>Long      | RLL      | N       |            | 22     |

| Logical<br>Right A       | LRA      | N       |            | 24     |

| Logical<br>Right B       | LRB      | Ν       |            | 25     |

| Logical Right<br>Long    | LRL      | N       |            | 26     |

| Arithmetic<br>Left A     | ALA      | Ν       |            | 28     |

| Arithmetic<br>Left B     | AL B     | Ν       |            | 29     |

| Arithmetic<br>Left Long  | ALL      | Ν       |            | 2 A    |

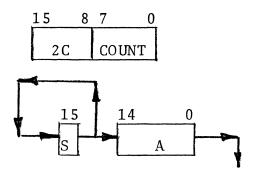

| Arithmetic<br>Right A    | ARA      | Ν       |            | 2 C    |

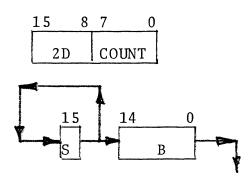

| Arithmetic<br>Right B    | ARB      | Ν       |            | 2 D    |

| Arithmetic<br>Right Long | ARL      | Ν       |            | 2E     |

Figure 3-2 Shift Instructions

I

I

I

I

Í

RLA - Rotate Left A

| 15 | 8 | 7     | 0 |

|----|---|-------|---|

| 20 |   | COUNT |   |

The contents of the selected register are rotated left by the number of bit positions specified in COUNT. Bits shifted out of the most significant position are shifted into the least significant position.

RLB - Rotate Left B

RLL - Rotate Left Long

| 15 | 8 | 7     | 0 |

|----|---|-------|---|

| 22 |   | COUNT |   |

Indicators Affected: none. Assembler Language Coding: RLA N

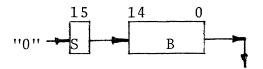

Programming Note: The rotate instruction is useful for moving data within a register without destroying any information. LRA - Logical Right A

| 15 | 8 | 7     | 0 |

|----|---|-------|---|

| 24 |   | COUNT | , |

The contents of the selected register are shifted right by the number of bit positions specified in COUNT. Zeros are shifted into the most significant position. Bits shifted out of the least significant position are lost.

Indicators Affected: none. Assembler Language Coding:

LRA N

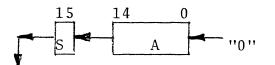

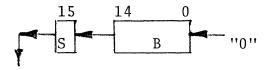

ALA - Arithmetic Left A

ALB - Arithmetic Left B

Indicators Affected: none. Assembler Language Coding:

ALA N

Programming Note: The arithmetic left shift can be used for multiplication by a power of two. An arithmetic left shift of n positions is equivalent to multiplication by  $2^n$ .

The contents of the selected register are shifted left by the number of bit positions specified in COUNT. Zeros are shifted into the least significant position and bits shifted out of the sign position are lost. ARA - Arithmetic Right A

The contents of the selected register are shifted right by the number of bit positions specified in COUNT. The sign bit of the register is propagated during shifting. Bits shifted out of the least significant position are lost.

ARB - Arithmetic Right B

ARL - Arithmetic Right Long

Assembler Language Coding:

ARA N

Programming Note: The arithmetic right shift can be used for division by a power of two. An arithmetic right shift for n positions is equivalent to division by  $2^{n}$ .

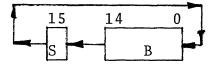

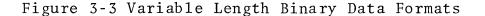

## 3.3 Variable Word Length Instructions

The length of binary data which must be processed varies from one application to another and from one instance to another within a given application. Variable word length instructions perform binary arithmetic and logical operations on one, two, three or four bytes of data. This is especially useful for character operations, single byte arithmetic, and extended precision arithmetic on 24 or 32-bit quantities.

The length of the binary data operated upon is specified by the word length indicator in the machine status register. Instructions described later in this section allow the programmer to specify the length of variable length data.

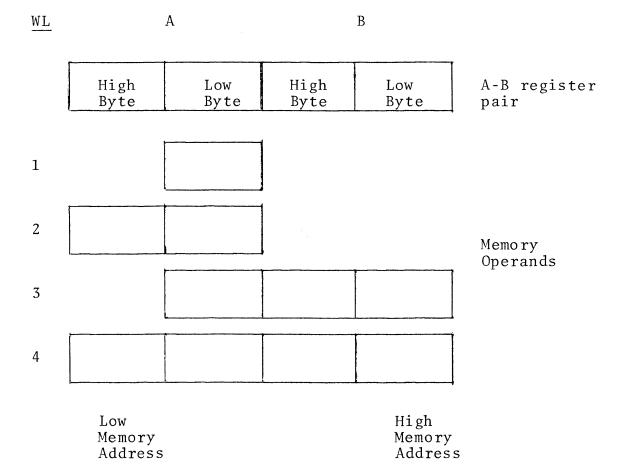

Variable word length instructions use two operands, one of which is in the A or A-B register, the other in memory. Except for the store instruction, the result of an operation replaces the contents of A or A-B. For one and two byte operations, only the A register participates, while for three and four byte operations, both the A and B registers are used. Figure 3-3 gives the exact operation for various word length values.

| Word<br>Length<br>Value | Operands                                      | Location of<br>Result            | Operation                                                                                                                  |

|-------------------------|-----------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 1                       | low byte of A<br>and 1 byte<br>memory operand | register                         | The result replaces the<br>contents of the low byte<br>of A. Bit seven of A is<br>propagated thru the high<br>8 bits of A. |