Sept, 1970

GEMINI COMPUTER SYSTEMS

PRINCIPLES OF OPERATION

# PRELIMINARY

#### PREFACE

This document is a preliminary version of GEMINI Computer Systems Principles of Operations. It is divided into 9 Chapters.

- 1.0 System Architecture

- 2.0 Memory

- 3.0 Addressing

- 4.0 Instruction Set

- 5.0 Iterative Execution

- 6.0 Execution Breakpoints

- 7.0 Interrupts

- 8.0 Memory Processor

- 9.0 Processor State Vector

The first chapter, Systems Architecture, provides an overview of GEMINI Computer Systems. Chapters 2, 3, and 4 on Memory, Addressing, and Instruction Set are fundamental to understanding the programming of GEMINI Systems. The remaining chapters are an amplification of the basic material of the previous chapters.

#### 1.0 SYSTEM ARCHITECTURE

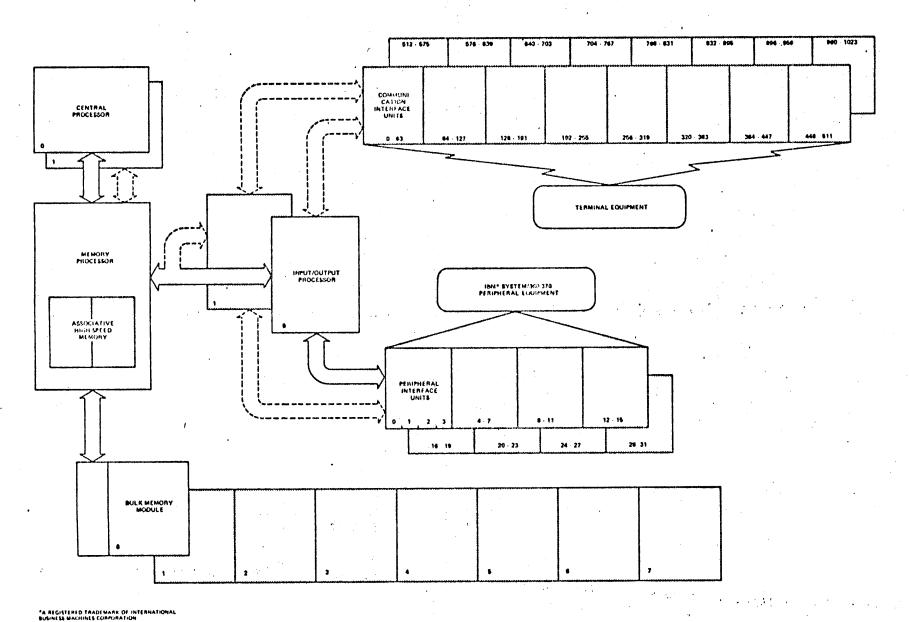

GEMINI Computer Systems are multiprocessing systems organized around a large central memory complex consisting of a single, high-performance bulk memory and a memory processor (see Figure 1.1). For this reason, the architecture of GEMINI Computer Systems is characterized as memory oriented. GEMINI Computer Systems include central processors, input/ output processors, and a memory processor. The central processor and the input/output processors can be duplexed for increased throughput and failsoft capability. The software component of the GEMINI Computer Systems is the GEMINI Operational Control Program (OCP). It performs all resource allocation as well as failure diagnosis and recovery, and includes the GEMINI Programming Language (GPL) and a complete set of user services. The Operational Control Program is reentrant and, in a dual central processor system, can be simultaneously executed by both central processors.

Communication between system processors is accomplished by means of an interprocessor control bus, interrupt signals, and bulk memory. The interprocessor control bus is common to all processors and provides programmed communication between a central processor and all the other processors. A central processor uses the interprocessor control bus to send data to and request data from another processor.

ILES MACHINES COMPONATION

Figure 1.1 GEMINI Computer System

Central processor response to asynchronous system events is accomplished by a multilevel priority interrupt scheme. The memory processor or an input/output processor can signal the occurrence of events by generating an interrupt that can be serviced by either central processor.

Access to bulk memory for all processors in the system is controlled by the memory processor. A central processor addresses only virtual memory and the memory processor transforms the virtual address into a real bulk memory address. The virtual memory organization makes it possible for a central processor to access memory with contiguous addresses even though the corresponding real bulk memory locations may be noncontiguous. An input/output processor accesses memory by presenting both a virtual address and its corresponding real bulk memory address.

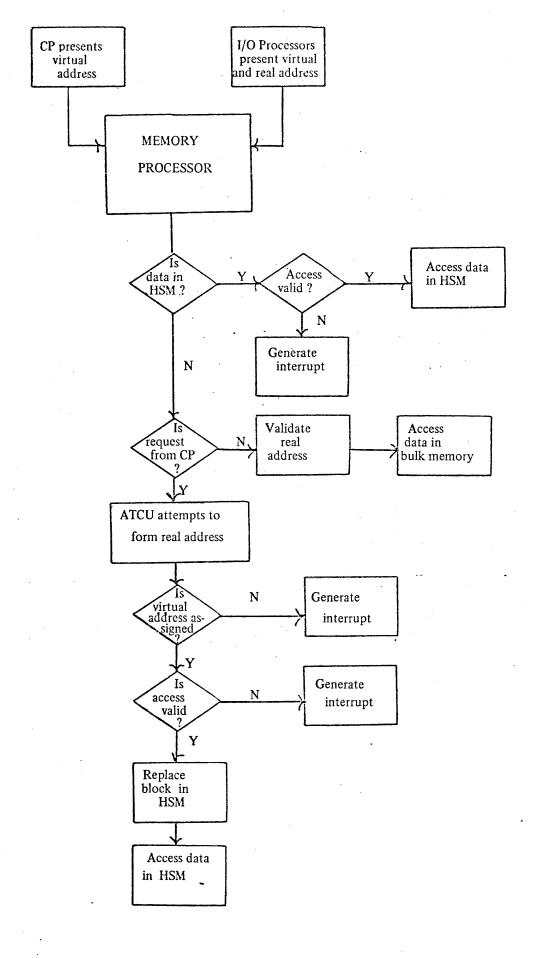

#### 1.1 MEMORY PROCESSOR

The GEMINI Memory Processor controls all accesses to memory.

Accesses to bulk memory are automatically buffered by an associative high-speed memory, which is transparent from a programming viewpoint. The contents of high-speed memory are dynamically maintained by a mechanism that replaces those portions of the memory least recently refer-

enced by a central processor. The high-speed memory is accessed by means of a virtual address. Therefore, any requested data that is currently in the high-speed memory is transferred between the high-speed memory and the requesting processor without requiring an address transformation.

When a central processor requests data that is not in the high-speed memory, the virtual address is transformed to a real bulk memory address. The required data is accessed from bulk memory and is used to replace data in the high-speed memory that was least recently used by a central processor. When an input/output processor requests data that is not in the high-speed memory, bulk memory is accessed directly using the real bulk memory address supplied by the requesting processor.

Virtual memory is divided into memory segments, and each segment consists of over a billion virtual byte addresses.

The segmenting of virtual memory provides the isolation of unrelated program areas that is required in a multiprogramming environment. A memory segment is divided into over a million pages, each page containing 1024 bytes.

The GEMINI memory processor incorporates individual page

access controls to prevent unauthorized accesses to

memory by a central processor. Unauthorized write accesses

by an input/output processor are similarly prevented by

separate write access controls for each page of memory

These two access protection mechanisms are independent of

each other.

#### 1.2 CENTRAL PROCESSOR

The GEMINI Central Processor is a microprogrammed digital computer which incorporates the following

features.

## 1.2.1 Operating Mode

A central processor operates in a hierarchy of four possible modes: private, subsystem, service, and supervisor mode.

The mode determines which instructions can be executed, which memory segments can be accessed, and restricts the accessing of individual pages within segments.

## 1.2.2 <u>Instruction Format</u>

A GEMINI instruction consists of an operation code, breakpoint control information, and from 1 to 11 addresses. Depending on the operation code of the instruction, each address can define an operand that is from 1 to 16 bytes in length. All operations have a required number of addresses, and many operations include addresses that can optionally be specified.

In addition to the standard instructions, there are two extended instructions that permit up to 256 user-defined operations and up to 256 additional system-defined operations. The microprograms associated with the extended instructions can reside in either bulk memory or control memory.

#### 1.2.3 Instruction Set

The GEMINI instruction set provides arithmetic operations, byte string operations, list operations, and control operations.

Arithmetic Operations --

The arithmetic operations provided by the standard GEMINI instruction set include:

Computational Signed binary and decimal integer Binary magnitude integer Address Logical The computational operations permit the use 8 data types which include binary or decimal, real or complex, and which have fixed or floating-point adjustment.

Binary Computational Arithmetic operations have a precision of just over 33 decimal digits and an exponent range of over 19,728 decimal orders of magnitude.

Decimal computation arithmetic operations have a maximum precision of 27 digits and an exponent range of 1,999 orders of magnitude. The instruction set provides for optional rounding and normalization of the results of all computational arithmetic operations. If a result is not to be normalized, it can be adjusted to a specified precision.

Signed binary integer arithmetic operations have a maximum precision just over 38 decimal digits, while signed decimal integer operations have a maximum precision of 31 digits. Magnitude binary integer operations have a maximum precision of 128 bits, and address arithmetic operations have a maximum precision of 126 bits. The logical operations can be performed on data that is from 8 to 128 bits in length.

Byte String Operations --

The GEMINI instruction set provides operations that manipulate a byte string or any 8-bit character within the byte string. The byte strings can be from 1 to 16 bytes in length.

Copy operations can be performed with an optionally specified bit displacement and an optionally specified mask.

Comparison operations can be performed with an optional mask specification. Other operations include the generating of a string of contiguous 1 or 0 bits, and the counting of the number of binary or decimal digits in a string having a 0 or non-0 value.

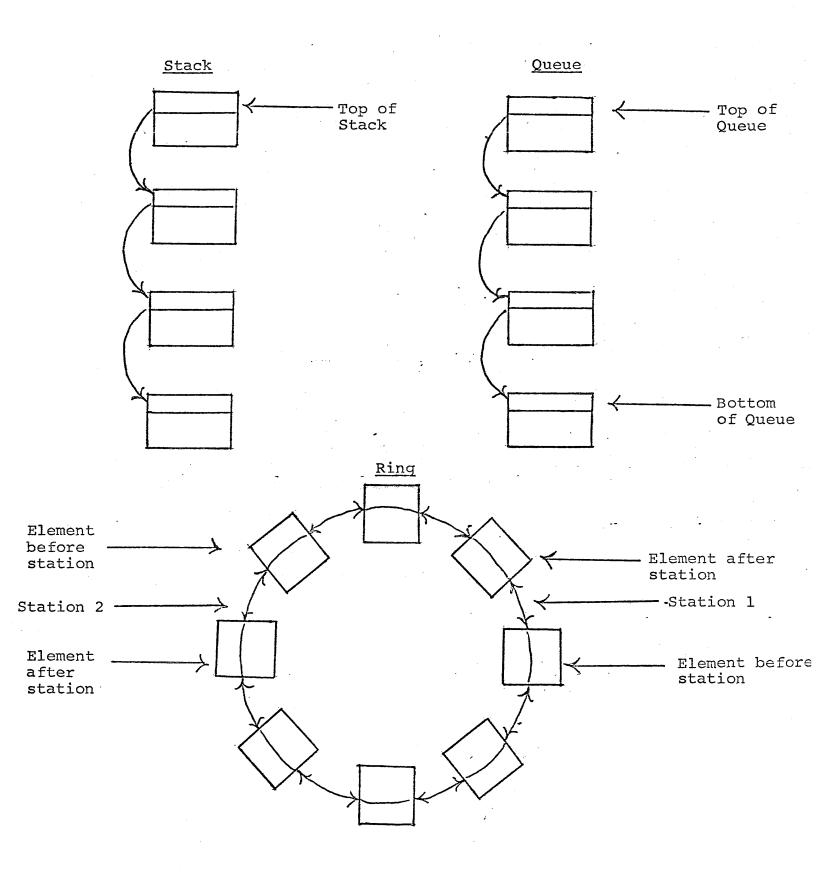

List Operations --

The GEMINI instruction set provides list operations that permit the generation and maintenance of stack, queue, and ring structures. The lists can be easily expanded and relocated in memory.

#### 1.2.4 Execution Breakpoints

These breakpoints permit program interrupts to be generated before or after a specified instruction is executed, or when a specified standard or extended operation code is detected. In addition, there are 8 simultaneous address breakpoints providing selective memory access monitoring. There are also breakpoints that monitor statement execution and thus provide source language debugging.

#### 1.2.5 State Vectors

There are two state vectors, namely the processor state vector and the system state vector. The processor state vector contains the information necessary to control

instruction execution and report the current status of a central processor. Information such as the mode, the address of the instruction currently being executed, the instruction breakpoint controls, and the interrupt controls are located in the processor state vector. When an interrupt is activated, the required processor state vector information is automatically preserved and subsequently restored when the interrupt servicing routine has completed execution.

Similarly, the system state vector contains the information necessary to control the devices which are external to a central processor and report the current operating status of the system.

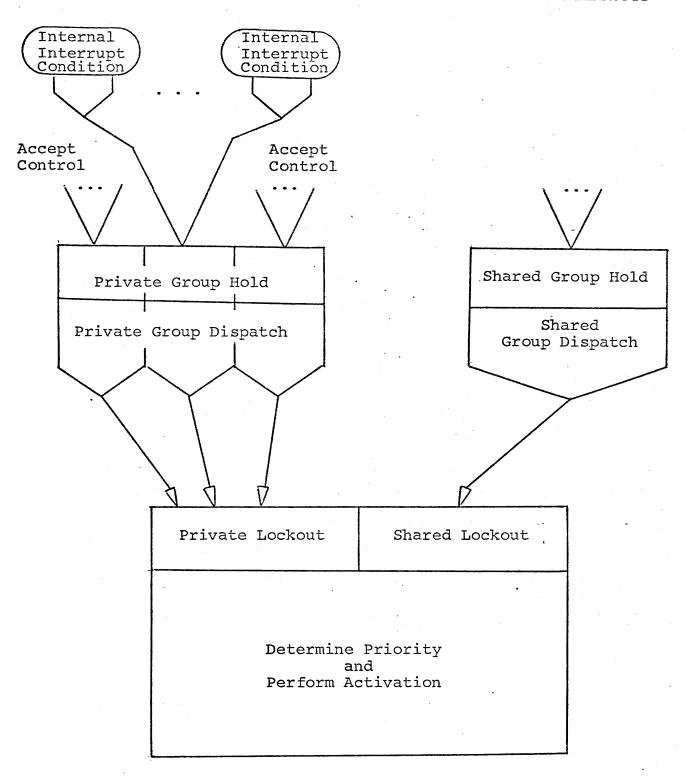

#### 1.2.6 Interrupt System

The multilevel priority interrupt system controls both private and shared interrupts. Private interrupts are the result of conditions caused directly by a central processor. Shared interrupts result from the occurrence of asynchronous conditions and in a dual central processor system may be serviced by either central processor.

Individual controls are associated with each interrupt and permit a central processor to service the interrupt or ignore the occurrence of the interrupt condition. In addition, interrupts may be deferred under program control.

#### 1.3 INPUT/OUTPUT PROCESSOR

The GEMINI Input/Output Processor links all peripheral devices and communication lines to the Memory Processor.

Peripheral devices are attached through peripheral interface units and communication lines are attached through communication interface units.

Up to 32 peripheral interface units are supported in groups of 4. Each unit has a bandwidth of 5 million bytes per second and is physically and electrically compatible with all IBM System/360 and System/370 device controllers.

Any peripheral interface unit can be utilized as a System/360 or System/370 selector, block multiplexor, or byte multiplexor channel. Up to 1024 block multiplexor subchannels are available in 64-unit increments, and up to 256 byte multiplexor subchannels are available in 16-unit increments.

The communication interface units connect communication equipment to the GEMINI system. Up to 1024 communication interface units are supported in 64-unit increments. Each unit has a bandwidth of 9600 bits per second and conforms to EIA RS232C interface specifications.

The combined bandwidth of all peripheral interface units and communication interface units is 12 million bytes per second.

#### 2.0 MEMORY

The GEMINI Computer Systems memory organization is based on a virtual memory concept. This organization allows the use of a virtual memory that is larger than the available real memory, and therefore requires a mechanism that converts virtual addresses to real addresses. In GEMINI Computer Systems, virtual-to-real address transformation is performed by the memory processor.

Related to the accessing of memory is the format in which information is stored. The GEMINI System allows variable-length, multiaddress instructions and accommodates many types of data.

#### 2.1 ORGANIZATION

The basic unit of addressable information in GEMINI Computer Systemsis the <a href="byte">byte</a>, which is composed of 8 contiguous bits numbered as shown below:

| trailing | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | leading |

|----------|---|---|---|---|---|---|---|---|---------|

Bit position 0 is defined as the leading bit position, and bit position 7 is defined as the trailing bit position.

A page of memory is defined as 1024 contiguous bytes numbered from 0 to 1023. The page is the basic unit for assignment and protection of memory.

#### 2.1.1 Virtual Memory

The <u>Virtual memory</u> organization of GEMINI Computer Systems allows a central processor to use contiguous addresses to access programs and data that reside in non-contiguous pages of real memory. Virtual memory is divided into segments so that unique segments can be assigned to distinct tasks executing in a multiprogramming environment. There are 2<sup>20</sup> virtual pages in a memory segment. A memory segment is defined as a contiguous set of address values ranging from 0 to 2<sup>30</sup>-1. There are 2<sup>16</sup>-1 memory segments, each of which is identified by a unique <u>segment number</u>. The following shows the organization of virtual memory:

| Segment Number | 2 <sup>16</sup> -1 | ·       | 2                    | 1                     |

|----------------|--------------------|---------|----------------------|-----------------------|

| VIRTUAL MEMORY |                    |         |                      | 2 <sup>30</sup> bytes |

| Byte Addresses | 2 <sup>30</sup> -1 | <b></b> | 2 <sup>30</sup> -1 0 | 2 <sup>30</sup> -1 0  |

A complete virtual address is required to access virtual memory. A complete virtual address is a 46-bit binary number consisting of 16 high-order bits that specify the segment number and 30 low-order bits that specify the address value.

| COMPLETE           |    | 16 bits        |    | 3   | o bito     |    |

|--------------------|----|----------------|----|-----|------------|----|

| VIRTUAL<br>ADDRESS |    | Segment Number |    | Ado | dress Valu | .e |

| Bit Position       | 45 |                | 30 | 29  |            | 0  |

The segment number specifies the memory segment, and the address value specifies the byte location within the segment The formation of a complete virtual address is discussed in the following sections.

## 2.1.2 Virtual Address to Real Address Transformation

A page of a memory segment that has been referenced by a task is referred to as an <u>assigned page</u>. A page becomes assigned to a task when the task makes a write access to a previously unreferenced page of a memory segment.

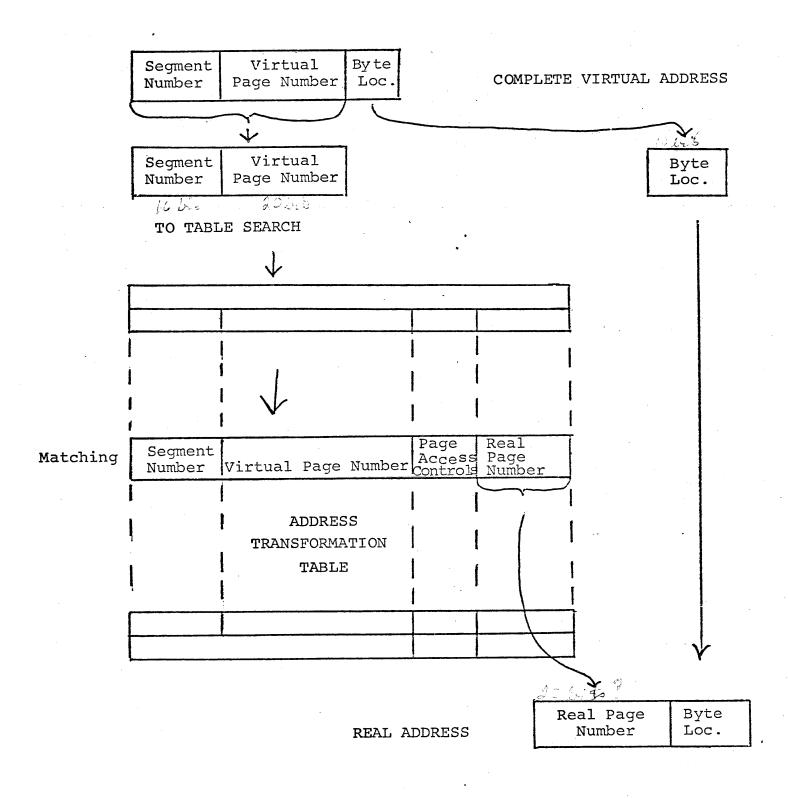

A central processor addresses only virtual memory. The transformation of a complete virtual address to a real memory address is automatically performed by the memory processor. The memory processor utilizes an address transformation table to accomplish the transformation of

virtual to real addresses. For each assigned page of virtual memory, the address transformation table contains an entry that consists of the <u>virtual page address</u>, the number of the real page associated with the virtual page, and <u>page access controls</u> that define the memory protection associated with the page.

A virtual page address is formed by using the high-order 36 bits of the complete virtual address, which is in effect dividing the complete virtual address by 1024. The transformation of a virtual address to a real address is shown in Figure 2.1.

A detailed discussion of the assignment of memory pages and the address transformation process is in 9.0 Memory Processor.

Figure 2.1 Virtual Address to Real Address Transformation

## 2.2 CENTRAL PROCESSOR MEMORY ACCESSES

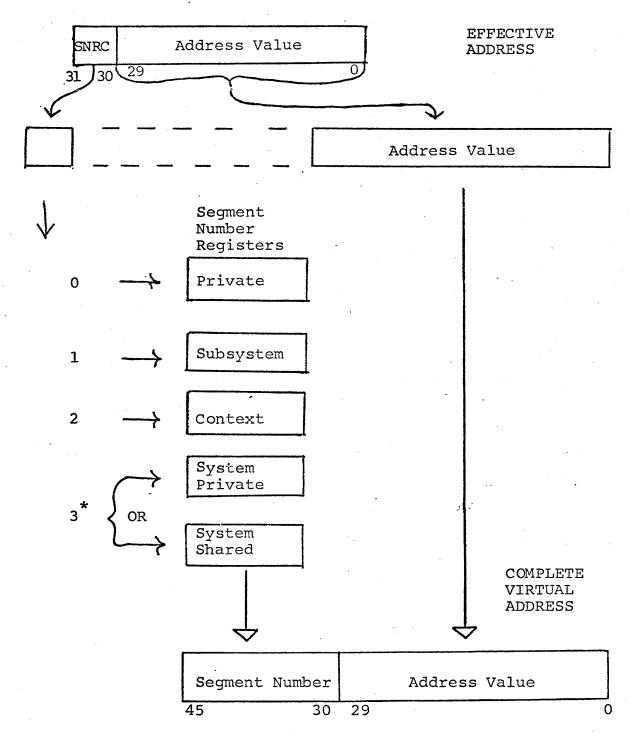

In the formation of a complete virtual address, the segment number is obtained from one of the five 16-bit segment number registers, which are located in the processor state vector. An execution mode control in the processor state vector (as described in 2.2.3 Access Mode) determines which segment number registers can be used.

## 2.2.1 Segment Number Registers

The segment number registers are numbered 0 through 4.

The associated memory segments are identified as follows:

| Segment  | Memory                                                                        |

|----------|-------------------------------------------------------------------------------|

| Number   | Segment                                                                       |

| Register | <u>Nomenclature</u>                                                           |

| 0        | Private                                                                       |

| 1        | Subsystem                                                                     |

| 2        | Context                                                                       |

| 3<br>4   | System (private to a central processor) System (shared by central processors) |

Note that the memory segment being referenced by either segment number register 3 or 4 is referred to as the system segment.

#### 2.2.2 Formation of a Complete Virtual Address

A Central Processor accesses virtual memory by first forming an <a href="effective address">effective address</a> which consists of a 30-bit address value and a 2-bit segment number register code (SNRC). The formation of an effective address is discussed in 3.0 Addressing.

. The segment number register code specifies the segment number register that is to be used during the formation of the complete virtual address according to the following convention:

| SNRC | Segment Number Register                           |

|------|---------------------------------------------------|

| 0    | Private (SNRO)                                    |

| 1    | Subsystem (SNR1)                                  |

| 2    | Context (SNR2)                                    |

| 3    | System (SNR3) if address value <214               |

|      | System (SNR4) if address value $\geqslant 2^{14}$ |

Note that when the segment number register code equals 3, both the code and the address value are used to specify the segment number.

A complete virtual address is formed by concatenating the address value in the effective address with the contents of the specified segment number register. The formation of a complete virtual address is shown in Figure 2.2.

\* If SNRC = 3 and the Address Value <214 then System Private is chosen for its Segment Number value; else System Shared is chosen.

Figure 2.2 Formation of A Complete Virtual Address

#### 2.2.3 Access Mode

The specification of the segment number registers is restricted by the access mode. The access mode is normally equal to the central processor mode, but in certain circumstances the value for the access mode is specified under program control.

Instruction Access --

An instruction is accessed from the effective address specified by the <u>instruction location register</u> located in the processor state vector. During instruction access access mode is equal to the central processor mode.

The following restrictions apply to the specification of segment number registers during instruction access:

|                | Legal Segment Number   |

|----------------|------------------------|

| Access Mode    | Register Specification |

|                |                        |

| Private (0)    | Private                |

| Subsystem (1)  | Subsystem, Context     |

| Service (2)    | System, Context        |

| Supervisor (3) | System, Context        |

A control located in the processor state vector allows the access mode restrictions on instruction access to be ignored.

Data Access --

Data is accessed at the location specified by the effective address. During data accesses the access mode is equal to one of the following:

- The central processor mode.

- The link mode specified by a subprogram control block. This condition is true if the effective address resulted from an argument addressing calculation. Argument addressing is described in 3.7 Argument Addressing.

- The mode specified by an operand of an ANALYZE instruction. These instructions are discussed in 4.7 Control Operations.

During data accesses the following restrictions apply to the specification of segment number registers:

| Access Mode                                                   | Register Specification                                                                              |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Private (0)<br>Subsystem (1)<br>Service (2)<br>Supervisor (3) | Private Private, Subsystem, and Context All registers can be selected All registers can be selected |

A control located in the processor state vector allows the access mode restrictions on data access to be ignored.

#### 2.2.4 Page Access Controls

In addition to the access mode restrictions that constrain the specification of the segment number registers, page access controls are associated with each page of virtual memory. These controls are located in the address transformation table and are shown in Figure 2.1.

The page access controls include a page mode access and a private write access control. The page mode access specifies the minimum mode required to access the page.

During all memory accesses, the access mode must be greater than or equal to the page mode access control. When the same memory segment is being referenced by independent tasks which execute in different modes, this control enables the protection of the higher access mode pages.

The <u>private write access</u> allows a page to be protected from write accesses by a central processor. —

#### 2.3 DATA AND INSTRUCTION FORMATS

The following describes the data and instruction formats used in GEMINI Computer Systems. The formats of addresses are described in 3.1 Address Formats.

#### 2.3.1 Byte Strings

A byte string is defined as a set of contiguous bytes:

| trailing | n | n-1 | ••• | 1 | 0 | leading |

|----------|---|-----|-----|---|---|---------|

|----------|---|-----|-----|---|---|---------|

Byte position 0 is the leading byte and corresponds to the lowest numbered memory address: the trailing byte corresponds to the highest numbered memory address.

## 2.3.2 <u>Data Encoding</u>

Several methods of data representation are used in GEMINI Computer Systems. The GEMINI Computer Systems data types are composed of one or more of the following basic forms: character, binary or decimal digits, integers, fractions.

#### Character --

The GEMINI Computer Systems can accommodate any of the 6-, 7-, or 8-bit codes in common usage. However, the code used by the GEMINI Operational Control Program is an 8-bit extension of the 7-bit ASA code for Information Interchange (ANSI X3.4-1968). ASACII is embedded in the GEMINI byte structure as follows:

| 14 |                |                |                |                |                | . <u>.</u>     |                |  |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

| 7  | 6              | 5              | 4              | 3              | . 2            | 1              | 0              |  |

| 0. | b <sub>7</sub> | b <sub>6</sub> | b <sub>5</sub> | b <sub>4</sub> | b <sub>3</sub> | b <sub>2</sub> | b <sub>1</sub> |  |

Bit Position GEMINI Representation

Binary/Decimal Digits --

Within the arithmetic data types, either binary or decimal representations of numbers are used. A binary digit can be 0 or 1; a decimal digit consists of four binary digits and can have a numeric value of 0 through 9. A sign digit at the trailing end of a number indicates whether the number is positive or negative. A binary sign digit of 0 indicates a positive value, and a binary sign digit of 1 indicates a negative value. A decimal sign digit of 10 (binary 1010) indicates a positive value, and a decimal sign digit of 11 (binary 1011) indicates a negative value.

#### Integer --

The integer (a signed or unsigned whole number) assumes a leading (low-order) binary or decimal point. For signed integers the trailing digit is the sign digit, while for the unsigned integers the trailing digit is the highest order digit of the number.

The maximum value of an integer is expressed as:

$$+ (r^{n-1})$$

where r is the radix (2 for binary, 10 for decimal)

n is the number of digits in the operand,

excluding the sign digit

Any other integer value represented may be expressed as:

$$\pm (\underline{d}_{\underline{n}-1}\underline{r}^{\underline{n}-1} + \underline{d}_{\underline{n}-2}\underline{r}^{\underline{n}-2} + \dots + \underline{d}_{1}\underline{r}^{1} + \underline{d}_{0}\underline{r}^{0})$$

where d is the ith digit in the operand

n is the number of digits in the operand,

excluding the sign digit

r is the radix (2 for binary, 10 for decimal)

Fraction --

The fraction always has a sign digit in the trailing digit position. The fraction assumes a binary or decimal point between the trailing (high-order) numeric digit and the sign digit. The value of the fraction is expressed as follows:

## 2.3.3 Arithmetic Operands

There are 3 basic forms of arithmetic data: the computational, integer, and logical. The <u>computational</u> form has an exponent part with integer format and a fixed-point part with fraction format. There are 8 data types that have the computational form; they are distinguished as having BINARY or DECIMAL

base, FIXED or FLOAT scale, and REAL or COMPLEX mode. The

integer form has only an integer part in the integer format.

There are 4 data types that have the integer form: the 2

signed INTEGER data types, distinguished as having BINARY

or DECIMAL base, and the 2 unsigned data types, MAGNITUDE

and ADDRESS. The logical form has a byte-string format.

All bits in each byte in the string are treated independently. The LOGICAL data type has the logical form.

This discussion presents the formats of the data types with the computational and integer forms. The computational data types include real and complex operands, and the integer data types include integer, magnitude, and addressing operands.

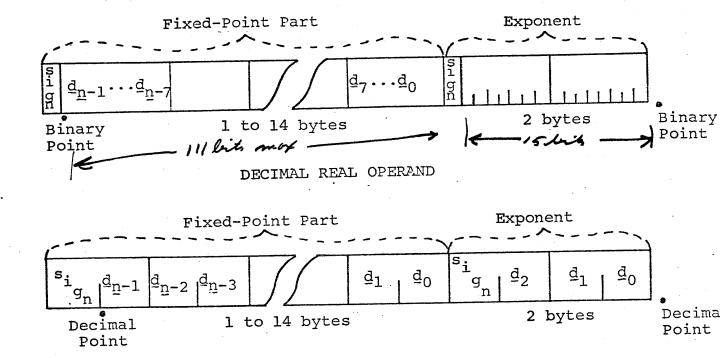

Real Operand --

A <u>real operand</u> (see Figure 2.3) is a binary or decimal number consisting of a fixed-point part and an exponent.

The exponent has an integer format and occupies the 2 leading bytes; the fixed-point part has a fraction format and occupies the next 1 to 14 bytes. The trailing digit in both fixed-point part and exponent is a sign digit.

The value of the real operand is the product

fre.

where  $\underline{\underline{f}}$  is the value of the fixed-point part  $\underline{\underline{r}}$  is the radix (2 or 10)  $\underline{\underline{e}}$  is the value of the exponent

The range of the real operand is constrained by the value of the exponent. The maximum absolute value of  $\underline{e}$  is  $2^{15}-1$  for binary and  $10^3-1$  for decimal.

A real operand has either a binary format or a decimal format in both exponent and fixed-point parts. For each format there are 2 data types distinguished as FIXED or FLOAT. This distinction serves to specify which of 2 sets of computational controls are used during execution of an operation. (The computational controls are discussed in 4.3 Computational Arithmetic.) Thus, there are 4 data types for real operands:

- BINARY FIXED REAL

- BINARY FLOAT REAL

- DECIMAL FIXED REAL

- DECIMAL FLOAT REAL

#### BINARY REAL OPERAND

Figure 2.3 Real Operands

Complex Operand --

A <u>complex operand</u> (see Figure 2.4) represents numbers of the form

$$z = x + yi$$

where  $\underline{i}$  is the imaginary coefficient and consists of the pair of equal-length real operands  $\underline{x}$  and  $\underline{y}$ . The leading member of the pair is the real component  $\underline{x}$ , and the trailing real number is the imaginary component  $\underline{y}$ . The resulting complex operand may be 6 to 32 bytes long in even increments.

The two real operands have the same base (BINARY or DECIMAL) and scale (FIXED or FLOAT). Thus, there are 4 data types for complex operands:

- BINARY FIXED COMPLEX

- BINARY FLOAT COMPLEX

- DECIMAL FIXED COMPLEX

- DECIMAL FLOAT COMPLEX

| imaginary component | real component |  |

|---------------------|----------------|--|

| 3 to 16 bytes       | 3 to 16 bytes  |  |

Figure 2.4 Complex Operand

Integer Operand --

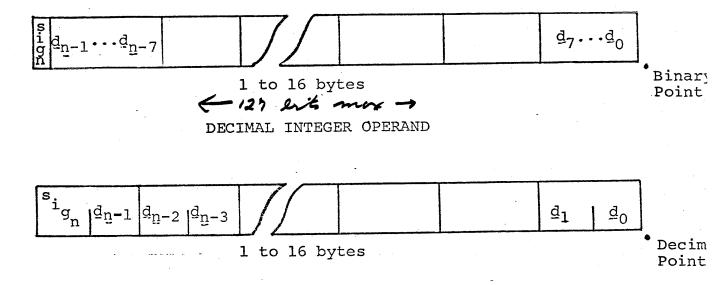

An <u>integer operand</u> (see Figure 2.5) is a signed binary or decimal integer from 1 to 16 bytes long. The trailing digit of the operand is a sign digit, and the digit that immediately precedes the sign digit is the highest order digit. A binary or decimal point is assumed to precede the lowest order (leading) digit. There are 2 data types for integer operands:

- BINARY INTEGER

- DECIMAL INTEGER

### BINARY INTEGER OPERAND

Figure 2.5 Integer Operands

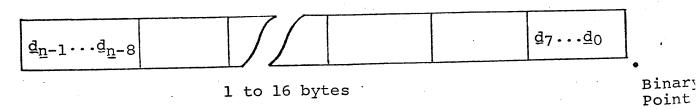

Magnitude Operand --

A magnitude operand (see Figure 2.6) is an unsigned binary integer from 1 to 16 bytes long. The trailing digit position has the highest order of magnitude. All magnitude operands have the MAGNITUDE data type.

Figure 2.6 Magnitude Operand

#### Address Operand --

An <u>address operand</u> (see Figure 2.7) is an unsigned binary integer 1 to 16 bytes long. The two trailing bits are ignored in address arithmetic. The two trailing bit positions are treated separately so that segment number register codes remain unaffected by address arithmetic (see 3.1.2 Address Elements). All address operands have the ADDRESS data type.

Figure 2.7 Address Operand

## 2.3.4 Logical

The <u>logical operand</u> is a set of 1 to 16 contiguous bytes.

These operands are used in character or bit string manipulations with logical operations (Boolean arithmetic).

The instruction set permits bit manipulation within operands that have byte lengths. Logical operands have the LOGICAL data type.

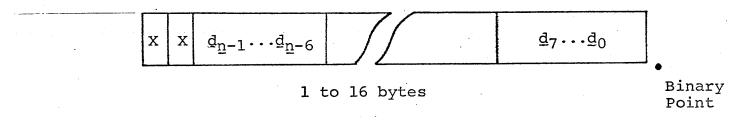

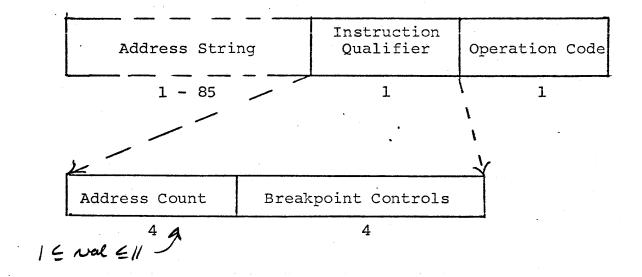

#### 2.3.5 Instructions

GEMINI Computer Systems provide 3 formats for instructions: standard, extended, and null. The formats of these instructions are shown in Figure 2.8.

Standard Instructions --

A standard instruction consists of an operation code followed by an instruction qualifier and a variable-length address string.

The <u>operation code</u> is one byte long and is used to specify the function to be performed by the instruction.

The <u>instruction qualifier</u> byte contains an address count and breakpoint controls. The address count indicates the number of addresses to be found in the address string and may vary from 1 to 11 in value. The address count is a function of the operation specified by the instruction. The breakpoint controls permit tagging of an instruction for debugging purposes. The breakpoint controls are described in detail in 6.0 <u>Execution Breakpoints</u>.

The number of addresses in an <u>address string</u> corresponds to the address count. Each address, depending upon its type, can vary from 1 to 17 bytes in length. Address formats are discussed in 3.1 Address Formats.

#### STANDARD INSTRUCTIONS

EXTENDED INSTRUCTIONS

| Address String | Instruction<br>Qualifier | Extended<br>Operation<br>Code | Operation<br>Code =<br>Extend |

|----------------|--------------------------|-------------------------------|-------------------------------|

| 1 - 85         | 1 /                      | 1                             | 1                             |

|                | 1 = wal = 16)            |                               |                               |

NULL INSTRUCTION

Figure 2.8 Instruction Formats Showing Field Lengths in Bytes

#### Extended Instructions --

An extended instruction consists of an operation code followed by an extended operation code, an instruction qualifier, and an address string. The operation code specifies that the byte following it is an extended operation code. The instruction qualifier and address string for extended instructions are the same as those defined for standard instructions, except that there can be as many as 16 addresses in the address string.

#### Null Instruction --

The null instruction consists of an operation code only and specifies that no operation is to be performed.

#### 2.3.6 Control Operand

The instruction set utilizes a variety of implicit operand formats for passing information between called and calling routines; for providing tables of entries to system and subsystem services; and for providing base addresses, pointers, and element lengths for the queues, stacks, and rings of list processing. These formats are presented here for summary reference only; detailed information is given where the formats are discussed in context with related material.

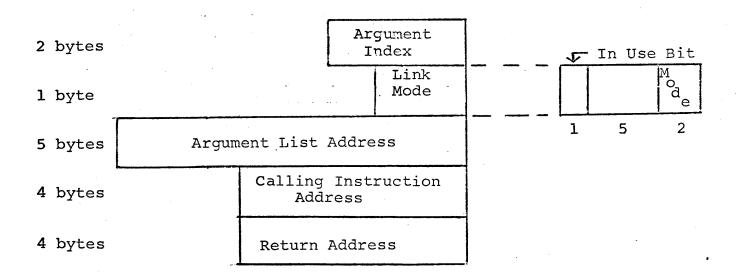

Subprogram Control Block --

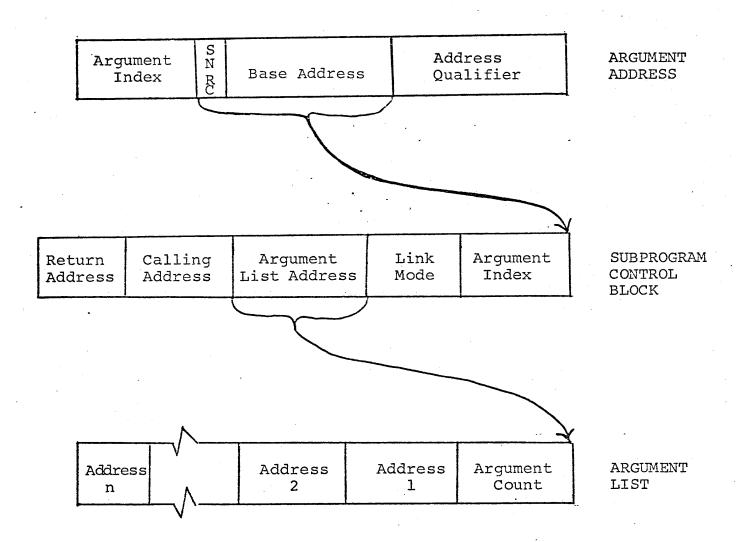

The <u>subprogram control block</u> contains information needed by a service program or a subprogram to effect a return to the program that called it and to refer to arguments provided by the calling program. The control block contains addresses of the calling instruction and the return location, and an argument list address for referring to operands used by the subprogram but provided by the calling program. An argument index and link mode are provided for utility and system integrity. The subprogram control block has a 16-byte format, as shown in Figure 2.9.

Figure 2.9 Subprogram Control Block

System and Subsystem Service Entry Tables --

The system and all subsystems maintain tables to specify the entry location of the routines that perform system and subsystem services. Each entry in the table is 4 bytes long and provides a 30-bit address value and a 2-bit transition mode value, as shown in Figure 2.10. For the system service entry table the address value points to the entry of a system service routine and has an understood segment number register code of 3. For a subsystem service entry table, the address value points to the entry of a subsystem service routine and has an understood segment number register code of 1. The transition mode specifies a central processor mode for execution of the service.

| Entry | 2                    | 30            |  |

|-------|----------------------|---------------|--|

| 1     | Transi-<br>tion Mode | Address Value |  |

| 2     | Transi-<br>tion Mode | Address Value |  |

| 1     |                      |               |  |

| •     |                      |               |  |

| •     |                      |               |  |

| n     | Transi-<br>tion Mode | Address Value |  |

| -     | 21011 11000          |               |  |

Figure 2.10 Service Entry Table

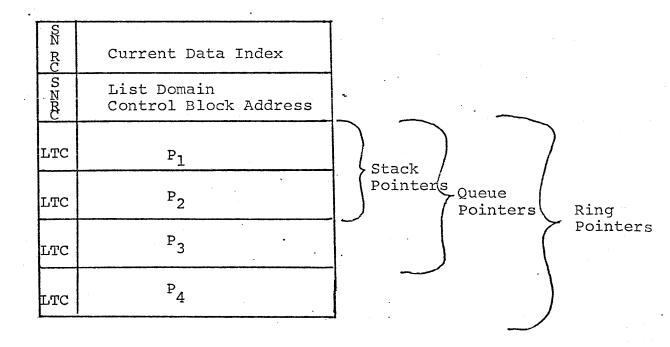

List and List Domain Control Blocks --

The list control block and the list domain control blocks are used by the list processing operations. The list control block contains addresses and pointers to list elements, while the list domain control block provides characteristics of the list domain such as size, element length, and location of next free element. The formats of these control blocks are given in Figure 2.11.

| E.                 | lem                               | nent Data Index    |                                                                                          |  |  |

|--------------------|-----------------------------------|--------------------|------------------------------------------------------------------------------------------|--|--|

|                    | Lis                               | st Domain Index    |                                                                                          |  |  |

| LTC Pointer 1 (pl) |                                   | Pointer l (pl)     |                                                                                          |  |  |

| LT(                | 3                                 | Pointer 2 (p2)     | Stack Control Block                                                                      |  |  |

| LTC Pointer 3 (p3) |                                   | Pointer 3 (p3)     | Queue Control Block                                                                      |  |  |

| LTO                | LTC Pointer 4 (p4)                |                    | Ring Control Block                                                                       |  |  |

| LIST               | DC                                | MAIN CONTROL BLOCK |                                                                                          |  |  |

| E<br>L             | Data Length Pointer Address Value |                    | EL = Element Size Code<br>LTC = List Type Code<br>SNRC = Segment Number<br>Register Code |  |  |

| CZZC               |                                   |                    |                                                                                          |  |  |

| CH ZO CHZO         | Data Address Value                |                    |                                                                                          |  |  |

| 0                  | Next Free<br>Element Number       |                    |                                                                                          |  |  |

Figure 2.11 List and List Domain Control Blocks

### 3.0 ADDRESSING

A standard instruction or an extended instruction contains a variable length address string (see Figure 2.8 Instruction Format). The address string contains a variable number of addresses and each address provides the necessary information to define an operand. An operand is a value or a storage location referenced in the execution of an instruction. Each address in the address string either defines an operand or specifies the location of another address which in turn defines the operand.

An address defines an operand either by containing the operand value or by specifying the location of the operand. The location of an operand is referred to by an effective address, which specifies the beginning byte location. Because an operand can be variable in length, an address may also specify the length of the operand. The various methods of defining an operand form 5 classes of addressing:

- Null the address is omitted from the address string

- Immediate the address contains the operand value

- Direct the address specifies the location of an operand

- Indirect the address specifies the location of another address which in turn defines the operand

- Argument The address references a byte string that contains a list of addresses. An address in the list defines the operand

Two of the classes, direct and indirect, permit the use of indexing to specify an effective address. When indexing is used, the effective address is calculated using a value in the address modified by a value in an index. An index is a 4-byte field in memory that contains an effective address.

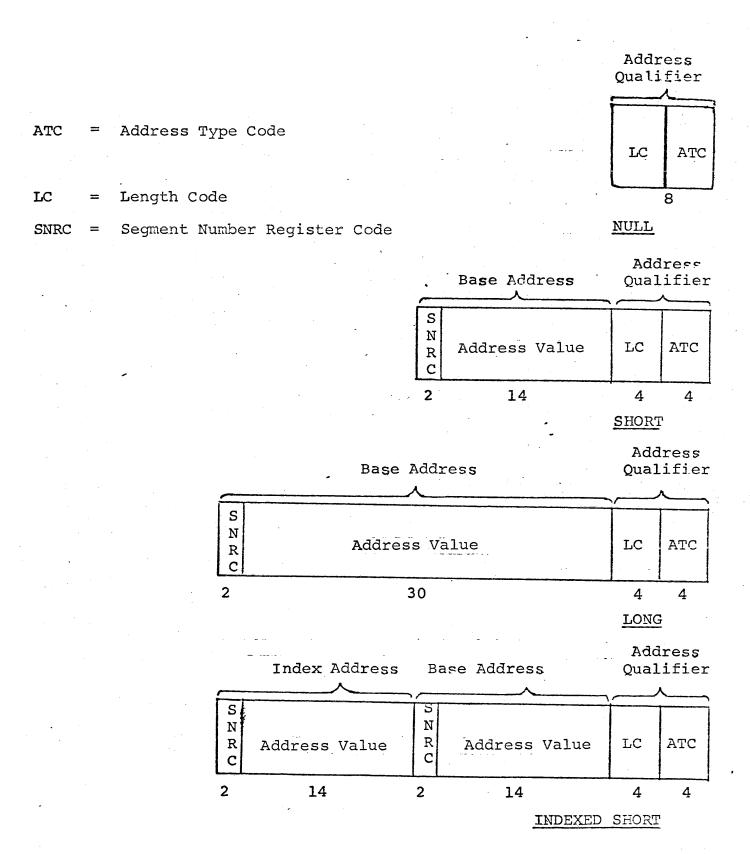

### 3.1 ADDRESS FORMATS

An <u>address</u> is a byte string consisting of an address qualifier and 0, 1,or 2 of the following elements:

- Base Address

- Index Address

- Argument Index

- Immediate Operand

There are 8 address formats, ranging in length from 1 to 17 bytes. Permissible combinations are depicted in Figure 3.1.

# 3.1.1 Address Qualifier

The <u>address qualifier</u> is the leading byte of each address and consists of a 4-bit address type code and a 4-bit length code.

The <u>address type code</u> indicates the class of addressing, the address format, and optionally an indexing method. The address type codes are listed in Table 3.1.

The <u>length code</u> specifies the operand length. Values of 1 through 15 specify, respectively, operand lengths of 1 through 15 bytes. A value of 0 specifies an operand length of 16 bytes, or in certain uses it specifies an address that requires no length specification.

### 3.1.2 Address Elements

An <u>address value</u> specifies a byte location as a binary magnitude number that is either 14 or 30 bits in length.

Figure 3.1 Address Formats (1 of 2)

| _                | Index Address | J (              | Base Address       |    | dress<br>Lifier |

|------------------|---------------|------------------|--------------------|----|-----------------|

| S<br>N<br>R<br>C | Address Value | S<br>N<br>R<br>C | -<br>Address Value | ĿC | ATC             |

| 2                | 14            | 2                | 30                 | 4  | 4               |

| N                |               |                  |                    |    |                 |

# INDEXED LONG

Figure 3.1 Address Formats (2 of 2)

Table 3.1 Address Type Codes

|                         | ·         |                | † <del></del>                               |

|-------------------------|-----------|----------------|---------------------------------------------|

| Address<br>Type<br>Code | Class     | Format         | Addressing Type                             |

| 0                       | Null      | Null           | Null                                        |

| 1                       | Direct    | Short          | Short Direct                                |

| 2                       | Direct    | Indexed Short  | Short Direct With Displacement Indexing     |

| 3                       | Direct    | Indexed Short  | Short Direct With Alignment Indexing        |

| 4                       | Indirect  | Short          | Short Indirect                              |

| 5                       | Argument  | Argument Short | Short Argument                              |

| .6                      | Indirect  | Indexed Short  | Short Indirect With Displacement Indexing   |

| 7                       | Indirect  | Indexed Short  | Short Indirect With<br>Alignment Indexing   |

| 8                       | Immediate | Immediate      | Immediate                                   |

| 9                       | Direct    | Long           | Long Direct                                 |

| 10                      | Direct    | Indexed Long   | Long Direct With<br>Displacement Indexing   |

| 11                      | Direct    | Indexed Long   | Long Direct With<br>Alignment Indexing      |

| 12                      | Indirect  | Long           | Long Indirect                               |

| 13                      | Argument  | Argument Long  | Long Argument                               |

| 14                      | Indirect  | Indexed Long   | Long Indirect With<br>Displacement Indexing |

| 15                      | Indirect  | Indexed Long   | Long Indirect With Alignment Indexing       |

|                         |           |                |                                             |

|                         |           |                |                                             |

A 14-bit number is referred to as a short address value, and a 30-bit number is referred to as a long address value. When a short address value is used, 16 high-order 0's are appended prior to its use in the computation of the effective address.

A <u>segment number register code</u> is a 2-bit binary magnitude number used in the specification of a segment number register. (See discussion in 2.2.2 <u>Formation of a Complete Virtual Address.</u>)

A <u>base address</u> consists of an address value and a segment number register code. When a base address is present in an address format, it immediately follows the address qualifier. A <u>short base address</u> contains a short address value and is 2 bytes long. A <u>long base address</u> contains a long address value and is 4 bytes long.

An <u>index address</u> specifies the location of a <u>4-byte</u> index and has the same format as a short base address. When an index address is present in an address format, it immediately follows the base address. An index address is always 2 bytes long.

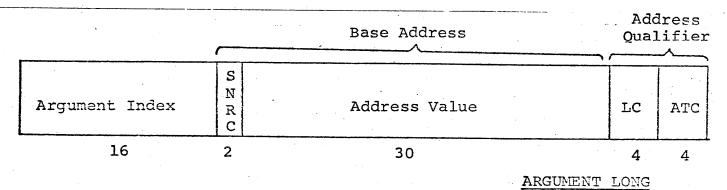

An <u>argument index</u> is a 16-bit binary magnitude number. In an address that specifies argument addressing, the argument index immediately follows the base address.

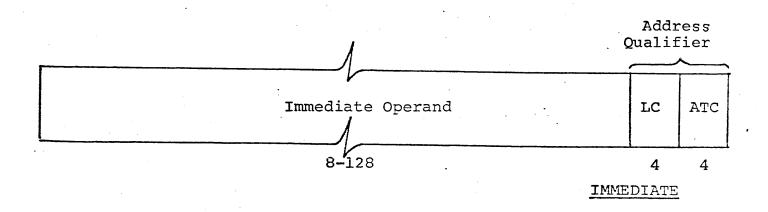

An <u>immediate operand</u> is a value in the address that is used as an operand in the execution of an instruction. The immediate operand immediately follows the address qualifier.

#### 3.2 INDEXING

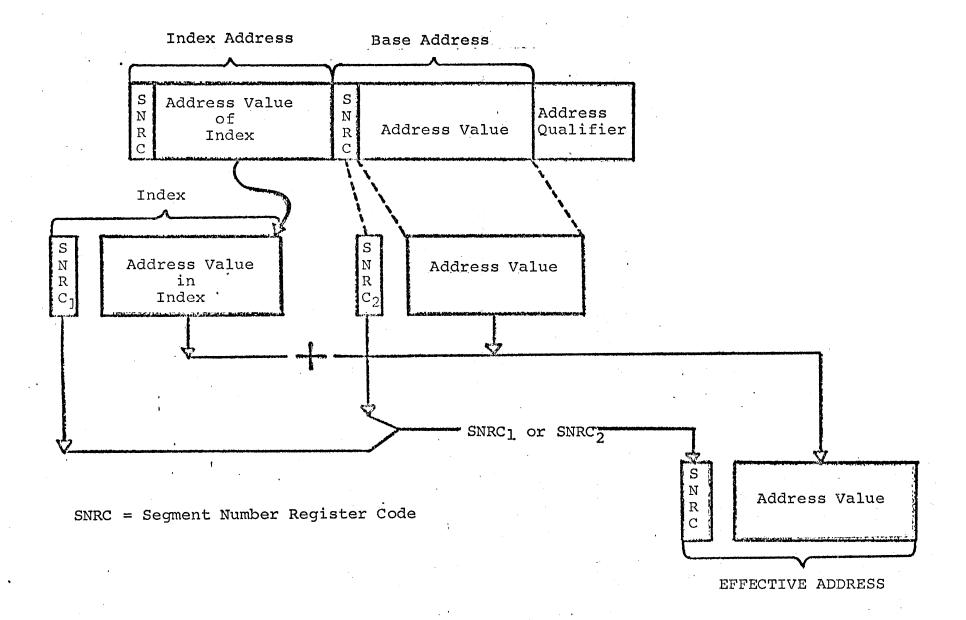

Indexing operations can be performed in both direct and indirect addressing. Indexing requires an address format with a base address and an index address. When indexing is performed, the address value specified by the base address is modified by the contents of an index to form the effective address. The segment number register code in the effective address is specified either by the base address or the index.

An <u>index</u> is 4 bytes in length and contains a long address value and a segment number register code. The format of the index is identical to that of an effective address.

All indexing operations are performed using binary magnitude arithmetic which produces a result in the range 0 to 2<sup>30</sup>-1. The operation performed is identical to that described in 4.5 <u>Magnitude Operations</u> except that the truncation interrupt is never generated.

# 3.2.1 <u>Displacement Indexing</u>

In displacement indexing, the address value in the base address is added to the address value in the index to form the address value in the effective address (see Figure 3.2).

Figure 3.2 Displacement Indexing

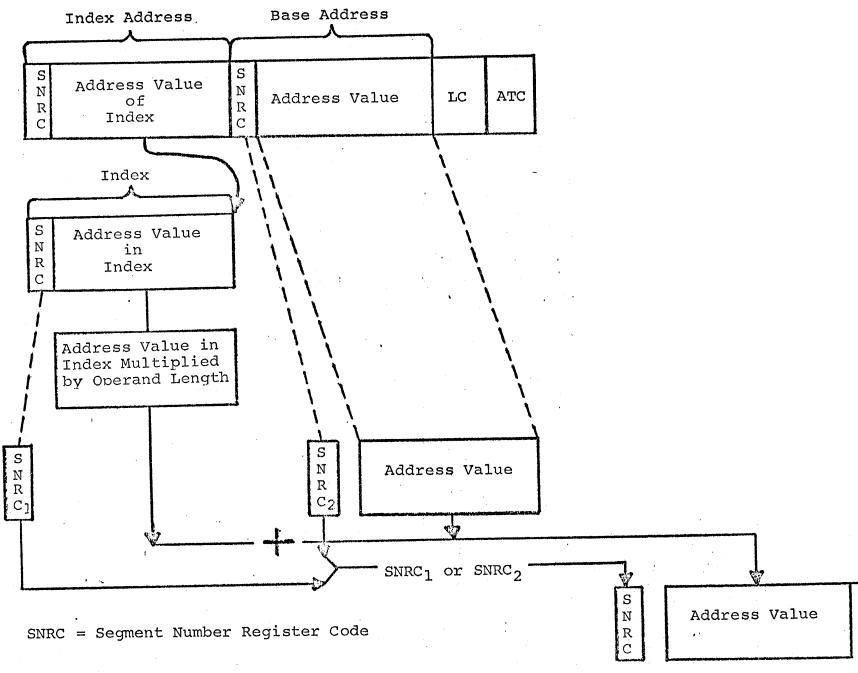

### 3.2.2 Alignment Indexing

In alignment indexing, the address value in the index is multiplied by the length of the operand. The product is then added to the address value in the base address to produce the address value in the effective address (see Figure 3.3).

Alignment indexing specifies elements in an array by their position within the array. The positions within an array are numbered 0 through  $\underline{n}$ -1, where  $\underline{n}$  is the total number of elements in the array. The length of the elements in the array is specified by the length code of the instruction that references the array.

# 3.2.3 Specification of the Segment Number Register Code

When indexing is performed, the segment number register code in the effective address is the segment number register code in the index or the segment number register code in the base address, whichever is greater. However, the segment number register code in the index must be less than or equal to the segment number register code in the index address.

### 3.3 NULL ADDRESSING ...

A null address consists of only an address qualifier containing an address type code of 0 and a length code of 0.

A null address either indicates the omission of an operand

Figure 3.3 Alignment Indexing

EFFECTIVE ADDRESS

or indicates that the first address in the instruction specifies the effective address. The use of null addressing is discussed in 4.2.2 <u>Implicit Addresses</u> and 4.2.1 <u>Optional</u> Operands.

#### 3.4 IMMEDIATE ADDRESSING

Immediate addressing uses a value in the address, called an immediate operand, as an operand in the execution of the instruction. The data format of the immediate operand is determined by the operation code of the instruction.

One addressing type is associated with immediate addressing. The address format consists of an address qualifier with a length code value from 1 to 8, followed by an operand that is from 1 to 16 bytes in length. Except for complex operations, the length code specifies the length of the immediate value. For complex operations the length code specifies the length code specifies the length of the real component, and the imaginary component is assumed to be the same length; thus, for complex operations the immediate operand is twice the length specified by the length code.

Immediate addressing cannot be used to specify an operand that is used as the destination for the result of an operation nor to specify a location for the transfer of control.

### 3.5 DIRECT ADDRESSING

Direct addressing specifies the effective address using a base address or a base address modified by a displacement or alignment indexing calculation. The address format consists of an address qualifier, a base address, and optionally an index address. Associated with direct addressing are 6 addressing types:

- Short Direct Type -

The effective address is specified by a short base address.

- Long Direct Type -

The effective address is specified by a long base address.

- Short Direct with Displacement Indexing -

The effective address is specified by a short base address modified by a displacement indexing calculation.

- Long Direct with Displacement Indexing The effective address is specified by a long base address modified by a displacement indexing calculation.

- Short Direct with Alignment Indexing -The effective address is specified by a short base address modified by an alignment indexing calculation.

- Long Direct with Alignment Indexing The effective address is specified by a long base address modified by an alignment indexing calculation.

# 3.6 INDIRECT ADDRESSING

When <u>indirect addressing</u> is used, the address in the address string of the instruction specifies the location of another address. That address, referred to as the <u>final address</u>, defines the operand.

In indirect addressing the location of a final address is specified by a base address or by a base address modified by a displacement or alignment indexing calculation. The address format consists of an address qualifier, a base address, and an optional index address. The length code specifies the length of the final address. Six addressing types specify indirect addressing:

- Short Indirect Type The location of a final address is specified by a short base address.

- Long Indirect Type The location of a final address is specified by a long base address.

- Short Indirect with Displacement Indexing The location of a final address is specified by a short base address modified by a displacement indexing calculation.

- Long Indirect with Displacement Indexing -The location of a final address is specified by a long base address modified by a displacement indexing calculation.

- Short Indirect with Alignment Indexing The location of a final address is specified by a short base address modified by an alignment indexing calculation.

- Long Indirect with Alignment Indexing The location of a final address is specified by a long base address modified by an alignment indexing calculation.

Only one level of indirect addressing is permitted, and the final address must specify null, immediate, or direct addressing.

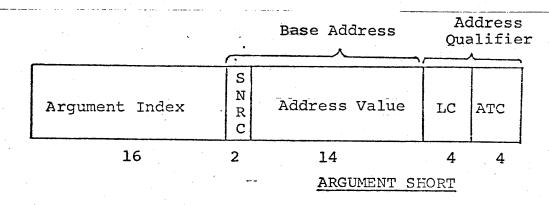

### 3.7 ARGUMENT ADDRESSING

Argument addressing (see Figure 3.4) provides a method for passing operands to and from a called subprogram. When argument addressing is used, reference is being made to an operand defined by an address in an argument list. The argument list contains a count of the number of addresses as well as the actual list of addresses. The location of the argument list is specified in a subprogram control block along with control information necessary for argument addressing.

SNRC = Segment Number Register Code

Figure 3.4 Argument Addressing

The addressed operand is accessed through two levels of indirection:

- First, the base address in the instruction specifies the location of the subprogram control block. The subprogram control block specifies the location of the argument list.

- Second, an argument index in the instruction, or the subprogram control block, specifies the appropriate address in the argument list. The alternate argument index in the subprogram control block is chosen whenever the argument index value in the instruction has the value 0.

The resulting address, referred to as the final address, defines the operand.

# 3.7.1 Argument Addressing Formats

The <u>argument address</u> has a format that consists of an address qualifier specifying argument addressing and a length code of 0, a base address, and an argument index. The base address specifies the location of a subprogram control block. The <u>argument index</u> occupies 2 bytes and contains a binary magnitude number.

An argument index in the range of 1 to 2<sup>16</sup>-1 specifies the position of an address in the argument list. An argument index value of 0 indicates that the alternate argument index in the subprogram control block is to be used for the specification of an address position in the argument list.

There are 2 addressing types that specify argument addressing.

# Short Argument

A short base address specifies the location of the subprogram control block.

### • Long Argument -

A long base address specifies the location of the subprogram control block.

# 3.7.2 Subprogram Control Block

A subprogram control block, with the exception of the value of the alternate argument index, is automatically generated during the execution of CALL, SYSTEM, and SUB-SYSTEM instructions. The use of this control block is discussed in 4.9 Control Operations. The following topics discuss the argument index, argument list address, and link mode used during argument addressing.

# Argument Index --

The argument index field contains an argument index that is used only if the argument index in the argument address is equal to 0. If this argument index is used, its value ranges from 1 to 2<sup>16</sup>-1 and specifies, respectively, the first through the last addresses in the argument list. If the argument address contains a nonzero argument index, this field is ignored.

# Argument List Address --

The argument list address field contains a long direct address that specifies the location of an argument list. During argument addressing, the length code specified by the argument list address is ignored.

#### Link Mode --

The leading 2 bits of the link mode field contain a value in the range 0 through 3 that specifies the access mode used during argument addressing. This field is required only if argument addressing is performed in a central processor mode greater than 0. If the central processor mode is 0, the link mode is assumed also to be 0. The access mode is discussed in 2.2.3 Access Mode.

# 3.7.3 <u>Argument List</u>

An <u>argument list</u> is a byte string consisting of a 2-byte  $\frac{16}{1}$  argument count and from 0 to  $2^{16}-1$  fields that are each 8

bytes in length. The argument count specifies the number of fields in the list. Each field contains an address adjusted to the leading byte of the field. The argument list format is shown below:

|              |          |              |              | <del></del>       |

|--------------|----------|--------------|--------------|-------------------|

| Address<br>n |          | Address<br>2 | Address<br>1 | Argument<br>Count |

|              | L        |              | <u> </u>     |                   |

| 8            | <b>/</b> | 8            | 8            | 2                 |

# 3.7.4 Mechanism of Argument Addressing

The base address associated with an argument address specifies the location of a subprogram control block. The subprogram control block is accessed and it specifies the location of an argument list. In order to access the argument list, the access must be legal in the mode specified by the link mode. The link mode must be less than or equal to the central processor mode.

An address in the argument list is specified either by the argument index in the argument address or by the argument index in the subprogram control block. If the argument index in the argument address is equal to 0, the argument index in the control block is used. If both argument indexes equal 0, or if the argument index used is greater than the argument count, the illegal argument index interrupt condition occurs.

The location of the referenced address in the argument list is calculated as follows:

Location = ALEA + 2 + 8\*(AI-1)

where ALEA is the effective address of the argument list and

AI is the argument index used

The specified address in the argument list is referred to as the <u>final address</u> and it defines the operand. Only one level of argument addressing is permitted and the final address must specify null, immediate, or direct addressing. If the final address references an operand in memory, the access must be legal in the mode specified by the link mode.

#### 4.0 INSTRUCTION SET

The GEMINI instruction set is divided into 8 groups according to the data format on which the instructions operate:

- Computational Arithmetic Operations -- REAL and COMPLEX data

- Integer Arithmetic Operations -- INTEGER data

- Magnitude Arithmetic Operations -- MAGNITUDE and ADDRESS data

- Logical Operations -- LOGICAL data

- Miscellaneous Byte Operations -- byte strings

- Control Operations -- instruction locations

- List Operations -- list control blocks

- Select Operations -- data formats specific to internal and external devices

The notation used to describe the instruction set is defined in 4.1 Notation, and the features that are common to more than one group of instructions are presented in 4.2 Common Characteristics. The succeeding topics (4.3 thru 4.10) enumerate and describe the individual instructions in each of the eight groups listed above.

### 4.1 NOTATION

This section defines the types of operands that are used in the various instructions and explains the manner in which the individual instructions are discussed.

# 4.1.1 Operand Type

In the description of each instruction, the addresses that form the address string in the instruction are classified

according to the way the operation uses the operand that each address specifies.

Under this classification, there are 3 types of operands: destination operands, source operands, and address operands.

Destination Operands --

A <u>destination operand</u> is a byte string in memory whose contents may be altered by the operation. A destination operand is either the receiving field for the result of an operation or a control block that is affected by the operation. For all instructions that have destination operands, the destination operand is specified by the first address in the instruction address string. A destination operand cannot be specified using null addressing or immediate addressing.

Source Operands --

A <u>source operand</u> is a value used by the operation. Source operands are specified by any type of addressing. Null addressing specifies an implicit operand (see 4.2.2 <u>Implicit Addresses</u>) or an omitted optional operand (see 4.2.1 <u>Optional Operands</u>). Immediate addressing specifies the value of the operand. Direct addressing specifies a byte string in memory whose contents are the value of the operand. If indirect or argument addressing is used, the final address may specify null, immediate, or direct addressing.

# Address Operands --

An address operand is the effective address of a memory location to which control may be transferred.

The contents of that memory location are not read or altered by the operation. An address operand can be specified only by direct addressing in the instruction address string or by direct addressing in the final address when indirect or argument addressing is used.

# 4.1.2 Instruction Descriptions

Each instruction description consists of the name of the instruction and the following topics:

- Operation

- Syntax

- Program Interrupts

- Semantics

# Operation --

This topic lists names for all operations to which the instruction description applies. If only one operation is applicable, its name is identical to the name of the instruction and the operation topic is omitted.

### Syntax --

This topic specifies the syntax of the instruction in the format of a GEMINI Programming Language (GPL) statement.

The syntax consists of keywords, special characters, function names, metavariables, and metacharacters.

Keywords appear in capital letters. They are used to identify the instruction or the meaning of particular operands.

Special characters are operators or delimiters. The operators are the traditional arithmetic, relational, and logical operators. The equal sign is used as a relational operator when it appears in a comparison operation and as the assignment operator in noncomparison operations. The delimiters are parentheses and commas. Parentheses are used to group one or more operands into a list. The list may specify the operands of a function, or it may follow a keyword that requires more than one operands in the list.

Function names appear in small letters. In function notation, the function name is used instead of a special character to denote an operation. Function notation is used only with the assignment operation; otherwise, keyword notation is used.

Metavariables appear in boldface and represent addresses in the address string. Each metavariable consists of a letter indicating the usage of the operand specified by the address, and a number indicating the position of the address in the instruction address string. The letters

used are <u>d</u> for destination operand, <u>s</u> for source operand, and <u>a</u> for address operand. The allowable metavariables are <u>dl</u>, <u>sl</u> through <u>sll</u>, and <u>al</u> through <u>a5</u>. In an actual GPL statement, programmer-specified symbols or literal values would replace these metavariables. The data type of the programmer-specified symbols determines which of a set of operation codes, all with the same syntactic representation, is specified for execution. The data type is ordinarily specified in a GPL DECLARE statement.

Another type of metavariable consists of the name of an option in boldface letters. This type of metavariable is used to specify options that are common to many instructions and whose format is described separately.

The metacharacters are the boldface brackets [ ]. The brackets are used to indicate an option in the address string (see 4.2.1 Optional Operands).

### Program Interrupts --

This section of the instruction description names the special interrupt conditions that can occur when one or more of the described operations is executed. If no special interrupt conditions can occur, this topic is omitted. Interrupt conditions that are common to all instructions (see 4.2.6 Program Interrupt) are not included.

Interrupt conditions are listed individually, by class, or by subclass. The class and subclass names refer to the classification of interrupts in 7.6. Program Interrupt Group. When a class or subclass name appears, it indicates that every interrupt condition in that class or subclass can occur when one or more of the operations are executed.

### Semantics --

This section gives a description of the instruction execution and how the various operands affect the operations. It does not include a description of steps common to all instructions or to an entire group. Steps common to all instructions are described in 4.2 Common Characteristics. Those common to a group of instructions are discussed before the descriptions of that group.

#### 4.2 COMMON CHARACTERISTICS

Certain features of the instruction set are common to all instructions or to instructions in more than one group of instructions. Those features are explained in the following paragraphs.

# 4.2.1 Optional Operands

Almost all instructions allow one or more of the possible operands to be omitted. Operands that are not needed for meaningful execution are called optional operands. The omission of an optional operand from an instruction is indicated through null addressing.

In the syntax of an instruction, optional portions are enclosed in brackets. In the following instruction format the operand <u>s4</u> is optional; it and the keyword 'MASK' may be omitted, and the instruction will still be valid.

IF  $\underline{s2} = \underline{s3}$  [MASK  $\underline{s4}$ ] THEN GO TO al [iteration]

# 4.2.2 Implicit Addresses

Many instructions allow the original contents of the destination operand to be used as a source operand. This is called <u>implicit</u> addressing. When implicit addressing is permitted, null addressing in the address string of the

instruction, or in the final address when indirect or argument addressing is used, indicates that the source operand is being specified by the destination operand address.

Any source operand that is not defined as an optional operand (see 4.2.1 Optional Operands) can be specified by implicit addressing if the first address in the string is a destination operand. Note that source operands in comparison operations cannot be specified by implicit addressing because the first address is an address operand. In the following example, source operands s2 and s3 are not optional; therefore, they can be specified by implicit addressing.

dl = s2 + s3 [ADJUST (s4 [, s5] )] [iteration]

In the formation of the instruction address string, null addresses that indicate either implicit addressing or omitted optional operands can be excluded from the address string completely if they are not followed by any nonnull addresses. If a nonnull address does appear, all previous null addresses are required in the address string to mark the position of the nonnull address.

# 4.2.3 <u>Iteration</u>

The arithmetic, magnitude, logical, and miscellaneous byte groups of instructions can be performed iteratively by specifying an iteration count and index increments for appropriate operands. The iteration count is specified by a source operand following the keyword 'PERFORM'. The index increments are specified by a parenthesized list of source operands following the keyword 'INCREMENTS'. One index increment may be specified for each operand in the instruction; therefore, depending on the instruction, there can be 2 to 5 index increments. Each index increment is optional. An omitted index increment is treated as if an index increment with a value of zero had been specified.

When iteration is specified, the instruction is executed the number of times specified by the iteration count except in comparison operations, which are described below. After each execution, every index that is being used to specify the location of an operand is incremented by the corresponding index increment. In this way the successive executions of the instruction can operate with successive elements in an array. When an operand is specified by indirect or argument addressing, only an index in the final address is incremented.

In comparison operations, iteration is discontinued when the comparison condition is met even if the iteration count is not exhausted. If the comparison is true, control is transferred to a location specified in the instruction. Indexes

are not incremented when the comparison is true. If the comparison is false, the indexes are incremented. The instruction is then repeated unless the iteration count has been exhausted, in which case control passes to the next sequential instruction.

In all instructions for which iteration is permitted, the iteration operands follow the other operands and are separated from them by a comma. Iteration is optional and the option is indicated in the instruction syntax by enclosing in brackets the metavariable 'iteration' as in the following example:

$$d1 = s2$$

&  $s3$  [iteration]

If the syntax were not abbreviated by using the metavariable, the option would appear as follows:

The numbering of the iteration operands ( $\underline{s4}$  through  $\underline{s7}$  in the above example) varies according to the number of operands that precede them in the instruction format.

A more complete discussion of iteration is contained in 5.0 ITERATIVE EXECUTION.

# 4.2.4 Suboperation Codes

The exact operation to be performed when an instruction is executed is often specified by a <u>suboperation code</u>. Suboperation codes are always source operands. Suboperation codes are interpreted bit by bit rather than as numeric values. Some bits may be ignored depending on the settings of other bits of the code. Only a certain number of leading bits in the specified operand are examined. All other bits are ignored. The bits that are examined may have any of the possible bit configurations.

# 4.2.5 Constraints

The operation code of an instruction constrains the operand lengths, the operand values, and the addressing types which can be specified. Whenever a constraint is violated, a program interrupt condition occurs. The constraints associated with a particular operation are discussed with the description of the operation. Following is a list of the constraints which are common to instruction execution.

#### Mode Constraints --

The segment number register code constraints which are dependent on central processor mode are discussed in 2.2.3

Access Mode.

Length Code Constraints --

The length code is constrained by the addressing type, and by the data format required for the operation. The constraints associated with an addressing type are discussed in 3.1 Address Formats, and the data formats are discussed in 2.3 Data and Instruction Formats.

Because the length of a control block is a function of the operation being performed, the address which specifies a control block must have an associated length code of 0.

Also, whenever an address specifies a location for the transfer of control, the length code must be 0.

Destination Operand Constraints --

A destination operand cannot be specified by null or immediate addressing.

Iteration Constraints --

The iteration count operand cannot exceed 2<sup>32</sup>-1. The index increment operands are assumed to be of ADDRESS data type.

Control Transfer Constraints --

A control transfer location cannot be specified by null or immediate addressing.

The segment number register code associated with the control transfer location is constrained by the central processor mode as follows:

- For central processor mode 0 (private mode),

only segment number register code 0 (private segment)

can be specified.

- For central processor mode 1, only segment number register code 1 or 2 can be specified .

- For central processor modes 2 and 3, only segment number register code 2 or 3 can be specified.

## 4.2.6 Program Interrupt

During instruction execution, conditions associated with the program interrupt group can occur. Those conditions which pertain to an individual instruction are listed in the description of the instruction, and those conditions which pertain to all instructions are listed in the following paragraphs. Program interrupts are further described in 7.4 Interrupt Processing and in 7.6 Program Interrupt Group.

Page Assignment Class --

These interrupt conditions occur when an attempt is made to write into an unassigned virtual address or to make any kind of access to a page currently in secondary storage. Generally, a real page assignment is made automatically by a service program.

Mode Violation Class --

These conditions occur when an attempt is made to execute a privileged instruction or to address memory while the central processor mode or the current access mode is less than required.

Illegal Addressing Class --

These conditions occur when a read access is attempted from an unassigned virtual address or a write access to a page protected against write access.

### Illegal Instruction Class --

These conditions occur when an attempt is made to execute a nonexistent standard or extended operation code or when an instruction qualifier, address qualifier, argument index, or subprogram control block is inconsistent with the operation code being executed or the effective addressing calculation being made.

Address Bounds Breakpoint Class --

These conditions occur when an access is attempted to an address within the bounds specified by an active address bounds register.

Instruction Breakpoint Class --

These conditions occur when the various breakpoint conditions are satisfied and the appropriate controls in the processor state vector and instruction qualifier are set. The breakpoint controls are discussed in 6.0 EXECUTION BREAKPOINTS.

Critical Operand Class --

These conditions occur when an operand specifies a value that is inconsistent with the operation codes of the instruction.

#### 4.3 COMPUTATIONAL ARITHMETIC

There are 8 types of computational arithmetic operations corresponding to the 8 computational data types, which are described in 2.3.3 <u>Arithmetic Operands</u>. These are a complete set of the data types with BINARY or DECIMAL base, FIXED or FLOAT scale, and REAL or COMPLEX mode.

For each computational data type there is a complete set of the following operations: replace, add, subtract, multiply, divide, absolute value, square, inner product, polynomial, if equal, and if not equal. For the 4 REAL types only, there are the additional operations square root, if less than, and if not less than.

Before the result of a computational operation is stored into memory or used in a comparison determination, it is adjusted and truncated. Adjustment is according to one of 3 methods, automatic, normalized, or manual, depending on controls in the processor state vector and in adjustment operands that optionally appear in the instruction. Truncation consists of either simply chopping off the low-order

digits of the result or <u>rounding</u> the portion to be retained before chopping off the low-order digits. Controls in the processor state vector and in adjustment operands specify whether or not rounding is done. Rounding is never done in comparison operations.

For each data type there is a set of 2 control bits in the processor state vector, a <u>normalization control</u> and a <u>rounding</u> <u>control</u>. An instruction can override the current settings of these controls by including the optional adjustment operands.

The following sections are an introduction to GEMINI computational arithmetic.

## 4.3.1 <u>Intermediate Results</u>

All computational arithmetic operations are carried out to produce intermediate results that represent the high order portion of the true result and which are contained in a 116 bit register for the fixed-point part and a separate register for the exponent part. The fixed-point part consists of a sign digit position and 115 binary or 28 decimal digits.

Two separate results are produced for the real and imaginary components of complex numbers. The intermediate results are adjusted by aligning both fixed-point and exponent parts according to one of three adjustment methods: normalized, automatic, and manual. The adjusted result is then truncated

either by rounding or chopping off low-order digits to produce the final result within a target length. Target length, adjustment methods, and truncation methods are all described in 4.3.2 through 4.3.9.

### 4.3.2 Target Length

For assignment operations (those in which the value of the result is stored into a destination operand) the target length is the length of the destination operand. For comparison operations the target length is the length of the longer of the two source operands being compared unless adjustment operands are included in the instruction and specify an explicit target length. For complex operations the target length is the same for both real and imaginary components.

#### 4.3.3 Normalized Representation

A REAL data item or a component of a COMPLEX data item is normalized if it has a non-zero digit in the high-order digit position of the fixed-point part or if it is an absolute zero (see 4.3.4 Absolute Zero and Relative Zero). Normalized representation provides a unique way of representing any value of a given data type.

## 4.3.4 Absolute Zero and Relative Zero

Absolute zero consists of a fixed-point part with a <u>negative</u> <u>sign</u> and all zero digits. The exponent part may have any value, but only an exponent value of +0 is returned by the computational operations for an absolute zero result. Absolute zero is understood to represent zero exactly and is distinguished from <u>relative zero</u>, which is understood to represent zero approximately. <u>Relative zero</u> is represented by a fixed-point part with a <u>positive sign</u> and all zero digits and an exponent part with any legitimate value. In computational operations a relative zero source operand is treated like any non-zero operand with regard to alignment of operands and determination of the exponent of the result.

## 4.3.5 Automatic Adjustment

When the automatic adjustment method is specified, adjustment of the intermediate result is made according to the exponents and the number of high-order zeros in the source operands. The kind of adjustment made depends on the nature of the operation.

The adjustments are made to provide automatic monitoring of significant digits in the fixed-point part of the result.

Automatic significant digit monitoring uses the binary or decimal point in the high-order position of the fixed-point