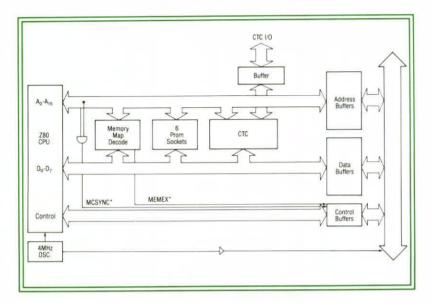

four CTC channels for longer count sequences.

All three Z80 interrupt modes are supported by the COLEX STD-CPU2 and multi-level interrupt processing is also supported. Nonmaskable interrupts are accepted and force a restart at location

COLEX STD-CPU2 boards are ideal solutions for OEM products as well as processor controllers, industrial automation, and a wide variety of other applications. They are completely compatible with other STD-Z80 Bus products.

### **SPECIFICATIONS**

#### ELECTRICAL

□ System Bus: STD-Z80

□ System Clock:

4.0 MHz

□ Address

Bus:

16 bits standard with

8 bits extended (for multiplex bank select)

□ Data Bus:

Loading:

8 bits, bi-directional

□ Signal

Inputs: One 74LS load

maximum

Outputs: -3mA min

@ 2.4 volts 24mA min

@ 0.5 volts

□ On-Board

Six 28-pin sockets Memory: Supports all three Z80 □ Interrupts:

modes

☐ System Interrupt Units: 1 SIU

□ Operating Temperature: 0° to 60° C

□ Power Requirements: @ 25° C

| Parameter | Condition | Min  | Тур | Max  | Units |

|-----------|-----------|------|-----|------|-------|

| Vcc       |           | 4.75 | 5.0 | 5.25 | volts |

| $I_{cc}$  | @ 5V      |      | 567 | 805  | mA*   |

<sup>\*</sup>Measured with no ROM/PROM/RAM installed in sockets

#### MECHANICAL

□ Card Dimensions:

| Form Factor | H    | W   | L   | Units  |

|-------------|------|-----|-----|--------|

| STD Bus     | 0.60 | 4.5 | 6.5 | inches |

□ PC Board Thickness: 0.062 inches

□ Connectors:

STD Bus: 56-pin dual readout;

0.125 inch centers

CTC Channel: 26-pin dual readout;

0.100 inch grid

### ORDERING INFORMATION

| Part Number | Description                                      |

|-------------|--------------------------------------------------|

| STD-CPU2    | 4 MHz Z80 Based Multi-                           |

| STM-CPU2    | function Processor Board<br>Technical Manual for |

| STWI-CI UZ  | STD-CPU2                                         |

# **FEATURES**

- □ Fully Buffered Z80A Processor

- □ STD-Z80 Bus Compatible

- □ 4 MHz Clock

- □ Memory Decoding on Any 2K Byte Boundary

- ☐ User Selectable Memory Devices: 28-pin Sockets

- □ Four Programmable Counter/Timer Channels

- □ Phantom PROM Capability

- □ Supports Memory Bank Switching

- □ Automatic Transparent Dynamic Memory Refresh Generation

- □ DMA to On-Board Memory Capability

- Supports All Three Z80 Interrupt Modes

- □ Power On Reset

- □ Selectable Wait State Generator

- □ Single +5 Volt Supply

- □ 4 MHz Operation

- □ Full 1 Year Warranty

## DESCRIPTION

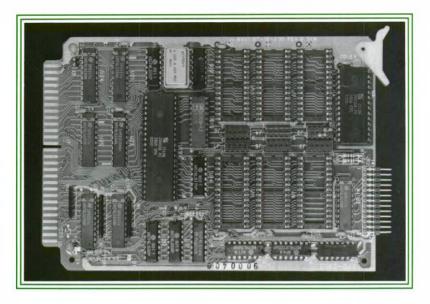

The COLEX STD-CPU2 is a powerful multi-function processor board for the industry standard STD Bus. It features a Z80 microprocessor, four counter/timer channels, and six 28-pin sockets for memory devices.

Exceptional memory flexibility is provided by six 28-pin memory sockets, enabling the user to populate the COLEX STD-CPU2 board with various combinations of ROM, RAM and EPROM. User selectable address decoding allows the user to configure each memory device within any 2K boundary of the 64K memory map for the board. A decoder PROM (supplied) allows the user to choose any of four preselected memory configurations. Alternately, the user may program a new decoder PROM to assign any of the six sockets to memory addresses as required by the application.

Expansion of the memory map beyond 64K of memory is possible by bank switching. This scheme is compatible with the COLEX STD-128DRAM and STD-256DRAM cards.

The STD-CPU2 generates all address and control signals necessary to refresh system dynamic RAM (such as STD-DRAM) boards. Refresh occurs automatically during each OP code fetch cycle, and is completely transparent to the system. Address, data, and control busses are bi-directional to allow external masters to directly access CPU memory.

A 4-channel counter/timer circuit (CTC) is included to support software controlled counting and timing functions. The CTC Trigger inputs and Zero Count outputs are buffered and externally available at a connector. In addition, a jumper selection makes it possible to cascade the