Filed Aug. 26, 1963

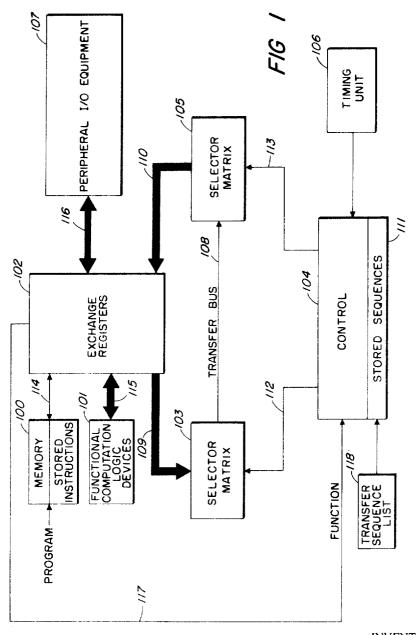

115 Sheets-Sheet 1

INVENTORS

MELVIN L. DOELZ

GEORGE F. GRONDIN

BY

Moody and Phillion

ATTORNEYS

Filed Aug. 26, 1963

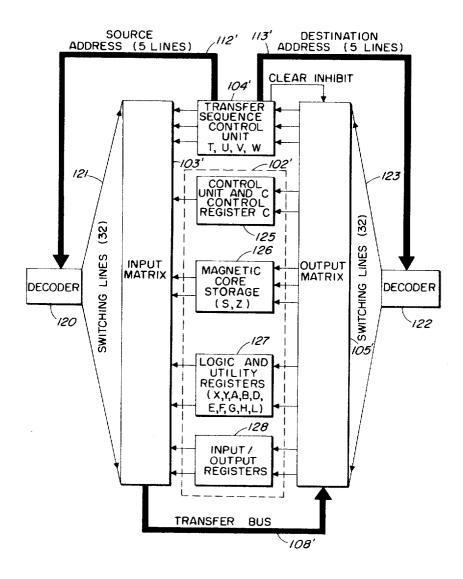

115 Sheets-Sheet 2

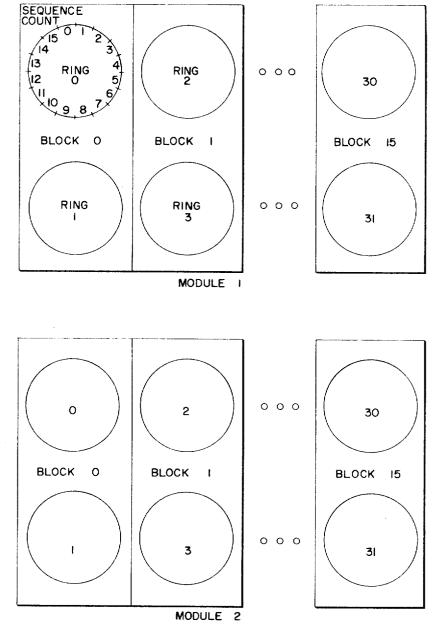

FIG 2

INVENTORS

MELVIN L. DOELZ

GEORGE F. GRONDIN

Moodyand Phillion

ATTORNEYS

Filed Aug. 26, 1963

115 Sheets-Sheet 3

|        | ****          |       |          |                               | *****    |             |

|--------|---------------|-------|----------|-------------------------------|----------|-------------|

| 1 1015 |               | OCTAL | MNE-     | 103" NA                       | TRIX C   | OCTAL       |

| LINE   | . 17          | חח-   | MONIC    | C23=O                         | MONIC    | IAD- I      |

| FUNC-  | MNE-<br>MONIC | DRÉSS |          | C23-1                         | PI2      | DRESS<br>36 |

| RI-8   | B8            | 36    | PI2      | C33=1                         | ' '-     |             |

|        |               |       |          | C23=U                         | PII      | 34          |

| D. 0   | 200           | 7.4   | <b>5</b> | C23=0 PIIB 1/0 PIIA 1/0 C23=1 | FII      | 34          |

| RI-9   | B9            | 34    | PH       | C23=1 C23=0                   |          |             |

|        |               |       |          | C23=0 PIOB 1/0 PIOA 1/0 C23=1 | PIO      | 32          |

| RI-12  | BI2           | 32    | PIO      | C23=1 C23=0                   |          |             |

|        |               |       |          | C23=0 C23=1                   | P9       | 30          |

| RI-13  | B13           | 30    | Р9       | C33=1 P9B 1/0P P9A 1/0P       |          |             |

|        |               |       |          | U23-U                         |          |             |

| R1-14  | BI4           | 26    | no       | C23=0 P8B I/O P8A I/O C23=1   | P8       | 26          |

| K 1-14 | D14           | 20    | P8       | C23=1 C23=0                   | <u> </u> |             |

|        |               |       |          | C23=0 P7B 1/0 P7A 1/0 C23=1   | P7       | 24          |

| R I-15 | B15           | 24    | P7       | C23=1 P7B 1/0 P7A 1/0 C23=0   |          |             |

|        |               |       |          | 007.4                         | P6       | 22          |

| RIIO   | BIO           | 22    | Р6       | C23=0 P6B I/O P6A I/O C23=1   |          |             |

|        | 5.0           |       | 10       | C23=0                         |          |             |

|        |               |       |          | C23=0 P5B I/O P5A I/O C23=1   | P5       | 20          |

| RI-16  | BI6           | 20    | P5       | C23=1                         |          |             |

| RI-7   | B7            | 17    | P4       | ← P4 I/0 ←                    | P4       | 17          |

| RI-5   | B5            | 25    | Р3       | P3 1/0                        | P3       | 25          |

| RI-11  | BH            | 21    | P2       | P2 1/0                        | P2       | 21          |

| RI 6   | В6            | 33    | PI       | PI 1/0                        | PI       | 33          |

|        |               | _     |          |                               |          |             |

| RI 4   | B4            | 23    | PO       | PO 1/0                        | PO       | 23          |

| RI-2   | B2            | 31    | ΕI       | FI AC C25 XMIT                | Εı       | 31          |

|        |               |       |          | DATA BUS                      |          |             |

| RI-3   | 83            | 27    | E2       | E2 TSSU C26(B)                | E2       | 27          |

| DI-I   | Di            | 05    | DI       | 1-16 DI PARITY 1-16 (L/R)1-16 | DI       | 02          |

| D2-1   | D2            | 07    | D2       | 143                           | , D,     | 02          |

| C-21   | -D2           | 06    | - D2     | H6 D2 COMPLEMENT              | D2       | 07          |

| D31    | D3            | 13    | D3       | 1-16 D3 FIX WIRE (L/R)        | D3       | 13          |

|        |               |       |          | 143                           |          |             |

| D4-I   | D4            | 15    | D4       | D4 UTILITY L/R                | D4       | 15          |

| RI-I   | Ві            | 16    | D5       | D5 UTILITY                    | D5       | 05          |

|        |               |       |          | ·                             |          |             |

| 1      |               |       |          | FIG 3                         |          |             |

|        |               |       |          | 110 0                         | INVE     | NTORS       |

INVENTORS MELVIN L. DOELZ GEORGE F. GRONDIN

Moody and Phillis

Filed Aug. 26, 1963

115 Sheets-Sheet 4

|   |                   | Mug. X        | .0, 10         | 00            | 115 Sueers-Sneer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4  |

|---|-------------------|---------------|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |                   |               |                |               | 144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1  |

|   | У                 | RI            | 03             | Ri            | LOGIC(L/R) RI 03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ı  |

|   | or                | -RI           | OI             | -RI           | I-I6 I-I6 RI ROTATE I-I6 -RI 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ١  |

|   | R2-1              | R2            | 11             | R2            | R2 ROTATE R2 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | C-20              | С             | 14             | С             | 142 25,24 1,2,3A 02.03,23 3B,3C 01,19, 4A,4B 01,19, 4A,4B 02,19, 4A,4B 02,75-16,4C,5-16,10 01,19, 4A,4B 02,75-16,4C,5-16,10 01,19, 4A,4B 02,75-16,4C,5-16,10 01,19, 4A,4B 02,75-16,4C,5-16,10 01,19, 4A,4B 02,75-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C,5-16,4C |    |

|   |                   |               |                |               | 123A3B3C4A7 -C 16<br>124AC5-1213141516                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1  |

|   |                   |               | i              | 154           | S MCS H6 C2=0 S 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|   | Z-1<br>Z-9<br>Z-1 | ZH<br>ZH<br>Z | 12             | ZH            | SIG=1 9-16 Z MCS DATA 9-16 SIG=1 ZH 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | 2-1               | 2             | 10             | Z             | 1-16 1-16 1-16 Z 10<br>153 147 A2 ADDEND 1-16 1-16 A2 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|   | AI-I              | ΑI            | 35             | ΔI            | 1-16 148 A3 AUGEND 1-16 1-16 A3 OI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|   | L-1               | L             | 37             | L             | "I" L (/R) 7-10 13C-16C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   | —<br>В            | V<br>VL<br>VR | 00<br>02<br>04 | V<br>VL<br>VR | 21-30 U TSCU ADDRESS 2 U M 04 16,7-16,31-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| • |                   |               |                |               | =RI-II-RI-I2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _! |

|   |                   | L             |                |               | TRANSFER LINK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|   |                   |               |                |               | 108"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|   |                   |               |                |               | FIG 3a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   |                   |               |                |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |                   |               |                | 1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

FIG 3a FIG 4

INVENTORS MELVIN L. DOELZ GEORGE F. GRONDIN

Moody and Phillips ATTORNEYS

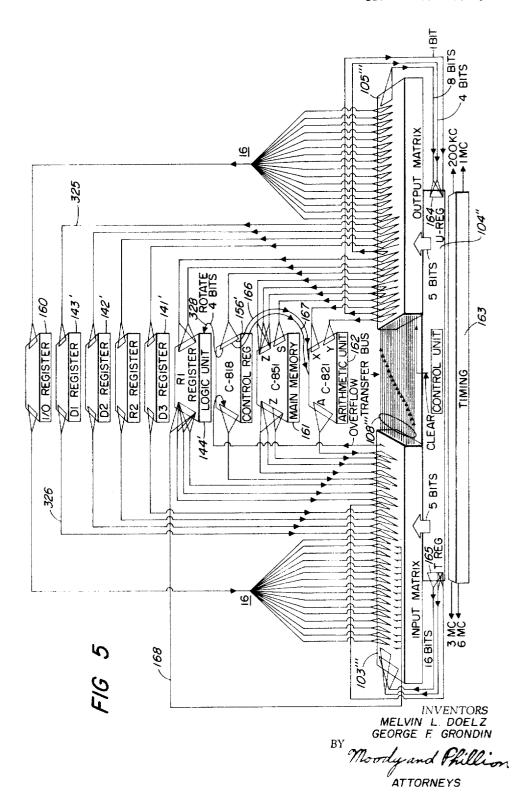

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

Filed Aug. 26, 1963

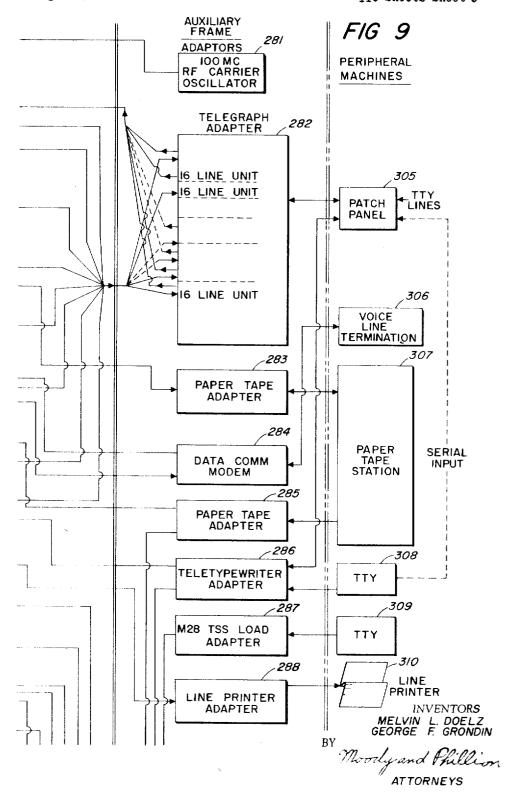

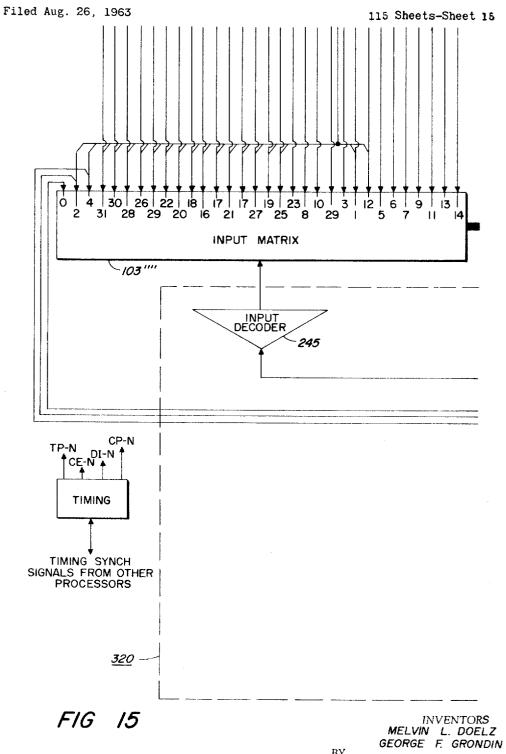

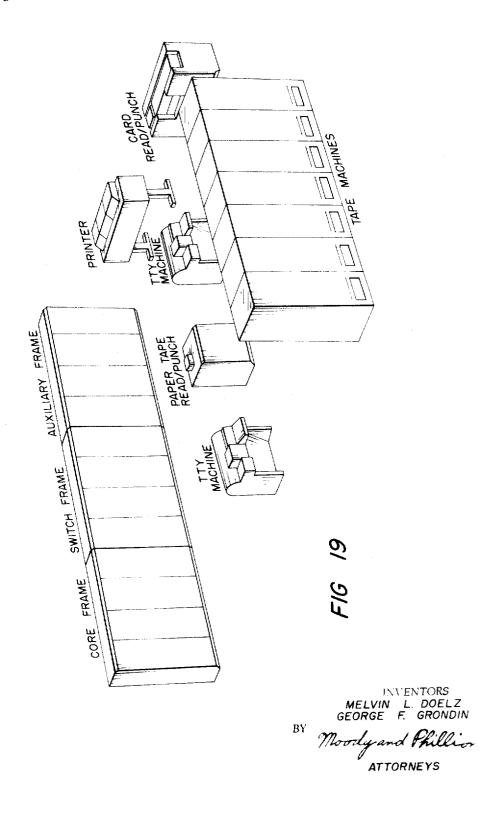

Filed Aug. 26, 1963 115 Sheets-Sheet 14 299 DISK FILE 3// 12 24 DISK FILE ADAPTER 312 *300* CARD READ/ PUNCH ADAPTER CARD READ PUNCH lookc" REAL TIME CLOCK 302 3/3 MAGNETIC TAPE 000 10 2 **ADAPTER** 303 **CROSS - BAR** SWITCH TELEPHONE LINES 280 REFERENCE OSCILLATOR 5.34 KC 304 CROSS - BAR SWITCH ADAPTER PERIPHERAL MACHINES **AUXILIARY** FRAME ADAPTERS FIG 14

INVENTORS

MELVIN L. DOELZ

GEORGE F. GRONDIN

BY Moodyand Phillion

**ATTORNEYS**

BY Moody and Phillis

ATTORNEYS

Jan. 24, 1967

## M. L. DOELZ ETAL

3,300,764

DATA PROCESSOR

Filed Aug. 26, 1963

115 Sheets-Sheet 16

# FIG 16

## TRANSFER SEQUENCE CONTROL

INVENTORS

MELVIN L. DOELZ

GEORGE F. GRONDIN

Morrhand Phillip

ATTORNEYS

FIG 17

INVENTORS MELVIN L. DOELZ GEORGE F. GRONDIN

BY

Moody and Phillion ATTORNEYS

Filed Aug. 26, 1963

| 19          | n l         | eđ<br>! | Aug. 2                                                                                | 6, 196                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33<br>!                                       |                                                         | 115 Sheets-Sheet 20                              |

|-------------|-------------|---------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------|--------------------------------------------------|

|             | 100         | 6       | 252<br>252<br>253<br>545<br>545<br>545<br>545<br>545<br>545<br>545<br>545<br>545<br>5 | -24<br>-25<br>-26<br>-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |                                                         |                                                  |

| - 14        | MC          | 2       |                                                                                       | ネネネネ<br>-ળw4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               | ⊃⊃⊃⊃<br>~&èō                                            |                                                  |

|             | 2-00        | RO-2    | 5000<br>6000<br>6450<br>6450                                                          | ර්රීර්රී<br>ර්රීර්රීර්<br>රුත්රේර්                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | READOUT INDICATOR<br>LIGHTS                   |                                                         |                                                  |

| !!          | 3           | 9       | - <u>111</u>                                                                          | <del>~</del> <del>°</del> - <del>°</del> <del>°</del> - <del>°</del> - <del>°</del> - <del>°</del> <del>°</del> - <del>°</del> - <del>°</del> <del>°</del> - <del>°</del> |                                               |                                                         |                                                  |

| - 1         | - OO        | -       | <u> </u>                                                                              | 94-86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                               |                                                         |                                                  |