Monochrome and RGB Graphics Display Board

0

-03

0

dh.

0

劔

0 0

A493

V//ASYN™

0

\$20.00

## CONTENTS

| ABOUT THE PC VIDEO BOARD 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HARDWARE SECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Attaching Devices and Cables to the PC Video Board2Choosing a Display Monitor2-4Choosing a Keyboard4Choosing a Light Pen4Connecting Cables to the PC Video Board5-7Video Display Interface Memory Addressing8-9Video Display Interface Memory Mapping9-11Alphanumeric Display Modes:(80 x 25h High Resolution)(40 w x 25h Low Resolution)10Line Drawing and Other Character Graphic Display Mode12-13Medium Resolution (640 w x 200h) Graphics Display Mode13-15Low Resolution (160w x 100h) Graphics Display Mode15Available Display Colors15-16Observed Color Distortion and Display Monitor Adjustment16Video Display Interface Port Addressing17Video Display Interface Port Mapping17-22Interrupts22-23 |

| SOFTWARE SECTION - CODE EXAMPLES 24-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Common Equates and Data Storage Variables24-26Keyboard/Light Pen Status and Data Input Routines26Keyboard/Light Pen Initialization Routine26Keyboard/Light Pen Data Input Interrupt Routine27Keyboard/Light Pen Data Available Status27Keyboard Coded Data/Light Pen Position Input Routines27Light Pen Position data and Status Input Routines27-28Keyboard Scan Code Data Input and Translation Routine28-34Video Display Data Output Routines35-40                                                                                                                                                                                                                                                        |

| THEORY OF OPERATION 41-96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

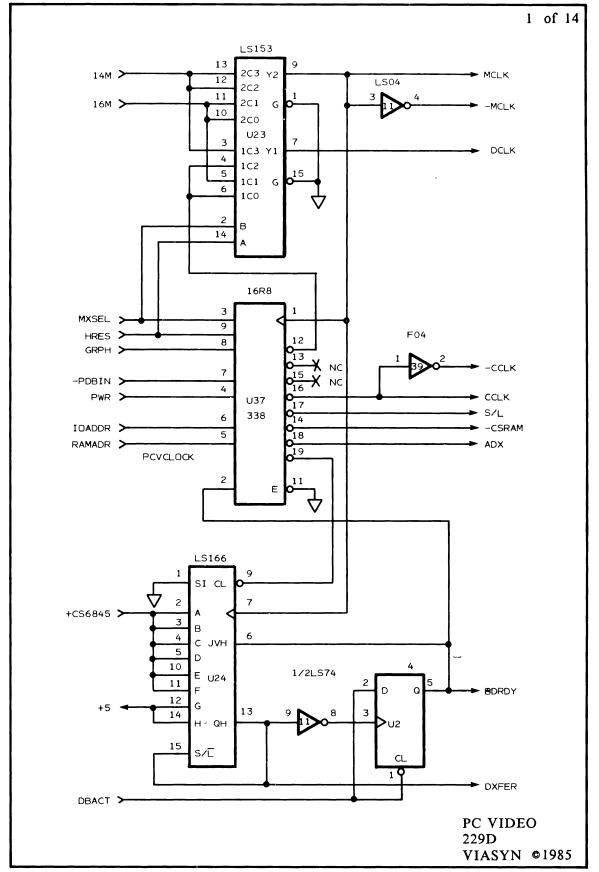

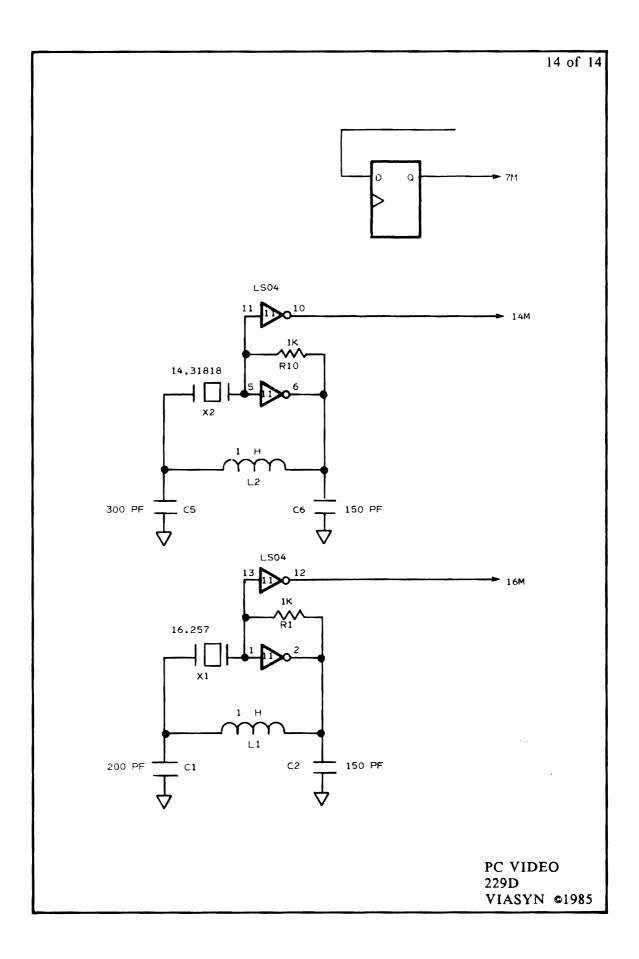

| Master Clock and Display Mode Selection41-42Character Clock Cycle Selection and Timing42-43Design Constraints Affecting the Character Clock Cycle43-44Character Clock Cycle Function Overview44-45State Machine Registers - Counter/Sequencer Logic45-46State Machine Registers - Data Transfer Control Logic46Raster Character Dot Transfer Phase47Host Processor Requested Internal Data Transfer Phase47-49Interaction Effect Between Adjacent Data Transfer Phases49-50IEEE 696/S-100 Bus Interface Logic50                                                                                                                                                                                              |

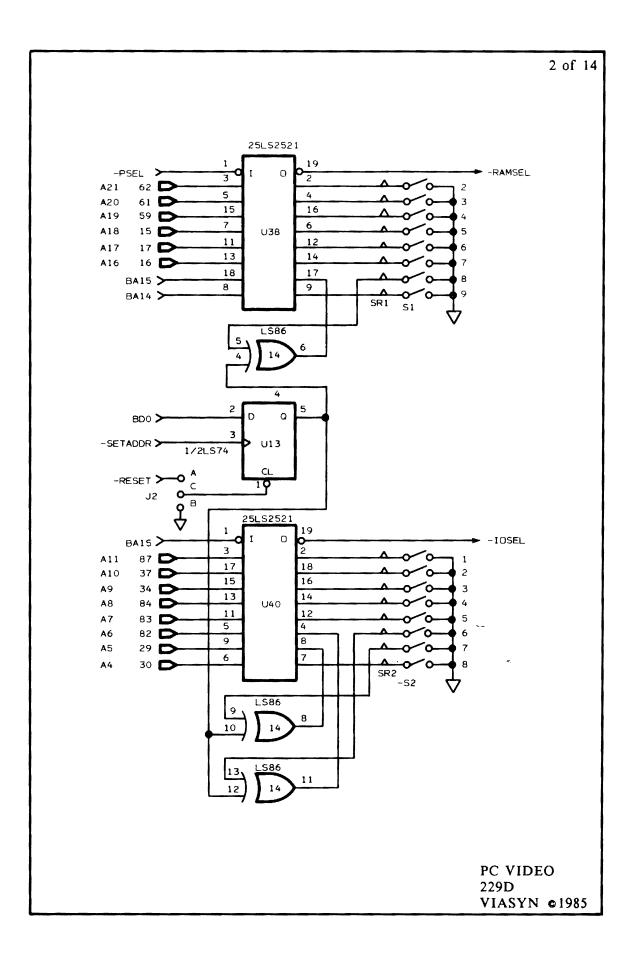

| Bus Address Decoder Logic 50-51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

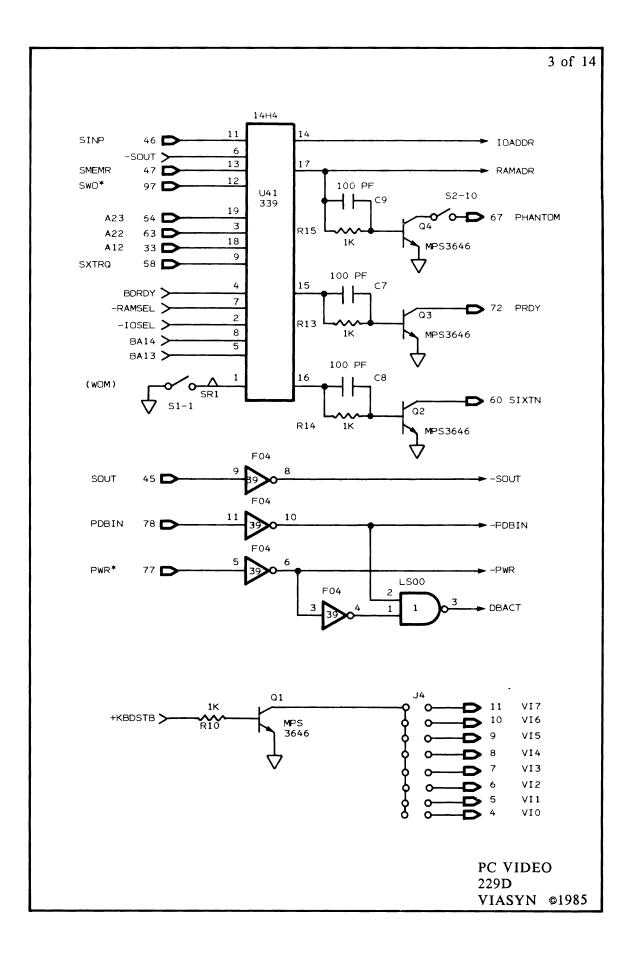

| Automatic Wait State Generation                                | 51-52  |

|----------------------------------------------------------------|--------|

| 16-bit Wide Data Transfer Acknowledge Logic                    | 52     |

| Write Only Memory (WOM) Mode Control Logic                     | 52-53  |

| S-100 Bus to Local Data Bus Buffer and Control Logic           | 53     |

| Memory Select Decoder and Data Bus Buffer Control Logic        | 54     |

| Local General Purpose Data Bus Functional Elements             |        |

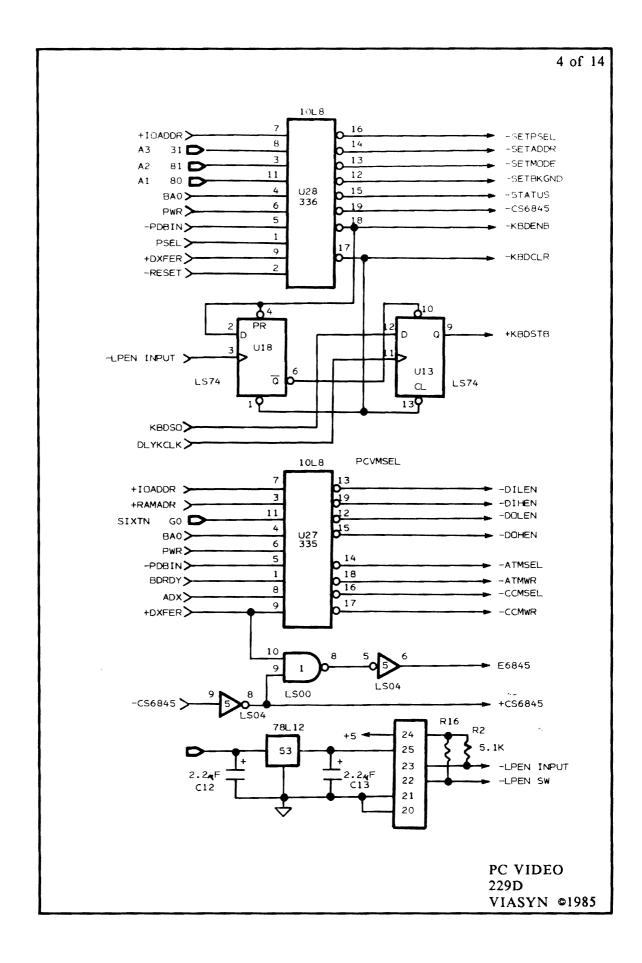

| Input/Output Port Select Decoder and Data Buffer Control       | 56     |

| CRT Controller and Video Display Raster Timing Logic           |        |

| CRT Controller I/O Port Interface Timing and Control Logic.    | 58     |

| CRT Controller Synchronization Interface and Timing            | 59-60  |

| CRT Controller Synchronization Status Logic                    |        |

| Display Memory Data Buses and Raster Character Latch Logic . 6 |        |

| Character Memory Data Bus and Related Logic                    | 51-62  |

| Attribute Memory Data Bus and Related Logic                    | 52-63  |

| Video Dot Multiplexing and Output Drivers                      | 53     |

| Attribute Decoder Logic for Alphanumeric Modes                 | 53-64  |

| Video Dot Multiplexer and Decoder Logic                        | 55-66  |

| Background Color Register and Graphics Color Logic             | 56     |

| TTL Level Video Output Signal and Driver                       | 57     |

| Composite Video Output Signal Level                            | 58     |

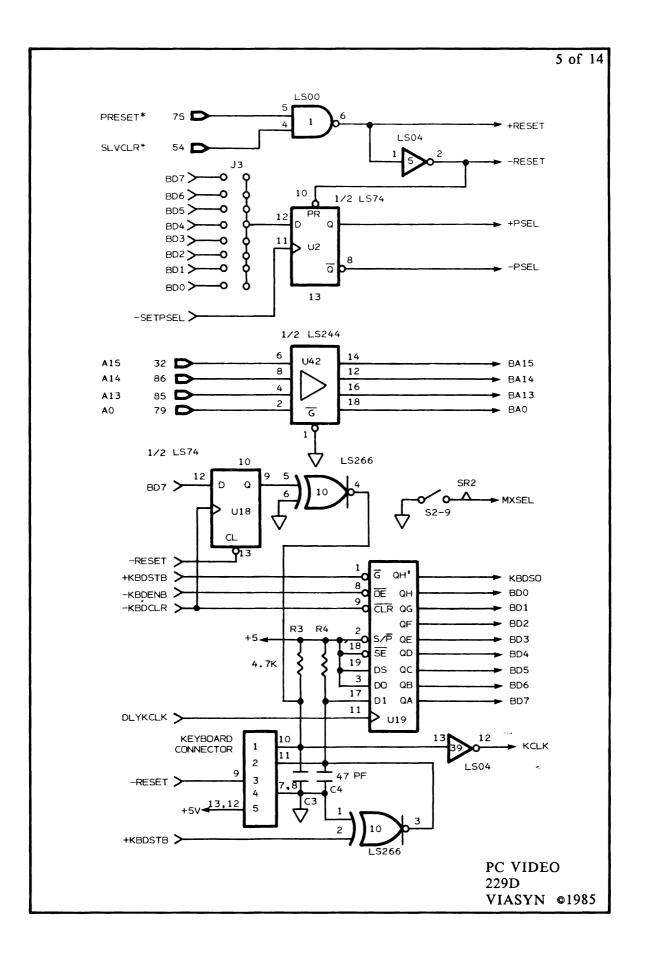

| Keyboard and Light Pen Input                                   | 58-70  |

| Timing Diagrams                                                | 71-73  |

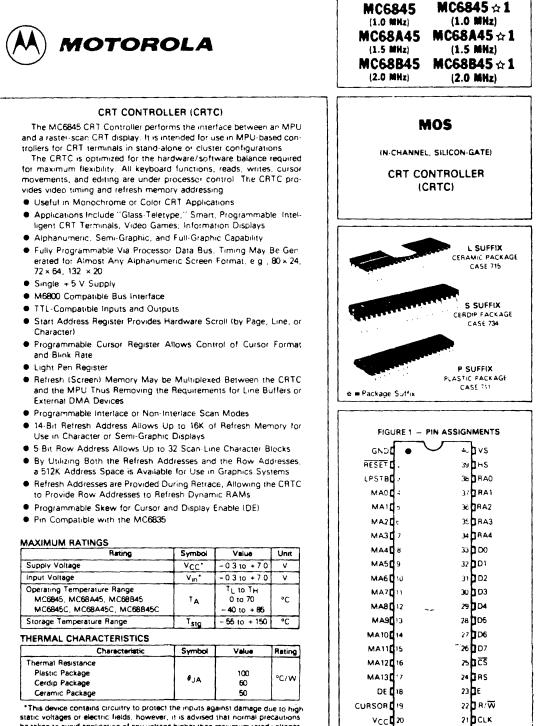

| 6845 CRT Controller Data Sheet                                 | 74-96  |

|                                                                |        |

|                                                                |        |

| HARDWARE DESCRIPTION                                           | 97-113 |

|                                                                |        |

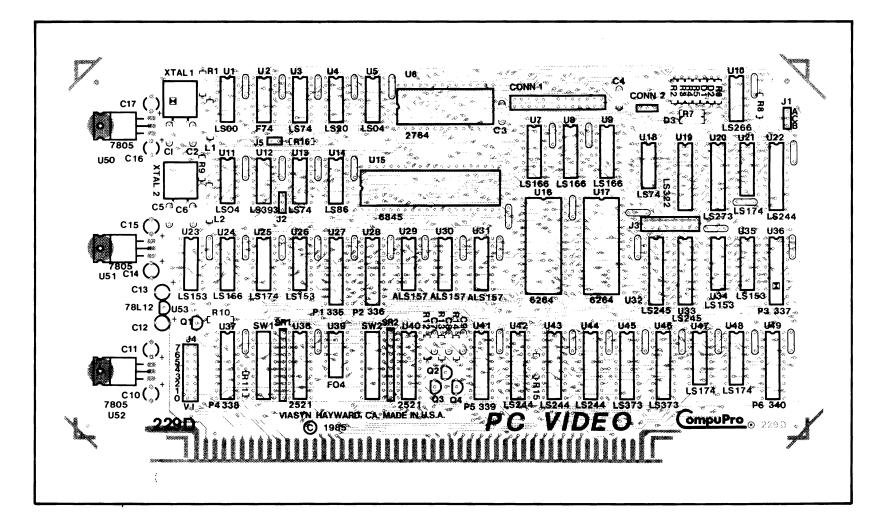

| Logic Diagram                                                  |        |

| Parts List                                                     |        |

| Component Layout                                               | 113    |

# LIST OF TABLES

| Table | 1:  | Display Monitor Switch Settings 2                   |

|-------|-----|-----------------------------------------------------|

| Table | 2:  | PC Video Main Output Connector                      |

| Table | 3:  | Switch Settings for Memory Addressing               |

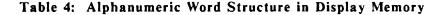

| Table | 4:  | Alphanumeric Word Structure in Display Memory 10    |

| Table | 5:  | Display Character Representations 11-12             |

| Table | 6:  | 640w and 320w x 200h Graphics Memory Map 13         |

| Table | 7:  | 320w x 200h Graphics Mode Pixel Structure           |

| Table | 8:  | 320w x 200h Graphics Mode Color Palettes            |

| Table | 9:  | 160w x 100h Graphics Character Raster 15            |

| Table | 10: | The 16 Possible PC Video Colors Generated           |

| Table | 11: | Input/Output Port Address Switch Settings 17        |

| Table | 12: | Relative Port Address Functions 17                  |

| Table | 13: | Bank Select Jumper Block, J3 18                     |

| Table |     | I/O Port and Address Values for IBM Adapters 18     |

| Table | 15: | 6845 CRT Controller Register Functions              |

| Table | 16: | Relative I/O Port #8 Control Bit Functions          |

| Table | 17: | Useful Master Display Mode Control Values           |

| Table | 18: | Relative I/O Port #9 Control Bit Functions          |

| Table | 19: | Relative I/O Port #10 Status Bit Functions          |

| Table |     | Vector Interrupt Jumper Block, J4                   |

| Table |     | Master Display Modes 42                             |

| Table | 22: | Character Clock Cycle Selection Chart               |

| Table | 23: | State Machine Data Transfer Signals                 |

| Table | 24: | Local and Host Data Bus Interconnection Elements 54 |

| Table |     | Memory Select Decoder PAL Output Signals            |

| Table |     | General Purpose Data Bus BD0-BD7 Connections 56     |

| Table |     | Input/Output Port Control Strobes                   |

| Table |     |                                                     |

|       |     | Character Byte Data Bus CC0-CC7 Connections61       |

| Table |     |                                                     |

| Table |     |                                                     |

| Table |     | -                                                   |

| Table |     | 6                                                   |

| Table |     | · · ·                                               |

| Table | 35: | Composite Video Output Signal Levels                |

## ABOUT THE PC VIDEO BOARD

VIASYN's PC Video board is a high speed, bit-mapped, monochrome and RGB graphics display board. The PC Video interface operates with the IBM<sup>®</sup>-PC compatibility module included in CompuPro's Concurrent DOS<sup>m</sup> 8-16<sup>m</sup> operating system, as well as with Digital Research's GSX graphics interface software (included with Concurrent DOS 8-16).

The PC Video board has a monochrome as well as color display mode. A keyboard and light pen may also be attached.

The PC Video board meets all IEEE 696/S-100 bus specifications and includes the following features:

- \* 16 Kbytes of static CMOS RAM

- \* 24 address bits for memory, 16 address bits for I/O ports

- \* Automatic wait state generation

- \* Programmable 6845 video display controller with switch-set master mode

- \* Up to 8 boards can be accessed independently with unique addresses

#### HARDWARE SECTION

This section begins with a discussion of the types of display monitors, keyboards, and light pens that may be attached to the PC Video Graphics interface board. The choice of which display monitor to use should be a careful one as it will determine how to set the primary configuration switches and jumpers. This primary configuration will also select the permissible Master Display Modes. The Hardware Section is designed to be read completely, from start to finish, before any unusual installation or attempts at debugging.

## ATTACHING DEVICES AND CABLES TO THE PC VIDEO BOARD

#### Choosing a Display Monitor

The PC Video graphics interface can operate with three different types of display monitors. Two of these, the Color and Monochrome displays, have very specific interface characteristics. An attempt to attach a display monitor, which does not conform to these characteristics, may cause problems beyond which VIASYN is normally able to support. In particular, NOT ALL RGB type monitors will work with this interface board.

Display monitors which may work correctly are "IBM-PC compatible." Check your monitor to see if the manufacturer states that it is IBM-PC compatible. This means that it has a 9 pin "D type" subminiature male connector to plug into the back of a computer. If the cable is of some other type, the monitor is probably not going to work in conjunction with the PC Video interface. If it is a Color monitor, and more than one display type is supported by the monitor, then it is essential that it be connected or switch selected to the RGB-I (Red, Green, Blue type #1) display configuration. Even if a particular monitor meets all of these qualifications, it still does not guarantee that the display monitor will operate in an entirely correct manner. To help remove any ambiguities in the selection process to obtain a fully functional display monitor, VIASYN has tested and found the models listed below to operate with 100% compatibility.

## Table 1: Display Monitor Switch Settings

#### Recommended Color (RGB) Display Monitors:

1. IBM PC Color/Graphics Display Monitor

2. Zenith Data Systems model ZVM-135

If you are using one of these monitors or compatible ones, use the following switch settings on your PC Video board:

DIP switch S1 paddle #10 set to ON = Normal Vertical Sync DIP switch S2 paddle #9 set to OFF = Color Mode

#### **Recommended Monochrome Display Monitors:**

1. IBM PC Monochrome Display

If you are using this monitor or one compatible, use the following switch settings on your PC Video board:

DIP switch S1 paddle #10 set to <u>OFF</u> = Invert Vertical Sync DIP switch S2 paddle #9 set to <u>ON</u> = Monochrome Mode

DIP switch S1, paddle 10 selects the vertical sync polarity, which is opposite for Color and Monochrome display monitors. If you have a non-IBM monitor, this switch may need to be set the other way to make the screen synchronize its vertical display.

DIP switch S2, paddle 9 selects between the Color and Monochrome Display Monitor Modes by routing the master timing chain signals and selecting the correct portion of the character generator PROM. Once selected, ONLY the associated Color or Monochrome Master Display Modes may be programmed successfully into the board. If Color Mode is chosen, none of the Monochrome Display Modes will produce anything useful, and if Monochrome Mode is chosen, none of the Color Display Modes produce anything useful. A major difference between the CompuPro PC Video Graphics interface and the IBM Monochrome Adaptor is that the PC Video board will support either high or medium resolution graphics (similar to the IBM Color Graphics Adaptor) on a monochrome monitor. The IBM Monochrome Adaptor will not support either graphics mode.

Jumper J1 is an adjustment for the horizontal sync signal output to the display monitor. Changing this jumper from A-C to B-C will cause the data displayed on screen to move one character to the left. This adjustment exists to help set up various monitors to display default IBM-PC initialization sequences with the display data centered on the screen. If you have any difficulty with the position of the data image on the screen, first check the monitor alignment, but if necessary the horizontal position is readily adjusted by altering the values of certain CRT controller registers through software. If the shunt at jumper J1 is removed, there will be no horizontal sync output and the screen data becomes scrambled.

Jumper J1: A-C selects normal horizontal sync signal B-C selects delayed horizontal sync signal

The third type of display monitor that may be used with your PC Video board is commonly connected to the PC Video interface via a single coaxial cable. The signal generated by the board and transmitted through the cable is RS-170 composite video compatible. The interface produces this signal on a second connector, independently of the data output on the 9 pin TTL level connector. The interface board produces the RS-170 signal at a 1 Volt peak-peak level into a 75 ohm load. This is the normal signal level for most composite video display monitors. Note that the composite video signal is **Black and White** only. This means that no color information is encoded by the interface. There is a wide variety of "off the shelf" display monitors that will accept and operate correctly using this output signal.

Composite video type display monitors will usually have raster timing similar to the Color Mode, particularly when the interface has been programmed to match the standard IBM-PC display modes. DIP switch S2, paddle 9 should probably be set to the <u>ON</u> position. If you wish to use the PC Video interface with nonstandard display modes or programming, then set the switch according to whichever master frequency (14.31318 or 16.257 MHz), and character generator is appropriate for your monitor and application. Jumper J1 and DIP switch S1, paddle 10 have no effect on the composite video output signal.

**NOTE:** It is possible to connect an RF modulator to the RGB output lines to generate composite color video. However, VIASYN does not support customized interface modules or connections.

#### Choosing a Keyboard

Nearly any keyboard which is IBM-PC plug compatible is also compatible with the PC Video interface board. The only restriction is that the keyboard draw no more that 0.5 amperes at 5 Volts from the interface board. If more current is needed, connect the keyboard to an external 5 Volt power supply.

#### Choosing a Light Pen

The light pen input cable connection provided at the top of the PC Video interface board has several possible interconnect configurations. In addition to ground, +5 Volts and +12 Volts power supply outputs which may be used to power the light pen, the light pen section of the connector has two LS-TTL level inputs. One of these LS-TTL inputs responds by generating a data available status signal for polled applications or an interrupt and is positive edge triggered. The other input is passed directly to a status port without latching or conditioning.

If you are considering using a light pen as an important factor in your system configuration, please be aware that it will not operate correctly with a "high persistence" display monitor. The IBM Monochrome Display Monitor has just such a high persistence screen and is incompatible with the use of a light pen. Most color display monitors do not have high persistence screens. Check the documentation that came with your monitor to determine which type of screen your monitor has.

#### Connecting Cables to the PC Video Board

The output from the PC Video board is derived from two connectors at the upper right hand side of the board. One of these is a 3 pin connector for Black and White composite video RS-170 output. Pin #2, the middle connection, is connected as the signal and pins #1 and #3 are connected to ground. This output should be connected via coaxial "RG" type cable, and may be of any length so long as the opposite end is terminated into 75 ohms.

The other input/output connector may have one of two physical cable configurations, depending on the intended use of the PC Video board. If only the RGB TTL output to either a Monochrome or Color IBM type monitor is needed, use only the DB-9 female connector at the rear of the box. It may be connected by using ribbon cable to a 10 pin header. This header connector should be attached to the left hand side of the PC Video main output connector to cover exactly ten pins.

If both a monitor and a keyboard need to be attached, use CompuPro cable #36 which has a 26 pin header for the PC Video board output connector. This cable splits in half, with the left half becoming a DB-9 female connector for TTL video output. The right half has signals for both the Light Pen and Keyboard inputs. Only the Keyboard signals are connected for cable #36, and terminate in a DIN-5 female connector, the same as used by IBM type keyboards. You may obtain keyboard extension cables from any computer supply store.

To use a light pen with the PC Video board, at present it is necessary for you to construct your own internal cable using the pinouts described in the following table:

#### Table 2: PC Video Main Output Connector

## (Top View)

| j     | 14 | 15    | 16   | 17    | 18   | x           | 20          | 21          | 22    | 23                | 24    | 25    | 26              |   |

|-------|----|-------|------|-------|------|-------------|-------------|-------------|-------|-------------------|-------|-------|-----------------|---|

| Pin:  | 1  | 2     | 3    | 4     | 5    | х           | 7           | 8           | 9     | 10                | 11    | 12    | 13              |   |

|       |    |       |      |       |      |             |             |             |       |                   |       |       |                 |   |

| Pin # | С  | onn   | ecto | г:    | Fu   | nct         | ion:        |             |       |                   |       |       |                 |   |

|       |    |       |      |       |      | _           |             | _           |       |                   |       |       |                 |   |

| 1     |    | ideo  |      |       | Sign |             |             |             |       |                   |       |       |                 |   |

| 2     |    | ideo  |      |       | Sign |             | -           |             |       |                   |       |       |                 |   |

| 3     |    | ideo  |      |       | Red  | _           |             |             |       | -                 | -     |       |                 |   |

| 4     |    | ideo  |      |       | Gree | -           | -           |             |       | -                 |       | -     | al              |   |

| 5     | V  | idec  | )    |       | Blue | gu          | n co        | ontr        | olo   | utpu              | t si  | gnal  |                 |   |

| 6     |    |       | nne  |       |      |             |             |             |       |                   |       |       |                 |   |

| 7     | K  | eyb   | oard | l     | Pow  | er/s        | sign        | al g        | roun  | d                 |       |       |                 |   |

| 8     |    |       | oard |       | Pow  |             | •           | -           |       |                   |       |       |                 |   |

| 9     |    |       | oard |       | RES  |             |             |             |       |                   |       |       |                 |   |

| 10    |    | -     | oard |       | KCL  |             |             |             |       |                   |       |       |                 |   |

| 11    | K  | eyb   | oard | I     | KDA  | <b>۱</b> Т/ | <b>4*</b> k | eyb         | oard  | l inp             | outo  | data  | signal          |   |

| 12    | K  | cyb   | oard | I     | Pow  | er s        | supp        | oly, ·      | +5 V  | olts              |       |       |                 |   |

| 13    | K  | eyb   | oarc | 1     | Pow  | er s        | supp        | oly,⊸       | +5 V  | olts              | at    | less  | than 0.5 amp    |   |

| 14    | V  | ideo  | )    |       | Inte |             | -           |             |       | -                 |       |       |                 |   |

| 15    | V  | ideo  | )    |       | Blac |             |             |             |       |                   |       |       |                 |   |

| 16    | V  | ideo  | )    |       | Hor  | izor        | ntal        | Syn         | c pu  | ilse              | outp  | out s | ignal           |   |

| 17    | V  | ideo  | 0    |       | Ver  | tica        | I Sy        | nc          | oulse | e ou              | tput  | sig   | nal             |   |

| 18    | Ν  | lo co | onne | ctio  | n    |             |             |             |       |                   |       |       |                 |   |

| 19    | Ν  | lo co | onne | ctio  | n    |             |             |             |       |                   |       |       |                 |   |

| 20    | L  | ight  | Pei  | n     | Pow  | er/s        | sign        | al g        | rour  | ıd                |       |       |                 |   |

| 21    | L  | ight  | Pei  | n     | Pow  | er/s        | sign        | al g        | rour  | ıd                |       |       |                 |   |

| 22    | L  | ight  | Pei  | n     | LPE  | N-5         | SW*         | ligh        | t pe  | n sv              | vitcl | h in  | put signal      |   |

| 23    | L  | ight  | Pei  | n     | LPE  | N-I         | NP          | UT <b>*</b> | ligh  | nt pe             | en p  | ulse  | input signal    |   |

| 24    | L  | ight  | Pei  | n     | Pow  | er s        | supp        | oly, -      | +5 V  | <sup>7</sup> olts | , < ( | 0.5 a | mp inc. keyboar | d |

| 25    |    | -     | Pei  |       |      |             |             |             |       |                   |       |       | s than 0.1 amp  |   |

| 26    | N  | lo c  | onne | ectio | n    |             |             |             |       |                   |       |       | -               |   |

26 No connection

Most IBM type Color or Monochrome monitors come with about 4 feet of cable for connection directly into the rear of the computer. This may be extended by another 4 feet by using a specially constructed extension cable available at most computer supply stores where monitors are sold. The monitor cables should not be extended beyond a single extra 4 foot length (a total of less than 10 feet because an "impedence mismatch" may occur).

The terms "impedence matched" or "impedence mismatched" are used when describing how a cable system carries its signal." If a cable and the devices at both ends are impedence matched, the signal carried between the two devices will not be distorted—as it passes through. This allows the cable to be of any length. This is true for the PC Video RS-170 output, the interconnection cable and most RS-170 compatible monitors, where care has been taken so that all three have been impedence matched to 75 ohms. Since the output needed to drive IBM type monitors is of "TTL signal level" type, it is not matched to any normal "RG type" transmission cable in either the monitor or the PC Video board output. Because of this, the length of cable which is used will affect this impedence mismatch and cause some of the signal to be reflected back from the monitor to the PC Video board. At certain precise lengths of cable (which are dependent on the "characteristic impedence" of the cable and the video clock master frequency), the entire signal will be reflected. Nothing will appear at the monitor even though the PC Video board is functioning perfectly. Unless you are extremely familiar with this phenomena and the methods and calculations needed to correct for it, DO NOT attempt to construct your own extension cable for the display monitor.

•

#### **VIDEO DISPLAY INTERFACE MEMORY ADDRESSING**

The PC Video graphics display interface has a dual port array of static RAM accessed by both the internal CRT controller and the external host processor. Internally, this memory appears as 16-bits by 8K words for display of alphanumeric or graphic data. To the host processor, the array occupies an area of either 16K bytes or 8K words of memory address space, depending on whether byte or word data transfers are performed.

The display memory array is addressed in multiples of 16K bytes by switch selection to determine the matching values of A14 through A21 on the IEEE 696/S-100 bus. Address lines A22 and A23 are decoded in the address selection PAL which is programmed to respond to an address match with both bits equal to zero as the standard release. DIP switch S1, paddles 1 thru 9, are used to select the read/write mode and base address of the display memory on the PC Video interface as shown in the following table:

#### Table 3: Switch Settings for Memory Addressing

"SI" SWITCH POSITION ADDRESS BIT

| 1 | Write Only Memory matrix $A23 = A22 = 0^{\circ}$ | ode, $ON = Read/Write$ ) |

|---|--------------------------------------------------|--------------------------|

| 2 |                                                  |                          |

|   | A20                                              | ON = '0'                 |

|   | A19                                              |                          |

| 5 | A18                                              |                          |

| 6 | A17                                              | OFF = '1'                |

| 7 | A16                                              |                          |

| 8 | A15                                              |                          |

| 9 | A14                                              |                          |

Wait states are automatically generated by the PC Video interface to synchronize access by the host processor with an available data transfer window. These windows occur between successive internal data word transfers timed by the raster display process. There are no switch settings for the number of wait states because the synchronization time is variable. The delay period generated is dependent on the relationship of a bus request occuring with respect to the internal master timing cycle of the PC Video interface, but will be no longer than 850 nanoseconds for the worst case.

NOTE: Most DMA devices cannot directly read or write the RAM on the PC Video board. Due to the wait states inserted by the arbitration circuitry, most nonbuffered DMA devices will overrun while reading or writing to the PC Video RAM.

The interface memory array may also behave as "Write Only Memory" (WOM) for the special case where there is other RAM that must appear in the same address space as the PC Video interface board.

If switch S1, paddle 1 is set to <u>ON</u>, then the PC Video memory will only respond to write operations from the bus. To function correctly, there must be other Read/Write RAM occupying the same address. This memory must also be of "8-16" type to match the response of the PC Video interface board. Write Only Memory mode will run somewhat faster than normal because no wait states are needed for display memory read operations.

To permit the use of more than one PC Video interface addressed at the same base location, the memory array on each board may be enabled or disabled by its bank select register. Board selection is performed via an output to relative port #0 which sets the state of each board's bank select register. When the register value is zero, the individual PC Video interface is disabled and will not respond to any data transfers in the memory address space. The bank select register function is given in detail in the "Video Display Interface Port Mapping" section of this manual.

When more than one PC Video interface is addressed in the same memory address space AND there is also additional RAM addressed in this space as well, then the phantom memory control should be enabled. This is done by setting DIP switch S2, paddle #10 to the ON position. In all other cases this switch should be in the Although this and all other current memory OFF position. products from VIASYN are designed to run with processor speeds up to 12 MHz, there is a potential problem in using the phantom line at speeds exceeding 6 MHz due to its "open collector" signal This problem may exist particularly if all boards in a type. system adhere precisely to the IEEE 696/S-100 standard. The standard is the source of the potential problem because it specifies termination sourcing for speeds up to 6 MHz only. To operate at higher speeds, the phantom line needs a greater amount of pull-up than is specified in the bus standard to overcome its "RC" delay. If you do not absolutely need to use memory phantoming, don't activate it.

## VIDEO DISPLAY INTERFACE MEMORY MAPPING

## Alphanumeric Display Modes: (80w x 25h High Resolution) (40w x 25h Low Resolution)

Both 80x25 and 40x25 alphanumeric display modes have two bytes in a word structure associated with each character displayed. The low order byte of each character word is the representation yalue for the character itself, which is usually its ASCII code value. The representation value addresses an area of PROM programmed with the correct bit representations for each scan line to display that character. If the PC Video interface is configured for color monitor output, the character generation PROM produces 7x7 dot characters with single line descenders, which are displayed within an 8x8 dot box. If configured for monochrome monitor output, then the character generation PROM produces 7x9 dot characters with 2 line descenders, which are displayed in a 9x14 box. The monochrome monitor does not support display in 40x25 resolution mode.

The high order byte of a character word contains the control attributes of that character, which differs between color and monochrome modes. For color displays, the attribute byte affects the foreground and background colors and the blink/intensity mode. For monochrome mode the attribute byte affects the reverse video, blink/intensity and underlining modes. The relative locations within the display memory array and internal structure of alphanumeric character words are listed in the following table:

Starting at the display memory base address, the first character is displayed in the upper left corner of the screen. Each sequential character word in memory is displayed to the right of the previous one, until the rightmost possible position of a screen line (column #80) is reached. The next character word then appears as the first character on the left of the next line downward. Mapping of the display memory to the screen positions has linear one to one position correspondence with no gaps. This means that the controller will display only the first 2000 (80x25) or 1000 (40x25) character word locations starting from the base address. Additional pages of memory may be displayed by altering the "start address" programmed in the 6845 CRT controller. This programmed value determines the base address of the upper left corner character in the display memory. The start address does not affect the number of lines or columns displayed, only the locations in the display memory that will appear on screen. By changing this value in the CRT controller, it is possible to display up to 4 different 80x25 screens without altering the display memory array. Refer to the 6845 CRT controller chip data specifications in the "Theory of Operation" section of this manual for more detailed information.

#### Line Drawing and Other Character Graphic Displays

Halfway between alphanumeric and true graphics display modes is the realm of "line drawing" graphics. In both color and monochrome character PROMs, there are 40 alphanumeric representations which display combinations of various single and double line segments. Only horizontal and vertical line segments are available. These segments extend to the edges of the character box, producing large unbroken structures when combined on screen. The character generator PROM on the PC Video graphics board will display all of the representations shown in the following table:

#### Table 5: Display Character Representations

Lower Half of Character Generator PROM (MONOCHROME Mode Display Representations)

Upper Half of Character Generator PROM (COLOR Mode Display Representations)

#### High Resolution (640w x 200h) Graphics Display Mode

In true graphics modes, the display memory map is quite different from the alphanumeric modes explained above. Due to logic which routes the CRT controller scan addresses in a different manner from alphanumeric display modes, the memory map splits into 2 blocks of equal size. The graphic display logic will obtain data from alternating memory blocks depending on whether the output is appearing on an even or odd numbered line. The first scan line displayed, #0, and all other even numbered lines, come from the area of the block located at the true base or lower half of display memory. The second scan line displayed, #1, and all other odd numbered lines, are located in the block at the true base plus 8K bytes (2000 hexadecimal), which is the upper half of display memory.

Within each scan line, the rule for determining the memory locations that will be displayed is similar to that for alphanumeric modes. Both graphic modes display the same number of words as for 40 column alphanumeric mode on a line by line basis. The difference is that the actual data bits are-displayed rather than a multiple scan line representation from a character generator. The display structure is byte wide, which means that first byte #0, then byte #1, is output from the same word.

Each discrete dot displayed in a graphics mode is called a "pixel," short for "picture element," and is also sometimes referred to as a "pel". For 640 pixel wide graphics, each bit in a byte is a dot, or pixel. These are displayed from the leftmost screen dot as the most significant bit linearly to the right for the least significant bit of each byte. A graphics scan line is completed when 40 words separated into 80 bytes have been displayed. The next scan line, odd numbered, is found at the same base address as the previous even numbered line plus 2000 hexadecimal. When the next even numbered scan line is displayed, its first memory location starts at the byte following the last one displayed on the previous even scan line. If that still seems confusing, a diagram showing the memory locations displayed from the top of the screen downwards is shown below:

#### Table 6: 640w and 320w x 200h Graphics Memory Map

| Upper Left Corner                    | Upper Right Corner |

|--------------------------------------|--------------------|

| Byte Locations Displaye              | ed                 |

| 0, 1, 2, 3,                          |                    |

| 8192,8193,8194,8195,                 |                    |

| 80, 81, 82, 83,                      |                    |

| 8272,8273,8274,8275,                 |                    |

| continues for a total of 200 scan li | nes.               |

## Medium Resolution (320w x 200h) Graphics Display Mode

For 320 pixel wide graphics mode, the pattern of bytes output is the same as for 640 wide, but uses 2 bits per pixel instead of one. Each byte displayed is made up of 4 pixels of 2 bits in the following pattern:

#### Table 7: 320w x 200h Graphics Mode Pixel Structure

| Data Bit:     | D7 | D6   | D5 | D4  | D3 | D2 | Dl | D0 |

|---------------|----|------|----|-----|----|----|----|----|

| Pixel Bit:    | bl | ь0   | bl | b0  | bl | ь0 | bl | ъ0 |

| Pixel Number: | [# | ⊧0 ] | [# | :1] | [# | 2] | [# | 3] |

The pixels are displayed left to right, lowest to highest number on screen as they are shown in the above pattern. Because each pixel is comprised of 2 bits, it is possible to output any one of 4 colors for each display dot. This collection of colors that can be displayed by a graphics mode is called its "palette." The color which is generated by each bit pattern is determined as follows: each pixel bit is connected directly to one of two primary color controls. Pixel bit "b0" drives the color green, and pixel bit "b1" drives the color red.

Two possible color palettes are available. They are dependent upon the state of the third primary color control, blue. Its state is controlled by the palette select register (bit #5 of relative port #9) described in the I/O port map portion of this section. If the 320 pixel black/white control is enabled in the master display mode register (bit #2 of relative port #8), it will override the palette select control, giving a third possible palette, titled "black and white." If enabled, the 320 pixel black/white control gates the color blue to be identical to the color green, which follows the value of the "b0" pixel bit. Thus, if the green pixel bit is a one, or <u>ON</u>, then the color blue is also on for that pixel. The following tables show how the color blue output, and resulting display color are determined for the three different master 320 wide graphics modes.

|                                                                                                  | Table 8: 320               | w x 200h            | Gra   | phics | Mode C    | Color Palettes |

|--------------------------------------------------------------------------------------------------|----------------------------|---------------------|-------|-------|-----------|----------------|

| F                                                                                                | Palette #1: "Co            | lor Mode            | e" wi | th Pa | lette Se  | lect = '0'     |

|                                                                                                  | Port #8                    | Port #9             |       |       |           |                |

|                                                                                                  | B/W Mode                   | Palette             | bl    | ь0    | Blue      | Pixel Color    |

|                                                                                                  | 0                          | 0                   | 0     | 0     | x         | (Background)   |

|                                                                                                  | 0                          | 0                   | 0     | 1     | 0         | Green          |

|                                                                                                  | 0                          | 0                   | 1     | 0     | 0         | Red            |

|                                                                                                  | 0                          | 0                   | 1     | 1     | 0         | Yellow         |

| J                                                                                                | Palette #2: "Co<br>Port #8 | olor Mod<br>Port #9 | e" wi | th Pa | alette Se | elect = 'l'    |

|                                                                                                  | B/W Mode                   |                     | b1    | ь0    | Blue      | Pixel Color    |

|                                                                                                  | _,                         |                     |       | -•    |           |                |

|                                                                                                  | 0                          | 1                   | 0     | 0     | x         | (Background)   |

|                                                                                                  | 0                          | 1                   | 0     | 1     | 1         | Cyan           |

|                                                                                                  | 0                          | 1                   | 1     | 0     | 1         | Magenta        |

|                                                                                                  | 0                          | 1                   | 1     | 1     | 1         | White          |

| Palette #3: "Black and White Mode"<br>Port #8 Port #9<br>B/W Mode Palette b1 b0 Blue Pixel Color |                            |                     |       |       |           |                |

|                                                                                                  | 1                          | x                   | 0     | 0     | x         | (Background)   |

|                                                                                                  | 1                          | x                   | ŏ     | ĩ     | î         | Cyan           |

|                                                                                                  | i                          | x                   | ĭ     | Ō     | 0         | Red            |

|                                                                                                  | -                          |                     | -     | -     | -         |                |

Table 8: 320w x 200h Graphics Mode Color Palettes

where "x" = any value

х

1

1

1

White

1

The rationale behind calling the third palette "black and white" will not be immediately obvious from its display on a color RGB monitor because it is not the intended output device for this mode. If the individual color control bits are each assigned an equal intensity value and they are summed together algebraically, there will be 4 possible intensity levels for each pixel. The "bl" pixel bit controls only the red output and has an assigned "weight" of '1', while the "b2" pixel bit controls both the green and blue outputs giving it an assigned weight of '2'. The various bit combinations will therefore generate an output having 4 different "gray levels." The various intensities effectively map a color graphics display onto a black and white only display monitor. Although there is no logic on the PC Video interface which directly generates this mutilevel intensity output, it may be obtained by using a few resistors and diodes connected to the RGB output signals.

The "background" color in Table 8 is defined by the outside border color controls (the lowest 4 bits of relative port register #9), and may be any one of 16 possible colors.

#### Low Resolution (160w x 100h) Graphics Display Mode

The lowest resolution graphics mode available (160x100) actually uses a hybrid display memory map combining aspects of both alphanumeric and true graphics modes. There are a total of 200 scan lines displayed in all color display modes which indicates that each pixel in low resolution graphics appears in 2 different scan lines of the monitor. This is effected in the CRT controller by altering the character height register from the normal 8 scan lines per character down to 2 scan lines. То obtain the correct number of scan lines for the total screen, the CRT registers are further modified to display 80 characters by 100 character lines instead of the normal 25. Another special case adjustment of alpha mode is used to divide each character into 2 horizontal pixels. The entire array of 8000 alpha mode character bytes is first initialized with the value ODD hexadecimal, whose display representation is as follows:

#### Table 9: 160w x 100h Graphics Character Raster

| Bits:       | 7 6 5 4 3 2 1 0                                       |         |

|-------------|-------------------------------------------------------|---------|

| Displayed   | 11110000 Scan line #1                                 |         |

| PROM cells: | 1 I I I O O O O Scan line #2                          |         |

|             | 1 1 1 1 0 0 0 0                                       |         |

|             | 1 1 1 1 0 0 0 0                                       |         |

|             | 1 1 1 1 0 0 0 0 Scan lines #3 thru #7                 | are not |

|             | 1 1 1 1 0 0 0 0 displayed for low reso                | lution  |

|             | 1 1 1 1 0 0 0 0 160 x 100 graphics mo                 | de.     |

|             | 11110000                                              |         |

|             | $1 \ 1 \ 1 \ 1 \ 0 \ 0 \ 0 \ 0$ Character Code = $0I$ | ) Dh    |

This fixed array of character bytes is translated by the PROM character generator to display 2 different pixel dots, each representing either the foreground or background colors of the corresponding attribute byte. Finally, the individual display dots are controlled by altering either the foreground (left pixel dot) or background (right pixel dot) color and intensity bits in the corresponding attribute byte. This corresponds to 4 bits per pixel. This mode is highly inefficeint because all even numbered bytes must have a fixed code value. This graphic mode can display 16 colors for either pixel (foreground/background nibbles) which permits full color graphics.

#### Available Display Colors

Throughout this manual, we mention that 16 colors can be displayed by various alphanumeric and graphic modes. To assist you in determining what colors are actually generated and in what manner, the following table shows the 4 video output control signals in all combinations and the associated colors that they produce.

## Table 10: The 16 Possible PC Video Colors Generated

| Intensity | Red | Green | Blue | Color Produced: |

|-----------|-----|-------|------|-----------------|

| 0         | 0   | 0     | 0    | Black           |

| 0         | 0   | 0     | 1    | Dark Blue       |

| 0         | 0   | I     | 0    | Dark Green      |

| 0         | 0   | 1     | 1    | Dark Cyan       |

| 0         | 1   | 0     | 0    | Dark Red        |

| 0         | 1   | 0     | 1    | Dark Magenta    |

| 0         | 1   | 1     | 0    | Brown           |

| 0         | 1   | 1     | 1    | Light Gray      |

| 1         | 0   | 0     | 0    | Dark Gray       |

| 1         | 0   | 0     | 1    | Light Blue      |

| 1         | 0   | 1     | 0    | Light Green     |

| 1         | 0   | 1     | 1    | Light Cyan      |

| 1         | 1   | 0     | 0    | Light Red       |

| 1         | 1   | 0     | 1    | Light Magenta   |

| 1         | 1   | 1     | 0    | Yellow          |

| 1         | 1   | 1     | 1    | White           |

#### **Observed Color Distortion and Display Monitor Adjustment**

The true color appearing on most RGB monitors is dependent on several factors outside the control of the PC Video interface board. The most noticable is the change in color as the "intensity" control on the display is adjusted. You will see that yellow appears as gold, then brown as the intensity is decreased. The characterics of colors generated by pairs of the primary colors may also be different due to alternate phosphors used in monitor manufacture, or if the monitor's internal color intensity balance is incorrectly adjusted or aligned.

The second effect that will alter the observed color is well known to artists and others who often deal with color perception. It is possible to have any colored area perceived differently than the color that would be normally expected. This perception is dependent upon the visual area that a color occupies in relation to other adjacent area sizes and colors. This change in perceived color occurs because the human eye/brain nerve network performs a type of optical integration over the entire picture it It then adjusts its perception of various colors such receives. that the most reasonable picture results. What the eye/brain integrator believes to be reasonable is sometimes radically different from the "absolute" picture. An optical illusion can. for example, change the appearance of an interior color from green to red, when the entire surrounding visual region is altered in both color and intensity, even though the interior color remains physically the same!

## **VIDEO DISPLAY INTERFACE PORT ADDRESSING**

The PC Video graphics display interface uses a block of 16 input/output port addresses for control and status communication with the host processor. These 16 port addresses are bank selectable and switch setable within certain range limits. This address range may be changed only by replacing the associated address select PAL chip. The base address of the first port is switch selectable in multiples of 16, and appears as the middle two nibbles of a 16-bit port address. All 16-bits of any I/O port address are always decoded, and the standard release PAL for this board is programmed with the upper nibble equal to zero. DIP switch S2, paddles 1 thru 8 are used to select the base address of the input/output ports on the PC Video display interface as shown in the following table:

#### Table 11: Input/Output Port Address Switch Settings

| "S2" | Switch Position | <b>Address Bit</b><br>A15 = A14 = A13 = . | A12 = '0' |

|------|-----------------|-------------------------------------------|-----------|

|      |                 | A11<br>A10                                |           |

|      | 3               |                                           | ON = '0'  |

|      | 5               | A7                                        |           |

|      |                 | A6<br>A5                                  | OFF = '1' |

|      | 8               | A4                                        |           |

## **VIDEO DISPLAY INTERFACE PORT MAPPING**

Although the PC Video board will respond to access at all 16 relative port addresses, only 9 of these perform any useful operation. These 9 ports will be referred to in this manual as relative ports 0 - 12 as shown below:

## Table 12: Relative Port Address Functions

| Relative Direction: |       | Direction: | Function:                                 |

|---------------------|-------|------------|-------------------------------------------|

| Port:               |       |            |                                           |

| 0 (                 | 00h)  | Write      | Bank select register always active        |

| 1 (                 | 01h)  | Write      | Address area select register              |

| 4 (                 | 04h)  | Write      | CRT controller address register           |

| 5 (                 | 05h)  | Write      | CRT controller data register              |

| 5 (                 | 05h)  | Read       | CRT controller data register              |

| 8 (                 | 08h)  | Write      | Master display mode register              |

| 9 (                 | 09h)  | Write      | Background color, palette select register |

| 10 (                | (OAh) | Read       | Video display, keyboard status buffer     |

| 11 (                | (OBh) | Write      | Clear keyboard status, set clock register |

| 12 (                | (OCh) | Write      | Set keyboard / light pen status register  |

| 12 (                | (0Ch) | Read       | Keyboard input data register              |

**NOTE:** All of these I/O ports, except relative port 0, are also conditionally enabled by the on-board bank select register status. See the following bank select register discussion for more details.

#### **Port #0 --** Bank Select Register (write only)

The purpose of this register is to permit as many as eight PC Video interface boards to occupy the same I/O port and memory address spaces. This capability is needed if all displays are to be running IBM-PC compatible software. By utilizing the bank select register, individual interface boards may be enabled at different times for operation in a multi-user environment. If the status of the bank select register is set to '0', the bus interface for all memory and I/O addresses, except the bank select register, is disabled. At reset, all PC Video boards have their bank select register status set to '1', making all of them appear at their selected addresses. The data bit used to control a particular board is selected by placing a shunt on the corresponding bit position of jumper block J3 as shown below:

#### Table 13: Bank Select Jumper Block, J3

| Data Bit:           | D0  | DI | D2 | D3 | D4 | D5 | D6 | <b>D</b> 7 |

|---------------------|-----|----|----|----|----|----|----|------------|

| Bank Select Number: | [1] | [] | [] | [] | [] | () | [] | 0          |

| Jumper Block J3     | 0   | [] | [] | [] | [] | [] | [] | 0          |

#### **Port #1** -- Address Area Select Register (write only)

This register is connected to three of the address select decode bits via exclusive-or gates. It permits limited alteration of the established board address value under software control. The state of the address area select register is controlled by the least significant bit of the byte written to this I/O port. The switch settings affected by this function are memory address bit A15, (S1, paddle 8), and I/O port address bits A5 and A6 (S2, paddles 7 and 6). A system reset will clear this register to zero causing the affected address bits to follow normal switch settings. If the jumper at J2 is placed at B-C instead of A-C, then this register is disabled and PC Video board addressing will always match switch settings.

#### Table 14: I/O Port and Address Values for IBM Adaptors

| Video Interface Type: I | /O Ports  | Display Memory Address         |

|-------------------------|-----------|--------------------------------|

| (                       | Switch 2) | (Switch 1)                     |

|                         | *         | <pre>* = difference bits</pre> |

| IBM Color Adaptor       | 03Dx      | 0B8000 (hexadecimal)           |

| IBM Monochrome Adapte   | or O3Bx   | 0B0000                         |

The purpose of this register is to permit software testing at both of the IBM Color and Monochrome standard address locations without removing the PC Video interface from the system bus. As an example of how this works, set the board memory and I/O port addresses by switches at the standard values (shown in the preceeding table) for the IBM Color Adaptor video interface. If an output to relative port #1 contains a '1' in the least significant bit, then the address area select register will alter the board address select circuitry such that future accesses 'rom the bus are possible only by using the Monochrome Adaptor locations. To return to the Color Adaptor address space, it is necessary only to output a '0' to relative port #1 in the Monochrome Adaptor address space.

Port #4 -- CRT Controller Address Register (write only) and Port #5 -- CRT Controller Data Registers (read and write)

There are two ports that the 6845 CRT controller chip responds to on the PC Video interface board. The one at relative port #4 is write only and is used to select one of 18 internal data registers of the chip. Relative port #5 is both write for register control set-up and read for status sense operations. The following table gives the functions of each of the 6845 CRT controller's internal registers.

#### Table 15: 6845 CRT Controller Register Functions

| Register<br>Number: | Data<br>Direction: | Function:                               | Units:                 |

|---------------------|--------------------|-----------------------------------------|------------------------|

| 0 (00h)             | Write              | Horizontal total                        | Character              |

| 1 (01h)             | Write              | Horizontal displayed                    | Character              |

| 2 (02h)             | Write              | Horizontal sync position                | Character              |

| 3 (03h)             | Write              | Horizontal sync width                   | Character              |

| 4 (04h)             | Write              | Vertical total                          | Char. Row              |

| 5 (05h)             | Write              | Vertical total adjust                   | Scan Line              |

| 6 (06h)             | Write              | Vertical displayed                      | Char. Row              |

| 7 (07h)             | Write              | Vertical sync position                  | Char. Row              |

| 8 (08h)<br>9 (09h)  | Write              | Interlace mode<br>Max scan line address | Scan Line              |

| II (OBh)            |                    | Cursor start<br>Cursor end              | Scan Line<br>Scan Line |

| 12 (0Ch)            |                    | Display start address                   | High Byte              |

| 13 (0Dh)            |                    | Display start address                   | Low Byte               |

| 14 (0Eh)            |                    | Cursor address                          | High Byte              |

| 15 (0Fh)            | Read/Write         | Cursor address                          | Low Byte               |

| 16 (10h)            | Read               | Light pen address                       | High Byte              |

| 17 (11h)            | Read               | Light pen address                       | Low Byte               |

Initialization values for these registers for the common display modes are given in the Software Section of this manual. Further details on the function of individual registers within the 6845 CRT controller chip, along with the reprinted data sheets, are given in the "Theory of Operation" section of this manual.

## **Port #8** -- Master Display Mode Register (write only)

This 6-bit register controls the primary display modes of the PC Video interface board. These signals determine the master timing for display dots and select their signal routing to produce the various possible graphic and alphanumeric display types. The names and bit positions within this mode register are shown in the following table.

#### Table 16: Relative I/O Port #8 Control Bit Functions

## Data Bit: Function:

- 7 None

- 6 None

- 5 Enable character blink/Foreground intensity attribute

- 4 Special mode bit enables 640 X 200 graphics display

- 3 Video display output enable

- 2 Black/White display type for 320 X 200 color graphics

- 1 Graphics/Alphanumeric display mode select

- 0 High/Low resolution master timing mode select

The Master Display Mode control values for both color and monochrome monitors are listed in the following table:

## Table 17: Useful Master Display Mode Control Values

## **Color Display Monitor:**

| Bits: | 5 | 4 | 3 | 2 | 1 | 0 | Function:                 |

|-------|---|---|---|---|---|---|---------------------------|

|       | 1 | 0 | 1 | x | 0 | 0 | 40 x 25 Alphanumeric      |

|       | 1 | 0 | 1 | х | 0 | 1 | 80 x 25 Alphanumeric      |

|       | x | 0 | 1 | 1 | 1 | 0 | 320 x 200 Graphics, B/W   |

|       | x | 0 | 1 | 0 | 1 | 0 | 320 x 200 Graphics, color |

|       | x | 1 | 1 | 1 | 1 | 0 | 640 x 200 Graphics, B/W   |

## Monochrome Display Monitor:

| Bits: | 5   | 4 | 3  | 2   | 1  | 0  | Function:               |

|-------|-----|---|----|-----|----|----|-------------------------|

|       | 1   | 0 | 1  | x   | 0  | 1  | 80 x 25 Alphanumeric    |

|       | х   | 0 | 1  | 1   | 1  | 0  | 320 x 200 Graphics, B/W |

|       | x   | 1 | 1  | 1   | 1  | 0  | 640 x 200 Graphics, B/W |

|       | "x" | = | do | n't | ca | re |                         |

To produce a correct raster display, both the master display mode register and the 6845 CRT controller registers #0 thru #15 must be initialized in a consistent manner. This is usually done by sequentially loading all of these registers in the same routine to minimize the time period that the display monitor is subjected to abnormal sync pulse timing. Default initialization sequences showing these register values are covered, along with an initialization routine, in the Software Section of this manual.

# **Port #9 --** Background Color and Palette Select Register (write only)

This 6-bit control register is only functional when using color display monitors. It selects the master color display characteristics by selecting the color displayed in the outside border region area of the monitor for all but 640 x 200 graphics mode. It selects the foreground intensity level, and also selects one of two palettes available for medium resolution (320 x 200) graphic display mode as indicated in the following table:

## Table 18: Relative I/O Port #9 Control Bit Functions

Data Bit: Function:

| 7                | None                                                                                    |

|------------------|-----------------------------------------------------------------------------------------|

| 6                | None                                                                                    |

| 5                | Palette select for color 320 x 200 graphics display                                     |

| 4                | High/Low intensity for foreground graphics colors                                       |

| 3<br>2<br>1<br>0 | High/Low intensity<br>Red color enable<br>Green color enable<br>Blue color enable<br>// |

#### **Port #10** -- Video Display and Keyboard Status Buffer (read only)

This 4-bit master status port returns only those specific hardware signals that are not available from the CRT controller. Two of the bits concern the keyboard and light pen data input status and may be polled as part of a keyboard data input routine. The other two bits contain the state of the display enabled and vertical sync signals, which may be used to synchronize display memory alterations with screen blanking periods.

#### Table 19: Relative I/O Port #10 Status Bit Functions

Data Bit: Function:

- 3 Vertical Sync status (raster active indicator)

- 2 Light Pen switch activated status (not latched)

- 1 Keyboard/Light Pen data available status (latched)

- 0 Monitor Display Enabled (display not blanked indicator)

# Port #11 -- Clear Keyboard Status and Set Clock Register (write only)

This control port acts to reset both the keyboard data port and its data available status by writilg any value to it. It also has a single bit register controlled by the value of the most significant bit of the data byte sent to it. The register controls an open collector gate attached to the keyboard clock signal which, in nopmal operation, synchronizes data sent from an IBM compatible keyboard. By precisely controlling the ON/OFF period of vhis register, it enables the clock signal to be used the reverse direction as a simple asynchronous data in communications line. This is needed by a few specialized keyboards which are able to download data from the computer to perform additional functions such as speech recognition.

## Port #12 -- Set Keyboard/Light Pen Status Register (write only)

By writing any data value to this port, the keyboard/light pen data available status bit is set, indicating that data is ready. It really has only one minor function, which is to hold off the light pen from making any additional false interrupts while the current light pen signal is being processed.

## **Port #12 --** Keyboard Input Data Register (read only)

Reading this port sets the data available status register, but also returns data sent by the keyboard or light pen. Both devices may be connected at the same time to this data and status/interrupt circuit, so either may be the source of the data available flag being set. This is resolved by reading the keyboard data returned and testing for all zeros. The keyboard will never generate a zero data value, but a zero is forced into the data register whenever the keyboard clear port is written. Note that all keyboard input data register read operations should be followed by a write to the clear keyboard status port. This will enable another keyboard or light pen signal to be received by the PC Video board.

## INTERRUPTS

The PC Video interface is capable of operating in-either a polled status or interrupt driven mode for data input. Operation in the interrupt driven mode is particularly suited for multi-user or multi-tasking environments, such as with Concurrent DOS 8/16. When functioning in interrupt mode, the output of the light pen/keyboard status register is connected to drive one of the vectored interrupt lines (VIO<sup>\*</sup> thru VI7<sup>\*</sup>) on the IEEE 696/S-100 bus. This is accomplished by inserting the correct shunt on jumper block J4, positions 0-7, corresponding to the desired interrupt vector number. The interrupt vector position numbers are identified on interrupt jumper block, J4, as follows:

## Table 20: Vector Interrupt Jumper Block, J4

| Interrupt Jumper<br>Block J4:<br>CompuPro standard | V17<br>V16<br>V15<br>V14<br>V13<br>V12<br>V11 |

|----------------------------------------------------|-----------------------------------------------|

|                                                    | VII<br>VI0                                    |

If correctly jumpered, an interrupt will be generated when the data ready status is set from either source of input: keyboard or light pen. All CompuPro software, which operates interrupt driven from this board, expects that vectored interrupt #5 has been shunted.

## **SOFTWARE SECTION - CODE EXAMPLES**

This section discusses the control setup and data input/output sequences needed for correct operation of the PC Video interface board. It is intended only as an introduction to producing functional software. Every operational detail of the PC Video interface software is not covered. The 8086 source code examples presented are derived from actual driver routines that perform these functions within related CP/M operating systems from VIASYN. They are expected to execute correctly with only a few code additions necessary to fill out a completed driver. For example, code and data segment areas in the sample routines have no references to any base or origin because they are not complete To produce runable code, it is necessary to create a programs. main program, which then calls the sample routines presented in this section to perform the indicated functions.

More specific details of software operation may be obtained by listing a TMXBIOS (CP/M-86 or CP/M 8-16 BIOS source code) that has been assembled with the PCVIDEO variable equated "true" in the file ACTIVE.EQU. Please read the associated CP/M-86 or CP/M 8-16 documentation for the information necessary to assemble and use TMXBIOS.

## COMMON EQUATES AND DATA STORAGE VARIABLES

Common Equate statements start the sample 8086 code and are used by the routines which follow in the rest of the Software Section of this manual. Included are base specifications for both Color and Monochrome configurations that match those of the IBM-PC display adaptors. Also included are mnemonics for the PC Video relative input/output port offsets and the four input status port bits. The remainder of the equates deal with other types of hardware base specifications and ASCII control characters.

The Common Data Storage Area deals with those variables which are utilized by more than one type of routine. This starts with PCVBASE, which holds the current base input/output port address. By making all ports referenced by input/output instructions relative to a storage variable, all of the routines apply equally to both Monochrome and Color configurations of the PC Video board. Similarly, PCVWIDE as a variable permits both 40 and 80 column wide alphanumeric displays as well as graphics modes to be selected without altering or directing the flow of various routines.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* PC VIDEO GRAPHICS BOARD EQUATES \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* **COLOR Mode Equates:** PCVCSEG 0B800h ;Memory segment base EQU PCVCOLP EQU 03D0h ;Base port address PCVCCUR EOU 0607h :Cursor raster limits (underline) 0007h (block cursor) **MONOCHROME** Mode Equates: PCVMSEG EOU 0B000h ;Memory segment base PCVMONP EOU 03B0h ;Base port address PCVMCUR EQU 0B0Ch ;Cursor raster lines (underline) 000Ch (block cursor) PC Video Relative I/O Port Offset Equates: EQU PCVBANK 00h ;Bank select register output port PCVFLIP EOU 01h ;Base address switch flip reg. output port Register address port of 6845 CRT Controller PCV6845A 04h EQU PCV6845D EQU 05h Register data input/output port of 6845 CRTC 08h ;Master Display Mode latch output port PCVMASTR EOU PCVBGRND EQU 09h Background Color latch output port ;Status Buffer input port PCVSTATUS EQU 0Ah PCVLPCLR EQU 0Bh ;Clear Light Pen / Keyboard status/data regs. ; and Keyboard Clock Control reg. output port PCVLPSET EQU 0Ch ;Set Ready Flag / Keyboard Data input port ; Input Status Port (PCVSTATUS) bit definitions. VRT 1000Ъ :Vertical retrace bit EQU LPEN SW EOU 0100b :Light Pen Switch activated bit 0010b :Light Pen / Keyboard data byte ready bit LPEN RDY EOU HRT EOU 0001Ъ ;Horizontal retrace (display enable) bit **Priority Interrupt Controller Equates:** MASTER PIC 0 EQU 50h ;System support I master PIC port #0 MASTER PIC 1 EQU 51h ;System support I master PIC port #1 SEOI EQU 01100000b ;Specific End Of Interrupt **ASCII Control Character Equates:** ;Control-C for system restart ETX EQU 03h :XON /DC1 control code X ON EQU 11h X<sup>OFF</sup> :XOFF/DC3 control code EQU 13h DEL EQU 7Fh ;Delete

DSEG

;

PCVBASE DWPCVCOLP ; PCVMONP;Color/Monochrome base I/O port addr<br/>; (Dynamically alterable to either)PCVWIDE DB80; 40;Horiz columns (40 for graphics)

## **KEYBOARD/LIGHT PEN STATUS AND DATA INPUT ROUTINES**

This section contains four routines for Keyboard or Light Pen data available status and data input. The sample routines have been only minimally condensed from their originals so that the full set of potential software/hardware interactions is apparent. The only inline instruction code not completely present is the scan code and ASCII character input buffering for keyboard interrupts. This is so dependent on operating system parameters and handshaking that it would have greatly enlarged the coded examples were it fully incorporated. Instead, a set of comments clearly indicates the location of this buffering code and the functions that must be performed.

The only other condensation that affects the execution of the routines in this section involves the ASCII code translation tables. These are excessively large tables near the end of the data storage area for these routines, and have been reduced to simple "Reserve Storage" statements to simplify the examples. Each table storage definition indicates the nature of the original translation byte codes. These need to be correctly filled out if the code is to function in a real system.

## Keyboard/Light Pen Initialization Routine

There are two parts to this initialization sequence; first the PC Video board keyboard data/status is cleared, which is followed by enabling the associated interrupt at Priority Interrupt Controller (PIC). The keyboard/light pen status and data input registers need flushing to permit the keyboard input logic to function correctly at the first keystroke. Master PIC initialization for vector interrupt #5 is optional, but if present should come after the keyboard data/status flush sequence to prevent any spurious scan code data for the first keyboard character input.

## **KEYBOARD/LIGHT PEN DATA INPUT INTERRUPT ROUTINE**

Keyboard or light pen data inputs can interrupt the host CPU if enabled and physically connected on the PC Video board via a jumper at VI5. On interrupt, this routine saves the CPU register state and switches the data segment context to local storage.

A consequence of the non-interrupt data input routine is that the interrupt line at V15 is released when the keyboard data/status registers are cleared. The final portion of the interrupt handling routine resets the Master PIC so it can correctly receive another V15 interrupt and restores the CPU registers to their entering states. The exit instruction, IRET, performs a far return to the interrupted code and restores the entering flag registers, including interrupt enable.

## Keyboard/Light Pen Data Available Status Routine

Console Data Input Available status determination is performed by this routine for the keyboard and light pen inputs. The result of sampling the PC Video status input port is returned directly in the high byte of the accumulator. It is masked by the keyboard/light pen data available bit in the low byte of the accumulator, which returns a non-zero value with the Zero Flag reset if the status bit indicates input data is ready at the keyboard/light pen data byte holding register.

## Keyboard Coded Data/Light Pen Position Input Routines