18651 Von Karman / Irvine, California 92664 / Telephone (714) 833-8830 TWX 910-595-1767

# **NAKED MINI**

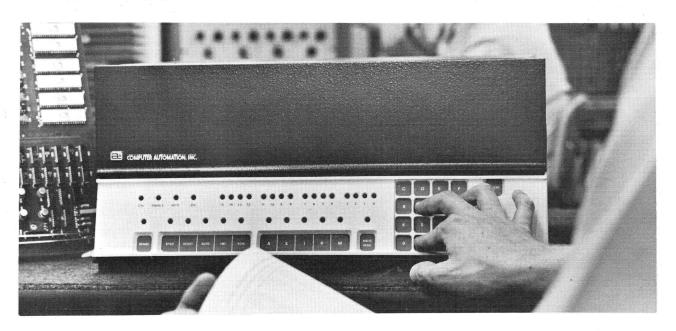

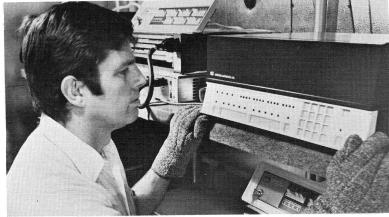

The unique Alpha/LSI hexadecimal keyboard makes data entry and program debugging fast and convenient.

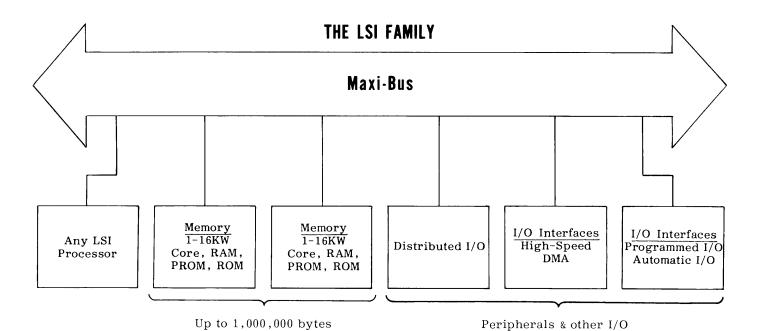

## THE LSI FAMILY

A family of low-cost OEM computers with a range to handle almost any job, big or small. With a low price tag that makes it really practical. And with complete compatibility so you can move in any direction as your needs change, quickly and easily.

## THE NAKED MINI SERIES

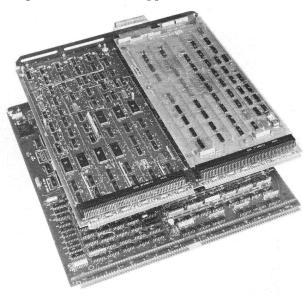

The mid-range of the LSI family, the NAKED MINI® series is truly the computer that's a component. To use it, just plug it into your product. The full-scale central processor, with full instruction set, DMA, and options is on a single card, 15" x 17". Memory up to 16K words is on a similar card. They're powered by your existing system supply.

#### One-On-One

Imagine all the products you can bury the NAKED MINI in. All your products that can benefit from a computer having powerful arithmetic capabilities, full byte and 16-bit word processing, and extremely flexible I/O. All your products that will now be more competitive, more flexible, and immune to obsolescence.

The possibilities seem endless. NAKED MINI belongs in any system that needs to see that certain things happen in certain ways at specific times. NAKED MINI lets you plug-in the intelligence you need to monitor, sequence and control effectively.

For the first time, OEM's can think of using a computer for 1-on-1 applications: smart

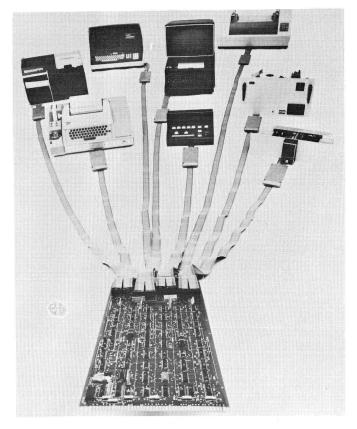

Shown is a NAKED MINI LSI-2 configuration, with processor board on top and memory board below.

terminals, key-to-disk data entry systems, automated bank tellers, delivery truck routing devices, continuous inventory control at fast-food outlets and other point-of-sale situations; information displays, communications concentrators, building security systems, laboratory instruments, patient monitoring systems, and classroom learning machines. Even mundane applications like vending machines and gas stations can now have their very own computer. A real computer.

# ALPHA/LSI Minicomputer

If you need the NAKED MINI installed in its own fully encased mainframe chassis, we can do that, too. It's called ALPHA/LSI, and includes a power supply and a control console. It can easily be expanded to 512K words of 16-bit memory. And as many peripheral controllers and special-purpose interfaces as you need.

## WE DID IT: THE GREAT OEM GAP

Very few suppliers really understand the OEM.

Other minicomputer companies don't. They're busy building end-user systems with lots of peripherals, one-of-a-kind features, and more speed

and software than the job needs right now. The application is loosely defined and constantly changing. Someday the end user might — just might — need the extra goodies. Just in case, he has to pay fancy prices for them now.

Chip companies (so-called "microcomputers") don't really understand the OEM, either. They're producing do-it-yourself kits with weak instruction sets and limited input/output capability that end up costing more than a NAKED MINI by the time you buy the memory and get the chips interconnected, functionally tested, burned in, and truly operating. And even after doing all that, you wind up with something which performs more like a smart calculator than a real computer.

The OEM, on the other hand, has a well-defined problem. He needs a computer powerful enough to answer his product's requirements, with enough performance margin to accommodate the growth he expects in the future. Initial cost is important to him, since any savings are translated directly into profit. And because maintenance costs come right out of that same profit, he demands unfailing reliability.

Besides these requirements, the OEM has other needs — unique to him — which further separate him from the end user.

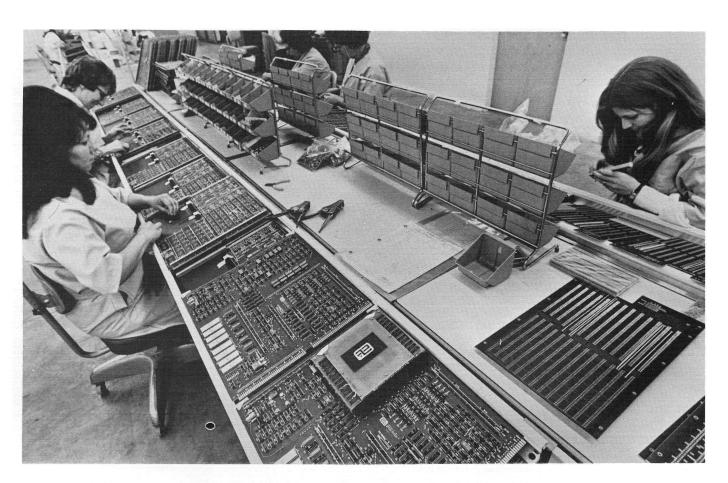

Pretested components being assembled onto boards and inspected.

He needs to get his product to the marketplace fast, to establish his position before the competition can react. This means he wants to shorten his development cycle as much as he can. He needs working hardware <u>now</u>, so he can get going on his prototype fast.

Also, an OEM may build a complete product line with a wide range of performance. At the low end of the line, he may need somewhat less computing power and slower, smaller memories, but he has to have the lowest possible price. In the middle and high ranges, he needs different combinations of computing power and memory size/speed but his cost constraints are less severe.

Further, for maximum flexibility, he needs to be able to reconfigure in the field — to change computing power, memory size, memory speed, special features — any or all of them, quickly and easily. His system has to be able to "grow up" as needed.

Overall, he has to have a low-cost, truly flexible way to satisfy these conflicting needs.

After seeing this gap and listening to what OEM people really wanted, we knew the time was right for the NAKED MINI family. Because of our specialized knowledge of the OEM, we were able to accurately define the needs of this market, overlooked by others.

# THE 2/10 AND 2/20

The NAKED MINI series includes two processors, the LSI-2/10 and LSI-2/20. The LSI-2/20 is the faster processor in the series, with internal speed great enough to take advantage of our highest speed memories. The LSI-2/10 is about half the speed of the 2/20, but otherwise identical.

This means that user programs run correctly on any NAKED MINI, and one can be substituted for the other without program changes. You choose exactly the speed you need.

Some of the memories available for the LSI family are described below. Any combination of memories in any mix of types and speeds can be used with any processor. This means the user can configure exactly the combination which best suits his needs now, and later change the combination to meet new needs merely by exchanging or adding the appropriate processor or memory boards.

Now, indeed, any LSI system can "grow up" and change easily and quickly, even in the field.

## Memories

To provide maximum flexibility, the LSI family offers a variety of memories in various types, speeds, and capacities. All memories work with any LSI processor, in any combination of types,

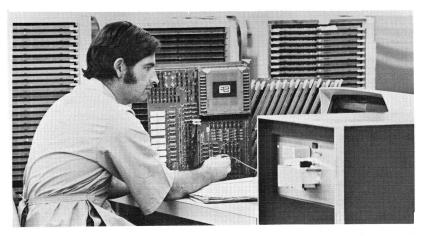

Processor board undergoing test, using our CAPABLE<sup>TM</sup> Computer-controller tester. CAPABLE verifies the correctness of every function — completely and automatically.

High temperature testing in an oven to verify long-term reliability. Test inincludes seventy-two hours at 50°C.

speeds, and sizes up to the maximum memory capacity of 512K words. As new memories become available, they will also work with all LSI processors.

#### **CORE 1600**

Core memory with a cycle time of 1.6 microseconds, in modules of 4K and 8K words.

#### **CORE 1200**

Core memory with a cycle time of 1.2 microseconds in modules of 16K words.

#### **CORE 980**

Fast core memory with a cycle time of 980~nanoseconds, in modules of 4K~and~8K~words.

#### PROM/ROM/RAM

Programmable read-only (PROM), read-only (ROM) and random access semiconductor (RAM) memories; available in various combinations.

## HOW LSI COMPONENTS FIT TOGETHER

Since all elements — memories, processors, options interfaces — of the LSI family are designed to work together in any combination, it is possible to configure thousands of distinct combinations, merely by plugging the modules into the system, without special wiring or modification.

Shown below are only a few examples as illustrations of the many possibilities.

Problem 1. The user starts out with an LSI-2/10 processor with 8K of Core 1600 because processing requirements are not so severe. At some future time, he finds he needs more memory to handle his expanded requirements, and also more speed in processing and input/output.

Solution. Add 8K of fast Core 980, which provides more program storage. For greater overall speed, interleave the existing 8K of Core 1600 with the new 8K of Core 980, to give a total of 16K with an average effective cycle time of approximately 1.1 microseconds. If still more speed is needed, switch to the LSI-2/20 processor.

Problem 2. The user has a large processing program of more than 16K words, one part of which is a highly repetitive inner loop which must run very quickly.

Solution 1. Use the LSI-2/20 with 4K words of Core 980 to provide faster execution of the inner loop plus a 16K module of Core 1200 for greater economy in storing the rest of the operating program.

Solution 2. If even faster processing is desired, use two 4K or two 8K modules of Core 980 which are interleaved, since the LSI-2/20 processor can take maximum advantage of the faster effective cycle time of the interleaved memories. The remainder of the memory requirement can be satisfied with lower cost, lower speed Core 1200 or Core 1600.

# POWERFUL INSTRUCTIONS FOR SHORTER, FASTER PROGRAMS

There's a big and very important difference between raw cycle time and "getting the job done" time. We believe computers should work smart, as well as hard. They should offer built-in features that assure faster execution.

With NAKED MINI you get what many consider to be the most powerful instruction set on the market. With 188 instructions on the LSI-2 series — including 8 addressing modes and hardware multiply/divide — the NAKED MINI offers better memory efficiency than other mini's.

Development of cost-cutting software systems in our complete programming laboratory.

This efficiency lets you write shorter programs with faster run times — and keeps memory costs to a minimum, since tasks run in less memory. And programs are easier to write, too.

In short, you get speed where it counts: on the job.

## **Memory Reference Instructions**

In typical mini-computer applications, the computer usually spends a large percentage of its execution time successively doing a few operations on each of many pieces of data stored in memory — rather than performing repeated operations on just a few pieces of data which could be stored in registers. This usually means that memory is referenced frequently.

NAKED MINI optimizes its instruction set for these typical minicomputer applications, to get greater efficiency and ease of programming. It provides a varied and powerful set of 30 memory reference instructions ideal for OEM's.

# Multiply/Divide

Most minicomputers offer hardware multiply/divide instructions only as an extra cost option; slow and inefficient, memory-consuming programmed subroutines are the only alternative if the option is not purchased. Our instruction set includes hardware Multiply and Divide as a standard feature. And our Multiply instruction also performs a "Multiply and Add", useful in directly evaluating mathematical expressions of the form AX+B.

# **Indirect Addressing**

True multi-level indirect addressing lets the user construct and use powerful addressing methods for effective table addressing.

## Normalize

For efficient floating point operations, we include a complete double-word Normalize instruction which normalizes and updates the exponent.

# **Memory Scan**

Here's a good example of multifunction instructions which, in other computers, would require time and memory-consuming subroutines. Scan provides a rapid search of any portion of memory for any word or byte value. Any block of contiguous memory locations can be scanned in a single instruction to see if it contains the desired value.

## **Compare Between Limits**

By using only two Compare Memory And Skip instructions, it is possible to do a comparison between upper and lower limits quickly and simply in just two instructions.

# **Word and Byte Addressing**

We provide both word and byte addressing for most memory reference instructions. This means that you can deal directly with either bytes or full words, as the application requires, without the complications required in computers without byte addressing. Twenty of the memory reference instructions provide arithmetic, logical, data transfer, and comparison capabilities for efficient handling of bytes and words.

## Immediate Instructions

We provide a full complement of ten immediate instructions. The address portion of the instruction actually contains the 8-bit operand itself, rather than an address. Only half as much memory is needed, since both instruction and operand are contained in a single word. Immediates include Add, Subtract, Load, and Compare.

# Single Word Instruction Format

With only a few exceptions, our instructions require only one memory location. Compare this with many other minicomputers which require two or more memory locations for most instructions.

# **Full Shift Capability**

We provide a full complement of 16 shift instructions which can be: single or multiple place; left or right; single or double register; logical, circular, or arithmetic. Compare this with the basic single place shift found in most minicomputers.

# Fast, Efficient, Conditional Jumps

The 63 conditional jump instructions test conditions within the processor (overflow, sense register, A and X registers) and perform conditional jumps, depending upon the results. Since each of these single word instructions performs both the test and the jump, memory is more efficiently utilized than with other computers which need two words for this function. Any combination of testable conditions can be tested in a single instruction.

## Stack Instructions

Fifteen stack instructions allow the use of any memory location as a stack control pointer to maintain a stack anywhere else in memory.

Any number of routines can maintain any number of stacks located anywhere in memory. Further, it is possible to use any number of separately maintained stack pointers to access the same physical stack — a unique and exceptionally powerful implementation that invites the use of extremely sophisticated and effective programming techniques.

In addition, we accommodate not only the conventional load and store (Pop and Push) stack accesses but also arithmetic, Boolean, and compare operations on data contained in stacks.

## I/O MAXI-BUS FOR EASE OF INTERFACING

Maxi-Bus provides 58 parallel lines for data, command, device address, status, and control information. This eliminates the timing problems created when data and address lines are timeshared. It makes interfacing easier, faster and less expensive.

Memory and input/output interfaces connect directly to the Maxi-Bus. Each operates asynchronously, at its own pace. This means that transfers can be made directly between an external device and memory without affecting the central processor, if desired.

It also means that as faster or lower cost memories and processors become available, they can be plugged into the system directly, without the need for modification.

This open ended design assures you of growth capabilities for the future, whenever your needs change.

# Multiple Input/Output Modes for Maximum Power

You get three standard input/output systems for flexibility. Combined with a powerful set of 33 I/O instructions, this results in an I/O structure which is exceptionally efficient and easy to use.

Both word and byte data can be handled directly, with byte data being packed or unpacked automatically as desired.

#### DIRECT MEMORY ACCESS (DMA)

For highest speed transfer rates, DMA transfers data on a cycle-stealing basis directly between the memory and the external device, bypassing the central processor.

#### PROGRAMMED INPUT/OUTPUT

For greater flexibility, Programmed I/O provides transfers between the external interface and the A or X registers, in words or bytes. Especially effective in applications where data must be examined immediately upon input (such as message handling, keyboard response, etc.) or where data is the result of a computation which must be output immediately.

Programmed I/O instructions can be combined with Sense-and-Skip instructions to produce a single instruction which performs a test and transfers only if the test result is satisfactory. For example, the two functions "Sense For Ready" and "Input" can be combined in one "Read" instruction. And, these instructions are interruptable.

6

#### AUTOMATIC I/O CHANNELS

Each channel transfers data between memory and external interfaces in blocks of any size without disturbing the processor's working registers. Word or Byte Count and Current Address for each channel are held in memory; each transfer automatically updates them until the count is complete. This use of memory for control registers lowers the cost of interfacing. Multiple channels can operate concurrently, with hardware priority control of each channel. Transfers can be full 16-bit words or 8-bit bytes with automatic packing/unpacking.

## HARDWARE PRIORITY INTERRUPTS

Our hardware priority interrupts provide automatic handling of:

- recognition of an external event which requires immediate attention

- identification of which event, among many, actually occurred

- assignment of priority when several events occur simultaneously.

It also means really  $fast\ response$  to the event which caused the interrupt.

The necessary interrupt routines are simple, easy to write, take less memory space, and execute more quickly. Wasteful polling is completely eliminated.

Because we provide so many multi-function instructions, it is frequently possible to perform the equivalent of an entire interrupt subroutine in

a single instruction. In such cases, the interrupt can be recognized and serviced without changing control from the current program, completely eliminating the overhead needed to save and restore processor status.

#### OPTIONS

To increase flexibility for various applications, we offer a number of useful options:

## Power Fail/Restart

Monitors power supply voltage to provide an orderly shutdown upon power failure and automatic restart when power is restored.

#### Real Time Clock

Provides interrupts at jumper selectable frequencies of 0.1K, 1K, or 10K Hz or twice the AC line frequency. External frequency source may also be substituted.

## Autoload

Allows program loading to be initiated automatically, remotely or from a front panel switch. The single option provides loading from Teletype, Paper Tape, Cassette, Magnetic Tape and Disc.

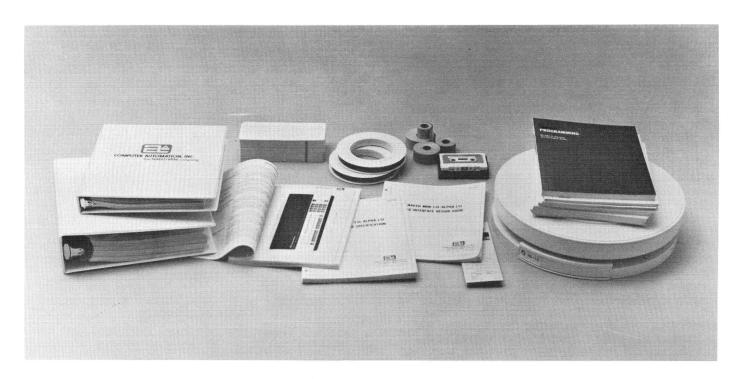

Computer Automation support includes extensive software and full documentation.

## **Memory Bank Controller**

Provides for memory expansion to 524,288 words and for rapid context switching by controlling up to 32 memory segments.

## **Memory Parity**

Generates and checks parity on each memory transfer and provides an interrupt if an error is detected. Available on special order.

# Teletype/CRT Interface

Controls CRT or modified teletype in full duplex mode. For CRT provides 9 user-selectable speeds from 75 to 9600 baud.

## PERIPHERAL EQUIPMENT

The product line includes a wide variety of standard peripheral equipment in most major functional types, such as teletypes, paper tape readers and punches, line printers, card readers, magnetic tape units, digital cassettes, plotters, keyboard displays, and various types of disk units.

We offer the entire device complete with interface; or, for OEM ecomony, just the interface alone.

## COMMUNICATIONS EQUIPMENT

A selection of communications interface equipment is available, including: dual Teletype/CRT/modem interfaces; single channel asynchronous modem controllers; asynchronous modem multiplexers; synchronous modem controllers; and automatic calling unit multiplexers.

# DISTRIBUTED INPUT/OUTPUT SYSTEM

Computer Automation's Distributed I/O System provides a low-cost, high performance, and extremely flexible input/output system for interfacing a wide variety of standard peripherals or special purpose devices to any LSI series computer. Distributed I/O is a total system solution to the problems of peripheral interfacing.

The Distributed I/O System consists of a half-card I/O Distributor to which one to eight Intelligent Cables can be connected. Intelligent Cables are ribbon cables which include a microprogrammed PicoProcessor™ at the peripheral end of the cable. Standard PicoProcessors are available for most common peripheral devices and standard I/O disciplines. Because each individual PicoProcessor interface is a small computer which performs the detailed management of data flow and error checking, the software for all I/O devices interfaced with the Distributed I/O System is essentially identical.

I/O Distributor pictured with a variety of standard peripherals and user-designed I/O devices, including special consoles, instruments, etc.

One I/O Distributor can support up to eight Intelligent Cables interfaced to any combination of input or output, serial or parallel peripherals, all transferring data directly to or from memory concurrently.

High throughput is achieved with minimum overhead because Computer Automation's unique interrupt-driven Direct Memory Channel mode of I/O is used by the Distributed I/O System.

- Low Cost

- High Performance

- Simplified Cabling

- · Simplified Programming

- Improved Reliability

- · High Packaging Density

- Direct Memory Transfers

- Automatic End-of-Block Character Detection (Carriage Return Character)

- Error Detection

- Serial Interfaces Support Any Mix of Baud Rates from 75 Baud thru 19.2K Baud

# GENERAL PURPOSE INPUT/OUTPUT INTERFACES

We offer a number of general purpose input/output interfaces in standard production. New interfaces are added frequently. Some representative units:

## 16-Bit Input/Output Module

Provides 16-bit input/output compatible with DTL/TTL, with control and sense lines.

# Relay Output Module

Provides a set of 32 relay contacts which may be used to drive lamps, external relays, etc.

# Relay Input Module

Presents 32 relay coils to the external environment. The contacts of these relays are presented to the processor's I/O bus. Interrupts are generated automatically upon a change in input.

# 64-Bit Output Module

Provides 64 DTL/TTL compatible outputs which may be used as a single output 64 bits wide or addressed and strobed in groups of 32, 16, or 8 bits.

# 64-Bit Input Module

Provides 64 DTL/TTL compatible inputs which may also be used in groups of 16 or 8 bits for multiple devices.

# Priority Interrupt Module

Provides 16 inputs with individual change of state detectors. For use with momentary or toggle switches for operator initiated interrupts or as a general purpose priority interrupt module.

# 1/0 Driver Module

Permits extending the processor I/O bus up to 25 feet from the processor.

## SOFTWARE BUILT TO CUT COSTS

From the beginning, we built our software to cut the cost of OEM user programming. We did this first be designing it specifically to meet the needs of the OEM user — powerful enough to get his job done well because it was optimized for that job, but still fast and easy to use.

Then, to cut overall <u>system</u> cost, we made it efficient. Typically, our software is modular in construction. If you only use some of it, only a minimum configuration is required. This means you use only as much memory as you actually need, with no waste or unnecessary memory expense.

If you need more capability, it is available in larger, more powerful systems built to get maximum results from larger hardware configurations.

And, this comprehensive software produces efficient user code, so the programs it helps you to produce are efficient, too.

Described below are only a few of the software systems. Complete descriptions are available in a series of data sheets.

# **Operating Systems**

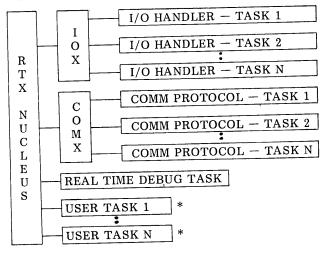

REAL TIME EXECUTIVE SYSTEM (RTX)

A good example of software specifically engineered to help get an OEM user and his product to market fast. RTX is actually a modular system of many real-time elements — subsystems, subprograms, handlers — with a standard way of communicating. This means you can build up your application quickly and easily by combining RTX modules with your own application modules.

And, RTX is a completely open-ended system which is steadily growing in capability because we are always adding new program modules (tasks) to its library. This means that as your needs change and grow in the future, you can selectively add new tasks — of your own or from our library — or change any existing tasks without having to redo your entire application program.

#### INPUT/OUTPUT EXECUTIVE (IOX)

Operates as a subsystem under RTX. It provides the user with a complete, modular method of I/O device management and support. Application programming is faster since I/O protocol is already established and well-defined. Time-consuming I/O programming need no longer be done by the user.

IOX is also open-ended. This means the user can develop virtually any kind of device handler unique to his application and operate it under IOX control. IOX supports most currently offered peripherals and communications devices.

#### COMMUNICATIONS EXECUTIVE (COMX)

Operates as a subsystem under RTX. It provides a modular method of communication protocol management and support.

#### REAL-TIME DEBUG (RTDBUG)

An interactive program which helps the user debug his application program. Because RTDBUG runs under RTX, the user can examine and — if necessary — alter his program, while the real-time program is actually running. This means user programs become operational faster and easier.

Tasks marked \* are application dependent. All other tasks are available from the Computer Automation library.

## DISK OPERATING SYSTEM (DOS)

A comprehensive system oriented toward fast development of user programs. Provides efficient control of sequential job operations, using easy-to-understand control cards on-line communications through the Teletype. DOS gives the user a complete system of program storage, maintenance and retrieval to simplify his program development. DOS supports all devices, with convenient methods of dealing with files of virtually any length, providing both random and sequential access. It is device-independent and automatically handles all user input/output, including service of all devices. It uses the disk for system secondary storage.

# Higher Level Languages

#### ADVANCED BASIC

Includes all the features of Advanced BASIC above, plus Text Variables (string manipulation) and Matrix Instructions. This BASIC provides the user with capabilities not usually found in a small machine environment. Runs in 8K of memory.

## EXTENDED MULTIPLE-USER BASIC

Same powerful language as Extended BASIC above. Supports up to eight users.

#### FORTRAN IV

A new FORTRAN IV compiler for the LSI family, which provides full ANSI X3.9-1966 compatibility plus added features that provide for real-time execution, in-line assembly language capability, and simplified I/O programming — a powerful tool for producing efficient applications software.

Recognizing that the OEM user is concerned about the cost of his product, and that processor memories contribute heavily to product cost, we have implemented a FORTRAN IV compiler that generates object code optimized for compactness.

## Other Software

Our complete range of software also includes standard and Macro assemblers; file managers; utility programs; math packages; and diagnostics.

Since these software packages are constantly increasing in number and scope, please refer to the appropriate software data sheets for the latest information.

# TYPICAL EXECUTION TIMES

All NAKED MINI processors have the same set of 188 instructions in common.

Execution times vary according to the processor type (LSI-2/10 or LSI-2/20) and the speed of the memory used. Following are some typical instruction times, shown in microseconds for three speeds of core memory. Direct relative addressing is assumed in calculations.

In most cases with the LSI-2/20 processor, execution times can be improved by interleaving memories to get faster effective cycle times. See the technical reference manual for a complete list of instruction execution times.

|             |                  | $\operatorname{Core}$ | $\operatorname{Core}$ | $\operatorname{Core}$ |

|-------------|------------------|-----------------------|-----------------------|-----------------------|

| Instruction | Processor        | 980                   | 1200                  | 1600                  |

| ADD/SUB     | 2/20             | 2.06                  | 2.4                   | 3.2                   |

|             | 2/10             | 4.12                  | 4.8                   | 6.4                   |

| AND/IOR     | 2/20             | 2.06                  | 2.4                   | 3.2                   |

| 111.27.1    | 2/10             | 4.12                  | 4.8                   | 6.4                   |

| JMP         | $\frac{2}{2}$    | 1.38                  | 1.4                   | 1.6                   |

|             | 2/10             | 2.76                  | 2.8                   | 3.2                   |

| DVD         | $\frac{7}{2}/20$ | 12.44                 | 12.7                  | 13.35                 |

|             | 2/10             | 24.9                  | 25.4                  | 26.7                  |

| AXI/SXI     | 2/20             | 1.08                  | 1.2                   | 1.6                   |

| 11111/ 5/11 | $\frac{2}{10}$   | 2.16                  | 2.4                   | 3.2                   |

|             |                  |                       |                       |                       |

## LIST OF INSTRUCTIONS

# Memory Reference

| Arithmetic |                      |

|------------|----------------------|

| ADD        | Add to A             |

| ADDB       | Add Byte to A        |

| SUB        | Subtract from A      |

| SUBB       | Subtract Byte from A |

|            |                      |

# Logic AND

| 5 · C |                          |

|-------|--------------------------|

| AND   | AND to A                 |

| ANDB  | AND Byte with A          |

| IOR   | Inclusive OR to A        |

| IORB  | Inclusive OR Byte with A |

| VOD   | Evalueiva OR to A        |

Exclusive OR Byte with A XORB

#### Data Transfer

| ta rrano-or |                   |

|-------------|-------------------|

| LDA         | Load A            |

| LDAB        | Load A with Byte  |

| LDX         | Load X            |

| LDXB        | Load X with Byte  |

| STA         | Store A           |

| STAB        | Store Byte from A |

| STX         | Store X           |

| STXB        | Store Byte from X |

|             |                   |

Exchange A and Memory EMA Exchange A and Memory Byte EMAB

#### Program Transfer

| , Brann ann |                                |

|-------------|--------------------------------|

| JMP         | Unconditional Jump             |

| $_{ m JST}$ | Jump and Store P Counter       |

| IMS         | Increment Memory, Skip on Zero |

| SCM         | Scan Memory                    |

| SCMB        | Scan Memory Byte               |

| CMS         | Compare A with Memory, skip    |

|             | (high, low, equal test)        |

| CMSB        | Compare A with Memory Byte,    |

|             | skip (high, low, equal test)   |

|             |                                |

## Stack

| ack          |                                  |

|--------------|----------------------------------|

| ADDS         | Add Stack Element to A           |

| ANDS         | AND Stack Element to A           |

| CMSS         | Compare Stack Element to A       |

|              | and skip (high, low, equal test) |

| EMAS         | Exchange Stack Element and A     |

| IMSS         | Increment Stack Element and      |

|              | Skip on Zero                     |

| IORS         | Inclusive OR Stack Element to A  |

| $_{ m JMPS}$ | Jump to Stack Element            |

| JSTS         | Jump and Store to Stack Element  |

| LDAS         | Load Stack Element into A        |

| LDXS         | Load Stack Element into X        |

| SLAS         | Stack Pointer Value to A         |

| STAS         | Store A in Stack Element         |

| STXS         | Store X in Stack Element         |

| SUBS         | Subtract Stack Element from A    |

| XORS         | Exclusive OR Stack Element to A  |

|              |                                  |

# **Double Word Memory Reference**

| DVD | Divide            |

|-----|-------------------|

| MPY | Multiply and Add  |

| NRM | Normalize A and X |

# Byte Immediate

| AAI | Add to A Register Immediate  |

|-----|------------------------------|

| AXI | Add to X Register Immediate  |

| SAI | Subtract from A Register     |

|     | Immediate                    |

| SXI | Subtract from X Register     |

|     | Immediate                    |

| CAI | Compare to A Immediate, skip |

|     | if not equal                 |

| CXI | Compare to X Immediate, skip |

|     | if not equal                 |

| LAP | Load A Positive Immediate    |

| LXP | Load X Positive Immediate    |

| LAM | Load A Minus Immediate       |

| LXM | Load X Minus Immediate       |

|     |                              |

# **Conditional Jump**

| Conditional<br>JOC | Jump on Condition Specified     |

|--------------------|---------------------------------|

| Arithmetic         |                                 |

| JAG                | Jump if A Greater than Zero     |

| $_{ m JAP}$        | Jump if A Positive              |

| JAZ                | Jump if A Zero                  |

| JAN                | Jump if A not Zero              |

| ${ m JAL}$         | Jump if A less than or equal to |

|                    | Zero                            |

| JAM                | Jump if A Minus                 |

| JXZ                | Jump if X Zero                  |

| JXN                | Jump if X Not Zero              |

| Control            |                                 |

| JSS                | Jump if Sense Indicator On      |

| JSR                | Jump if Sense Indicator Off     |

| $_{ m JOS}$        | Jump if OV Set                  |

| JOR                | Jump if OV Reset                |

# **Shift Class**

| Arithmetic Right A     |

|------------------------|

| Arithmetic Right X     |

| Arithmetic Left A      |

| Arithmetic Left X      |

|                        |

|                        |

| Logical Right A        |

| Logical Right X        |

| Logical Left A         |

| Logical Left X         |

|                        |

|                        |

| Rotate Right A with OV |

| Rotate Right X with OV |

| Rotate Left A with OV  |

| Rotate Left X with OV  |

|                        |

|                        |

| 1 T C                  |

| Long Logical Left      |

| Long Logical Right     |

|                        |

| Rotate        |                                   | Bit Clear/Set  |                                         |

|---------------|-----------------------------------|----------------|-----------------------------------------|

| LRL           | Long Rotate Left with OV          | BCA            | Bit Clear A                             |

| LRR           | Long Rotate Right with OV         | BCX            | Bit Clear X                             |

|               |                                   | BSA            | Bit Set A                               |

| D!- L Ob      |                                   | BSX            | Bit Set X                               |

| Register Chan | ge                                |                |                                         |

|               |                                   | Control        |                                         |

| Accumulator   |                                   |                |                                         |

| ZAR           | Zero A                            | Processor      |                                         |

| ARP           | Set A to Positive 1               | NOP            | No Operation                            |

| ARM           | Set A to Minus 1                  | HLT            | Halt                                    |

| CAR           | l's Complement A                  | STOP           | Halt with Operand                       |

| NAR           | Negate A                          | WAIT           | Wait for Interrupt                      |

| IAR           | Increment A                       |                | •                                       |

| DAR           | Decrement A                       | Mode Control   |                                         |

|               |                                   | SBM            | Set Byte Operand Mode                   |

| Index         | 7 7                               | SWM            | Set Word Operand Mode                   |

| ZXR           | Zero X                            |                | -                                       |

| XRP           | Set X to Positive 1               | Status         |                                         |

| XRM<br>CXR    | Set X to Minus 1                  | SIN            | Status Inhibit                          |

| NXR           | l's Complement X                  | SIA            | Status Input to A                       |

| IXR           | Negate X<br>Increment X           | SIX            | Status Input to X                       |

| DXR           | Decrement X                       | SOA            | Status Output from A                    |

| DAN           | Decrement X                       | SOX            | Status Output from X                    |

| Overflow      |                                   |                |                                         |

| SOV           | Set Overflow                      | Interrupts     |                                         |

| ROV           | Reset Overflow                    | EIN            | Enable Interrupts                       |

| COV           | Complement Overflow               | DIN            | Disable Interrupts                      |

| SAO           | Sign of A to OV                   | CIE            | Console Interrupt Enable                |

| SXO           | Sign of X to OV                   | CID            | Console Interrupt Disable               |

| LAO           | Least significant bit of A to OV  | PFE            | Power Fail Interrupt Enable             |

| LXO           | Least significant bit of X to OV  | PFD            | Power Fail Interrupt Disable            |

| BAO           | Bit of A to OV                    | TRP            | Trap                                    |

| BXO           | Bit of X to OV                    |                |                                         |

|               |                                   | Execute        | December In stress than a sink of the   |

| Multi-        |                                   | EIX            | Execute Instruction pointed to          |

| Register      |                                   |                | by X                                    |

| ZAR           | Zero A and X                      |                |                                         |

| AXP           | Set A and X to Positive 1         | Input/Output   |                                         |

| AXM           | Set A and X to Minus 1            | •              |                                         |

| TAX           | Transfer A to X                   | Control        |                                         |

| TXA           | Transfer X to A                   | ${\tt SEL}$    | Select                                  |

| ANA           | AND of A and X to A               | SEA            | Select and Present A                    |

| ANX           | AND of A and X to X               | $\mathbf{SEX}$ | Select and Present X                    |

| NRA           | NOR of A and X to A               | SEN            | Sense and Skip on Response              |

| NRX           | NOR of A and X to X               | SSN            | Sense and Skip on no Response           |

| CAX           | l's Complement A and put in X     | 11.1 1         |                                         |

| CXA           | l's Complement X and put in A     | Unconditional  | T., 4 TIV 3 A A                         |

| NAX           | Negate A and put in X             | INA            | Input Word to A Magical                 |

| NXA           | Negate X and put in A             | INAM           | Input Word to A Masked                  |

| IAX           | Increment A and put in X          | INX            | Input Word to X                         |

| IXA           | Increment X and put in A          | INXM<br>OTA    | Input Word to X Masked                  |

| DAX<br>DXA    | Decrement A and put in X          | OTX            | Output A<br>Output X                    |

|               | Decrement X and put in A          | OTZ            | Output X<br>Output Zero's               |

| EAX<br>IPX    | Exchange A and X                  | Olz            | Output Zero s                           |

| ILV           | Increment P and put in X          | Conditional    |                                         |

|               |                                   | Word           |                                         |

| Console       |                                   | RDA            | Read Word to A                          |

| Registers     |                                   | RDAM           | Read Word to A Masked                   |

| ICA           | Input Console Data Register to A  | RDX            | Read Word to X                          |

| ICX           | Input Console Data Register to X  | RDXM           | Read Word to X<br>Read Word to X Masked |

| ISA           | Input Console Sense Register to A | WRA            | Write A                                 |

| ISX           | Input Console Sense Register to X | WRX            | Write X                                 |

| OCA           | Output A to Console Data Register | WRZ            | Write Zero's                            |

| OCX           | Output X to Console Data Register | •••            |                                         |

|               |                                   |                |                                         |

Unconditional Byte Block **IBA** Input Byte to A BIN Input Block to Memory IBAMInput Byte to A Masked BOT Output Block from Memory Input Byte to X

Input Byte to X Masked IBX **IBXM** Automatic (DMC) Automatic Input to Memory-Word Automatic Output from Memory-AIN Conditional Byte AOT Read Byte to A Read Byte to A Masked Read Byte to X Read Byte to X Masked RBA Word **RBAM** AIB Automatic Input to Memory-Byte RBX AOB Automatic Output from Memory-

Byte

**RBXM**

THE LSI FAMILY

#### **SPECIFICATIONS**

## Memory

Word Size: 16 bits/ word

Memory Size: 1,024 to 524,288 words Addressing: Both word and byte

Memory Parity: Available option which adds

one bit per byte

## **Functional**

Instructions: 188 distinct basic instructions,

plus many variations through

address modes

Index Register: Standard

Indirect Addressing: Multi-level

Instruction Format: Single word for most

instructions

Direct Addressing: 768 words or bytes

Indirect Addressing: 32,768 words or 65,536 bytes

Power Fail Restart: Available option Real Time Clock: Available option Autoload: Available option

# **Physical**

Dimensions: H W D

NAKED MINI/

LSI-2: 1.5" 19.5" 18.5" ALPHA LSI-2: 8.7" 19.5" 19.6"

Weight:

NAKED MINI/

LSI-2: 29.0 lbs., with full complement

of options

ALPHA/LSI-2: 67.0 lbs., with full complement

of options, power supply and

panel

#### Electrical

Power Requirements:

NAKED MINI/ LSI-2: +5 volts dc at 13.5 amps;

+12 volts de at 0.6 amps;

-12 volts at 2.8 amps

ALPHA LSI-2:

Voltage: 115 (98 to 127) volts RMS or

230 (196 to 254) volts RMS

Frequency: 47 to 63 Hz, single phase Power: Without options — LSI-1 225

watt; LSI-2 275 watts

With all slots full - 675 watts

Logic: MOS LSI and TTL

I/O Bus Logic Level: DTL/TTL compatible, 0 and

+5 volts

## Environmental

Temperature: 00 to 50°C

Humidity: 90% (non-condensing)

## Software

Real Time Executive (RTX) includes modular Input/Output (IOX) and Communications

Input/Output (IOX) and Communications COMX) subsystems

Disk Operating System

BASIC: Advanced, Extended and Multi-User

versions

FORTRAN IV with real-time features

Conversational Assembler in addition to standard

batch Assembler

Utility and Library programs

Quality Control Diagnostic (QCD) programs

File Managers

360/370 Cross Assembler

| Input/Output                                                                        | LSI-2/20 with memory speed of 980 1200 1600 |           | - 1       | LSI-2/10 with memory speed of 980   1200   1600 |           |           |

|-------------------------------------------------------------------------------------|---------------------------------------------|-----------|-----------|-------------------------------------------------|-----------|-----------|

| I/O Transfer Rates<br>(words/bytes/sec)<br>DMA (std)                                | 1,020,000                                   | 833,000   | 625,000   | 1,020,000                                       | 833,000   | 625,000   |

| DMA (Interleaved)                                                                   | 1,666,000                                   | 1,429,000 | 1,250,000 | 1,666,000                                       | 1,429,000 | 1,250,000 |

| Programmed I/O<br>(Std; via registers)                                              | 130,000                                     | 125,000   | 112,000   | 65,000                                          | 62,500    | 56,000    |

| Programmed I/O (Std; direct to memory)                                              | 90,000                                      | 83,000    | 70,000    | 45,000                                          | 41,500    | 35,000    |

| Automatic I/O Channels (Std; multiple device capability without multiplexer); total | 80,000                                      | 73,000    | 62,000    | 40,000                                          | 36,500    | 31,000    |

Conditional I/O:

Maximum number of I/O

devices addressable:

I/O Word Length:

Priority Levels:

Interrupts:

Standard

248

8 and 16 bits

5 standard (2 internal; 3 external)

Fully vectored: 6 standard:

additional provided by all standard I/O options

All specifications subject to change without notice.

## **FEATURES**

# **Obsolescence-Proof Family**

Open-ended design: change capacity or speed, quickly and easily, in the field.

Many processors; many kinds of memories in fourteen sizes; variety of options and interfaces.

# **Quality Construction**

100% burn-in of IC's to MIL-STD-883

Full one-year unconditional factory warranty

# Efficient Hardware Means Easy Integration

Memory from 1,024 to 524,288 16-bit words

Relative addressing eliminates fixed page problems

Indexed addressing for efficient loop control and table processing

Multi-level indirect addressing

Vectored priority interrupts

Full range of options includes Memory Parity, Power Fail/Restart, Real Time Clock, and Autoload

Complete set of peripheral and general purpose interface modules

# Powerful Instruction Set for More Efficient Use of Memory

Hardware Multiply/Divide standard

Single word instruction format saves memory

Extensive byte capability means easier programming

Double-register Normalize instruction for floating point operations

Immediate instructions save storage space for constants

Complete set of logical instructions: OR, XOR AND, NOR

Memory Scan instruction for rapid memory search

Single and Double register rotate, logical, and arithmetic shift instructions

Stack instructions for program efficiency

# Maxi-Bus Provides Multiple Input/Output Systems

Direct Memory Access (DMA) standard for very high speed transfers

Automatic I/O Channels for concurrent I/O

Programmed I/O through A or X registers

# Comprehensive OEM Software Cuts Cost of Programming

Real Time Executive (RTX) is modular, includes Input/Output (IOX) subsystem

Disc Operating System

BASIC: Advanced, Extended and Multi-User versions

FORTRAN IV with real-time capability

File Manager in Disc, Magnetic Tape and Cassette versions

Conversational mode Assembler in addition to standard Assemblers

Utility and Library programs

360/370 Cross Assembler

Quality Control Diagnostic (QCD) programs

#### DOMESTIC OFFICES

Corporate Headquarters:

Computer Automation, Inc. 18651 Von Karman Irvine, California 92664 (714) 833-8830 TWX: 910-595-1767

Eastern Region:

(Regional Headquarters)

79 No. Franklin Turnpike Ramsey, New Jersey 07446 (201) 825-0990 TWX: 710-988-2254

214 W. Main Street Moorestown, New Jersey 08057 (609) 234-2844

474 Thurston Road, Suite D-5 Rochester, New York 14619 (716) 436-8330

69 Hickory Drive Waltham, Massachusetts 02154 (617) 890-7190

One Prestige Drive Meriden, Connecticut 06450 (203) 634-3253

1419 Forest Drive, Suite 102 Annapolis, Maryland 21403 (301) 263-0210

7130 So. Orange Blossom Trail Orlando, Florida 32809 (305) 857-0100

Midwestern Region

(Regional Headquarters) 262l Greenleaf Avenue Elk Grove Village, Illinois 60007 (312) 956-6400 TWX: 910-222-1839

29518 Five Mile Road Livonia, Michigan 48154 (313) 261-5170 or 5172

26777 Lorain Road No. Olmsted, Ohio 44070 (216) 777-8700

42 E. Rahn Road Kettering, Ohio 45429 (513) 434-5688 or 5689 Western Region 3315 Mercer Houston, Texas 77027 (713) 626-9430 TWX: 910-881-2568

2618 Electronics Lane, Suite 308 Dallas, Texas 75220 (214) 358-0278 TWX: 910-861-9102

3y0 120th Avenue, N.E. Building No. 2, Suite 210 Bellevue, Washington 98005 (206) 455-9650

706 No. Winchester Blvd. San Jose, California 95128 (408) 247-2026

Suite 100, #6 Garden Center Broomfield, Colorado 80020 (303) 466-1749

#### INTERNATIONAL

United Kingdom

CAI, Ltd. (Computer Automation)

31/35 Clarendon Road Watford, Hertfordshire WDI IJA (London) PH: Watford (0923) 39627 TLX: 851-922654

<u>Australia</u>

Original Equipment Sales Pty. Ltd. 63 Mitcham Road Donvale, Victoria 3111 PH: 873-2911 TLX: 790-34332

Austria UNITECHNIK Johnstrasse 45 A-1150, Wien (Vienna) PH: 90222) 42 10785 TLX: 47-13870

Belgium GEVEKE ELEKTRONIQUE ET AUTOMATION BELGIQUE SA 37-39, Quai sux Pierres de Taille 1000 - Bruxelles (Brussels) PH: 02-192-431 TLX: 846-23028

Computer Automation, Inc. 1255 University Street, Suite 309 Montreal 110, Quebec PH: 514/861-6155

$\frac{\texttt{Denmark}}{\texttt{SC METRIC A/S}}$ Skodsborgvej 305, 2850 Naerum Copenhagen PH: (01) 80-4200 TLX: 855-15763  $\frac{\textbf{Finland}}{\textbf{FINN METRIC OY}}$ Ahertajantic 6D 02100 Tapiola, SF-02100 ESPOS 10 Helsinki

GEVEKE ELEKTRONIK UND AUTOMATION GmbH & Co. 2 Norderstedt Gutenbergring 40 Postfach 1229 (Hamburg) PH: (040) 52 35 061

TLX: 841-2174297

Italy SILVERSTAR, LTD. S.p.a. 20, Via dei Gracchi 20146 Milano PH: 4996 TLX: 243-39189

Japan ELECTRO MARKETING Sanei Building 8 Saneicho, Shinjuku-ku Tokyo, 160 PH: 03-359-6247 TLX: 781-24952

Netherlands/Luxembourg GEVEKE ELEKTRONICA EN AUTOMATIE BV P.O. Box 652, Kabelweg 25 Amsterdam PH: 020-802802 TLX: 844-12219

New Zealand

TECHNICAL AGENCIES LTD.

383 Neilson Street P.O. Box 3727 CPO Auckland, 6 PH: 662-909, 662-919 TLX: 791-2901

Norway METRIC A.S. Postboks 80, Bekkelagshorgda PH: 02-282624 TLX: 856-18461

Philippines/Malaysia/Singapore

DATA SYSTEMS INTERNATIONAL INC. Rms. 619-620 MBCP Bldg. 313 Buendia Avenue Makati, Rizal (Manial) PH: 89-41-06 TLX: 762-3734

$\frac{South\ Africa}{COMPUTER}\ ADVANCES\ (PTY.)\ LTD.$ 51 Juta Street Braamfontein, Johannesburg PH: 724-9301 TLX: 960-430924

Spain ALFATRONICA Avenida de la Habana 137 Madrid 16 PH: 458-2969 TLX: 831-22397

Sweden SCANDIA METRIC AB Fack S-171 19 Solna 1 Stockholm PH: 08-82-04-10 TLX: 854-10766

Switzerland DATACARE AG Untere Bahnhafstr. 19 CH 9500 Wil (Zurich) PH: 073/22 05 92 TLX: 845-71440