PROGRAMMERS REFERENCE MANUAL

# PROGRAMMERS REFERENCE MANUAL

FOR THE

DDP-116

GENERAL PURPOSE COMPUTER

February 1966

Computer Control Company, Inc. Old Connecticut Path Framingham, Massachusetts COPYRIGHT 1966 by Computer Control Company, Incorporated, Framingham, Massachusetts. Contents of this publication may not be reproduced in any form, in whole or in part, without permission of the copyright owner. All rights reserved.

Printed in U.S.A.

# TABLE OF CONTENTS

| Paragraph                       | Title                               | Page  |

|---------------------------------|-------------------------------------|-------|

| ,                               | SECTION I<br>COMPUTER ORGANIZATION  |       |

| Specifications                  |                                     | 1-1   |

| System Description              |                                     | 1 - 3 |

| Word Formats                    |                                     | 1 - 5 |

| Data Words                      |                                     | 1-5   |

| Instruction Words               |                                     | 1 - 7 |

| Memory Addressing               |                                     | 1-10  |

| Sector Addressing               |                                     | 1-10  |

| Indexing                        |                                     | 1-10  |

| Indirect Addressing             |                                     | 1-11  |

| Instruction Logic and Timing    |                                     | 1-12  |

| S                               | SECTION II<br>STANDARD INSTRUCTIONS |       |

| Load and Store Instructions     |                                     | 2-1   |

| Arithmetic Instructions         |                                     | 2-4   |

| Logical Instructions            |                                     | 2-8   |

| Shift Instructions              |                                     | 2-8   |

| Control Instructions            |                                     | 2-17  |

| Input/Output Instructions       |                                     | 2-22  |

| Transfer of Control Instruction | s                                   | 2-24  |

|                                 | SECTION III<br>INPUT/OUTPUT         |       |

| Input/Output Control and Comm   |                                     | 3-1   |

| Single-Word Transfer Mo         |                                     | 3-3   |

| Standard Interrupt              |                                     | 3-5   |

| ASR-33 Teletype Unit (Standard  | 1)                                  | 3-7   |

| Keyboard and Carriage F         |                                     | 3-7   |

| Keyboard Interlock              |                                     | 3-7   |

| Tape Reader                     |                                     | 3-7   |

| Tape Punch                      |                                     | 3-9   |

| Off-Line Operation              |                                     | 3-9   |

| On-Line Operating Modes         |                                     | 3-9   |

| Character Modes                 |                                     | 3-10  |

| Instructions                    |                                     | 3-10  |

| Memory Protect                  |                                     | 3-10  |

# TABLE OF CONTENTS (Cont)

| Paragraph                   | Title                           | Page  |

|-----------------------------|---------------------------------|-------|

|                             | SECTION IV<br>OPTIONS           |       |

| Priority Interrupt Option,  | Model 116-25/26                 | 4-1   |

| Direct Multiplex Channel C  |                                 | 4-3   |

| Real Time Clock, Model 1    | 16-12                           | 4-5   |

| Applications                |                                 | 4-5   |

| Sensing and Control         |                                 | 4-6   |

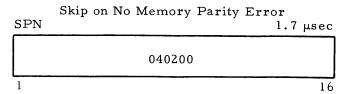

| Memory Parity, Model 116    | 0-07, 07-1                      | 4-6   |

| Optional Input and Output C | hannels, Models 116-32/33/34    | 4-7   |

| Parallel Input Channe       |                                 | 4-7   |

| Parallel Output Chan        | nel (Model 116-33)              | 4-8   |

| Parallel Buffered I/0       | Channel (Model 116-34)          | 4-8   |

| Direct Data Channel, Mode   | el 116-21                       | 4-10  |

| Power Failure Interrupt, 1  | Model 116-09                    | 4-10  |

| Watchdog Timer, Model 11    | 6-13                            | 4-11  |

| Applications                |                                 | 4-11  |

| Alarm Circuits              |                                 | 4-11  |

| Sensing and Control         |                                 | 4-12  |

| Memory Expansion, Model     | 4-12                            |       |

| JST Instruction Modi        | fication                        | 4-12  |

| Additional Instructio       | ns                              | 4-12  |

|                             | SECTION V<br>PERIPHERAL DEVICES |       |

| High-Speed Paper-Tape Ro    | eader, Model 116-50             | 5 - 1 |

| Reader Modes                |                                 | 5 - 1 |

| Codes                       |                                 | 5-1   |

| Specifications              |                                 | 5 - 1 |

| Sensing and Control         |                                 | 5-1   |

| High-Speed Paper-Tape Pu    | nnch, Model 116-52              | 5-3   |

| Specifications              |                                 | 5 - 3 |

| Sensing and Control         |                                 | 5-4   |

| Card Reader, Model 116-6    | 50                              | 5 - 5 |

| Modes of Operation          |                                 | 5 - 5 |

| Specifications              |                                 | 5-6   |

| Timing                      |                                 | 5-6   |

| Sensing and Control         |                                 | 5-8   |

| Operation                   |                                 | 5-9   |

# TABLE OF CONTENTS (Cont)

| Paragraph                              | Title                      | Page |

|----------------------------------------|----------------------------|------|

| Card Punch, Model 116-64               |                            | 5-10 |

| Specifications                         |                            | 5-10 |

| Timing                                 |                            | 5-12 |

| Sensing and Control                    |                            | 5-12 |

| Operating Notes                        |                            | 5-13 |

| Magnetic Tape Systems, Models 116-4    | 40, -41 and -42            | 5-14 |

| Modes of Operation                     |                            | 5-14 |

| Special Character Conversion           |                            | 5-17 |

| Timing                                 |                            | 5-17 |

| Specifications of Model 116-40 M       | TTM                        | 5-19 |

| Specifications of Models 116-41,       | /42 MTT                    | 5-19 |

| Tape Format                            |                            | 5-20 |

| MTT Parity Checking                    |                            | 5-20 |

| Sensing and Control                    |                            | 5-21 |

| Program Restriction                    |                            | 5-25 |

| Transport Operational Precaution       | ons                        | 5-25 |

| Line Printer, Model 116-67             | 5-26                       |      |

| Line Printer Operation                 |                            | 5-26 |

| Specifications                         |                            | 5-29 |

| Sensing and Control                    |                            | 5-30 |

| Timing                                 |                            | 5-32 |

| Operating Notes                        |                            | 5-32 |

|                                        | SECTION VI<br>PLE PROGRAMS |      |

| Fixed Point, Double Precision Add Sul  | broutine                   | 6-1  |

| Fixed Point, Double Precision Subtrac  | t Subroutine               | 6-2  |

| Fixed Point, Single Precision Multiply | Subroutine                 | 6-3  |

| Fixed Point, Single Precision Divide S | Subroutine                 | 6-5  |

| Output on ASR-33                       |                            | 6-7  |

| Paper Tape Read Subroutine             |                            | 6-7  |

| Output on High-Speed Paper Tape Pund   | eh                         | 6-8  |

| Line Printer Output Subroutine         |                            | 6-9  |

| Card Read (ASCII) Subroutine           |                            | 6-9  |

|                                        |                            |      |

# TABLE OF CONTENTS (Cont)

Title

Paragraph

2-3

2-4

2-5

2-6

2-7

2-8

Page

2-7

2-10

2-18

2-23

2-25

2-26

|                                                                     | SECTION VII<br>OPERATION                                    |         |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|-------------------------------------------------------------|---------|--|--|--|--|--|--|--|

| Control F                                                           | Panel                                                       | 7 - 1   |  |  |  |  |  |  |  |

|                                                                     | Registers                                                   | 7 - 1   |  |  |  |  |  |  |  |

|                                                                     | a Display                                                   | 7 - 1   |  |  |  |  |  |  |  |

|                                                                     | a Insertion                                                 | 7 - 1   |  |  |  |  |  |  |  |

| Memory                                                              | Location Data                                               | 7 - 3   |  |  |  |  |  |  |  |

| •                                                                   | gle Memory Location Data Display                            | 7 - 3   |  |  |  |  |  |  |  |

|                                                                     | cessive Memory Location Data Display                        | 7 - 3   |  |  |  |  |  |  |  |

|                                                                     | gle Memory Location Data Insertion/Change                   | 7 - 3   |  |  |  |  |  |  |  |

|                                                                     | cessive Memory Location Data Insertion/Change               | 7 - 4   |  |  |  |  |  |  |  |

|                                                                     | Procedure                                                   | 7-4     |  |  |  |  |  |  |  |

| A DDEND                                                             | IX A I/O Code Assignments                                   | A - l   |  |  |  |  |  |  |  |

| APPENDIX A I/O Code Assignments  APPENDIX B DDP-116 Character Codes |                                                             |         |  |  |  |  |  |  |  |

| APPENDIX C ASCII Code                                               |                                                             |         |  |  |  |  |  |  |  |

| APPENDIX D Instructions                                             |                                                             |         |  |  |  |  |  |  |  |

|                                                                     | LIST OF ILLUSTRATIONS                                       |         |  |  |  |  |  |  |  |

| Figure                                                              | Title                                                       | Page    |  |  |  |  |  |  |  |

| 1 - 1                                                               | DDP-116 General Purpose Computer, Simplified Block Diagram  | 1-4     |  |  |  |  |  |  |  |

| 1-2                                                                 | Data Word Format, Single Precision                          | 1-5     |  |  |  |  |  |  |  |

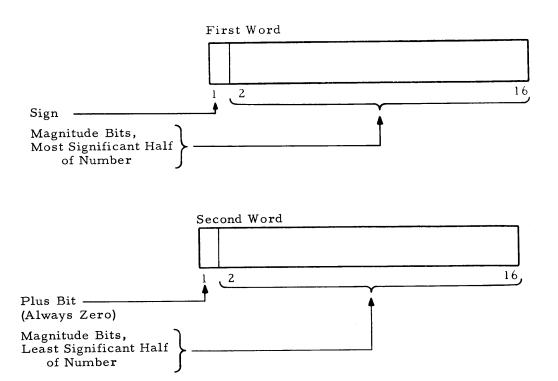

| 1 - 3                                                               | Data Word Format, Double Precision                          | 1-8     |  |  |  |  |  |  |  |

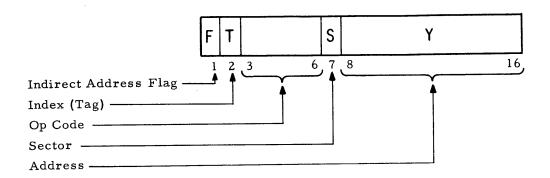

| 1-4                                                                 | Memory Reference Instruction Format                         | 1-8     |  |  |  |  |  |  |  |

| 1 -5                                                                | D. C. Turkwatiana                                           |         |  |  |  |  |  |  |  |

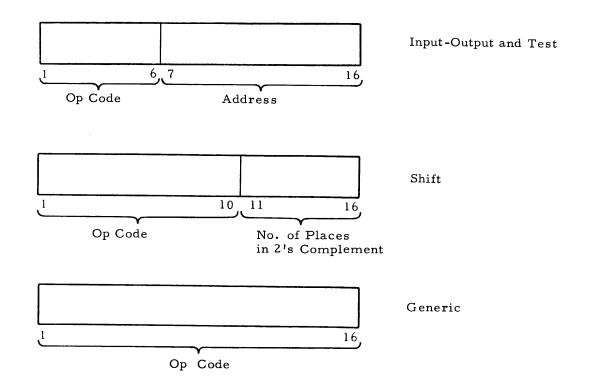

| 1-6                                                                 | Memory Sectors in 4096-Word DDP-116                         | 1-11    |  |  |  |  |  |  |  |

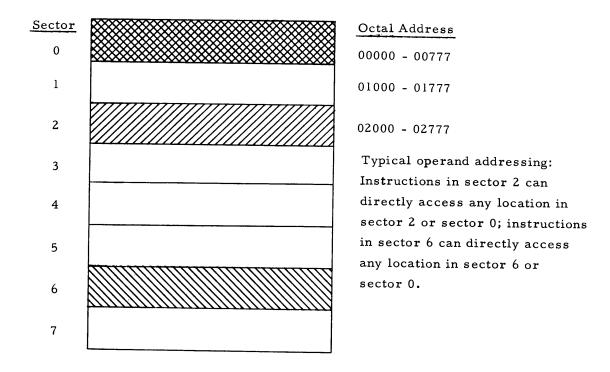

| 1 -7                                                                | Indirect Address Format                                     | 1 - 1 1 |  |  |  |  |  |  |  |

| 1-8                                                                 | Fetch, Indexing and Indirect Addressing, Logic Flow Diagram | 1-13    |  |  |  |  |  |  |  |

| 2-1                                                                 | STA, LDA, and IMA Instructions, Flow Diagram                | 2-2     |  |  |  |  |  |  |  |

| 2-2                                                                 | Add Instruction, Flow Diagram 2-                            |         |  |  |  |  |  |  |  |

IRS Instruction, Flow Diagram

CAS Instruction, Flow Diagram

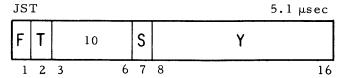

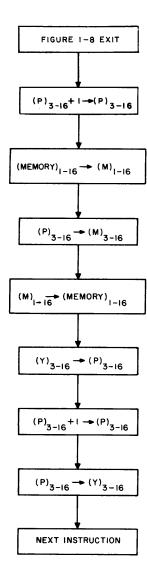

JST Instruction, Flow Diagram

Shift Instructions, General Flow Diagram

IOT Instructions, General Flow Diagram

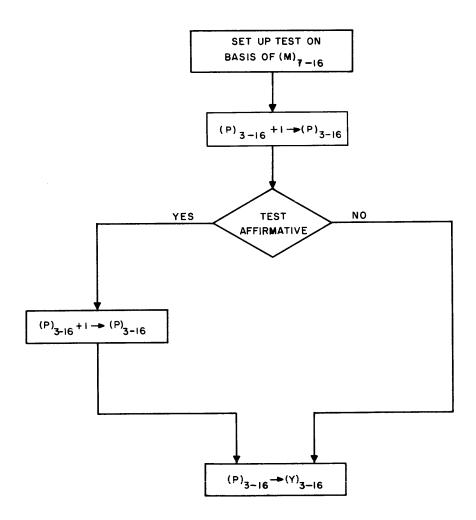

Skip Instructions, General Flow Diagram

# TABLE OF ILLUSTRATIONS (Cont)

| Figure       | Title                                                        | Page         |

|--------------|--------------------------------------------------------------|--------------|

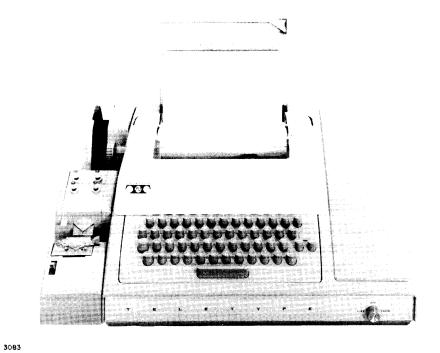

| 3-1          | ASR-33 Teletype Unit                                         | 3-8          |

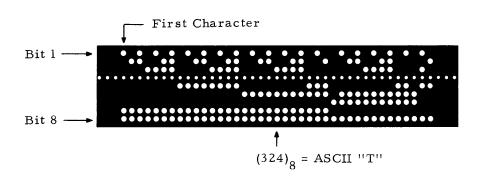

| 3-2          | DDP-116 Tape Format                                          | 3-8          |

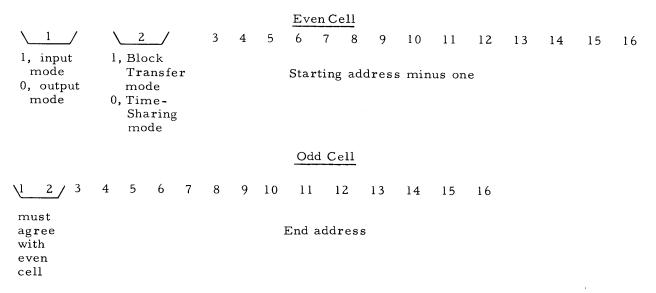

| 4-1          | DMC Control Word Format                                      | 4-5          |

| 4-2          | Alteration in Phase Sequence for 32K Memory Expansion        | 4-13         |

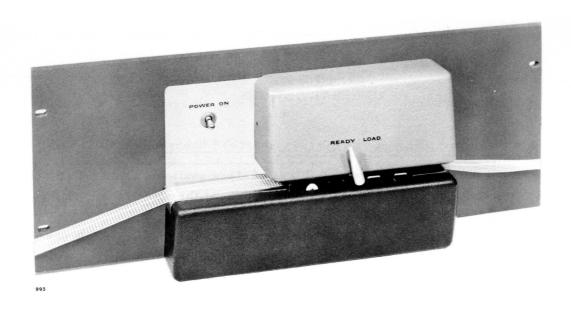

| 5 - 1        | High-Speed Paper-Tape Reader, Model 116-50                   | 5 - 2        |

| 5-2          | High-Speed Paper-Tape Punch, Model 116-52                    | 5-4          |

| 5-3          | Card Reader, Model 116-50                                    | 5-6          |

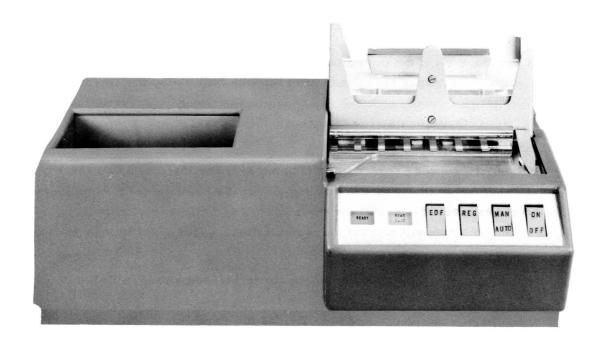

| 5-4          | Card Punch, Model 116-64                                     | 5-11         |

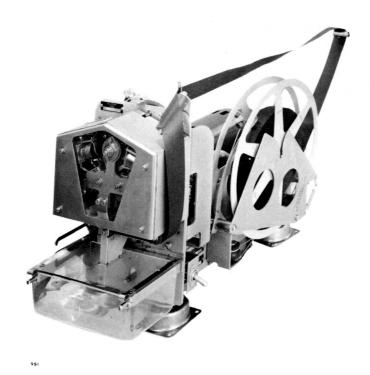

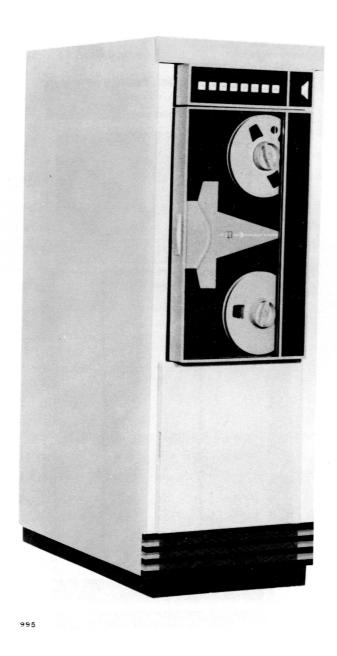

| 5 <b>-</b> 5 | Magnetic Tape Transport, Model 116-40                        | 5-15         |

| 5-6          | Magnetic Tape Transport, Models 116-41 and 116-42            | 5-16         |

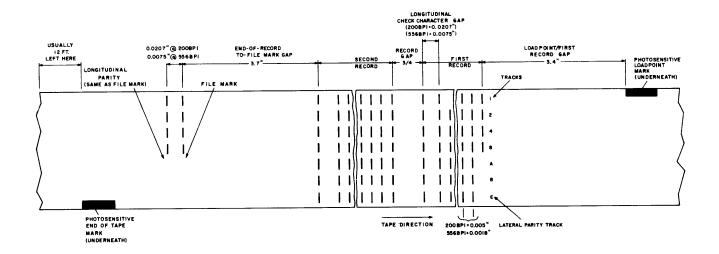

| 5 - 7        | Magnetic Tape Format                                         | 5-20         |

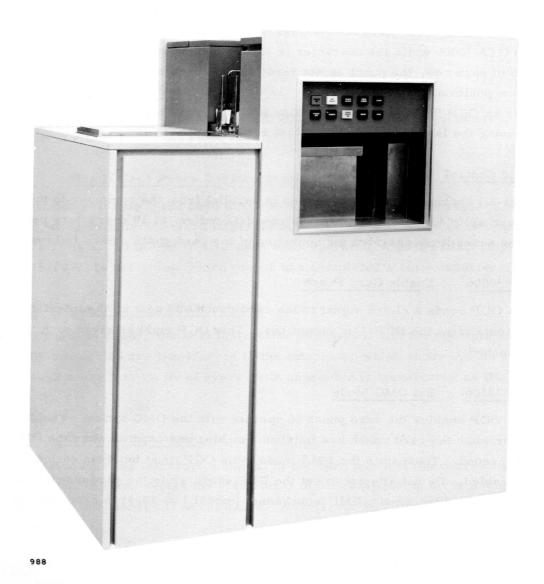

| 5-8          | Line Printer, Model 116-67                                   | 5-27         |

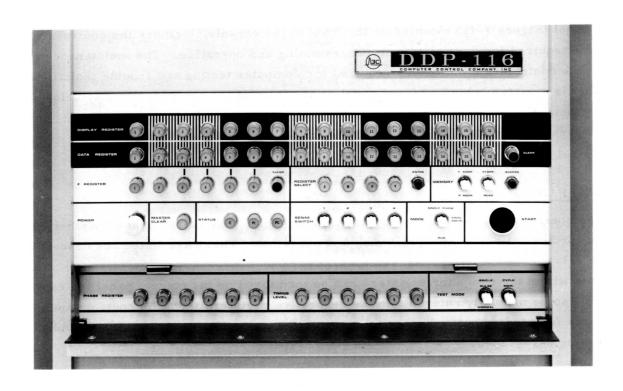

| 7 - 1        | DDP-116 Control Panel, Front View                            | 7 - 2        |

|              | LIST OF TABLES                                               |              |

| Table        | Title                                                        | Page         |

| 2 - 1        | Summary Description of DDP-116 Instructions                  | 2-30         |

| 2-2          | Symbol Glossary                                              | 2-36         |

| 3-1          | Input/Output Bus Lines                                       | 3-2          |

| 3-2          | Standard Interrupt Mask Assignments                          | 3-6          |

| 4-1          | Standard Locations for First Eight Groups of Interrupt Lines | 4 <b>-</b> 1 |

| 4-2          | Priority Interrupt Mask Assignments                          | 4-2          |

| 4-3          | DMC Standard Locations                                       | 4-4          |

| 4-4          | Additional I/O Bus Lines Required for DMC Option             | 4-4          |

| 5 - 1        | Card Code                                                    | 5 <b>-</b> 7 |

| 5 - 2        | ASCII and Magnetic Tape Codes                                | 5-18         |

| 7 - 1        | Control Panel Controls and Indicators and Their Functions    | 7-5          |

#### INTRODUCTION

This manual, one of a series of support documents for the DDP-116 General Purpose Digital Computer, provides the information normally required by a programmer in preparing and running programs on the computer.

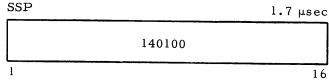

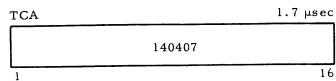

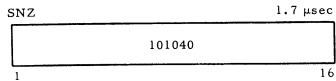

The DDP-116 is a low cost, 16-bit binary word general purpose digital computer with a 1.7-µsec memory cycle time and a standard 4096-word core memory. The DDP-116 has a fully parallel machine organization and both indexing and multilevel indirect addressing. Standard features include a flexible instruction repertoire of 62 commands, a powerful I/O bus structure, and standard Teleprinter keyboard and paper tape I/O unit. An extensive programming package, including a symbolic assembler, FORTRAN IV and diagnostic and utility routines, is provided with the basic DDP-116. Options include memory parity, a high-speed arithmetic option, direct multiplexed channel, a real-time clock and a full line of peripheral equipment.

The 16-bit word of the DDP-116 allows a straightforward and efficient addressing scheme. Most internal operations can be performed in two cycle times (3.4  $\mu$ sec), including instruction access and execution time. A single word instruction can directly address any one of 1024 words. The 16-bit word is directly compatible with the ASCII 8-bit character code.

The DDP-116 is designed for both open-shop scientific applications and real-time on-line data processing and control. Modular design, a flexible I/O structure, and command repertoire enable the DDP-116 to be tailored to a broad variety of applications both on and off line. These include data reduction, process control, instrumentation, simulation and open-shop scientific and engineering computation.

Programming the DDP-116 computer is similar to programming other single-address binary computers using two's complement notation. Therefore, no major differences confront the programmer who is new to the DDP-116. This manual also presents programming considerations in enough detail to satisfy the needs of a programmer who is new to single-address binary computers in general.

741

DDP-116 General Purpose Computer

# SECTION I COMPUTER ORGANIZATION

The DDP-116 General Purpose Computer is a solid-state, parallel, 16-bit binary machine with an internally stored program. The memory cycle time is conservatively rated at 1.7 µsec. Memory is available in 1024-, 4096-, and 8192-word modules and can be expanded to 32,768 words. The instruction repertoire includes 62 commands. An arithmetic option permits the addition of multiply, divide, and normalize hardware commands. A powerful sector addressing technique combined with large 512-word sectors permits the majority of instructions to be one word and maximizes memory efficiency. Multilevel indirect addressing and indexing are provided.

The input/output system includes a word parallel I/O bus system, an interrupt line, sense line, and 10 external function address lines. A paper tape reader, paper tape punch and a Teleprinter are provided as standard equipment. Software includes the DAP-116 assembler, FORTRAN IV, COP bugging system, I/O library, math library, and diagnostic programs. Support services include programming and maintenance training, logistic support program, maintenance services, and a user organization.

A full line of optional moderate and high-speed peripheral equipment is available. In addition, a line of compatible general-purpose logic modules (S-PACs) is available for system interface implementation.

## **SPECIFICATIONS**

Type

Parallel binary, solid state

Addressing

Single address with indexing and indirect addressing

Word Length

16 bits

Machine Code

Two's complement

Memory Type

Coincident-current ferrite core

Memory Size

1024-, 4096-, or 8192-word basic modules expandable to 32,768 words

Memory Cycle Time

1.7 µsec

#### Speed

Add 3.4 µsec

Subtract 3.4 µsec

Multiply (subroutine) 243 µsec

Divide (subroutine) 336 µsec

Multiply (hardware option) 9.18 µsec maximum

Divide (hardware option) 16.67 µsec maximum

# Standard Peripheral Equipment

ASR-33 Teletype Unit providing the following capabilities:

- a. Read paper tape at 10 cps

- b. Punch tape at 10 cps

- c. Print at 10 cps

- d. Keyboard input

- e. Off-line paper-tape preparation, reproduction and listing

#### Optional Peripheral Equipment

300 cps photoelectric paper-tape reader

110 cps paper-tape punch

300-line-per-minute (120-character-per-line) high-speed printer

100-card-per-minute card reader

100-card-per-minute card punch

IBM compatible magnetic tape units:

| Unit       | Tape Speed (ips) | Density (bpi) |

|------------|------------------|---------------|

| Low speed  | 45               | 200, 556      |

| High speed | 75               | 200, 556, 800 |

#### Standard Input/Output Lines

16-bit input bus

16-bit output bus

10-bit device address bus

External control and sense lines

# Input/Output Modes

Four modes are available for data transfer between peripheral devices and the DDP-116.

- a. Single word transfer

- b. Single word transfer with priority interrupt

- c. Direct multiplexed channel (DMC) (optional)

- d. Direct data channel (DDC) (optional)

#### Interrupt

Single interrupt line standard. Optional priority interrupts are available in multiples of eight up to a maximum of 256 lines.

#### Circuits

Computer Control Company standard S-PAC Digital Modules

#### Signal Levels

Zero volt for logical ZERO; -6v for logical ONE

#### Dimensions

22-1/16 in. wide; 22-1/16 in. deep; 68-13/16 in. high

### Weight

Approximately 500 lb (standard single-bay machine)

#### Cooling

Filtered, forced convection cooling provided within cabinet

#### Power

Single-phase,  $115v \pm 10v$ , 60 cycles

#### SYSTEM DESCRIPTION

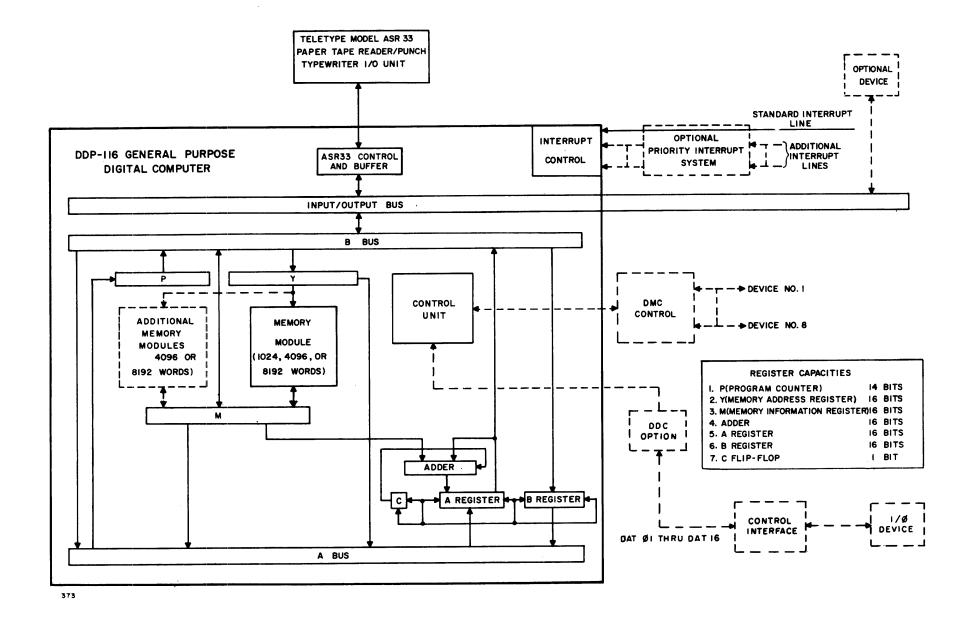

Figure 1-1, a block diagram of the DDP-116, shows the data storage registers, the control unit of the central processor and the input/output controls. The random access memory, shown as a single block, is a magnetic core unit containing one or more modules of 1024, 4096, or 8192 16-bit words. Data from the core memory is transferred to and from the DDP-116 registers through the M-register and the A- and B-buses. The DDP-116 memory can be expanded to include up to 16,384 16-bit words, or up to 32,768 words by means of the extended addressing option.

The functional units of the central processor and the input/output controls are as follows:

A-Register (A): A 16-bit register used as the primary arithmetic and logic register of the computer.

B-Register (B): A 16-bit secondary arithmetic register used primarily to hold arithmetic operands which exceed one word in length.

Program Counter (P): A 14-bit counter that contains the location of the next instruction to be executed. The program counter is incremented by one each time an instruction is performed and may be incremented additional times during the execution of conditional skip instruction. In the case of a jump, the program counter is loaded with the memory location to which the program is to jump.

Adder: Performs the basic arithmetic processes of addition and subtraction.

$\underline{\text{M-Register}}$  (M): A 16-bit register used to transfer information to and from the magnetic core memory.

Y-Register (Y): A 16-bit register used to store the address for the memory.

C-Bit Flip-Flop: The C-bit flip-flop, associated with the A- and B-registers, stores overflow indications occurring during the execution of arithmetic instructions, and can be tested by sense instructions in connection with shifting operations.

Figure 1-1. DDP-116 General Purpose Computer, Simplified Block Diagram

F-Register: A 6-bit register that contains the indirect address bit, index bit, and 4-bit operation code.

A-Bus and B-Bus: Two gating structures to which the computer registers and counters are connected both as source and destination. Transfer of information from one register or counter to another is effected by the simultaneous gating of the proper paths from one register to a bus, and from the bus to the other register.

Output Bus (OTB): Sixteen lines that transmit data from the computer B-bus to an I/O device.

Input Bus (INB): Sixteen lines that transmit data from an I/O device to the computer B-bus.

Address Bus (ADB): Ten lines used in conjunction with I/O devices. Bits on lines 1 through 4 define the function to be performed by the I/O device. Bits on lines 5 through 10 designate the I/O device to be used.

<u>Control Clock:</u> The control clock generates timing pulses required for the operation of the computer.

## WORD FORMATS

#### Data Words

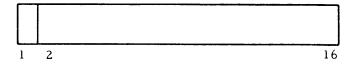

The format for data words stored in the DDP-116 is shown in Figure 1-2.

Figure 1-2. Data Word Format, Single Precision

Sixteen-bit data words are stored in two's complement form. The first bit of a data word represents the sign and is zero for positive data. Bits 2 to 16 represent the magnitude in true binary form. Positive values thus range from zero (which always has a positive sign) to 32,767 as follows:

Negative numbers are represented in two's complement form and always have a one in the sign bit position.

Two's Complement Arithmetic. -- The two's complement of a binary number is obtained by complementing (reversing) each bit and adding one. For example, the two's complement of +1, which represents -1, is obtained as follows:

The number range for negative values is from -1 to -32,768 as follows:

While -1 has the largest magnitude of any negative number, if +1 is added to it, the result is zero. Thus:

Note that a carry bit from the most significant position has been ignored. In two's complement arithmetic, if numbers of unlike signs are added together, carries from the most significant bit are disregarded.

Overflow. -- Overflow is the condition that occurs when two number of like signs are added together to produce a sum of a different sign. For example, adding +1 to +32,767 would produce a result larger than the capacity of a single data word.

The different sign of the result defines an overflow condition.

Addition on the DDP-116 is performed by adding a quantity in the memory to a quantity in the A-register. True signed arithmetic takes place. Overflow conditions automatically result in the setting of the C-bit indicator, even though no carry is propagated from the sign position. In the preceding example, the C-bit indicator would be set.

<u>Double Precision.</u> -- When further precision is required than that obtainable from a data word, the double precision format is used (Figure 1-3). The sign position of the second (least significant) word is always zero. Thirty bits of magnitude are obtainable. This is the format for the product of the multiplication of two single precision words. It is also the data format for double precision subroutines. An example of a double precision addition is shown in Section

Logical Data. -- Logical data, such as the condition of sixteen binary switches, can be stored in a single data word. This type of data is generally not treated arithmetically by the program but logically by means of Boolean operators such as "AND" and "exclusive OR." In this case, bit 1 of a word does not represent the sign but the first of sixteen conditions.

#### Instruction Words

Instruction words are divided into two types: non-memory reference and memory reference.

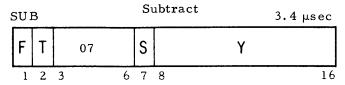

The basic instruction word format in the DDP-116 is that for a memory reference instruction, which is shown in Figure 1-4. Bits 3 to 6 contain the operation code, which defines the function to be performed. For example, if bits 3 to 6 contain 0110, the instruction is identified as an add instruction; if they contain 1011, the instruction is a compare. For ease of communication, operation codes are generally expressed either in octal or as a mnemonic. "Subtract," for example, which has an op-code bit configuration of 0111, is referenced in machine language as (07)<sub>8</sub> and has a mnemonic of SUB. The latter is the way the programmer writes an op code when programming in DAP, the DDP-116 assembly language. The table below shows the op codes expressed in binary, octal, and mnemonically for representative instructions of each type.

|                          |                             |                       | Opera  | tion Code |

|--------------------------|-----------------------------|-----------------------|--------|-----------|

| Instruction              | $\underline{\mathtt{Type}}$ | Binary                | Octal  | Mnemonic  |

| Subtract                 | Memory<br>Reference         | x x01 llx xxx xxx xxx | 07     | SUB       |

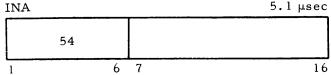

| Input to A               | Input/Output                | l 011 00x xxx xxx xxx | 54     | INA       |

| Arithmetic<br>Left Shift | Shift                       | 0 100 001 101 xxx xxx | 0415   | ALS       |

| Clear A                  | Generic                     | 1 100 000 000 100 000 | 140040 | CRA       |

Certain configurations in bits 3 to 6 are interpreted to signify not a single instruction but a group of instructions. Further decoding of other bits is necessary to uniquely identify the instruction. Instead of using 4 bits to identify the operation code (as in the memory reference instruction) 6, 10, or all 16 bits are utilized for identification. These operation codes identify non-memory reference instructions.

Figure 1-3. Data Word Format, Double Precision

Figure 1-4. Memory Reference Instruction Format

Non-Memory Reference Instructions. -- The non-memory reference instructions are subdivided into three types, each type having its own unique format. These types are:

- a. Input-output and test (6-bit op code)

- b. Shift (10-bit op code)

- c. Generic (16-bit op code)

Their formats are shown in Figure 1-5.

Figure 1-5. Formats of Non-Memory Reference Instructions

Memory Reference Instructions. -- The DDP-116 is a single address computer and can access one operand in memory with each instruction. For example, to add the contents of memory address X to the contents of memory address Y and put the sum in memory address Z requires three instructions, one to address each of the three factors. The program to do this is expressed mnemonically as

LDA X

ADD Y

STA Z

The first instruction loads the A-register with the data in address X, the second adds the data in address Y to it, and the third stores the contents of the A-register (the sum) in location Z.

Memory reference instructions in the DDP-116 (see Figure 1-4) are extremely flexible in their addressing capability and can directly reference large portions of memory in a single cycle. All the bits in the instruction except for the op-code bits are utilized in various forms of addressing. These bits are:

- a. Bit 1, indirect address bit (FLAG)

- b. Bit 2, index bit (TAG)

- c. Bit 7, sector bit

- d. Bits 8-16, address bits

The use of these bits is described after the general description of memory addressing.

## MEMORY ADDRESSING

Several techniques are used in the DDP-116 for memory addressing; sector addressing, indexing and indirect addressing.

## Sector Addressing

The memory of the DDP-116 is considered to be divided into sectors of 512 words each. A 4096-word computer will have 8 sectors; and 8192-word computer, 16. Any word in a sector can be addressed with 9 bits ( $2^9 = 512$ ). The address portion of a memory reference instruction (bits 8 to 16) can thus define a unique word in a sector. Addresses within sectors run from  $(000)_8$  to  $(777)_8$ . The sector bit, bit 7 of the instruction, identifies the sector of the word addressed in accordance with the following rules:

Sector Bit = 0 The address is in sector 0 (octal address 000-777).

Sector Bit = 1 The address is in the same sector as the instruction being executed.

For example, assume an ADD 444 instruction is in address (02100)<sub>8</sub>, or sector 2 word 100. If the sector bit in the instruction is 0, the instruction references word 444 in sector 0, or (00444)<sub>8</sub>. If the sector bit is 1, then the instruction references word 444 in sector 2, or (02444)<sub>8</sub>, because the instruction itself is in sector 2.

A single instruction can thus directly address 1024 words in two sectors of memory, half of which are in sector 0 and half of which are determined by the location of the instruction. Figure 1-6 represents the memory that can be directly addressed by an instruction in sector 2 and an instruction in sector 6.

#### Indexing

Further addressing flexibility is implemented on the DDP-116 through the use of indexing. The index "register" is a 16-bit word in memory location 0 whose contents can be added to the direct address of an instruction to produce a new effective operand address. Indexing is specified by putting a one in bit 2 of a memory reference instruction. In assembly language, indexing is specified by placing a comma followed by a one after the operand (that is, ADD B, 1).

Figure 1-6. Memory Sectors in 4096-Word DDP-116

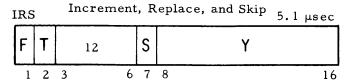

The value in the index register can be positive or negative. If negative, the effective address is less than the base (instruction) address. The latter is the usual means of utilizing the index register when controlling program loops; each time through the loop the negative content of the index register is incremented by one by means of an IRS (increment, replace and skip) instruction. When the index register reaches zero, the program automatically breaks out of the loop.

#### Indirect Addressing

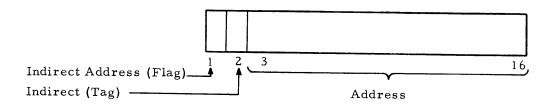

If bit 1 of a memory reference instruction is set, indirect addressing takes place. When indirect addressing is specified, the effective address of the operand is assumed to be in the location specified by the address portion of the instruction and the sector bit. The format of the indirect address location is shown in Figure 1-7.

Figure 1-7. Indirect Address Format

To illustrate indirect addressing, consider that an add command in sector 2 is flagged for indirect addressing (this is specified in DAP by placing an asterisk after the op code).

ADD\* 444

Location 444 contains

(06231)<sub>8</sub>

The effective address would then be (06231)<sub>8</sub>, which is in sector 6. Its contents would be added to the A-register.

If the indirect bit within an indirect address location is set, a further level of indirect addressing takes place. This chaining of indirect addresses can continue indefinitely.

If both the indirect bit and the index bit are set in an instruction, indexing takes place first. To have indexing occur after indirect addressing (that is, the effective address is the sum of the indirect address and the contents of the index register), the index bit is set in the indirect location.

Indirect addressing thus enables an instruction to address 16K of memory. With the memory extension option 116-15, indirect addressing of 32K memory is possible.

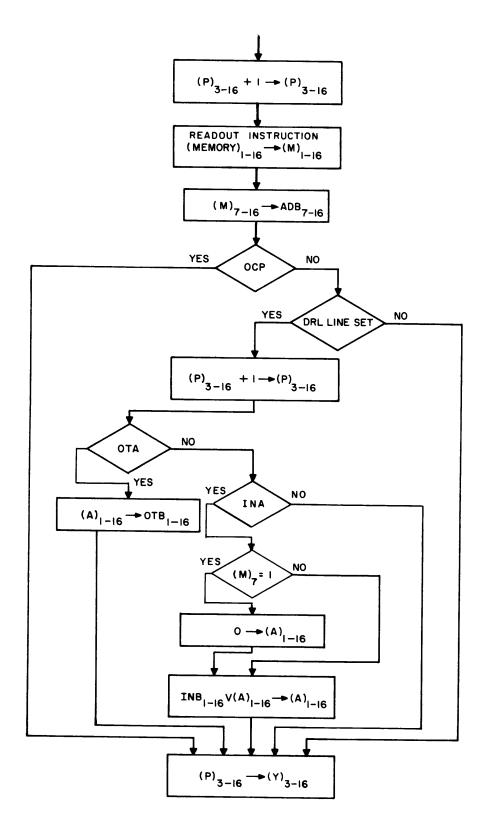

#### INSTRUCTION LOGIC AND TIMING

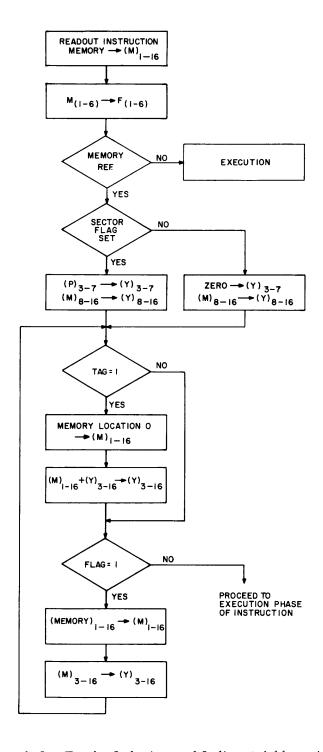

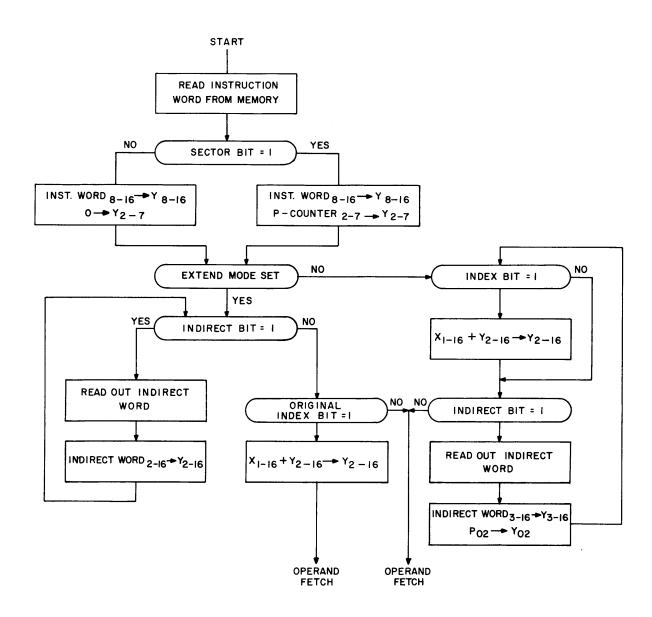

Figure 1-8 is a logic flow diagram of the fetch, indexing and indirect addressing phases of an instruction. Initially, the P-register (program counter) contains the address of the instruction to be executed. The Y-register (memory address) also contains the same address. The instruction in the address specified by Y is then read out of memory into the M-register (memory information), and the first 6 bits are transferred from M into the F-register.

Assuming that the instruction is a memory reference instruction such as an add, the sector bit is next examined. If set, the first 5 bits of the P-register (the sector the instruction came from) are put into the Y-register together with the least significant 9 bits from M (the address portion of the instruction). If the sector bit is not set, zeroes are put in the first 5 bits of the Y-register.

If the instruction is neither indexed nor indirect addressed, the Y-register now contains the effective address of the operand, and the processor proceeds to the execution phase of the command. One memory cycle, or 1.7  $\mu$ sec, has been utilized thus far.

If indexing is called for, the contents of the index register are added to the address in Y. This adds 2.04  $\mu sec$  to the instruction timing.

Following indexing, the indirect bit is examined. If set, the contents of the address specified by Y are read into the M-register and the 14 least significant bits transferred to Y. The processor then executes further indexing and indirect cycles if necessary. Every level of indirect addressing adds 1.7  $\mu$ sec to the execution time.

After all levels of indexing and indirect addressing have been completed, the processor proceeds to the execution phase of the instruction. The execution phase of each instruction is described in the following section. During the execution of most instructions, the P-register is incremented by one, and its contents are transferred to Y to set up the fetch of the next instruction.

All data transfers in the DDP-116 are effected in parallel. Thus the execution of most instructions such as load, store, add, or subtract are accomplished in one cycle. The times listed for each instruction include fetching the instruction and executing it but do not include indexing and indirect addressing time.

Figure 1-8. Fetch, Indexing and Indirect Addressing, Logic Flow Diagram

#### SECTION II STANDARD INSTRUCTIONS

Contained in this section are descriptions of all standard DDP-116 instructions, grouped within the following functional categories: load and store, arithmetic, logical, shift, control, input/output, and transfer of control. The descriptions include the following information:

- a. The 3-letter mnemonic assigned to the instruction

- b. The time required to execute the instruction, including memory access of the instruction and operand, as applicable. Add 1.7  $\mu$ sec to the listed time for each level of indirect addressing, and add 2.04  $\mu$ sec for each use of indexing.

- c. The effect of the instruction

- d. Indicators affected by the instruction, where applicable

- e. The type of instruction (memory reference, IOT, shift, or generic)

The type of the instruction determines the number of bits that must be used to specify the instruction (4 for memory reference instructions, 6 for IOT instructions, 10 for shift instructions, and 16 for generic instructions). Additionally, if the instruction is a memory reference type, the flag, tag, and sector bits (bits 1, 2, and 7) will function as described in Section I.

Flow diagrams showing the instruction execution process are provided where necessary. Table 2-1 at the end of this section contains summary descriptions of the instructions, listed in alphabetical order. Table 2-2 contains definitions of symbols and abbreviations.

#### LOAD AND STORE INSTRUCTIONS

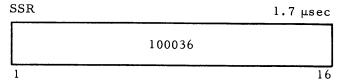

| CRA | Clear A | l.7 μsec |

|-----|---------|----------|

|     | 140040  |          |

| 1   |         | 16       |

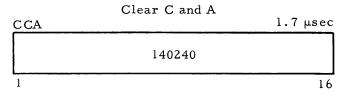

DESCRIPTION: The contents of the A-register, bits 1 through 16, are cleared to ZEROs. TYPE: Generic

DESCRIPTION: The contents of the C-bit and the A-register, bits 1 through 16, are cleared to ZEROs.

TYPE: Generic

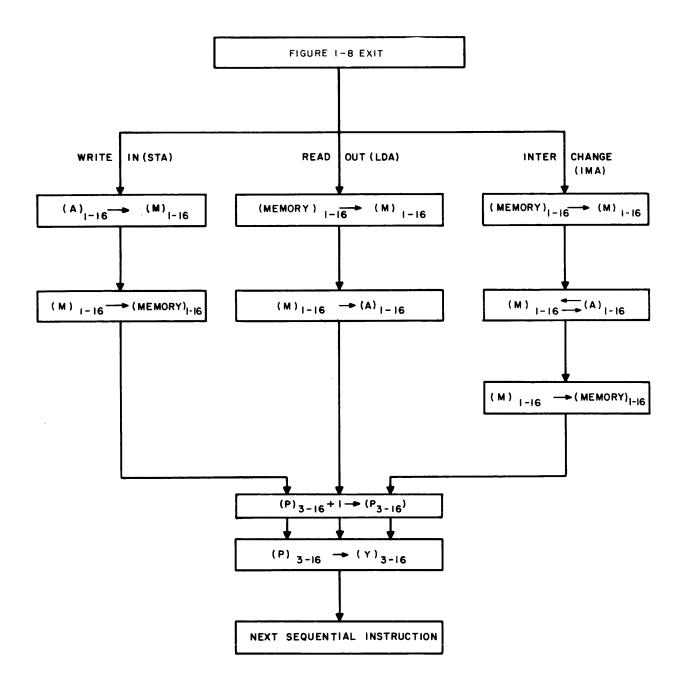

Figure 2-1. STA, LDA, and IMA Instructions, Flow Diagram

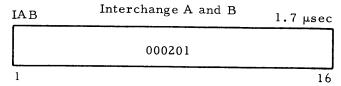

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 1 through 16, are interchanged.

TYPE: Generic

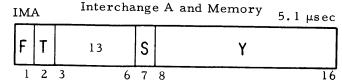

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the effective operand address in memory, bits 1 through 16, are interchanged. (See Figure 2-1.) TYPE: Memory reference

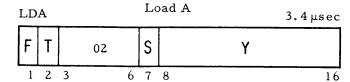

DESCRIPTION: The contents of the effective operand address in memory, bits 1 through 16, replace the contents of the A-register, bits 1 through 16. The contents of the effective operand address in memory, bits 1 through 16, remain unchanged. (See Figure 2-1.) TYPE: Memory reference

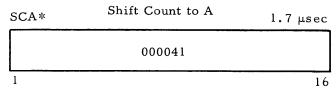

DESCRIPTION: The SCA instruction is used to store the contents of the shift counter in the A-register, bits 12 through 16. Bits 1 through 11 of the A-register are cleared. The shift counter is utilized by the multiply-divide and normalize instructions. Therefore, the contents of the shift counter must be extracted, if pertinent, prior to any subsequent use of the MPY, DIV, or NRM instructions.

TYPE: Generic

<sup>\*</sup>Optional

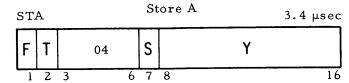

DESCRIPTION: The contents of the A-register, bits 1 through 16, replace the contents of the effective operand address in memory, bits 1 through 16. The contents of the A-register are unchanged. (See Figure 2-1.)

TYPE: Memory reference

#### ARITHMETIC INSTRUCTIONS

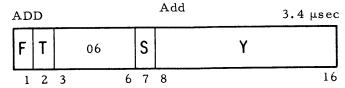

DESCRIPTION: The contents of the A-register, bits 1 through 16, are algebraically added to the contents of the effective operand address in memory, bits 1 through 16. The resultant sum replaces the contents of the A-register, bits 1 through 16. If overflow occurs, the C-bit is set and the computer proceeds to the next sequential instruction. The C-bit is reset if overflow does not occur. (See Figure 2-2.)

TYPE: Memory reference

INDICATORS: C-STATUS indicator lights to indicate overflow.

| DIV*  |    | Divide | 15.5 μsec avg<br>16.67 μsec max |

|-------|----|--------|---------------------------------|

| FT    | 17 | S      | Υ                               |

| 1 2 3 | 6  | 7 8    | 16                              |

DESCRIPTION: The contents of the effective operand address in memory, bits 1 through 16, are divided into the contents of the combined A- and B-registers. The sign and the most significant half of the dividend is contained in the A-register, bits 1 through 16. The least significant half of the dividend is contained in the B-register, bits 2 through 16. The 16-bit quotient replaces the contents of the A-register, bits 1 through 16. The remainder replaces the contents of the B-register, bits 2 through 16. Bit 1 of the B-register is set to ZERO. With one exception, if the initial magnitude of the A-register is equal to or greater than the contents of the effective operand address in memory, the C-bit is set and the computer proceeds to the next sequential instruction. The exception is the case where the contents of the A-register and operand address are equal and opposite in sign, the A-register having the negative sign. For this case division is valid and the C-bit is not set. The C-bit is reset if an illegal divide does not occur.

\*Optional

Figure 2-2. Add Instruction, Flow Diagram

TYPE: Memory reference

INDICATORS: C-STATUS indicator lights to indicate overflow.

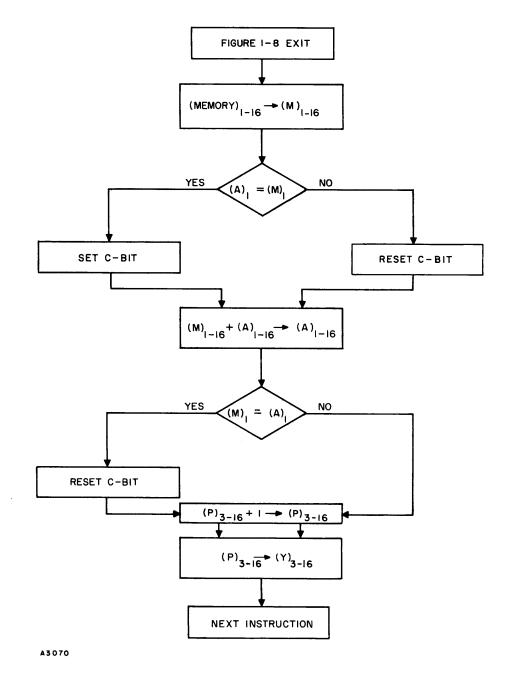

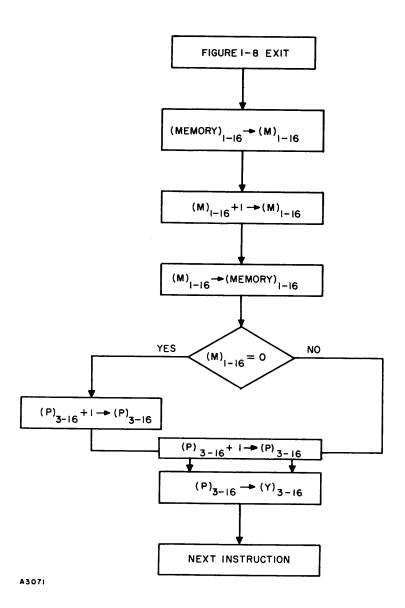

DESCRIPTION: The contents of the effective operand address in memory, bits 1 through 16, are incremented by 1 and the resulting sum replaces the contents of the effective operand address in memory, bits 1 through 16. If the result of the incrementation is ZERO, the next sequential instruction is skipped. Otherwise, the next sequential instruction is executed. (See Figure 2-3.)

TYPE: Memory reference

| MF | MPY* |   |    | Multiply<br> |   |   |   | 9.18 µsec |  |  |

|----|------|---|----|--------------|---|---|---|-----------|--|--|

| F  | Т    |   | 16 |              | S |   | Υ |           |  |  |

| 1  | 2    | 3 |    | 6            | 7 | 8 |   | 16        |  |  |

DESCRIPTION: The contents of the A-register, sign and bits 2 through 16, are multiplied by the contents of the effective operand address in memory, sign and bits 2 through 16, forming a 30-bit product. The A-register, sign and bits 2 through 16, contain the most significant part of the product. The B-register, bits 2 through 16, contains the least significant part of the product. Bit 1 of the B-register is set to ZERO. There is no overflow indication on this instruction.

TYPE: Memory reference

DESCRIPTION: The contents of the effective operand address in memory, bits 1 through 16, are algebraically subtracted from the A-register, bits 1 through 16. The resultant difference replaces the contents of the A-register, bits 1 through 16. If overflow occurs, the C-bit is set and the computer proceeds to the next sequential instruction. The C-bit is reset if overflow does not occur.

TYPE: Memory reference

INDICATORS: C-STATUS indicator lights to indicate overflow.

\*Optional

Figure 2-3. IRS Instruction, Flow Diagram

#### LOGICAL INSTRUCTIONS

| A | ANA |   |   |    | Logical AND |   |   | 3.4 µsec |    |

|---|-----|---|---|----|-------------|---|---|----------|----|

|   | F   | Т |   | 03 |             | S |   | Y        |    |

| L | 1   | 2 | 3 |    | 6           | 7 | 8 |          | 16 |

DESCRIPTION: The logical product of the contents of the A-register, bits 1 through 16, and the contents of the effective operand address in memory is formed and the result replaces the contents of the A-register, bits 1 through 16. A ZERO is placed into the corresponding bit position in the A-register for each ZERO in the contents of the effective operand address in memory. The contents of the corresponding bit positions in the A-register are unchanged for each ONE in the contents of the addressed memory location. The contents of the addressed memory location are unchanged.

TYPE: Memory reference

| ERA |               |   |   |    | Ex | clu | sive OR | 3.4 µsec |    |  |

|-----|---------------|---|---|----|----|-----|---------|----------|----|--|

|     | F             | Т |   | 05 |    | S   |         | Y        |    |  |

|     | $\overline{}$ | 2 | 3 |    | 6  | 7   | 8       |          | 16 |  |

DESCRIPTION: The logical difference of the contents of the A-register, bits 1 through 16, and the contents of the effective operand address in memory, bits 1 through 16, is formed and the result replaces the contents of the A-register. The contents of the corresponding bit position of the A-register is complemented for each ONE in the contents of the addressed memory location. The corresponding bit of the A-register is unchanged for each ZERO in the contents of the addressed memory location. The contents of the addressed memory location, bits 1 through 16, are unchanged.

TYPE: Memory reference

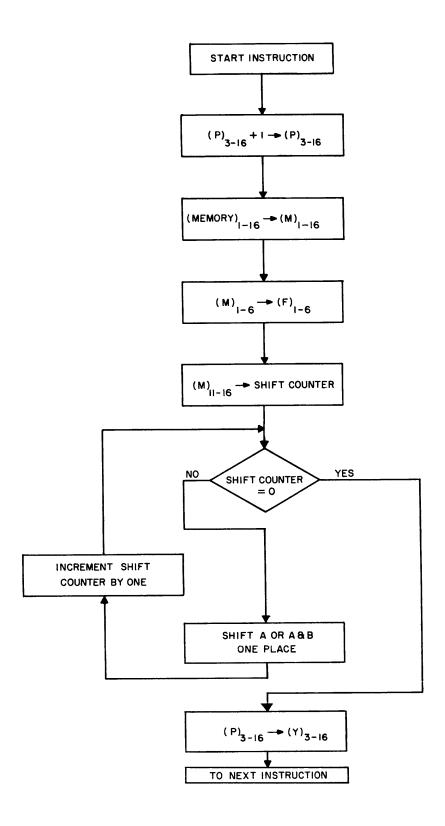

# SHIFT INSTRUCTIONS (See Figure 2-4.)

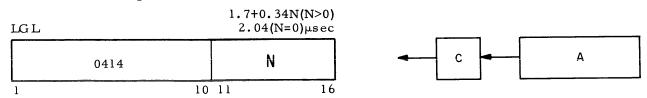

#### Logical Left Shift

DESCRIPTION: The contents of the A-register, bits 1 through 16, are shifted left through the C-bit the number of positions specified in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of the A-register are lost and ZEROs are shifted into the vacated positions of the register. Each bit shifted out of the A-register enters the C-bit. A maximum shift of 63-bit positions may be specified. If a shift greater than 15 is specified, bits 1 through 16

of the A-register will be ZERO. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

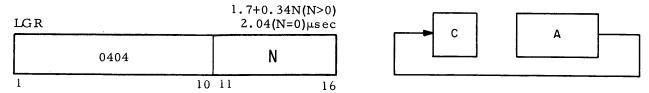

Logical Right Shift

DESCRIPTION: The contents of the A-register, bits 1 through 16, are shifted right through the C-bit the number of positions specified in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of the A-register are lost and ZEROs are shifted into the vacated positions of the register. Each bit shifted out of the A-register enters the C-bit. A maximum shift of 63 bit positions may be specified. If a shift greater than 15 is specified, bits 1 through 16 of the A-register will be ZERO. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction .

Logical Left Rotate

DESCRIPTION: The contents of the A-register, bits 1 through 16, are rotated to the left (end around carry) the number of positions specified in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of bit position 1 of the A-register enter bit position 16 of the A-register. Each bit shifted out of bit position 1 of the A-register enters the C-bit. A maximum shift of 63-bit positions may be specified. If a shift of greater than 15-bit positions is specified, the net result of the shift is modulo 15. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

Figure 2-4. Shift Instructions, General Flow Diagram

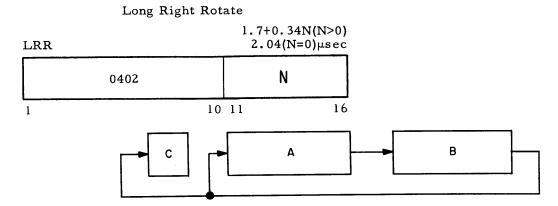

#### Logical Right Rotate

DESCRIPTION: The contents of the A-register, bits 1 through 16, are rotated to the right (end-around carry) the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of bit position 16 of the A-register enter bit position 1 of the A-register. Each bit shifted out of bit position 16 of the A-register enters the C-bit. A maximum shift of 63-bit positions may be specified. If a shift greater than 15 is specified, the net result of the shift is modulo 15. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

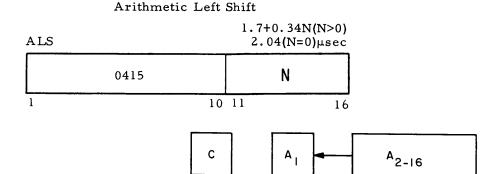

DESCRIPTION: The contents of the A-register, bits 1 through 16, are shifted left the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. The C-bit indicates an overflow in this instruction. It is set if the sign bit (bit 1) is altered during execution of the instruction and reset if the sign bit is not altered. Bits shifted out of the A-register are lost and ZEROs are shifted into the vacated positions of the register. A maximum shift of 63 bit positions may be specified. If a shift greater than 15 is specified, bits 1 through 16 of the A-register will be ZERO. The number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights to indicate overflow.

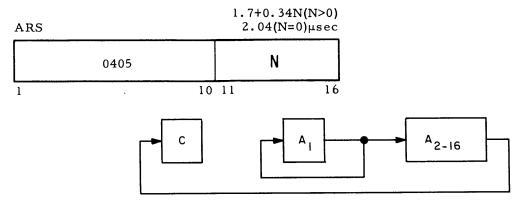

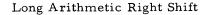

## Arithmetic Right Shift

DESCRIPTION: The contents of the A-register, bits 1 through 16, are shifted right through the C-bit the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. The sign bit, bit 1, of the A-register does not change. The sign bit (bit position 1) is shifted into the vacated positions of the A-register. Each bit shifted out of the A-register enters the C-bit. A maximum shift of 63 bit positions may be specified. If a shift greater than 14 is specified, bits 2 through 16 of the A-register will be the same as the sign. However, the number of actual shifts performed equals the number specified by the instruction. The sign bit remains as it was prior to the execution of the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

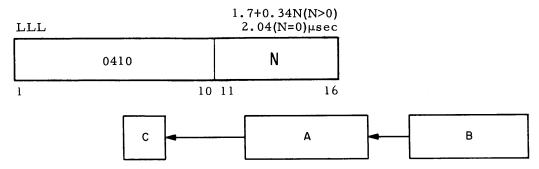

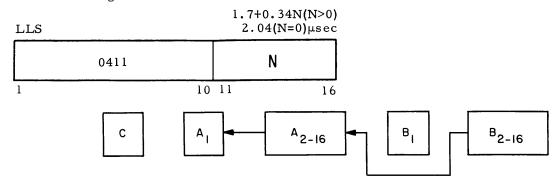

Long Left Logical Shift

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 1 through 16, are treated as a single 32-bit register. These bits are shifted to the left through the C-bit the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of the bit position 1 of the B-register enter bit position 16 of the A-register. Bits shifted out of bit position 1 of the A-register, through the C-bit, are lost. Each bit shifted out of bit position 1 of the A-register enters the C-bit. ZEROs are shifted into the vacated positions of the A- and B-registers through bit position 16 of the B-register.

A maximum shift of 63 bit positions may be specified. If a shift greater than 31 is specified, bits 1 through 16 of the A- and B-registers will be ZERO. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

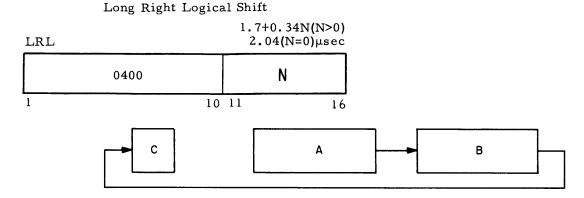

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 1 through 16, are treated as a single 32-bit register. These bits are shifted to the right through the C-bit the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of bit position 16 of the A-register enter bit position 1 of the B-register. Bits shifted out of bit position 16 of the B-register, through the C-bit, are lost. Each bit shifted out of the B-register enters the C-bit. ZEROs are shifted into the vacated positions of the A- and B-registers through bit position 1 of the A-register. A maximum shift of 63-bit positions may be specified. However, the number of actual shifts performed equals the number specified by the instruction. If a shift greater than 31 occurs, bits 1 through 16 of the A- and B-registers will be ZERO.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

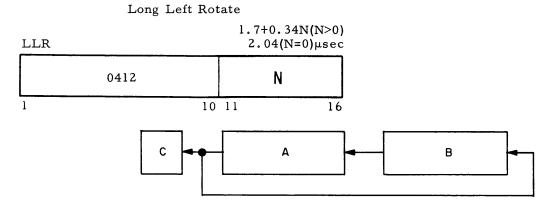

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 1 through 16, are treated as a 32-bit register. These bits are rotated

to the left (end-around carry) the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of bit position 1 of the B-register enter bit position 16 of the A-register. Bits shifted out of bit position 1 of the A-register enter bit position 16 of the B-register. Each bit shifted out of bit position 1 of the A-register enters the C-bit. A maximum shift of 63-bit positions may be specified. If a shift greater than 31 is specified, the net result of the shift is modulo 32. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 1 through 16, are treated as a single 32-bit register. These bits are rotated to the right (end-around carry) the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bits shifted out of bit position 16 of the B-register enter bit position 1 of the A-register. Bits shifted out of bit position 16 of the A-register enter bit position 1 of the B-register. Each bit shifted out of bit position 16 of the B-register enters the C-bit. A maximum shift of 63-bit positions may be specified. If a shift of greater than 31 is specified, the net result of the shift is modulo 32. However, the number of actual shifts performed equals the number specified by the instruction.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

#### Long Arithmetic Left Shift

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 2 through 16, are treated as a single 31-bit register. These bits are shifted to the left the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. The sign bit, bit 1 of the B-register is not changed. The C-bit is set if the sign, bit 1 of the A-register, is altered during execution of the instruction. It is reset if the sign bit is not altered. Bits shifted out of bit position 2 of the B-register enter bit position 16 of the A-register. Bits shifted out of bit position 1 of the A-register are lost. ZEROs are shifted into the vacated positions of the A- and B-registers through bit position 16 of the B-register. A maximum shift of 63 bit positions may be specified. However, the number of actual shifts performed equals the number specified by the instruction. If a shift greater than 31 is specified, bits 1 through 16 of the A-register and bits 2 through 16 of the B-register will be ZERO.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights to indicate overflow.

DESCRIPTION: The contents of the A-register, bits 1 through 16, and the contents of the B-register, bits 2 through 16, are treated as a single 31-bit register. These bits are shifted to the right through the C-bit the number of positions specified, in two's complement notation, by the six least significant bits, bits 11 through 16, of the instruction. Bit 1 of the A- and B-registers do not change. Bits shifted out of bit position 16 of the

B-register are lost. Bits shifted out of bit position 16 of the A-register enter bit position 2 of the B-register. Each bit shifted out of the B-register enters the C-bit. The sign is copied into the vacated positions of the A- and B-registers through bit position 1 of the A-register. A maximum shift of 63 bit positions may be specified. However, the number of shifts performed equals the number specified by the instruction. If a shift greater than 30 is specified, bits 2 through 16 of the A- and B-register will be the same as the sign of the A-register.

TYPE: Shift

INDICATORS: The C-STATUS indicator lights if the C-bit is set at the end of the instruction.

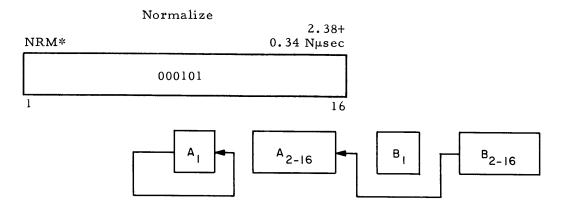

DESCRIPTION: The normalize instruction considers the 15 magnitude bits of the B-register and the A-register to be one 30-bit register. The A-register comprises the most significant half of the number. When the number to be normalized is positive, bits 2 through 16 of both the A- and B-registers are shifted until bit position 2 of the A-register contains a ONE. When the number is negative, bits 2 through 16 of both the A- and B-registers are shifted left until bit position 2 of the A-register becomes a ZERO. The number of positions shifted (or the exponent) is stored in the shift counter. This count (or exponent) is made available by the SCA instruction (shift count to A-register). If the contents of both registers are ZERO, 32 shifts are performed before the instruction is terminated, leaving ZERO in the shift counter. Bits shifted out of bit position 2 of the A-register are lost. Bits shifted out of bit position 2 of the B-register through bit position 16 of the B-register.

<sup>\*</sup>Optional

#### CONTROL INSTRUCTIONS

Add C to A

1.7 μsec

141216

DESCRIPTION: If the contents of the C-bit is a ONE, it is added to the contents of the A-register, bits I through 16. The resulting sum replaces the contents of the A-register, bits I through 16. If the content of the C-bit is ZERO, no operation occurs. Overflow is possible with this instruction. If overflow occurs, the C-bit is set. If overflow does not occur, the C-bit is reset.

TYPE: Generic

INDICATORS: C-STATUS indicator lights to indicate overflow.

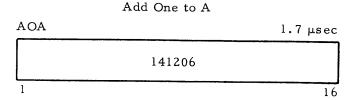

DESCRIPTION: Add ONE to the contents of the A-register, bits 1 through 16. The resulting sum replaces the contents of the A-register, bits 1 through 16. Overflow is possible with this instruction. If overflow occurs, the C-bit is set. If overflow does not occur, the C-bit is reset.

TYPE: Generic

INDICATORS: C-STATUS indicator lights to indicate overflow.

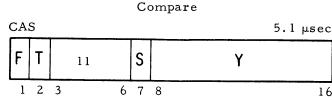

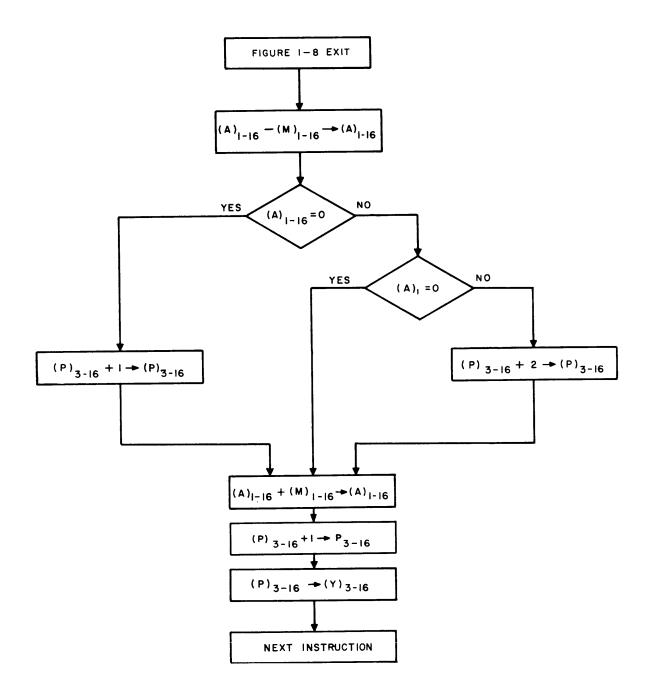

DESCRIPTION: The contents of the A-register, bits I through 16, are algebraically compared to the contents of the effective operand address in memory, bits I through 16. If the value in the A-register is greater than the value in memory, the computer proceeds to the next sequential instruction. If the value in the A-register is equal to the value in memory, the next sequential instruction is skipped. If the value in the A-register is less than the value in memory, the next two sequential instructions are skipped. The contents of the A-register, bits I through 16, and the contents of the memory, bits I through 16, are unchanged. (See Figure 2-5.)

TYPE: Memory reference

Figure 2-5. CAS Instruction, Flow Diagram

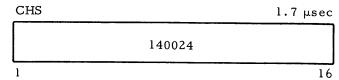

DESCRIPTION: The sign of the A-register, bit position 1, is complemented. Bits 2 through 16 of the A-register do not change.

TYPE: Generic

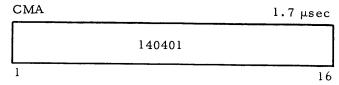

# Complement A Register

DESCRIPTION: The contents of the A-register, bits 1 through 16, are complemented (one's complement) and the complement replaces the contents of the A-register, bits 1 through 16. Bit positions that are ZERO are changed to ONE. Bit positions that are ONE are changed to ZERO.

TYPE: Generic

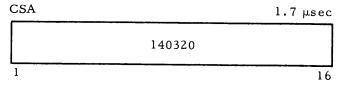

Copy Sign and Set Sign Plus

DESCRIPTION: The sign bit, bit 1, of the A-register, minus or plus, is copied into the C-bit and the sign bit position, bit 1, of the A-register is cleared to ZERO. Bits 2 through 16 of the A-register do not change.

TYPE: Generic

INDICATORS: C-STATUS indicator lights if C-bit is set.

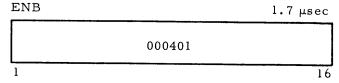

# Enable Program Interrupt

DESCRIPTION: This instruction enables program interrupt. It sets the interrupt control flip-flop so as to permit interrupts. If an interrupt is present on the basic interrupt line or any optional interrupt lines at the end of the next instruction, control will be

transferred through the appropriate standard location.

TYPE: Generic

INDICATORS: PI indicator lights to indicate that interrupt is enabled.

#### NOTE

Do not give the ENB instruction before the desired interrupt masks are set up by an OTA '0020.

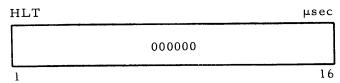

Halt

DESCRIPTION: The computer will halt until the START button on the operator's console is depressed at which time execution will be resumed at the next sequential instruction.

TYPE: Generic

INDICATORS: HALT indicator (in START button) is lighted to indicate machine is in halt condition.

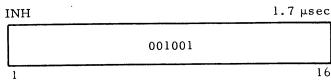

Inhibit Program Interrupt

DESCRIPTION: This instruction inhibits interrupt. The computer cannot be interrupted until another ENB (enable program interrupt) instruction is executed.

TYPE: Generic

INDICATOR: PI indicator is extinguished indicating that program interrupt is inhibited.

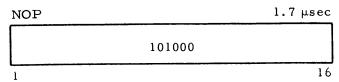

DESCRIPTION: No operation is performed by this instruction. The computer proceeds to and executes the next sequential instruction.

Reset C to Zero

DESCRIPTION: The content of the C-bit is reset to ZERO. If the content of the C-bit is ZERO, no change occurs.

TYPE: Generic

INDICATORS: C-STATUS indicator is extinguished.

Set C to One

DESCRIPTION: The content of the C-bit is set to ONE. If the content of the C-bit is ONE, no change occurs.

TYPE: Generic

INDICATORS: C-STATUS indicator lights.

Set A Sign Minus

DESCRIPTION: If the sign of the contents of the A-register is plus ( $A_1=0$ ), the sign is changed to minus ( $A_1=1$ ). If the sign is minus, no change occurs. Bits 2 through 16 of the A-register do not change.

TYPE: Generic

Set A Sign Plus

DESCRIPTION: If the sign of the contents of the A-register is minus  $(A_1=1)$ , the sign is changed to plus  $(A_1=0)$ . If the sign is plus, no change occurs. Bits 2 through 16 of the A-register do not change.

#### Two's Complement A

DESCRIPTION: The contents of the A-register, bits 1 through 16, are two's complemented and the result replaces the contents of the A-register, bits 1 through 16.

TYPE: Generic

# INPUT/OUTPUT INSTRUCTIONS

#### General

The basic information flow for the four input/output instructions is shown in Figure 2-6. Bits 11 through 16 are generally used to specify the device to which the instruction refers and bits 7 through 10 are used to specify the function to be performed by the I/O device.

Input to A

DESCRIPTION: Bits 7 through 16 of the instruction word are taken to the I/O bus address lines and decoded; however, bit 7 is normally not used as part of a function code. If the ready flip-flop for the device specified is not set, the instruction is treated as a NOP and the next sequential instruction is executed. If the device ready flip-flop is set (device ready) bit 7 of the instruction word is tested. If bit 7 is set, the A-register is cleared and the contents of the input bus, bits 1 through 16, are transferred to the A-register, bits 1 through 16. If bit 7 is not set, the contents of the input bus, bits 1 through 16, are ORed with the contents of the A-register, bits 1 through 16.

TYPE: IOT

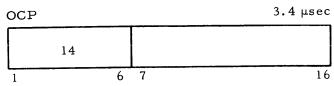

Output Control Pulse

DESCRIPTION: Bits 7 through 16 of the instruction word are taken to the I/O bus address lines. The 10 bits are decoded within the device interface enabling generation of an output control pulse (OCP) used to set up the operating mode or perform a control function in a device. Bits 11 through 16 select the device interface. Bits 7 through 10 specify the function to be performed by the I/O device. The OCP may cause the I/O device to perform a mechanical motion, set up the mode of a device, etc.

TYPE: IOT

Figure 2-6. IOT Instructions, General Flow Diagram

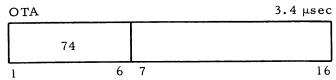

#### Output from A

DESCRIPTION: Bits 7 through 16 of the instruction word are taken to the address lines of the I/O bus. Bits 11 through 16 are decoded and select the proper device interface. Bits 7 through 10 specify the function to be performed. If the device is not ready, the next sequential instruction is executed. If the device is ready, the contents of the A-register, bits 1 through 16, are transferred to the output bus, bits 1 through 16, and the next sequential instruction is skipped. The number of bits accepted by the device interface is contingent upon the size of the device buffer. Example: Only the least significan 8 bits, bits 9 through 16, are transmitted to the ASR-33 buffer.

TYPE: IOT

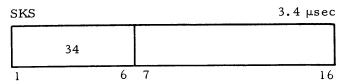

Skip If Ready Line Set

DESCRIPTION: Bits 11 through 16 of the instruction specify the device to be interrogated; bits 7 through 10 of the instruction specify the condition to be sensed. If the selected condition causes the ready line to be set, the computer skips the next sequential instruction and continues with the program. If the ready line is not set, the computer proceeds to the next sequential instruction.

TYPE: IOT

#### TRANSFER OF CONTROL INSTRUCTIONS

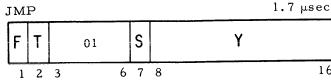

Unconditional Jump

DESCRIPTION: The effective operand address of the instruction replaces the contents of the program counter (P), bits 3 through 16.

TYPE: Memory reference

## Jump and Store Location

DESCRIPTION: The contents of the program counter (P), bits 3 through 16, replace the 14 least significant bits, bits 3 through 16, of the memory location addressed by the effective operand address. The two most significant bits of the memory location, bits 1 and 2, are left unchanged. The effective operand address plus one is loaded into the program counter, P, bits 3 through 16. (See Figure 2-7.)

TYPE: Memory reference

Figure 2-7. JST Instruction, Flow Diagram

## Skip If C Reset

DESCRIPTION: Skip the next sequential instruction if the C-bit is reset. Execute the next sequential instruction if the C-bit is set. (See Figure 2-8 for a general flow diagram of the skip instructions.) The C-bit is unchanged.

Figure 2-8. Skip Instructions, General Flow Diagram

DESCRIPTION: Skip the next sequential instruction if the C-bit is set. Execute the next sequential instruction if the C-bit is reset. The C-bit is unchanged.

TYPE: Generic

DESCRIPTION: If the least significant bit of the A-register is ONE (A<sub>16</sub>=1), the computer skips the next sequential instruction. If the least significant bit of the A-register is ZERO (A<sub>16</sub>=0), the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged.

TYPE: Generic

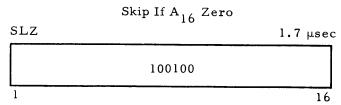

DESCRIPTION: If the least significant bit of the A-register is ZERO (A<sub>16</sub>=0), the computer skips the next sequential instruction. If the least significant bit of the A-register is not ZERO (A<sub>16</sub>=1), the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged.

TYPE: Generic

DESCRIPTION: If the sign of the A-register is negative (A<sub>1</sub>=1), the computer skips the next sequential instruction. If the sign of the A-register is positive (A<sub>1</sub>=0), the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged. The magnitude bits, bits 2 through 16, of the A-register are not examined.

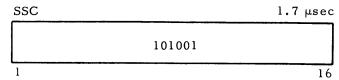

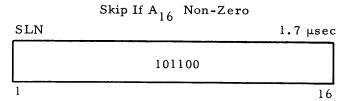

#### Skip If A Not Zero

DESCRIPTION: If the contents of the A-register, bits 1 through 16, are not ZERO, the computer skips the next sequential instruction. If the contents of the A-register, bits 1 through 16 are ZERO, the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged.

TYPE: Generic

Skip If A Plus

DESCRIPTION: If the sign of the A-register is positive (A<sub>1</sub>=0), the computer skips the next sequential instruction. If the sign of the A-register is negative (A<sub>1</sub>=1), the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged. The magnitude bits, bits 2 through 16, of the A-register are not examined.

TYPE: Generic

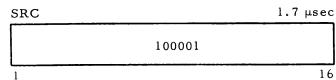

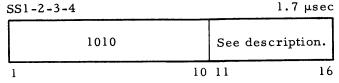

Skip If Sense Switches Set

DESCRIPTION: Skip the next sequential instruction if the sense switch specified by bits 11 through 16 of the instruction word is set. Execute the next sequential instruction if the sense switch specified by bits 11 through 16 of the instruction word is reset.

| Sense<br>Switch | Bits<br>11-16 |                 |

|-----------------|---------------|-----------------|

| SS1             | 20            | (bit $12 = 1$ ) |

| SS2             | 10            | (bit $13 = 1$ ) |

| SS3             | 04            | (bit $14 = 1$ ) |

| SS4             | 02            | (bit 15 = 1)    |

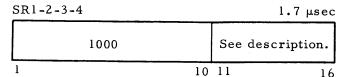

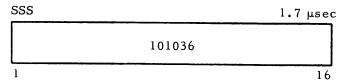

Skip If Sense Switches Reset

DESCRIPTION: Skip the next sequential instruction if the sense switch specified by bits 11 through 16 of the instruction word is reset. Execute the next sequential instruction if the sense switch specified by bits 11 through 16 of the instruction word is set.

| Sense  | Bits  |                 |

|--------|-------|-----------------|

| Switch | 11-16 |                 |

| SRl    | 20    | (bit $12 = 1$ ) |

| SR2    | 10    | (bit $13 = 1$ ) |

| SR3    | 04    | (bit $14 = 1$ ) |

| SR4    | 02    | (bit $15 = 1$ ) |

TYPE: Generic

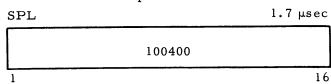

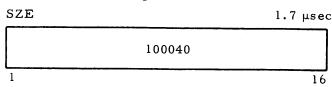

Skip If No Sense Switch Set

DESCRIPTION: Skip the next sequential instruction if no sense switch is set.

TYPE: Generic

Skip If Any Sense Switch Set

DESCRIPTION: Skip the next sequential instruction if any sense switch is set.

TYPE: Generic

Skip If A Zero

DESCRIPTION: If the contents of the A-register, bits 1 through 16, are ZERO, the computer skips the next sequential instruction. If the contents of the A-register, bits 1 through 16, are not ZERO, the computer proceeds to the next sequential instruction. The contents of the A-register, bits 1 through 16, are unchanged.

Table 2-1.

Summary Description of DDP-116 Instructions

| Mnemonic | Functional<br>Description | Description                                                                                                                           | Time (µsec)                    |

|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| ACA      | Add C to A                | If $C=1$ , $(A)+1 \rightarrow (A)$<br>If $C=0$ , $(A) = (A)$<br>If Overflow $1 \rightarrow (C)$<br>If no Overflow $0 \rightarrow (C)$ | 1.7                            |

| ADD      | Add                       | $(A)+(EOA) \rightarrow (A)$ If Overflow $1 \rightarrow (C)$ If no Overflow $0 \rightarrow (C)$                                        | 3.4                            |

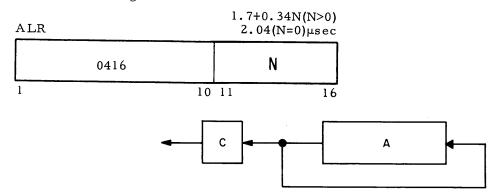

| ALR      | Logical Left Rotate       | C A                                                                                                                                   | 1.7+0.34 N (N>0)<br>2.04 (N=0) |

| ALS      | Arithmetic Left Shift     | If $A_1$ changed $1 \rightarrow (C)$ If $A_1$ not changed $0 \rightarrow (C)$                                                         | 1.7+0.34 N (N>0)<br>2.04 (N=0) |

| ANA      | AND to A                  | (A)∧(EOA) →(A)                                                                                                                        | 3.4                            |

| AOA      | ADD 1 to A                | $(A) + 1 \rightarrow (A)$ If Overflow $1 \rightarrow (C)$ If no Overflow $0 \rightarrow (C)$                                          | 1.7                            |

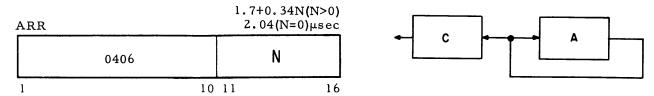

| ARR      | Logical Right Rotate      | CAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAAA                                                                                               | 1.7+0.34 N (N>0)<br>2.04 (N=0) |

| ARS      | Arithmetic Right Shift    | C A <sub>1</sub> A <sub>2</sub> - 16                                                                                                  | 1.7+0.34 N (N>0)<br>2.04 (N=0) |

| CAS      | Compare Memory and A      | If (A)>(EOA) Go to P If (A)=(EOA) Go to P+1 If (A)<(EOA) Go to P+2                                                                    | 5.1                            |

Table 2-1. (Cont)

Summary Description of DDP-116 Instructions

| Mnemonic | Functional<br>Description              | Description                                                                      | Time (µsec)     |

|----------|----------------------------------------|----------------------------------------------------------------------------------|-----------------|

| CCA      | Clear C and A                          | O → (C)                                                                          | 1.7             |

|          |                                        | O → (A)                                                                          |                 |

| CHS      | Change Sign                            | $(\overline{A})_1 \rightarrow (A)_1$                                             | 1.7             |

| CMA      | Complement A                           | $(\overline{A}) \to (A)$                                                         | 1.7             |

| CRA      | Clear A                                | 0 →(A)                                                                           | 1.7             |

| CSA      | Copy sign to C-bit and set A sign plus | $(A_1) \rightarrow (C),  0 \rightarrow (A_1)$                                    | 1.7             |

| DIV*     | Divide                                 | (A) (B) ÷ (EOA) → (A) <sub>Quotient</sub> (B) <sub>Remainder</sub>               | 16.67 (maximum) |

|          |                                        | A High order dividend                                                            |                 |

| ENB      | Turn Program Interrupt On              | Enable Program Interrupt System                                                  | 1.7             |

| ERA      | Exclusive OR to A                      | (A) <del>∀</del> (EOA) → (A)                                                     | 3.4             |

|          |                                        | Logical Difference                                                               |                 |

| HLT      | Halt                                   | Stop Program Operation                                                           |                 |

| IAB      | Interchange A and B                    | (A) <del>←</del> (B)                                                             | 1.7             |

| IMA      | Interchange Memory and A               | (A) <del>←</del> (EOA)                                                           | 5.1             |

| INA      | Input to A                             | If (Ready) = 0, Go to P, no input                                                | 5.1             |

|          |                                        | If $(Ready) = 1$ , and $(IW)_7 = 1$ , $(INB) \rightarrow (A)$<br>Go to P+1       |                 |

|          |                                        | If $(Ready) = 1$ , and $(IW)_7 = 0$ , $(INB)\lor(A)\rightarrow(A)$ - Go to $P+1$ |                 |

| INH      | Turn Program Interrupt Off             | Inhibit Program Interrupt System                                                 | 1.7             |