# PRELIMINARY DAP ASSEMBLY PROGRAM FOR THE DDP-24 GENERAL PURPOSE COMPUTER

# **CONTENTS**

| Title                                    | Pag  |

|------------------------------------------|------|

| SECTION I                                |      |

| INTRODUCTION                             | 1 -1 |

| SECTION II                               |      |

| SECTION II                               |      |

| GENERAL                                  | 2-1  |

| THE CODING FORM                          | 2-1  |

| THE LOCATION FIELD                       | 2-1  |

| THE OPERATION CODE FIELD                 | 2-1  |

| THE VARIABLE FIELD                       | 2-3  |

| THE COMMENTS FIELD                       | 2-3  |

| SYMBOLS AND EXPRESSIONS                  | 2-3  |

| SYMBOLS                                  | 2-3  |

| EXPRESSIONS                              | 2-3  |

| LITERALS                                 | 2-4  |

| ASTERISK CONVENTIONS                     | 2-5  |

| SOURCE PROGRAM PREPARATION               | 2-5  |

| PAPER TAPE                               | 2-5  |

| CARDS                                    | 2-5  |

| SECTION III                              |      |

| GENERAL                                  | 3-1  |

| ASSEMBLY CONTROLLING PSEUDO-OPERATIONS   | 3-1  |

| END                                      | 3-2  |

| MOR                                      | 3-2  |

| ORG                                      | 3-3  |

| REL                                      | 3-3  |

| DATA DEFINING PSEUDO-OPERATIONS          | 3-3  |

| BCI                                      | 3-6  |

| DEC                                      | 3-6  |

| OCT                                      | 3-7  |

| DICTIONARY CONTROLLING PSEUDO-OPERATIONS | 3-7  |

| CALL                                     | 3-7  |

| NTRY                                     | 3-8  |

| RTRN                                     | 3-8  |

|                                          |      |

| Title                                 | Page |

|---------------------------------------|------|

| SECTION III (continued)               |      |

| LIST CONTROLLING PSEUDO-OPERATIONS    | 3-8  |

| LIST                                  | 3-8  |

| NLST                                  | 3-9  |

| MACRO DEFINING PSEUDO-OPERATIONS      | 3-9  |

| MAC                                   | 3-10 |

| ENDM                                  | 3-11 |

| STORAGE ALLOCATION PSEUDO-OPERATIONS  | 3-11 |

| BES                                   | 3-11 |

| BSS                                   | 3-11 |

| COMN                                  | 3-12 |

| SYMBOL DEFINING PSEUDO-OPERATION      | 3-12 |

| EQU                                   | 3-12 |

| SECTION IV                            |      |

|                                       |      |

| GENERAL                               | 4-1  |

| SUBROUTINE LIBRARY                    | 4-2  |

| LIBRARY DIRECTORY                     | 4-2  |

| SUBROUTINE PROGRAMS                   | 4-2  |

| UTILITY UPDATER                       | 4-2  |

| SUBROUTINE LIBRARY CHANGES            | 4-2  |

| SECTION V                             |      |

| GENERAL                               | 5-1  |

| ASSEMBLER OPERATION                   | 5-1  |

| SENSE SWITCHES                        | 5-1  |

| ASSEMBLER PRODUCTS                    | 5-2  |

| LISTING                               | 5-2  |

| PUNCHED TAPE                          | 5-3  |

| RELOCATION SPECIFIERS                 | 5-4  |

| DIAGNOSTICS                           | 5-4  |

| DIAGNOSTICS                           |      |

| APPENDIX A DDP-24 CHARACTERISTICS     | A-1  |

| APPENDIX B DAP INSTRUCTION REPERTOIRE | B-1  |

| APPENDIX C OCP CONTROL PULSE CODES    | C-1  |

| APPENDIX D SKS SENSE LINE CODES       | D-l  |

| APPENDIX E TYPEWRITER CODES           | E-1  |

| APPENDIX F NUMERICAL INSTRUCTION LIST | F-1  |

APPENDIX G -- ALPHABETICAL INSTRUCTION LIST ..... G-1

# SECTION I INTRODUCTION

The DDP-24 Assembly Program (DAP) is a programming aid that will translate a symbolic language to permit writing programs in a form more convenient to the programmer while maintaining the flexibility of machine language (binary) coding. It enables the substitution of mnemonic symbols for desired binary instructions, such as ADD in place of 001000, and allows the programmer to assign names to specific data items or groups such as DAY, RATE, or MACH and to use these names when referring to the items as operands. Several pseudo-operations are provided to allow the programmer to express concepts that have no counterpart in normal machine language. Additional features of DAP include the facility for programmer defined macro-operations, the capability for linking with FORTRAN II programs and vice versa, the option of producing absolute or relocatable object programs, and operations that give the flexibility of using subroutines (either library or non-library).

DAP is designed to work with a minimum machine configuration: a paper tape reader, a paper tape punch, an on-line typewriter and 4,096 words of memory. No optional features are required to assemble a program using DAP; however, provision is made for utilization of a line printer, magnetic tapes and card equipment when available. Thus, by using a smaller system the user may assemble a program designed to run on, and take advantage of a more complex system.

### **SECTION II**

# SOURCE LANGUAGE FORMAT

#### GENERAL

The general format of the DAP source language consists of four major subsections; these are the Location, Operation, Variable and Comments Fields. The rules governing the use of these fields are the same for either a paper tape system or a card system; however, the preparation of the source program for processing by DAP (keypunching) is different for the two systems. This difference is discussed under SOURCE PROGRAM PREPARATION.

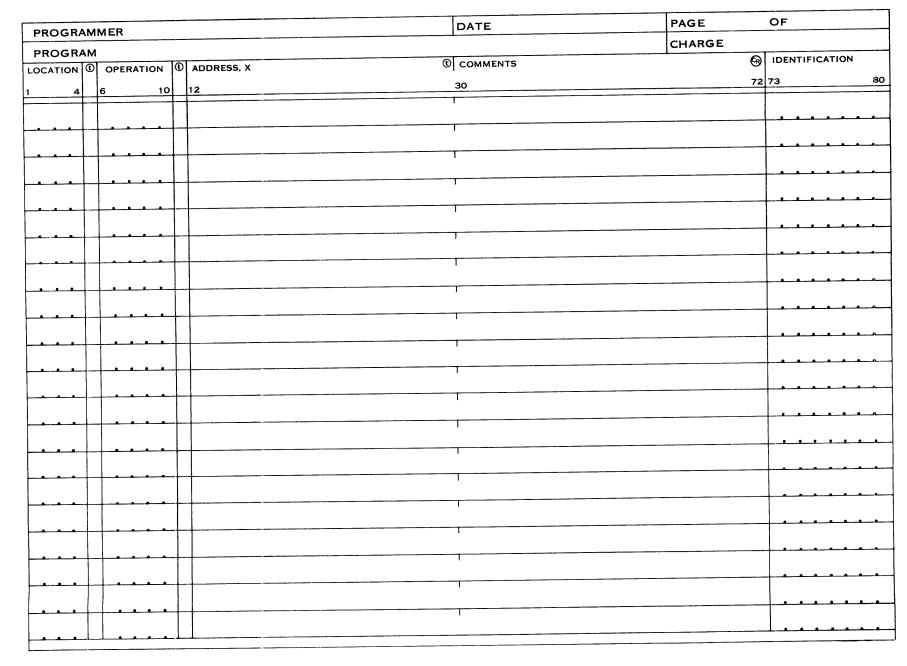

#### THE CODING FORM

Figure 1 illustrates the coding form that may be used for writing DAP source programs for either the paper tape system or the card system. The line and column spacing on the form has been designed to be compatible with standard typewriter spacing and the color (dark green print on light green paper) has been used to minimize reflective glare.

#### THE LOCATION FIELD

The Location Field is normally used to assign a symbolic label to an instruction, constant, or buffer area when it is necessary to refer to that location elsewhere in the program. The symbolic label in the Location Field consists of from one to four characters from among the thirty-six character set composed of the alphabet and the ten numeric digits. At least one of the characters in any label must be alphabetic.

Labels provide the means of symbolic addressing in programs. When a label occurs in the Location Field of the input format, it is assigned the current value of the DAP location counter (unless an EQU or ORG operation in the Operation Field causes it to be assigned otherwise). The first such occurrence constitutes the definition of the label and any subsequent occurrence will cause redefinition and an error print-out.

#### THE OPERATION CODE FIELD

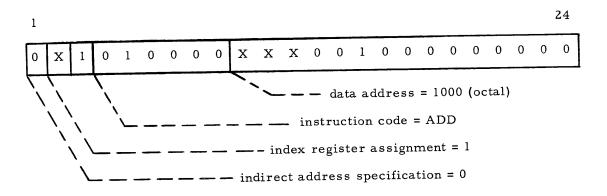

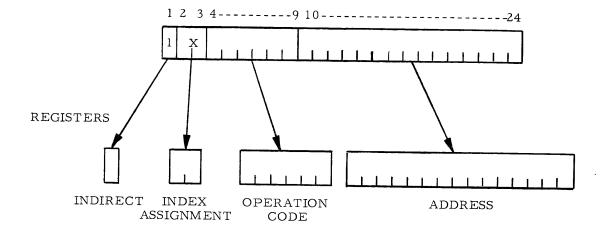

Mnemonic operation codes are used to represent machine instructions, commands to the assembler itself, and macro-operations. Operation codes are either 3 or 4 characters in length. Appendix B summarizes operation codes recognized by DAP. In addition to specifying an operation, the Operation Field is also used to specify whether indirect addressing is desired. This is indicated by writing an asterisk (\*) immediately following the operation code.

Figure 1. DAP Coding Form

#### THE VARIABLE FIELD

The Variable Field has different uses for different classes of commands. The specific use for a particular command is covered under the explanation of that command. The most general use of this field is for the specification of an address and index register. One may write any permissible expression (an expression is defined below) to represent the address portion of the command. If this expression is not followed by a comma, no index register is specified. An index register is specified by following the address expression with a comma and another expression indicating the desired index register.

#### THE COMMENTS FIELD

This field may be used for any comments the programmer cares to write. The Comments Field has no effect on the assembler, but is printed out on the symbolic listing during Pass Two, if a listing has been requested.

#### SYMBOLS AND EXPRESSIONS

#### SYMBOLS

Symbols consist of one to four characters, one of which must be alphabetic. The remaining characters, if any, may be any alphabetic and/or numeric combination. The following 11 characters may not be used as part of a symbol:

| +  | (plus sign)   | 1 | (apostrophe)        |

|----|---------------|---|---------------------|

| -  | (minus sign)  | , | (comma)             |

| *  | (asterisk)    | ( | (left parenthesis)  |

| /  | (slash)       | ) | (right parenthesis) |

| \$ | (dollar sign) | & | (ampersand)         |

| =  | (equal sign)  |   |                     |

The period (.) may be used as a character in a symbol, but the programmer is cautioned to avoid possible confusion with the decimal literal.

#### **EXPRESSIONS**

An expression may be either <u>simple</u> (composed of a single element) or <u>compound</u> (composed of two or more elements separated by operators). Both expression types may have either "relocatable" or "absolute" modes. A relocatable expression is one which is relative to the first instruction of the program; an absolute expression is one which has a constant value regardless of its relative position in the program. The overall mode of the expression depends on the mode of each of the individual elements used to make up the expression.

An <u>element</u> is the smallest component of an expression. An element is either a symbol, a decimal integer less than  $2^{23}$ , or an octal integer less than  $2^{23}$ . An octal integer is denoted by a preceding apostrophe (e.g., '123). (An asterisk may also be used as an element as described below.)

An  $\underline{\text{operator}}$  may be used to separate elements in compound expressions. The operators have the following meanings:

plus or ampersand addition

minus subtraction

asterisk multiplication

slash

An asterisk may also be used as an element, as explained under ASTERISK CONVENTIONS.

The multiplication and division operators take precedence over the addition and subtraction operators. Parentheses are not allowed; therefore, implied parenthetical groupings are processed from left to right, for example:

division

A\*B+C\*D is interpreted as (A\*B) + (C\*D)

A+B\*C is interpreted as A + (B\*C)

A-B+C is interpreted as (A-B) + C

A\*B/C is interpreted as (A\*B)/C

A/B/C is interpreted as (A/B)/C

Two operators may not appear in succession (e.g., A++B); however, when the asterisk is used as an element, its meaning is unambiguous and is therefore allowed. For example,

\*+1

means "this location plus one",

and

\*\*2

means "this location times two".

#### LITERALS

It is often necessary to refer to a memory location containing a constant to be defined by the programmer. This can easily be done by the use of one of the data defining pseudo-operations provided in the DAP language. However, it is sometimes more convenient to reference a constant literally rather than symbolically. Consider the following examples:

LDA ONE

LDA ONE

CONE DEC 1

END

LDA = 1

CONE CONE

In the first example the decimal constant l is referred to symbolically as ONE and must be defined by the programmer; however, in the second example, the programmer is not required to define the constant. DAP will interpret "=1" as a literal, will automatically assign a location for the constant at the end of the program, and will insert the address of that location in the LDA instruction.

Three different types of literals are interpreted by DAP: decimal, octal and alphanumeric.

1) Decimal Literals.

A decimal literal consists of the equals character (=) followed by a signed or unsigned fixed-point decimal number (Decimal Numbers are discussed in Section III).

2) Octal Literals

An octal literal consists of the equals character (=) followed by an apostrophe (') followed by a signed or unsigned octal number (refer to the discussion of Octal Numbers).

3) Alphanumeric Literals.

An alphanumeric literal consists of the equals character (=) followed by the letter A followed by four alphanumeric characters. With the exception of the space, control characters cannot be used in an alphanumeric literal (e.g., carriage return, tab, stop code, etc).

#### ASTERISK CONVENTIONS

The following programming conventions using the asterisk are allowed by DAP:

- \* in column 1 or first element in Location Field; treat entire card or line as remarks.

- 2) \* appended to instruction mnemonic: set indirect address flag.

- 3) \* an element: current value of the Location Counter.

- 4) \*\* as a symbolic address: address will be modified by another instruction.

- 5) \*\*\* as an operation code: op-code will be modified by another instruction.

#### SOURCE PROGRAM PREPARATION

#### PAPER TAPE

In order to make more efficient use of the paper tape as an input medium to DAP, a terminating code has been used to define the difference between fields rather than specifying "columns." For example, if the Location Field is not used, it is not necessary to space five times in order to be in position for the Operation Field. The terminating code used is the tab. In addition, the carriage return will terminate the entire line. In the example used above, a tab would immediately define the start of the Operation Field. The general format for the entire line would be:

Location Field (tab) Operation Field (tab) Variable Field (tab) Comments Field (carriage return)

#### CARDS

When using cards, no purpose is served by trying to make a line of code more compact since the entire card must be read. Therefore, the card columns are used to define the fields. The only exception to this is the termination of the Variable Field and the start of the Comments Field. DAP will assume the Comments Field to start after the first blank column following the Variable Field. If a blank is embedded within the Variable Field, DAP will assume the remainder of the line to be comments. The general format for the card would be:

Location Field Columns 1 to 4

Operation Field Columns 6 to 10

Variable Field Columns 12 to first blank column

Comments Field First blank column to column 72

Identification Field Columns 73 to 80

# SECTION III PSEUDO-OPERATIONS

#### GENERAL

In addition to translating all of the DDP-24 instruction mnemonics, DAP will also translate certain pseudo-operations specifying optional controls and programmer aids for number conversions. Operations that fall into this category are called "pseudo" because they have no counterpart in the list of actual DDP-24 instructions.

Primarily, pseudo-operations are provided to give the programmer a flexible language. It is possible to generate equivalent information by using different instructions or pseudo-operations; however, the choice made by the programmer is often intended to be meaningful in the context of the program listing for the convenience of others who may examine the program. For example, the octal word 40000144 could be generated by any one of the following DAP operations:

| HLT* | '144   |

|------|--------|

| HLT* | 100    |

| MZE  | 100    |

| PZE* | '144   |

| BCI  | 1,-01M |

| DEC  | -100   |

| OCT  | -144   |

#### ASSEMBLY CONTROLLING PSEUDO-OPERATIONS

The pseudo-operations in this category (ABS, END, MOR and REL) are used for directing DAP to perform various assembly functions; they do not generate instructions in the object program.

ABS

The ABS ( $\underline{ABSOLUTE}$ ) pseudo-operation is used to direct DAP to assemble the subsequent instructions in the absolute mode. The format for using the ABS pseudo-operation is:

| LOCATION  | Ignored |

|-----------|---------|

| OPERATION | ABS     |

| VARIABLE  | Ignored |

| COMMENTS  | Normal  |

The effect of the ABS pseudo-operation is to cause a termination of the current block of output information and the start of a new block in which words are assigned absolute locations. The assembler will then continue to run in the absolute mode until a REL or ORG pseudo-operation is encountered. Initialization of the assembler automatically sets the absolute mode.

END

The END (END) pseudo-operation is used to direct DAP to terminate the current assembly pass and prepare for the next pass. The format for using the END pseudo-operation is:

LOCATION Ignored

OPERATION END

VARIABLE 1) Main Program. An expression that defines the address of the instruction to which control should be transferred at the conclusion of the loading process at object time.

2) Subroutine. Ignored.

COMMENTS Normal

The END pseudo-operation causes DAP to perform the following functions:

1) If in pass one, halt. When the start button is depressed, start processing pass two (while the computer is halted, the operator must reposition the source tape to the beginning).

#### 2) If in pass two:

- a) The current block of assembly output information is terminated.

- b) The transfer vector is tested to see if subroutines are required; if so, a request is typed for the subroutine tape and a pass is made to fetch the requested subroutines.

- c) If this is a main program, a jump record is written following the assembly output. The address of the jump is the value of the expression in the Variable Field. If this is a subroutine, no jump record is written.

- d) The assembly process is terminated.

If an END pseudo-operation is used, it must be the last operation of the source program.

MOR

The MOR (MORE) pseudo-operation has various meanings which depend on Sense Switch settings (see below). The format for using the MOR pseudo-operation is:

LOCATION Ignored

OPERATION MOR

VARIABLE If the MOR pseudo-operation is to be treated as an END pseudo-operation, the rules for the Variable Field are the same as those described

for the END pseudo-operation; otherwise this field is ignored.

COMMENTS Normal

The MOR pseudo-operation causes DAP to perform the following functions:

1) If Sense Switch 4 is down, halt. When the start button is depressed, interrogate Sense Switch 5 (this will allow the operator to change paper tapes in the event the source program has been produced in more than one piece).

- 2) If Sense Switch 4 is up, do not halt, but interrogate Sense Switch 5.

- 3) If Sense Switch 5 is down, continue the assembly process.

- 4) If Sense Switch 5 is up, treat the MOR pseudo-operation as an END pseudo-operation.

ORG

The ORG (ORIGIN) pseudo-operation is used to assign a new value to the Location Counter. The format for using the ORG pseudo-operation is:

LOCATION Normal

OPERATION ORG

VARIABLE Any relocatable or absolute expression (if left blank, an absolute origin of zero will be assumed). Any symbol used in this field must

have been previously defined.

COMMENTS Normal

The ORG pseudo-operation performs the following functions:

1) The expression in the Variable field is evaluated for value and mode (relocatable or absolute).

- 2) The location counter is reset to the value thus determined.

- 3) If there is a symbol in the Location Field, it is given this value and mode.

The ORG pseudo-operation will cause DAP to switch to relocatable or absolute mode and will continue in this mode until an ABS, REL or another ORG is encountered.

REL

The REL (RELOCATABLE) pseudo-operation is used to direct DAP to assemble the subsequent instructions in the relocatable mode. The format for using the REL pseudo-operation is:

LOCATION Ignored

OPERATION REL

VARIABLE Ignored

COMMENTS Normal

The effect of the REL pseudo-operation is to cause a termination of the current block of output information and the start of a new block in which words are assigned relative locations. The assembler will then continue to run in the relocatable mode until an ABS or ORG pseudo-operation is encountered.

#### DATA DEFINING PSEUDO-OPERATIONS

The pseudo-operations in this category (BCI, DEC and OCT) are used for the generation of data to be included as part of the object program. The following is a discussion of the three different types of data that can be interpreted by DAP.

#### 1) Alphanumeric Data.

Certain restrictions are placed on the use of alphanumeric data within the scope of the data defining features of DAP (for both the BCI pseudo-operation and the alpha-numeric literal). These restrictions have to do with the control characters: back space, lower case shift, upper case shift and carriage return. With the exception of these specific characters, all of the characters listed in Appendix E may be used in alphanumeric data fields.

#### 2) Decimal Data.

#### a) Fixed-point decimal data.

A significance of six decimal digits can be maintained in single precision fixed-point arithmetic on the DDP-24. In many arithmetic operations, this degree of significance is adequate and is desirable because of the speed in computation. DAP provides two facilities for generating fixed-point numbers using decimal notation: decimal literal and the DEC pseudo-operation.

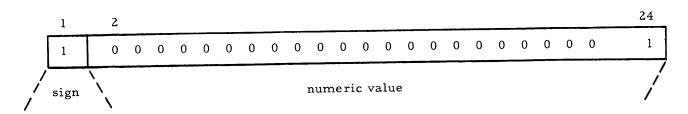

A fixed-point decimal number requires one computer word (sign and 23 bits of significance) and is specified in the DAP language by the use of two parts:

i) The significant part, which is a signed or unsigned decimal number with or without a decimal point. If the decimal point is not specified, it is assumed to be immediately to the right of the last digit (a decimal integer).

ii) The scaling part, which is the letter B followed by a signed or unsigned decimal integer specifying the position of the understood binary point. The scaling part need not be present (in which case the number will be a truncated decimal integer whose understood binary point is immediately to the right of the least significant bit in the computer word -- position 23).

The general form of the scaling part is B+nn, where nn gives the position of the understood binary point relative to the machine binary point, the - defines the understood binary point to be to the left of the machine binary point, and the + (or no sign) defines the understood binary point to be to the right of the machine binary point. The machine binary point is defined to be between the sign bit and the most significant bit of the computer word (between positions 1 and 2).

The following are examples of how DAP would produce fixed-point numbers. The right column shows the decimal number to be translated and the left column shows the resulting octal word that would be generated by DAP.

00000017. 15 00000017. +15.14 00000017. 15B+23 17.000406 15.001B5

a indicates understood binary point

Fixed-point numbers are limited to a magnitude less than  $2^{23}$ .

#### b) Floating-point decimal data.

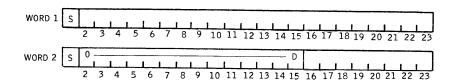

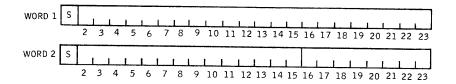

There are two types of floating-point numbers available to the DAP user, both of which require two computer words; these are 1) single precision floating-point (sign and 23 bits of mantissa, sign and 8 bits of exponent), and 2) extended precision floating point (sign and 38 bits of mantissa, sign and 8 bits of exponent). Figure 2 shows the formats of floating point numbers. A floating point decimal number may be defined by the use of the DEC pseudo-operation only. A floating point decimal number is specified in the DAP language by the use of two parts:

i) The mantissa part, which is a signed or unsigned decimal number preceded by a decimal point.

ii) The exponent part, which is one letter E or two E's followed by a signed or unsigned decimal integer specifying the power of ten which is the coefficient of the mantissa. The single letter E specifies a single precision floating-point number; a double letter E specifies an extended precision floating-point number. An exponent part must be specified for floating-point numbers; if omitted, DAP will assume the mantissa to be a fixed-point decimal integer. The magnitude of the exponent may not exceed 75 decimal (coefficient =  $10^{75}$ ).

SINGLE PRECISION

WORD 1 - SIGN, BITS 2-23: MANTISSA

WORD 2 - SIGN, BITS 16-23: EXPONENT (BITS 2-15

ARE ZERO)

EXTENDED PRECISION

WORD 1 - SIGN, BITS 2-23: MOST SIGNIFICANT BITS OF MANTISSA

WORD 2 - BITS 2-15: LEAST SIGNIFICANT BITS OF MANTISSA

SIGN, BITS 16-23: EXPONENT

Figure 2. Floating Point Format

The following are examples of how DAP would produce floating-point numbers. The right column shows the decimal number to be translated and the left column shows the resulting two octal words that would be generated by DAP (assigned to successive storage locations). The second octal word for each example contains the exponent (power of two) in the low order 2-2/3 octal digits; the sign bit of the second octal word is the sign of the exponent. All numbers are normalized.

| 36000000<br>00000004 | .15E2   |

|----------------------|---------|

| 76000000<br>00000004 | 15E2    |

| 36000000<br>00000004 | +.15E+2 |

| 3000000<br>00000001  | .15E1   |

| 31463146<br>54631403 | .1EE0   |

| 71463146<br>54631403 | 1EE+00  |

#### iii) Octal data.

Normal

DAP provides two facilities for generating octal numbers using octal notation: octal literal and the OCT pseudo-operation. The only allowable characters in an octal data field are: + - 0 1 2 3 4 5 6 7

Octal numbers may be signed or unsigned and are limited to a magnitude that is less than  $2^{23}$ .

#### BCI

The BCI (BINARY CODED INFORMATION) pseudo-operation is used to direct DAP to generate binary words from alphanumeric data. The format for using the BCI pseudo-operation is:

| • | LOCATION  | Normal                                                                                                                    |

|---|-----------|---------------------------------------------------------------------------------------------------------------------------|

|   | OPERATION | BCI                                                                                                                       |

|   | VARIABLE  | n, followed by 4n alphanumeric characters. n specifies the number of words to be converted and may not exceed 10 decimal. |

The effect of the BCI pseudo-operation is to convert each group of four characters into a binary word; these words are stored in successively higher storage locations as the variable field is processed from left to right. If there is a symbol in the location field, it refers to the first word of data generated.

#### DEC

The DEC (<u>DECIMAL</u>) pseudo-operation is used to direct DAP to generate binary words from decimal data. The format for using the DEC pseudo-operation is:

| LOCATION  | Normal |

|-----------|--------|

| OPERATION | DEC    |

COMMENTS

VARIABLE One or more subfields, each containing a decimal data item. The

subfields are separated by commas; the number of subfields permissible is limited only by the restriction that the last subfield must be

terminated by a tab code or carriage return.

COMMENTS Normal

The effect of the DEC pseudo-operation is to cause DAP to convert each subfield to one or two binary words depending on the decimal data being fixed-point or floating-point, respectively. These words are stored in successively higher storage locations as the variable field is processed from left to right. If there is a symbol in the Location Field, it refers to the first word of data generated.

OCT

The OCT (OCTAL) pseudo-operation is used to direct DAP to generate binary words from octal data. The format for using the OCT pseudo-operation is:

LOCATION Normal

OPERATION OCT

VARIABLE One or more subfields, each containing an octal data item. The subfields are separated by commas; the number of subfields permissible

is limited only by the restriction that the last subfield must be termi-

nated by a tab code or carriage return.

COMMENTS Normal

The effect of the OCT pseudo-operation is to cause DAP to convert each subfield to a binary word; these words are assigned to successively higher storage locations as the Variable Field is processed from left to right. If there is a symbol in the Location Field, it refers to the first word of data generated.

#### DICTIONARY CONTROLLING PSEUDO-OPERATIONS

The pseudo-operations in this category (CALL, NTRY and RTRN) are used for the generation of subroutine linkage facilities to allow communication between programs.

#### CALL

The CALL (CALL) pseudo-operation is used to direct DAP to generate instructions that will transfer control to a specified subroutine. The format for using the CALL pseudo-operation is:

LOCATION Normal

OPERATION CALL

VARIABLE A subroutine name.

COMMENTS Normal

The effects of the CALL pseudo-operation are:

1) To enter the subroutine name from the Variable Field into the transfer vector if it is not already there.

2) To enter into the sequence of assembled instructions a JST\* with an address that is the transfer vector location containing the Variable Field subroutine name.

3) If there is a symbol in the Location Field, it is assigned to the JST\* instruction inserted in step 2 above.

#### NTRY

The NTRY (ENTRY) pseudo-operation is used to define a DAP subroutine and to symbolically assign a name to the subroutine for external reference. The format for using the NTRY pseudo-operation is:

LOCATION The name of the subroutine

OPERATION NTRY

VARIABLE A name defining the entry point of the subroutine (if left blank, the

first executable instruction of the subroutine will be assumed to be

the entry point).

COMMENTS Normal

The effect of the NTRY pseudo-operation is to cause the name in the Location Field to be punched on the paper tape output as identification for the subroutine library (refer to Section IV). There may be as many NTRY pseudo-operations in a subroutine as there are entry points; however, the NTRY pseudo-operation must be the first operation of the subroutine, preceded only by another NTRY, if present.

#### RTRN

The RTRN (RETURN) pseudo-operation is used to direct DAP to generate an instruction that will transfer control back to a calling program. The format for using the RTRN pseudo-operation is:

LOCATION Normal

OPERATION RTRN

VARIABLE Ignored

COMMENTS Normal

The effect of the RTRN pseudo-operation is to cause a jump instruction to be generated with the appropriate address specified by the use of the NTRY pseudo-operation. There may be more than one RTRN in a subroutine and may be placed anywhere within the subroutine as an exit from the routine.

#### LIST CONTROLLING PSEUDO-OPERATIONS

The pseudo-operations in this category (LIST and NLST) are used to specify the listing options provided in DAP.

#### LIST

The LIST (<u>LISTING</u>) pseudo-operation is used to direct DAP to produce a side-by-side listing of the program being assembled. The format for using the LIST pseudo-operation is:

LOCATION Ignored

OPERATION LIST

VARIABLE Ignored

COMMENTS Normal

The effect of the LIST pseudo-operation is to cause the source program and its octal representation to be listed on the on-line typewriter. The assembler then continues to operate in the "listing" mode until an NLST pseudo-operation is encountered.

#### NLST

The NLST (NO LISTING) pseudo-operation is used to direct DAP to refrain from producing a side-by-side listing of the program being assembled. The format for using the NLST pseudo-operation is:

| LOCATION  | Ignored |

|-----------|---------|

| OPERATION | NLST    |

| VARIABLE  | Ignored |

| COMMMENTS | Normal  |

The effect of the NLST pseudo-operation is to cause DAP not to produce a listing of the source program and its octal representation on the on-line typewriter. The assembler than continues to operate in the "no-listing" mode until a LIST pseudo-operation is encountered (initialization of the assembler automatically sets the "no listing" mode).

#### MACRO DEFINING PSEUDO-OPERATIONS

A macro operation is defined by the use of the MAC and ENDM pseudo-operations. MAC defines the start of the macro operation, identifies the operation by a unique name, and supplies a list of parameters for which symbols may be substituted each time the macro-operation is used. ENDM terminates the definition of the macro-operation. After a macro-operation has been defined, it may be used as often as desired. A macro sequence may be the following:

| MACA | MAC  |   |

|------|------|---|

|      | LDA  | Χ |

|      | ADD  | Y |

|      | STA  | Z |

|      | ENDM |   |

FMB X + 2, 1

Each time the pseudo-operation, MACA, appears in an instruction sequence, it is replaced by the three instructions defined by the above macro. For example, the coded sequence:

READ TWO WORDS

|                       | MACA |          |                |

|-----------------------|------|----------|----------------|

|                       | OTM  | Z        | OUTPUT SUM     |

| would be assembled as | s:   |          |                |

|                       | FMB  | X + 2, 1 | READ TWO WORDS |

|                       | LDA  | X        |                |

|                       | ADD  | Y        |                |

|                       | STA  | Z        |                |

|                       | ОТМ  | Z        | OUTPUT SUM     |

Thus, it is seen that the macro-instruction MACA can be regarded as an abbreviation for a sequence of instructions.

In most instances, it is undesirable to have the repetitive sequence of instructions operate on exactly the same data fields in exactly the same manner each time the macro substitution is used. It would be more convenient if the same general pattern could be repeated, but with certain substitutions depending on the requirements. This type of substitution is possible in the DAP assembly program. The previous example could be expanded in the following manner:

MACA MAC X, OPR, Y, Z

LDA (01)

(02) (04)

STA (03)

ENDM

and used as

FMB P+1

MACA P, SUB, P+1, P+2

OTM P+1

The sequence would then be assembled as:

FMB P + 1, 1

LDA P

SUB P + 2

STA P + 1

OTM P + 1

The sequence of instructions defined as a macro is retained in its external BCD form (including all accompanying remarks) within the computer memory and is processed as if read from an external source each time the macro is used. It therefore behooves the programmer to omit unnecessary comments, lines and fields so as to conserve memory and allow for as many macros as possible.

The rules governing the use of macros in DAP are as follows:

- 1) All macro definitions must appear before the main body of the program.

- 2) Nested macros are not allowed.

- 3) The parameter substitution list is limited to eight fields.

- 4) The number and length of the macros used in a single program are restricted by the available memory size. (It can be seen that by judicious programming, one may make quite efficient use of the available memory size.)

- 5) Parameter substitutions into OCT, DEC, or BCI data fields are not allowed.

- 6) The pseudo-operation END may not appear in a macro skeleton.

MAC

The MAC (MACRO) pseudo-operation is used to define the start of a programmer-defined macro. The format for using the MAC pseudo-operation is:

LOCATION The name of the MACRO

OPERATION MAC

VARIABLE One or more subfields, each containing a symbol (may be "dummy"

parameters)

COMMENTS Normal

The effect of the MAC pseudo-operation is to direct DAP to insert the subsequent instruction into the MACRO table.

#### **ENDM**

The ENDM (END OF MACRO) pseudo-operation is used to define the end of a programmer-defined MACRO. The format for using the ENDM pseudo-operation is:

LOCATION Ignored

OPERATION ENDM

VARIABLE Ignored

COMMENTS Normal

The effect of the ENDM pseudo-operation is to terminate the effect of the preceding MAC pseudo-operation.

#### STORAGE ALLOCATION PSEUDO-OPERATIONS

The pseudo-operations in this category (BES, BSS and COMN) are used for allocating storage for arrays of one or more elements.

BES

The BES (BLOCK ENDING WITH SYMBOL) pseudo-operation is used for reserving storage locations:

The format for using the BES pseudo-operation is:

LOCATION Normal

OPERATION BES

VARIABLE Any absolute expression. Any symbol used in this field must have

been previously defined.

COMMENTS Normal

The effect of the BES pseudo-operation is to increase the value of the location counter by the value of the expression in the Variable Field. If there is a symbol in the Location Field, it is assigned the value of the Location Counter after the increase.

The BSS (BLOCK STARTING WITH SYMBOL) pseudo-operation is used for reserving storage locations. The format for using the BSS pseudo-operation is:

LOCATION Normal

OPERATION BSS

VARIABLE Any absolute expression. Any symbol used in this field must have

been previously defined.

COMMENTS Normal

The effect of the BSS pseudo-operation is to increase the value of the Location Counter by the value of the expression in the Variable Field. If there is a symbol in the Location Field, it is assigned the value of the Location Counter before the increase.

#### COMN

The COMN (COMMON) pseudo-operation is used for absolutely assigning storage locations in upper memory. The format for using the COMN pseudo-operation is:

LOCATION Normal

OPERATION COMN

VARIABLE Any absolute expression. Any symbol used in this field must have

been previously defined.

COMMENTS Normal

The effect of the COMN pseudo-operation is to cause DAP to subtract the value of the expression in the Variable Field from the COMMON base and assign this value to the symbol in the Location Field. COMMON base is a user option, but is assumed to be the address of the last memory location in the standard version of DAP. The COMN pseudo-operation establishes a common data "pool" that may be referenced by several programs.

#### SYMBOL DEFINING PSEUDO-OPERATION

The pseudo-operation in this category (EQU) is used for assigning an absolute or relocatable value to a symbol.

#### EQU

The EQU (EQUALS) pseudo-operation is used for defining a value for a symbol that is referred to by other DAP operations. The format for using the EQU pseudo-operation is:

LOCATION Normal

OPERATION EQU

VARIABLE Any absolute or relocatable expression. Any symbol used in this field

must have been previously defined.

COMMENTS Normal

The EQU pseudo-operation causes DAP to evaluate the Variable Field expression for value and mode and assigns the value and mode to the Location Field symbol.

#### SECTION IV

## **SUBROUTINES**

#### GENERAL

A sizeable body of subroutines is available to the DAP programmer. These include floating point, double precision and transcendental functions. Other subroutines may be added to suit the requirements of a particular installation.

A list of DDP-24 subroutines and information concerning their use is included in the DEP and Utility Manual.

Subroutines are called by using the CALL pseudo-operation in the regular programming sequence. DAP automatically generates the correct machine language instruction for the link between the main program and the subroutine.

When a subroutine is called within a program, DAP adds the reference to a table called the "transfer vector" and replaces the CALL with the machine language instruction, JST\* A, where A is the address of the "transfer vector" table entry. Subsequent CALLs to the same subroutine will use the same table entry. When the END pseudo-operation is encountered, the "transfer vector" is tested to see if a subroutine was called. If no subroutine has been called, the assembly is terminated. If one or more subroutines have been called, the assembler requests that the subroutine library be mounted. The library is then scanned and the subroutines are added as part of the main program. If a called subroutine contains a CALL to a subroutine not used by the main program, this additional subroutine is also extracted from the library and punched as part of the program.

Figure 3 shows the memory layout of a program containing CALL's to two subroutines; each subroutine in turn calls one additional subroutine. Let the first two subroutines be names SUB1 and SUB2; SUB1 calls SUB3 and SUB2 calls SUB4. The subroutine library, in this example, contains the subroutines in the order of: SUB4, SUB3, SUB2, SUB1.

| MAIN PROGRAM                  |

|-------------------------------|

| LITERALS                      |

| MAIN PROGRAM TRANSFER VECTORS |

| SUB4                          |

| SUB3                          |

| SUB2                          |

| SUB2 TRANSFER VECTOR          |

| SUBl                          |

| SUB1 TRANSFER VECTOR          |

Figure 3. Memory Layout

#### SUBROUTINE LIBRARY

The subroutine library is contained on a punched paper tape, and is composed of two principal parts: 1) the library directory and 2) the subroutine programs.

#### LIBRARY DIRECTORY

The library directory consists of a set of tables defining each of the subroutines in the main body of the library. The tables contained in the directory are each two or more words in length. The first word contains the BCD name of the subroutine; the second word is divided into three fields -- these fields contain:

- 1) The number of computer words in the subroutine.

- 2) The number of erasable memory positions used by the subroutine.

- 3) A number, N, indicating any additional subroutines that are called by the current subroutine. N may be zero.

The remainder of the table is N words in length, where N is defined as in 3) above. Each word in this part of the table is a BCD subroutine name.

#### SUBROUTINE PROGRAMS

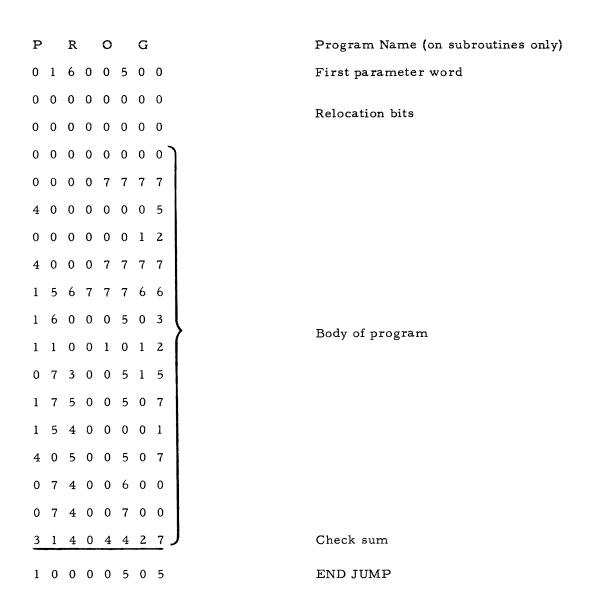

The program part of the subroutine library is made up of relocatable, assembled programs in a special format. This special format is supplied automatically by the assembly program when the pseudo-operation NTRY precedes a program to be assembled.

The first word of each program in the subroutine library is the BCD name of the subroutine. The second word is a parameter containing the number of erasable memory positions used by the subroutine in its address portion, and the number of COMN memory words used by the subroutine in the remainder of the word. With these specific exceptions, the relocatable subroutine programs are punched in the standard format.

#### UTILITY UPDATER

The Utility Updater may be used to duplicate, add to, or delete from the 3C subroutine library; control is exercised through the console typewriter. Stacked library modifications are possible; that is, one may make multiple insertions and/or deletions with a single pass over the library tape. The extent of this facility is limited only by the available memory size.

#### SUBROUTINE LIBRARY CHANGES

After the library updater has been called from the system tape, it will print on the typewriter:

#### ENTER INSTRUCTION:

The operator may then type in one of several instruction formats:

- 1) DUPLICATE

- 2) DELETE AAAA

- 3) INSERT AAAA AFTER BBBB

- 4) LIBRARY

<u>DUPLICATE</u>. After this instruction has been typed in, the machine will execute a HLT so that a paper tape may be mounted on the reader. Pressing the Program Start button on the console will then cause an identical copy of the input tape to be punched.

"DUPLICATE" will operate on an input tape of any format. The "DUPLICATE" operation will over-ride any previous instructions that may have been given to the update routine.

<u>DELETE AAAA</u>. After this instruction has been typed in, the machine will store the information, return the typewriter carriage and again type:

#### ENTER INSTRUCTION:

INSERT AAAA AFTER BBBB, CCCC AFTER DDDD, ---. After this instruction, followed by a period, has been typed in, the computer will execute a HLT so that the tape containing the new subroutines may be mounted on the reader. Pressing the Program Start button on the console will then cause the mounted paper tape to be read. The desired routines will be extracted and stored, the typewriter carriage will be returned, and the machine will type:

Remaining Storage: XXXXX

ENTER INSTRUCTION:

Since one or more programs may be read from a single tape it is possible to merge libraries each of which contain several subroutines.

It is possible to insert a new subroutine as the first routine of the new library by entering the instruction as:

INSERT AAAA AFTER 0000,

using four zeros as the second name in the instruction.

Note that one need not merge all the subroutines from the input tape; it is possible to request only certain ones. Any others will be ignored.

LIBRARY. After this instruction has been typed in, the machine will execute a HLT so that the sub-routine library may be mounted on the reader. Pressing the console Program Start button will cause the old library to be read and a new library with the requested modifications to be punched. The type-writer will list the subroutines in the order that they appear in the new library. The machine will then type:

LIBRARY UPDATE COMPLETED

and execute a HLT.

#### SECTION V

## DAP OPERATING PROCEDURES

#### GENERAL

A DAP source program is prepared on the coding form previously described. It consists of a set of symbolic instructions and pseudo-operations terminated by an END pseudo-operation. (The pseudo-operation MOR is substituted under certain conditions; see below under sense switches.) The program is then punched into a paper tape called the source tape.

The utility tape is loaded into the tape reader and DAP is called into memory; the computer then halts so that the source tape may be mounted. Pressing the start button on the console then allows DAP to begin the assembly.

#### ASSEMBLER OPERATION

DAP is a two-pass assembly program; that is, the source program is fully scanned twice before the completed program is ready to load and execute. In general, this implies that the operator must manually remove the source program and replace it in the tape reader for the second pass. However, within the computer memory capabilities, it is possible for small programs to avoid this manual step by retaining the entire source program in memory. This is done automatically by DAP whenever possible.

When a source program calls for a subroutine, the operator must mount the subroutine library before the assembly can be completed (refer to Section IV).

#### SENSE SWITCHES

Most of the functions of DAP are automatic; however, certain options are available to the operator through the use of the computer console sense switches. The use of the sense switches is given in the following table.

| S.S. No. | Condition | Meaning                           |  |  |  |

|----------|-----------|-----------------------------------|--|--|--|

| 1        | Down      | Listing is under program control. |  |  |  |

|          | Up        | All input is listed.              |  |  |  |

| 2        | Down      | Listing is under program control. |  |  |  |

|          | Up        | All listing is suppressed.        |  |  |  |

| 3        | Down      | Punching is normal.               |  |  |  |

|          | Up        | Punching is suppressed.           |  |  |  |

| 4        | Down      | MOR pseudo-op is normal.          |  |  |  |

|          | Up        | No halt on MOR.                   |  |  |  |

| 5        | Down      | MOR pseudo-op is normal.          |  |  |  |

|          | Up        | MOR pseudo-op = END.              |  |  |  |

#### ASSEMBLER PRODUCTS

Output from the DAP assembly program consists of a tabular on-line typewriter listing and a punched paper tape.

#### LISTING

The DAP printed output is called the assembly listing. It is a printing of the symbolic input instructions in the order in which they appeared together with the octal representation of the binary words produced by the assembler. A sample listing is shown in Figure 4.

The portion of the listing that is produced by the assembly appears on the left; the margin contains error symbols. The first column contains the line ID number -- an identification provided for the Source Program Update routine. The next column shows the location of each instruction; and, finally, in octal, the binary word assigned to the location. The machine operations are subdivided into separate subfields; numbers are given as eight octal digits with the appropriate sign; BCI words are eight digit logical groups.

The portion of the assembly listing appearing on the right is a copy of the original source program input. This part of the listing will be truncated on the right if the entire line exceeds the carriage capacity of the typewriter.

The assembler will indicate minor errors that occur in individual lines by inserting up to three flags in the left hand margin of the assembly listing (refer below to DIAGNOSTICS).

| 001 |                                                                           |                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ORG                                                                                                                                                                                                                                                                                                                                    | 320                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 002 | 00500                                                                     | +00000000                                                                                                                                                                                                                                                                                                           | OCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OCT                                                                                                                                                                                                                                                                                                                                    | +0, 7777, -5                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 00501                                                                     | +00007777                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

|     | 00502                                                                     | -00000005                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

| 003 | 00503                                                                     | +00000012                                                                                                                                                                                                                                                                                                           | XCON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DEC                                                                                                                                                                                                                                                                                                                                    | +10, -4095                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 00504                                                                     | -00007777                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                |

| 004 | 00505                                                                     | 0 1 56 77766                                                                                                                                                                                                                                                                                                        | STRT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LDX                                                                                                                                                                                                                                                                                                                                    | -10, 1                                                                                                                                                                                                                                                                                                                                                                                         |

| 005 | 00506                                                                     | 0 1 60 00503                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | CRA                                                                                                                                                                                                                                                                                                                                    | XCON, 1                                                                                                                                                                                                                                                                                                                                                                                        |

| 006 | 00507                                                                     | 0 1 10 01012                                                                                                                                                                                                                                                                                                        | RUTN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADD                                                                                                                                                                                                                                                                                                                                    | TABL+12, 1                                                                                                                                                                                                                                                                                                                                                                                     |

| 007 | 00510                                                                     | 0 0 73 00515                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JOF                                                                                                                                                                                                                                                                                                                                    | EXT2                                                                                                                                                                                                                                                                                                                                                                                           |

| 008 | 00511                                                                     | 0 1 75 00507                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | JXI                                                                                                                                                                                                                                                                                                                                    | RUTN, 1                                                                                                                                                                                                                                                                                                                                                                                        |

| 009 | 00512                                                                     | 0 1 54 00001                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADX                                                                                                                                                                                                                                                                                                                                    | 1, 1                                                                                                                                                                                                                                                                                                                                                                                           |

| 010 | 00513                                                                     | 0 1 05 00507                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STA*                                                                                                                                                                                                                                                                                                                                   | RUTN                                                                                                                                                                                                                                                                                                                                                                                           |

| 011 | 00514                                                                     | 0 0 74 00600                                                                                                                                                                                                                                                                                                        | EXTl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JMP                                                                                                                                                                                                                                                                                                                                    | RETN                                                                                                                                                                                                                                                                                                                                                                                           |

| 012 | 00515                                                                     | 0 0 74 00700                                                                                                                                                                                                                                                                                                        | EXT2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SMP                                                                                                                                                                                                                                                                                                                                    | EROR                                                                                                                                                                                                                                                                                                                                                                                           |

| 013 |                                                                           | 00505                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | END                                                                                                                                                                                                                                                                                                                                    | STRT                                                                                                                                                                                                                                                                                                                                                                                           |