## PERIPHERAL EQUIPMENT DIVISION

FOR

MODEL 5091-PDP8e

MAGNETIC TAPE CONTROLLER

PUBLICATION NUMBER 1219.3

## ADDENDUM

The jumper table below is the standard configuration for the PDP-8E

Tape Controller and is the way the unit will be shipped unless specific differences are called for by the customer.

| BOARD | JUMPER POINTS | CONFIGURATION | RESULT                                            |

|-------|---------------|---------------|---------------------------------------------------|

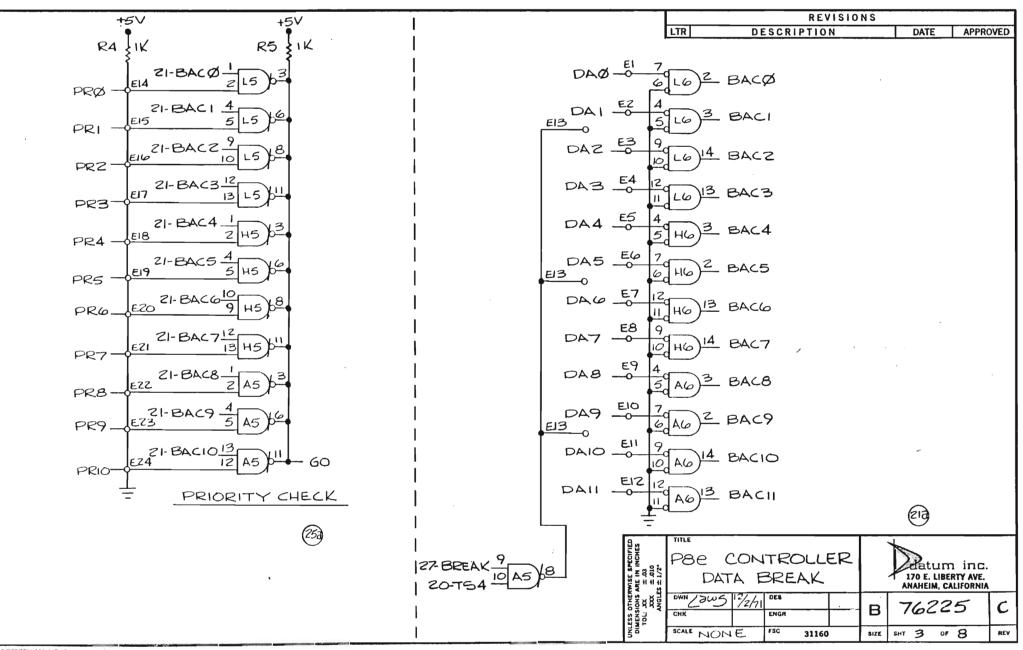

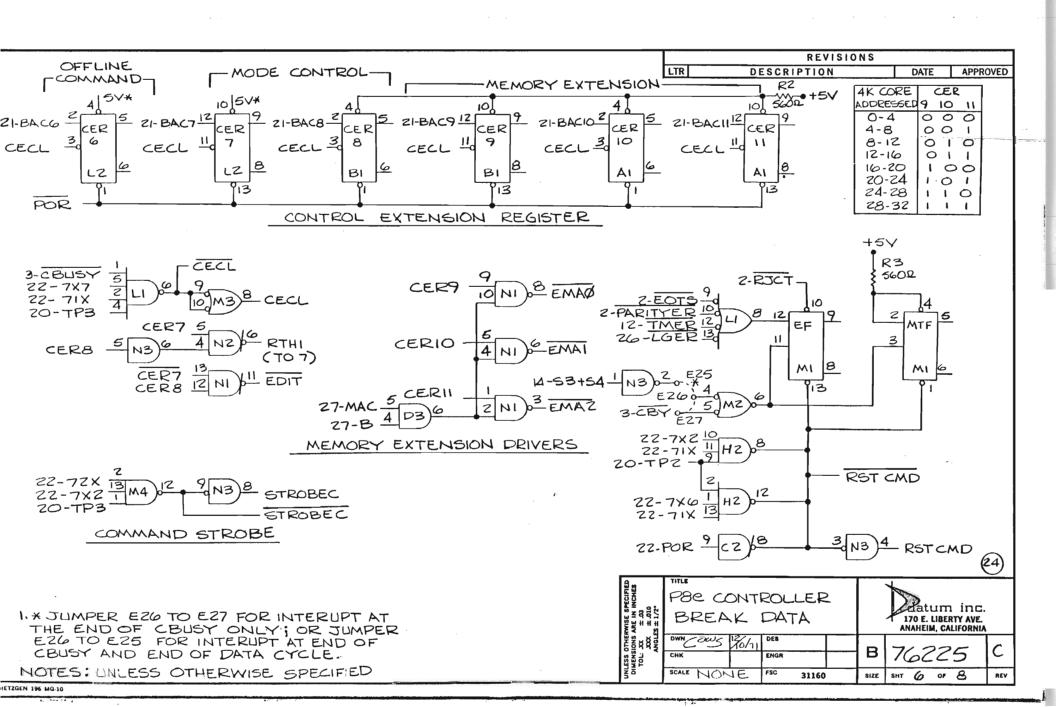

| 76225 | El thru El3   | 0pen          | No Priority Selection                             |

|       | E14 thru E24  | No etch cut   | No Priority Check                                 |

|       | E25 to E26    | Open          | No Interrupt at End of<br>Data Cycle              |

|       | E26 to E27 NÕ | Jumpered      | Interrupt at end of CBUSY                         |

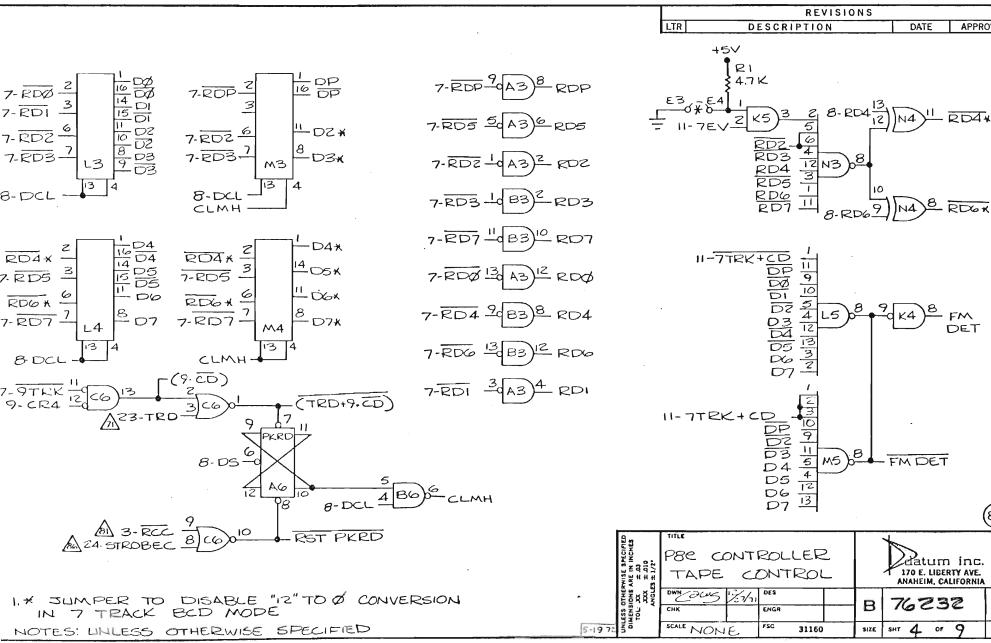

| 76232 | El to E2      | Open          | No 7-track file mark<br>in 9-track core dump mode |

|       | E3 to E4      | 0pen          | 0 to 12 Conversion enabled                        |

| 76233 | El to E2      | Jumpered      | Check Vertical Parity on file marks               |

|       | E3 to E4      | 0pe <b>n</b>  | Read after write present                          |

## TABLE OF CONTENTS

| Section |                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>Page</u>                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 1       | GENERAL DE                                                                                                                                                                                                                                        | ESCRIPTION AND SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                         |

|         | 1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                                                                          | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-1<br>1-2                                                              |

| 11      | INTERFACE                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                         |

|         | 2.1<br>2.2<br>2.2.1<br>2.2.1.1<br>2.2.1.2<br>2.2.1.3<br>2.2.2<br>2.2.2.1<br>2.2.2.2                                                                                                                                                               | Introduction Formatter/Transport(s) Interface Formatter to Transport Transport Address Control Write Data Transport to Formatter Status Lines Read Data and Read Clock Read Data and Clock                                                                                                                                                                                                                                                                      | 2-1<br>2-1<br>2-1<br>2-2<br>2-3<br>2-4<br>2-4<br>2-5                    |

| 111     | THEORY OF                                                                                                                                                                                                                                         | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                         |

|         | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.2.17<br>3.2.18<br>3.2.17<br>3.2.18<br>3.2.19<br>3.2.10<br>3.2.17<br>3.2.18 | Introduction Block Diagram Command Register and Valid/Reject Logic CBUSY Transport Control Formatter Select Tape Unit Select State Counter and Main Control Status Register Parity Control Parity Error Detect Character Parity Check LRC Check Read Data Storage Register Read Clock Activity Sense File Mark Detect Read Control Logic Write Storage-Register Parity Generator Write Data Select Gates File Mark Generator CRCC Generator Write Control Logic | 3-2<br>3-3<br>3-3<br>3-3<br>3-3<br>3-6<br>3-7<br>7<br>3-7<br>3-8<br>3-9 |

# TABLE OF CONTENTS (Cont'd)

| <u>Section</u> |                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                                                                                                               |

|----------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 1,11           | 3.2.2.24<br>3.2.2.26<br>3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3.3. | Crystal Oscillators and Tape Speed Select Density Select Data Transfer Control Delay Counter Inter Record Gap Detector Commands Basic Commands Read and Space Write, Erase 3 Inch Gap and Write File Mark Rewind and Offline Command and Mode Combinations State Flow Simplified State Flow Detailed State Flow Command Execution Timing Rewind (With Interrupt) Write File Mark (7-Track) Write File Mark (9-Track) Forward Space/Record Backspace/Record Backspace/Record (7-Track) Write/Record (9-Track) Read-One-Record (7-Track) Read-One-Record (7-Track) Erase 3-Inch Gap Continuous Write or Read Options Tape Speed Dual Densities Single/Dual-Stack Head Selection BCD 10 to Zero Converter No Parity Error for File Mark Delay Times Computer Adapter Section Computer Adapter Operation Block Diagram of Computer Adapter Logic Input/Output Transfer (10T) Control Pulses AC Outputs AC Outputs AC Inputs Interrupt/Skip Data Transfer Break Requests Programmed I/O 10T Instructions Skip on Error Flag (EF) or Mag Tape Flag (MTF). | 3-12<br>3-13<br>3-13<br>3-13<br>3-14<br>16<br>16<br>19<br>10<br>10<br>11<br>11<br>11<br>11<br>11<br>11<br>11<br>11 |

## TABLE OF CONTENTS (Cont'd)

| Section |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | Page                                     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|

|         | 3.9.9.2<br>3.9.9.3<br>3.9.9.4<br>3.9.9.5<br>3.9.9.9.6<br>3.9.9.9.9<br>3.9.9.9.9<br>3.9.9.9.10<br>3.9.9.12<br>3.9.9.13<br>3.9.14<br>3.9.16<br>3.9.17<br>3.9.18<br>3.9.18<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.23<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3.9.24<br>3 | Space Reverse | 3-4-4-2-2-3-4-4-4-4-4-4-4-4-4-4-4-4-4-4- |

| [17     | אויז אוינ כ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                          |

APPENDIX A REPLACEMENT PARTS

## TABLE OF CONTENTS (Contid)

# List of Figures

| <u>Figure</u> |                                                 | <u>Page</u>    |

|---------------|-------------------------------------------------|----------------|

| 1-1           | Installation of Model 5091 NRZI Controller      | 1-2a           |

| 1-2           | Wang NRZ Transport Interface Cable Connections  | 1-2b           |

| 1-3           | Interface Circuits                              | 1 <b>-</b> 3a  |

| 1-4           | 7-Track Format                                  | 1-3b           |

| 1-5           | 9-Track Format                                  | 1-3c           |

| 3-1           | NRZI Formatter Block Diagram                    | 3-1a           |

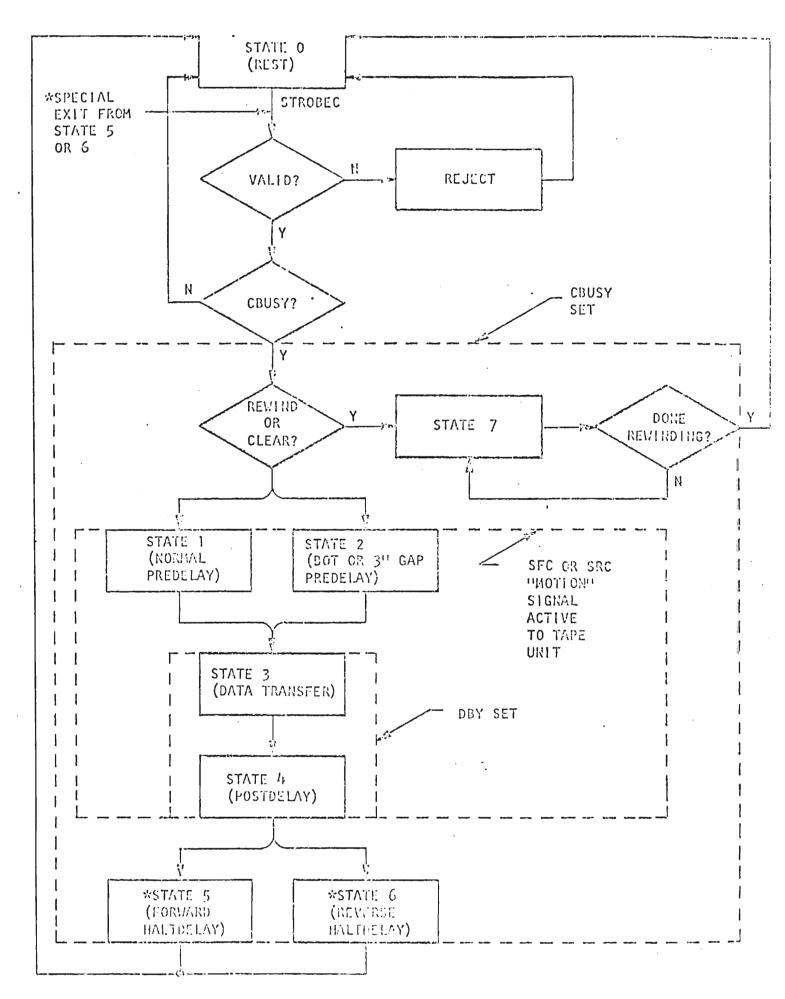

| 3-2           | Simplified State Flow                           | 3-16a          |

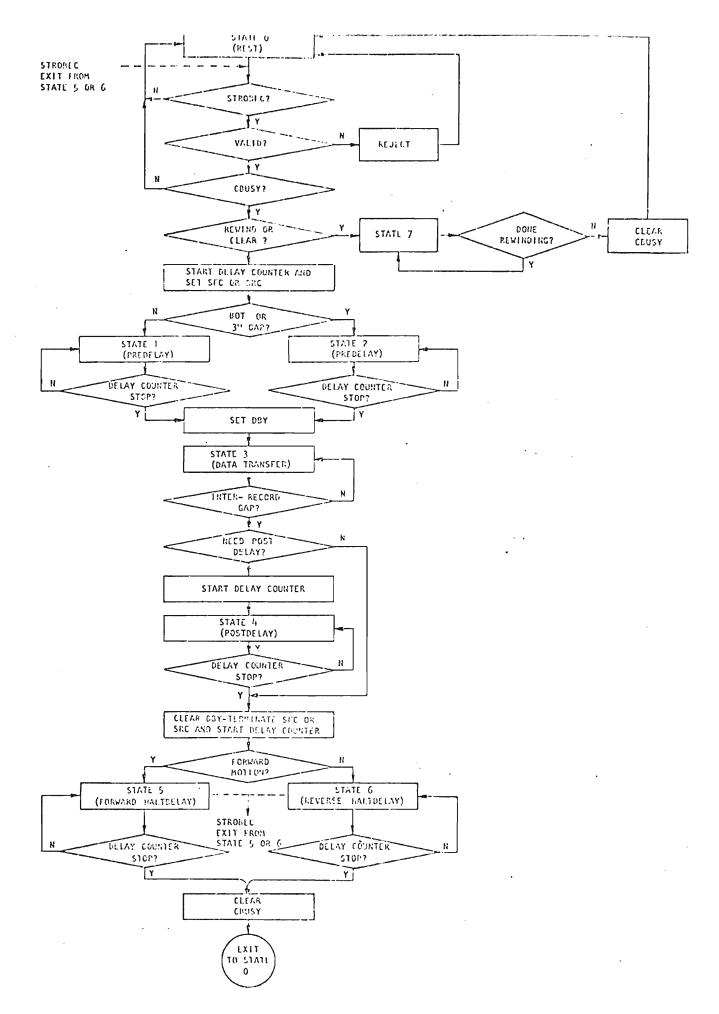

| 3-3           | Detailed State Flow                             | 3-19a          |

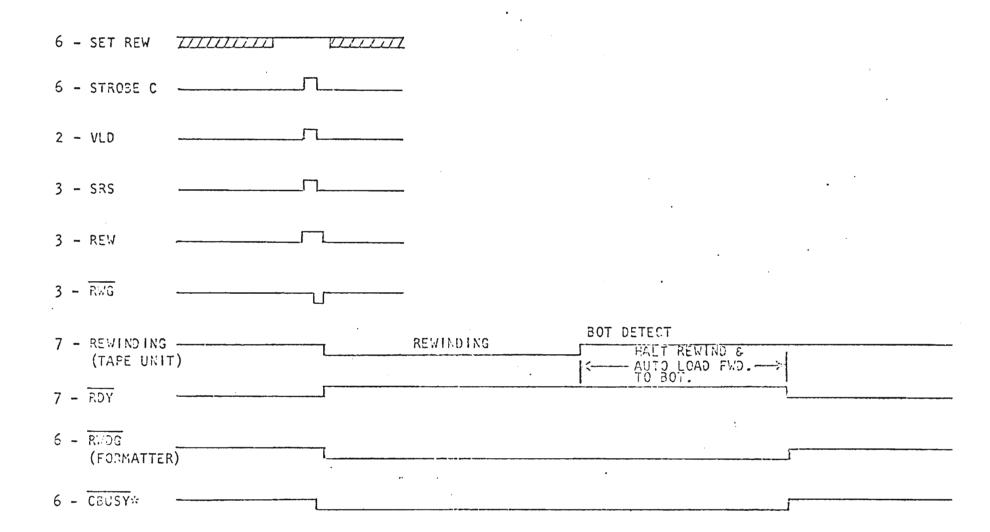

| 3-4           | Rewind Timing Diagram                           | 3-21a          |

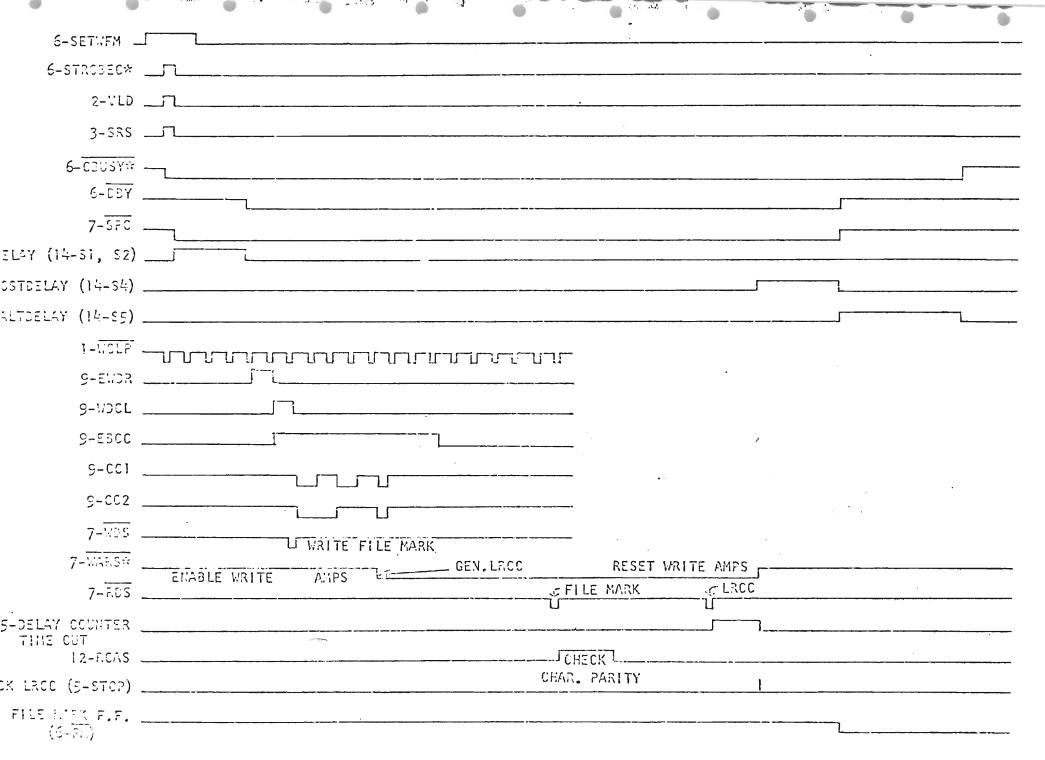

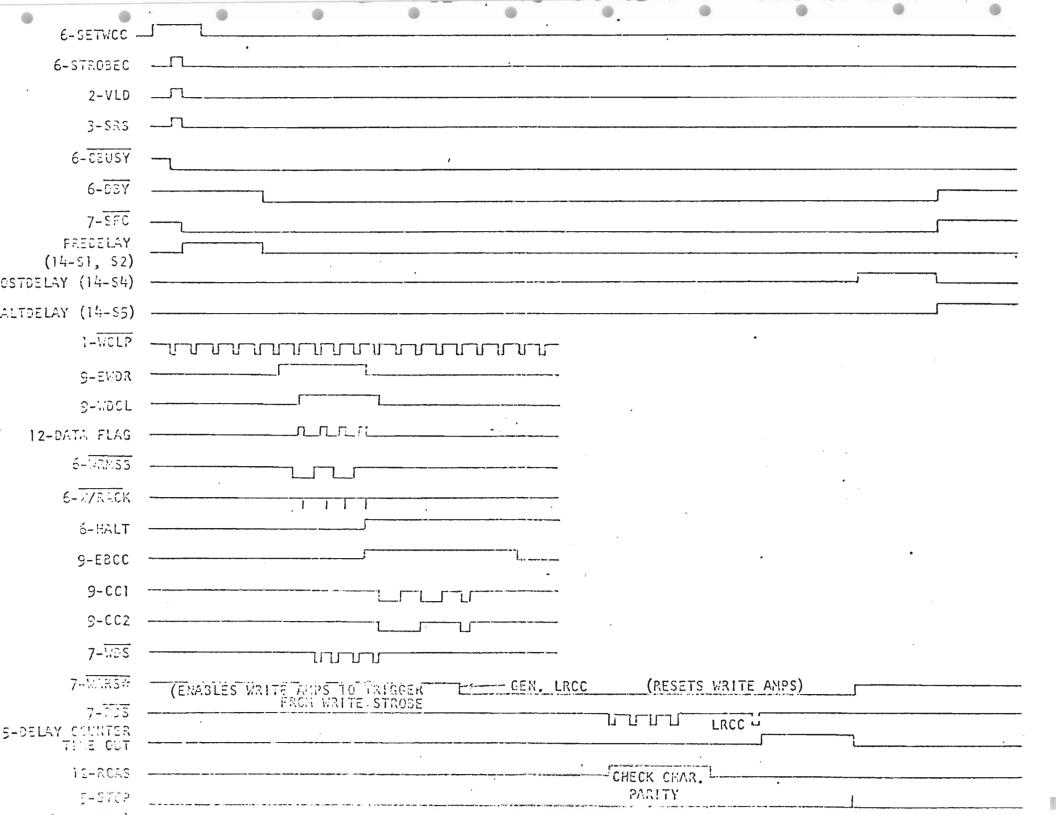

| 3-5           | Write File Mark Timing Diagram (7 Track Mode)   | 3 <b>-</b> 22a |

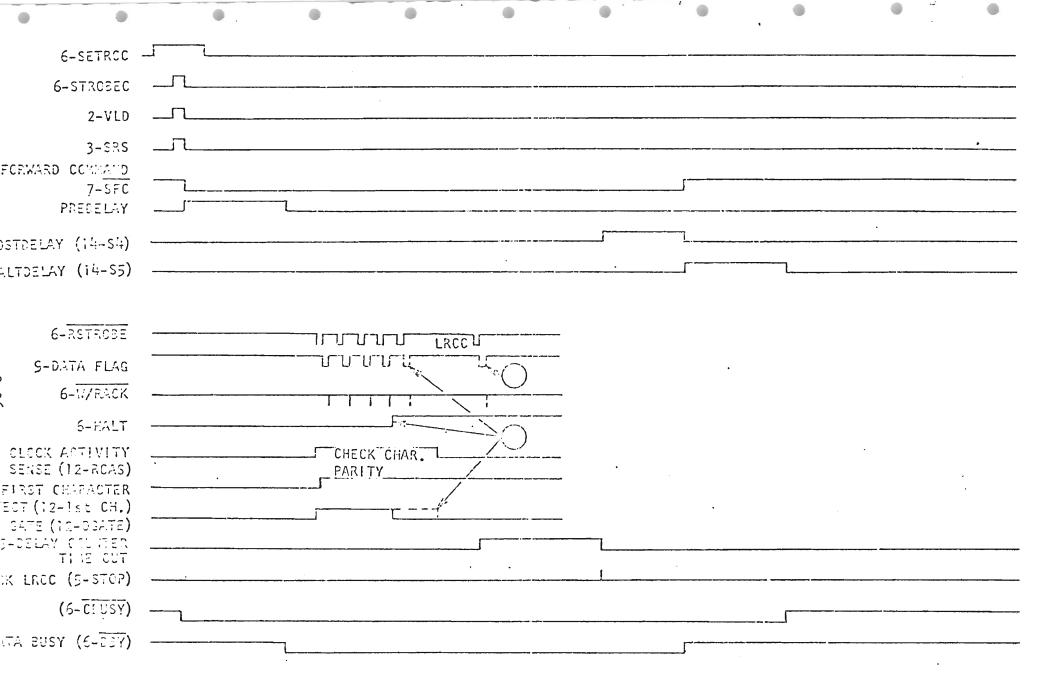

| 3-6           | Forward Space One Record Timing Diagram         | 3-23a          |

| 3-7           | Write One Record Timing Diagram (7 Track Mode)  | 3-24a          |

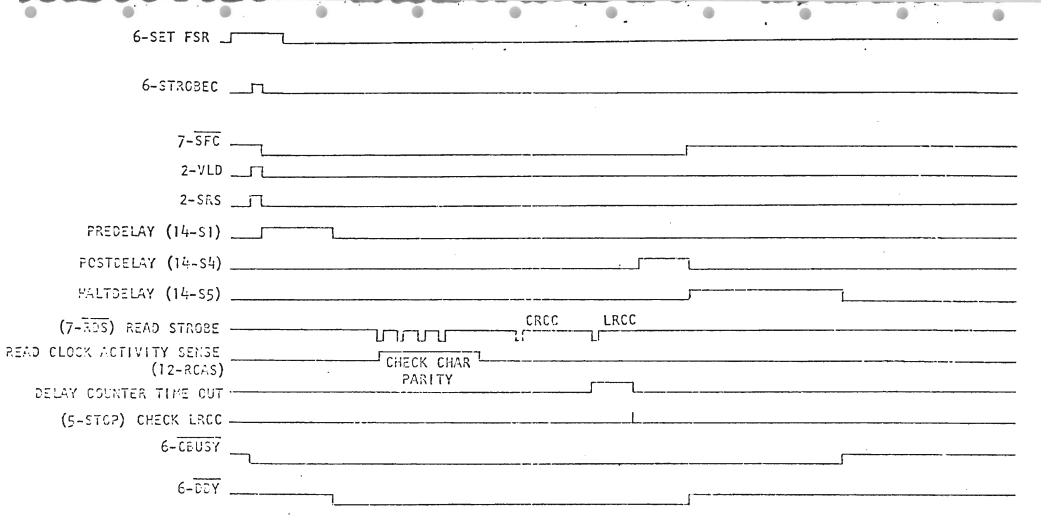

| 3-8           | Read One Record Timing Diagram (7 Track Mode)   | 3 <b>-</b> 26a |

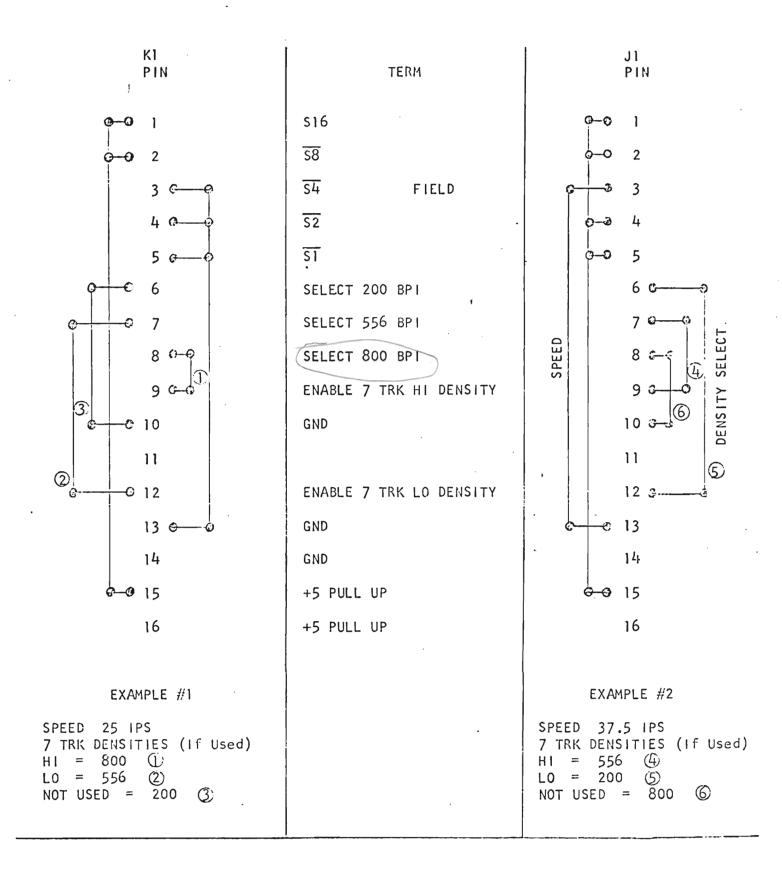

| 3-9           | Example Tape Speed Selection                    | 3-31a          |

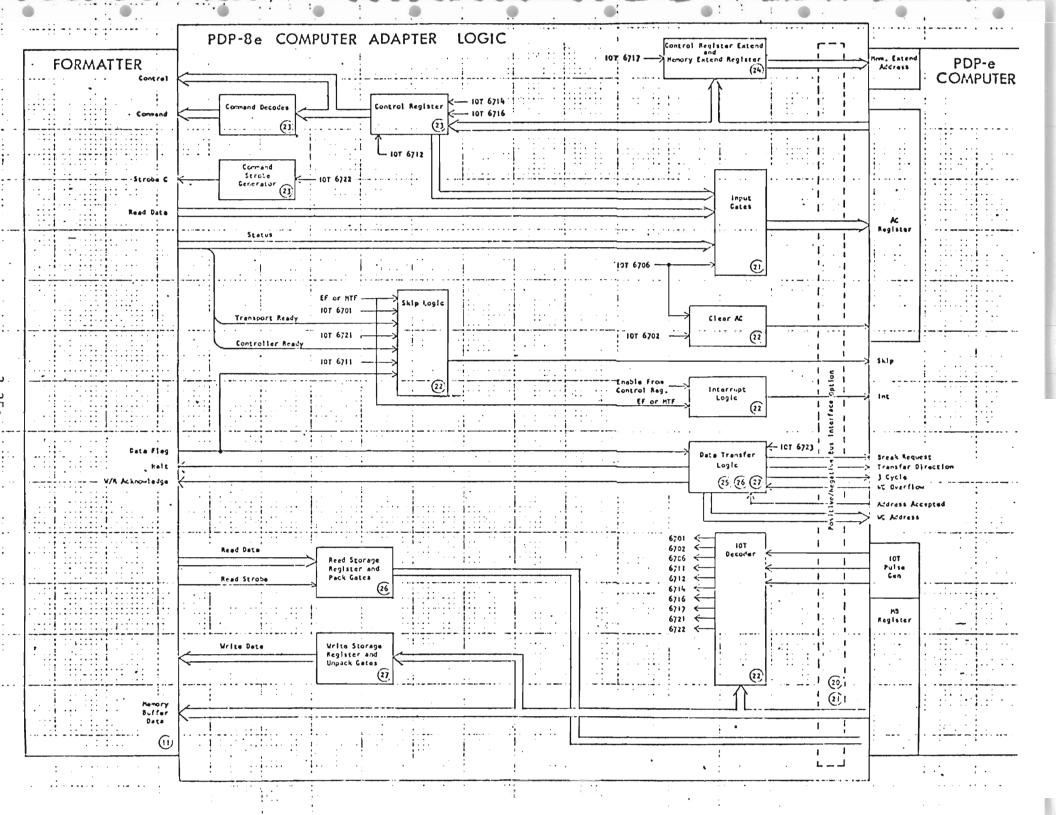

| 3-10          | PDP8e Computer Adapter Simplified Block Diagram | 3 <b>-</b> 35a |

## List of Tables

| <u>Table</u> |                             | <u>Page</u> |

|--------------|-----------------------------|-------------|

| 3-1          | Command & Mode Combinations | 3-15        |

| 3-2          | Tape Speed Selection        | 3-31        |

#### SECTION I

#### GENERAL DESCRIPTION AND SPECIFICATIONS

#### 1.1 FUNCTIONAL DESCRIPTION

The DATUM PDP8e Controller provides interface between the DEC PDP8e computer and 9-track, 800 BPI and/or 7-track 800/556/200 BPI tape machines, enabling computer-control of writing and reading IBM- or USACCII-compatible magnetic tapes.

All major operations are performed automatically under command of the Controller. Individual selection and operation with up to four "Daisy-Chained" tape transports is provided. Either single- or dual-gap machines can be accommodated.

Tape transport motion control, Cyclic Redundancy Check Character (CRCC) and Longitudinal Redundancy Check Character (LRCC) generation and checking, inter-record-gap generation and status reporting are included. All Write clocks and delay times are derived from a crystal-controlled oscillator. No "one-shots" or RC delays are utilized.

The unit plugs directly into the computer omnibus and uses computer power.

"On the Fly" operation (continuous read or write at maximum tape speed without stopping in each inter-record gap) is provided.

The IBM-compatible file mark (7- or 9-track formats) is written and recognized.

The "Edit" feature (allows a record anywhere on a previously recorded tape to be replaced with an updated record of equal size) is provided.

No calibration or adjustment potentiometers in the Formatter.

All timing is derived from a crystal oscillator.

Compatible to entire 12.5 to 75-ips tape-speed range without changing crystals. A single field-changeable jumper selects the frequencies needed for the tape speed.

#### 1.2 PHYSICAL DESCRIPTION

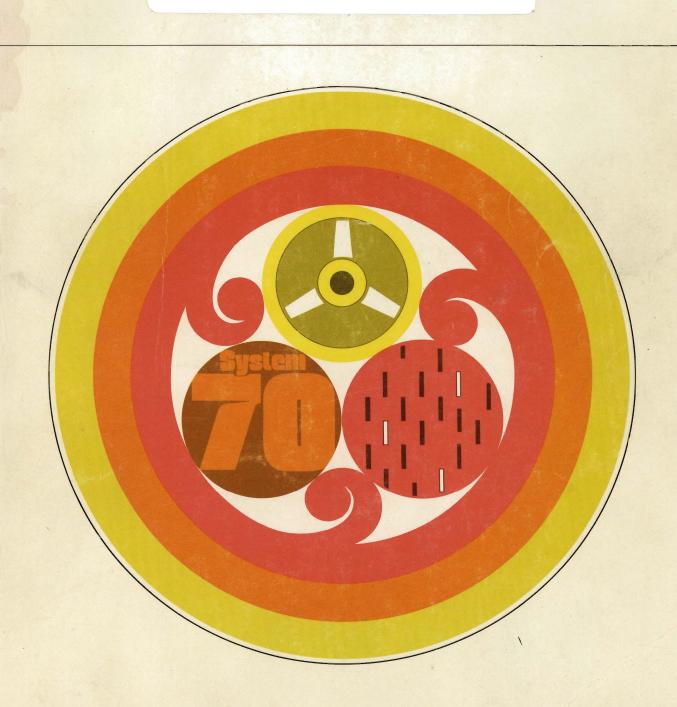

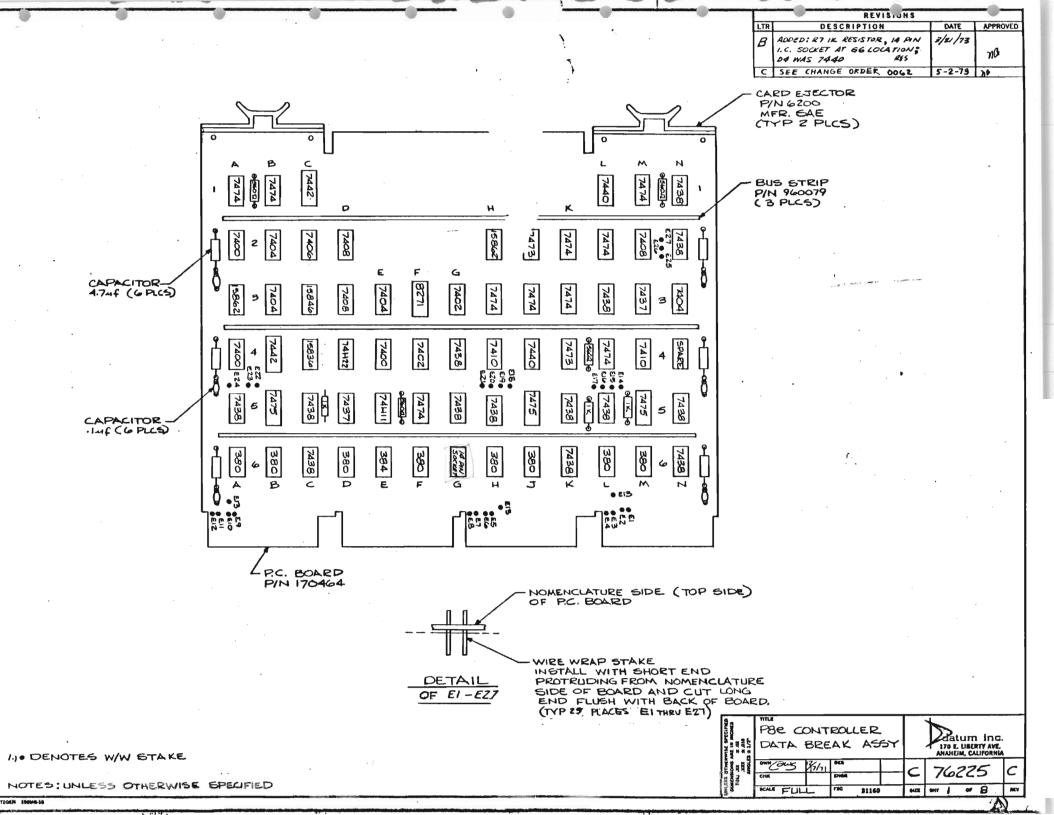

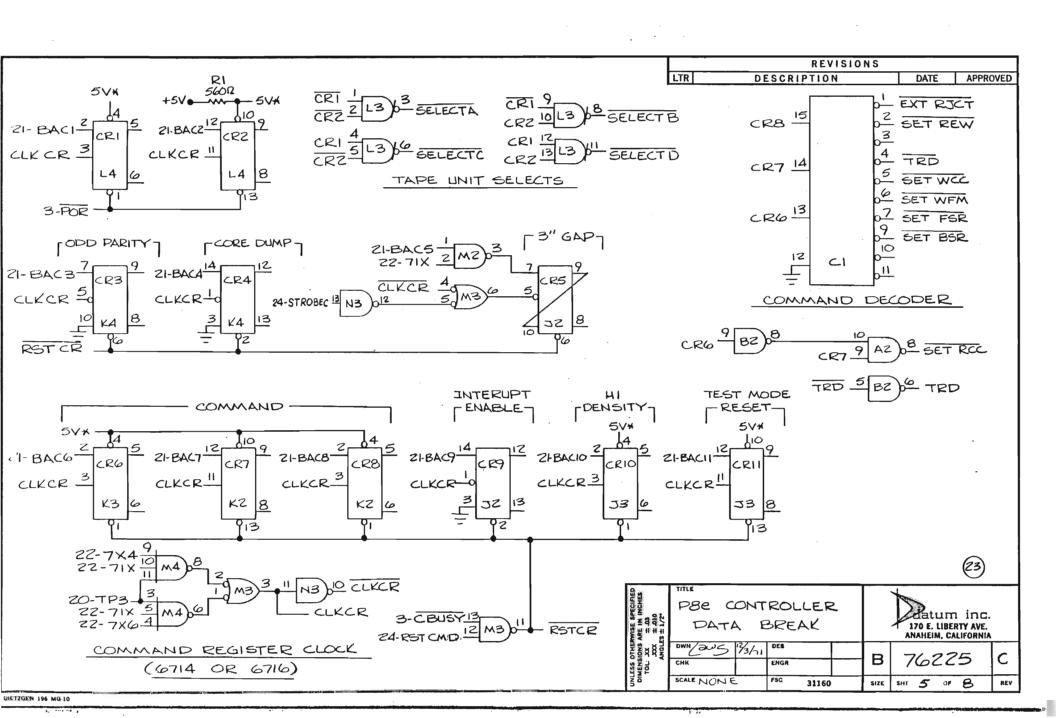

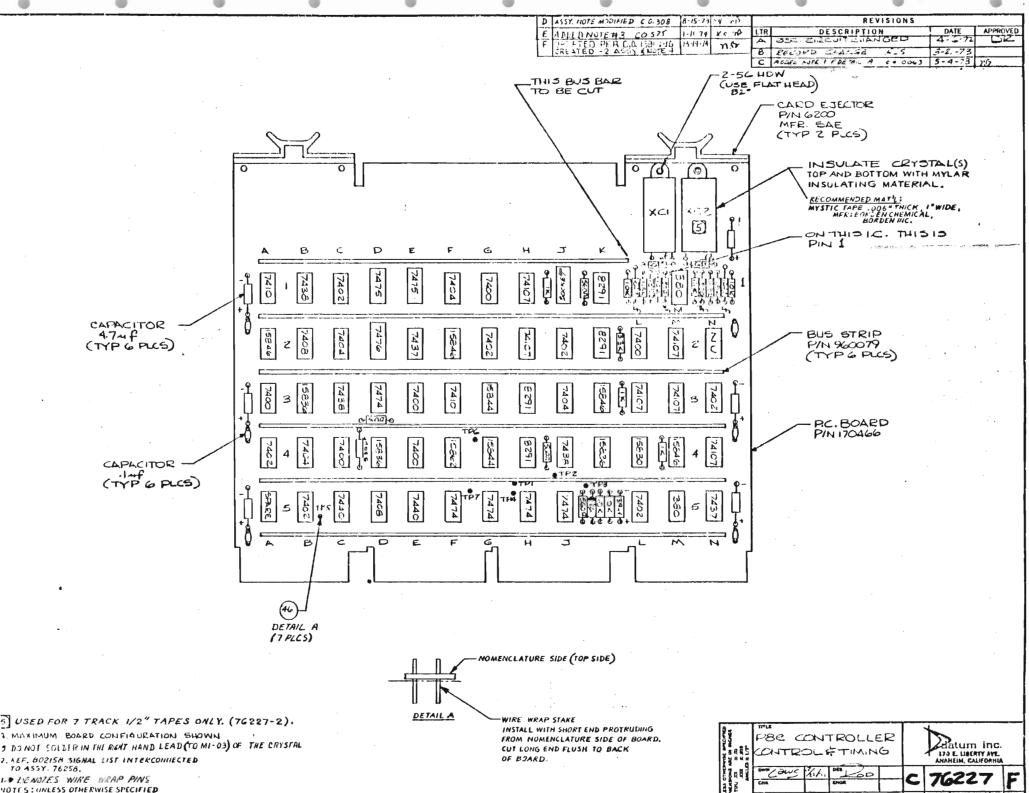

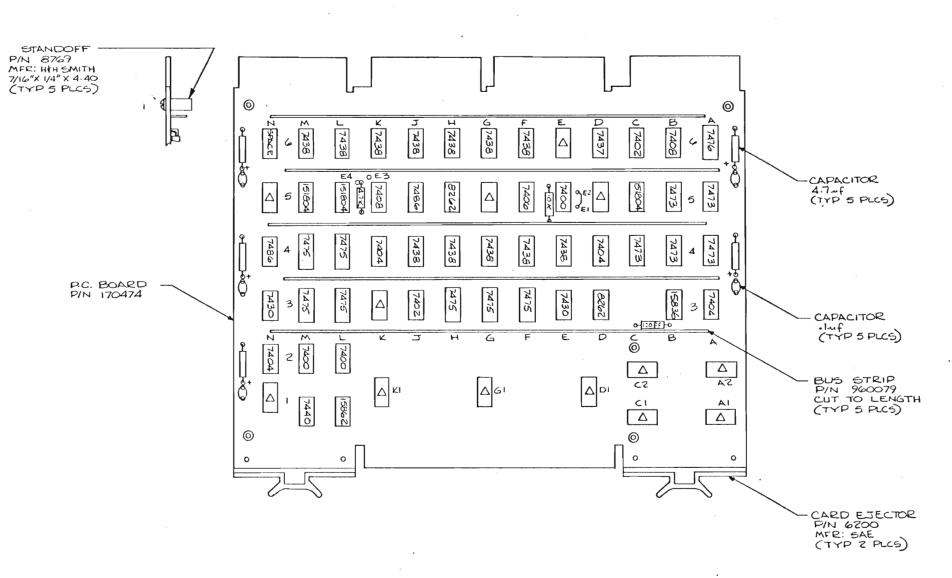

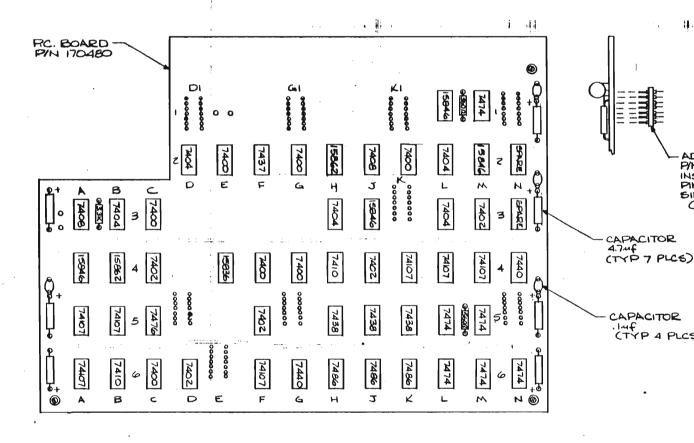

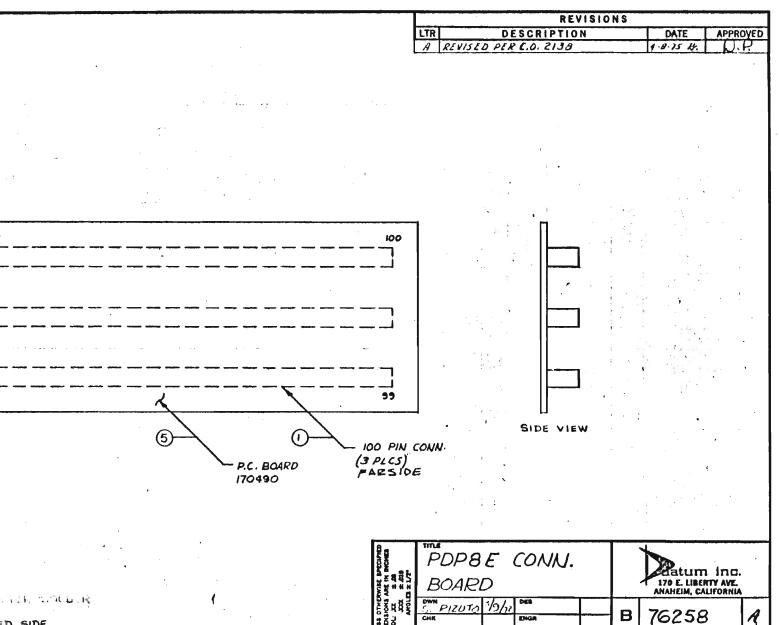

The DATUM Model 5091 NRZ1 Controller, complete on three large circuit boards, is designed to be installed in the PDP8e computer mainframe. Figure 1-1 shows this installation.

#### 1.3 SPECIFICATIONS

| Inter-record gap (7 track)                   | .75 inch nominal (.69 inch minimum) |

|----------------------------------------------|-------------------------------------|

| Inter-record gap (9 track)                   | .6 inch nominal (.54 inch minimum)  |

| Circuits                                     | All silicon                         |

| Operating Temperature                        | 0° to 50° C                         |

| Storage Temperature                          | <b>-</b> 40° to +70° C              |

| Altitude                                     | 0 to 20,000 feet                    |

| Relative Humidity                            | 10 to 95% (non-condensing)          |

| Interface Voltages<br>(DTL 900 series or TTL |                                     |

| 7400 series compatible)                      | $low = 0V \pm .4V$                  |

|                                              | $high = 3.9V \pm 1.5V$              |

Figure 1-1. Installation of Model 5091 NRZI Controller

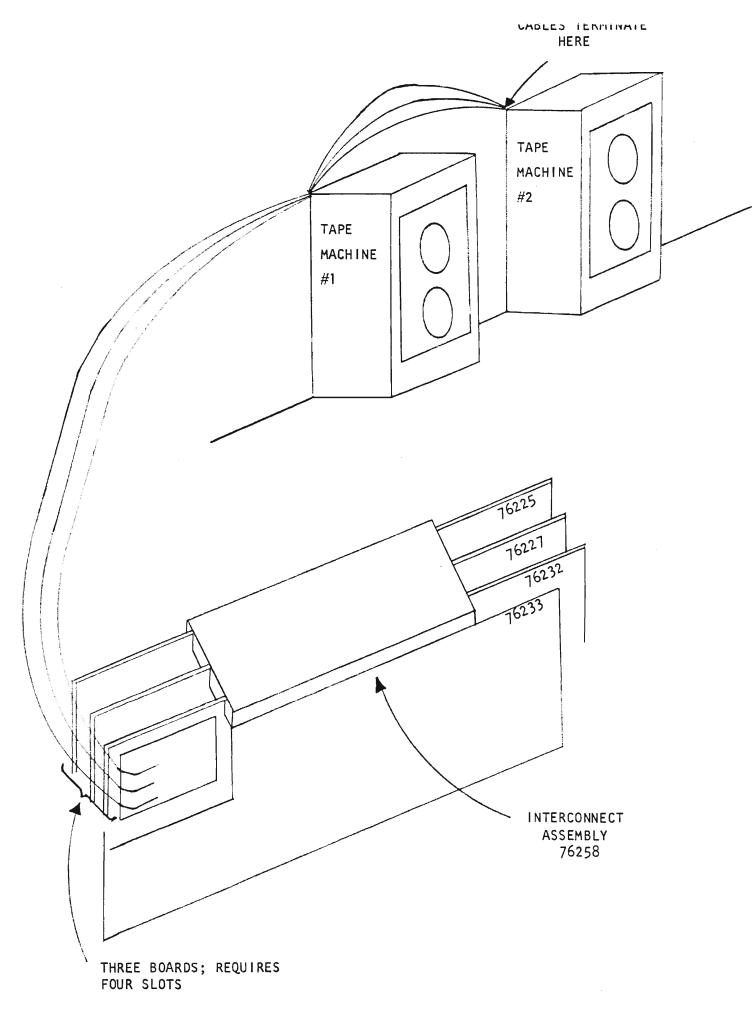

Figure 1-2. Wang NRZ Transport Interface Cable Connections

The interface is designed such that an open circuit is interpreted as a "high" signal.

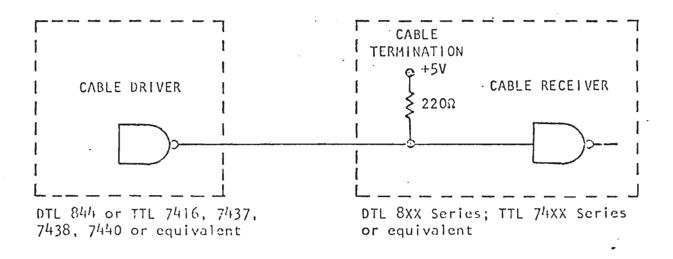

Figure 1-3 illustrates the configuration for which the interface has been designed.

## 1.4 MAGNETIC TAPE FORMATS

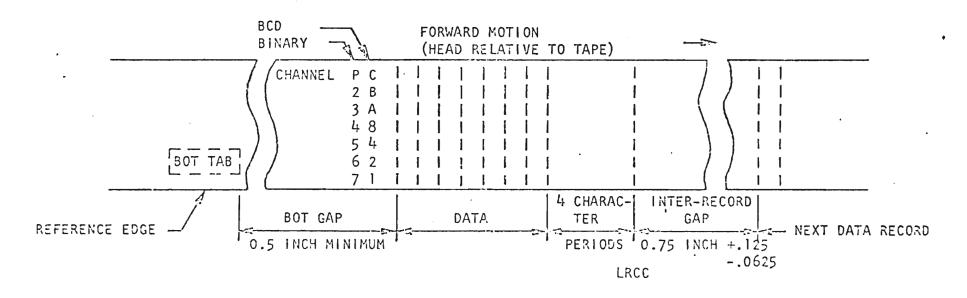

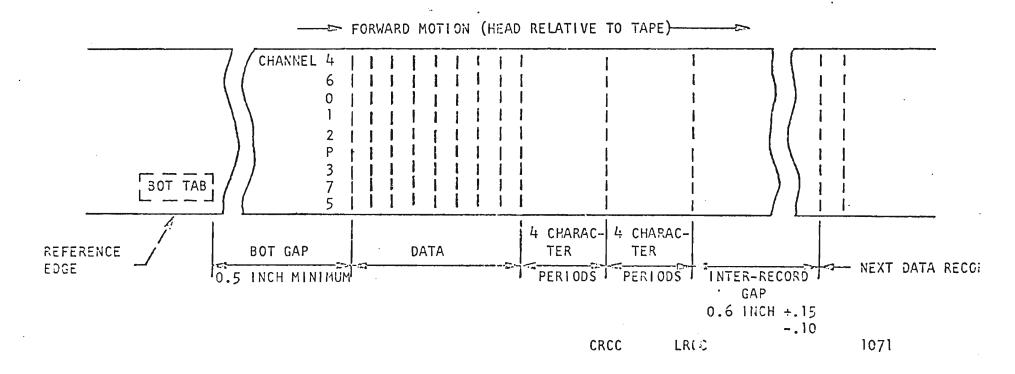

Figures 1-4 and 1-5 illustrate the IBM and USASCII magnetic tape formats for 7-track and 9-track tapes, respectively.

Figure 1-3. Interface Circuits

#### NOTES

- 1. TAPE SHOWN WITH OXIDE SIDE UP.

- 2. CHANNELS 2 THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE.

- 3. CHANNEL P (PARITY) CONTAINS CDD DATA PARITY FOR BINARY TAPES, OR EVEN PARITY FOR BCD TAPES.

- 4. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "I" BITS IN THAT TRACK (INCLUDING THE LRCC) IS EVEN. IT IS POSSIBLE IN THE 7-TRACK FORMAT FOR THIS CHARACTER TO BE ALL ZEROES, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED.

- 5. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "I" BITS IN CHANNELS 4, 5, 6

AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THE FILE MARK IS SEPARATED

BY NORMAL IRG'S (.75 INCH) FROM THE PREVIOUS AND FOLLOWING RECORDS. OPTION—

ALLY, A 3.5-INCH GAP CAN BE ERASED PRIOR TO WRITING THE FILE MARK.

- 6. DATA PACKING DENSITY MAY BE 200, 556, or 800 BITS PER INCH.

#### NOTES

- 1. TAPE SHOWN WITH OXIDE SIDE UP.

- 2. CHANNELS O THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE.

- 3. CHANNEL P (PARITY) ALWAYS CONTAINS ODD DATA PARITY.

- 4. EACH BIT OF THE LRCC IS SUCH THAT THE TOTAL NUMBER OF "I" BITS IN THAT TRACK (INCLUDING THE CRCC AND THE LRCC) IS EVEN. IN THE 9-TRACK FORMAT THE LRCC WILL NEVER BE AM ALL-ZEROES CHARACTER.

- 5. IT IS FOSSIBLE FOR THIS CRCC CHARACTER TO BE ALL ZEROES, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED.

- 6. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "1" BITS IN CHANNELS 3, 6, AND 7 FOR BOTH THE DATA CHARACTER AND THE LRCC. THE CRCC CONTAINS ALL ZEROES. THE FILE MARK IS SEPARATED BY NORMAL IRG'S (.6 INCH) FROM THE PREVIOUS AND FOLLOWING RECORDS. OPTIONALLY, A 3.5 INCH GAP CAN BE ERASED PRIOR TO WRITING A FILE MARK.

Figure 1-5. 9-Track Format

#### SECTION 11

#### INTERFACE

#### 2.1 INTRODUCTION

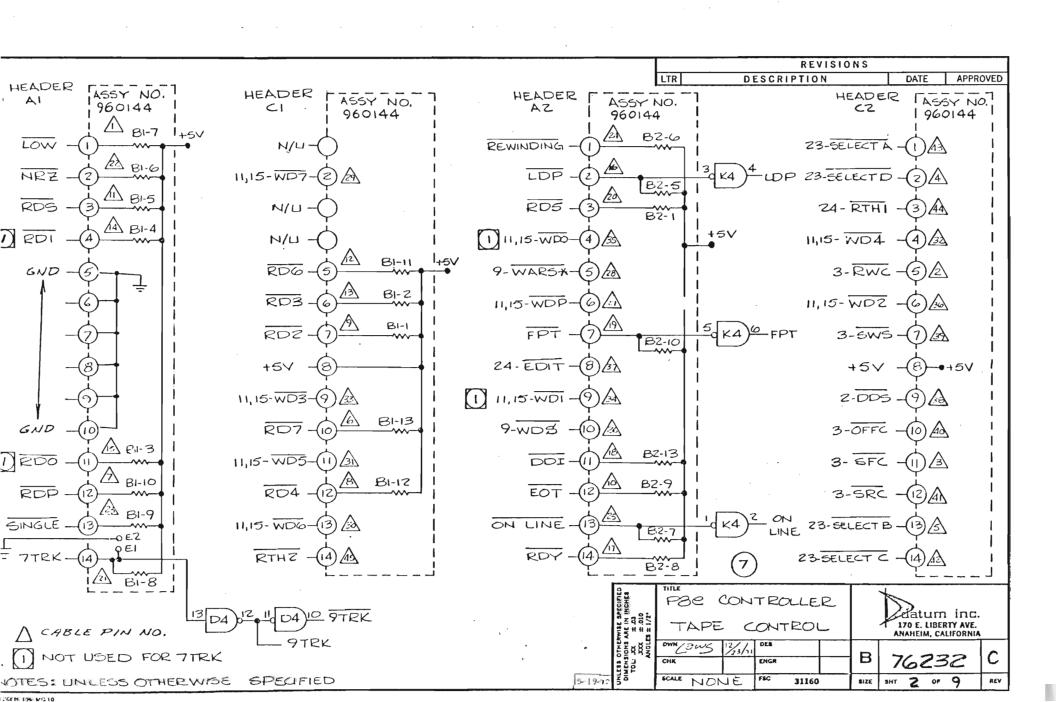

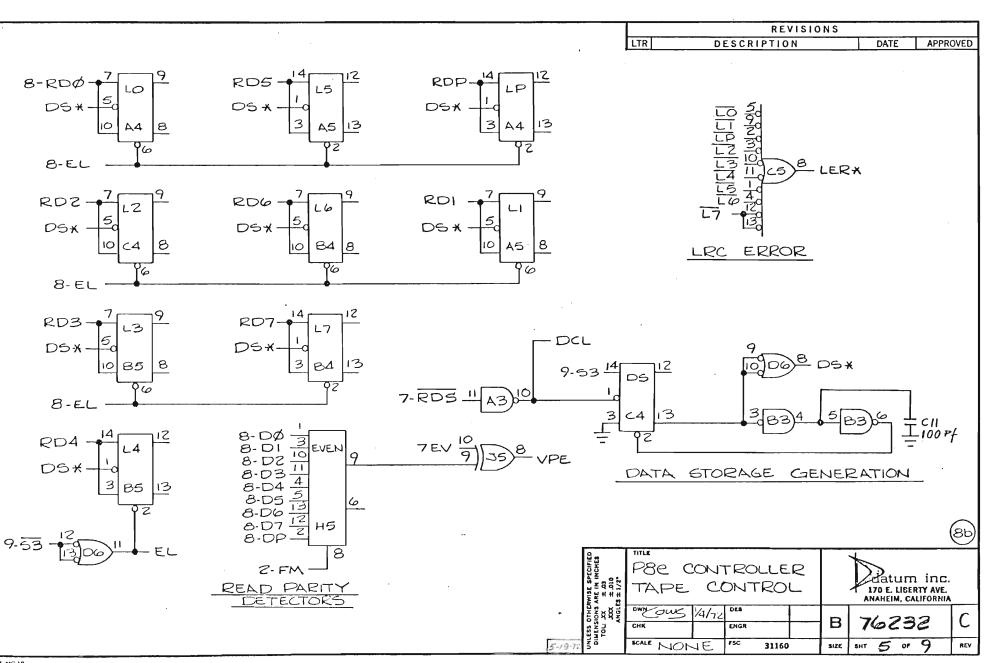

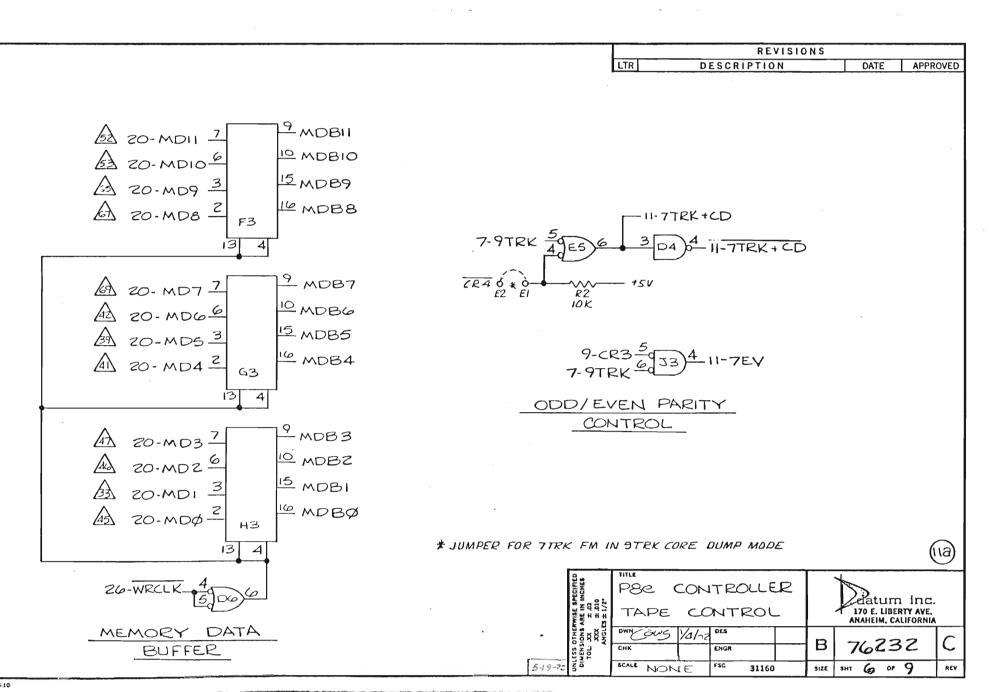

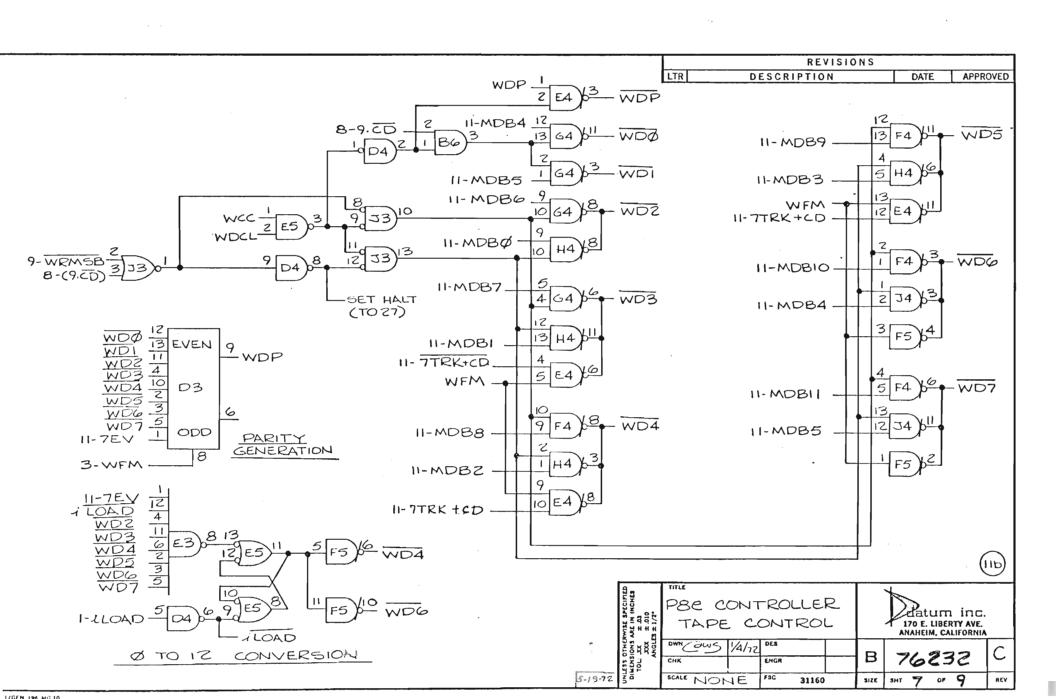

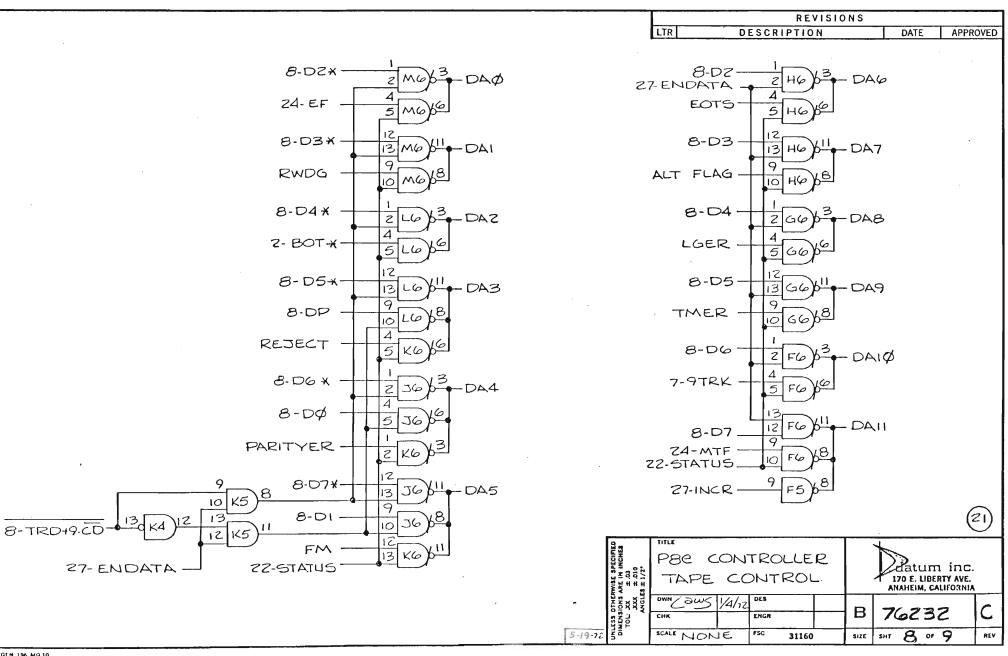

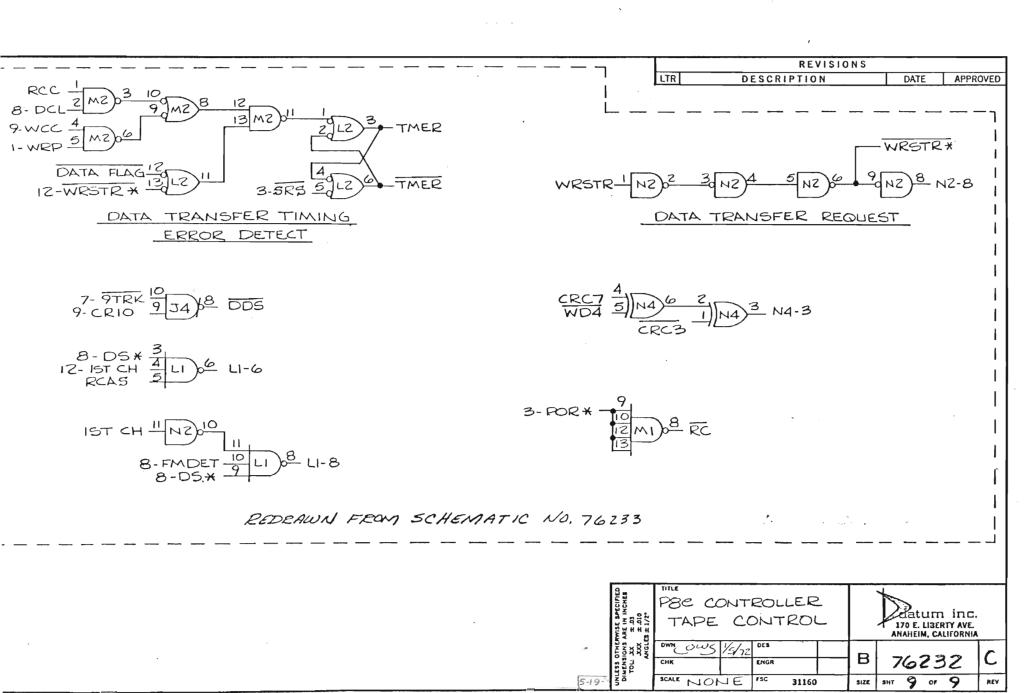

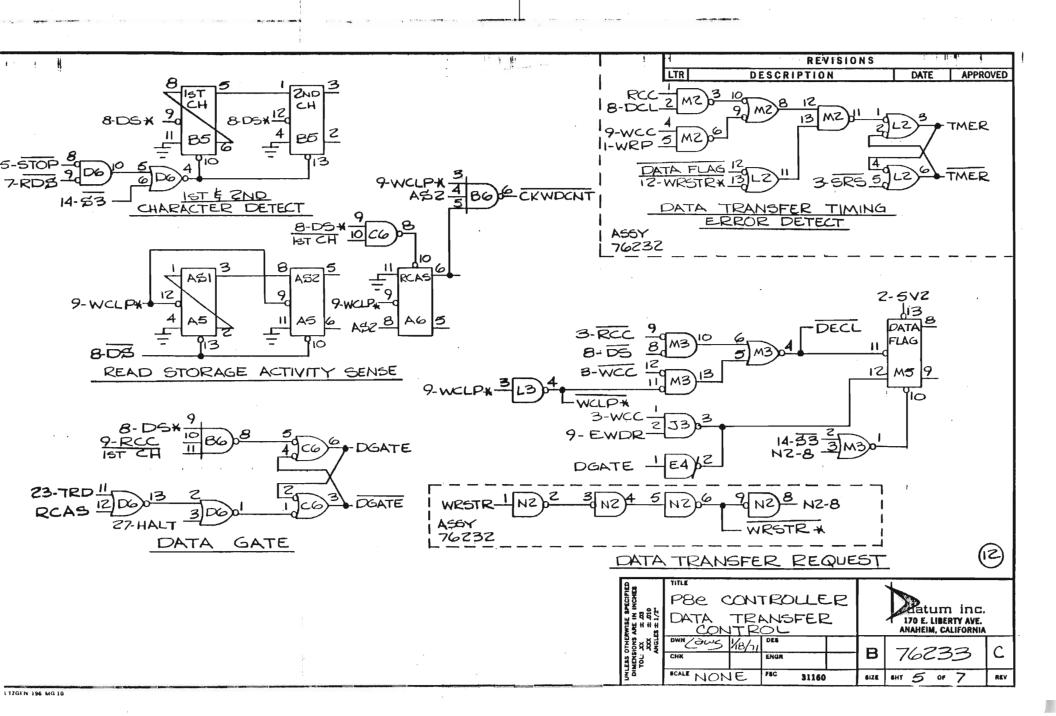

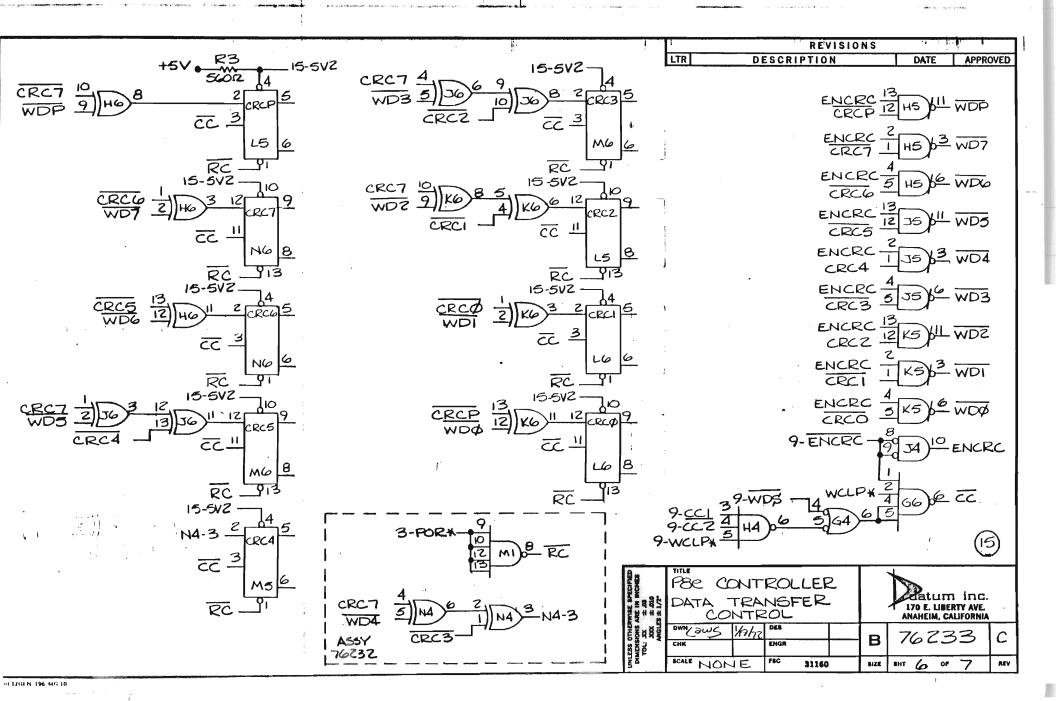

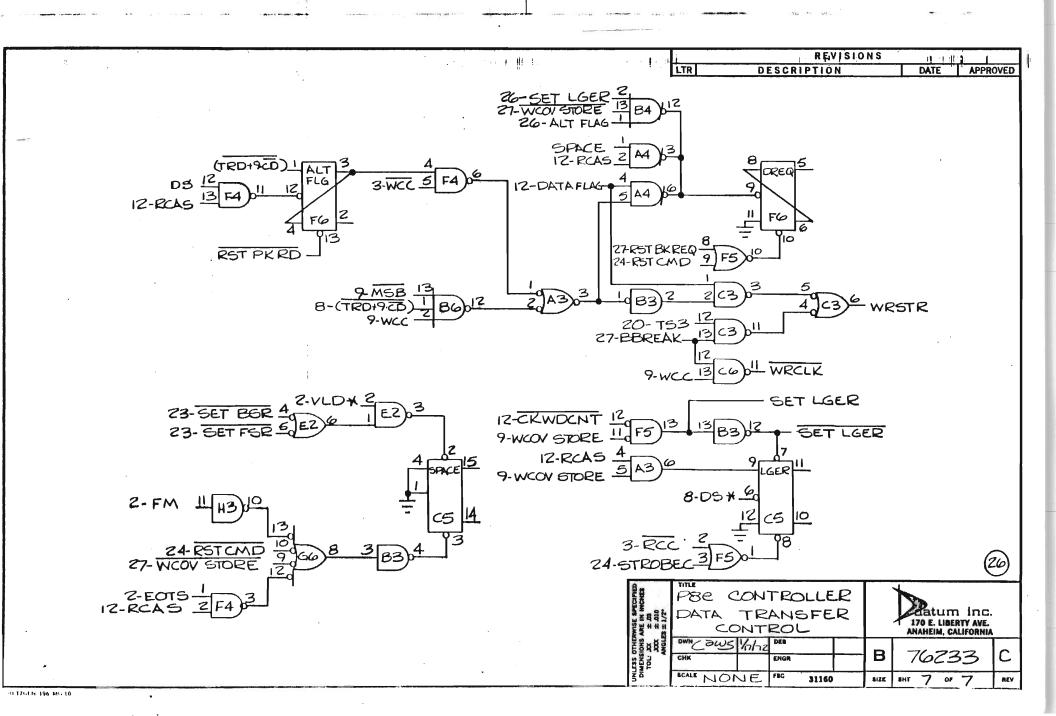

There are two interfaces to the Controller Formatter section, one to the computer adapter section and one to the tape units (76232 Al, A2, Cl and C2).

Individual, stranded, 22-26-gauge twisted-pair wires should be used. Maximum length should be twenty feet (total) for the tape-unit "Daisy-Chain" bus.

The twisted-pair wire should have at least one twist per inch and a minimum insulation thickness of .01 inch.

The ground wire of each twisted pair should be terminated to ground as close to the origin or destination of the signal as possible (within 6 inches maximum) to minimize ground-loop-current "crosstalk" effects.

## 2.2 FORMATTER/TRANSPORT(s) INTERFACE

#### 2.2.1 Formatter to Transport

### 2.2.1.1 Transport Address

SELECT A through SELECT D - Transport Select Lines. Four select lines to select one of the "daisy-chained" transports. Developed by decoding CR1 and CR2 from the command register.

#### 2.2.1.2 Control

The control lines activate the selected transport when it is "READY" and "ON LINE".

SFC - Synchronous Forward Command. A levelwhich, when low, causes the selected transport to "ramp" up to speed and drive forward at the rated speed until the level goes back high. When switches to the high level, the transport "ramps" down to halt.

SRC - Synchronous Reverse Command. A level which, when low, causes the same action as SFC except in reverse tape motion.

RWC - Rewind Command. A negative-going pulse which causes the selected transport to rewind to load point.

OFC - Offline Command. A negative-going pulse which causes the selected transport to revert to manual control. Transport must be manually placed "ON LINE" before it can again be operated.

The offline command <u>can</u> be transmitted to a tape transport that is rewinding (even though the transport status indicates NOT READY).

SWS - Set Write Status. The level of this signal is inspected within 20 microseconds after an SFC or SRC command is initiated to set the selected transport to the write or read mode. This mode is maintained until the next SFC or SRC command is initiated.

The write mode within the transport is also switched to read mode if:

- a) An RWC or OFC command is received.

- b) Loss of interlock occurs.

- c) The transport is manually switched offline.

EDIT - (Over Write). - This signal is a level that causes the transport write current enable/disable to "ramp" on and off to minimize rate of change of recorded inter block gap magnetism when rewriting a record in the EDIT mode.

This signal level also causes the write current and DC erase head current to be turned off <u>immediately</u> after rewriting the new record (to keep from erasing the beginning of the next record).

WARS - Write Amplifiers Reset. This signal controls the early turn-off of write and erase currents after rewriting a record in the EDIT mode.

The negative-going transition of this signal initiates the write current turn-off. In NRZI transports, this signal also generates the LRC character.

DDS - Select high density. Low = select high density (for NRZI Formatter only) for 7-track transport.

#### 2.2.1.3 Write Data

$\overline{\text{WDS}}$  - Write Data Strobe. This is a clock used to copy the write data (WDP and WDO through WD7) into the selected transport write flip-flops. The data levels <u>must</u> be static during WDS and the trailing edge (positive-going) of  $\overline{\text{WDS}}$  is used to clock the flip-flops. The clock rate is <u>twice</u> the character rate for 1600 CPI and <u>at</u> the character rate for NRZI.

$\overline{\text{WDP}}$ ,  $\overline{\text{WDO}}$  through  $\overline{\text{WD7}}$  - Write data.  $\overline{\text{WDP}}$  is the odd parity bit,  $\overline{\text{WDO}}$  is the most significant bit, and  $\overline{\text{WD7}}$  is the least-significant bit.  $\overline{\text{WDO}}$  and  $\overline{\text{WDI}}$  are not used for 7-track NRZI operation.

These signals are presented to the selected transport along with the  $\overline{\text{WDS}}$  clock. The write data is presented in a logic-level form (low = logic 1, high = logic 0).

## 2.2.2 Transport to Formatter

### 2.2.2.1 Status Lines.

RDY - Ready. A level that is low only when the selected transport is:

- a) Interlocked

- b) Through the initial load or rewind-to-load point sequence.

- c) On line

- d) Not rewinding

Note: A transport will go NOT Ready for approximately .5-second after reversing into load point and does not go Ready until approximately .5-second after termination of a Rewind.

ONLINE - On line. A level that is low when the selected transport is manually switched on line (to place it under remote control).

REWINDING - Rewinding. A level that is low while the selected transport is rewinding. The level remains low until the transport completes the automatic "return to load point" sequence but the transport does not become Ready until approximately .5 second after the RVD signal terminates.

FPT - File Protect. A level that is low when the selected transport has a supply reel of tape mounted that does not have a write-enable ring installed.

LDP - Load Point. A level that is low when the selected transport's beginning-of-tape reflector is located under the photo sensor, interlocks are made, and the initial load or rewind sequence is completed.

EOT - End of Tape. A level that is low when the end-of-tape reflector is under the photo sensor in the selected transport. This signal is not staticised and neither the positive nor negative-going transition is "clean".

SINGLE/DUAL - Head Stack. A level that reports the selected transport head type. Low for single stack, high for dual stack "read while writing".

7 TRK/9 TRK - Transport Type.

Low = 9-track

High = 7-track

DDI - Data Density Indicator

Low = High Density Selected

High = Low Density Selected

## 2.2.2.2 Read Data & Read Clock

RDP, RDO through RD7 - Read Data

## 2.2.2.3 Read Data & Clock

The read data is completely "buffered" in a special register. The data is allowed to change just before the leading edge of the read strobe pulse (RSTROBE) and is static throughout RSTROBE and until the leading edge of the next RSTROBE pulse.

#### SECTION 111

#### THEORY OF OPERATION

#### 3.1 INTRODUCTION

This section contains information on the operation of the NRZI Magnetic Tape Controller.

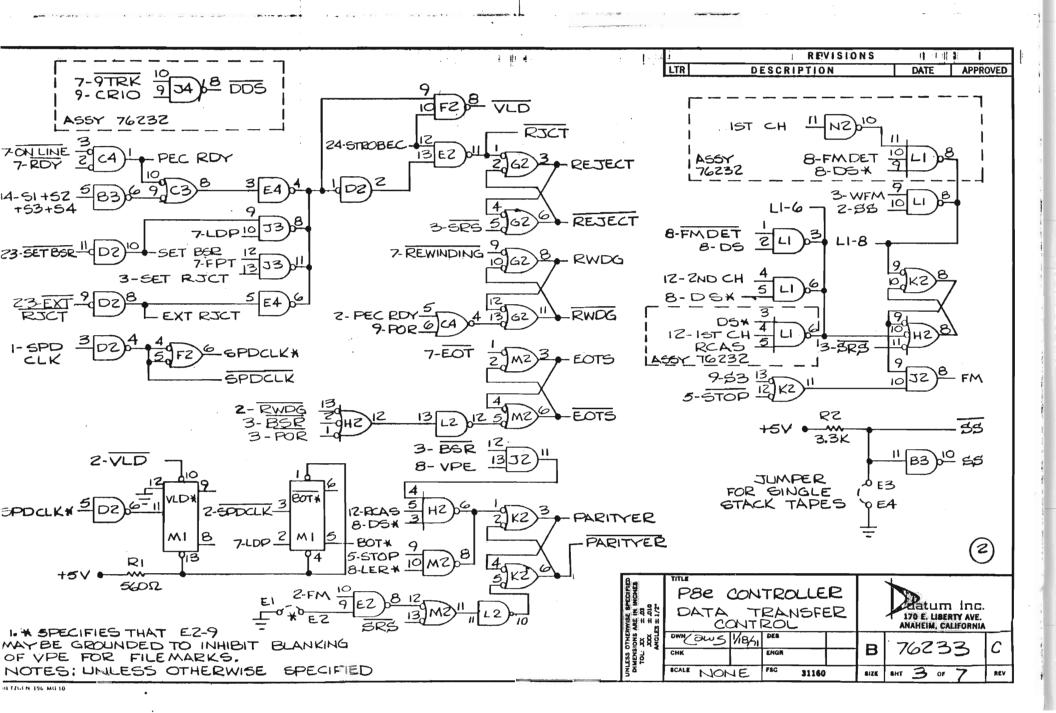

The information in this section is divided into two major topics. A discussion of the block diagram (Figure 3-1) is presented first, to provide an overall functional description and to illustrate the relationship between the formatter portion, the adapter portion and a discussion of the command execution, illustrated by timing diagrams, describes operation of the Controller circuitry during execution of computer-originated instructions.

The Controller performs three basic functions. These are:

- 1. Control

- 2. Write

- 3. Read

The Controller provides control over the selected tape unit including all timing necessary to perform automatically all Write, Read, Rewind, Space Forward or Backward, and Rewind commands.

Upon completion of the commanded operation, status is provided so that the computer can ascertain whether the operation was performed correctly.

The Controller performs all the Write functions for erasing tape, writing a file mark or writing a record of data. A 3.5-inch gap is automatically erased before the first record when starting from beginning of tape (BOT). The correct timing delays for erasing the inter-record gap (IRG) are provided and the file-mark code is developed by the formatter portion of the Controller.

The task of writing is reduced to mere transfer of the characters on a demand-response basis for the computer-adapter logic.

The Controller also reduces the reading and spacing operations to a minimum by performing all parity checks and positioning of the head in the IRG's automatically. The task of reading is reduced to transfer of the characters on a demand-response basis.

The Controller can accommodate as many as four magnetic tape transport units simultaneously. All input/output signal lines are daisy-chained to the tape transports. Only the selected tape transport unit will respond to the Formatter commands. Select is determined by unit-select switches located on each tape unit.

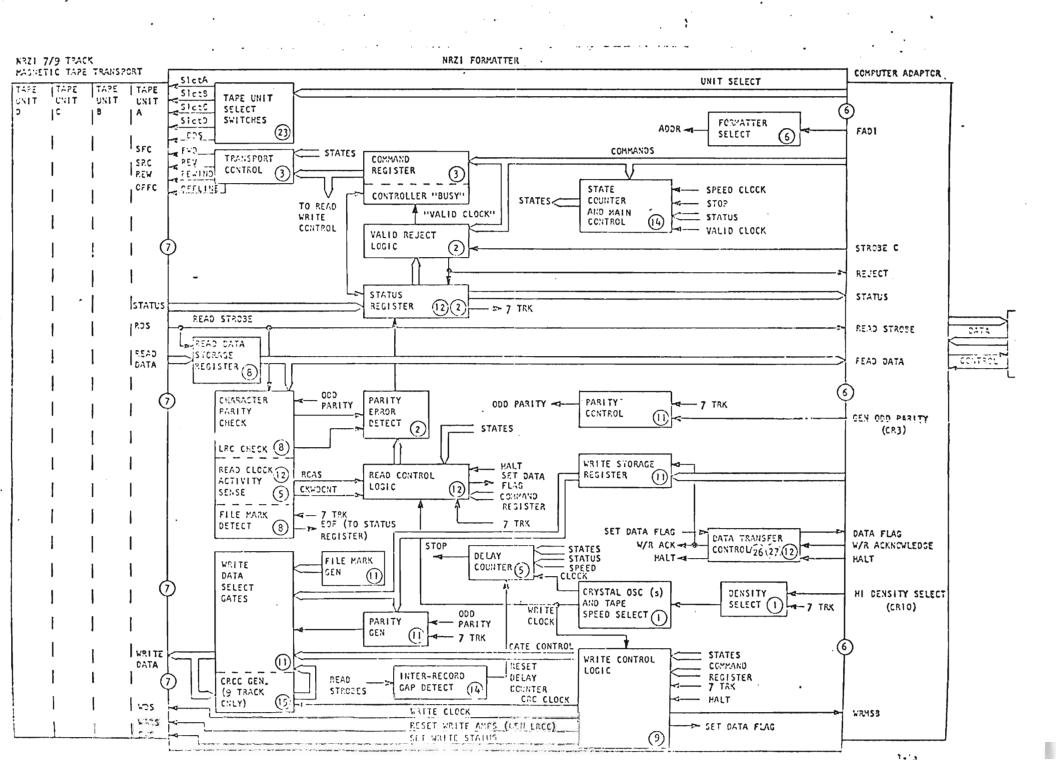

#### 3.2 BLOCK DIAGRAM

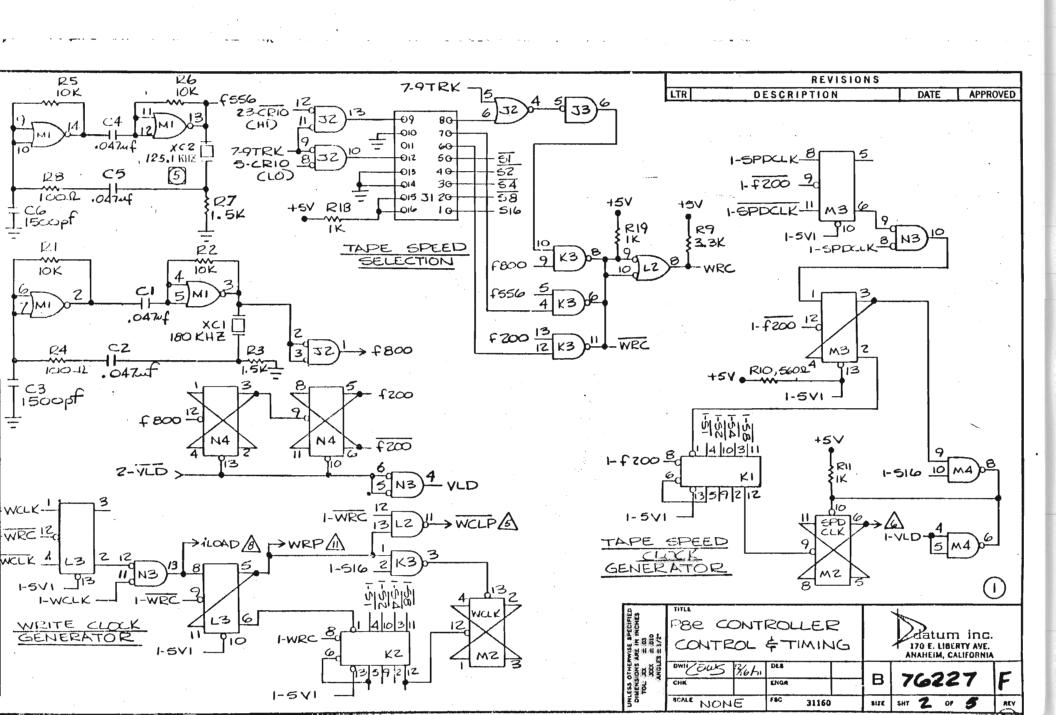

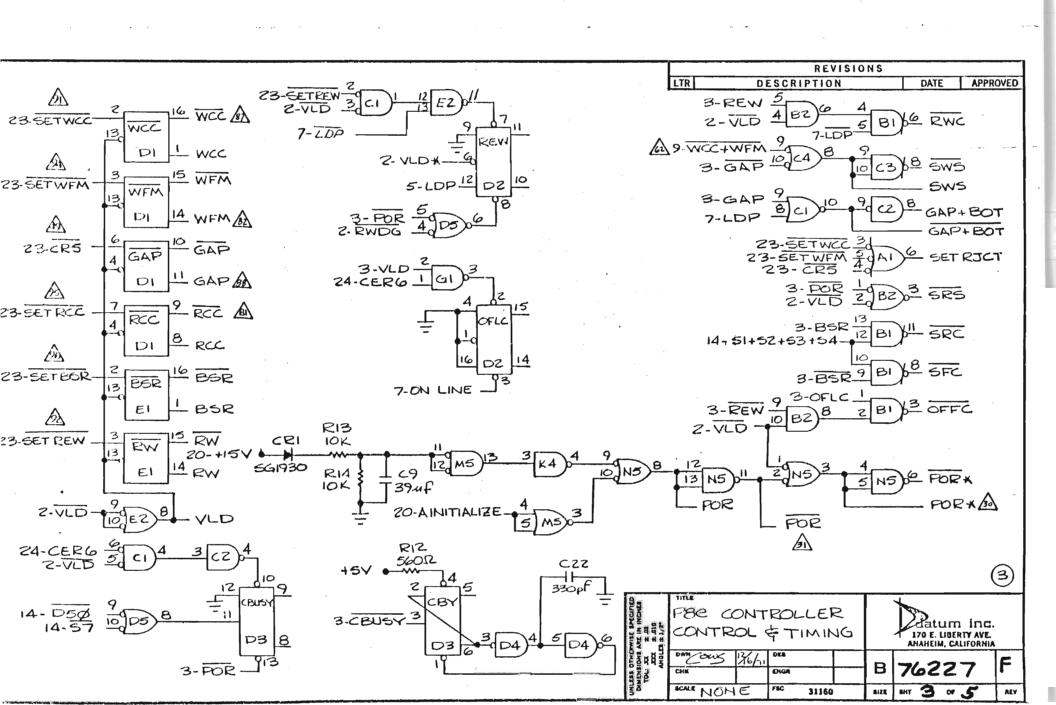

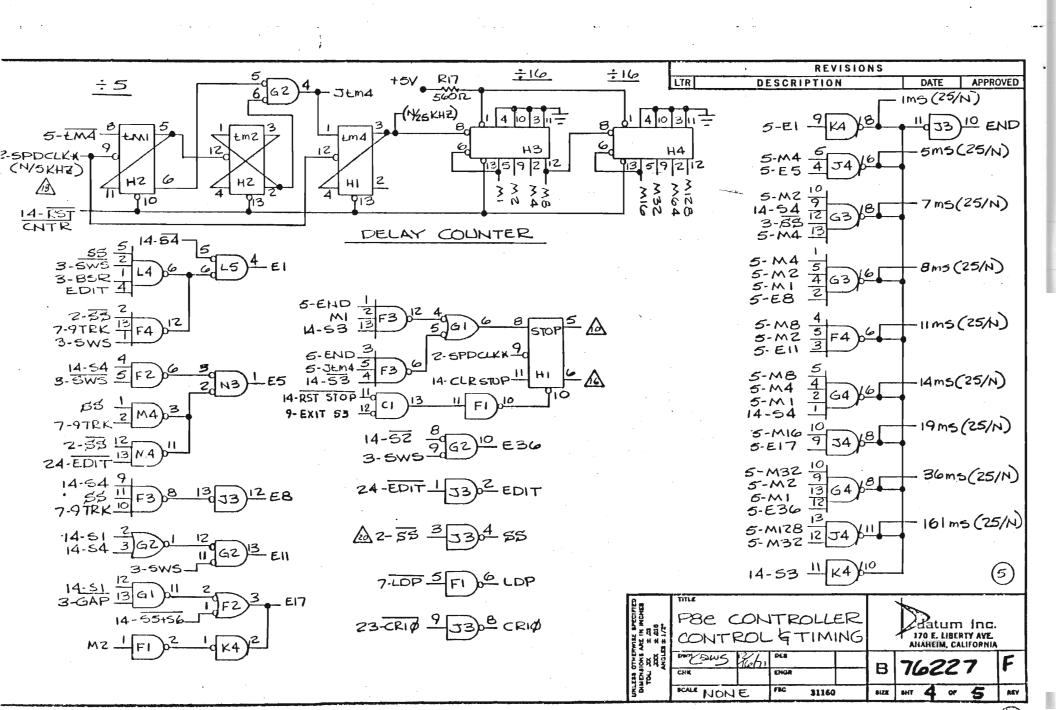

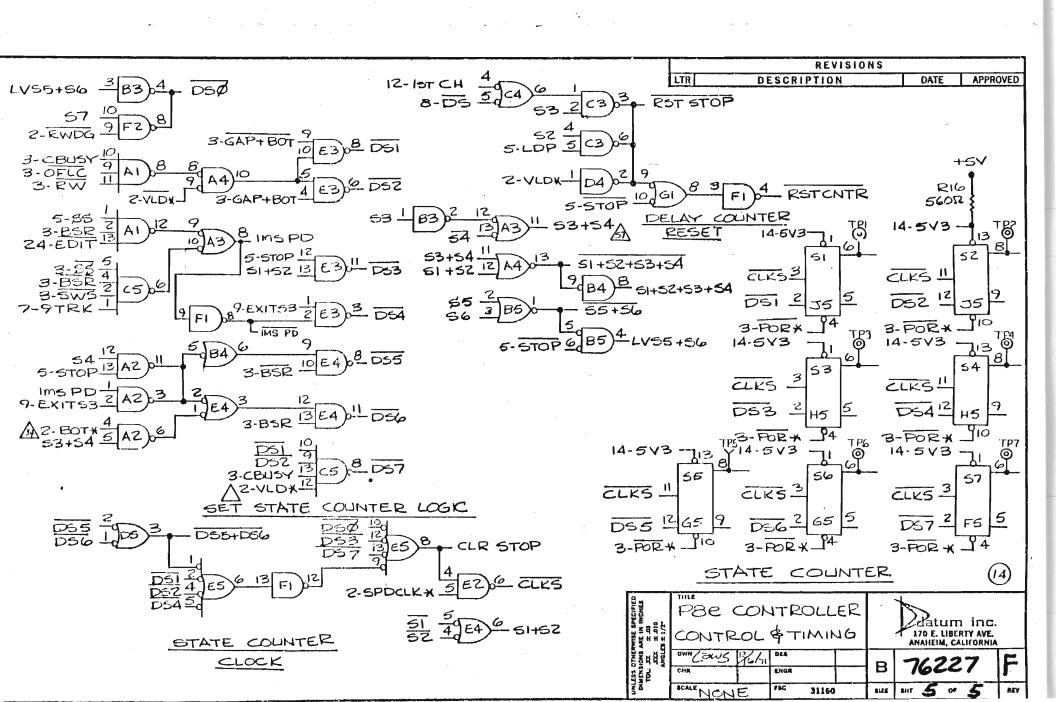

A simplified block diagram of the NRZI Formatting logic is shown by Figure 3-1. The block diagram illustrates the various functions performed by the standard 7-track, 9-track NRZI Controller and shows the relationship between the control, the tape transport units, and the computer adapter section.

The circled numbers refer to the "Logic Diagram Number" on which the indication function is drawn in detail. This number is located in the lower right hand corner of the detailed logic drawings.

#### 3.2.1 Command Register & Valid/Reject Logic

When a command is output from the computer, the command and a strobe pulse are delivered from the computer-adapter segment to the Controller valid-command-detect logic. If the command is acceptable, a "valid" clock is generated to enable the command to be loaded into the command register. If the command is not valid, a "reject" pulse is returned to the computer adapter. Each "valid" clock initiates a system reset (SRS) pulse, which is, in turn, used to reset the Formatter to initial conditions.

## 3.2.2 <u>CBUSY</u>

The "valid" clock also sets the controller-busy flip-flop. The controller-busy flip-flop normally is used by the computer adapter to signal termination of all commands. The transport control logic resets the controller-busy flip-flop after all tape motion has ceased for the commanded function. If "on-the-fly" writing or reading is desired, the Data Busy status must be utilized by the computer to initiate the next command as soon as Data Busy terminates.

## 3.2.3 <u>Transport Control</u>

The transport control logic develops the forward, reverse, rewind and offline commands to the selected tape transport unit under control of the command register and the state counter.

## 3.2.4 <u>Formatter\_Select</u>

The Formatter select logic allows a Formatter to be assigned the number zero or one so that two Formatters can be "Daisy-Chain" connected to one adapter section to provide control of up to eight transports or of a mixture of NRZI and 1600 CPI Phase Encoded Transports.

#### 3.2.5 Tape Unit Select

The Tape Unit Select switches allow the operator to assign unit numbers 0, 1, 2 or 3 to any of the four tape units. This allows physical tape units to be switched without requiring changes to the computer program. Indicator lamps give visual indication of which tape unit is selected.

## 3.2.6 State Counter and Main Control

The State Counter breaks the major operations (such as write and read) down into successive sub "states" that are sequentially stepped-through to perform the operation. These states are:

| State Count                          | Function                                                                                                                                                                                       |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Reset Predelay (not BOT and not 3-inch gap) Predelay (BOT or 3-inch gap) Write or Read execution Postdelay Forward Motion Halt time out Reverse Motion Halt time out Rewind or Clear execution |

The "delay" and "time out" states all use the Delay Counter to determine when the state count should terminate and the next state count entered. These delay count times vary, depending upon such factors as:

- 1. Tape speed

- 2. Single or dual-stack head

- 3. Edit or normal mode

- 4. Reverse or Forward motion

- 5. Seven or nine track tape unit selected

The pre and post delays are used to erase the inter-record gaps (IRG) and to halt the head in the correct position in the IRG when reading.

State O (the "rest" state) is the state the Controller enters after completing an operation.

State 1 (Predelay) is used to wait for the tape unit to get up to speed and to erase part of the IRG when writing. State 1 is used for predelay when not starting from BOT or not erasing a 3-inch gap.

State 2 (Predelay) is similar to State 1 except a longer delay is implemented to handle the 3-inch gap erased automatically at BOT and the Erase-3-Inch-Gap command.

State 3 (Write or Read Execution) is the State during which the record is written or read. When reading, State 3 is terminated when no more Read strobes occur (indicating the IRG has been reached).

IRG detection also terminates State 3 for Write operations when using a dual-stack read-after-write tape unit (so that the written record can be checked for correct parity). For single-stack writes, State 3 is terminated as soon as the LRC character is written at the end of the record.

State 4 (Postdelay) halts the head in the correct position in the IRG when reading. When writing, State 4 postdelay erases a portion of the IRG.

State 5 (forward motion halt time out) retains memory of the forward direction of motion during the time between the command to stop and the actual stop time. This delays termination of the CBUSY signal until the tape unit has completely halted in the IRG.

The DBUSY status terminates when State 5 is entered. Thus, successive "Writes" or successive "Reads" may be executed on-the-fly, without stopping in the IRG's.

State 6 (reverse motion halt time out) is similar to State 5 except for reverse motion commands. When performing on-the-fly operations, successive commands issued after DBUSY terminates but before CBUSY terminates must be of the same type. A Read cannot follow a Write and a forward motion command cannot follow a reverse motion command (or vice versa). There is, of course, no such restriction if the commands are not issued until after CBUSY terminates.

State 7 (Rewind or Clear) is entered upon issuance of a Rewind or Clear command by the computer. The state is terminated when the tape unit finishes rewinding.

## 3.2.7 Status Register

The Status Register stores both the tapc unit the the Controller status. This makes it possible for the computer to inspect the results of an operation to find out whether it was completed correctly or if some other action must be taken.

The status of the selected tape unit and the Controller are available for access by the computer at any time.

## 3.2.8 Parity Control

The Parity Control logic provides manual or program control over selection of odd or even parity for 7-track tape units. Odd parity is automatically selected for 9-track tape units. The output (odd parity) is used by the Parity Generator and Check logic.

## 3.2.9 Parity Error Detect

The Parity Error Detect logic searches for one or more parity errors in each tape record. Any detected errors cause the Parity Error Status bit to be set.

The Read Control logic uses the Read Clock Activity Sense logic (RCAS) output to enable the Parity Error Detect logic to inspect the Character Parity Check output only during the data portion of a record (since CRCC (9-track) and LRCC (7-track) can exhibit either odd or even parity).

The output of the LRC Check logic is inspected only after the entire record (including CRCC and LRCC) has been read.

#### 3.2.10 Character Parity Check

The Character Parity Check logic checks each character read from tape for either odd or even parity.

### 3.2.11 LRC Check

The Longitudinal Redundancy Character Check logic checks for an even number of 1's for each individual track down the length of the record, including the CRC and LRC characters.

## 3.2.12 Read Data Storage Register

The Read Data Storage Register stores each tape character at the leading edge of the Read Strobe in such a manner that the Read Data is static to the computer adapter interface throughout the entire period until the leading edge of the next Read strobe occurs. This deletes the requirement for a storage register in the computer adapter section. This register would otherwise be required to retain the data for the <a href="maximum">maximum</a> possible time after the Data Flag is set, to give the computer the maximum amount of time to accomplish the data transfer.

The outputs of the Read Data Storage Register are routed to the rest of the logic where Read data is utilized on the Controller.

#### 3.2.13 Read Clock Activity Sense

The Read Clock Activity Sense logic separates the data portion of each record from the CRC and/or LRC characters in the forward direction. Thus, the Set Data Flag (in the Read Control logic) is allowed to operate only for the data portion of the record, which "strips" off the CRC and/or LRC characters.

The check word count (CKWDCNT) pulse occurs just after the last data character but before the CRC or LRC character's Read Strobe destroys the contents of the Read Data Storage Register. The CKWDCNT pulse is delivered to the Computer Adapter interface, where it may be used to create an extra data transfer request to the computer for the case where an odd number of characters were read from tape and the "Pack" mode of operation is being used. The CKWDCNT pulse is also typically used by the Computer Adapter to determine if the expected number of characters were read from tape to create status bits which can inform the computer that the record was too long, too short and/or contained an odd number of tape characters.

## 3.2.14 File Mark Detect

The File Mark Detect logic checks for 7-track or 9-track file marks, depending upon which type of tape is selected. The EOF status bit is developed if a file mark is detected in a forward or backword direction.

## 3.2.15 Read Control Logic

The Read Control logic controls data transfer during State 3 until the IRG is detected, at which time the Postdelay (State 4) or one of the Halt delays (State 5 or 6) is entered.

The Set Data Flag signal is generated for each Read Strobe that occurs as long as RCAS indicates that the data portion of the record is present and the Halt signal hasn't occurred.

When the IRG is detected or the computer generates the Halt signal (to indicate that it doesn't want any more data), there are no more Data Flag signals generated even though there may be more data in the record.

The Read Control logic also controls the forward and reverse space operations. These operations are identical to reading forward or reverse except that the Data Flag is not set for data transfer requests. All parity checks are valid for the spacing operations as well as for the reading operations and for read-after-write operations when a dual-stack head is employed on the selected tape unit.

In the special, Test Read, mode, the CRC and/or LRC characters are not separated from the data in the Forward Read operation. This mode is used to check the CRC and LRC generator logic with diagnostic programs.

### 3.2.16 Write Storage-Register

The Write Storage-Register is provided so that the Computer Adapter does not need a register to store computer output data. The Data Transfer logic operates on a request/response basis via the Data Flag and Write/Read Acknowledge (W/R ACK) signals. Each data character is requested a full write-clock-period before it is needed. The computer can respond any time within this period with a W/R ACK strobe pulse to load the Write Data into the Write Storage Register.

#### 3.2.17 Parity Generator

The Parity Generator creates odd or even parity for each character presented from the Write Storage Register and sends the parity bit to the Write Data Select Gates. The Parity Control logic determines whether odd or even parity is generated.

### 3.2.18 Write Data Select Gates

The Write Data Select Gates consist of three sets of gates that are enabled by the Write Control logic to gate the Write data (and parity bit) or the File Mark code or the CRC Character onto the write data bus to the tape units.

#### 3.2.19 File Mark Generator

The File Mark Generator generates the appropriate file mark. This may be a normal 9-track file mark, a special 9-track file mark or a 7-track file mark. The Write Control logic gates the file mark code onto the write data bus at the appropriate time and generates a Write Clock to write the file mark.

The special 9-track file mark is an option that writes the 7-track file mark code to provide compatibility with some computer manufacturer's hardware and software when writing in the "unpack" mode on a 9-track tape.

#### 3.2.20 CRCC Generator

The Cyclic Redundancy Check Character (CRCC) Generator calculates the CRC Character while writing each record as each data character while writing each record as each data character appears on the write-data bus.

At the end of the record (9-track only) the Write Control logic gates the CRCC onto the bus and generates a Write clock pulse to write the CRC Character. The LRC Character is then written to finish the record. The CRCC may be all zeros and may exhibit odd or even parity.

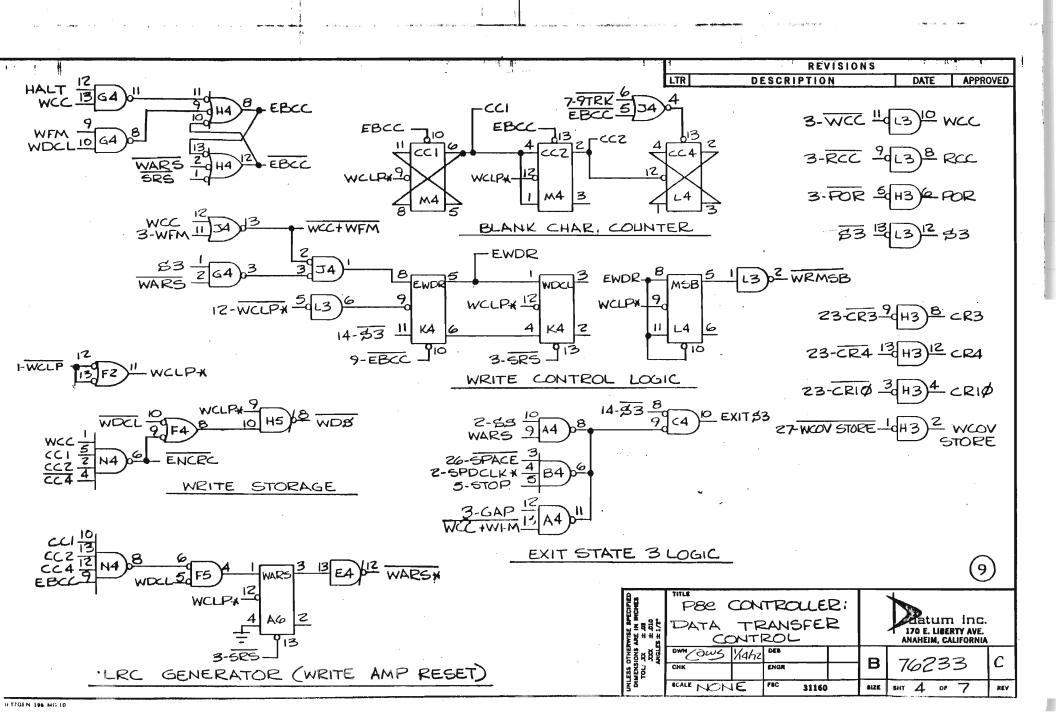

### 3.2.21 Write Control Logic

The Write control logic operates during State 3 for write, erase and write-file-mark operations. The Write control logic controls the Data Transfer logic for write operations by developing the Set Data Flag pulse to request each character to be written until the Write operation is terminated by the Halt signal from the Computer Adapter.

Upon receiving the Halt signal, the CRC and/or LRC character is automatically appended to the record and part of the IRG is then erased. If a single-stack (read/write) tape unit is selected, the Write Control logic triggers the State Counter to the State 4 postdelay when it finishes writing the LRC Character at the end of the record. If a dual-stack (read after write) tape unit is selected, the Inter-Record Gap Detect logic is utilized to exit State 3 to State 4 postdelay in order to allow all of the record to be read-after-write parity checked.

The data rate is developed from the write clock frequency (from the Crystal Oscillators) and the tape-speed-select logic.

The Write Control logic also sends the Write Most Significant Byte (WRMSB) signal to the Computer Adapter. This enables the odd/even characters to be separated when "unpacking" a computer word into two sequential tape characters.

## 3.2.22 Crystal Oscillators and Tape Speed Select

The Crystal Oscillators provide stable precision clock frequencies for packing densities of 800/556/200 bits per inch. One set of crystals covers the standard tape speeds from 12.5 to 75 ips. The Tape Speed Select and Density Select logic divides down the clock rates to the appropriate frequencies and selects the write clock frequency as determined by tape speed and packing density.

The Speed Clock signal is used by the Delay Counter to provide all the precise time delays for the Formatter. The Speed Clock is dependent only on tape speed.

#### 3.2.23 Density Select

The Density Select logic provides control over selection of Hi or Low density for 7-track tape units. Nine-track tape units are automatically operated at only 800 BPI. The Density Selection is controlled by the computer program via the Hi Density Select signal.

### 3.2.24 Data Transfer Control

The Data Transfer Control operates in conjunction with the Read or Write Control logic depending upon whether a Read or a Write operation is active.

The Read or Write Control logic generates the Set Data Flag pulse to signal that Read data is ready for input or to request a Write Data character. The Computer Adapter returns the W/R ACK signal, which clears the Data Flag and is used to strobe the Write data into the Write Storage Register for write operations. When the Computer Adapter desires to halt data transfer, it generates the HALT signal and the Data Flag signal is disabled.

### 3.2.25 Delay Counter

The Delay Counter is a flip-flop divider chain that counts the Speed Clock pulses to provide precise time intervals for Pre-, Post-, and Halt delays. The time interval begins when the counter starts counting (from a reset condition) and ends when the STOP signal is generated by the gates that decode various counts from the Delay Counter. The gate selected for a particular time interval depends upon which state the Controller is in as well as its configuration and the selected tape unit (provided by the STATUS signals to the Delay Counter).

## 3.2.26 Inter Record Gap Detector

The IRG Detector triggers the Formatter from State 3 to the Post Delay State 4, of Halt Delay State 5 or 6 when completing any Read or Space operation or any Write operation with a dual-stack, read-after-write tape unit. The IRG Detector resets the Delay Counter with each Read strobe. After the Read strobes stop, the Delay Counter is allowed to count for a prescribed interval until the STOP time is reached, at which time State 3 is terminated.

### 3.3 COMMANDS

#### 3.3.1 Basic Commands

Basic Commands provided by the Formatter are:

- 1. Read (one record)

- 2. Write (one record)

- 3. Space

- 4. Write File Mark

- 5. Erase 3-inch gap

- 6. Rewind

- 7. Offline

- 8. Clear

## 3.3.1.1 Read and Space

The Space operations can be a single or multiple record under control of the STOP SPACE Computer Adapter signal. In addition, the backspace operation can be conducted in the EDIT mode. This is to position the Write head correctly in the IRG preceeding a record that is to be replaced with an equal length but updated record. BOT will halt backspacing automatically.

## 3.3.1.2 Write, Erase 3 Inch Gap and Write File Mark

The Erase-3-Inch-Gap command can be performed by itself or combined with the Write or Write File Mark commands to cause a 3-inch gap to be erased prior to writing the record or file mark. A Write command can be performed in the Edit mode (if the record to be replaced has first been backspaced over in the Edit mode to position the head correctly) to replace a record with an equal length record of updated information.

#### 3.3.1.3 Rewind and Offline

The Rewind command causes the selected tape unit to rewind to Load Point (Beginning of Tape). The Controller goes "Busy" until the rewind is terminated (to provide a means of interrupting the computer upon termination of the operation).

The Offline command never sets the Formatter to the "Busy" state and may be sent to a selected tape unit even if the tape unit is "Not Ready" because it is performing a rewind operation.

#### 3.3.2 Command and Mode Combinations

The list of possible commands executable by the Formatter depends upon the 'mode' lines and are listed in Table 3-1.

NOTE 1 The GEN ODD PARITY and HIGH DENSITY mode lines are ignored for 9-track tape units. The GEN ODD PARITY line controls whether odd or even parity is written or checked for. The HI DENSITY line controls the written character packing density and the period of time allowed between read strobes in the Read Clock Activity Sensor Circuits.

TABLE 3-1. COMMAND & MODE COMBINATIONS

|                                  |                               | "SET XXX" COMMAND SIGNALS |     |     |     |     |     |     | TI  | 'MODE'' SIGNALS |                   |                               |      |     |               |    |

|----------------------------------|-------------------------------|---------------------------|-----|-----|-----|-----|-----|-----|-----|-----------------|-------------------|-------------------------------|------|-----|---------------|----|

|                                  | FORMATTER                     | REV                       | WCC | WFM | GAP | FSR | RCC | CLR | REW | 0FL             | GEN ODD<br>PARITY | HI<br>DENSITY                 | EDIT | TRD | STOP<br>SPACE | CD |

| 1.                               | Test Read Forward             |                           |     |     |     |     | Х   | 1   |     |                 | 1                 | 1                             |      | Х   |               | 5  |

| 2.                               | Read Forward                  |                           |     |     |     |     | Х   |     |     |                 | 1                 | 1                             |      |     |               | 5  |

| 3.                               | Write   Record (normal)       | ;                         | Х   |     |     |     |     |     |     |                 | 1                 | 1                             |      |     |               |    |

| 4.                               | Write   Record (edit)         |                           | Х   |     |     |     |     |     |     |                 | 1                 | 1                             | Х    |     |               |    |

| 5.                               | Space Forward 1 Record        |                           |     |     |     | Х   |     |     |     |                 | 1                 | l                             |      |     |               | 5  |

| 6.                               | Space Forward "n" Records     |                           |     |     |     | Χ   |     |     |     |                 | 1                 | 1                             |      |     | 4             | 5  |

| 7.                               | Space Reverse 1 Record        | X                         |     |     |     |     |     |     |     |                 | 1                 | 1                             |      |     |               | 5  |

| 8.                               | Space Reverse "n" Records     | Х                         |     |     |     |     |     |     | -   |                 | 1                 | 1                             |      |     | 4             | 5  |

| 9.                               | Space Reverse (edit mode)     | X                         |     |     |     |     |     |     |     |                 | 1                 | 1                             | Х    |     |               | 5  |

| 10.                              | Write File Mark               |                           |     | Х   |     |     |     |     |     |                 | 11                | 1                             | 6    |     |               | 5  |

| 11.                              | Erase 3 Inch Gap              |                           |     |     | Χ   |     |     |     |     |                 |                   |                               |      |     |               |    |

| 12.                              | Erase 3" then Write File Mark |                           |     | Х   | Х   |     |     |     |     |                 |                   |                               |      |     |               |    |

| 13.                              | Erase 3"thenWrite 1 Record    |                           | Х   |     | Х   |     |     |     |     |                 | . 1               | 1                             |      |     |               |    |

| 14.                              | Rewind                        |                           |     |     |     |     |     |     | Х   |                 |                   | Vince-0-000 N. 27 . Address 1 |      |     |               |    |

| 15. Off-line                     |                               |                           |     |     |     |     |     |     |     | Х               |                   |                               |      |     |               |    |

| 16. Initiate Rewind then Offline |                               |                           |     |     |     |     |     |     | Х   | X               |                   |                               |      |     |               |    |

SEE NEXT PAGE FOR NOTES 1-4

- NOTE 2 The STOP SPACE signal is used only for continuous spacing over multiple records. The DBY signal can be used by the Computer Adapter to count records to determine when the required number of records has been traversed.

- NOTE 3 The CD signal (Core Dump) is ignored in 7-track but can be used to write 7-track-type file marks and to check for 7-track file marks on a 9-track tape unit, i.e., an octal 17 with even parity is written (and decoded as a file mark when reading) instead of the normal octal 23 with odd parity.

This provides compatibility with some existing computer manufacturer's software.

NOTE 4 The Edit mode can be used to rewrite a file mark if the file mark is first backspaced over in the Edit mode.

## 3.4 STATE FLOW

Figure 3-2 illustrates the State Counts that the Controller sequences through in simplified form. Figure 3-3 illustrates the State Flow in detail.

# 3.4.1 Simplified State Flow (See Figure 3-2)

The Controller is in the "Rest" State 0 at initial conditions.

The strobe C command clock is rejected if the command is not a "valid" one.

If CBUSY is <u>not</u> set by a valid command then the command must be:

- 1. Offline

- 2. Rewind (with no interrupt)

In this event, the command is executed but the Formatter remains in State O.

Figure 3-2. Simplified State Flow

If CBUSY is set, than a rewind command causes the Formatter to enter State 7 until the rewinding status signal is false, at which time CBUSY is cleared and State 0 is re-entered.

Any other command causes one of the two Predelay States to be entered. State 1 is normally used, but State 2 is used when the Formatter is at BOT or a 3-inch Gap Command is executed. The appropriate motion signal (SFC for forward motion, SRC for reverse motion) is activated at this time.

The predelays are used to erase a 3-inch gap or part of the IRG when writing and to allow sufficient time for the tape unit to get "up to speed".

The State 3 data transfer then takes place. For writing, the data is written until the HALT signal from the Computer Adapter terminates the record. For "Erase" no data transfer is needed, so State 3 is terminated immediately and State 4 is entered. For "Write File Mark" no data transfer actually occurs, but the Formatter writes the file mark and the LRC character and then enters State 4.

For dual gap (read-after-write) tape units, the transition from State 3 to State 4 is delayed until the read head detects the end of the record (the beginning of the IRG) to allow the full record to be checked for no parity errors. State 4 Postdelay (in conjunction with the .2-inch distance the tape moves <u>after</u> the motion command terminates) is used to erase the first part of the IRG.

For Reading or Spacing operation, State 3 is maintained until the end of the record and the IRG is reached. For reading, the Computer Adapter HALT signal terminates actual data exchange. For reading or spacing, the State 4 Postdelay (in conjunction with the fixed .2-inch distance, the tape moves when halting after the motion command terminates) is used to position the head in the correct position in the IRG to allow for a subsequent write or read operation.

Note that the 53 + 54 (DBY) signal is active only during States 3 and 4, while the 'motion' signals to the tape unit are active from the beginning of the Predelay State through the Postdelay State.

After the Postdelay occurs, one of the forward/reverse HALT delays (State 5 or 6) is entered (to insure that the tape is allowed sufficient time to come to a halt in the IRG).

At the termination of the Halt Delay, signal CBUSY is cleared (to signal the computer that the next command can now be executed) and the Rest State 0 is entered.

The "Special Exit" from States 5 or 6 allows continuous writing or reading without stopping in the inter-record gap to optimize data transfer efficiency.

Since the Start/Stop characteristics of the tape units are "ramp" like, the gap traverse time is twice as long (as it would be at full speed) when the next command is delayed until the tape has completely halted.

This "special exit" allows a Write or a Read command to terminate the Halt Delay state and initiate the Predelay state without being "rejected", even though the CBUSY signal is active.

In any other State, with CBUSY active, a command (other than Clear) is rejected.

The computer can accomplish "on-the-fly" writing or reading by initiating the next command when DBY terminates at the end of State 4, rather than waiting until CBUSY terminates.

However, there are certain restrictions on this type of operation:

- The next command must not switch from a Write or Write-File Mark to a Space or Read (or vice versa).

- 2. The next command must not switch direction or motion.

- 3. The next command must not be a <u>Rewind</u> or <u>Offline</u> if the previous one was a Write, or Write File Mark type.

It is the computer program's responsibility to make sure these restrictions are followed.

The Delay Counter is used in States 1, 2, 4, 5 and 6 to generate the prescribed delay times.

## 3.4.2 Detailed State Flow (See Figure 3-3)

The Detailed State Flow chart shows the control over signals DBY, CBUSY and the motion commands SFC, SRC as well as the use of the Delay Counter. Otherwise the flow chart is like Figure 3-2.

In addition, the IRG detection exit from State 3 is detailed, as is the detour around State 4 Postdelay (to achieve minimum Postdelay) in certain cases.

#### 3.5 COMMAND EXECUTION TIMING

The main commands are discussed step-by-step and a timing diagram is included for each command.

The main commands are:

- Rewind (with interrupt)

- 2. Write file mark (7 track)

- 3. Write file mark (9 track)

Figure 3-3. Detailed State Flow

- 4. Forward Space 1 record

- 5. Backspace 1 record

- 6. Write 1 record (7 track)

- 7. Write 1 record (9 track)

- 8. Read 1 record (7 track)

- 9. Read 1 record (9 track)

- 10. Erase 3-inch gap

# 3.5.1 Rewind (With Interrupt)

The offline command doesn't set CBUSY. In this event, the commands are passed on to the selected tape unit as a pulse.

When the computer adapter generates the 6-STROBEC pulse while 6-SETREW is high and the Controller isn't busy, the command is accepted and the 2-VLD pulse is generated.

The 3-REW flip-flop is set to store the rewind command. When the 6-STROBEC clock pulse terminates, the Rewind command is generated to the selected tape unit (signal 3-RWC). When the tape unit responds that it is rewinding (signal 7-REWINDING) the 3-REW flip-flop is reset and the Controller 6-RWDG status bit is set. The tape unit goes "not ready" (7-RDY) during rewind. Since the tape unit rewind terminates before the tape unit returns to load point and becomes "Ready" again, the 6-RWDG status bit is interlocked to wait until the tape unit goes ready (7-RDY).

The 3-SRS (system visit) pulse clears the status register.

At this time 6-CBUSY\* resets to signal that the operation is complete.

## 3.5.2 Write File Hark (7-Track) (See Figure 3-4)

When signal 6-SET WFM is high during the 6-STROBEC clock pulse, the 3-WFM command-register flip-flop is set to initiate a Write-File-Mark command. The 2-SRS pulse is also generated to reset the Controller to initial conditions. The 3-CBUSY flip-flop is set by the 2-VLD clock, and the 7-SFC command is activated to start the tape moving in the forward direction. The selected tape unit write amplifiers are enabled as the 7-WARS\* signal is high. Command register flip-flop 3-WFM also sets the selected tape transport unit to the write mode via signal 7-SWS. The Predelay signal delays writing of the file mark character until the tape transport unit is up-to-speed and has generated a portion of the required inter-record gap.

If the tape transport unit is at the beginning of tape when the Write-File-Mark instruction is generated, the Predelay is longer to cause a 3-inch gap to be erased before the file mark is written. The Enable Write Data Request flip-flop (9-EWDR) is set upon the termination of the Predelay signal. The Write Data Clock flip-flop (9-WDCL) is set one write-clock-period later and is gated to set the enable blank character counter (9-EBCC) flip-flop. The 9-EWDR flip-flop is immediately reset, which causes flip-flop 9-WDCL to be reset one write-clock-period later. Thus, only one Write Data strobe is generated to the selected tape transport unit. The command register flip-flop 3-WFM gates the file mark code onto the write data bus.

The blank character counter (comprised of flip-flops 9-CC1, 9-CC2, and 9-CC4) begins counting from the occurrence of the Write-File-Mark clock. This causes the 9-WARS flip-flop to be set, resetting the tape unit write amplifier flip-flops, causing the LRC character to be written. The tape transport unit continues running in the forward direction until the file mark passes under the read head, thus the file mark and LRCC character can be checked for vertical parity and longitudinal parity.

Figure 3-4. Rewind Timing Diagram

The time interval in milliseconds, between writing the file mark and reading back the file mark character, is equal to 150 divided by the tape speed in inches-per-second. As the timing diagram illustrates, the Read Data strobe (7-RDS) will occur, and eight character times later (for 9-track), the LRC character read strobe will occur. The LRC character occurs four character times later for 7-track. The read clock activity sensor (12-RCAS) is set upon detection of the first 7-RDS pulse and times out two or three clock periods later. While the 12-RCAS circuit is active, the character parity is checked.

The Delay Counter is reset by each Read strobe and then times out a delay interval after the last Read strobe. Thus, the Delay Counter performs the taks of IRG detection. Upon termination of the Delay Counter time out, the 5-STOP pulse is generated and used to check for an LRCC error in the previous record. The 5-STOP pulse is also used to trigger the State 4 Post Delay circuits (14-S4). When the Post Delay terminates, the 7-SFC signal is terminated, and the State 5 Halt Delay is entered. The Halt Delay insures that the tape transport unit is guaranteed to have ceased all motion in the inter-record gap. If the next command is to be a write-type command, then the IRG can be erased "on the fly" at full tape speed (without stopping in the IRG). This is done by issuing the command after the signal 6-DBY terminates rather than waiting until 6-CBUSY terminates. Status is valid after the 6-DBY signal terminates, hence the status can be checked before issuance of the next command.

# 3.5.3 Write File Mark (9-Track) (See Figure 3-5)

Writing a File Mark in 9-track mode is similar to the 7-track mode except that eight character times separate the file mark and the LRC character. Note that there is effectively an "all zeros" CRC character, since for data records the CRCC occurs at the 4th character time then 4 character times later the LRCC is written.

Figure 3-5. Write File Mark Timing Diagram (7-Track Mode)

# 3.5.4 Forward Space/Record (See Figure 3-6)

When term 6-SET FSR is high with the 6-STROBEC, the 7-SFC signal is activated to move tape forward. The 2-VLD and 3-SRS pulses are generated to reset the Controller and initiate the space-forward operation.

NOTE The Space Forward Command results in spacing over ONE record if signal 6-STOP SPACE is "open circuit" or at the High level. If multiple records are to be spaced over, 6-STCP SPACE is held low until the leading edge of signal 6-DBY occurs for the last record. The 6-FM status signal and 6-EOTS status signal may also be utilized to switch STOP SPACE "high" so that a file mark or the end of tape will halt the multiple record spacing operation.

Note that 6-CBUSY remains low (for multiple spacing operations) until the final record has been passed.

The Predelay allows the tape unit to get up to speed before allowing Read strobes to be accepted. The Read strobes activate the Read Clock Activity Sensor (12-RCAS) to enable parity checks to be made while spacing. When the record is past, the Delay Counter times out to detect the IRG and the LRCC check is made. After the Signal 6-DBY terminates, status can be checked and the next command can be issued (if a Read or Space Forward) to accomplish non-stop operation.

If no new command is issued at this time, the normal Halt Delay sequence is entered.

# 3.5.5 Backspace/Record

Backspace is similar to Forward space except the LRC/CRC characters occur first.

1. CRCC MAY BE MISSING FOR 9 TRACK AND IS ABSENT ON 7 TRACK.

Figure 3-6. Forward Space One Record Timing Diagram

# 3.5.6 Write-One-Record (7-Track) (See Figure 3-7)

The write-one-record instruction causes the tape transport unit to turn on the write current, enable the write amplifiers, get up to speed, generate a portion of the inter-record gap, then request output data transfers from the computer adapter logic. The requested data characters are written on tape until a HALT signal terminates the record by writing the CRC character (9-track only) followed by the LRC character.

The tape transport unit read-after-write head enables parity checks to be performed upon the record that has just been written. After the parity checks are completed, the tape transport unit erases a portion of the next inter-record gap and is then commanded to halt. After sufficient time has elapsed to ensure that the tape has completely stopped moving, the completion of the write-one-record operation is signaled when 6-CBUSY terminates.

"On-the-fly" generation of the IRG without signal stopping may be accomplished by checking status, at the termination of signal (53 + 54) and issuing the next Write, Erase or Write File Mark command immediately. The Write mode is set by the command clock (2-VLD) to initiate the Write-One-Record instruction. The System Reset Pulse (3-SRS) is also generated by the Valid Command clock to reset the tape transport controller to initial conditions. The Controller Busy flip-flop (6-CBUSY) is set by the command clock to initiate the Write-One-Record instruction. The Synchronous Forward signal (7-SFC) is sent to the tape unit to initiate forward motion.

After the Predelay (14-S1, S2) times out, the enable write data request flip-flop (9-EWDR) is clocked set to begin the writing of the record. The Predelay erases the last portion of the inter-record gap as the write current is on for this period. The Write Data Clock flip-flop (9-WDCL) is clocked set one clock time after the 9-EDWR flip-flop to enable write strobes to be generated to the tape unit.

The first Data Flag signal is sent to the computer adapter. When the Computer Adapter logic has the first character ready to transfer, it generates the 6-W/RACK pulse, which stores the first output character in the Formatter Write Data Register and clears the Data Flag. The first write data strobe (7-WDS) is then generated by the next write clock pulse (1-WCLP) in order to clock the character stored in the write data storage register onto the magnetic tape. At the trailing edge of the write data strobe, the Data Flag is set to request the next character from the Computer Adapter logic.

The Write Data Strobe (7-WDS) is OR'ed with an extra CRC clock generation signal to clock the CRC generator register (logic diagram 15), to begin calculation of the CRC character. The CRC generator register is initially reset. The CRC generator register than monitors the write data output bus to generate a check character that is unique for the data characters written on tape.

If the output data character is not transferred to the tape controller before the next write data strobe is to occur, a "timing error" status bit will be set. The sequence of Data Flag-W/R ACK-Write Strobe continues until the HALT signal is generated by the Computer Adapter to terminate the writing. The HALT signal sets the enable-blank-character-counter (9-EBCC) flip-flop. Flip-flop 9-EBCC enables the Blank Character Counter (CCl, 2, 4), disables the Write Control flip-flops, and resets the Write Most Significant Byte (WRMSB) flip-flop.

The Blank Character Counter controls the generation of the CRC and LRC characters to generate the end of the record.

The character counter is decoded in the 9-track mode to create an extra CRC clock and to gate the contents of the CRC generator onto the write data bus. The character counter is also decoded in order to set the 9-WARS flip-flop to reset the write amplifiers via signals 7-WARS (in order to generate the LRC character).

The tape transport unit continues motion in the forward direction so that the read-after-write head can check parity of the entire record. The Read clocks (7-RDS) trigger the Read Clock Activity Sensor circuit (12-RCAS), which defines the characters that are to be checked for vertical parity. Two or three clock-periods after the last character in the record, the 12-RCAS signal terminates and vertical parity checking is disabled. The Delay Counter times out after the LRC character is detected at the end of the record to provide detection of the IRG. The 5-STOP pulse is then used to check for an LRC error. The Post Delay time-out interval ensures that a sufficient portion of inter-record gap is erased in the forward direction after a record is written. This permits the tape transport unit to start in the reverse direction and get up to speed for a backspace read. At the end of the Post Delay, the synchronous forward command terminates, and the Halt Delay begins timing out to ensure that the tape has come to a complete halt before the 6-CBUSY signal terminates.