Date: 12 April, 1996

From: Daniel Leibholz

Dept: Digital Semiconductor

MS: HLO2-3/J3 DTN: 225-6141 Enet: ad::leibholz

Topic: EV6 Chip Specification, Rev 2.0

Enclosed you will find the second revision of the EV6 specification.

This version includes a major rewrite of the external interface, substantial changes to the PAL/IPR sections, as well as inclusion of PAL coding restrictions and some electrical and packaging information.

As the EV6 design proceeds, we are filling in the details of the following topics:

- Electrical and packaging information

- Reset and initialization

- Test and debug features

- PLL Operation

- Error handling

We will send further documentation on these areas (plus errata/changes to rev. 2.0) when available.

Please note that the EV6 specification is Digital Confidential. Refer all requests for copies to Sue Jacquart (ad::jacquart/DTN 225-4967).

Please refer questions regarding the spec to the following individuals:

EV6 Microarchitecture/PALcode/IPR issues: Dan Leibholz EV6 System Interface/Electrical issues: Rick Hetherington (ad::hetherington, DTN 225-4571)

# **EV6** Specification

Rev 2.0 April 10, 1996

**Digital Company Confidential**

The drawings and specifications in this document are the property of Digital Equipment Corporation and shall not be reproduced, copied or used in whole or in part as the basis for the manufacture or sale of items without written permission.

The information in this document may be changed without notice and is not a commitment by Digital Equipment Corporation. Digital Equipment Corporation is not responsible for any errors in this document.

This specification does not describe any program or product that is currently available from Digital Equipment Corporation, nor is Digital Equipment Corporation committed to implement this specification in any program or product. Digital Equipment Corporation makes no commitment that this document accurately describes any product it might ever make.

Copyright © 1995, 1996 by Digital Equipment Corporation All Rights Reserved Printed in U.S.A.

| 1. EV6 AND THE ALPHA ARCHITECTURE                          | 7  |

|------------------------------------------------------------|----|

| 1.1 Alpha Architectural Extensions                         | 7  |

| 1.2 Implementation-Specific Features                       | 7  |

| 1.3 Instruction Set Features Defined as Optional           | 8  |

| 1.4 Arithmetic Exceptions                                  | 8  |

| 2. INTERNAL ARCHITECTURE                                   | 9  |

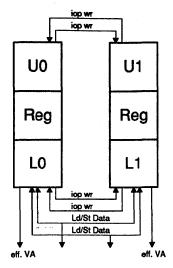

| 2.1 Chip Organization                                      | 9  |

| 2.1.1 Ebox                                                 | 9  |

| 2.1.2 Fbox                                                 | 10 |

| 2.1.3 Ibox                                                 | 11 |

| 2.1.4 On-chip Caches                                       | 13 |

| 2.1.5 Mbox                                                 | 14 |

| 2.1.6 Cbox                                                 | 15 |

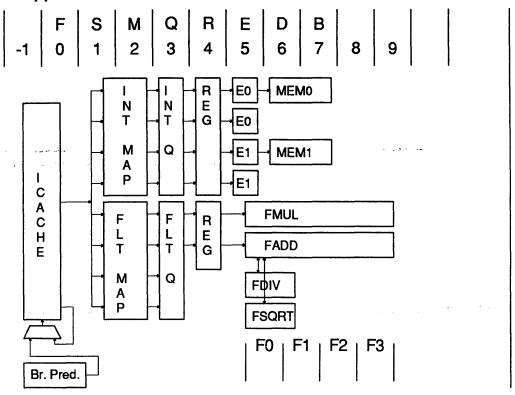

| 2.2 Pipeline Organization                                  | 16 |

| 2.2.1 Stage 0 - Instruction Fetch                          | 16 |

| 2.2.2 Stage 1 - Instruction Slot                           | 16 |

| 2.2.3 Stage 2 - Map                                        | 17 |

| 2.2.4 Stage 3 - Issue                                      | 17 |

| 2.2.5 Stage 4 - Register Read                              | 17 |

| 2.2.6 Stage 5 - Execute                                    | 17 |

| 2.2.7 Stage 6 - Deache Access                              | 17 |

| 2.2.8 Instruction Retire                                   | 17 |

| 2.2.9 Retire of Operates into R31/F31                      | 18 |

| 2.2.10 Pipeline Aborts                                     | 18 |

| 2.3 Memory And I/O Accesses                                | 19 |

| 2.3.1 Memory Space Load Instructions                       | 19 |

| 2.3.2 IO Space Load Instructions                           | 19 |

| 2.3.3 Memory Space Store Instructions                      | 20 |

| 2.3.4 IO Space Store Instructions                          | 20 |

| 2.4 Replay Traps                                           | 21 |

| 2.4.1 Mbox Order Traps                                     | 21 |

| 2.4.2 Other Mbox Replay Traps                              | 22 |

| 2.5 Software-Directed Prefetching and Loads into R31 & F31 | 22 |

| 2.5.1 Normal Prefetch: LDL, LDF, LDG, LDB, LDW             | 22 |

| 2.5.2 Prefetch with Modify Intent: LDS                     | 22 |

| 2.5.3 Prefetch, Evict Next: LDQ                            | 22 |

| 2.5.3 Ficietcii, Evict Next. LDQ                           | 22 |

| אינו ווער בער אווער | and the second s | 4,074,7 | managaratica . t. two yo to shakit | تاون وسبت ۱۰ ند |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------|-----------------|--|

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                    |                 |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •       |                                    |                 |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                    |                 |  |

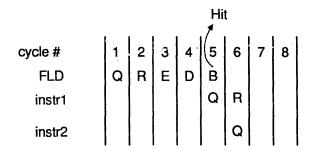

|    | 2.6 Special Cases 2.6.1 Load Hit Speculation                                      |      |          | 22<br>23 |

|----|-----------------------------------------------------------------------------------|------|----------|----------|

|    | 2.6.2 Floating Point Stores 2.6.3 CMOV                                            |      |          | 24<br>24 |

|    | 2.7 Instruction Issue Rules                                                       |      |          | 25       |

|    | 2.7.1 Instruction Class Definitions                                               |      |          | 25       |

|    | 2.7.2 Ebox Slotting 2.7.3 Instruction Latencies                                   |      |          | 25<br>28 |

|    | 2.7.5 Instruction Latencies                                                       |      |          | 20       |

| 3. | EXTERNAL INTERFACE                                                                |      |          | 29       |

|    | 3.1 Address Spaces                                                                |      |          | 29       |

|    | 3.1.1 I/O Ordering and Merge Rules                                                |      |          | 31       |

|    | 3.2 Cache Organization and Coherence                                              |      |          | 31       |

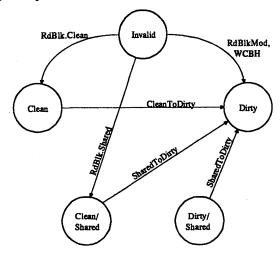

|    | 3.2.1 Cache Block States                                                          |      |          | 31       |

|    | 3.2.2 Cache Block State Transitions                                               |      |          | 32       |

|    | 3.2.3 System Knowledge of Bcache Contents                                         |      |          | 33       |

|    | 3.2.4 Dcache States & the Dcache Duplicate Tags                                   |      |          | 33       |

|    | 3.2.5 Memory Barrier (MB/WMB/TBfill flow)                                         |      |          | 33       |

|    | 3.2.6 Load/Locked and Store/Conditional                                           |      |          | 35       |

|    | 3.3 System Port                                                                   |      |          | 38       |

|    | 3.3.1 System Port Pins                                                            |      |          | 38       |

|    | 3.3.2 EV6 to System Address/Command Format                                        |      |          | 38       |

|    | 3.3.3 SysAdd Commands Generated by EV6                                            |      |          | 39       |

|    | 3.3.4 Probe Response Transfers                                                    |      |          | 41       |

|    | 3.3.5 SysAck & System Port Flow Control                                           |      |          | 41       |

|    | 3.3.6 SysReadValid and Speculative Reads                                          |      |          | 41       |

|    | 3.3.7 SysAdd Commands Generated by the System                                     |      |          | 42<br>44 |

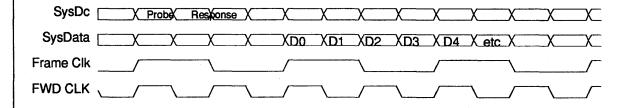

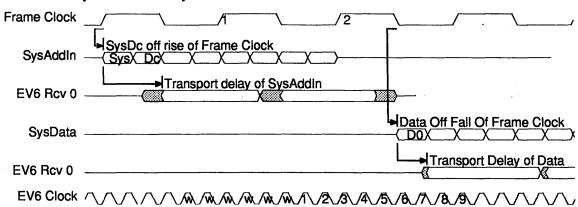

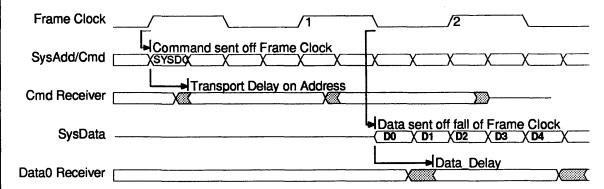

|    | 3.3.8 Two Cycle Commands For Data Transfers 3.3.9 Data Movement In and Out of EV6 |      |          | 44       |

|    | 3.3.10 Data ECC                                                                   |      | <b>.</b> | 50       |

|    | 3.3.11 Ordering of System Port Transactions                                       |      |          | 51       |

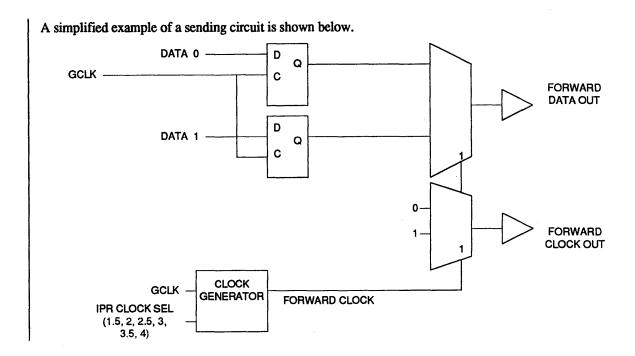

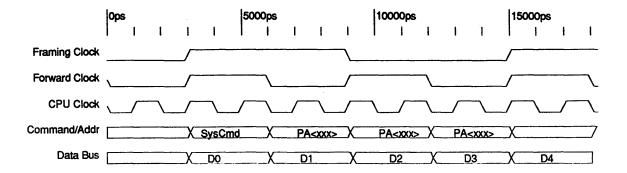

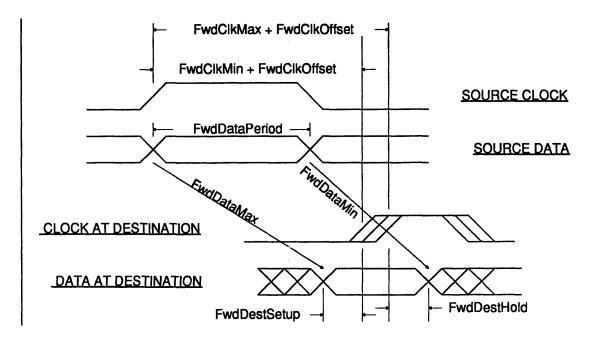

|    | 3.3.12 System Port Clocking                                                       |      |          | 53       |

|    | 5.51.2 5) 5.66.1 1 6.6 6.66.1.1.g                                                 |      |          | - 55     |

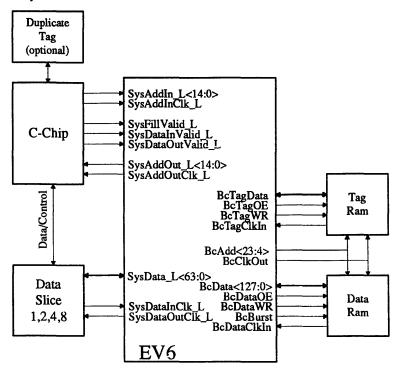

|    | 3.4 Bcache Port                                                                   |      |          | 66       |

|    | 3.4.1 Bcache Port Pins                                                            |      |          | 66       |

|    | 3.4.2 Pin Descriptions                                                            |      |          | 66       |

|    | 3.4.3 Bcache Banking                                                              |      |          | 67       |

|    | 3.4.4 Beache Transactions                                                         |      |          | 67       |

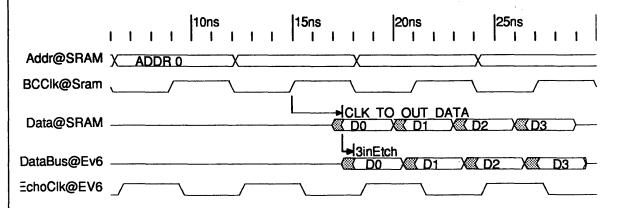

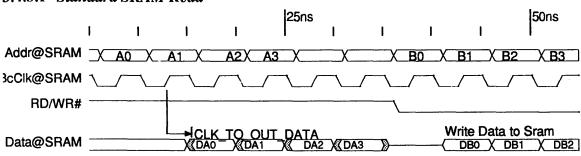

|    | 3.4.5 Bcache Clocking                                                             |      |          | 67       |

|    | 3.5 Interrupts                                                                    |      |          | 70       |

|    | 3.6 Pin List                                                                      |      |          | 70       |

| 4  | . PRIVILEGED ARCHITECTURE LIBRARY                                                 | CODE |          | 72       |

|    | 4.1 Use of Alpha Implementation-Specific Opcodes                                  |      |          | 72       |

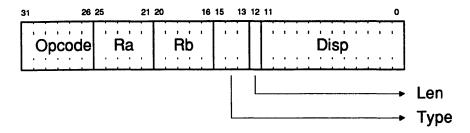

|    | 4 1 1 HW I D Instruction                                                          |      |          | 73       |

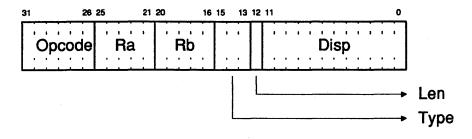

| 4.1.2 HW_ST Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

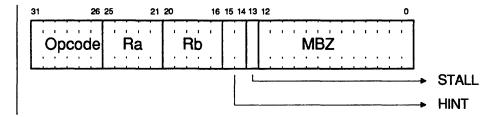

| 4.1.3 HW_RET Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75  |

| 4.1.4 HW MFPR and HW MTPR Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75  |

| 1.1.1 11 W _ 1 1 1 2 W 1 2 W _ 1 1 1 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W 1 2 W | ,,, |

| 4.2 Internal Processor Register Access Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77  |

| 4.2.1 IPR Scoreboard Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 77  |

| 4.2.2 Hardware Structure of Explicitly Written IPRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78  |

| 4.2.3 Hardware Structure of Implicitly Written IPRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78  |

| 4.2.4 IPR Access Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 79  |

| 4.2.5 IPRs and HW_RET Stalls                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79  |

| 4.3 PAL Shadow Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| 4.4 PALcode Emulation of FPCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80  |

| 4.4.1 Status Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 80  |

| 4.4.2 MF_FPCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80  |

| 4.4.3 MT_FPCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80  |

| 4.5 PALcode Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80  |

| 4.5.1 CALL_PAL entry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81  |

| 4.5.2 PALcode Exception Entry Points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81  |

| 4.5.217 Eloue Encoption Linky Forms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 01  |

| 4.6 TB Fill Flows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 82  |

| 4.6.1 DTB Fill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 82  |

| 4.6.2 ITB Fill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •   |

| 5. INTERNAL PROCESSOR REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | :   |

| 5.1 Ebox IPRs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86  |

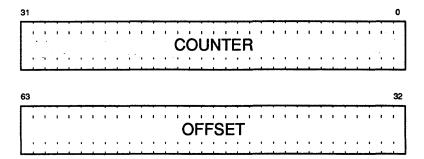

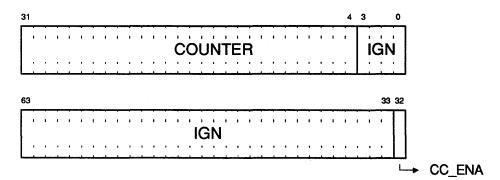

| 5.1.1 CC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86  |