VT48

display processor

unit

technical manual

# Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual or optional equipment covered herein.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

# **CONTENTS**

|           |                                                                | Page |

|-----------|----------------------------------------------------------------|------|

| CHAPTER 1 | GENERAL DESCRIPTION                                            |      |

| 1.1       | INTRODUCTION                                                   | 1-1  |

| 1.2       | PHYSICAL DESCRIPTION                                           |      |

| 1.3       | FUNCTIONAL DESCRIPTION                                         |      |

| 1.4       | RELATED DOCUMENTS                                              |      |

| 1.5       | SPECIFICATIONS                                                 |      |

| CHAPTER 2 | VT48 DISPLAY PROCESSOR UNIT INSTALLATION                       |      |

| 2.1       | UNPACKING                                                      | 2-1  |

| 2.2       | H7070 POWER SUPPLY MOUNTING PROCEDURE                          |      |

| 2.3       | VT48 DISPLAY PROCESSOR UNIT MOUNTING                           |      |

| 2.4       | VT48 DISPLAY PROCESSOR UNIT CHECKOUT                           |      |

| 2.4.1     | Instruction Processing Checkout                                |      |

| 2.4.2     | VT48 Analog (Vector Generator and Chapter Generator) Checkout  |      |

| CHAPTER 3 | VT48 OPERATION AND PROGRAMMING                                 |      |

| 3.1       | INTRODUCTION                                                   | 3-1  |

| 3.2       | POWER APPLICATION                                              |      |

| 3.3       | VT48 INSTRUCTION SET                                           |      |

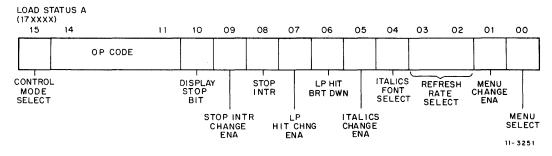

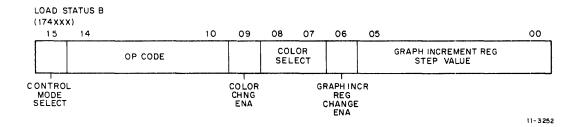

| 3.4       | LOAD STATUS INSTRUCTIONS                                       |      |

| 3.5       | SET GRAPHIC MODE INSTRUCTION                                   |      |

| 3.6       | GRAPHIC ENTITY INSTRUCTIONS                                    |      |

| 3.7       | BRANCH INSTRUCTIONS                                            | 3-28 |

| 3.8       | VT48 ADDRESSABLE REGISTERS                                     | 3-32 |

| 3.9       | IMAGE GENERATION AND MANIPULATION                              | 3-46 |

| 3.9.1     | Display File Make-up and Refresh Considerations                | 3-46 |

| 3.9.2     | Visible and Virtual Display File Entities                      | 3-47 |

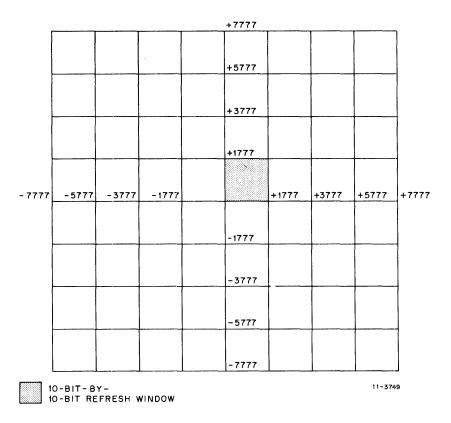

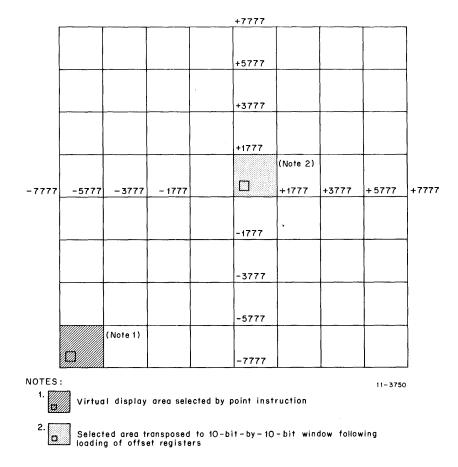

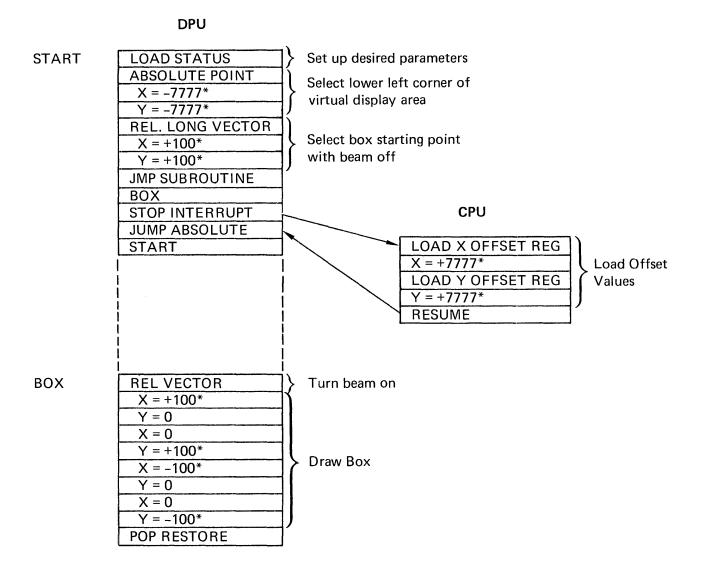

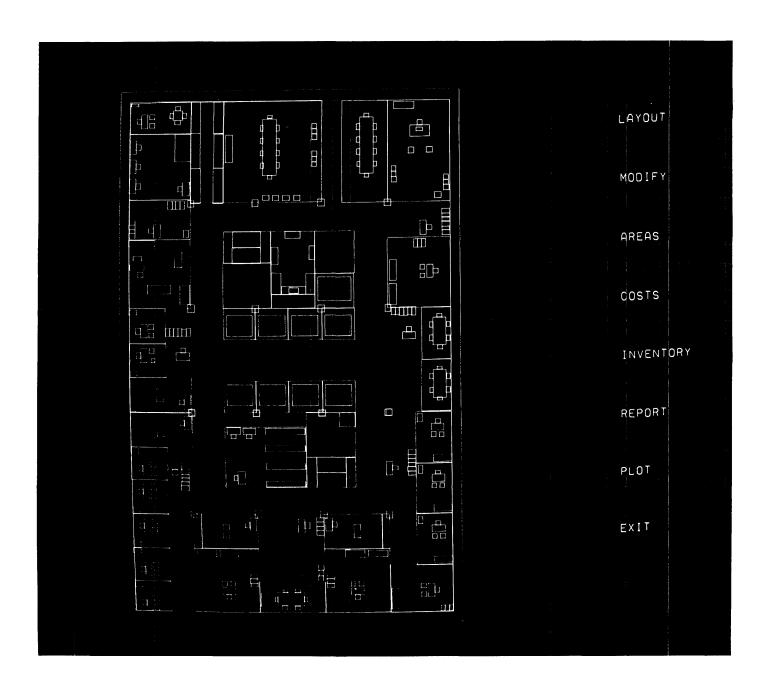

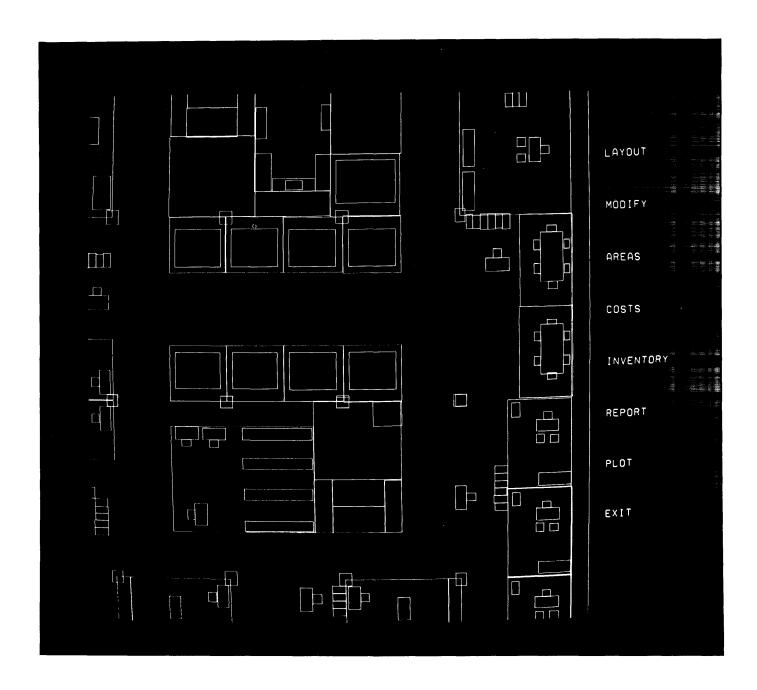

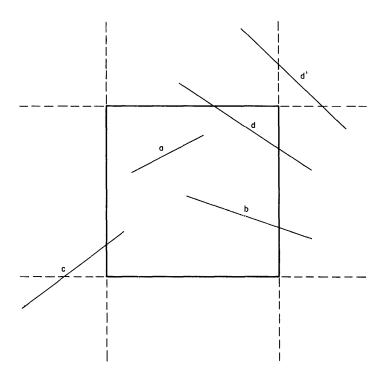

| 3.9.3     | Windowing Through Use of Point and Offset Capabilities         | 3-47 |

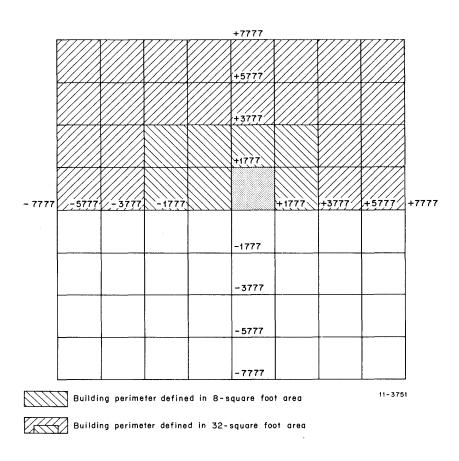

| 3.9.4     | Advantages of "Windowing"                                      | 3-50 |

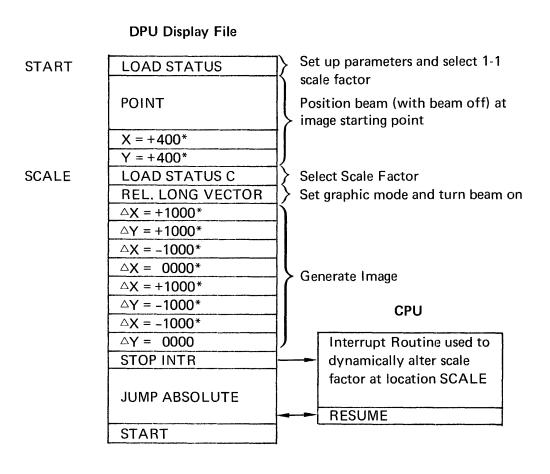

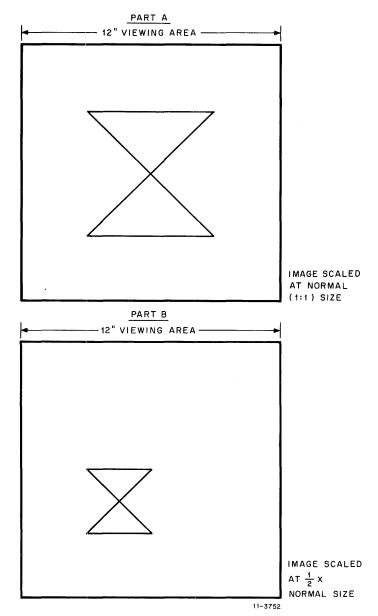

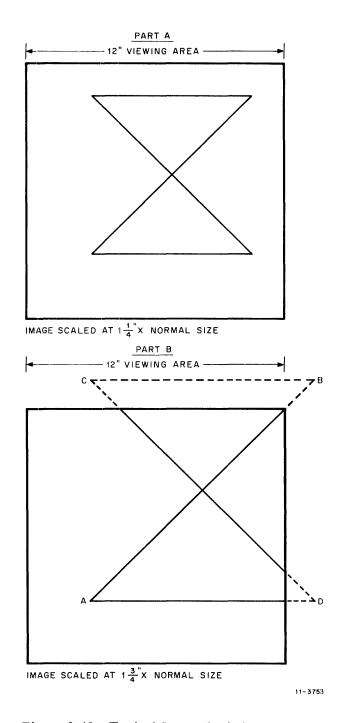

| 3.9.5     | Image Scaling and Scissoring                                   | 3-52 |

| 3.9.6     | Subpictures and Methods of Generation                          | 3-56 |

| 3.9.7     | Subroutine Nesting Through use of Stack Memory                 | 3-58 |

| 3.9.8     | Stack Status Byte Map                                          | 3-58 |

| 3.9.9     | Display File Searching Through use of Name Matching Techniques | 3-61 |

| 3.10      | INTERRUPT HANDLING                                             | 3-62 |

| 3.10.1    | General                                                        | 3-62 |

| 3.10.2    | Reinitiating Display File Processing Following                 |      |

|           | Interrupt Handling Routines                                    | 3-65 |

| 3.11      | SPECIAL FEATURES                                               |      |

| 3.11.1    | Dual Console Operation                                         |      |

| 3.11.2    | Use of Relocate Register in Systems Exceeding 32K of Memory    | 3-65 |

| 3.11.3    | Character String Escape                                        |      |

| 4.1         VT48 OVERALL BLOCK DIAGRAM         4-1           4.1.1         General         4-1           4.1.2         VT48 Startup Processing         4-1           4.1.3         Processsing Sequences per Instruction Category         4-1           4.1.3.1         Load Status Instruction         4-3           4.1.3.2         Set Graphic Mode Instruction         4-4           4.1.3.3         Graphic Entity Instructions         4-4           4.1.3.4         Processing from BDB Register Through the Stack/Silo Control Logic         4-5           4.1.3.5         Processing by the Graphics Calculation Logic         4-6           4.1.3.6         Processing by the Vector Generator/Character Generator         4-8           4.1.3.7         Branch Instructions         4-9           4.1.4         Read Status Multiplexer and Register Addressing         4-9           4.2         DETAILED DESCRIPTIONS         4-10           4.1.4         Read Status Multiplexer and Register Addressing         4-9           4.2.1         Vector Data Flow (Transfer Path)         4-10           4.2.1         Vector Data Flow (Transfer Path)         4-10           4.2.2         Character Data Flow (Transfer Path)         4-12           4.2.3         Display Instruction Control Proce                                      |           | Page                                                         |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------|--|--|--|--|--|

| 4.1.1   General   4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CHAPTER 4 | THEORY OF OPERATION                                          |  |  |  |  |  |

| 4.1.2   VT48 Startup Processing   4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.1       | VT48 OVERALL BLOCK DIAGRAM                                   |  |  |  |  |  |

| 4.1.2   VT48 Startup Processing   4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.1.1     |                                                              |  |  |  |  |  |

| 4.1.3.1       Load Status Instruction       4-1         4.1.3.1       Load Status Instruction       4-3         4.1.3.2       Set Graphic Mode Instruction       4-4         4.1.3.3       Graphic Entity Instructions       4-4         4.1.3.4       Processing from BDB Register Through the Stack/Silo Control Logic       4-5         4.1.3.5       Processing by the Graphics Calculation Logic       4-6         4.1.3.6       Processing by the Vector Generator/Character Generator       4-8         4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator Block Diagram Discussion       4-14         4.2.3       Basic Display Instruction Processing Cycle       4-14         4.2.3.1       Basic Display Instruction Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-14         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussio                                              | 4.1.2     |                                                              |  |  |  |  |  |

| 4.1.3.1       Load Status Instruction       4-3         4.1.3.2       Set Graphic Mode Instructions       4-4         4.1.3.3       Graphic Entity Instructions       4-4         4.1.3.4       Processing from BDB Register Through the Stack/Silo Control Logic       4-5         4.1.3.5       Processing by the Graphics Calculation Logic       4-6         4.1.3.6       Processing by the Vector Generator/Character Generator       4-8         4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator       Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1 <td>4.1.3</td> <td colspan="6"></td>            | 4.1.3     |                                                              |  |  |  |  |  |

| 4.1.3.2   Set Graphic Mode Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1.3.1   |                                                              |  |  |  |  |  |

| 4.1.3.3   Graphic Entity Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4.1.3.2   |                                                              |  |  |  |  |  |

| 4.1.3.4       Processing from BDB Register Through the Stack/Silo Control Logic       4-5         4.1.3.5       Processing by the Graphics Calculation Logic       4-6         4.1.3.6       Processing by the Vector Generator/Character Generator       4-8         4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator       Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-14         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-23         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-23         4.2.5.3       Routing of Status/Parameter Data on Generation of       Display Surface Related Inte                    | 4.1.3.3   |                                                              |  |  |  |  |  |

| 4.1.3.5       Processing by the Graphics Calculation Logic       4-6         4.1.3.6       Processing by the Vector Generator/Character Generator       4-8         4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-14         4.2.3       Display Instruction Control and Time Pulse Generator       Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-14         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5       VT48 Status/Parameter Data During       4-25         4.2.5.1       Routing of Status/Parameter Data on Generation of       Display Surface Related Interrupts       4-25                                     | 4.1.3.4   | Processing from BDB Register Through the Stack/Silo          |  |  |  |  |  |

| 4.1.3.6       Processing by the Vector Generator/Character Generator       4-8         4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | 200000000000000000000000000000000000000                      |  |  |  |  |  |

| 4.1.3.7       Branch Instructions       4-9         4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.1.3.5   |                                                              |  |  |  |  |  |

| 4.1.4       Read Status Multiplexer and Register Addressing       4-9         4.2.2       DETALLED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1.3.6   |                                                              |  |  |  |  |  |

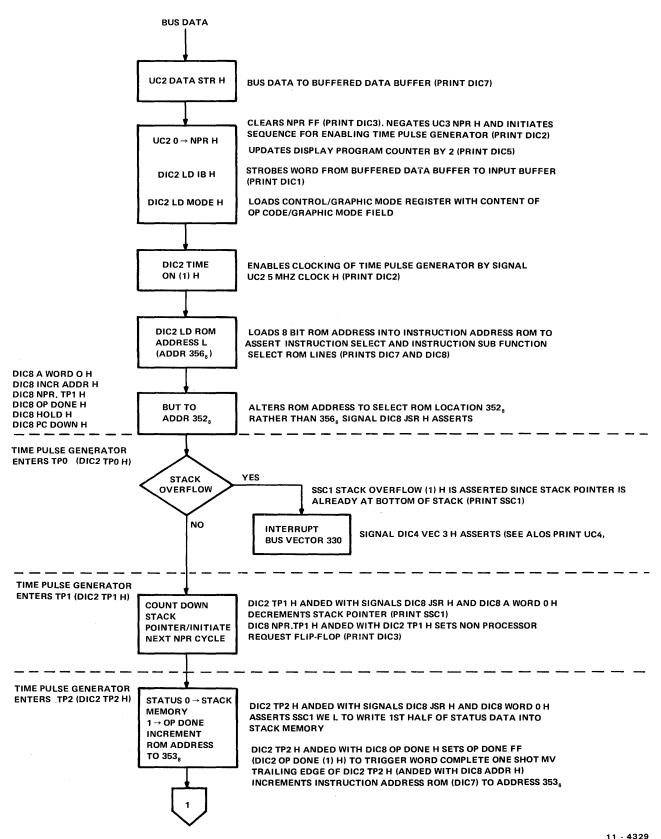

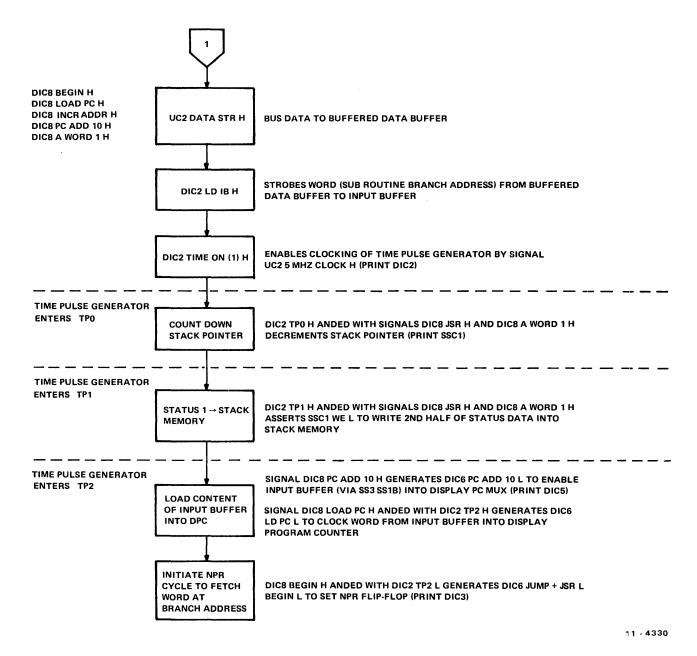

| 4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1.3.7   | Branch Instructions                                          |  |  |  |  |  |

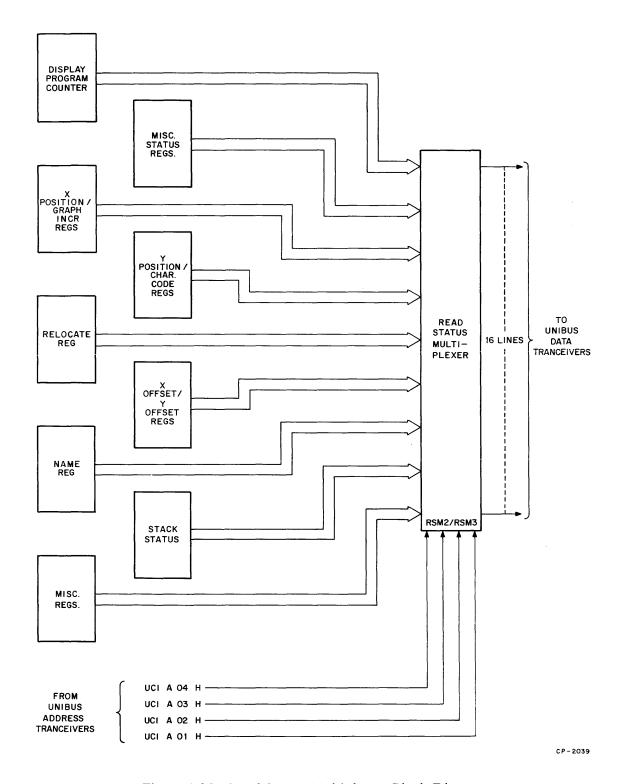

| 4.2       DETAILED DESCRIPTIONS       4-10         4.2.1       Vector Data Flow (Transfer Path)       4-10         4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.1.4     | Read Status Multiplexer and Register Addressing 4-9          |  |  |  |  |  |

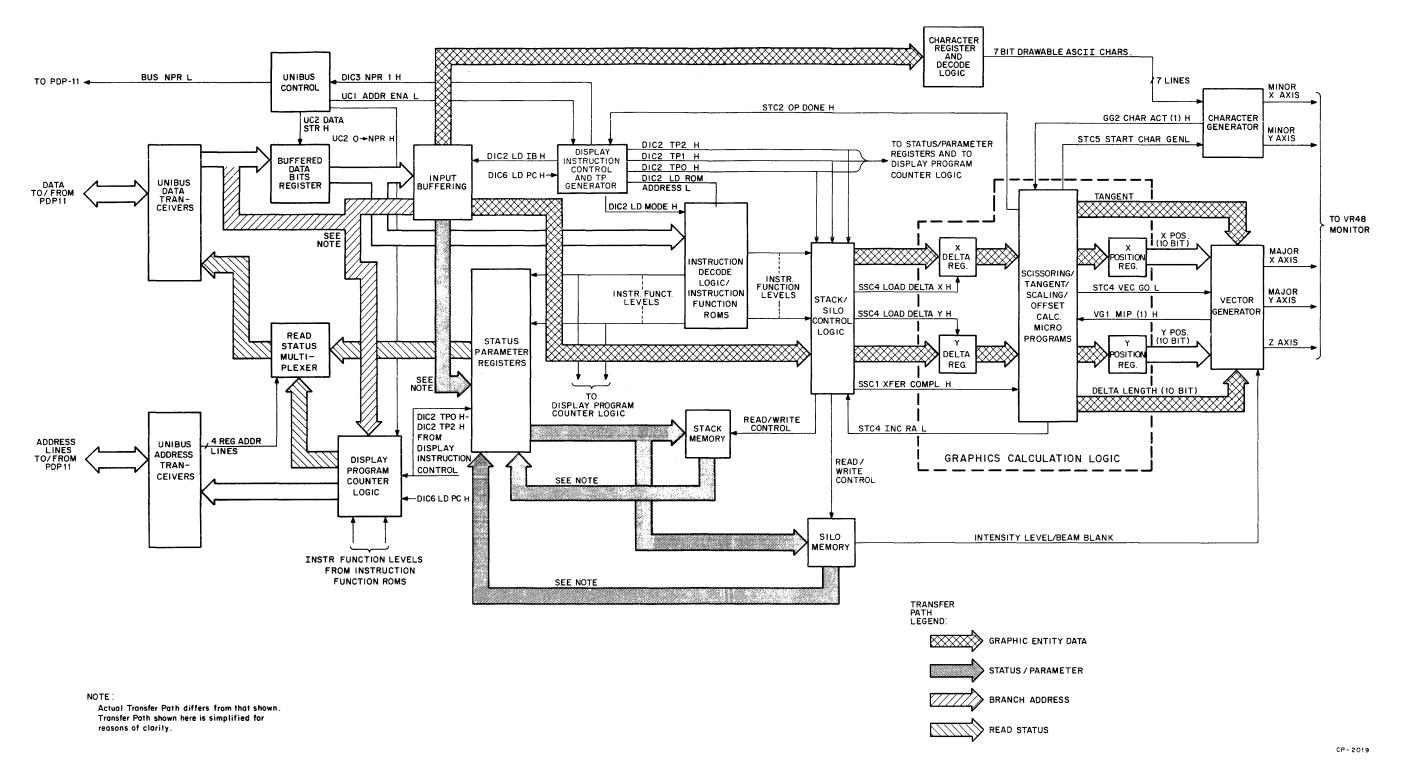

| 4.2.2       Character Data Flow (Transfer Path)       4-12         4.2.3       Display Instruction Control and Time Pulse Generator Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-24         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5       VT48 Status/Parameter Data During       Initial/Setup Operations       4-25         4.2.5.1       Routing of Status/Parameter Data on Generation of Display Surface Related Interrupts       4-25         4.2.5.2       Routing of Status/Parameter Data on Execution of JSR and POP Restore Instructions       4-28         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6.1       Start DPC Address Routing       4-29         4.2.6.2       Routin           | 4.2       |                                                              |  |  |  |  |  |

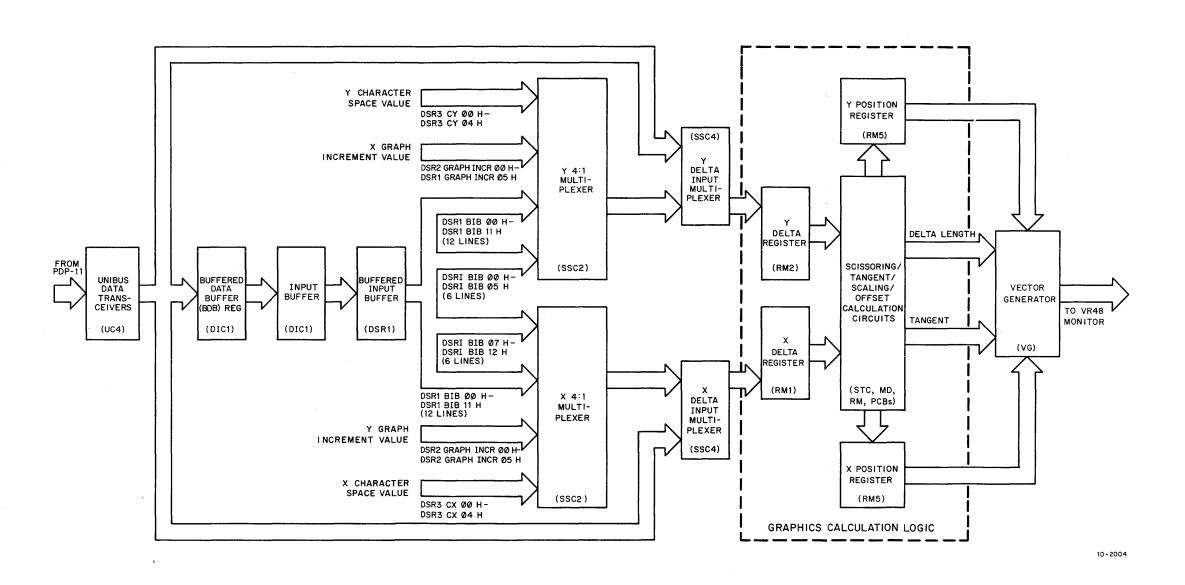

| 4.2.3       Display Instruction Control and Time Pulse Generator Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-28         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During       Initial/Setup Operations       4-25         4.2.5.2       Routing of Status/Parameter Data on Generation of Display Surface Related Interrupts       4-25         4.2.5.2       Routing of Status/Parameter Data on Execution of JSR and POP Restore Instructions       4-28         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6.1       Start DPC Address Routing       4-29         4.2.6.2       DPC Normal Update       4-29         4.2.6.3       Routing During Execution of Jump Relative and Jump to Subroutine Relative Instructions       4-31 | 4.2.1     | Vector Data Flow (Transfer Path)                             |  |  |  |  |  |

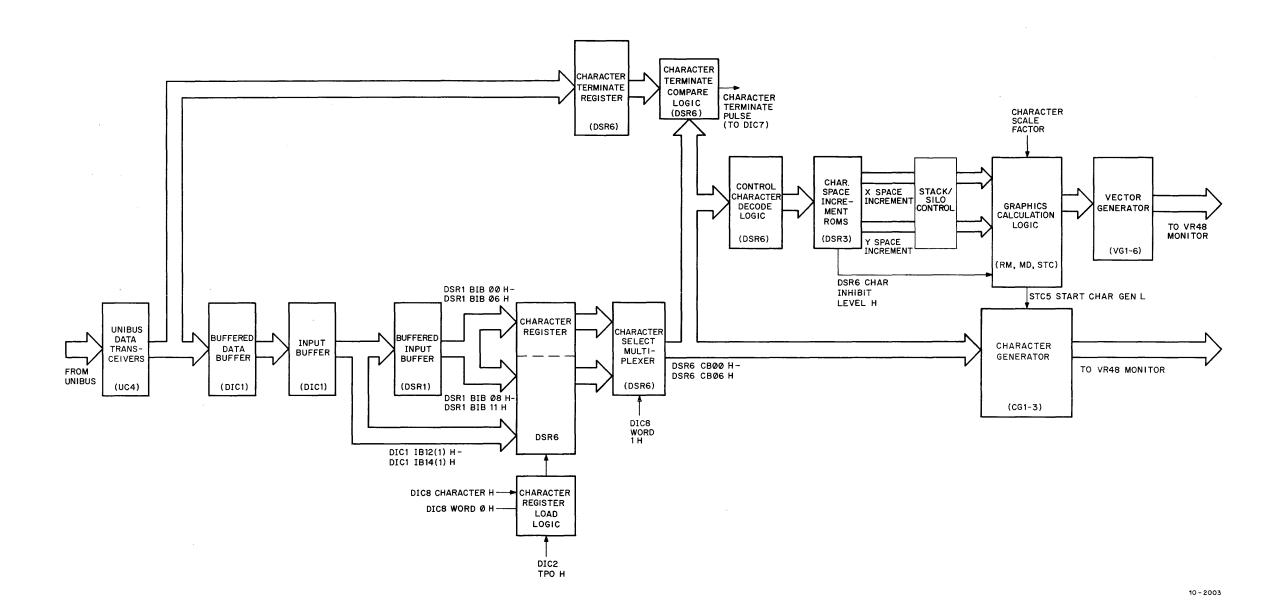

| 4.2.3       Display Instruction Control and Time Pulse Generator Block Diagram Discussion       4-14         4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-28         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During       Initial/Setup Operations       4-25         4.2.5.2       Routing of Status/Parameter Data on Generation of Display Surface Related Interrupts       4-25         4.2.5.2       Routing of Status/Parameter Data on Execution of JSR and POP Restore Instructions       4-28         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6.1       Start DPC Address Routing       4-29         4.2.6.2       DPC Normal Update       4-29         4.2.6.3       Routing During Execution of Jump Relative and Jump to Subroutine Relative Instructions       4-31 | 4.2.2     | Character Data Flow (Transfer Path)                          |  |  |  |  |  |

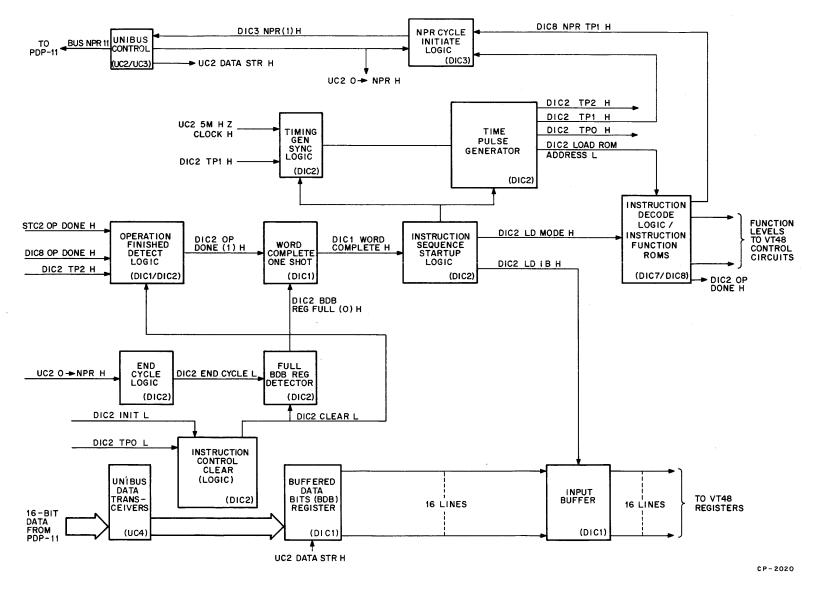

| 4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During       11114/Setup Operations       4-25         4.2.5.2       Routing of Status/Parameter Data on Generation of       24-25         4.2.5.3       Routing of Status/Parameter Data on Execution of       35-27         4.2.5.3       Routing of Status/Parameter Data on Execution of       4-27         4.2.6       Display Program Counter Input/Output Flow       4-28         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6.1       Start DPC Address Routing       4-29         4.2.6.2       DPC Normal Update       4-29         4.2.6.3       Routing During Execution of Jump Relative and       Jump to Subroutine Relative Instructions                            | 4.2.3     |                                                              |  |  |  |  |  |

| 4.2.3.1       Basic Display Instruction Control Processing Cycle       4-14         4.2.3.2       Implementation of NPR Cycle       4-16         4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During       11114/Setup Operations       4-25         4.2.5.2       Routing of Status/Parameter Data on Generation of       24-25         4.2.5.3       Routing of Status/Parameter Data on Execution of       35-27         4.2.5.3       Routing of Status/Parameter Data on Execution of       4-27         4.2.6       Display Program Counter Input/Output Flow       4-28         4.2.6       Display Program Counter Input/Output Flow       4-29         4.2.6.1       Start DPC Address Routing       4-29         4.2.6.2       DPC Normal Update       4-29         4.2.6.3       Routing During Execution of Jump Relative and       Jump to Subroutine Relative Instructions                            |           | Block Diagram Discussion                                     |  |  |  |  |  |

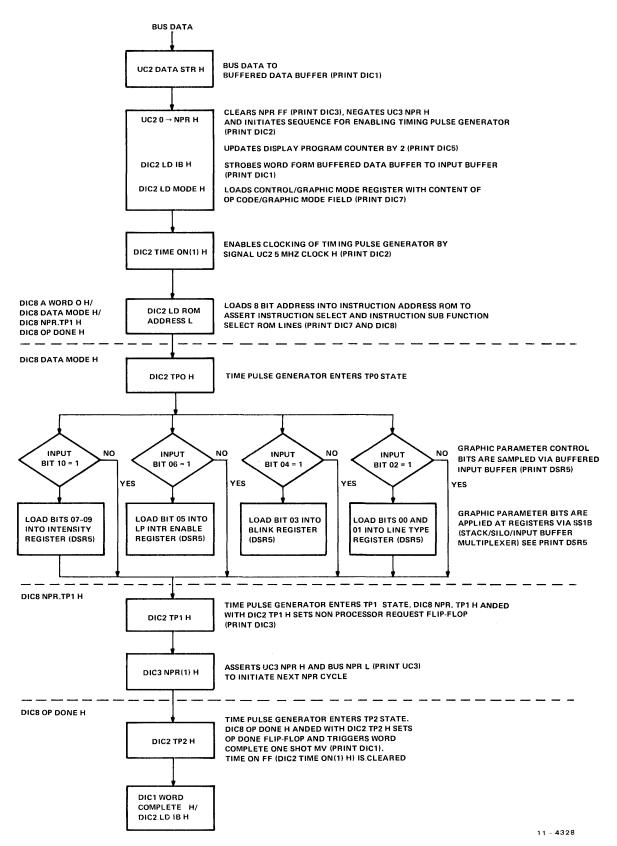

| 4.2.3.3       Operation Finished Detect Logic       4-17         4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4.2.3.1   | Basic Display Instruction Control Processing Cycle 4-14      |  |  |  |  |  |

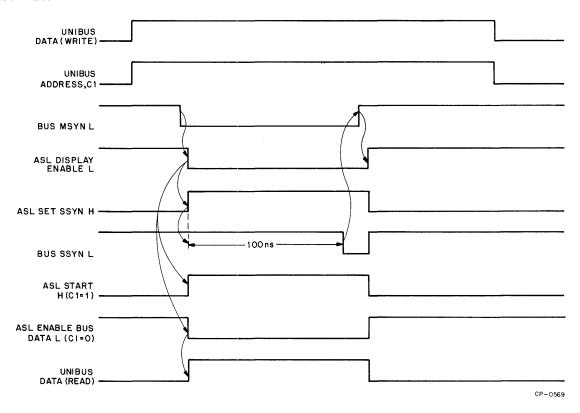

| 4.2.4       Instruction Decoding Circuits, Block Diagram Discussion       4-18         4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.2.3.2   | Implementation of NPR Cycle                                  |  |  |  |  |  |

| 4.2.4.1       Control Instruction Decoding       4-18         4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.3.3   | Operation Finished Detect Logic                              |  |  |  |  |  |

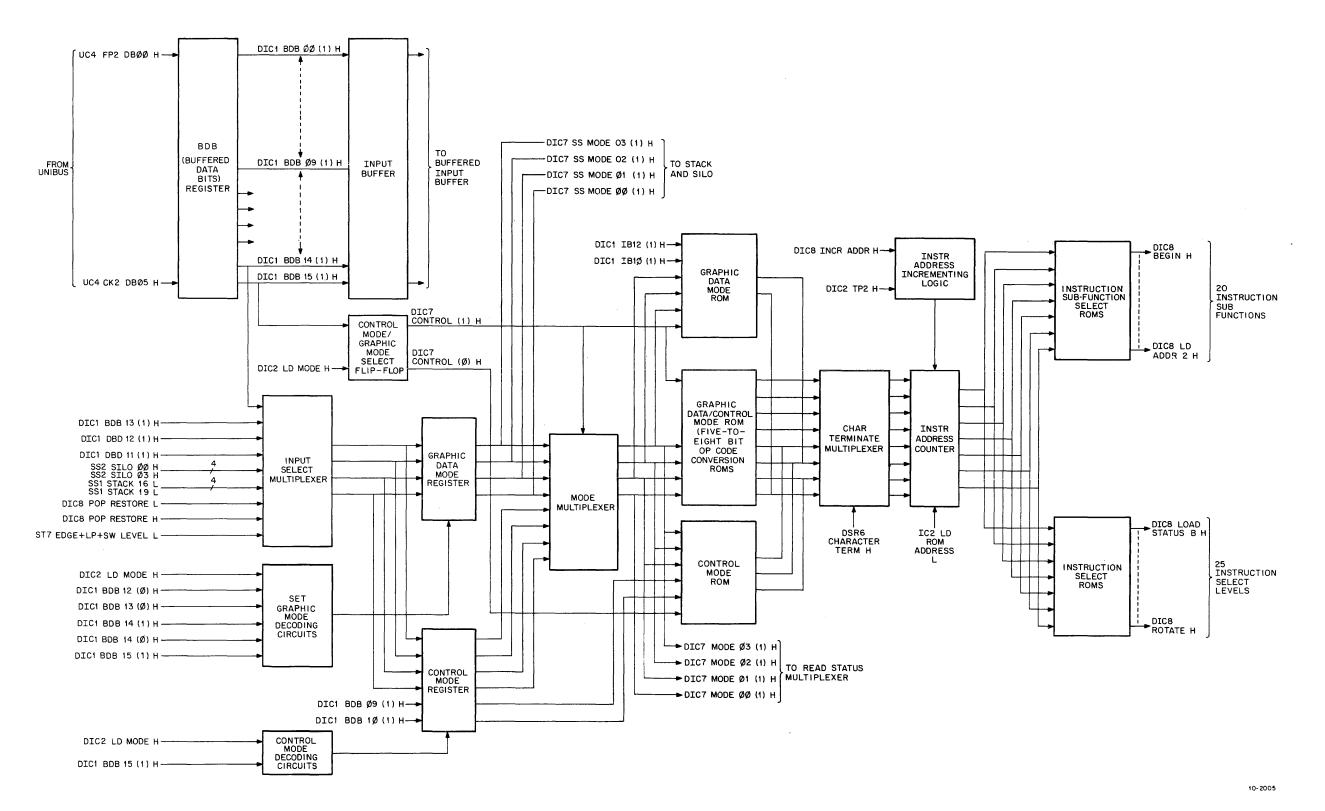

| 4.2.4.2       Set Graphic Mode Instruction Decoding       4-23         4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4.2.4     | Instruction Decoding Circuits, Block Diagram Discussion 4-18 |  |  |  |  |  |

| 4.2.4.3       Graphic Data Instruction Decoding       4-24         4.2.5       VT48 Status/Parameter Data Routing       4-25         4.2.5.1       Routing of Status/Parameter Data During                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4.2.4.1   | Control Instruction Decoding                                 |  |  |  |  |  |

| 4.2.5 VT48 Status/Parameter Data Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.4.2   | Set Graphic Mode Instruction Decoding                        |  |  |  |  |  |

| 4.2.5.1 Routing of Status/Parameter Data During Initial/Setup Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.4.3   | Graphic Data Instruction Decoding                            |  |  |  |  |  |

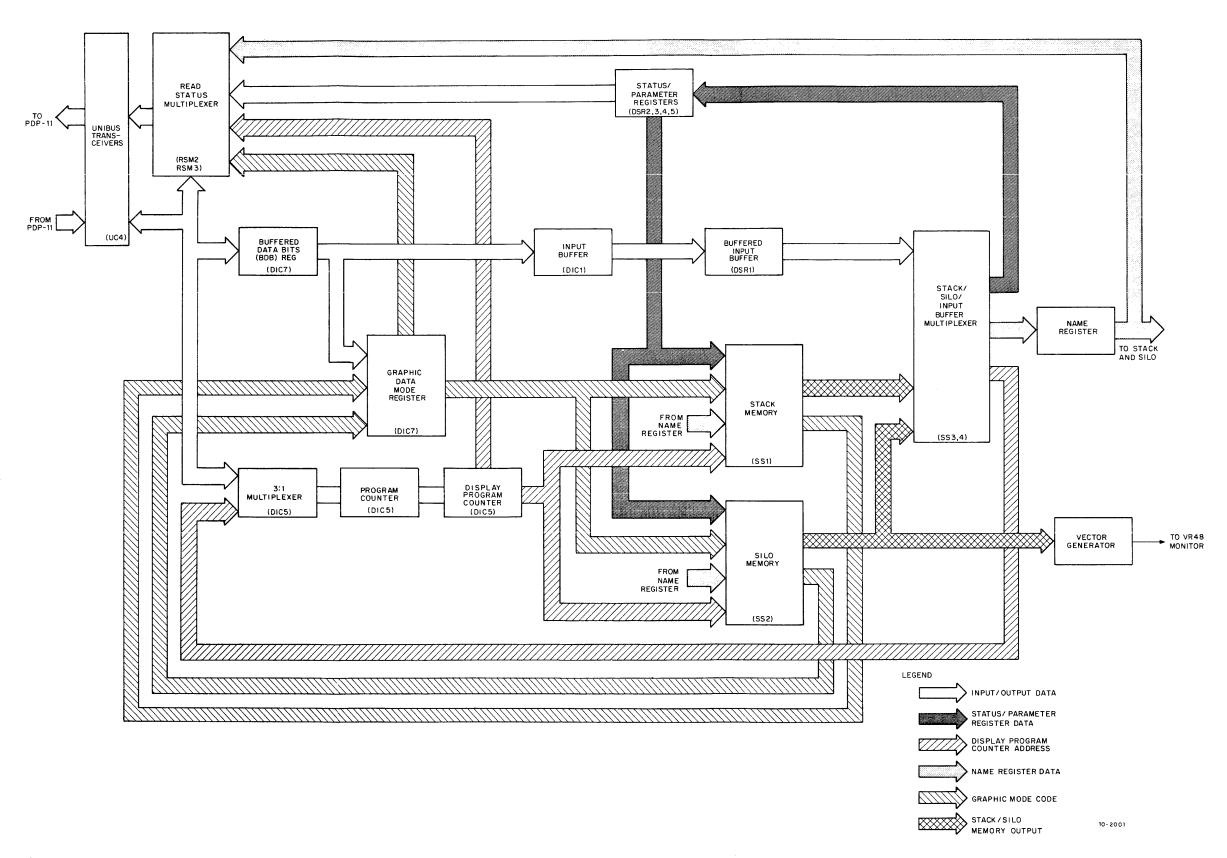

| Initial/Setup Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.5     | VT48 Status/Parameter Data Routing                           |  |  |  |  |  |

| 4.2.5.2 Routing of Status/Parameter Data on Generation of Display Surface Related Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4.2.5.1   | Routing of Status/Parameter Data During                      |  |  |  |  |  |

| 4.2.5.2 Routing of Status/Parameter Data on Generation of Display Surface Related Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | Initial/Setup Operations                                     |  |  |  |  |  |

| 4.2.5.3 Routing of Status/Parameter Data on Execution of JSR and POP Restore Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.2.5.2   | Routing of Status/Parameter Data on Generation of            |  |  |  |  |  |

| 4.2.5.3 Routing of Status/Parameter Data on Execution of JSR and POP Restore Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | Display Surface Related Interrupts                           |  |  |  |  |  |

| 4.2.6 Display Program Counter Input/Output Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.5.3   | Routing of Status/Parameter Data on Execution of             |  |  |  |  |  |

| 4.2.6 Display Program Counter Input/Output Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | JSR and POP Restore Instructions                             |  |  |  |  |  |

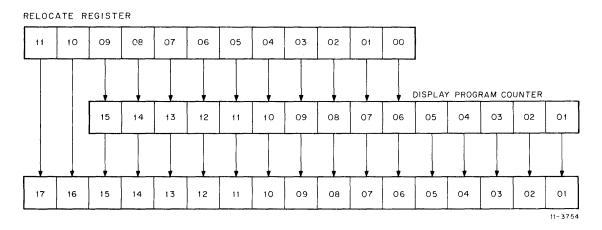

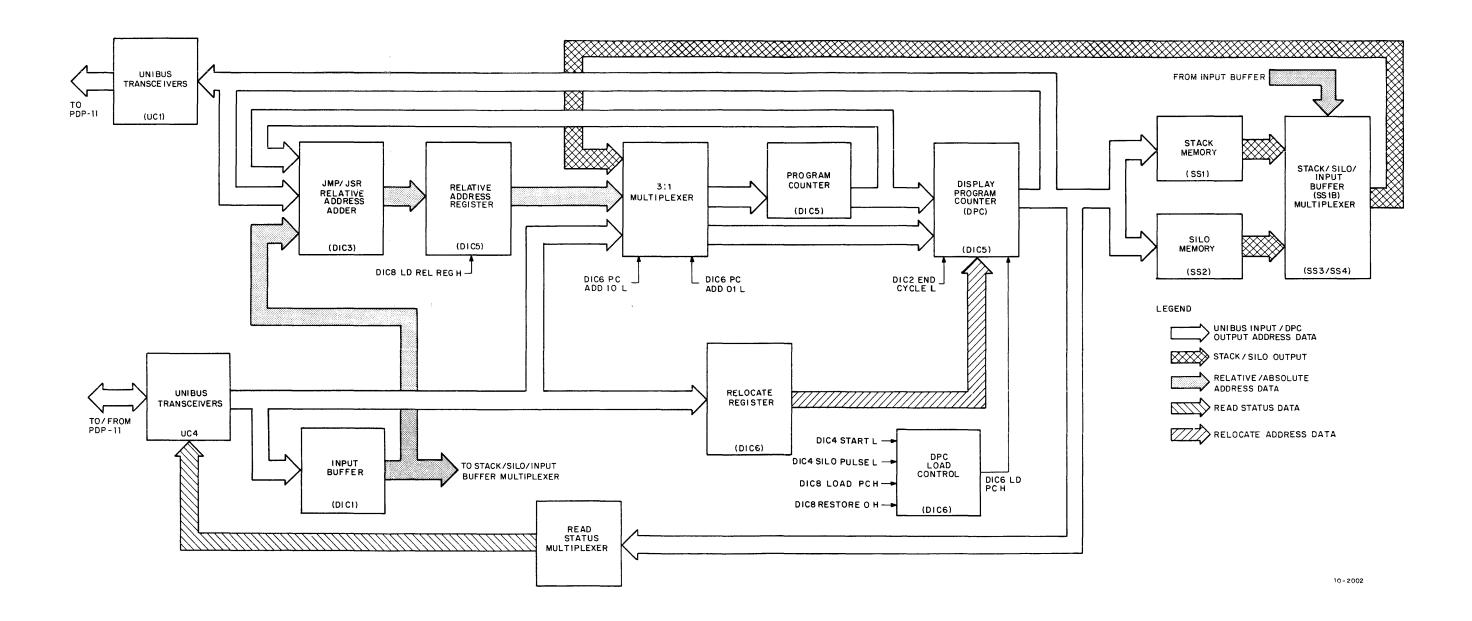

| 4.2.6.1Start DPC Address Routing4-294.2.6.2DPC Normal Update4-294.2.6.3Routing During Display Surface Related Interrupts4-294.2.6.4Routing During Execution of Jump Relative and<br>Jump to Subroutine Relative Instructions4-314.2.6.5Routing During Execution of Jump Absolute and<br>JSR Absolute Instructions4-314.2.6.6Routing on Execution of POP Restore Instructions4-324.2.6.7Routing on Loading of Relocate Register4-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.2.6     | Display Program Counter Input/Output Flow                    |  |  |  |  |  |

| 4.2.6.3 Routing During Display Surface Related Interrupts 4.2.6.4 Routing During Execution of Jump Relative and Jump to Subroutine Relative Instructions 4.2.6.5 Routing During Execution of Jump Absolute and JSR Absolute Instructions 4.2.6.6 Routing on Execution of POP Restore Instructions 4.2.6.7 Routing on Loading of Relocate Register 4.2.6.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.2.6.1   |                                                              |  |  |  |  |  |

| 4.2.6.3 Routing During Display Surface Related Interrupts 4.2.6.4 Routing During Execution of Jump Relative and Jump to Subroutine Relative Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.6.2   |                                                              |  |  |  |  |  |

| Jump to Subroutine Relative Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2.6.3   |                                                              |  |  |  |  |  |

| 4.2.6.5 Routing During Execution of Jump Absolute and JSR Absolute Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.6.4   | Routing During Execution of Jump Relative and                |  |  |  |  |  |

| JSR Absolute Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | Jump to Subroutine Relative Instructions                     |  |  |  |  |  |

| JSR Absolute Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4.2.6.5   | •                                                            |  |  |  |  |  |

| 4.2.6.6 Routing on Execution of POP Restore Instructions 4-32 4.2.6.7 Routing on Loading of Relocate Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | •                                                            |  |  |  |  |  |

| 4.2.6.7 Routing on Loading of Relocate Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.6.6   |                                                              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.6.7   |                                                              |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2.7     |                                                              |  |  |  |  |  |

|          |                                                             | Page |  |  |  |  |

|----------|-------------------------------------------------------------|------|--|--|--|--|

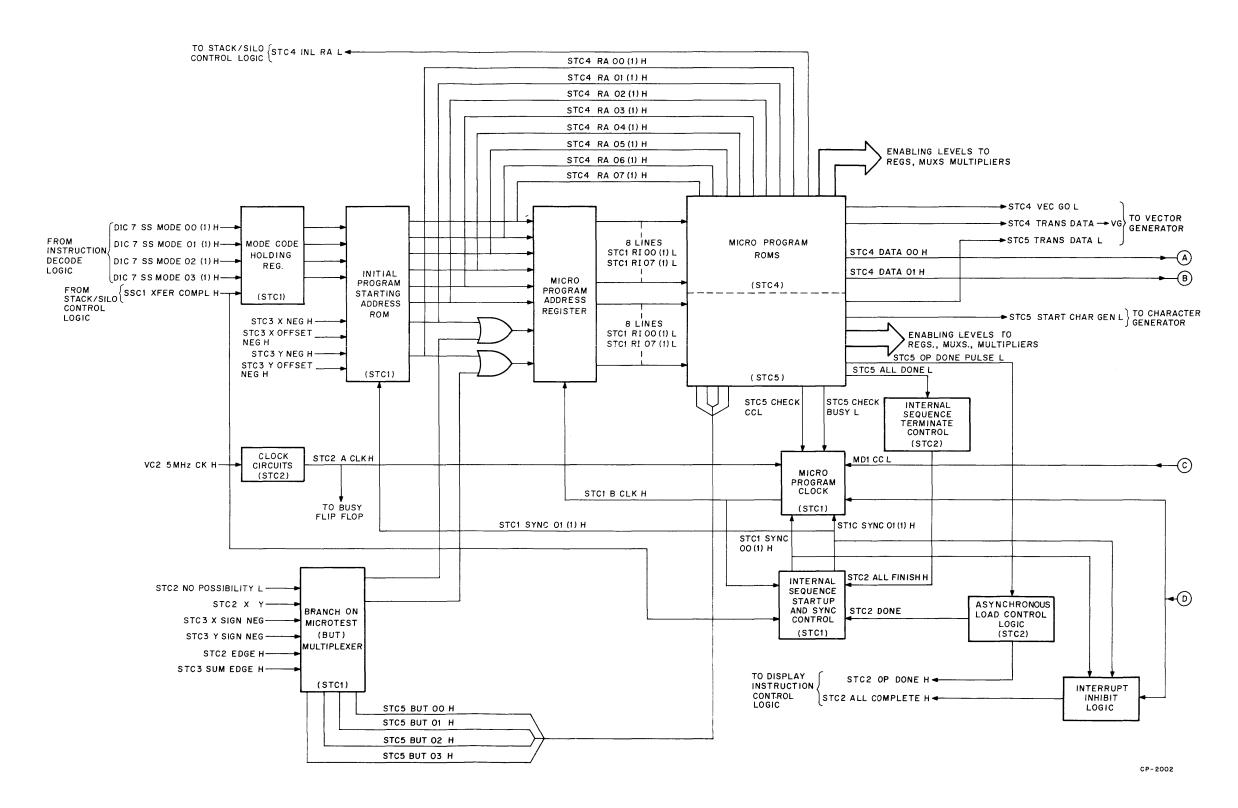

| 4.2.8    | Control Logic                                               | 4-32 |  |  |  |  |

| 4.2.8.1  | Microprogram Sequencing Startup                             |      |  |  |  |  |

| 4.2.8.2  | Internal Microprogram Sequencing and Branch-on              |      |  |  |  |  |

|          | Microtest Addressing                                        | 4-36 |  |  |  |  |

| 4.2.8.3  | Asynchronous Loading of the Next Graphic Entity             |      |  |  |  |  |

| 4.2.8.4  | Temporary Halts in Microprogram Sequencing                  |      |  |  |  |  |

| 4.2.8.5  | Microprogram Sequencing Shut Down                           |      |  |  |  |  |

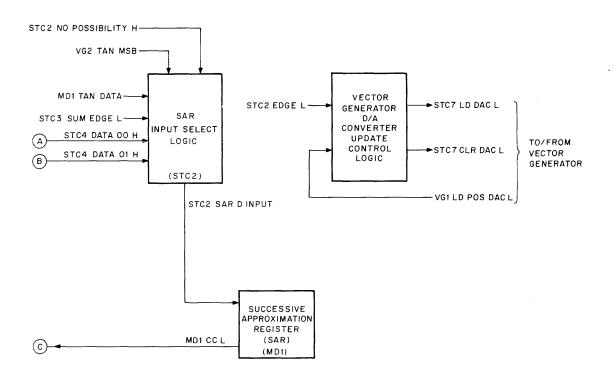

| 4.2.8.6  | Successive Approximation Register Input Control             |      |  |  |  |  |

| 4.2.8.7  | Vector Generator D/A Converter Update Control Logic         |      |  |  |  |  |

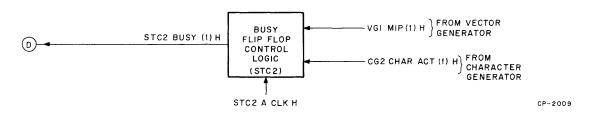

| 4.2.8.8  | Control Logic Asynchronous Interactive Control Signals      |      |  |  |  |  |

| 4.2.9    | Graphics Calculation Arithmetic Unit                        |      |  |  |  |  |

| 4.2.9.1  | Overview of Arithmetic Operations and Related Flow Drawings |      |  |  |  |  |

| 4.2.10   | Absolute Point Processing                                   |      |  |  |  |  |

| 4.2.10.1 | ON-to-ON Point Processing                                   |      |  |  |  |  |

| 4.2.10.2 | ON-to-OFF Point Processing                                  |      |  |  |  |  |

| 4.2.10.3 | OFF-to-ON Point Processing                                  |      |  |  |  |  |

| 4.2.10.4 | OFF-to-OFF Point Processing                                 |      |  |  |  |  |

| 4.2.11   | Relative Vector Processing                                  |      |  |  |  |  |

| 4.2.11.1 | ON-to-ON Vector Processing                                  |      |  |  |  |  |

| 4.2.11.2 | Tangent Calculation                                         | 4-58 |  |  |  |  |

| 4.2.11.3 | ON-to-ON Vector Processing Following Tangent Calculation    |      |  |  |  |  |

| 4.2.11.4 | ON-to-OFF Vector Processing                                 |      |  |  |  |  |

| 4.2.11.5 | ON-to-OFF (Scissored) Vector Tangent Calculation            | 4-66 |  |  |  |  |

| 4.2.11.6 | OFF-to-ON Vector Processing                                 |      |  |  |  |  |

| 4.2.11.7 | OFF-to-OFF Vector Processing                                | 4-69 |  |  |  |  |

| 4.2.12   | Absolute Vector Processing                                  | 4-73 |  |  |  |  |

| 4.2.12.1 | ON-to-ON Absolute Vector Processing                         | 4-73 |  |  |  |  |

| 4.2.12.2 | ON-to-OFF, OFF-to-ON, and OFF-to-OFF Absolute               |      |  |  |  |  |

|          | Vector Processing                                           | 4-73 |  |  |  |  |

| 4.2.13   | Relative Point/Graphplot Processing                         | 4-75 |  |  |  |  |

| 4.2.14   | Character Processing                                        | 4-75 |  |  |  |  |

| 4.2.14.1 | Processing Drawable Characters                              |      |  |  |  |  |

| 4.2.14.2 | Processing Control Characters Other than Carriage Return    | 4-77 |  |  |  |  |

| 4.2.14.3 | Carriage Return Processing                                  | 4-77 |  |  |  |  |

| 4.2.15   | Light Pen Hit Processing                                    | 4-78 |  |  |  |  |

| 4.2.15.1 | Processing Objectives                                       | 4-78 |  |  |  |  |

| 4.2.15.2 | ROM Starting Address Setup                                  | 4-78 |  |  |  |  |

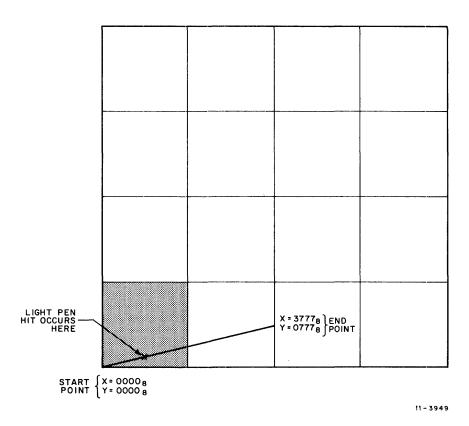

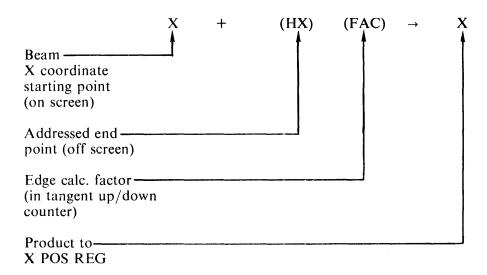

| 4.2.15.3 | Example of Light Pen Hit Calculations                       | 4-79 |  |  |  |  |

| 4.2.15.4 | Light Pen Hit Flow Sequence                                 | 4-81 |  |  |  |  |

| 4.2.16   | Edge Interrupt Processing                                   |      |  |  |  |  |

| 4.2.16.1 | Edge Interrupt Processing for ON-to-OFF Screen Vectors      | 4-86 |  |  |  |  |

| 4.2.16.2 | Edge Interrupt Processing for OFF-to-ON and                 |      |  |  |  |  |

|          | OFF-to-OFF Vectors                                          | 4-87 |  |  |  |  |

|           |                                                                | Page   |  |  |  |  |

|-----------|----------------------------------------------------------------|--------|--|--|--|--|

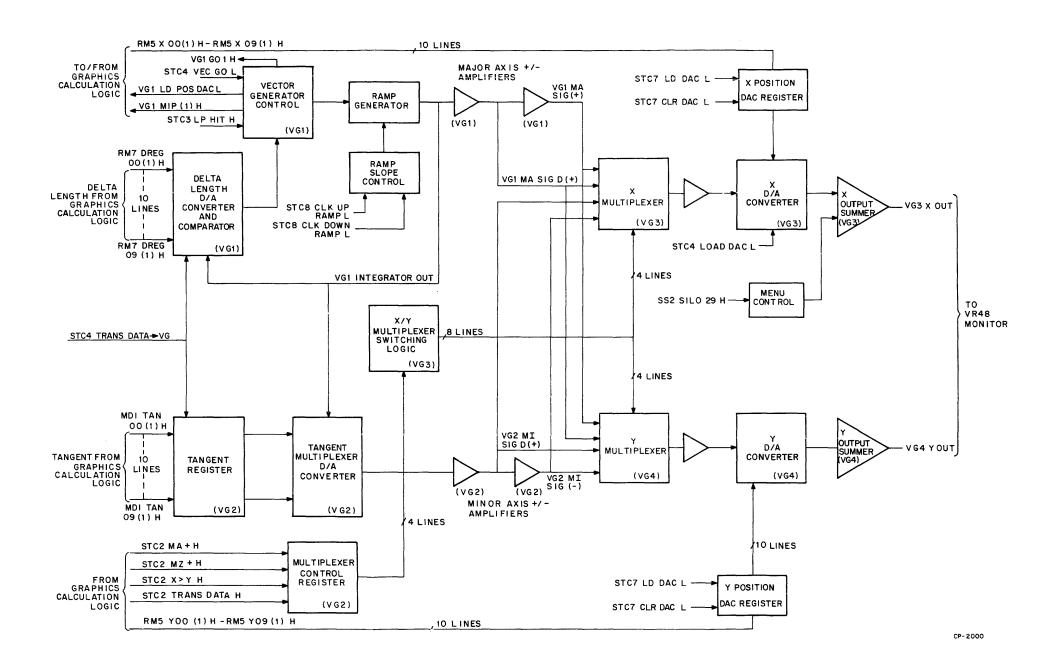

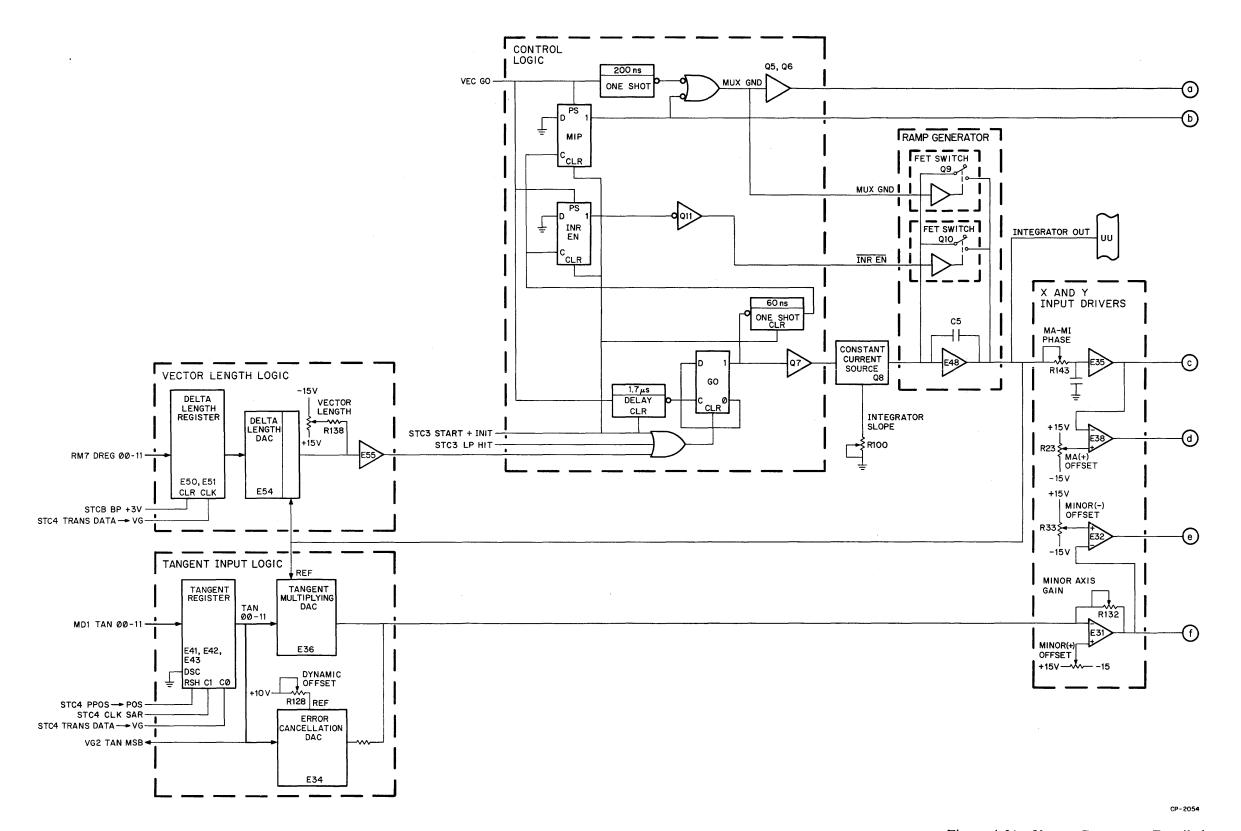

| 4.2.17    | Vector Generator Simplified Block Diagram Discussion           | . 4-87 |  |  |  |  |

| 4.2.17.1  | Ramp Generation                                                |        |  |  |  |  |

| 4.2.17.2  | Ramp Slope Control                                             |        |  |  |  |  |

| 4.2.17.3  | Tangent Register and Multiplying D/A Converter Circuit         |        |  |  |  |  |

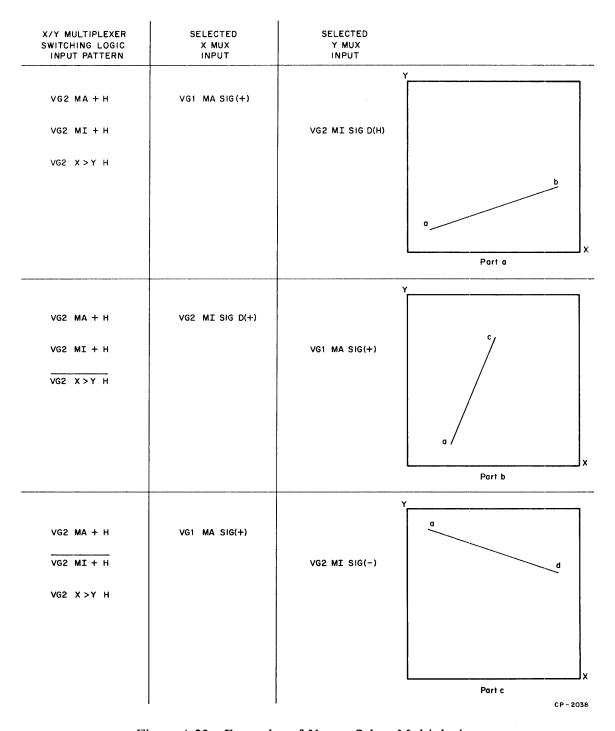

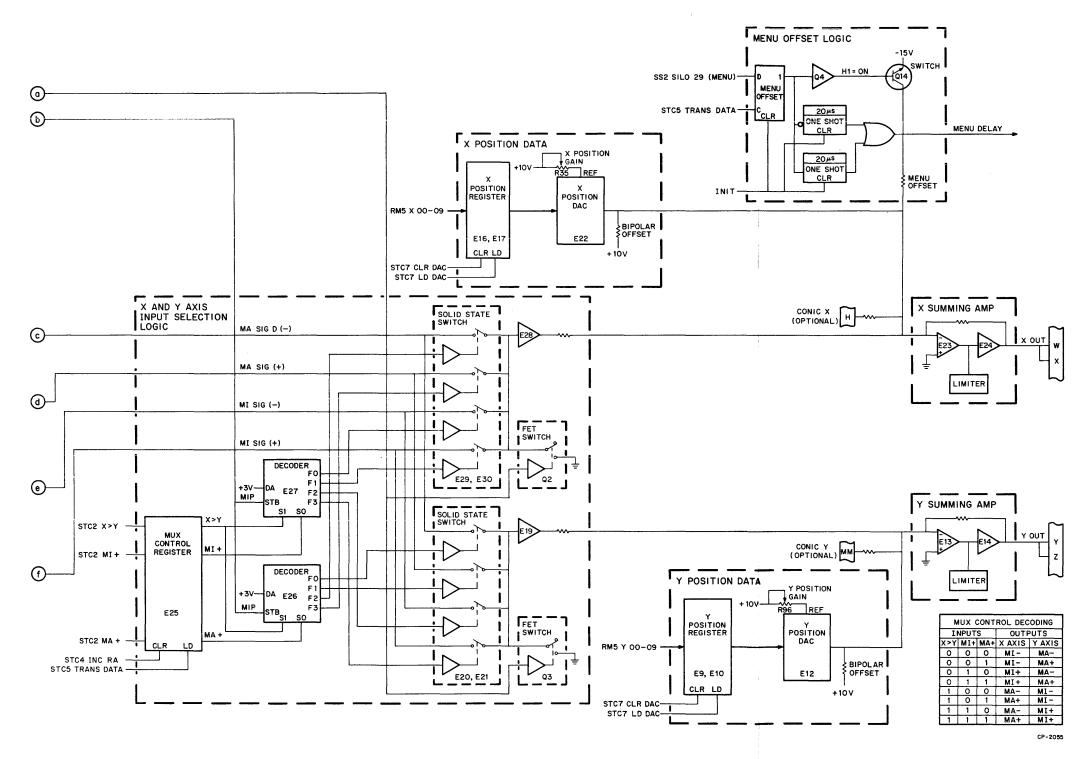

| 4.2.17.4  | Multiplexer Control Register and X/Y Multiplexer               |        |  |  |  |  |

|           | Switching Logic                                                | . 4-90 |  |  |  |  |

| 4.2.17.5  | X/Y Position DAC Registers and X/Y D/A Converters              |        |  |  |  |  |

| 4.2.17.6  | Menu Area Selection                                            |        |  |  |  |  |

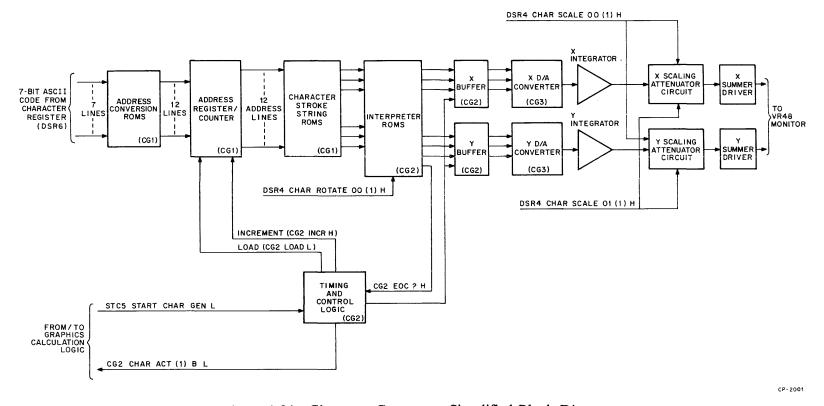

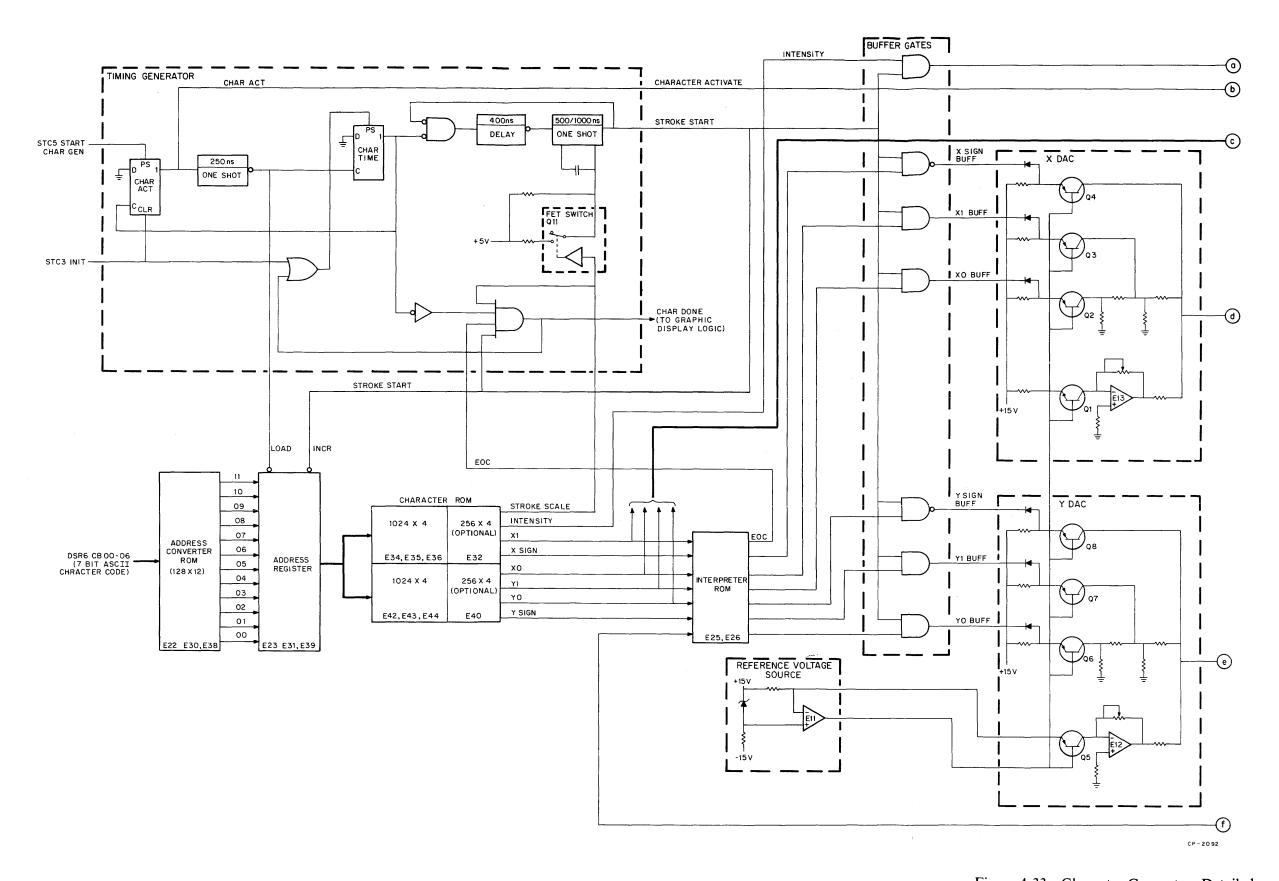

| 4.2.18    | Character Generator Simplified Block Diagram Discussion        |        |  |  |  |  |

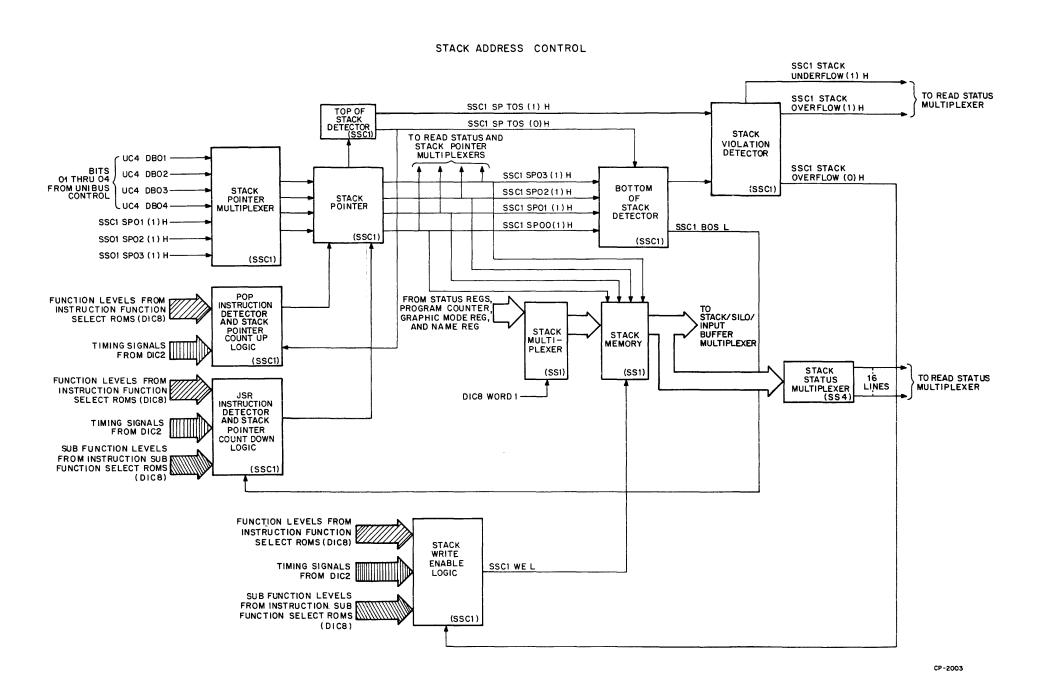

| 4.2.19    | Stack/Silo Addressing and Control Logic                        |        |  |  |  |  |

| 4.2.19.1  | Stack Memory Control Logic                                     |        |  |  |  |  |

| 4.2.19.2  | Stack Memory Addressing from the Unibus                        |        |  |  |  |  |

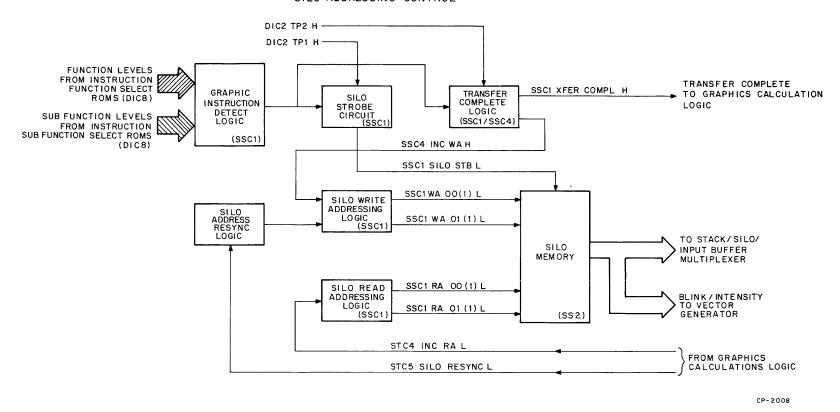

| 4.2.19.3  | Silo Addressing Control Logic                                  |        |  |  |  |  |

| 4.2.20    | Read Status Multiplexer                                        |        |  |  |  |  |

| 4.2.21    | Unibus Transfer Timing                                         |        |  |  |  |  |

| 4.2.22    | Control Instruction Flow Diagrams                              |        |  |  |  |  |

| 4.2.23    | Vector Generation Circuits, Detailed Block Diagram Description |        |  |  |  |  |

| 4.2.23.1  | Types of Input Signals                                         |        |  |  |  |  |

| 4.2.23.2  | X and Y Initial Position Determination                         |        |  |  |  |  |

| 4.2.23.3  | Vector Determination                                           |        |  |  |  |  |

| 4.2.23.4  | Major and Minor Axis Outputs                                   |        |  |  |  |  |

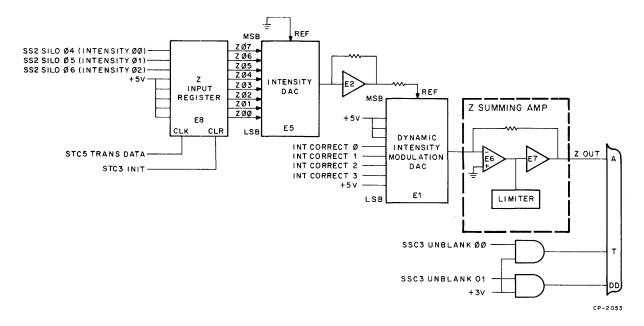

| 4.2.23.5  | Z Axis (Intensity) Circuits                                    |        |  |  |  |  |

| 4.2.23.6  | Voltage Regulators                                             |        |  |  |  |  |

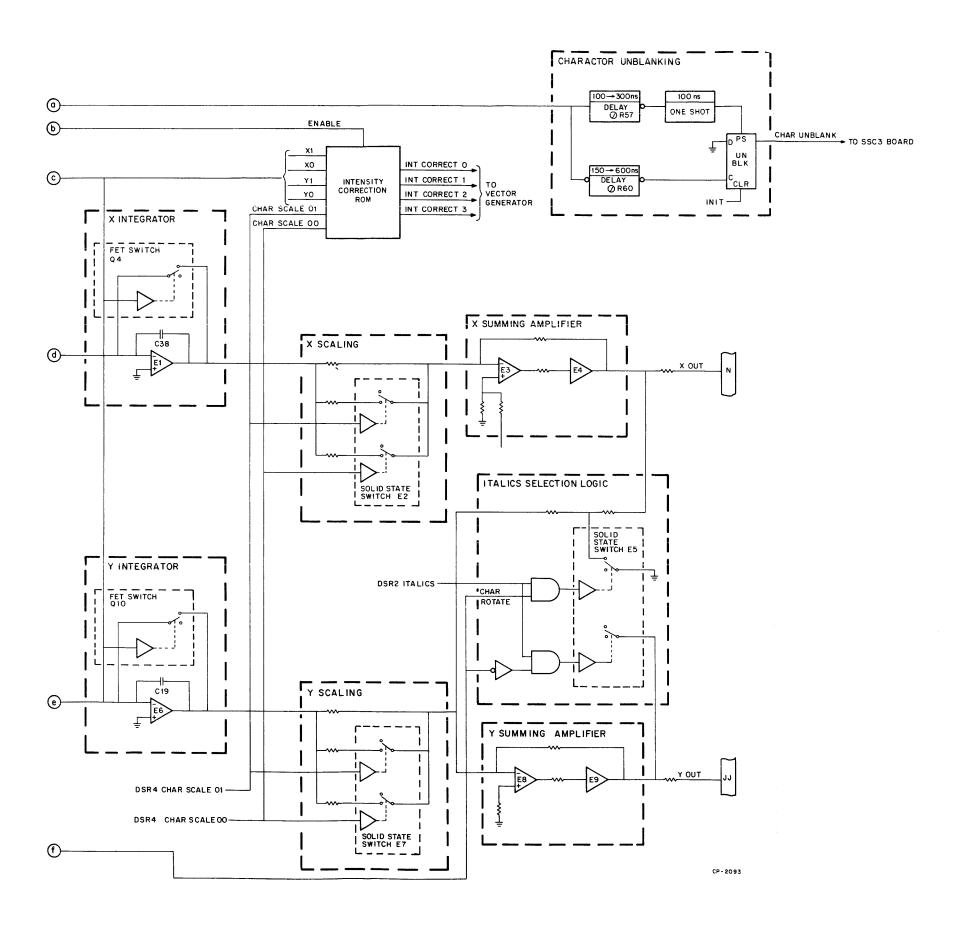

| 4.2.24    | Character Generator Detailed Block Diagram Discussion          |        |  |  |  |  |

| 4.2.24.1  | Character Generator Startup                                    |        |  |  |  |  |

| 4.2.24.2  | Character ROM Outputs                                          |        |  |  |  |  |

| 4.2.24.3  | Interpreter ROM                                                |        |  |  |  |  |

| 4.2.24.4  | D/A Converters                                                 |        |  |  |  |  |

| 4.2.24.5  | X/Y Integrators                                                |        |  |  |  |  |

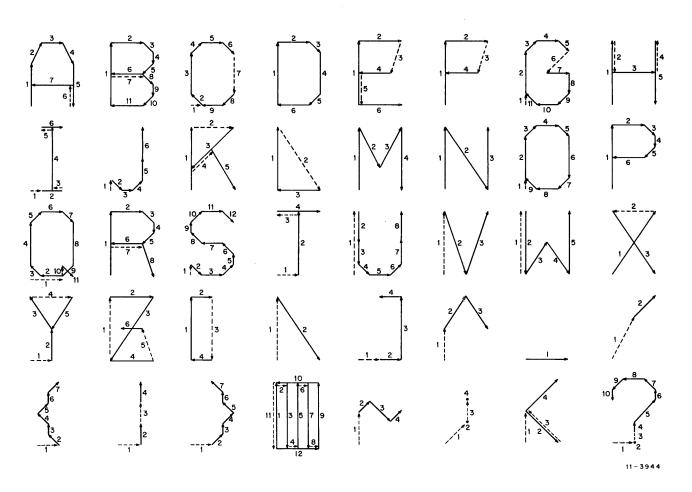

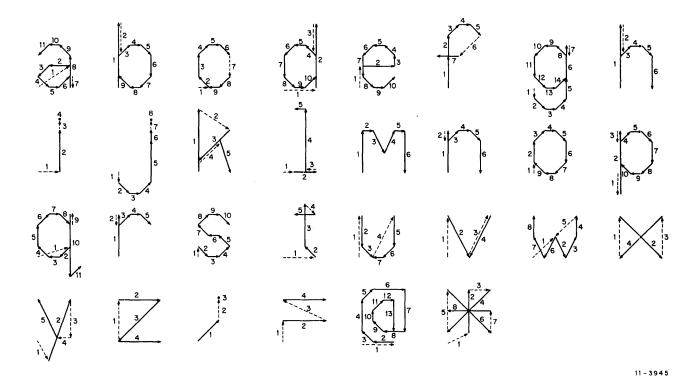

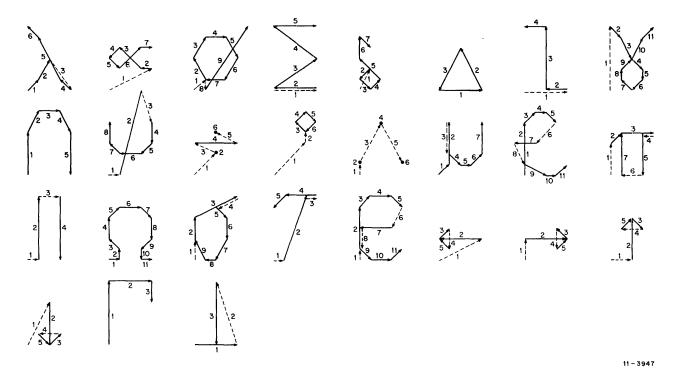

| 4.2.24.6  | Examples of Character Strokes                                  |        |  |  |  |  |

| 4.2.24.7  | Scaling Circuits and Drivers                                   |        |  |  |  |  |

|           |                                                                |        |  |  |  |  |

| CHAPTER 5 | VT48 DISPLAY PROCESSOR UNIT DIAGNOSTICS, PREVENTIVE            |        |  |  |  |  |

|           | MAINTENANCE, AND ALIGNMENT PROCEDURES                          |        |  |  |  |  |

| 5.1       | INTRODUCTION                                                   | . 5-1  |  |  |  |  |

| 5.2       | DIAGNOSTIC MAINTENANCE PROGRAMS                                |        |  |  |  |  |

| 5.2.1     | Instruction Test Diagnostics Load and Run Procedures           |        |  |  |  |  |

| 5.2.1.1   | Instruction Test Part I (11-DZVSA)                             |        |  |  |  |  |

| 5.2.1.2   | Instruction Test Part II (11-DZVSB)                            |        |  |  |  |  |

| 5.2.1.3   | Instruction Test Part III (11-DZVSC)                           |        |  |  |  |  |

| 5.2.2     | Visual Test Diagnostic Load and Run Procedure                  |        |  |  |  |  |

| 5.3       | MAINTENANCE SWITCH PURPOSES                                    |        |  |  |  |  |

| 5.4       | PREVENTIVE MAINTENANCE                                         |        |  |  |  |  |

| 5.4.1     | Mechanical Checks                                              |        |  |  |  |  |

| 5.4.2     | VT48 Alignment Procedures                                      |        |  |  |  |  |

Page

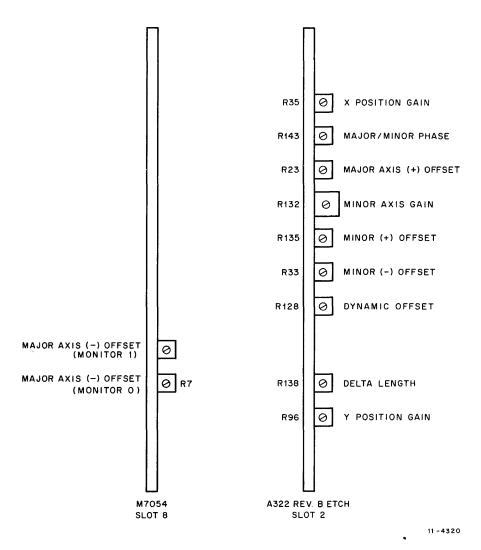

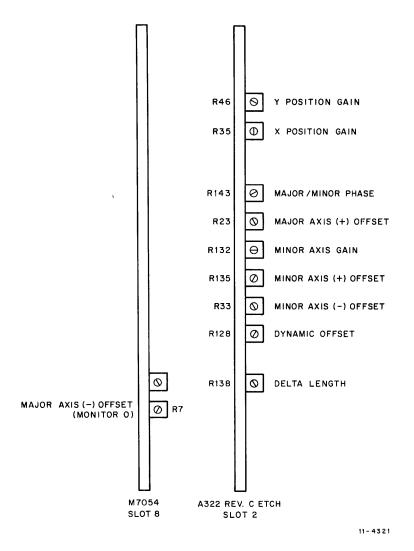

| Vector Generator (A322) Adjustments                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |