PDP-15 Systems

# Module Manual

## PDP-15 MODULE MANUAL

1st Edition July 1970 2nd Printing November 1970 3rd Printing (Rev) November 1972

Copyright © 1970, 1972 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

COMPUTER LAB

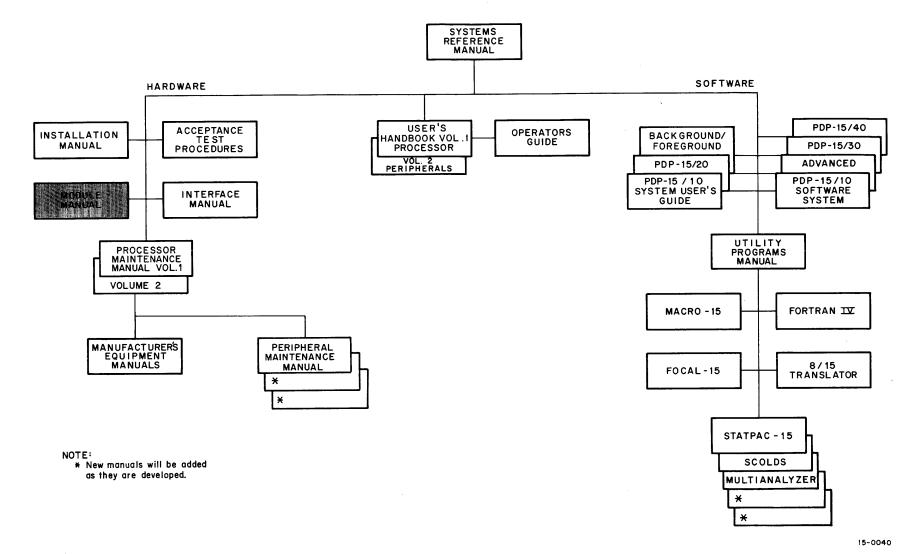

### PDP-15 FAMILY OF MANUALS

**SYSTEMS REFERENCE MANUAL** — Provides overview of PDP-15 hardware and software systems and options, instruction repertoire, expansion features, and descriptions of system peripherals. (DEC-15-BRZD)

USER'S HANDBOOK VOLUME 1, PROCESSOR — Principal guide to system hardware includes system and subsystem features, functional descriptions, machine-language programming considerations, instruction repertoire, and system expansion data. (DEC-15-H2DC-D)

**VOLUME 2, PERIPHERALS** – Features functional descriptions and programming considerations of peripheral devices. (DEC-15-H2DC-D)

**OPERATOR'S GUIDE** – Lists procedural data, including operator maintenance, for using the operator's console and the peripheral devices associated with PDP-15 Systems. (DEC-15-H2CB-D)

PDP-15/10 SYSTEM USER'S GUIDE – Features COMPACT and Basic I/O Monitor operating procedures. (DEC-15-GG1A-D)

PDP-15/20 SYSTEM USER'S GUIDE – Lists Advanced Monitor System operating procedures. (DEC-15-MG2B-D)

BACKGROUND/FOREGROUND MONITOR SYSTEM USER'S GUIDE — Lists operating procedures for the DECtape and disk-oriented Background/Foreground monitors. (DEC-15-MG3A-D)

PDP-15/10 SOFTWARE SYSTEM — Describes COM-PACT software system and Basic I/O Monitor System. (DEC-15-GR1A-D)

PDP-15/20/30/40 ADVANCED MONITOR SOFT-WARE SYSTEM — Describes Advanced Monitor System; programs include system monitor language, utility, and application types; operation, core organization, and input/output operations within the monitor environment are discussed. (DEC-15-MR2B-D)

PDP-15/30 BACKGROUND/FOREGROUND MONITOR SOFTWARE SYSTEM — Describes Background/Foreground Software System including the associated language, utility, and applications program. (DEC-15-MR3A-D)

### PDP-15/40 DISK-ORIENTED BACKGROUND/ FOREGROUND MONITOR SOFTWARE SYSTEM

- Describes Background/Foreground Monitor in disk-oriented environment; programs include language, utility, and application types. (DEC-15-MR4A-D)

MAINTENANCE MANUAL VOLUME 1, PROCES-SOR — Provides block diagram and functional theory of operation of the processor logic; lists preventive and corrective maintenance data, (DEC-15-H2BB-D)

**VOLUME 2, ENGINEERING DRAWINGS** – Provides engineering drawings and signal glossary for the basic processor and options. (DEC-15-H2BB-D)

**INSTALLATION MANUAL** — Provides power specifications, environmental considerations, cabling, and other information pertinent to installing PDP-15 Systems. (DEC-15-H2AB-D)

ACCEPTANCE TEST PROCEDURES – Lists stepby-step procedures designed to insure optimum PDP-15 Systems operation.

PDP-15 MODULE MANUAL — Provides characteristics, specifications, timing and functional descriptions of modules used in PDP-15 Systems. (DEC-15-H2EB-D)

INTERFACE MANUAL - Provides information for interfacing devices to a PDP-15 System. (DEC-15-H0AC-D)

UTILITY PROGRAMS MANUAL — Provides utility programs common to PDP-15 Monitor Systems. (DEC-15-YWZA-D)

**MACRO-15** – Provides MACRO assembly language for the PDP-15. (DEC-15-AMZA-D)

**FORTRAN IV** – Describes PDP-15 version of the FORTRAN IV compiler language. (DEC-15-KFZB-D)

FOCAL-15 — Describes an algebraic interactive compiler level language developed by Digital Equipment Corporation. (DEC-15-KJZB-D)

### List of Modules

| A124 | Analog Multiplexer                    |

|------|---------------------------------------|

| A222 | Selectable Gain Amplifier             |

| A405 | Sample and Hold Amplifier             |

| A607 | 10-Bit D/A Converter, Single Buffered |

| A708 | Dual Voltage Regulator                |

| A877 | Analog-to-Digital Converter           |

| G085 | Disk Read Amplifier                   |

| G100 | Sense Amplifier and Inhibit Driver    |

| G222 | Memory Selector                       |

| G223 | Read/Write Driver                     |

| G285 | Series Switch                         |

| G286 | Center Tap Selector                   |

| G290 | Writer Flip-Flop                      |

| G613 | X Diode Matrix                        |

| G614 | Y Diode Matrix                        |

| G681 | Track Matrix                          |

| G711 | Terminator Board                      |

| G775 | Indicator Panel                       |

| G821 | +5V Regulator                         |

| G822 | -6V Regulator                         |

| G823 | -24V Regulator                        |

| G825 | -24V Pass Element                     |

| G827 | Power Sequence Detector and Delays    |

| G829 | Power Connector                       |

| G858 | Teletype <sup>®</sup> Connector       |

| K303 | Timer                                 |

| M002 | Logic 1 Source                        |

| M101 | Bus Data Interface                    |

| M103 | Device Selector                       |

| M104 | I/O Bus Multiplexer                   |

| M111 | Inverters                             |

| M112 | NOR Gates                             |

| M113 | NAND Gates                            |

| M115 | NAND Gates                            |

| M117 | NAND Gates                            |

| M119 | NAND Gates                            |

| M121 | AND/NOR Gates                         |

| M127 | AND/NOR Gates                         |

| M129 | AND/NOR Gates                         |

| M133 | NAND Gates                            |

| M135 | NAND Gates                            |

| M139 | NAND Gates                            |

| M149 | NAND-Wired OR Matrix                  |

| M159 | 4-Bit Arithmetic Logic Unit           |

| M161 | Binary-to-Octal/Decimal Decoder       |

| M162 | Parity Circuit                        |

| M164 | 6-Bit Parallel Adder                  |

| M182 | Parity Circuit                        |

| M191 | Carry Look-Ahead Generator            |

|      |                                       |

<sup>&</sup>lt;sup>®</sup>Teletype is a registered trademark of Teletype Corporation.

### List of Modules (Cont)

|              | D. FIL. DI                         |

|--------------|------------------------------------|

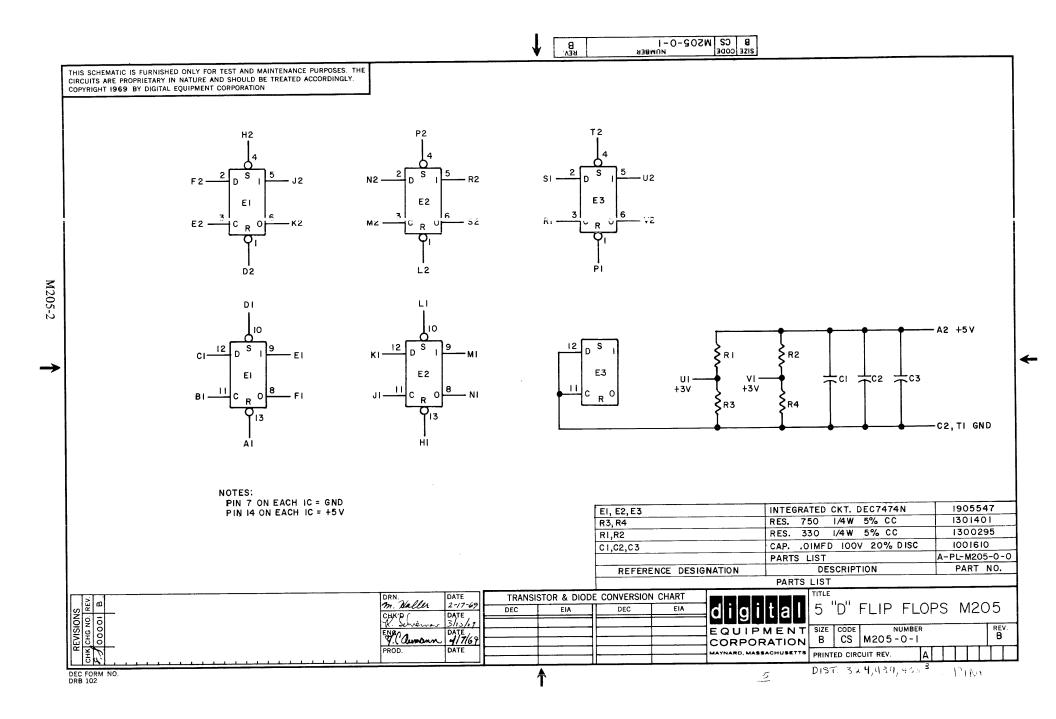

| M205         | D Flip-Flops                       |

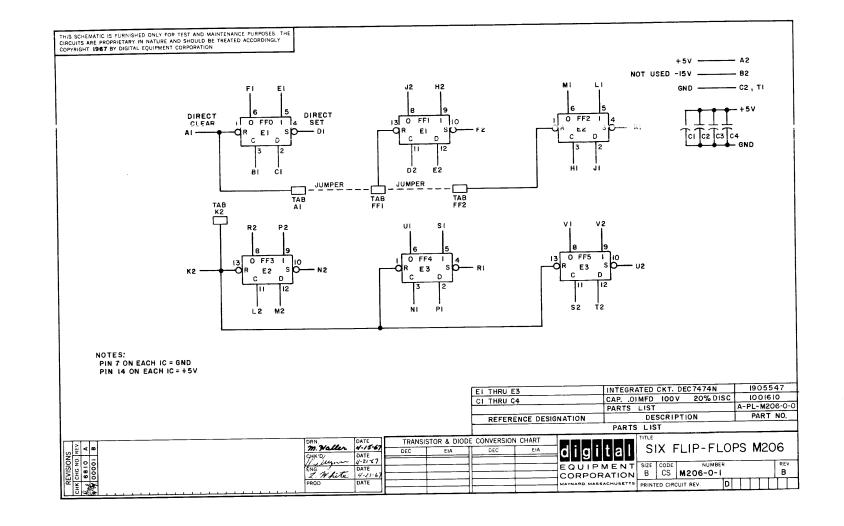

| M206         | D Flip-Flops                       |

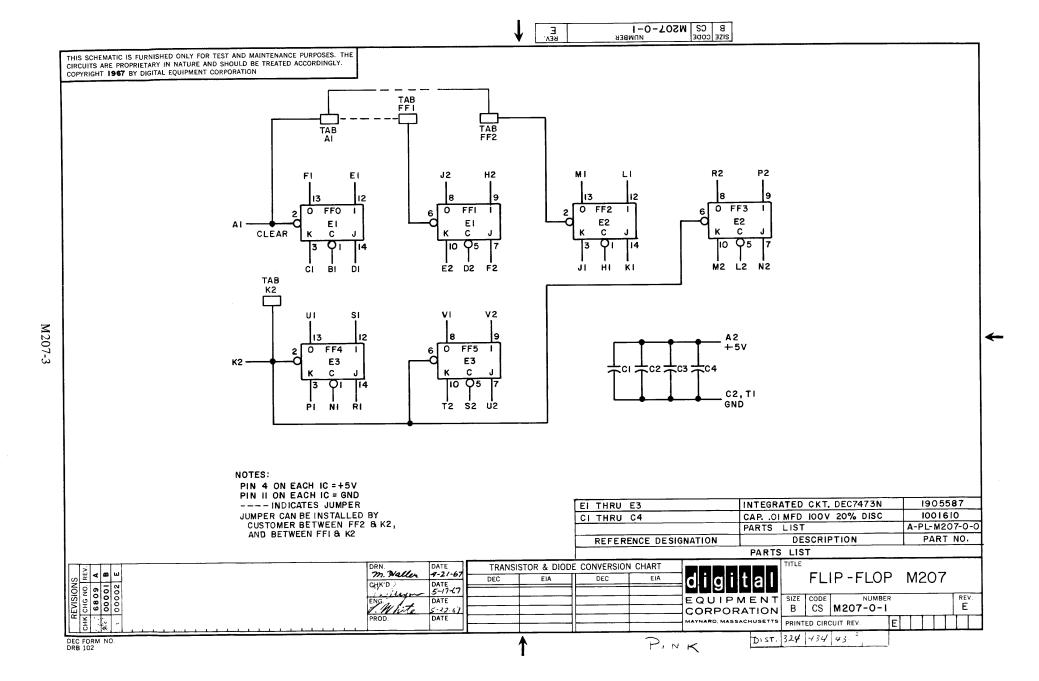

| M20''        | Flip-Flop                          |

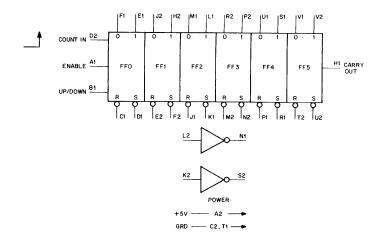

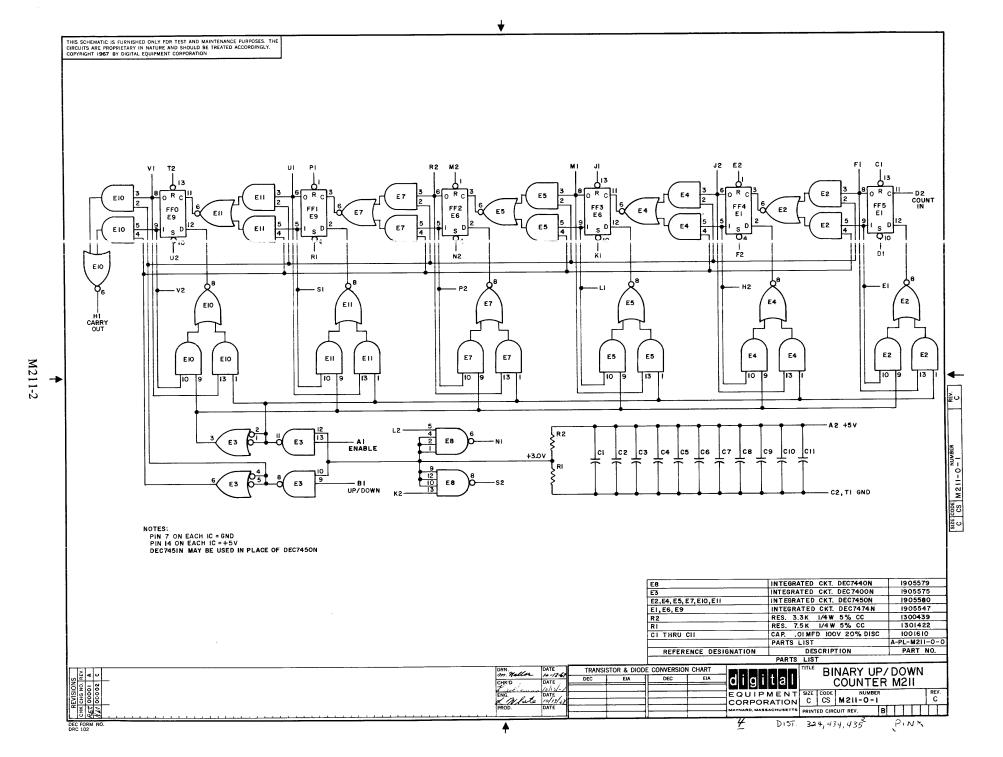

| M21          | Binary Up/Down Counter             |

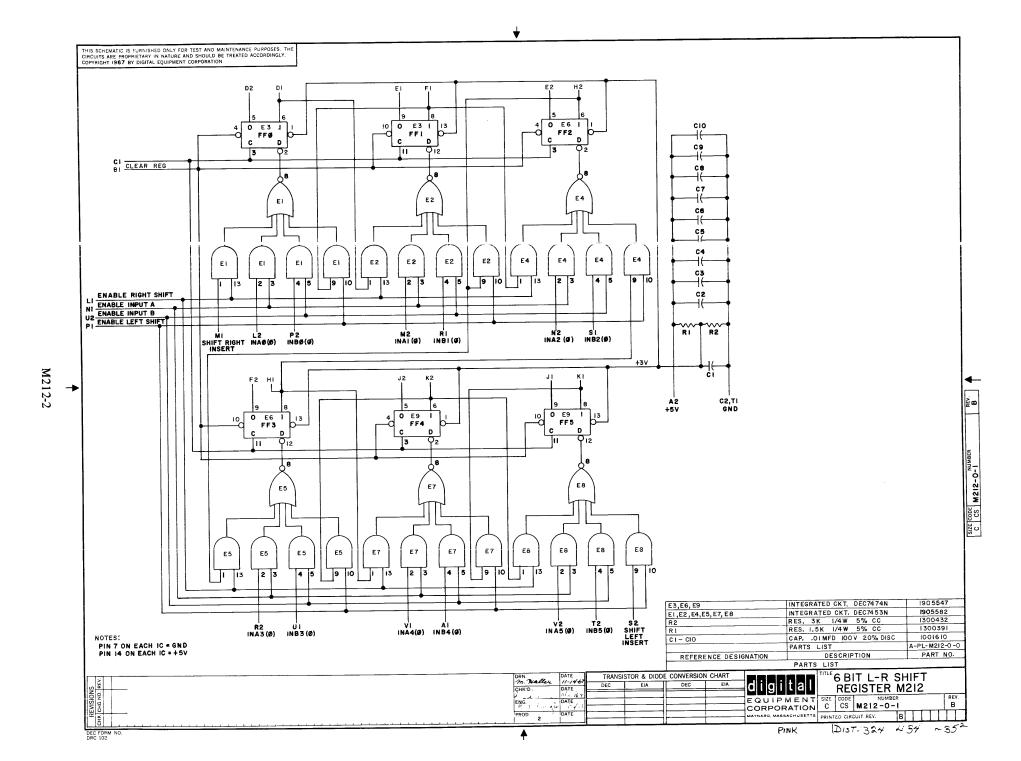

| M212         | 6-Bit Left/Right Shift Register    |

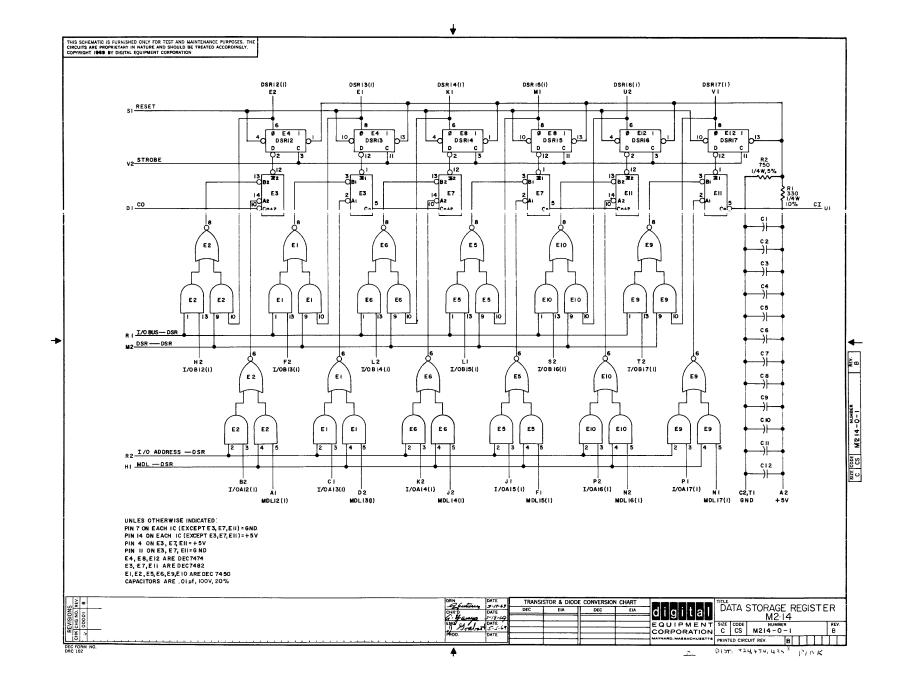

| M214         | Data Storage Register (6-Bit)      |

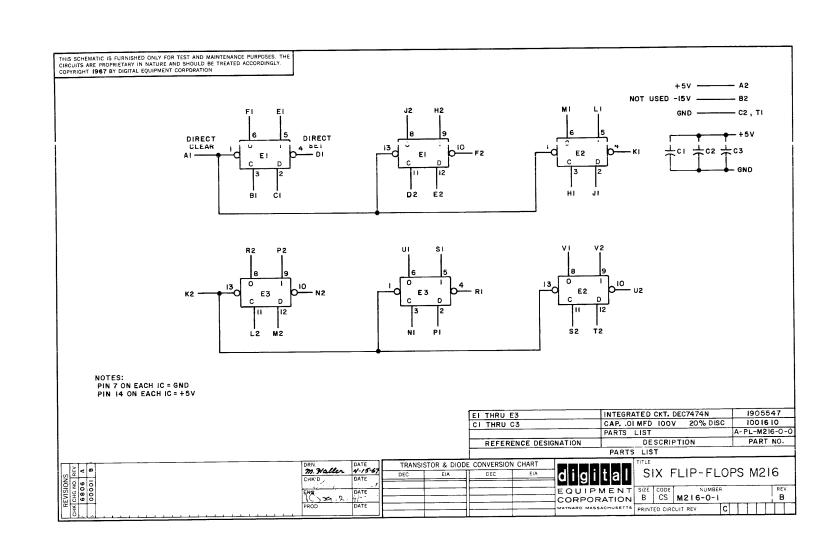

| M216         | D Flip-Flops                       |

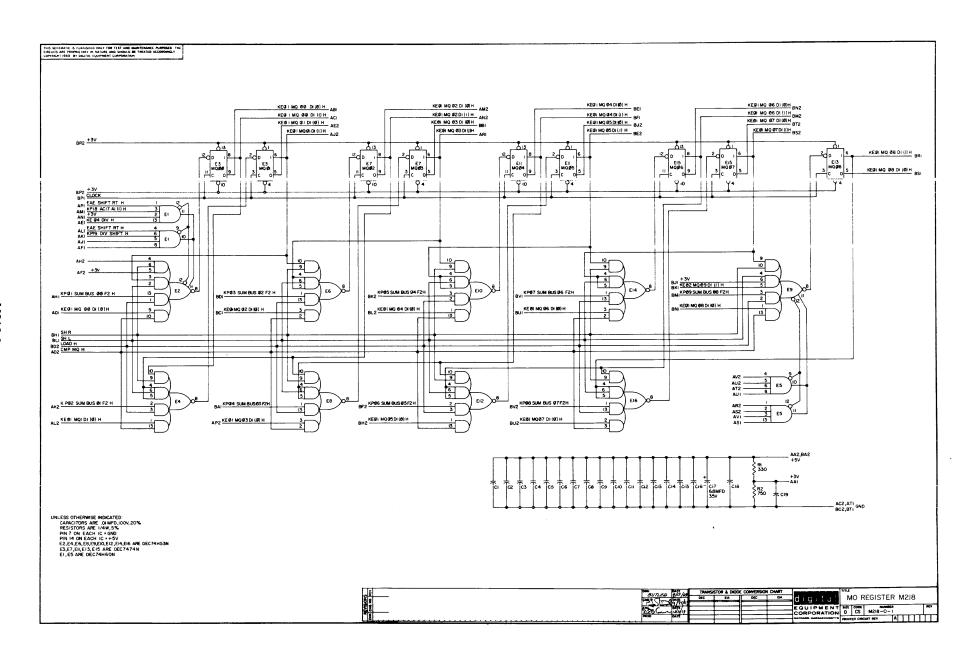

| M213         | MQ Register (9-Bit)                |

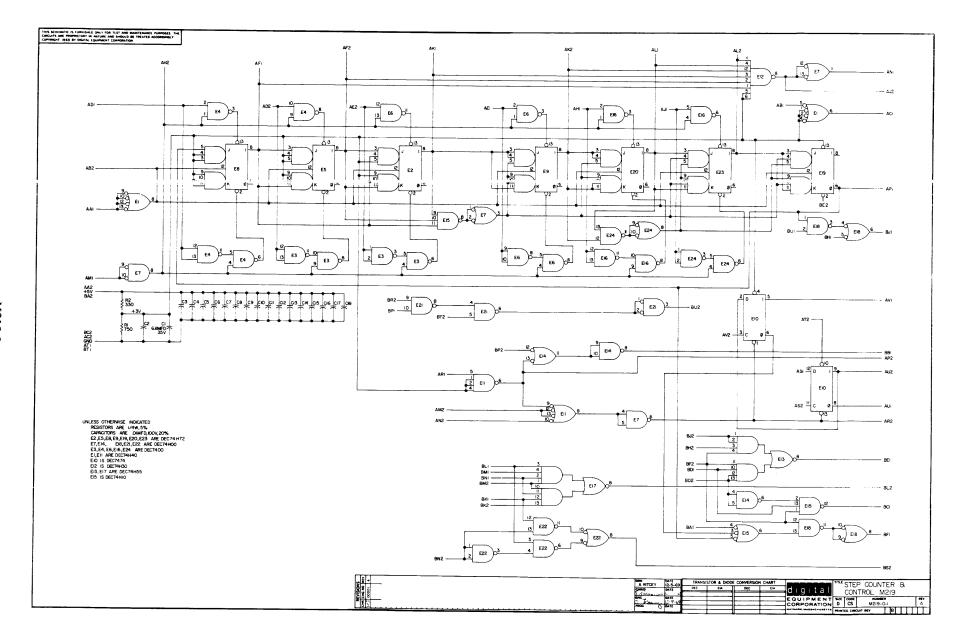

| M219         | Step Counter and Control           |

| M223         | MA and MB Register (4-Bit)         |

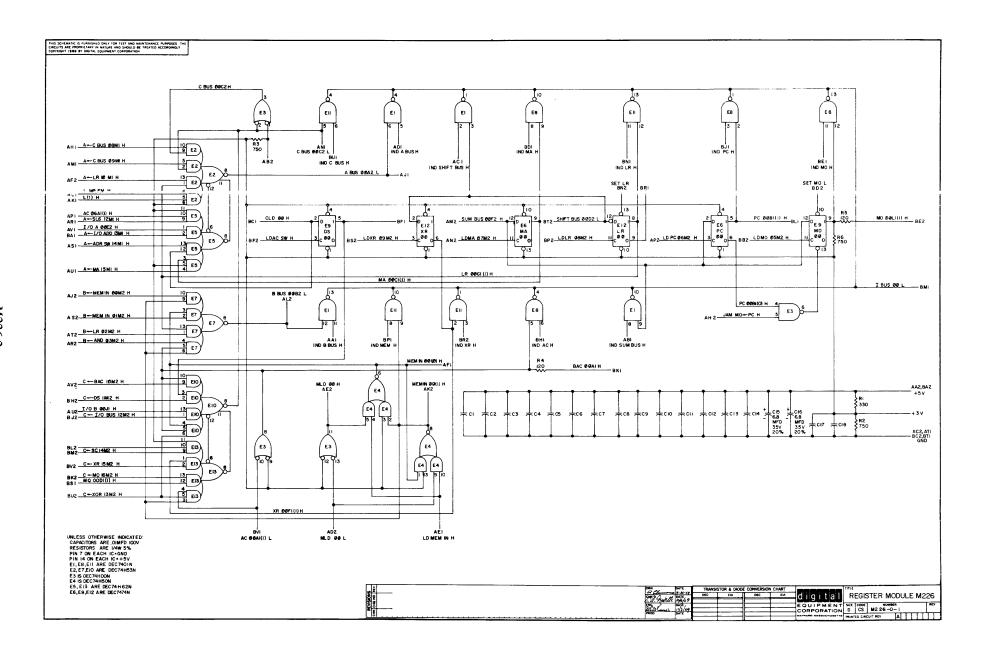

| M226         | Register (7-Bit)                   |

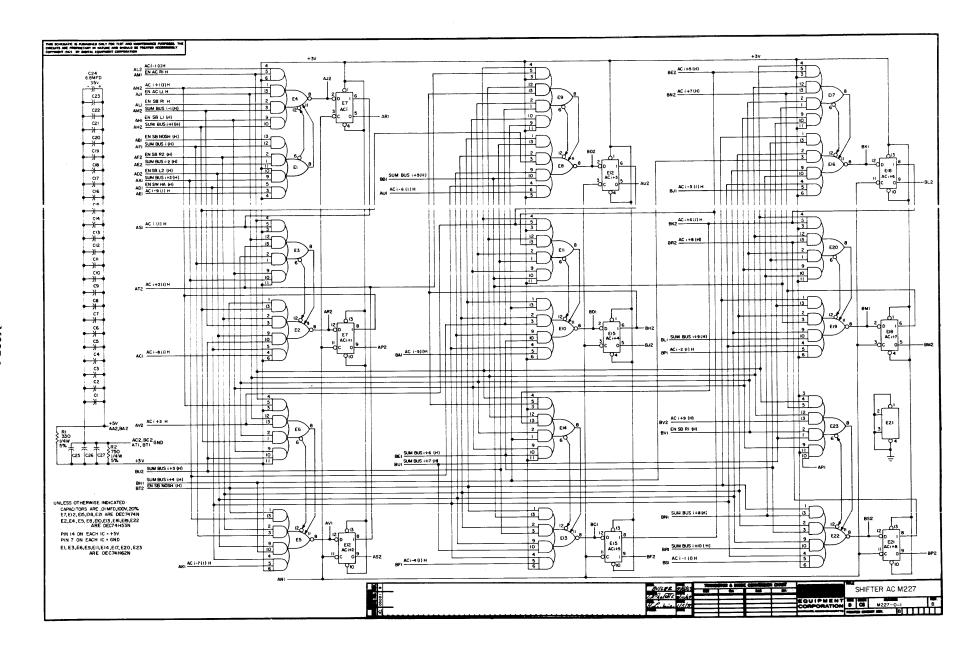

| M227         | AC Shifter (9-Bit)                 |

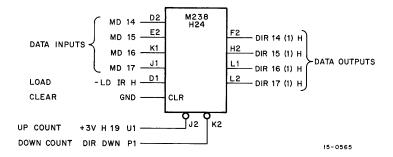

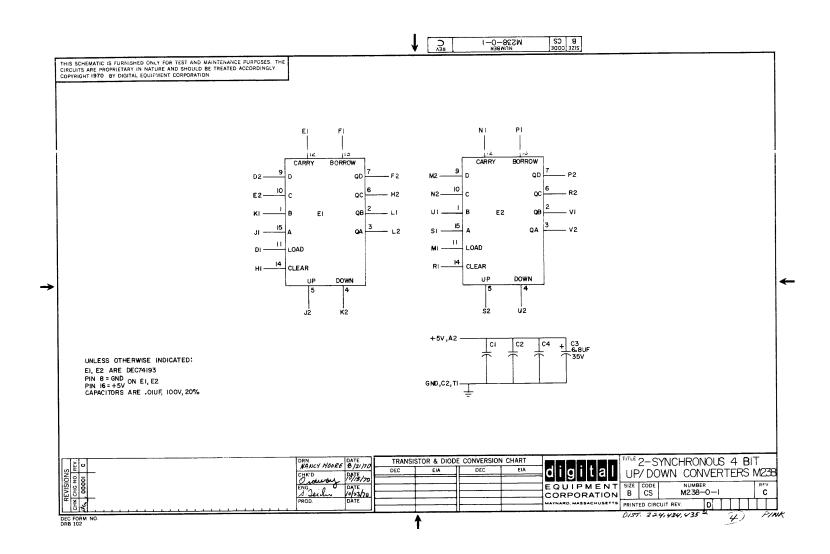

| M233         | Synchronous Up/Down Counter        |

| M241)        | R-S Flip-Flops                     |

| M242         | J-K Flip-Flops                     |

| M243         | Right Shift Parallel Load Register |

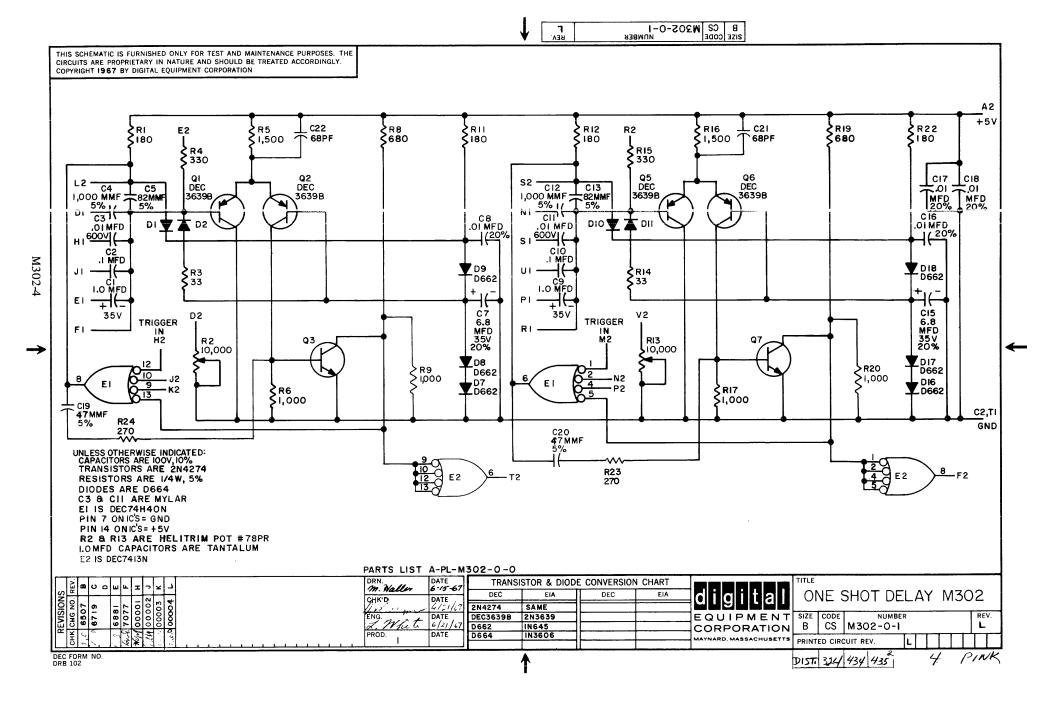

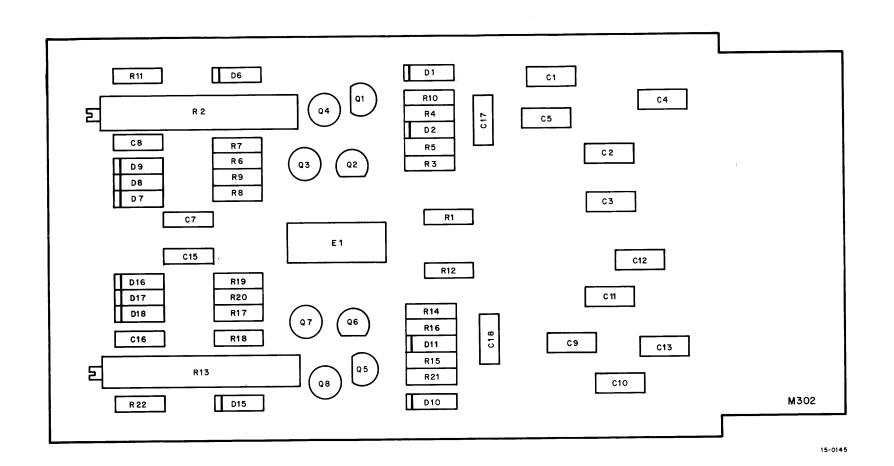

| M302         | Dual Delay Multivibrator           |

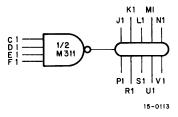

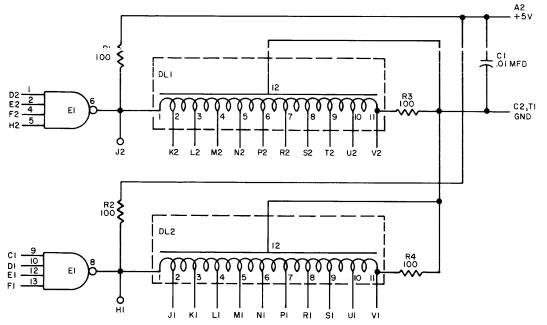

| M311         | Tapped Delay Lines                 |

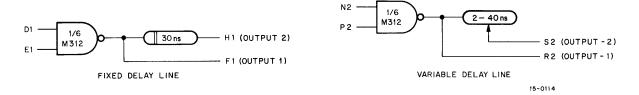

| M312         | Delay Lines                        |

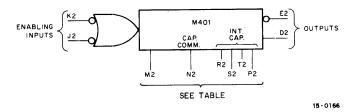

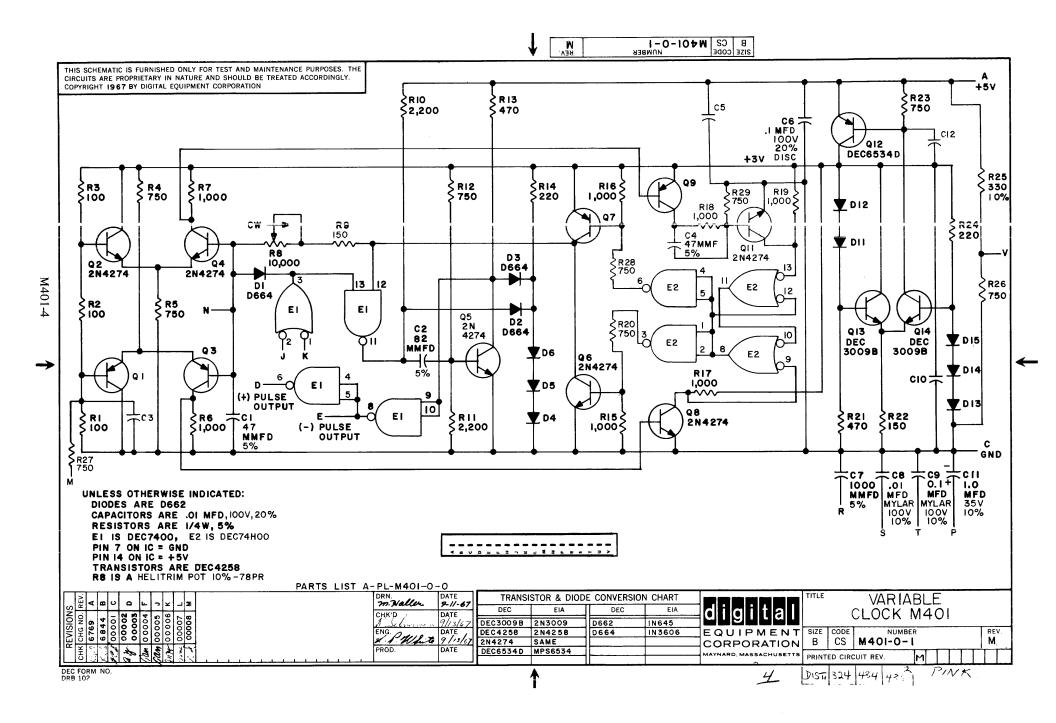

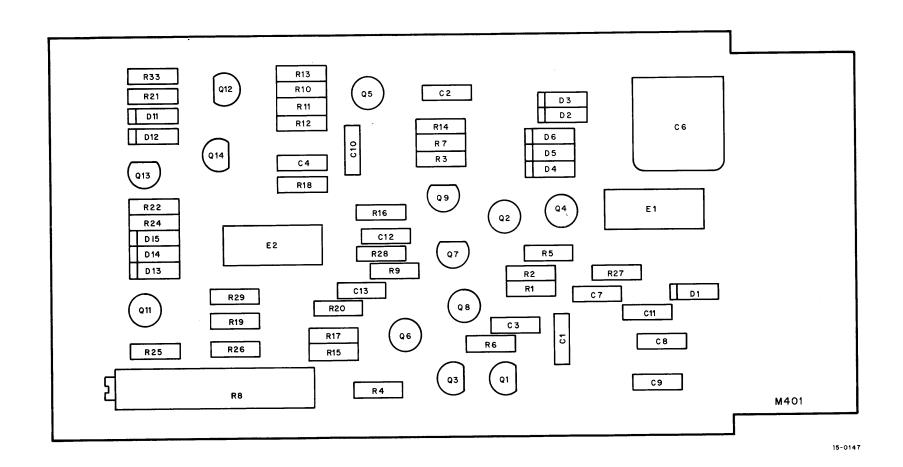

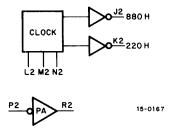

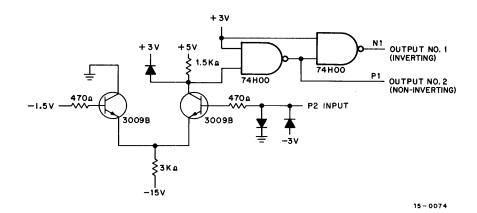

| M401         | Variable Clock                     |

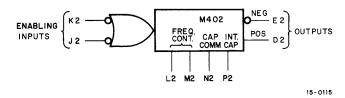

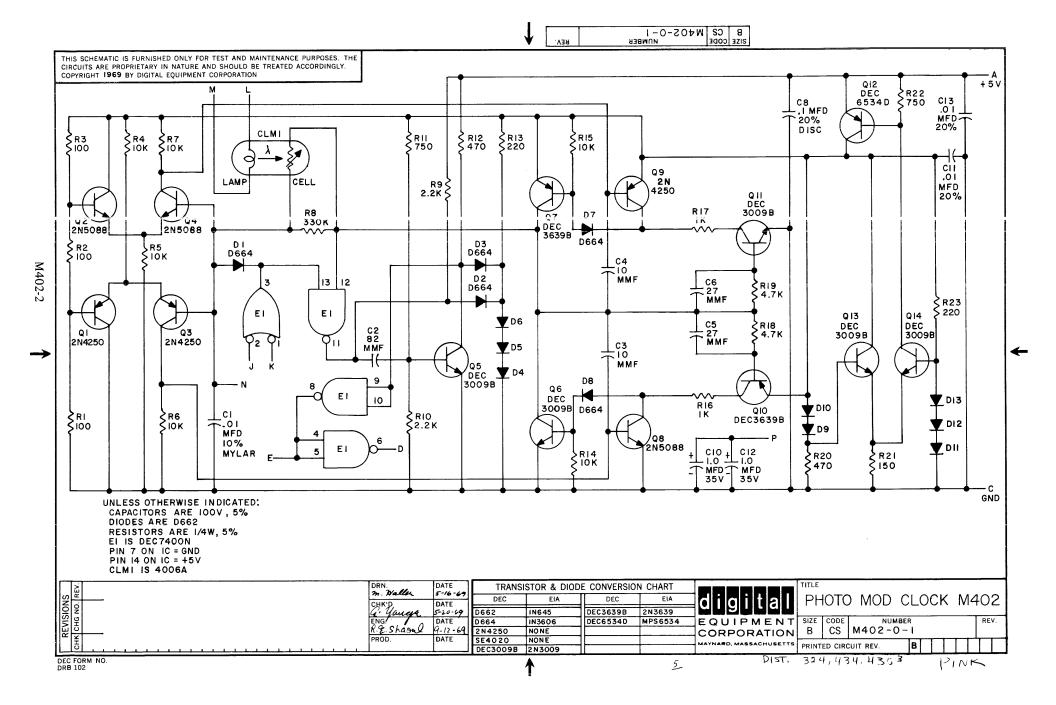

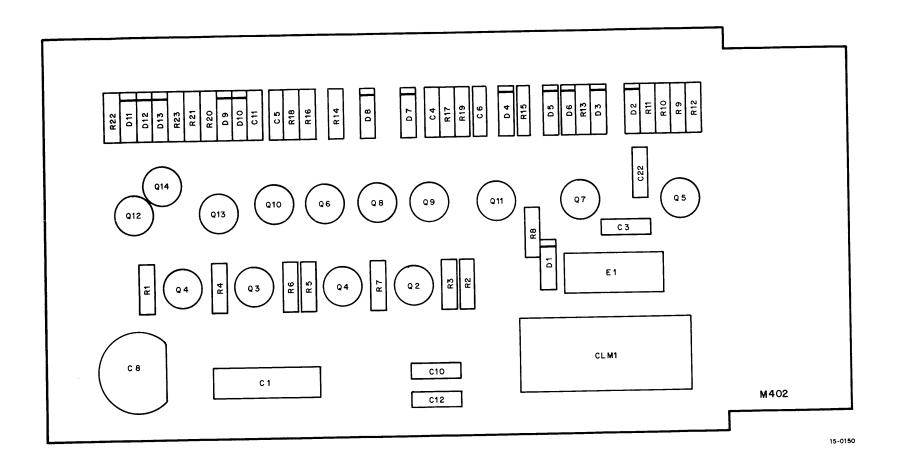

| M402         | Photo Mod Clock                    |

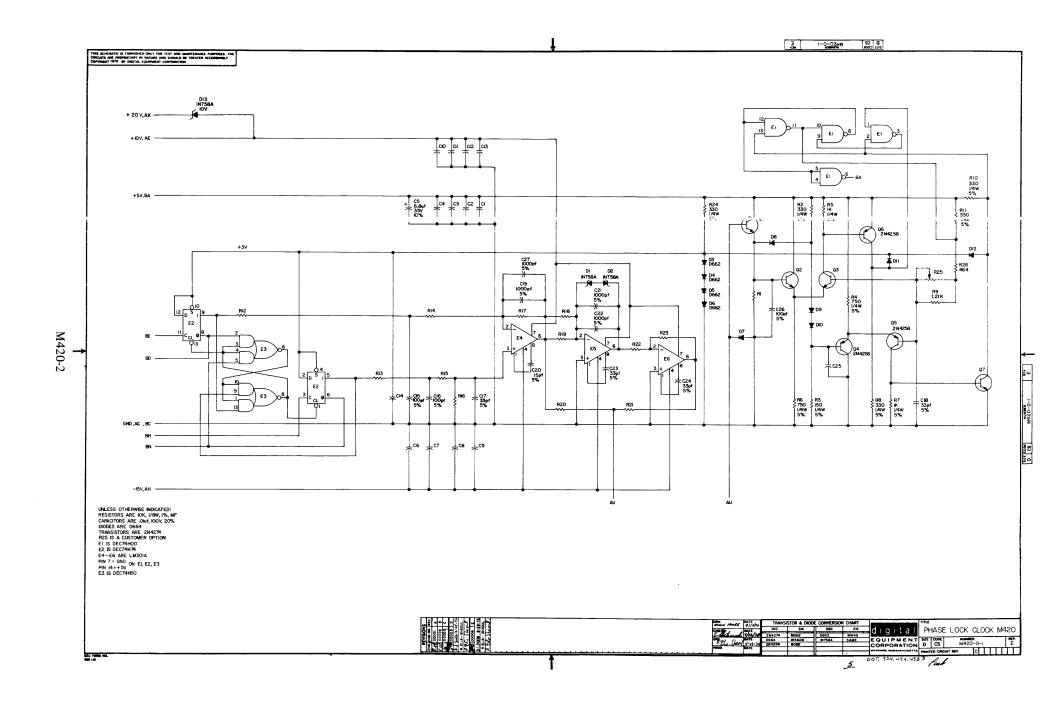

| M420         | Phase-Lock Clock                   |

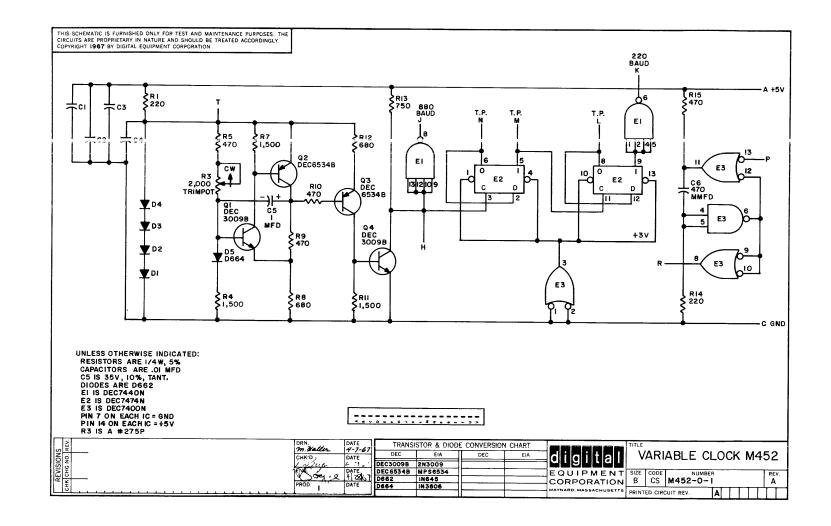

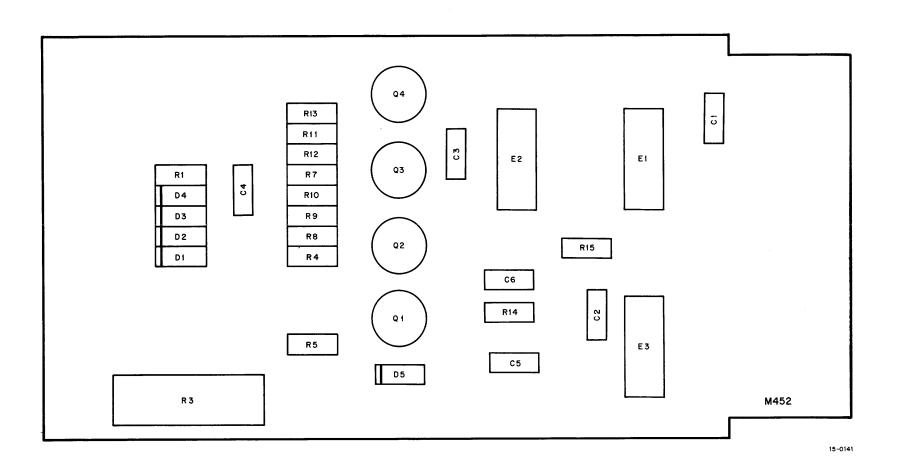

| M452         | Variable Clock                     |

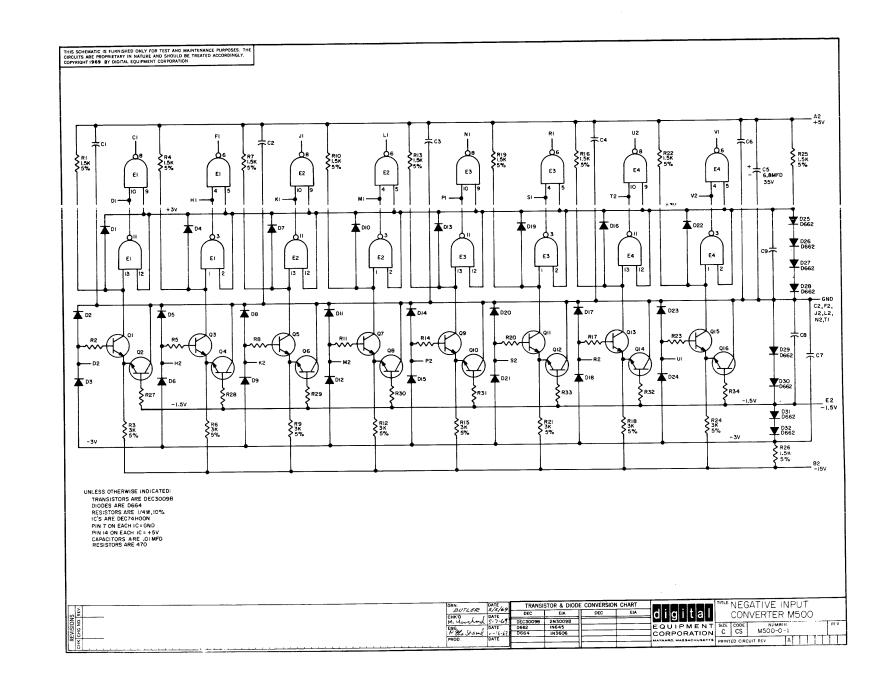

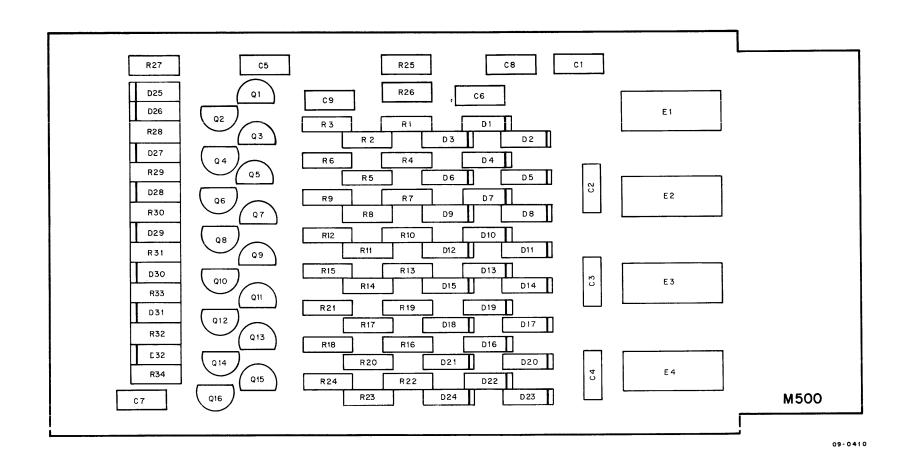

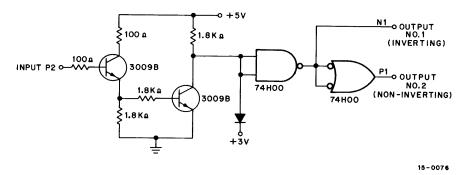

| M500         | Converter-I/O Bus Receiver         |

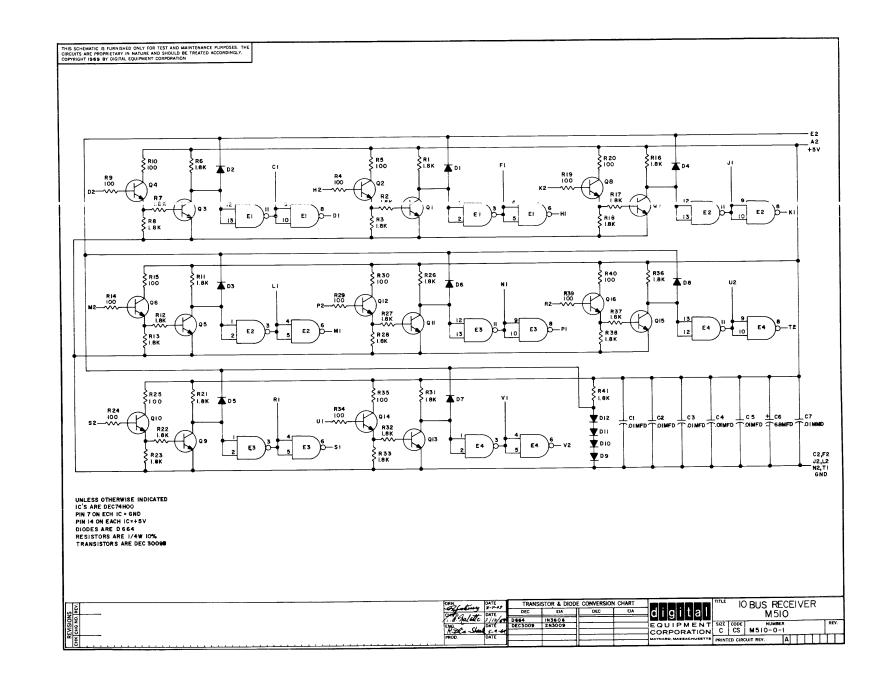

| M510         | I/O Bus Receiver                   |

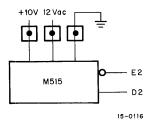

| M515         | Real Time Clock                    |

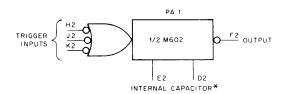

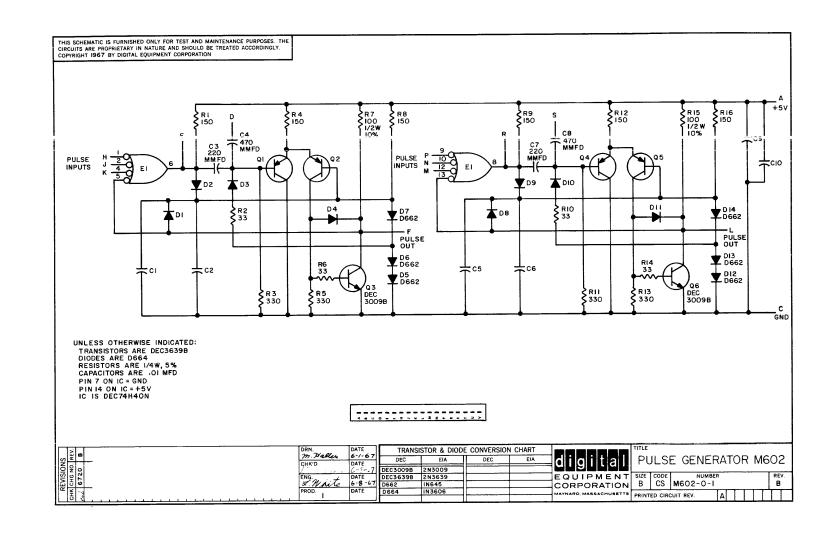

| M602         | Pulse Amplifiers                   |

| M605         | Pulse Generators                   |

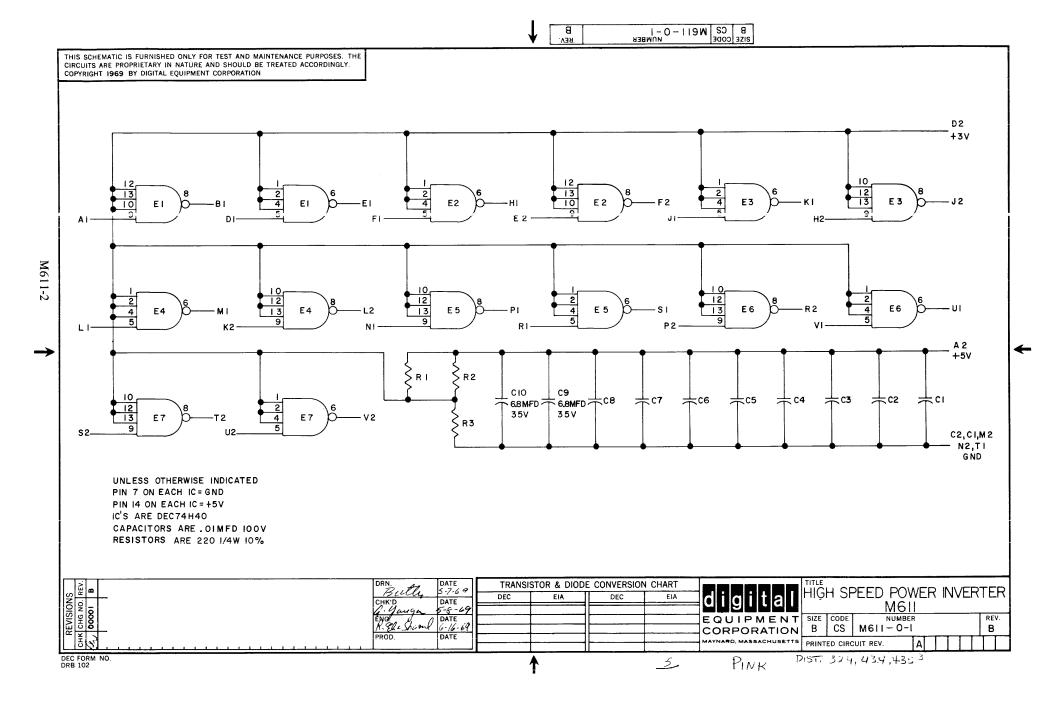

| M611         | High-Speed Power Inverters         |

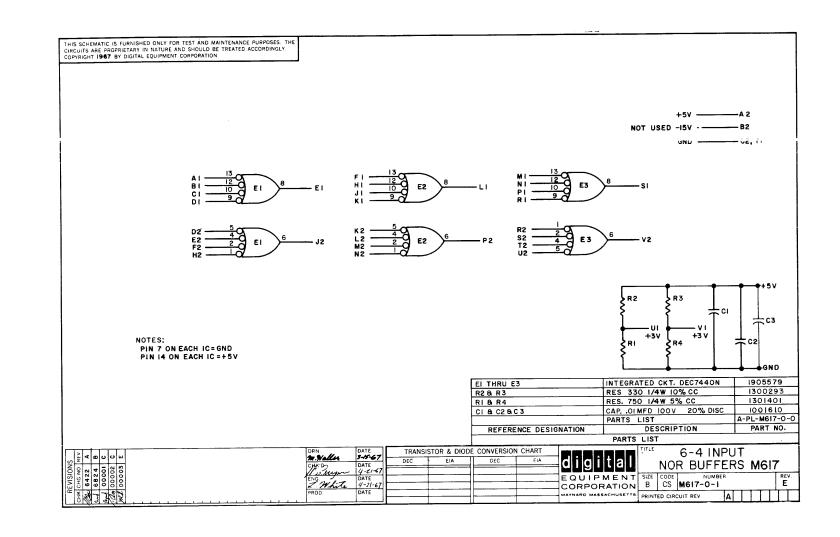

| M617         | Power NAND Gates                   |

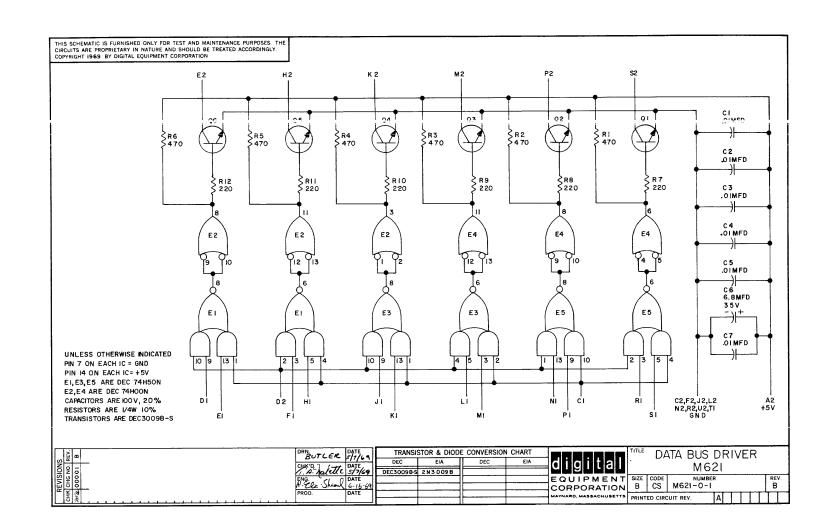

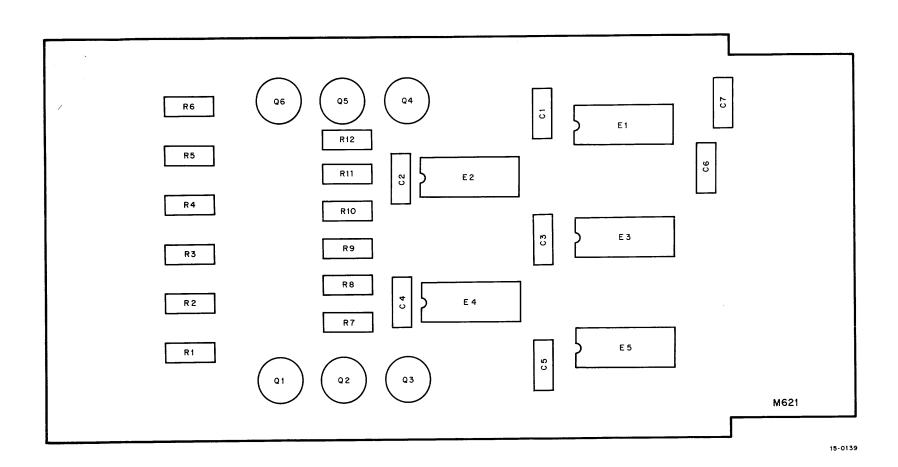

| M621         | Data Bus Drivers                   |

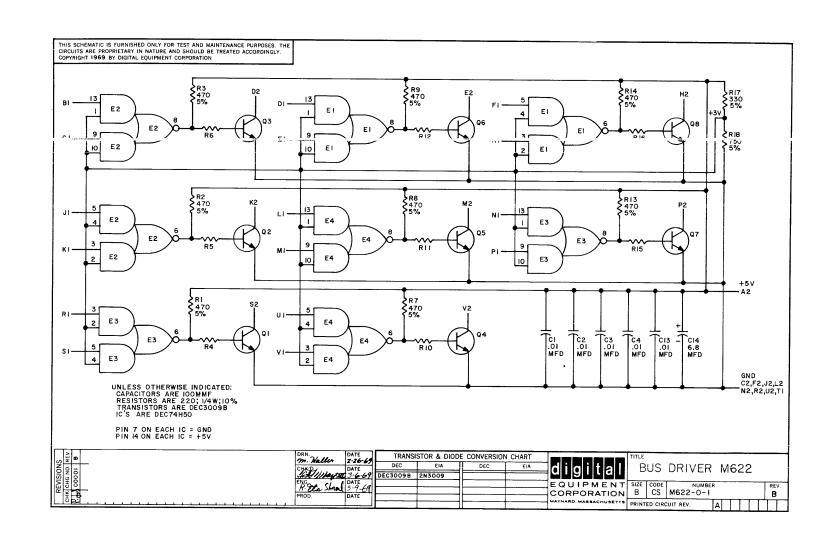

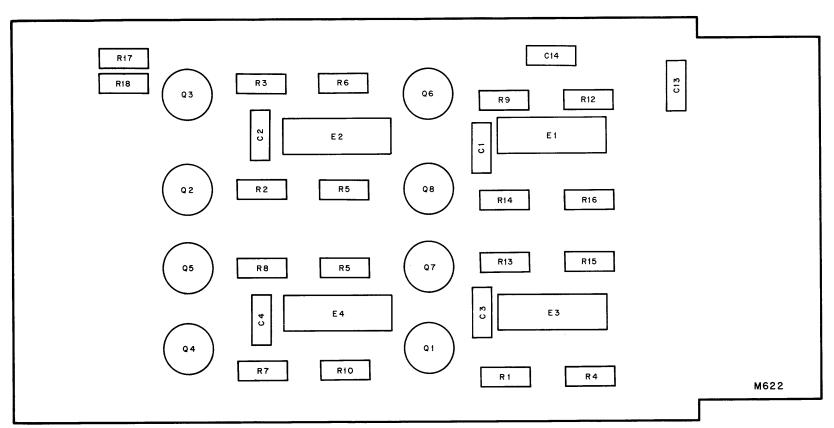

| M622         | I/O Bus Drivers                    |

| M627         | NAND Power Amplifiers              |

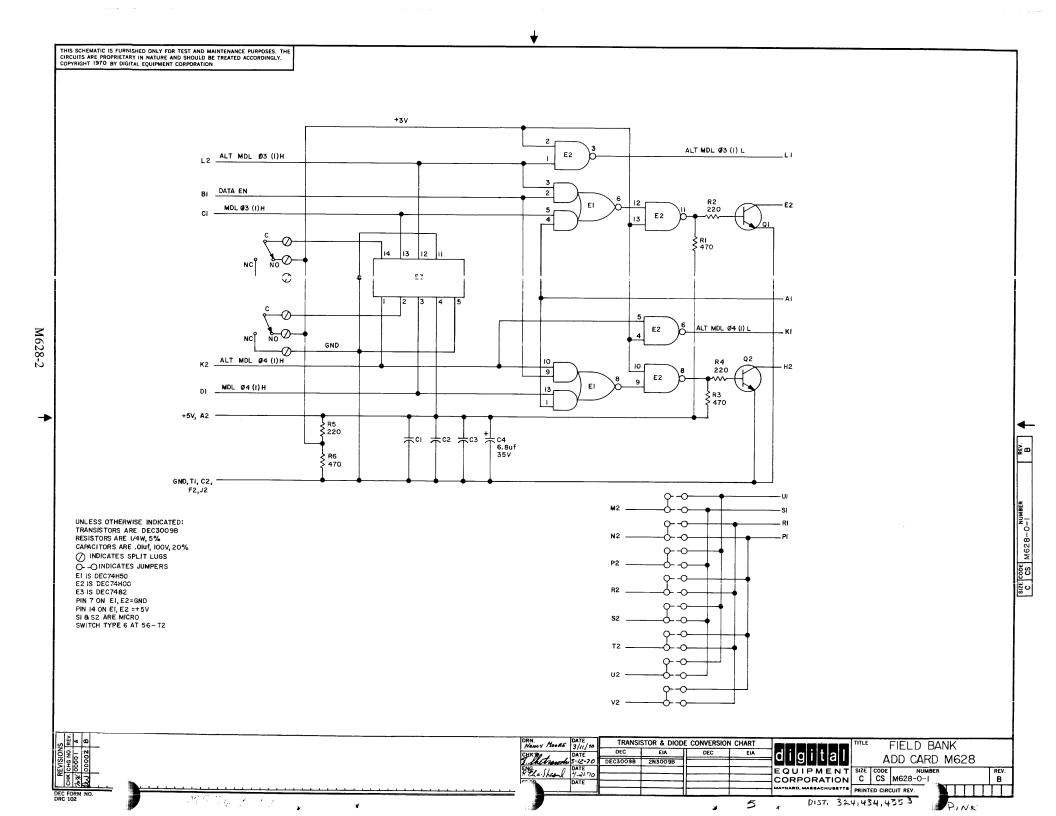

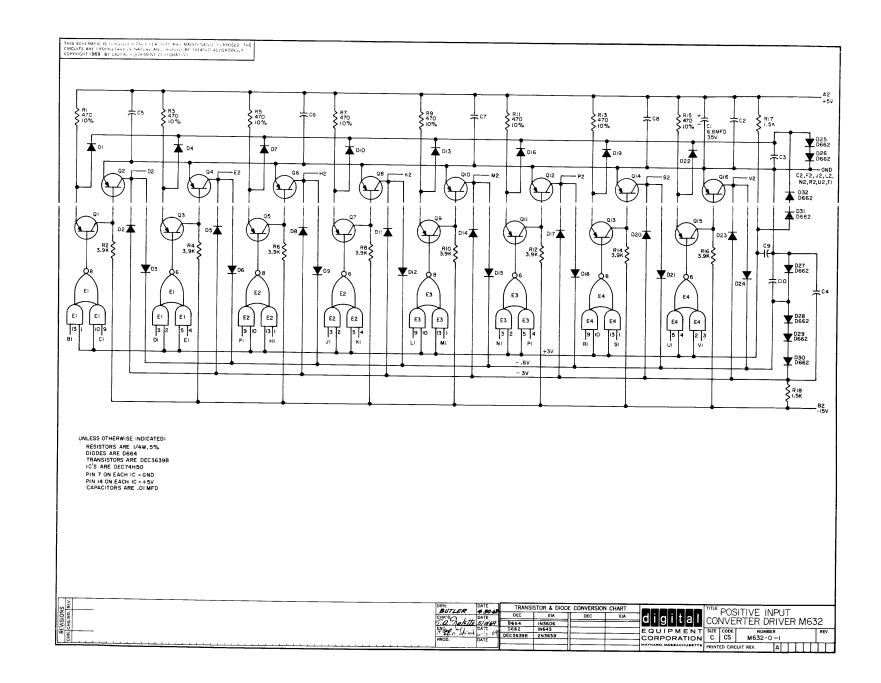

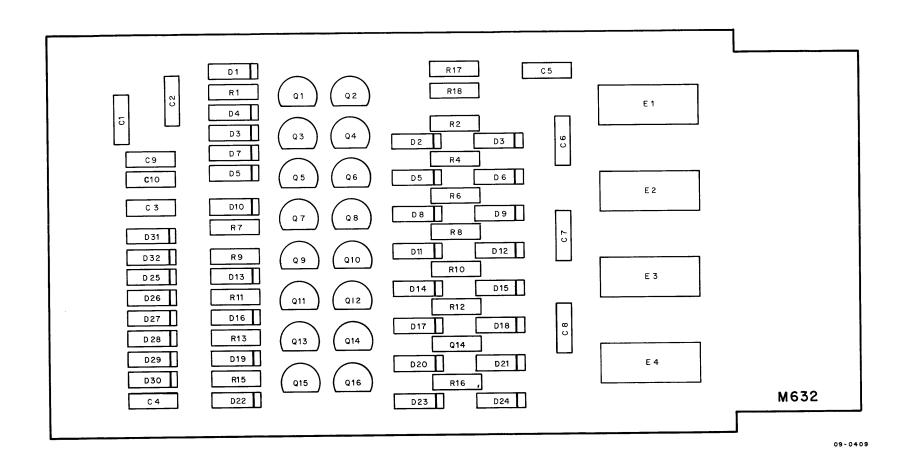

| M628         | Block-Bank Address Card            |

| M632         | Converter-I/O Bus Driver           |

| M706         | Teletype Receiver                  |

| M707         | Teletype Transmitter               |

| M717         | Display Control VP15               |

| M770         | EAE Control                        |

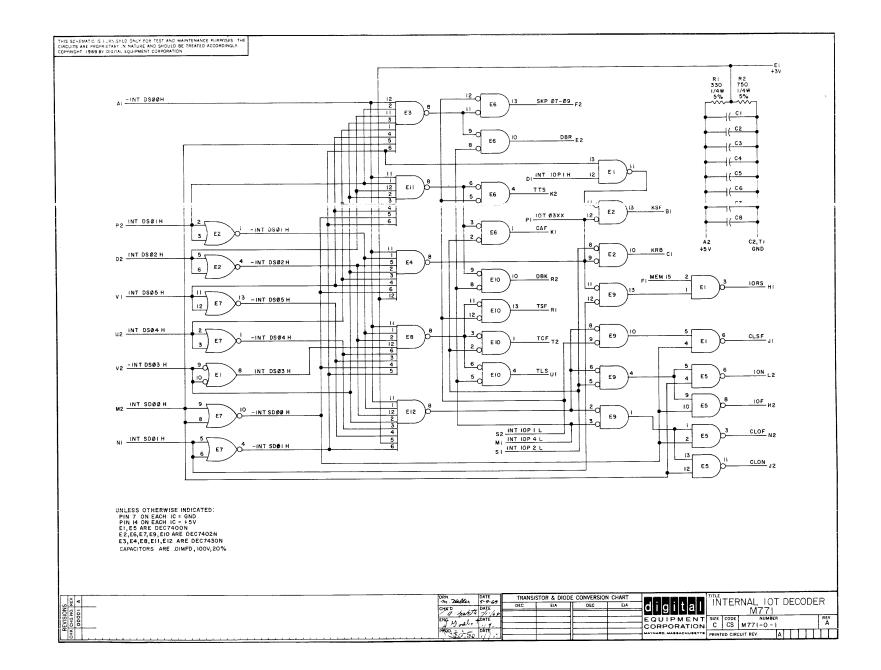

| M770<br>M771 | Internal IOT Decoder               |

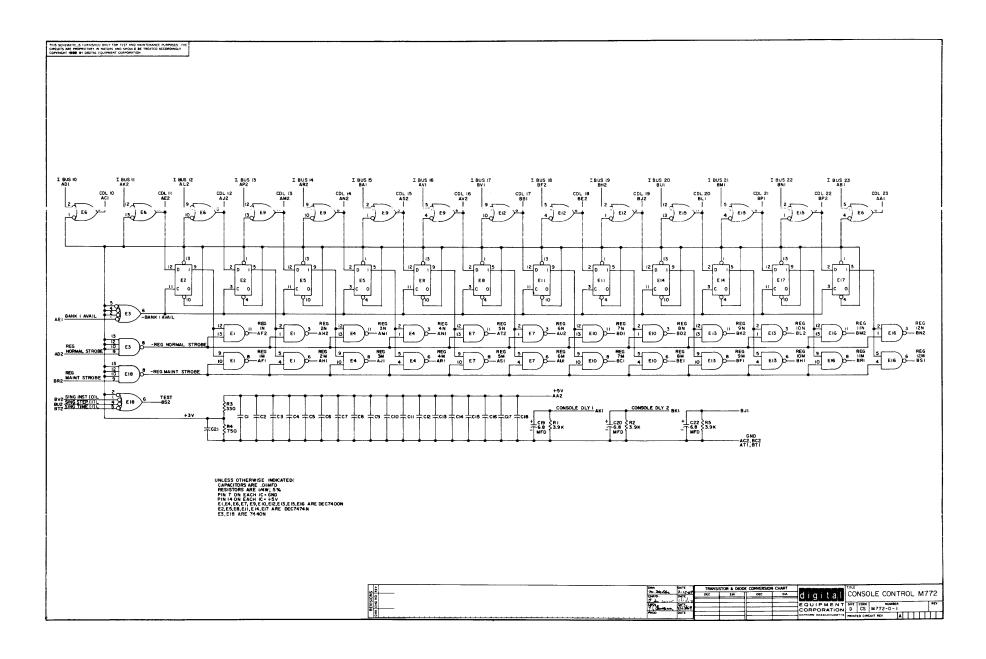

| M771<br>M772 | Console Control No. 1              |

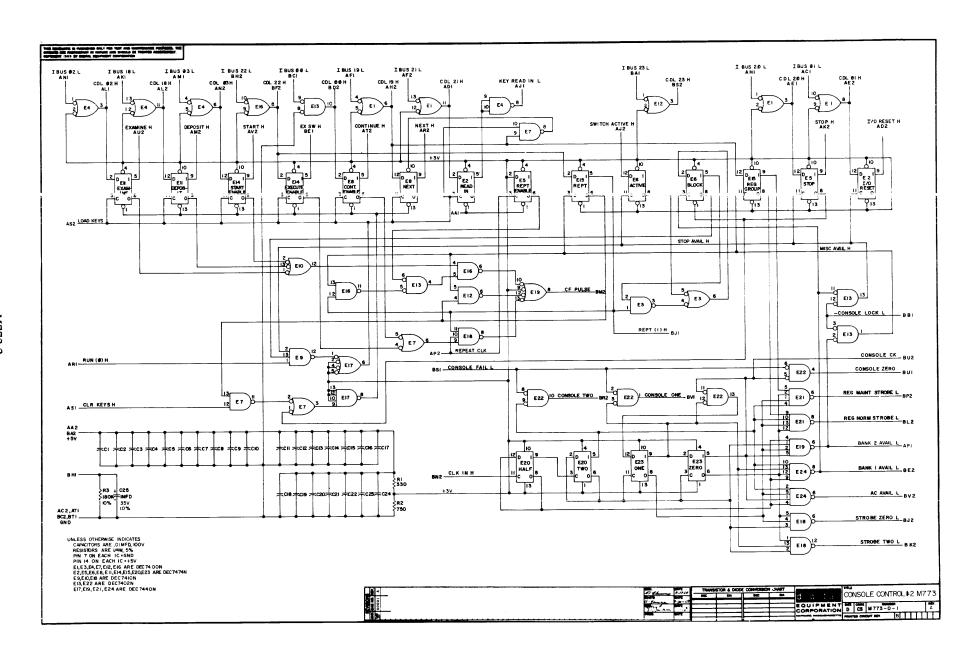

| M773         | Console Control No. 2              |

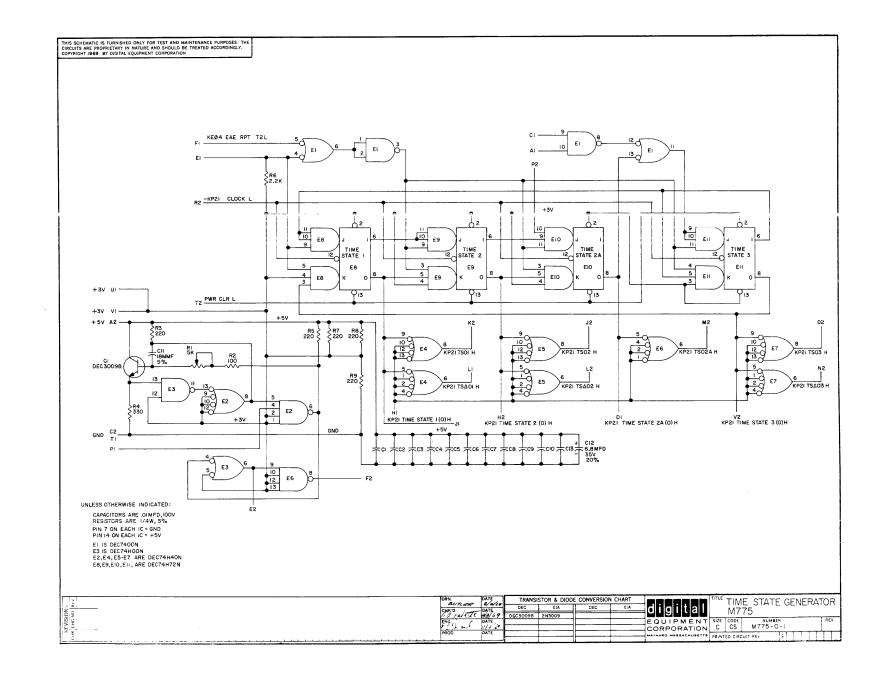

|              | Time State Generator               |

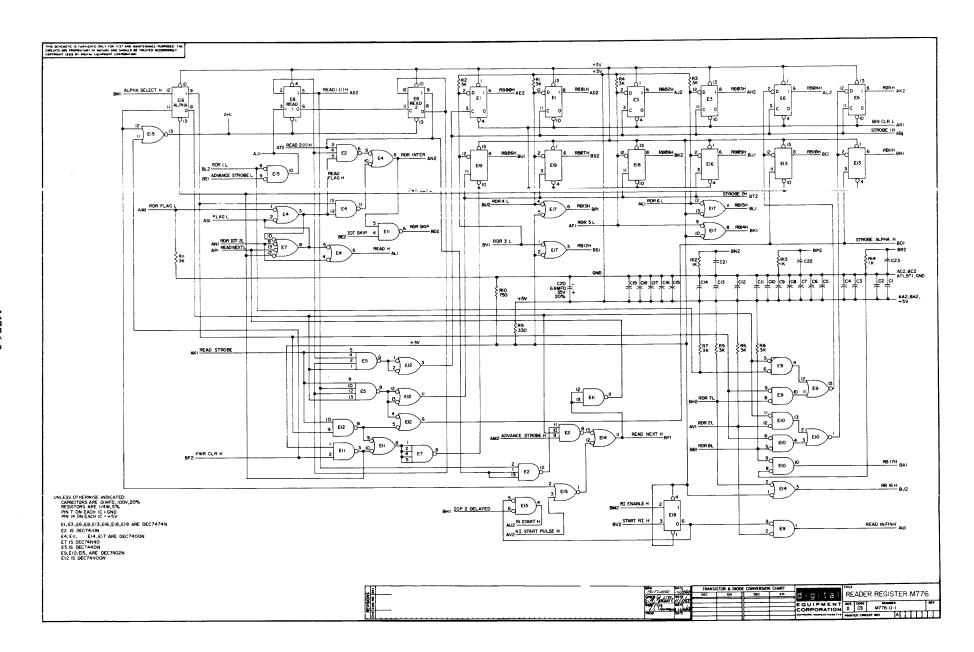

| M775<br>M776 | Reader Register                    |

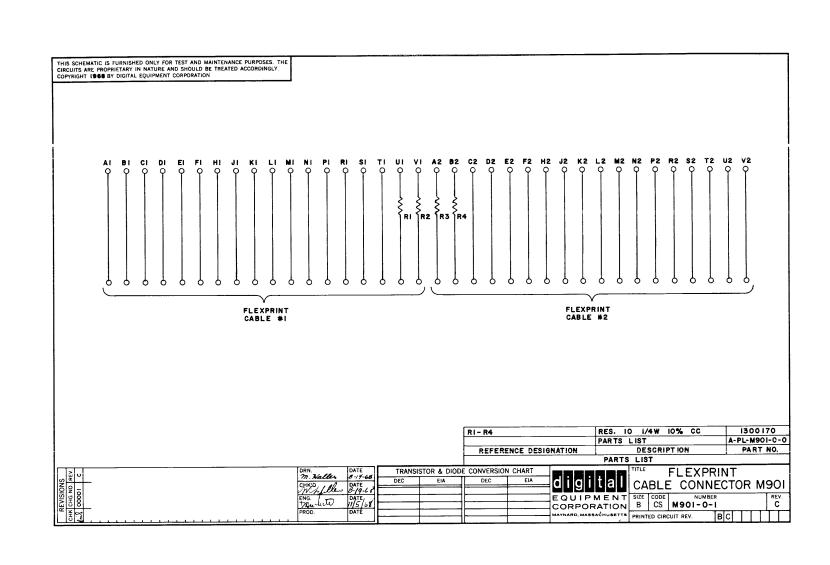

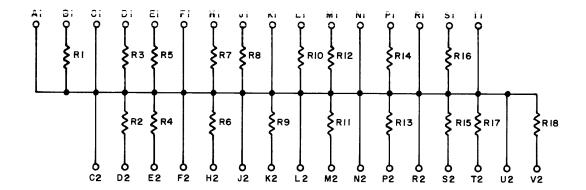

| M776         | Flexprint® Cable Connector         |

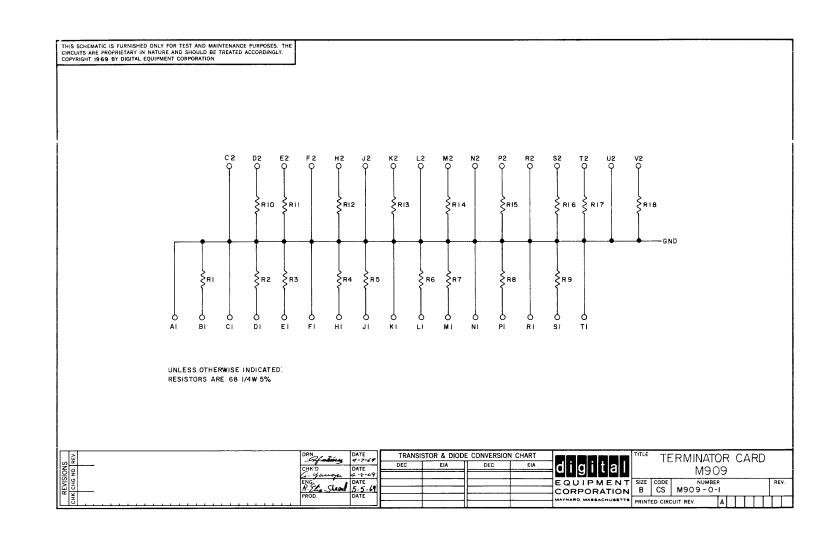

| M901         | Terminator Card                    |

| M902         | Coaxial Cable Connector            |

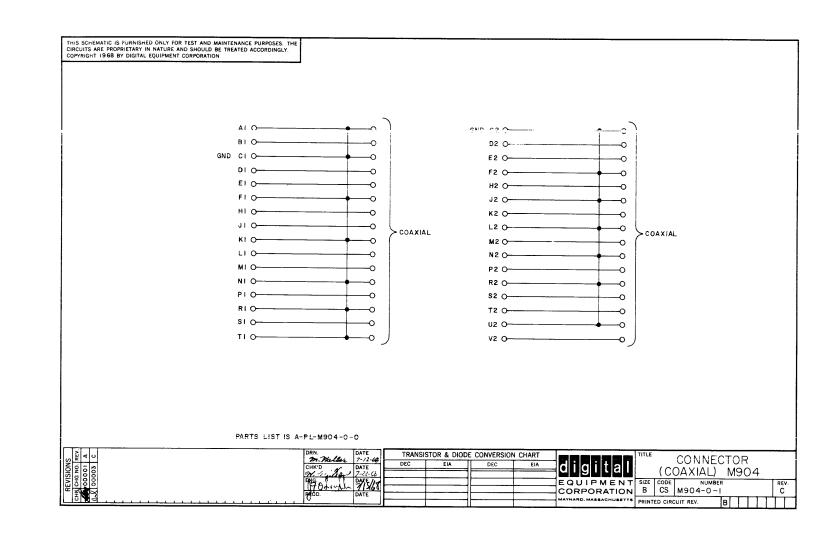

| M904         | Terminator Card                    |

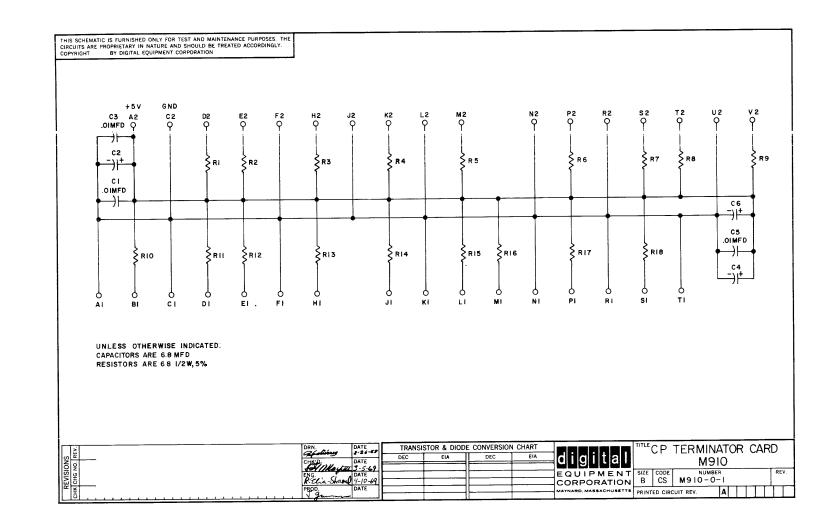

| M909         | CP Terminator Card                 |

| M9 10        | Ci reminiator Caru                 |

### List of Modules (Cont)

| M911  | Memory Bus CP Terminator Card         |

|-------|---------------------------------------|

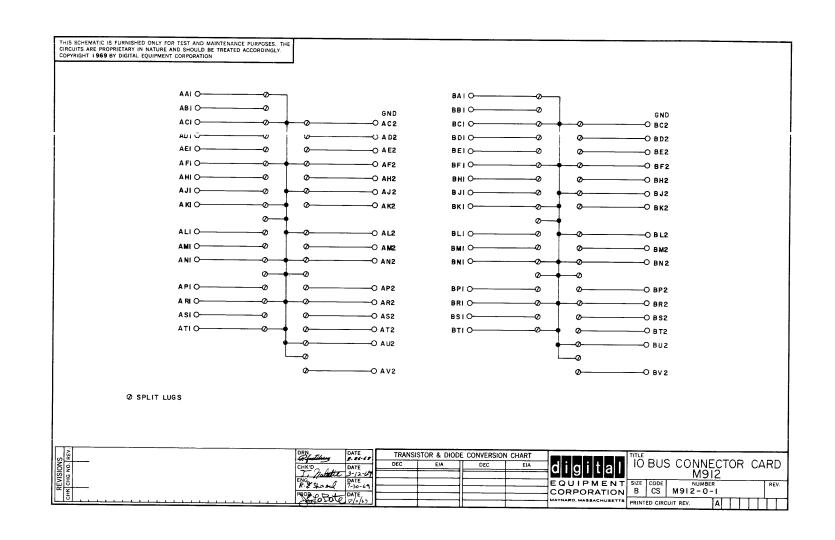

| M912  | I/O Bus Connector                     |

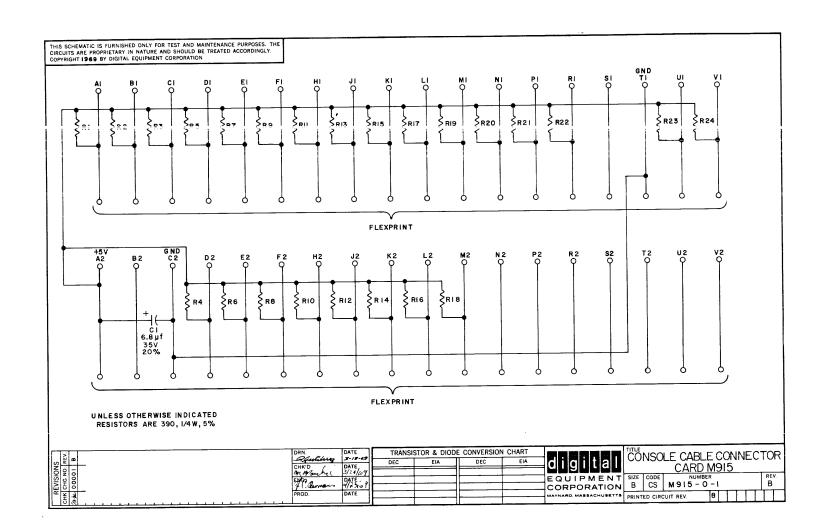

| M915  | Console Cable Connector               |

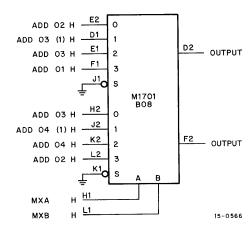

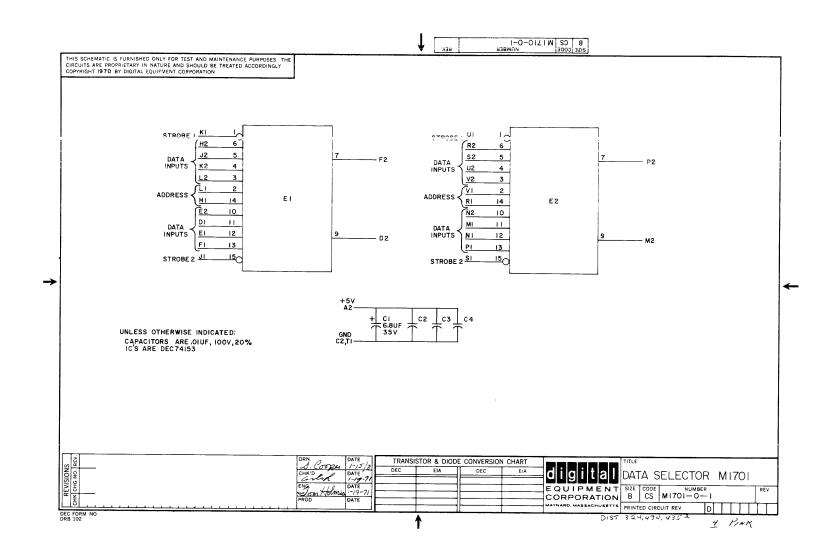

| M1701 | Data Selector                         |

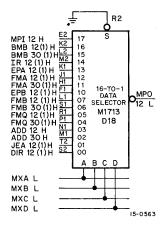

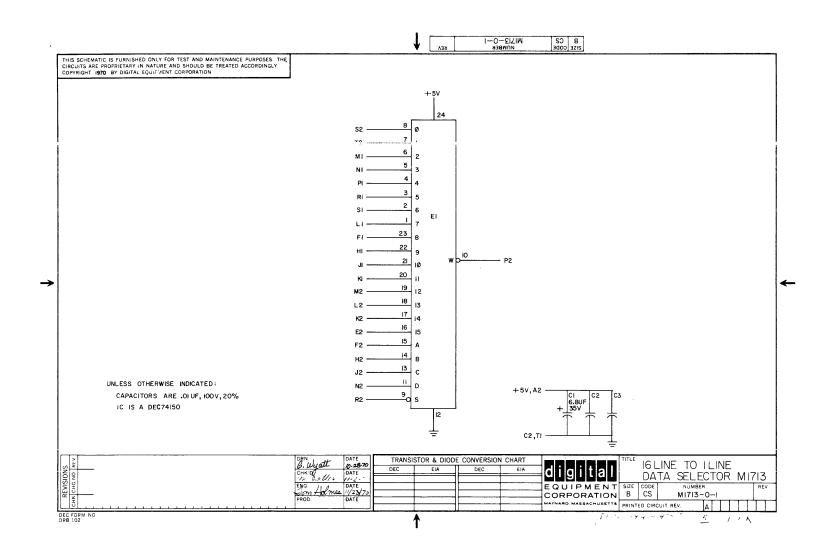

| M1713 | 16-to-1 Data Selector                 |

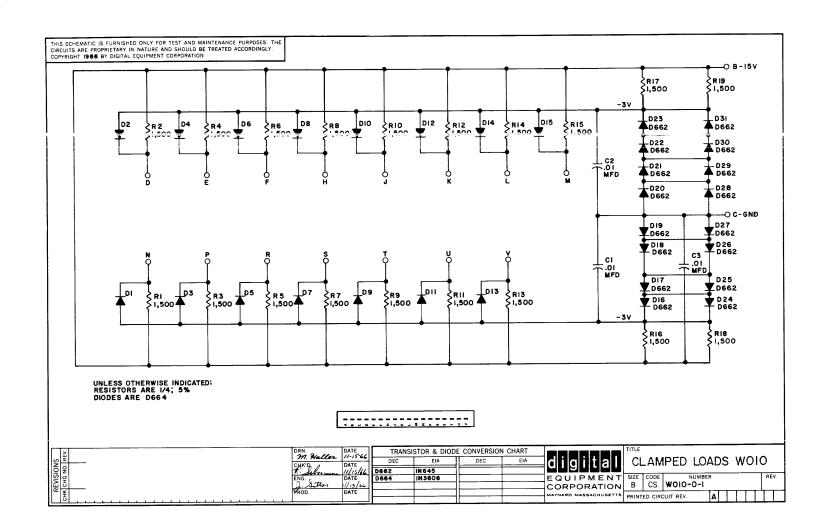

| W010  | Clamped Loads                         |

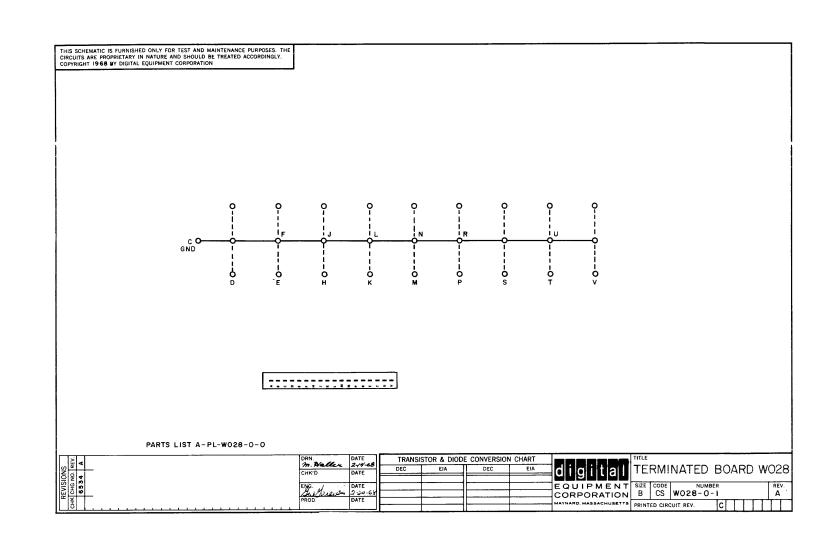

| W028  | Cable Connector for Levels and Pulses |

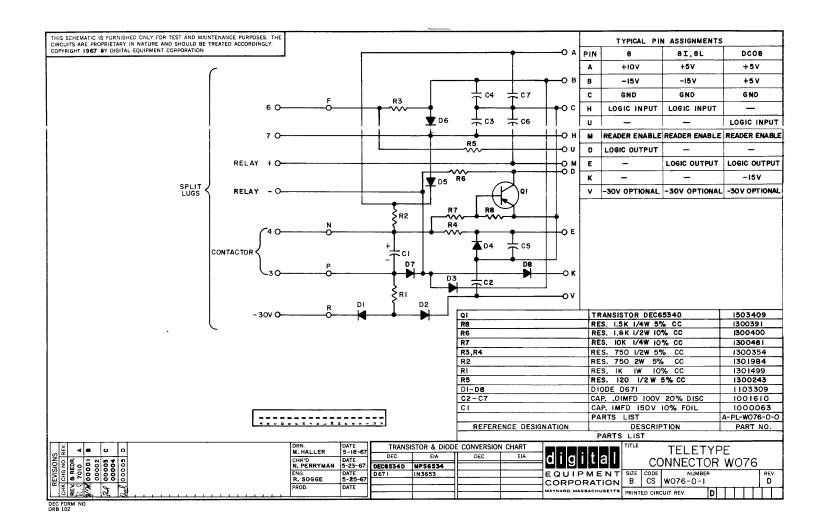

| W076  | Teletype Connector                    |

| W714  | Switches                              |

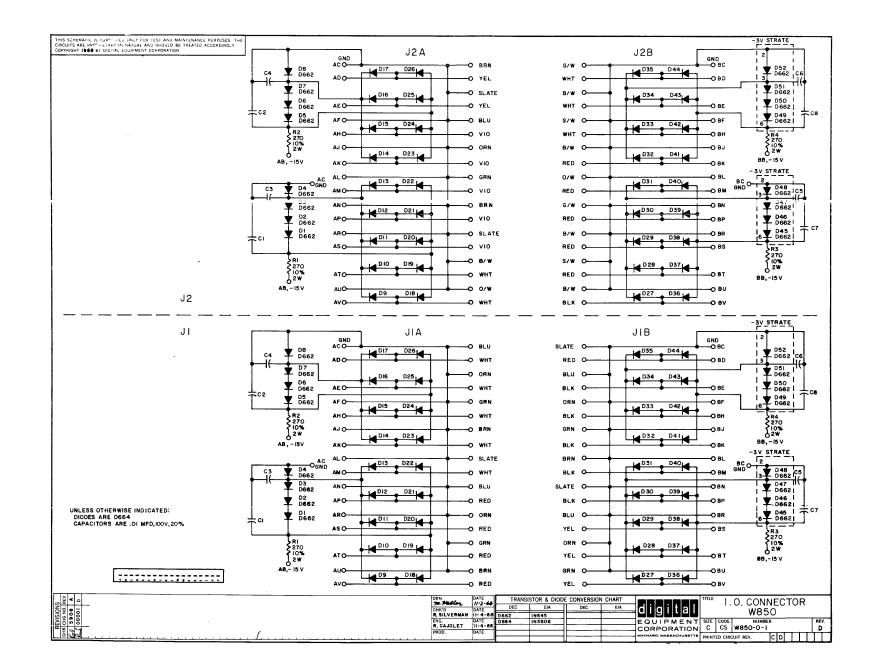

| W850  | I/O Connector                         |

### **General Description**

This manual provides descriptions of modules used in the PDP-15 System and its associated peripherals. A schematic diagram is included with each module description. Parts location diagrams are supplied for those modules that have numerous discrete components.

DEC builds three series of compatible below-ground logic (the B-, R- and S-series), two series of compatible above-ground logic (K- and M-series), an extensive line of modules to interface different types of logic (W-series), a line of special-purpose modules (G-series), and a line of support hardware for its module line (H-series).

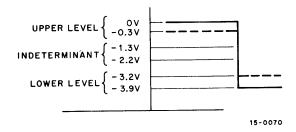

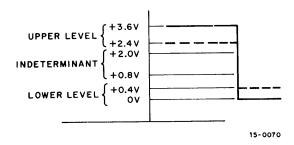

With few exceptions, the DEC below-ground logic operates with logic levels of ground to -0.3V (upper level) and -3.2V to -3.9V (lower level), using diode gates that draw input current at ground and supply output current at ground. Figure 1 shows the voltage spectrum of negative logic systems.

Figure 1 Voltage Spectrum of Negative Logic Systems

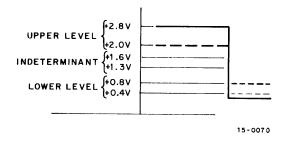

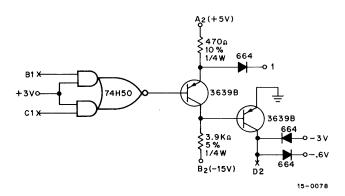

The compatible above-ground logic generally operates with levels of ground to +0.4V (lower level) and +2.4 to +3.6V (upper level), using TTL or TTL-compatible circuits with inputs that supply current at ground and outputs that sink current at ground. Figure 2 shows the TTL logic voltage spectrum.

Figure 2 Voltage Spectrum of TTL Logic

A set of special modules designed to operate on the PDP-15 I/O bus is also available. Figure 3 indicates the voltage spectrum in which these special modules operate.

The use of DEC's **Digital Logic Handbook** is recommended for readers of this manual who are not familiar with the basic principles of digital logic and the type of circuits used in DEC logic modules.

Figure 3 Voltage Spectrum for Positive PDP-15 I/O Bus Logic

#### MEASUREMENT DEFINITIONS

Timing is measured with the input driven by a gate or pulse amplifier of the series under test and with the output loaded with gates of the same series (unless otherwise specified). Percentages are assigned with 0 percent indicating the initial steady-state level and 100 percent indicating the final steady-state level, regardless of the direction of change.

Input/output delay is the time difference between input change and output change, measured from 50 percent input change to 50 percent output change. Rise and fall delays for the same module are usually specified separately.

Risetime and falltime are measured from 10 percent to 90 percent of waveform change, either rising or falling.

### **LOADING**

Input loading and output driving are specified in "units", with one unit equivalent to 1.6 mA. The inputs to low-speed gates usually draw 1 unit of load. High-speed gates draw 1.25 units, or 2 mA.

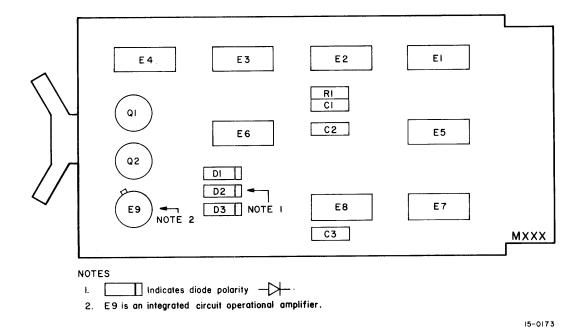

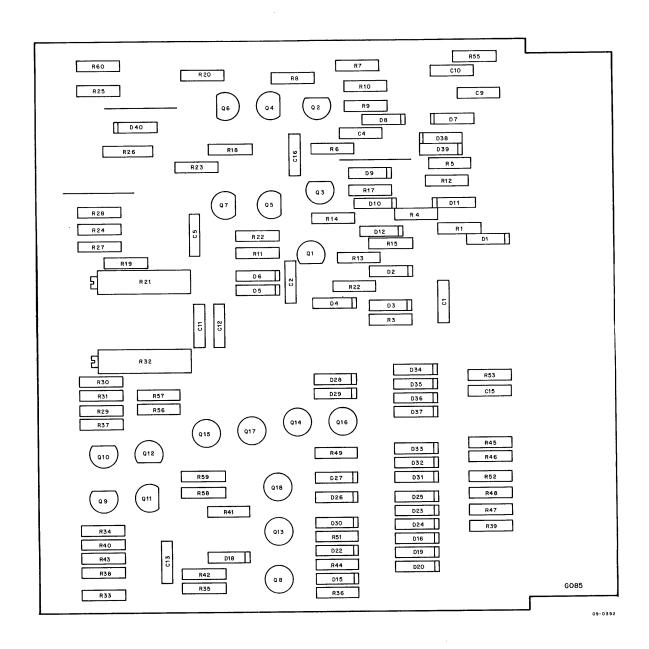

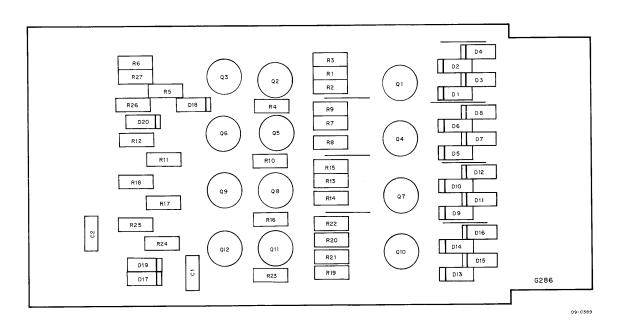

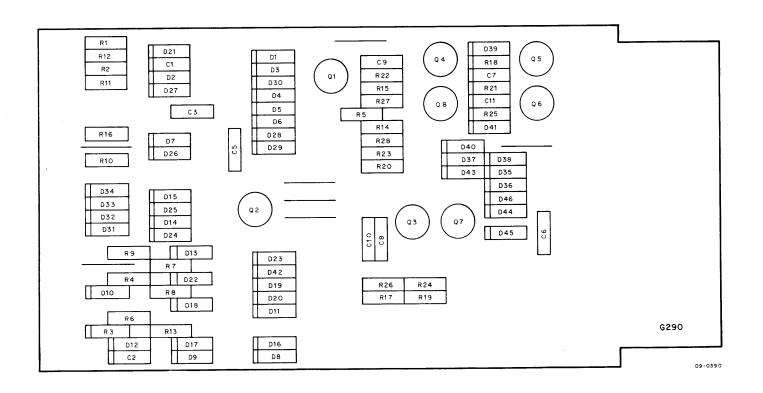

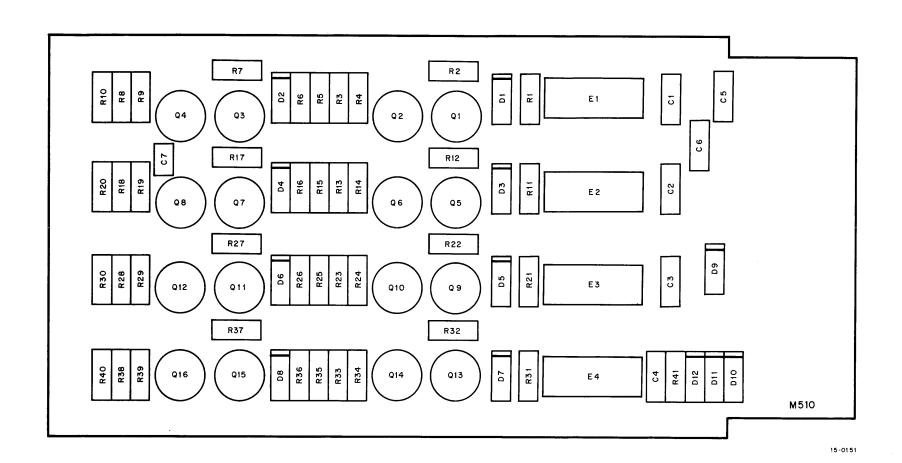

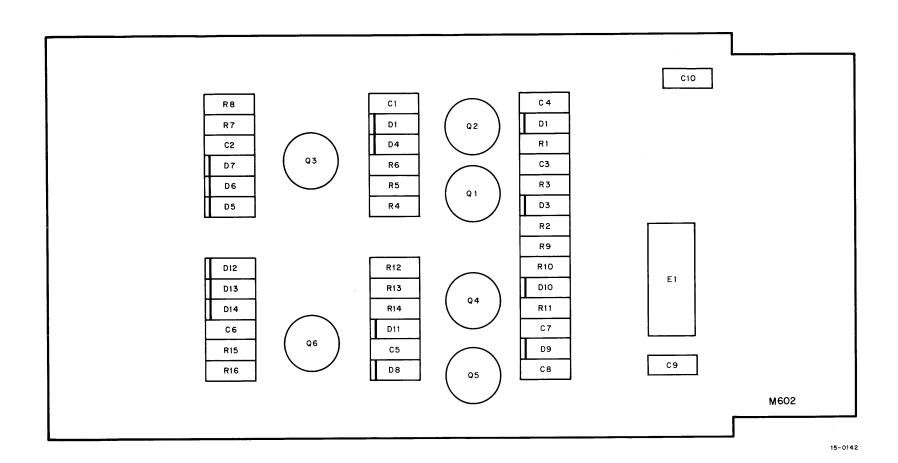

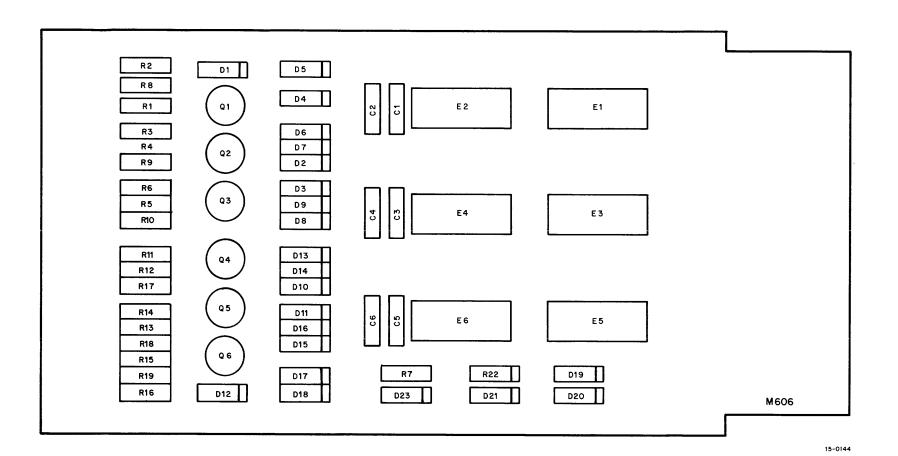

### **PARTS LOCATION**

A parts location diagram is provided for those modules that contain numerous discrete components and integrated circuits. The location of parts on integrated circuit modules can be determined by visual inspection and circuit schematic reference.

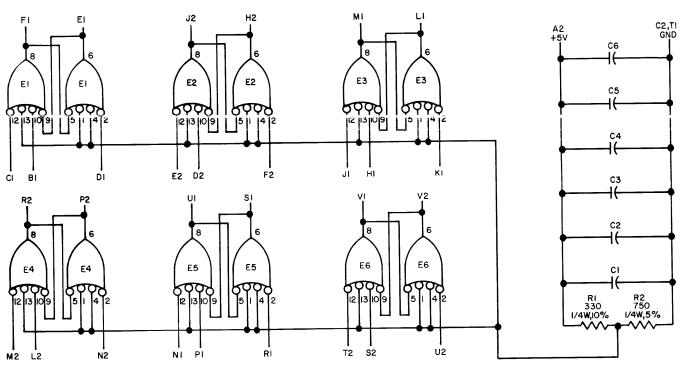

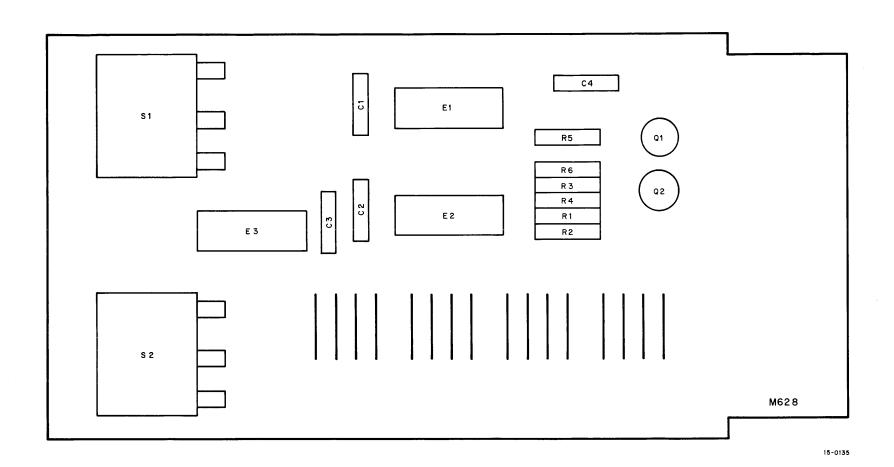

"E" designators are assigned to integrated circuits according to the following convention: looking at the component side of the module, "E" numbers are assigned from right-to-left within each horizontal row, starting with the top row. Figure 4 illustrates this convention and typical symbols used in the parts location diagrams.

Figure 4 Sample Parts Location Diagram

## A124 Analog Multiplexer

The A124 Analog Multiplexer consists of four MOSFET switches and four driver gates used for selection of single-ended analog inputs in the range of  $\pm 10$ V. This module is also used for gain selection with the A222 Selectable Gain Amplifier in the AD15 Analog Subsystem.

Isolated grounds are used in the module to help prevent program noise from causing analog signal acquisition errors. Analog and logic grounds may differ by as much as 9V without malfunction.

Each drive consists of 2-bit input decoding and a common enable input. All inputs are de-activated when power is removed.

INPUTS: Digital: Pin H (enable) presents 1 unit load; pins J, K, L, M, N and P present

1/2-unit load each.

Analog: Pins R, S, T, and  $U=\pm 10V$  normal,  $\pm 20V$  maximum.

**OUTPUTS:** Analog: Pin V series resistance < 2200 ohms, 3 mA max. load.

Response time to logic input change  $< 1.2 \mu sec.$

**POWER:** +15V at pin D, 25 mA

-20V at pin E, 30 mA +5V at pin A, 8 mA

5

DIST, 324, 434, 4353 PMC

A124-2

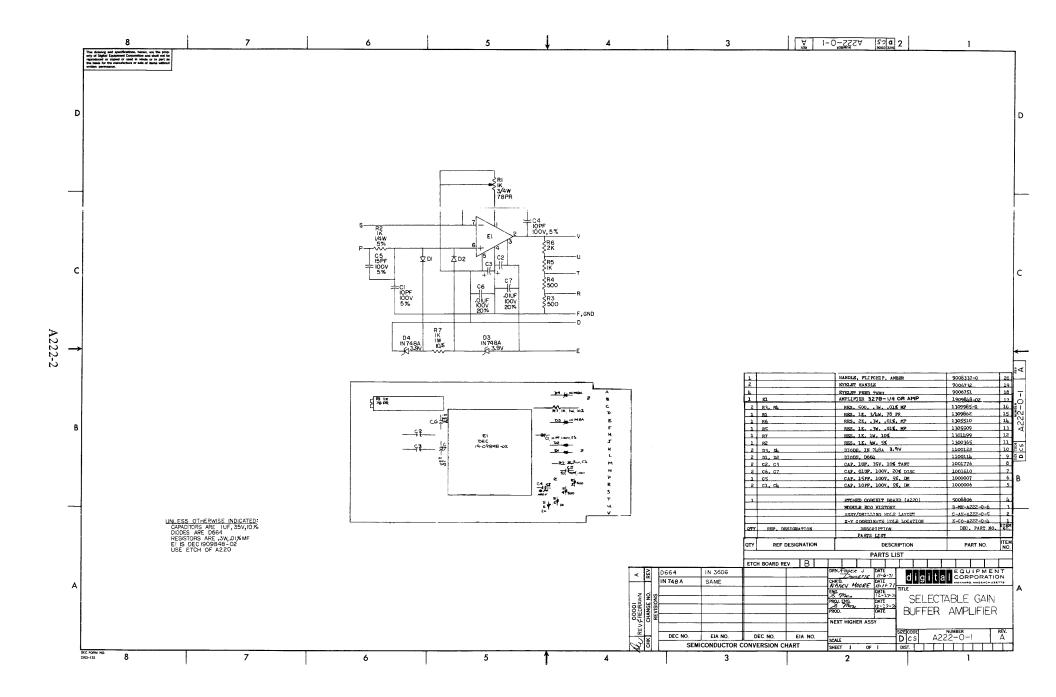

### Δ222

### Selectable Gain Amplifier

The A222 is a non-inverting operational amplifier with high input impedance. A precision voltage divider is connected between output and ground with taps at ratios of 1.0, 0.5, 0.25, and 0.125. This module is used with an A124 Analog Multiplexer in the AD15 Analog Subsystem to provide computer-controlled gain selection in the AD15. An IOT instruction causes two AC bits to be transferred to an AD15 buffer register. These bits are decoded by the A124 to select one of four available gains: 1, 2, 4, or 8.

INPUTS:

Inverting input (pin S) - Connect to the desired feedback tap through a series resistance of 3000 ohms or less (A124 Analog Multiplexer).

Non-inverting input (pin P) — Gain of 1, 2, 4, or  $8 \pm .02\%$  with .02% linearity error over a  $\pm 10V$  output range. Input impedance greater than 1000 megohms in parallel

with 10 pF. Protected against overload up to ±20V.

| <b>OUTPUTS</b> : | Analog Input Range             | Selected Gain | Output Selected |

|------------------|--------------------------------|---------------|-----------------|

|                  | ±1.25V                         | 8             | Pin V           |

|                  | ±2.5V                          | 4             | Pin U           |

|                  | ±5.0V                          | 2             | Pin T           |

|                  | $\pm 10.0 \mathbf{V}$          | 1             | Pin R           |

| POWER:           | +15V, ±1%, 20 mA, max. (Pin D) |               |                 |

|                  | -15V, ±1%, 20 mA, max. (Pin E) |               |                 |

### A405

### Sample and Hold Amplifier

The A405 Sample and Hold Amplifier is used in the AD15 Analog Subsystem to sample the rapidly varying analog input (25 kHz, minimum) and store the signal level at a particular time to allow an A/D converter to convert the signal to a digital word. The amplifier provides acquisition of a 10V step input to within 1 mV in less than 2  $\mu$ s.

Two digital Track Control inputs are provided to control the sample/hold function: pin BF for positive logic and pin BH for negative logic. In positive logic applications, the amplifier will sample (track) when the level at pin BF is high and hold when the level at pin BF is low. For pulsed RS flip-flop control, jumper W1 is removed and jumper W2 is connected. Then, a positive pulse at pin BF sets the flip-flop for tracking and a positive pulse at pin BH resets the flip-flop to hold the signal.

A voltage offset circuit is provided at the input to allow the output signal to be shifted more positive. To use this offset, pin AU is jumpered to pin BJ and pin BM is jumpered to pin AE. (-15V). This circuit is not used on the AD15 Analog Subsystem application.

INPUTS: Analog input: ±10V range, 2000 ± 1% ohms

Digital inputs: Positive logic Track Control at pin BF presents 1 unit load.

Pulse input to set hold at pin BH presents 1 unit load.

**OUTPUTS:** Analog output: ±10V at 10 mA, 0.1 ohm maximum output impedance at pin AV.

**POWER:** +15V at 35 mA at pin AD

-15V at 40 mA at pin AE (plus additional 11 mA if offset circuit is connected)

+5V at 15 mA at pin AA

## A607 10-Bit D/A Converter, Single Buffered

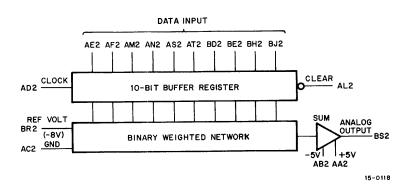

The A607 module contains a 10-bit D/A converter that consists of a 10-bit buffer register, a binary weighting network, and a current summing amplifier. The reference voltage used in the binary weighting network is externally supplied for greater efficiency and optimum scale factor matching in multi-channel applications. Data on register input lines must be settled 20 ns before the leading edge (positive-going voltage of the CLOCK pulse passes the threshold voltage and should remain stable 5 ms afterward. The duration of the positive CLOCK pulse should be at least 50 ns, and the duration of the negative CLEAR pulse should be at least 30 ns. Data present at the input of the register is transferred to the output when the leading edge of the CLOCK pulse passes the threshold. The analog output voltage is unipolar and varies from 0V to 2.0V (in two millivolt increments) in accordance with the binary input data.

The following are the input, output, and power characteristics of the A607 module.

INPUTS: Each DATA input presents one TTL unit load. The CLOCK input presents 2 unit loads,

and the CLEAR input presents 3 unit loads.

**OUTPUTS**: The analog output voltage is capable of driving a 10 mA load (maximum).

POWER: Power dissipation of the A607 is 5V at 200 mA (maximum) and -15V at 100 mA (maximum).

A607 Simplified Diagram

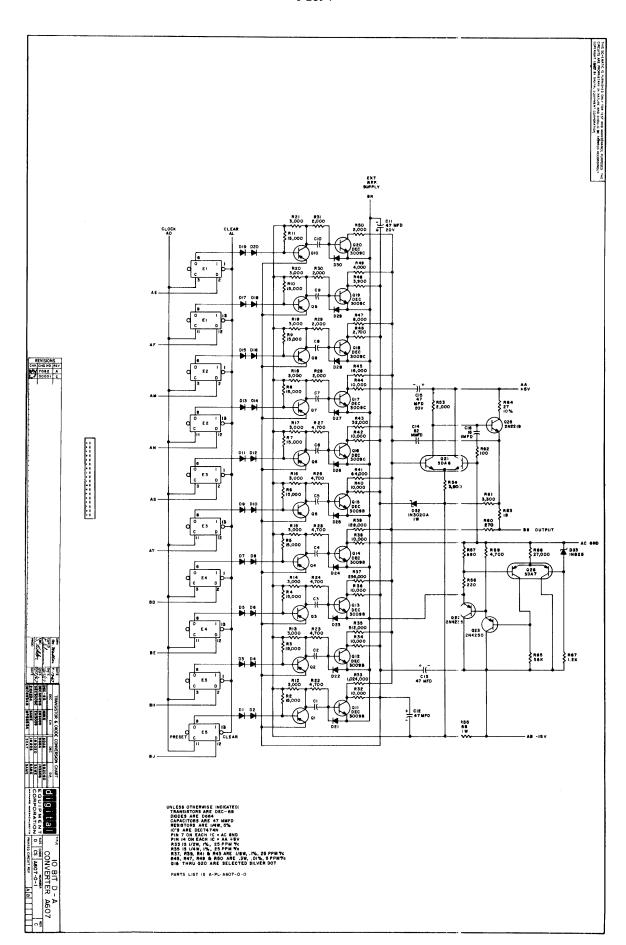

# A708 Dual Voltage Regulator

The A708 Dual Voltage Regulator is used in the AD15 Analog Subsystem to provide regulated -15V and +5V output voltages.

In the -15V regulator circuit, Q3 and Q4 control the forward bias on series regulator Q5 to maintain the -15V output within  $\pm 1\%$ . In the +5V regulator, any change in the +5V output is sensed at the base of Q2, which controls forward bias on Q1 to maintain the +5V output with  $\pm 5\%$ .

**INPUTS**: Less than 20 mV ripple.

-20V, ±1%, 0.25A max. Pin N2 +15V, ±1%, 1.25A max. Pin E2, V2

**OUTPUTS**: -15V, ±0.5%, 0.2A max. Pin S2

+5V,  $\pm1\%$ , 1.2A max. Pin A2

### **A877**

### **Analog-to-Digital Converter**

The A877 Analog-to-Digital Converter is used in the AD15 Analog Subsystem to convert the A405 Sample and Hold Amplifier output to a 13-bit digital word (12 bits plus a sign bit). A comparator amplifier compares the analog input voltage with a programmed sequence of internally-generated reference voltages to determine the polarity and amplitude of the input signal. The result is stored in a 13-bit data register. An A/D DONE signal is provided when the conversion is complete.

#### MAINTENANCE NOTE

The A877 uses special matched components to achieve specified measurement accuracy. If a fault is isolated to the A877, do not attempt to replace components in the field. Substitute a spare module and return the faulty module to DEC for service.

ANALOG INPUT SIGNAL: Full

Full scale range: ±10V

Connections: Single-ended Impedance: 28K ohms

Overvoltage limit: ±15V, maximum

Settling time:  $1 \mu s$

**ENCODING PROCESS:**

Digitalizing resolution: 1 part in 8,190 (2.5 mV)

Encoding word time:  $36 \mu s$ , typical Encoding word rate: 28,000s, typical Code: Parallel, binary 2's complement

**MEASUREMENT ACCURACY:**

Full range: 0.015%

Temperature coefficient: ±0.0020%/°C (over full operating

temperature range)

**CONTROL SIGNALS:**

Input: Command to Convert (CTC) initiates encoding process

on a logic 1-to-0 transition

Output: End of Conversion (EOC) pulse is 100 ns logic 1 pulse

DATA OUTPUTS:

13 bits, held in storage until next CTC input.

**POWER REQUIREMENTS:**

+15V, ±5%, 100 mA, typical, pin AD -15V, ±5%, 50 mA, typical, pin AE +5V, ±10%, 400 mA, typical, pin BA

### CONNECTOR PIN ASSIGNMENTS

| Pin                                                        | Function                                                                                     | Pin                                                         | Function                                                                                                   |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| AD1/2<br>AE1/2<br>AF1/2<br>AJ2<br>AK2<br>AU1<br>BA2<br>BC2 | +15V -15°V +15 V Common Analog Input Analog Return Command to Convert (CTC) +5V Logic Ground | BL2<br>BM2<br>BN2<br>BP2<br>BR2<br>BR2<br>BS2<br>BT2<br>BU2 | Function  Data Bit 4  Data Bit 5  Data Bit 6  Data Bit 7  Data Bit 8  Data Bit 9  Data Bit 10  Data Bit 11 |

| BE2<br>BF2<br>BJ2<br>BK2                                   | Sigr Bit, Complemented Sigr Bit Data Bit 2 Data Bit 3                                        | BV2<br>BJ1<br>BF1                                           | Data Bit 12 Data Bit 13 (LSB) End of Conversion (EOC)                                                      |

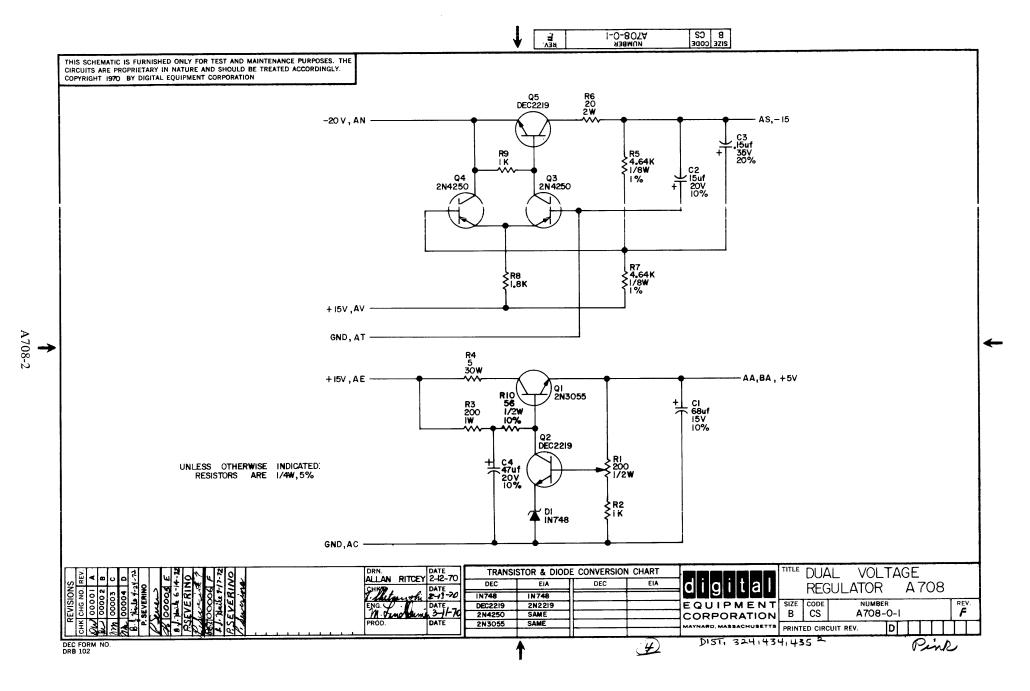

### ADJUSTMENT AND CALIBRATION

#### NOTE

Do not attempt to adjust any potentiometers other than the reference, gain, and zero adjust potentiometers at the rear of the module (see illustration).

Adjust the A877 while it is installed in slot C11 of the AD15. Remove the A405 module and allow 15 minutes warmup.

### Reference Voltage Adjustment

Use Fluke 585A voltmeter (or equivalent voltmeter with 0.005% accuracy) to measure voltage between +10V test point (red) and ground (black). Adjust reference potentiometer (top) to obtain 10.000V, ±1 mV.

### Gain Adjustment

Connect EDC voltage standard (or equivalent voltage standard with 0.005% accuracy) between pins C11J2 and C11F2 (See drawing D-AD-7007029-0-0 in AD15 manual).

Run MAINDEC-15-D6GA-D(I), with any channel and gain setting. Adjust the EDC to find the most positive switching point (007776-007777). Record the voltage. Reverse

the polarity of the EDC connections to find the most negative switching point. Record the voltage. The difference between the voltages should be 19.9995V,  $\pm 2$  mV. Adjust the gain potentiometer and repeat these measurements until the difference is within the specified tolerance.

#### Zero Adjust

Short-circuit pins C11J2 and C11F2 and note the conversion value. If the reading is outside the range 77776-000002, adjust the zero adjust potentiometer (bottom) to bring it within range. This adjustment interacts with the gain adjustment and several passes may be required to bring both adjustments within their specified tolerances.

## G085 Disk Read Amplifier

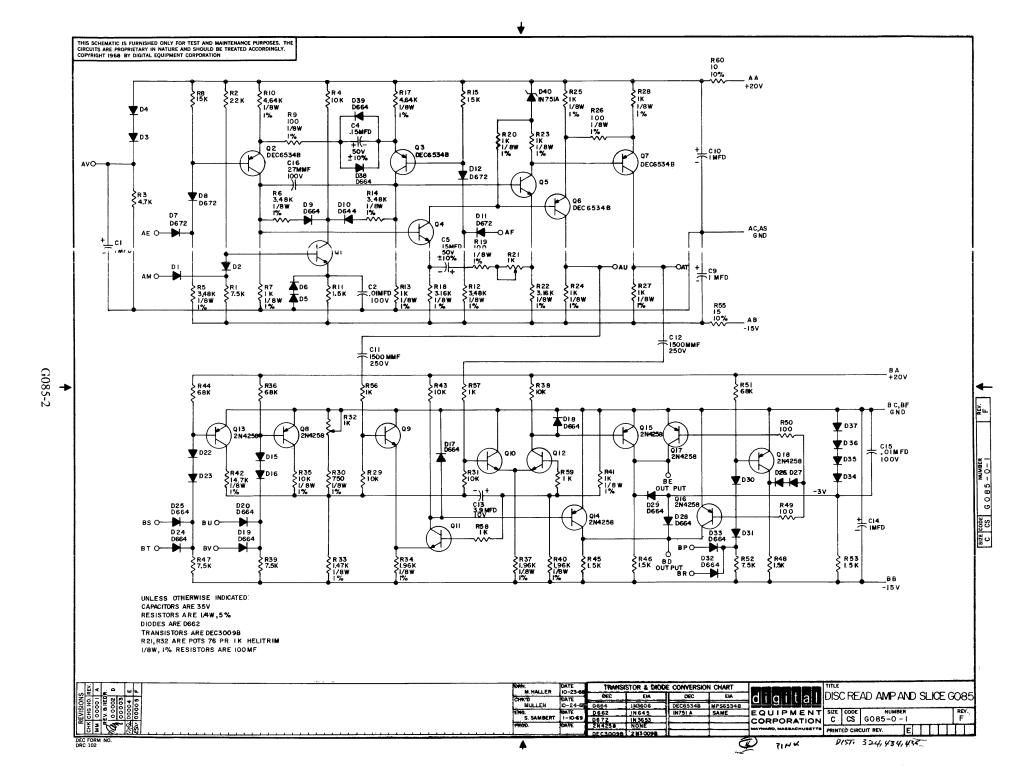

The G085 Disk Read Amplifier is a double-height module consisting of an ac-coupled amplifier with a bandwidth (-3 dB) from 20 kHz to approximately 1 MHz, followed by a slicer. The G085 module is used to detect and amplify timing tracks and data signals for the RS09 DECdisk. The maximum voltage gain (under potentiometer control) is approximately 60 dB (1000). Common mode rejection ratio is approximately 40 dB. The amplifier is insensitive to any power supply ripple voltage less than 5 percent. Pin AM increases the gain by approximately 20 percent when its input is low. The nonrectified slice output is gateable, and the slice point can be varied by logic inputs. A potentiometer is provided to adjust the slice. Pins at AT and AV are provided as amplifier test points. Proper grounding is critical in this module. G085 ground pins should not be bussed. Pins AS and AC should be connected to analog ground, and BF and BC should be connected to logical ground. All amplifier connections must be isolated from fast rise-time signals.

| X. | N. T | DI | רו  | rc |   |

|----|------|----|-----|----|---|

| 1  | N    | PΙ | , , |    | Ξ |

Voltage levels are 0 and -3V, except at the input to pins AE and AF.

| Pin   | Function           | Load or Input Voltage      |

|-------|--------------------|----------------------------|

| AE,AF | Read Head Input    | approx. 15 mV peak-to-peak |

| AM    | Read Gain Control  | 2 mA                       |

| BU,BV | Read Slice Control | 2 mA                       |

| BS,BT | Read Slice Control | 2 mA                       |

| BP,BR | Enable Output      | 2 mA                       |

### **OUTPUTS**:

Voltage levels are 0 and -3V except at AV, which provides +20V for the timing track center taps.

| Pin   | Function      | Drive |

|-------|---------------|-------|

| BE,BD | Signal Output | 10 mA |

INPUT/OUTPUT DELAY: 120 ns

POWER DISSIPATION:

2W at +20V 1.5W at -15V

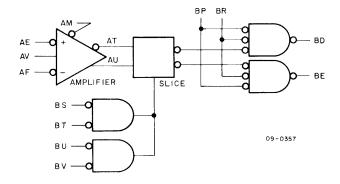

G085 Disk Read Amplifier and Slice, Block Schematic

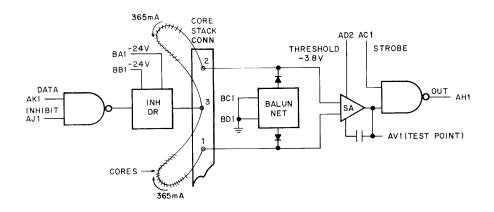

## G100 Sense Amplifier and Inhibit Driver

The G100 module contains four sense amplifiers and four inhibit drivers. Five of these modules are used in the PDP-15 for each 4K memory stack. (Refer to Engineering Drawings D-BS-MM15-0-10 through D-BS-MM15-0-15). Each inhibit driver consists of a two-input NAND gate and a high-speed current switch. One driver is used for each bit plane of the memory array. An inhibit signal is received by all inhibit drivers only during a write operation.

G100 Simplified Diagram

Each driver also receives a signal indicating the state of the corresponding bit in the MB. Inhibit drivers that receive a signal indicating a 0 state in the MB bit are gated on and cause inhibit current to be applied to the associated bit plane of the memory array. Each inhibit driver employs a discharge network to speed up inhibit current cut-off. The output of the inhibit driver is connected to the middle of one core sensing string, which represents one bit plane of the memory array. The balun network at the front end of the sense amplifier ensures equal current at all times through both sides of the core string. In addition to the balun network, the sense amplifier consists of a differential amplifier and output driver. One sense amplifier is used for each bit plane of the memory array. During a read operation only the signal induced on the sense winding of a core plane by a core-changing state is received by the differential amplifier. The differential amplifier has a nominal threshold of 17 mV. Output pulses of standard amplitude and duration are supplied by the output driver when the sense amplifier reads a logic 1 from the associated core, which in turn is strobed by a standard positive going pulse at AC1. Propagation delay from the input to the sense amplifier to the buffered output is 25 ns (maximum) and from strobe input to buffered output is 15 ns (maximum). These output pulses are used to direct set the MB register.

The following are the input, output, and power characteristics of the G100 module.

INPUTS: Inhibit driver DATA inputs present 1.25 TTL unit loads and INHIBIT inputs present 5 unit

loads. Sense amplifier inputs are 0-9 mV for a logic 0 and 31-35 mV for a logic 1.

**OUTPUTS**: Inhibit driver inhibit current is 730 mA.

POWER: Power dissipation of the G100 module is +5V at 130 mA (maximum), -6V at 60 mA

(maximum), and -24V at 800 mA (maximum).

This page intentionally left blank.

1

ja.

DIST, 324, 474, 4252

× 4

\_1

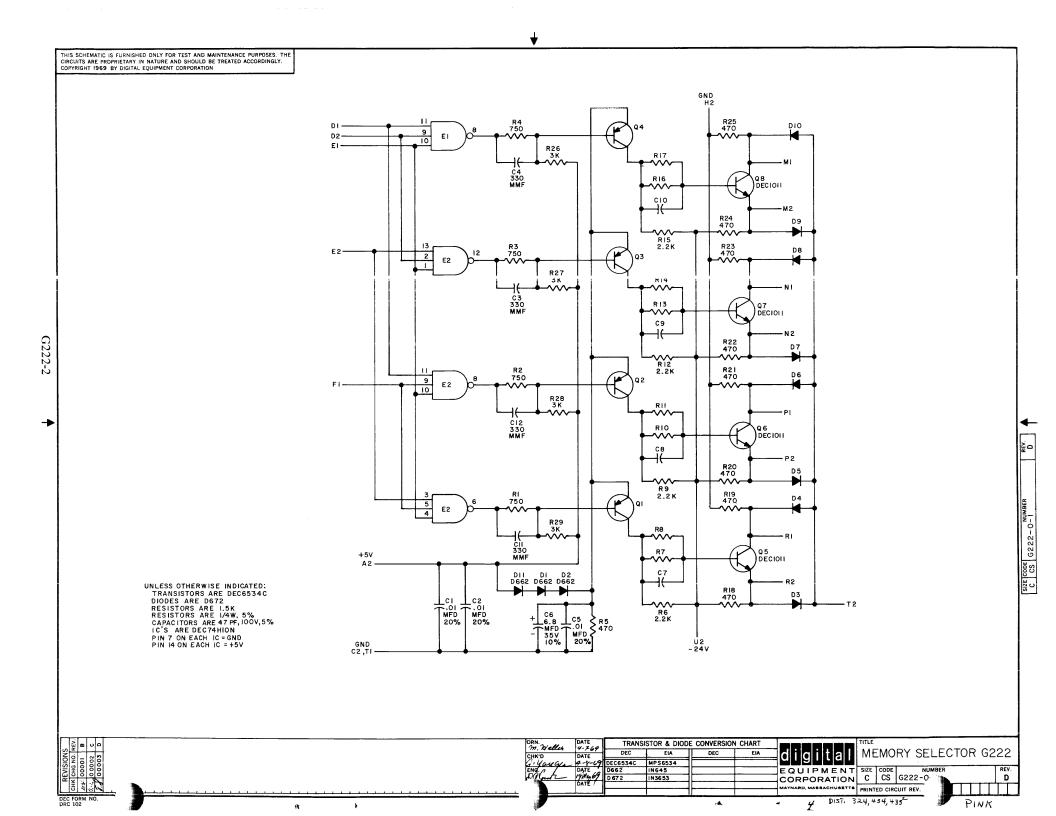

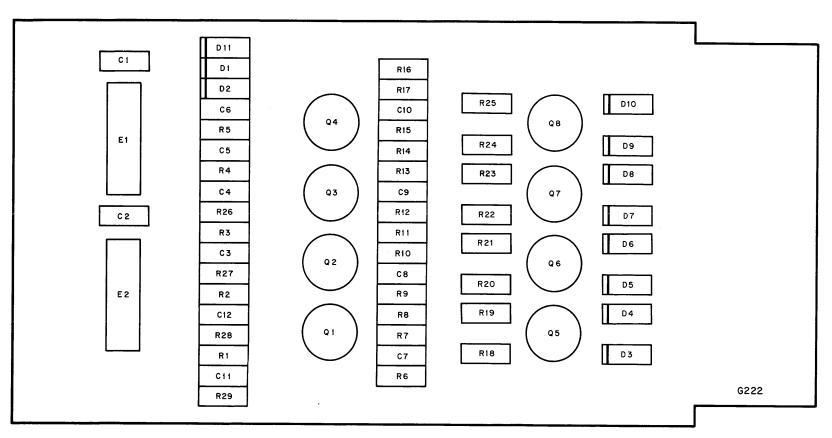

## G222 Memory Selector

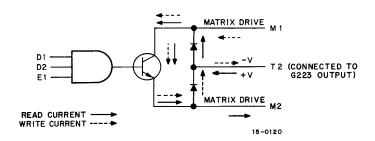

The G222 module contains four memory selectors. Eight of these modules are used in the PDP-15 for each 4K memory stack. (Refer to Engineering Drawings D-BS-MM15-0-6 and D-BS-MM15-0-7.) The modules are used to decode the memory address to obtain the X- and Y-axis select signals for accessing the core memory. Each memory selector consists of a 3-input NAND gate and a bidirectional current switch network for both read and write current. An 8 x 8 matrix (see G613 and G614) is used for each of the X and Y selection paths. Thus, two switches must be energized to establish the path in the X plane, and another two switches must be energized to establish the path in the Y plane. In a 4K system a total of four G222 modules are used to decode the first six bits of the memory address. This provides one out of 64 states for the Y plane. Similarly, four G222 modules are used to decode the remaining six bits of the memory address in order to establish the selection path in the X plane.

G222 Simplified Diagram

The following are the input and output characteristics of the G222 modules.

**INPUTS:** Each NAND gate input presents 2.5 TTL unit loads.

**OUTPUTS:** Each matrix selector switch handles 400 mA (typical).

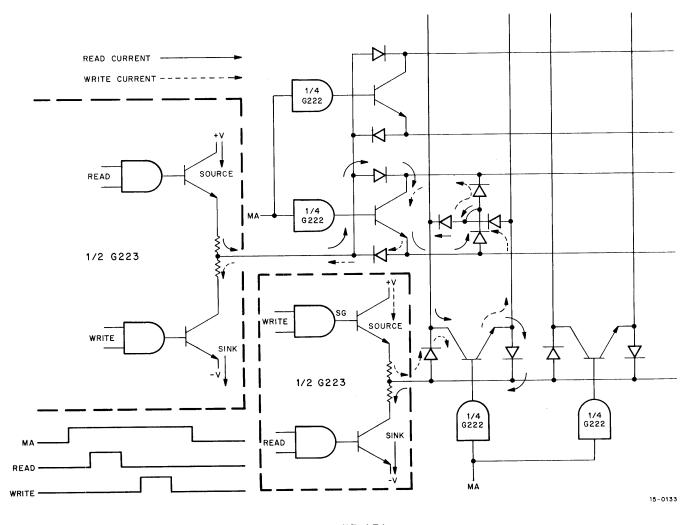

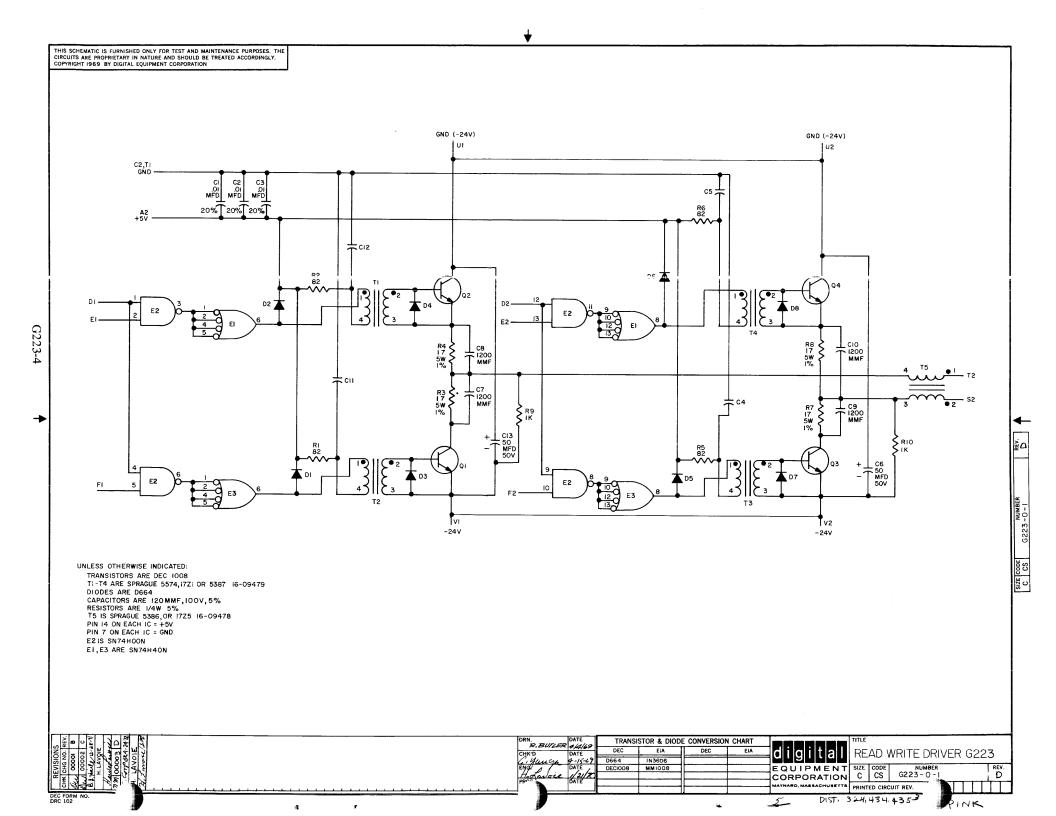

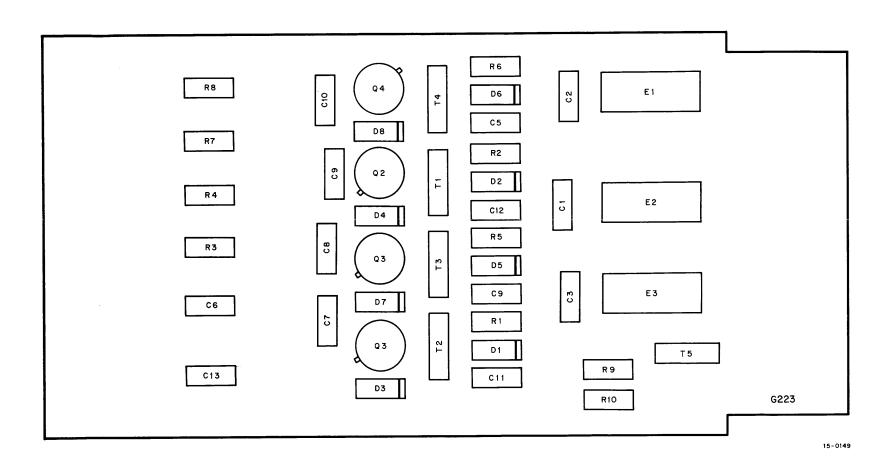

# G223 Read/Write Driver

The G223 module contains two read/write drivers. Two of these modules are used in the PDP-15 for each 4K memory stack; one provides the drive for the X plane and the other provides the drive for the Y plane. (Refer to Engineering Drawings D-BS-MM15-0-6 and D-BS-MM15-0-7.) The G223 and G222 modules work together (see illustration) in that the current path selection through the core memory is established by the G222 modules, and

G223 Simplified Diagram

the drive current for reading and writing is supplied by the G223 module. Reading and writing currents travel in opposite directions. Each read/write driver consists of two input control NAND gates and two current switches connected in series with a common output. The read and write commands and the page select command are applied to the input control NAND gates, turning on the corresponding current switches and establishing a current path from ground to -24V. The balun network at the output of the driver ensures equality of input and output current through the stacks at all times.

The following are the input and output characteristics of the G223 module.

INPUTS: The READ and WRITE inputs (pins E1 and F1) each present 1.25 unit loads. The page-

select input (pin D1) presents 2.5 unit loads.

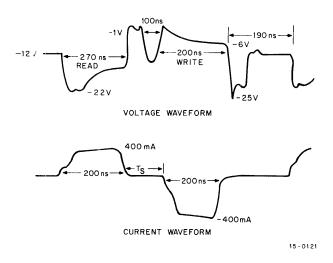

OUTPUTS: The measured read/write voltage waveform and its current waveform for the worst

case pattern take the form shown below for an 800 ns memory cycle time.

G223 Current and Voltage Waveforms

The current-rise time to get to 400 mA for both reading and writing is approximately 100 ns, while the fall time is 40 ns. The stagger time (Ts) between read and write currents is approximately 130 ns.

This page intentionally left blank.

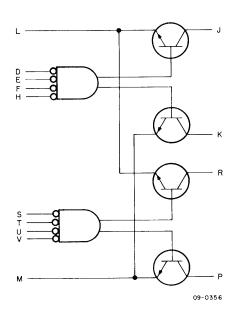

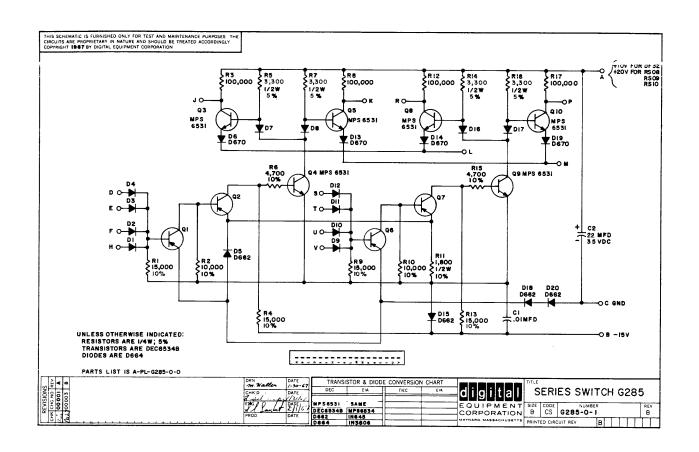

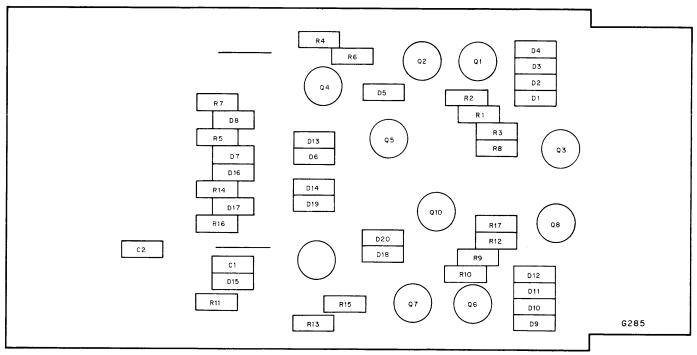

## G285 Series Switch

The G285 Series Switch is a single-height module consisting of two 4-inch AND gates, each driving the base of two driver transistors. This series switch is used together with the G290, the G286, and the G085 to form the Read/Write head matrix in the RS09 DECdisk. When a gate is enabled, it in turn switches its corresponding transistors that form part of the select and read/write matrix of the disk or memory.

INPUTS:

Voltage levels to the gates are 0 and -3V. In levels to the signal inputs

L and M are 0 and -15V.

| Pin       | Function             | Load              |

|-----------|----------------------|-------------------|

| D,E,F,H,S | Gate Enabling Inputs | 1 mA shared among |

| T,V,M     |                      | inputs at ground  |

| L,M       | Signal Inputs        |                   |

**OUTPUTS**:

Voltage levels are 0 and -15V (i.e., the input signal gated through the transistor). Each switch pole can drive up to 150 mA. Reverse voltage transients up to 100V do not destroy the switch circuits. Output pins J, K, R, and P must be returned through the load to +10V. The common pins (L and M) to both sets of switches must be returned to -15V. The switches will pass 1 MHz current. The voltage drop for 100 mA is approximately 1V.

INPUT/OUTPUT DELAY:  $1 \mu s$ POWER DISSIPATION: 1.5W

09-0391

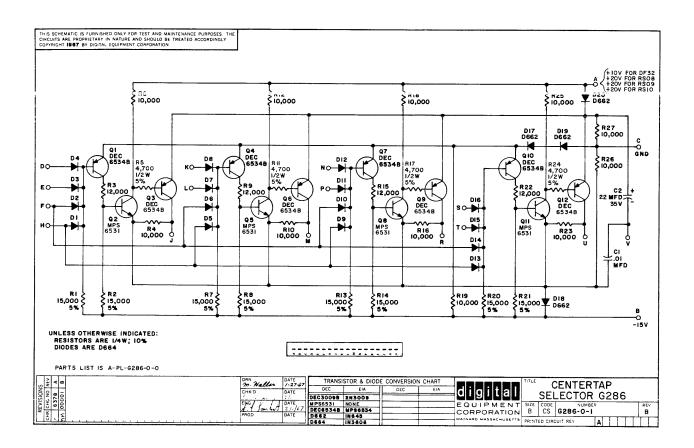

#### **G286**

## **Center Tap Selector**

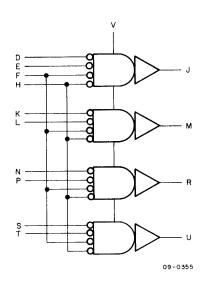

The G286 Center Tap Selector is a single-height module consisting of four AND gates, each of which drives a power output stage that applies a +20V level to its output pin when enabled by the gate. This module supplies the +20V read/write level to the coil of each head it drives in the RS09 DECdisk Read/Write matrix.

| T | N | D | П | 1 | 2 |  |

|---|---|---|---|---|---|--|

|   |   |   |   |   |   |  |

Voltage levels are 0 and -3V.

| Pin          | Function    | Load                |

|--------------|-------------|---------------------|

| D,E,K,L,N,P, | Gate inputs | 1 mA shared among   |

| S,T,F,H      | Gate inputs | inputs at ground in |

|              |             | each circuit        |

**OUTPUTS**:

Each output is +20V when the AND gate is enabled and 0V when the gate

is not enabled. Each output drives 150 mA at +20V.

**INPUT/OUTPUT DELAY:** 500 ns **POWER DISSIPATION:** 1.4W

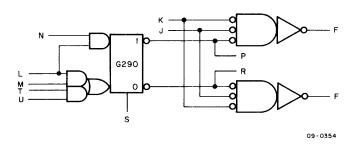

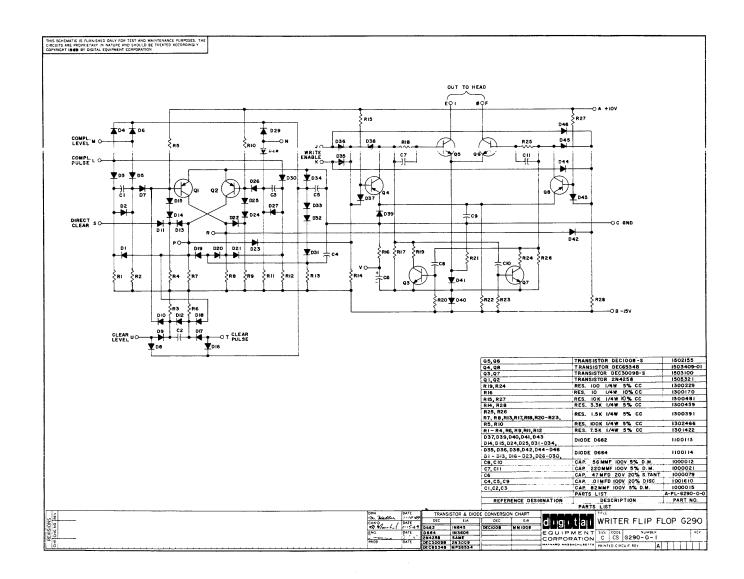

# G290 Writer Flip-Flop

The G290 Writer Flip-Flop is a single-height board containing one JR flip-flop driving two AND gates and two power drivers. This module, used in the RS09 DECdisk supplies the -15V write voltage to the G285 Series Switch. There are several gates to the input of the flip-flop.

**INPUTS:** Voltage levels are 0 and -3V.

| Pin      | Function             | Load                |

|----------|----------------------|---------------------|

| N,M,T,U, | Inputs to flip-flop  | Each gate is a 1 mA |

| L        | Input to flip-flop   | load shared among   |

| S        | Direct Clear         | its grounded inputs |

| K,J      | Enable input to out- | •                   |

|          | put driver gate      |                     |

OUTPUTS: The E and F outputs are -15V or an open collector. The P and R outputs

are 0 and -3V.

| Pin | Function                     | Drive  |

|-----|------------------------------|--------|

| E,F | Output to G285 Series Switch | 150 mA |

| P,R | Test output of flip-flop     | 10 mA  |

INPUT/OUTPUT DELAY: 90 ns POWER DISSIPATION: 1W

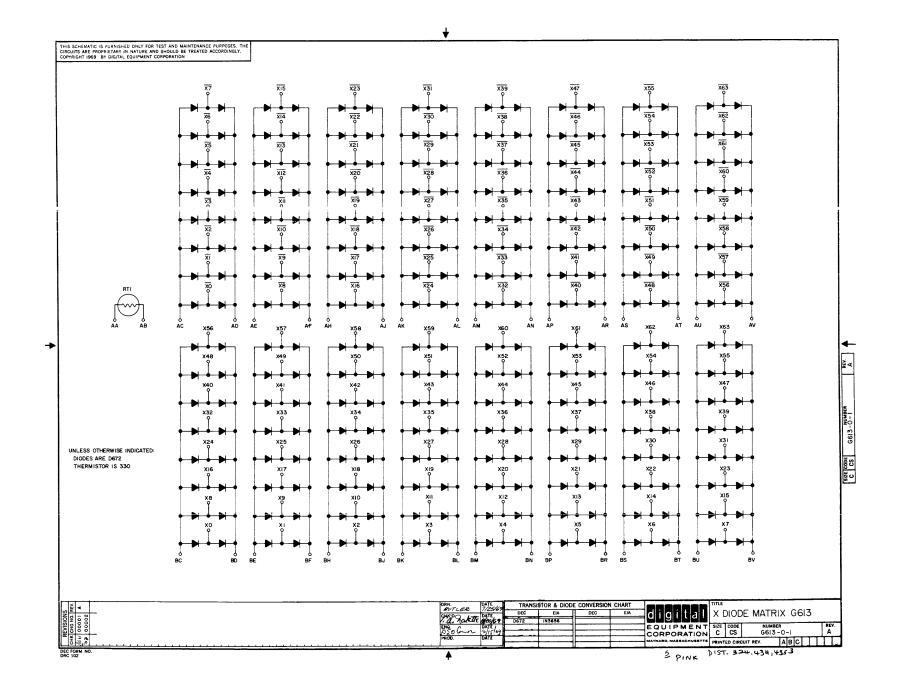

### G613 X Diode Matrix

The G613 module contains 256 diodes connected to form an 8 x 8 two-way crosspoint switching matrix that provides 64 pairs of interconnecting points. (Refer to Engineering Drawings D-BS-MM15-0-6 and D-BS-MM15-0-7.) Sixty-four cores from each of the 18 memory planes are connected between each pair of interconnecting points, thereby creating the current paths of the X-axis in the core memory stack. A thermistor is also included in the G613 module to control the read and write currents in response to temperature changes.

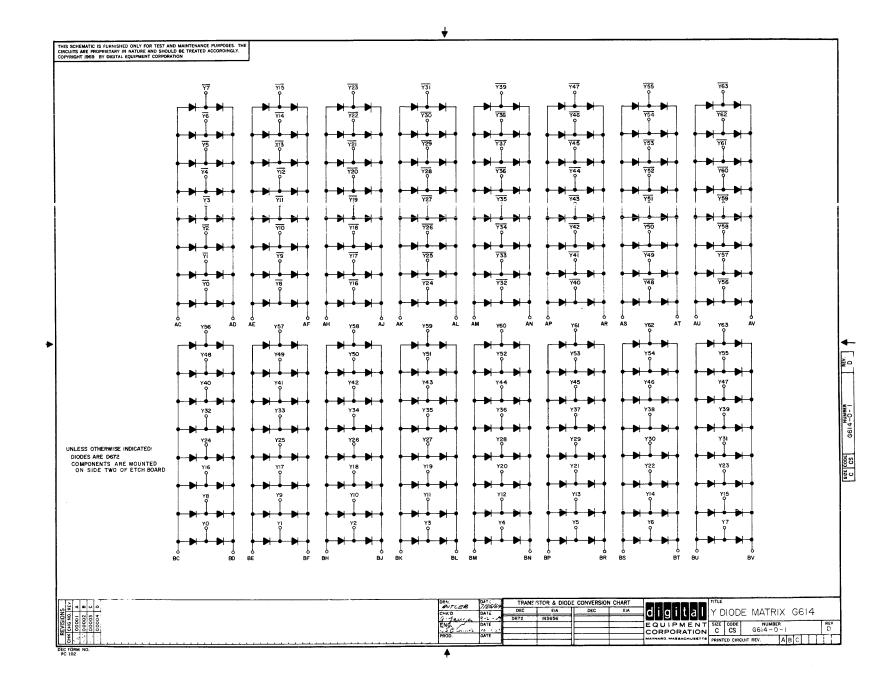

### G614 Y Diode Matrix

The G614 module contains 256 diodes connected to form an 8 x 8 two-way crosspoint switching matrix providing 64 pairs of interconnecting points. (Refer to Engineering Drawings D-BS-MM15-0-6 and D-BS-MM15-0-7.) Sixty-four cores from each of the 18 memory planes are connected between each pair of interconnecting points, thereby creating the current paths of the Y axis in the core memory stack.

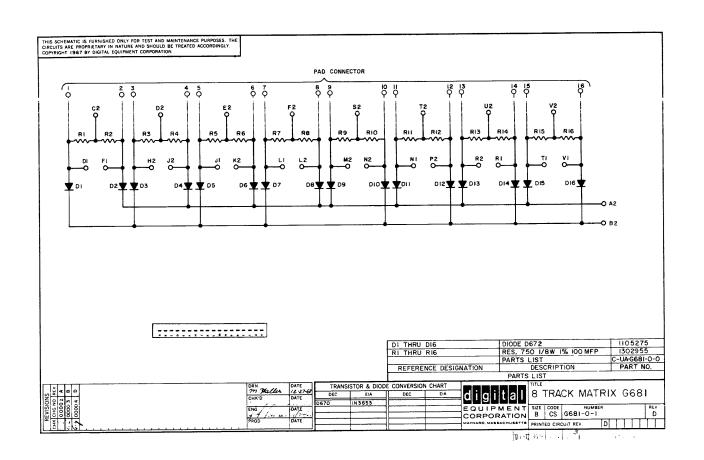

## G681,G711,G775 DECdisk Modules

#### 1. G681 8 TRACK MATRIX

The G681 Track Matrix is a single-height board containing the resistors and diodes for eight DECdisk read/write heads.

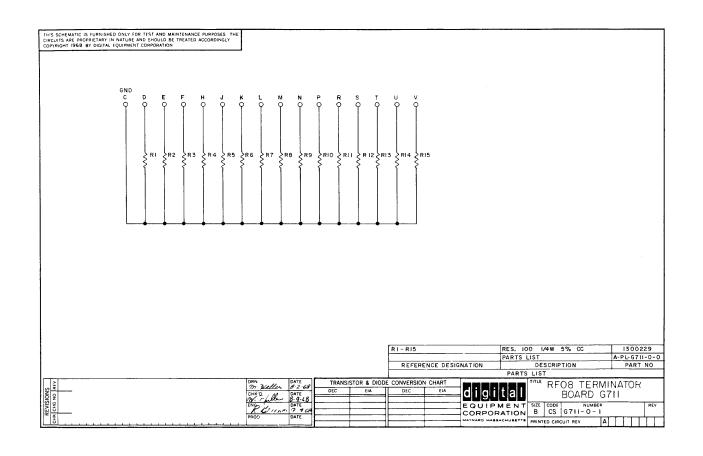

#### 2. G711 RF08 TERMINATOR BOARD

The G711 RF08 Terminator Board is a single-height board containing 15 terminating resistors that present  $100\Omega$  to ground at each input pin. This board must connect to the output cable slot of the last RS09 on each DECdisk cable bus.

**INPUTS:**

$100\Omega$  to ground

**OUTPUTS:**

None

POWER DISSIPATION:

Approximately 90 mW per terminator

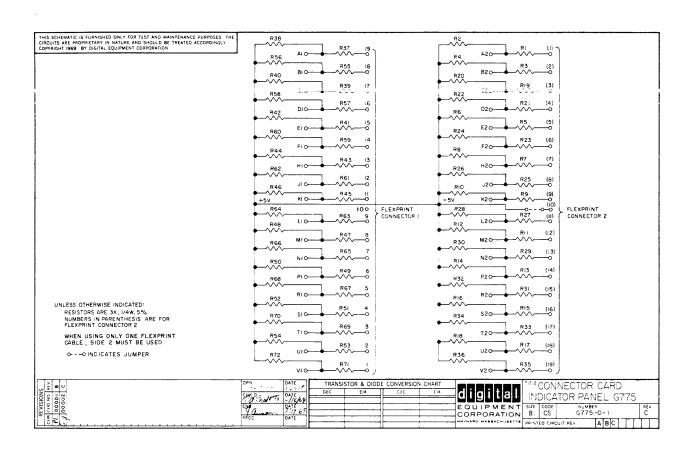

#### 3. G775 INDICATOR PANEL

The G775 Indicator Panel is a connector card that provides isolation for logic levels and allows these levels to directly drive indicator bulbs without using light drivers. The connector is designed to be used with the indicator panel, which supplies the necessary bias voltage.

**INPUTS**:

All inputs are 0 and -3V with 3 units of load each.

OUTPUTS:

The output connects a Flexprint cable to the indicator board.

POWER DISSIPATION:

150 mW

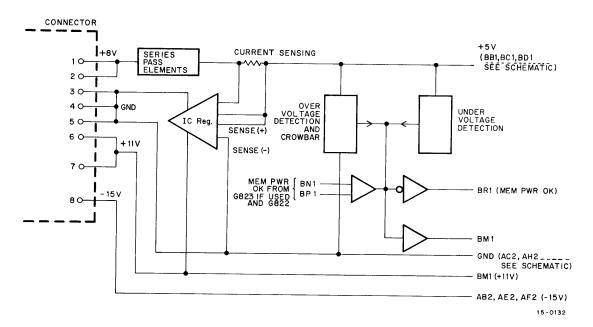

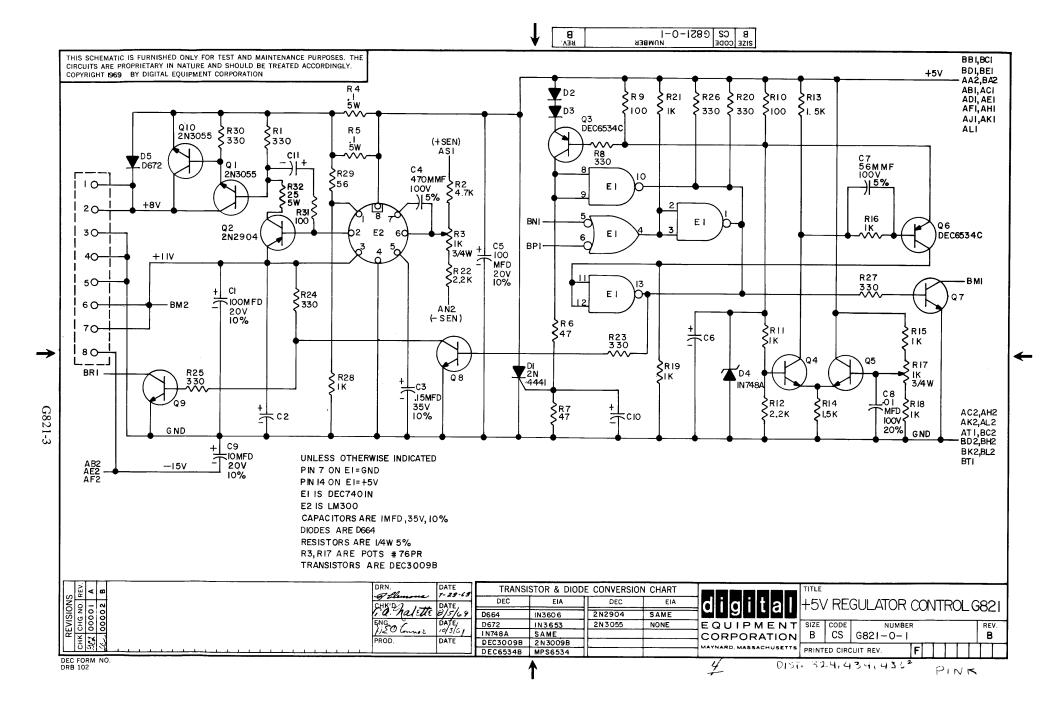

### G821 +5V Regulator

The G821 module contains a voltage regulator with over-voltage, under-voltage, and over-current protection circuits. This module supplies the regulated +5V in the memory of the PDP-15. Combinational logic circuits are also included in the module to provide lamp driver and memory power OK signals when the memory voltages are within set levels. The input power connections to the module are made with an 8-pin mate-in-lock connector at the back of the module.

The following are the input and output characteristics of the G821 module.

INPUTS:

The inputs to the G821 module are +8V, +11V, -15V, and ground. These voltages are supplied by the 715 power supply. The module also receives positive level power OK signals from the G822 and G823 modules.

**OUTPUTS**:

The outputs of the G821 module are variable 4.5V to 5.5V at 7A (maximum)\* (when set at 5V, regulation is  $\pm 2\%$  with a ripple voltage of 25 mV peak-to-peak);  $\pm 11V$  at 1.0 amp (maximum) with the same regulation as the input voltage; and  $\pm 15V$  at 3.0 amps (maximum) with the same regulation as the input voltage.

G821 Simplified Diagram

\*The 7A rating is valid only when adequate fan cooling is used. Without additional coding, the output rating is 2A (maximum). The +5V potentiometer must be rotated clockwise to obtain a higher output voltage.

Additional outputs include an open collector lamp driver (output pin BM1) that is turned on when the 5V power is within set limits (by rotating the voltage detection potentiometer CCW, the low voltage limit decreases) and an open collector driver (output pin BR1) that is turned on only when the 5V power is not within set limits. Voltage limits are usually set at 4.75V by the voltage detection potentiometer, while the upper voltage detection level is set at 5.5V.

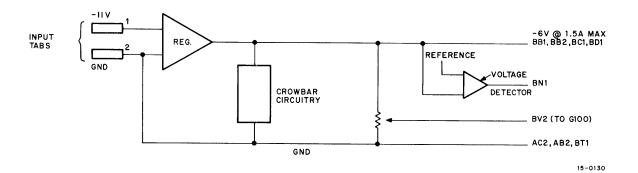

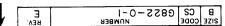

# G822 –6V Regulator

The G822 module contains a voltage regulator with an over-voltage protection circuit. This module supplies the regulated -6V in the memory of the PDP-15. A sensing circuit is also included on the module to provide a memory power OK signal when the output is more negative than -6.5V.

The following are the input and output characteristics of the G822 module.

**INPUTS:** The G822 module operates on 11V input power from the 715 power supply.

**OUTPUTS:** The outputs of the G822 module are:

- a. variable -5.0 to -7.0V at 1.5A. (When set at -6V, regulation is  $\pm 2\%$  with a ripple voltage of 50 mV peak-to-peak. The potentiometer must be rotated clockwise to obtain a more negative voltage setting);

- b. variable 0 to -6.0V used as the threshold voltage for the G100 module. (This voltage is nominally set at -3.8V. The potentiometer must be turned clockwise to obtain a more negative voltage setting);

- c. BN1, which is a TTL output that drops to ground when the -6V output voltage is more negative than -6.5V.

G822 Simplified Diagram

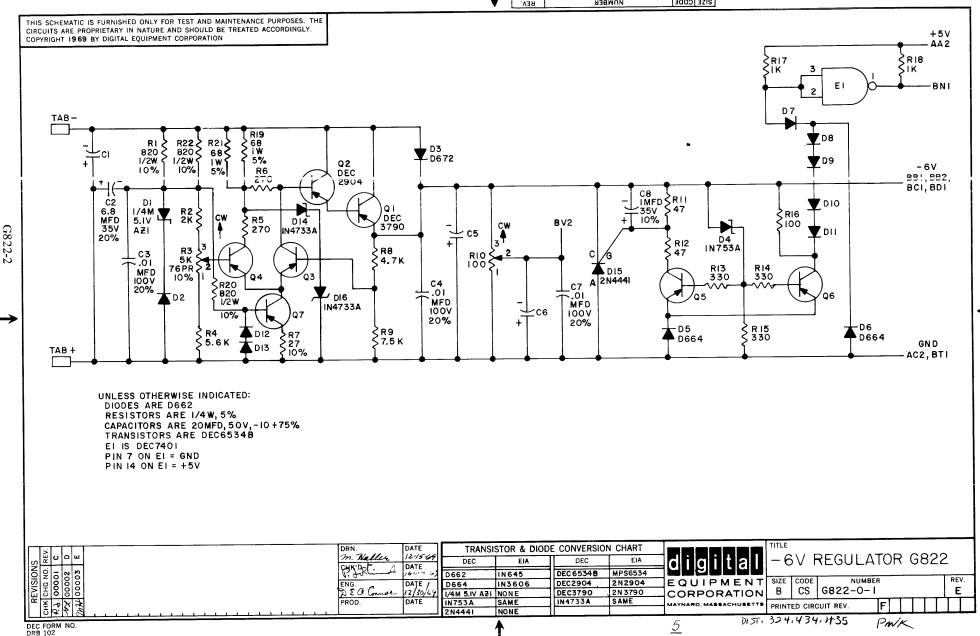

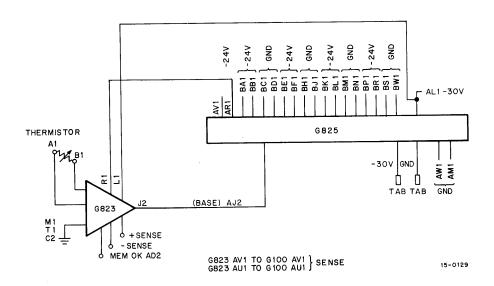

# G823 -24V Regulator Control

The G823 module contains a temperature-compensated voltage regulator control with an over-voltage protection circuit. This module is used in conjunction with the -24V pass element (G825) to supply a regulated -24V for the memory of the PDP-15 (see illustration). A thermistor mounted on the G613 module is connected to the -24V regulator control module to provide a negative temperature coefficient for controlling the regulated -24V. For a typical setting of -24V at 25°C and with an average output current of 4A, the output voltage changes to -22.4V at 50°C and to -25V at 0°C. The over-voltage protection circuit will disconnect the output above -26V.

The following are the input and output characteristics of the G823 module.

**INPUTS:** The G823 module receives -30V from the 715 power supply.

**OUTPUTS:** The outputs of the G823 module are:

- a. A variable -18V to -28V at 5.5A. When the module is set for -24V regulation, the output is ±1% with a ripple voltage of less than 50 mV peak-to-peak at full load. Rotating the potentiometer CCW provides a more negative voltage setting.

- b. An open collector driver (output pin N1) that supplies a memory power OK signal when the regulator control is operating properly.

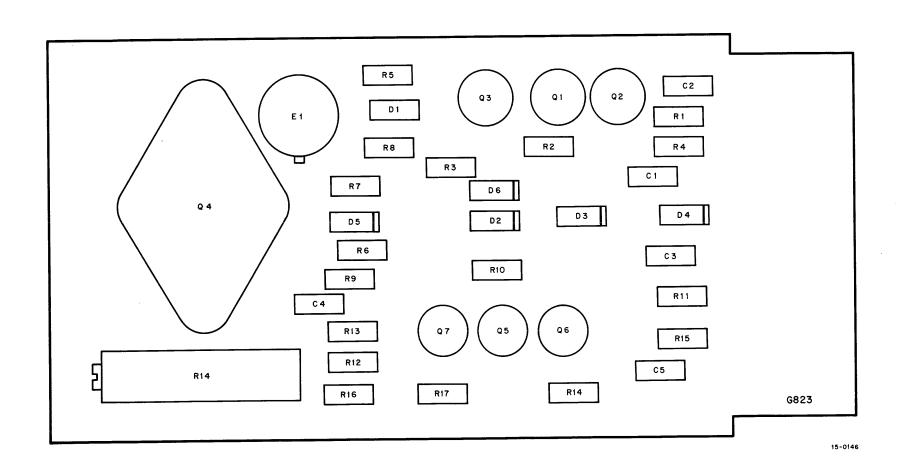

G823 Simplified Diagram

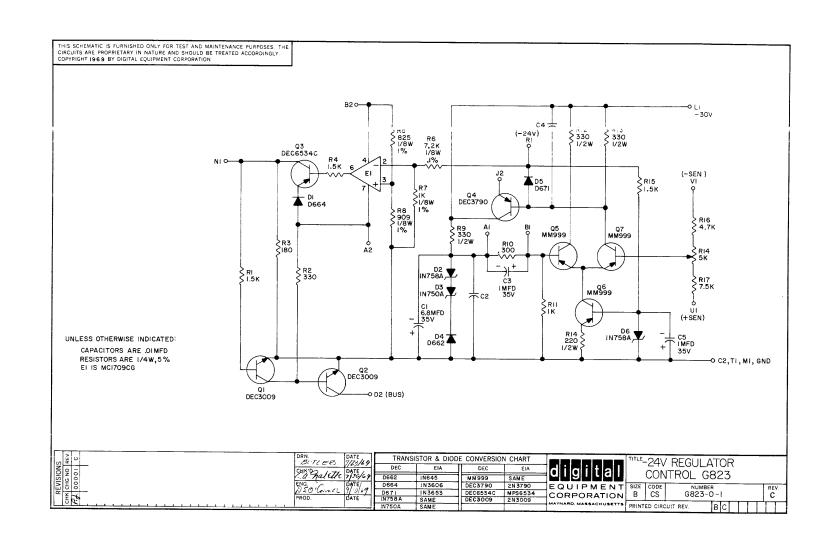

## G825 -24V Pass Element

The G825 module contains the power stage of the -24V regulator, which is controlled by the -24V regulator control module G823 to supply the regulated -24V for the memory of the PDP-15. Refer to the description of the G823 module.

THIS SCHEMATIC IS FURNISHED ONLY FOR TEST AND MAINTENANCE PURPOSES. THE CIRCUITS ARE PROPRIETARY IN NATURE AND SHOULD BE TREATED ACCORDINGLY. COPYRIGHT 1969 BY DIGITAL EQUIPMENT CORPORATION TAB -30V -O ALI - CI 50MFD + 50V 10% AJ2 O--O AV 2 ABI O-}R2 }.1 }R3 |,5K }.I OBF I,BKI,BLI,BPI,BRI -24V -O AMI, AUI, BCI, BDI, BHI TAB C UNLESS OTHERWISE INDICATED: RESISTORS ARE 5W, 5% TRANSISTORS ARE DEC 3790-1 TRANSISTOR & DIODE CONVERSION CHART -24V PASS ELEMENT G825 PROD DATE EIA DEC 2N3790 EQUIPMENT SIZE CODE NUMBER CORPORATION B CS G825-0-1

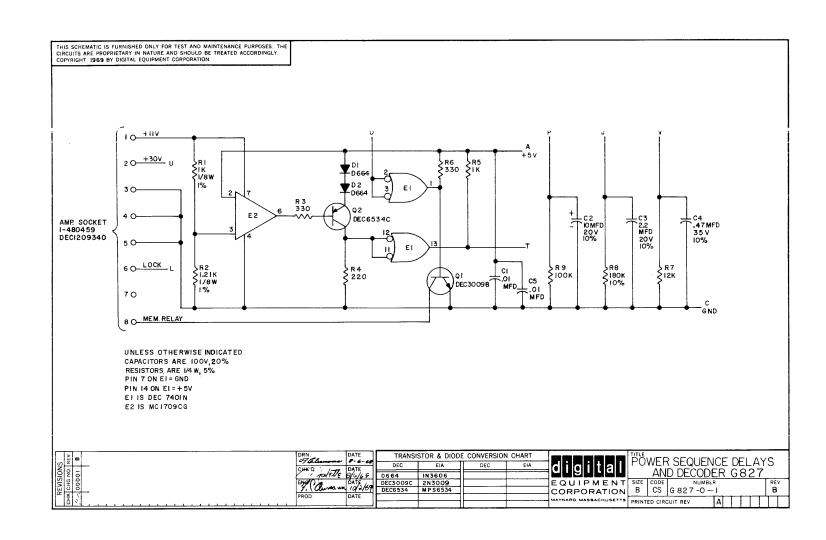

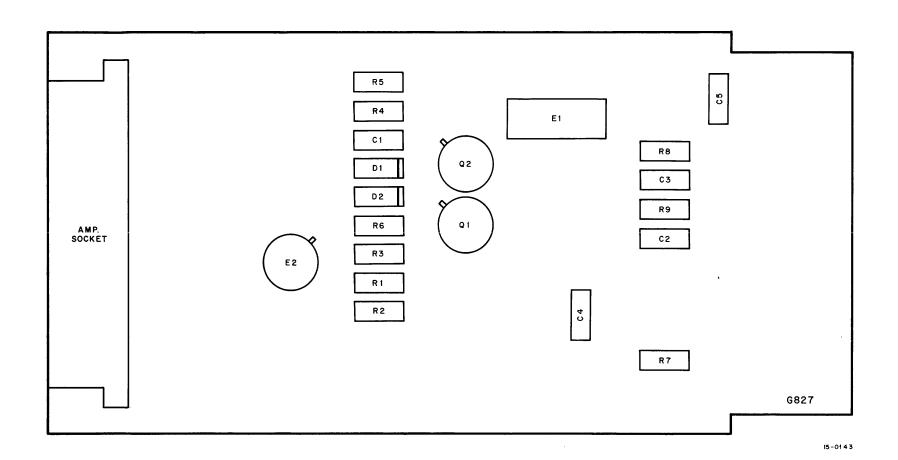

# G827 Power Sequence Detector and Delays

The G827 module contains a level detector, three RC networks, and an open-collector driver. This module is used in the I/O processor of the PDP-15. (Refer to Engineering Drawing D-BS-KP15-0-57.) The level detector is used to detect a power-low condition in the 11V supply and sequence the memory power off. The RC networks are connected to the K303 timers to establish the timer delays, and the open-collector driver is used to energize the memory power relay in response to the memory OK signal.

Power dissipation of the G827 module is 5V at 144 mA (maximum).

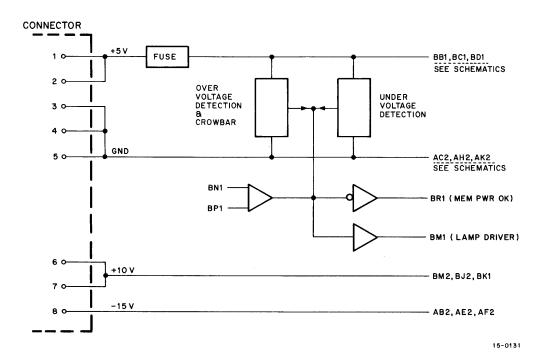

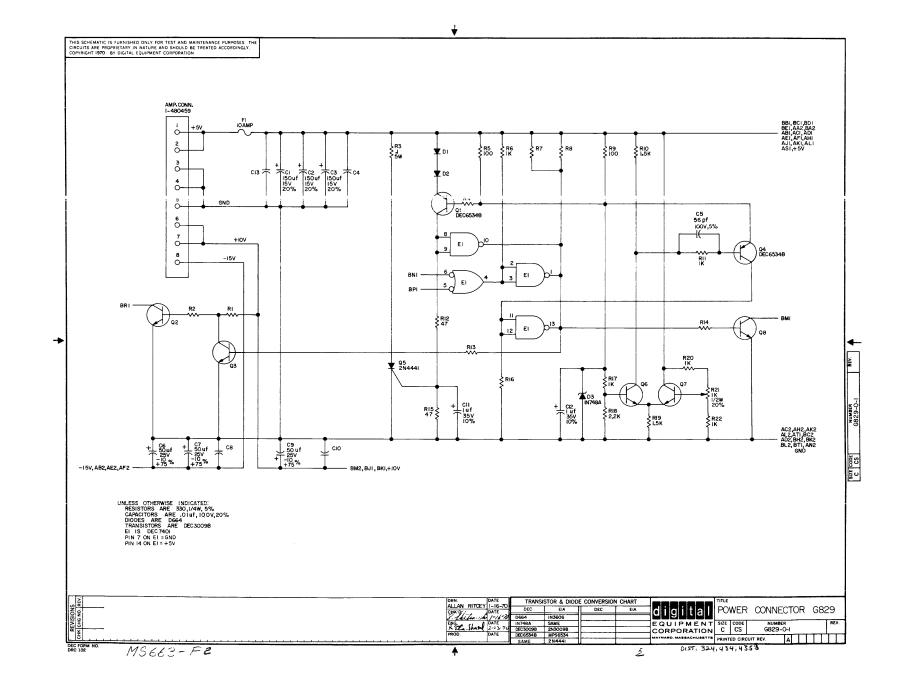

## G829 Power Connector

The G829 module is a power connector with over-voltage, under-voltage, and over-current protection circuits. This module connects the +5V to the peripherals of the PDP-15. Combinational logic circuits are also included in the module to provide lamp driver and power OK signals when the peripheral voltages are within set levels. Rotating the voltage detection potentiometer CCW lowers the low voltage limit. The potentiometer is normally set to detect voltage below 4.75V. The input power connections to the module are made with an 8-pin mate-in-lock connector at the back of the module.

The following are the input, output, and power characteristics of the G829 module.

**INPUTS:** The inputs to the G829 module are +5V, +10V, -15V, and ground. These voltages are sup-

plied by the 721 power supply. The module also receives positive power OK signals from

associated power supplies.

**OUTPUTS:** The outputs of the G829 module are:

a. +5V at 10A (maximum) with the same regulation as the input, +10V at 2.5A (maximum) with the same regulation as the input, and -15V at 3.5A (maximum) with the same regulation as the input;

G829 Simplified Diagram

THIS SCHEMATIC IS FURNISHED ONLY FOR TEST AND MAINTENANCE PURPOSES. THE CIRCUITS ARE PROPRIETARY IN NATURE AND SHOULD BE TREATED ACCORDINGLY. COPYRIGHT 1970 BY DIGITAL EQUIPMENT CORPORATION AMP. CONN. 1-480459 BBI, BCI,BDI BEI, AA2, BA2 ABI, ACI, ADI AEI, AFI, AHI AJI, AKI, ALI ASI, +5V FI IOAMP +5V R3 Siw \$ R7 ▼ Di CI C2 C3 ||50uf ||50uf ||50uf ||5V ||5V ||5V ||20% ||20% ||20% C13 7 **▼** D2 GND QI DEC6534B C5 56 pf ۳۵,۷۵۵۱ +IOV 0 Q4 DEC6534B -15V RII G829-2 ΕI ΕI RI4 ΕI RI3 R20 | K Q5 2N4441 Q3 + CII 1 u f 35 V 10% IN748A CI2 1 uf 35V 10% R15 ₹ RIS 2,2K ₹R19 \$1.5K ≯R22 ≯IK AC2,AH2,AK2 AL2,AT1,BC2 AD2,BH2,BK2 BL2,BT1,AN2 GND + C7 50 uf 25V -10 % +75% C9 50 uf 25V -10 % C8 CIO -15V, AB2, AE2, AF2 BM2, BJ1, BK1,+10V UNLESS OTHERWISE INDICATED:

RESISTORS ARE 330,1/4W, 5%

CAPACITORS ARE .01 ut, 1,0 V,20%

DIODES ARE D664

TRANSISTORS ARE DEC3009B

EI IS DEC740I

PIN 7 ON EI = GND

PIN 14 ON EI = +5V TRANSISTOR & DIODE CONVERSION CHART POWER CONNECTOR G829 DEC EIA EQUIPMENT SIZE CODE CORPORATION C CS NUMBER MAYNARD, MASSACHUSEYTS PRINTED CIRCUIT REV.

Rev.

DIST, 324, 434, 4352

(4)

This page intentionally left blank.

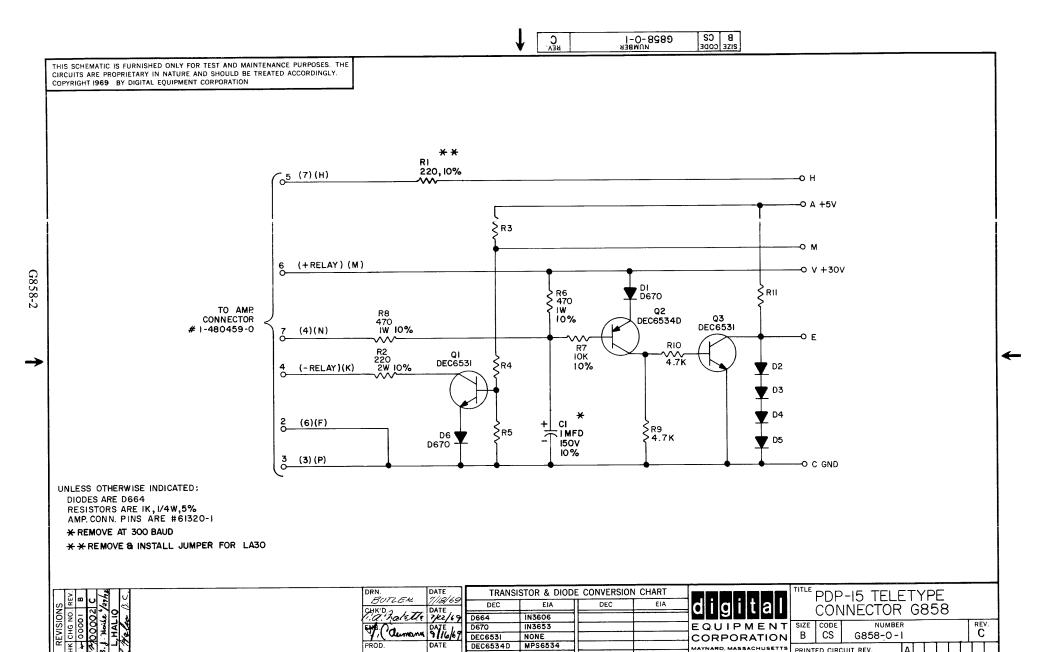

## G858 Teletype Connector

The G858 module contains a level converter, an open-collector driver, and interconnecting wiring. The module is used as a Teletype connector for the PDP-15, serving as the interface between the Teletype receiver/transmitter (M706 and M707) and the Teletype. The converter changes the 0V and +30V levels received from the Teletype to 0V and +3V levels for the receiver/transmitter, and the driver provides the reader run drive current for the Teletype.

The following are the input, output, and power characteristics of the G858 module.

**INPUT:** Input pin M2 (the reader run in) presents 4 unit loads.

**OUTPUT:** Output pin E2 (the Teletype keyboard in) is capable of driving 30 unit loads.

**POWER:** Power dissipated in the G858 module is 5V at 12 mA and 30V at 30 mA.

DIST. 324, 434, 4353 5

PRINTED CIRCUIT REV.

PINK

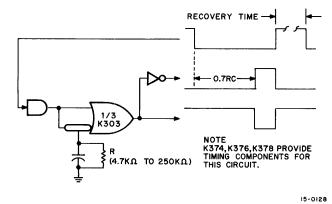

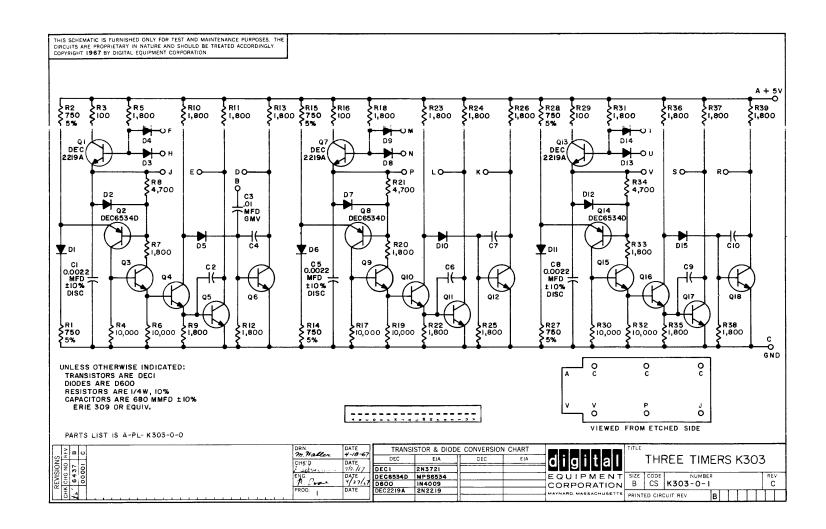

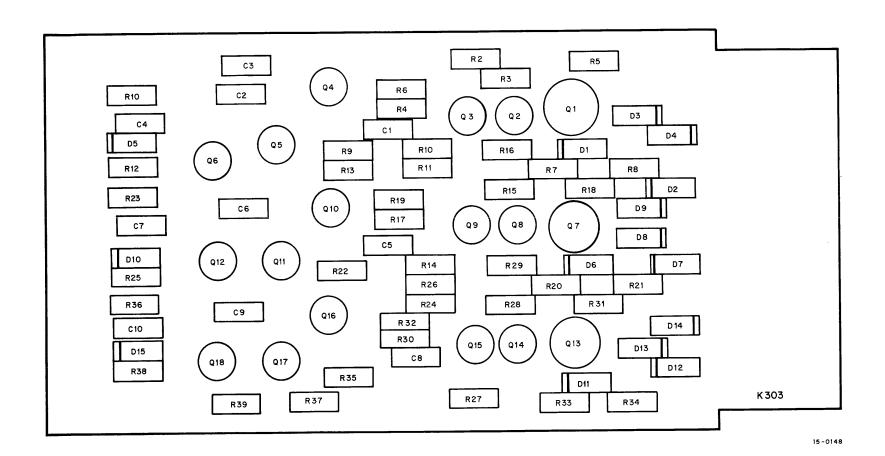

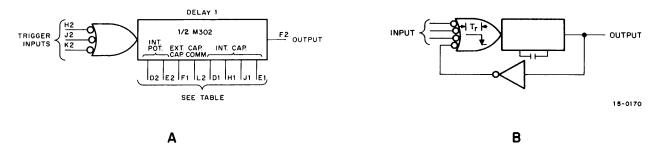

The K303 module contains three timers that are triggered by a level change from HIGH to LOW.

K303 timers provide time delays from  $10 \mu s$  to 30 sec and can be interconnected to form clocks with periods covering the same intervals. Fixed or adjustable delays and frequencies are obtainable. Calibrated controls are available (K371 through K378) for mounting directly on the K303. Remote controls can also be added, if desired.

When a K303 input gate steps to zero, the uninverted output falls after a controlled interval, while the inverted output rises (see simplified illustration). The interval can be as little as 10  $\mu$ s or as long as 30 sec, depending on the size of the R and C connected to pin J, P, or V. Recovery begins when the input gate rises to logic 1. A recovery time of at least 0.3 percent of the maximum delay obtainable from the capacitor is required in order to guarantee 95 percent repeat accuracy in the delay.

A positive step at the input gate resets the K303 timer outputs. If the step occurs before a timeout is complete, the timeout is terminated and no change appears at the outputs. This property is sometimes convenient for establishing a pulse repetition-rate threshold (frequency setpoint).

A built-in 2.2 nF timing capacitor assures adequate noise rejection when external capacitors are mounted several inches from the timer. Time threshold for resetting is always several percent of rated recovery time. Thus, noise rejection time increases in proportion to the size of the timing capacitor. If remote rheostats and timing capacitors are used, noise rejection is degraded. If several timing capacitors are to be switch selected, the smallest capacitor is wired near the module; and the other capacitors are switched in parallel with it.

For additional information, refer to DEC's Digital Logic Handbook, 1970 edition.

K303 Simplified Diagram

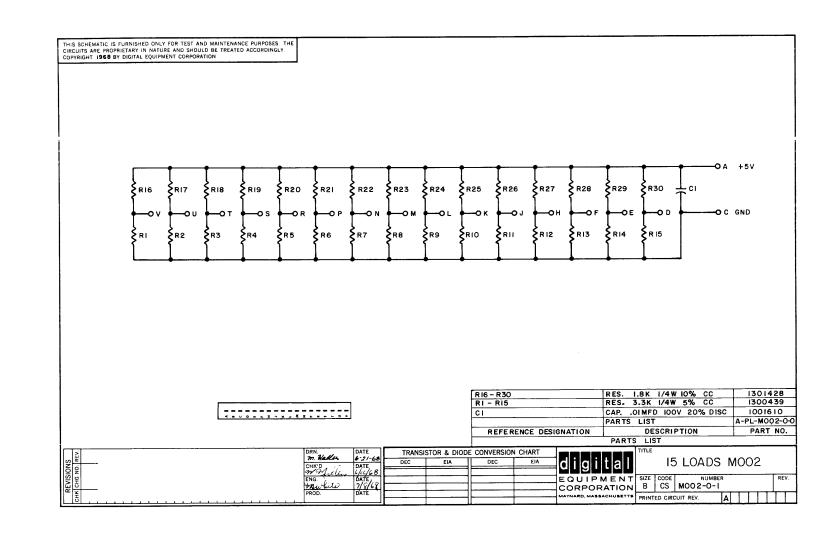

### M002 Logic 1 Source

The M002 provides 15 outputs at +3V (logic 1) on pins D2 through V2 to hold unused M-series TTL gate inputs HIGH. Up to 10 unused M-series gate inputs can be connected to any one output. If a M002 circuit is driven by a gate, the M002 circuit appears as two TTL unit loads, or 3.2 mA at ground.

Power dissipation of the M002 module is +5V at 16 mA (maximum).

### M101 Bus Data Interface

The M101 contains fifteen, two-input NAND gates. One input of each gate is tied to a common line so that all data signals on the second input of each gate can be enabled simultaneously. The M101 can also be used as inverters or a data multiplexer. All data inputs are protected from a negative or more than -0.8V.

INPUTS: Each data signal input presents one TTL unit load. The common line input

presents fifteen unit loads.

**OUTPUTS**: Each output can drive ten unit loads.

**POWER:** +5V at 82 mA (max.)

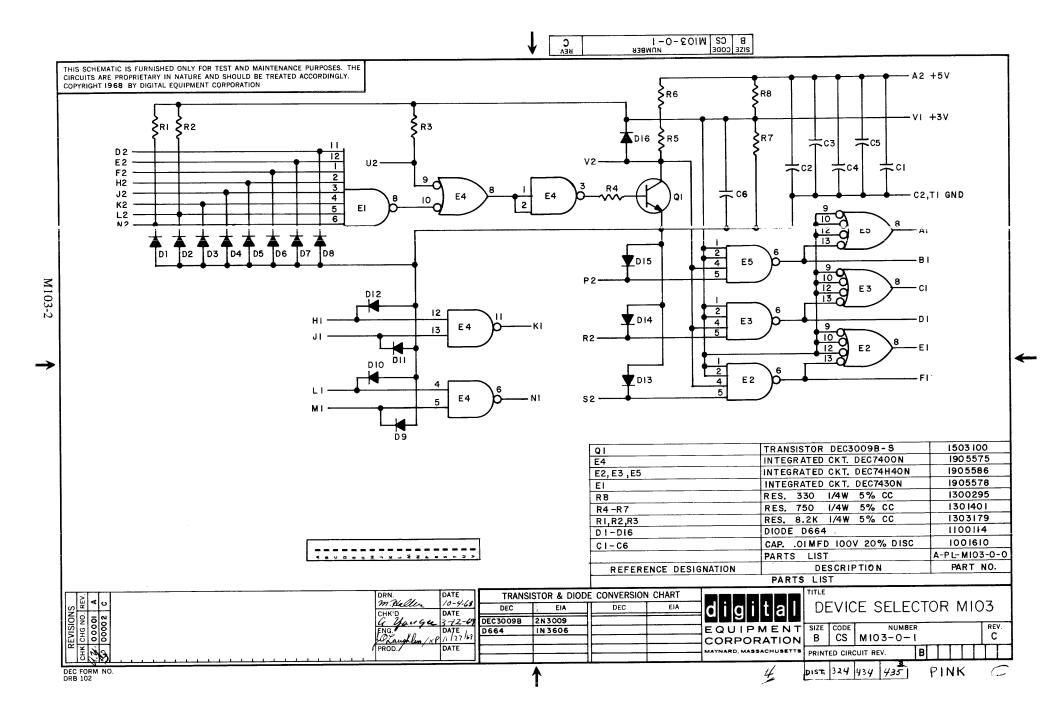

### M103 Device Selector

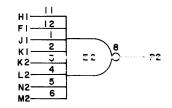

The M103 module is used to decode the six device bits transmitted in complement pairs on a positive bus in a digital system. Selection codes are obtained by selective wiring of the bus signals to the code select inputs; D2, E2, F2, H2, J2, and K2. The M103 module also includes pulse buffering gates for the IOP signals found on the positive bus in digital systems. Two 2-input NAND gates are also provided for any additional buffering that is required.

The following are the input, output, and power characteristics of the M103 module.

INPUTS: All inputs that receive positive bus signals are protected from negative voltage undershoot

of more than -0.8V. The following inputs each present one TTL unit load: D2; E2; F2; H2; J2; K2; H1; J1; L1; and M1. Inputs P2, R2, and S2 present 2.5 TTL unit loads. Inputs U2, L2, and N2 each present 1.25 unit loads. These inputs do not need to be tied to a source of

logic 1 when they are not in use.

OUTPUTS: Gate outputs K1 and N1 can each drive ten TTL unit loads. Pulse buffering outputs A1, B1,

C1, D1, E1, and F1 can each drive 37 TTL unit loads. The Option Select output can drive

16 TTL unit loads.

POWER: The power dissipation of the M103 module is +5V at 110 mA (maximum).

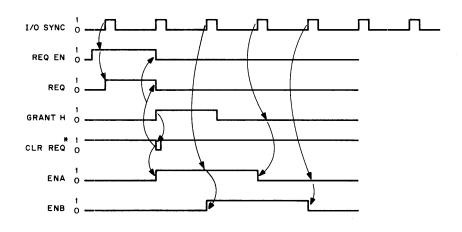

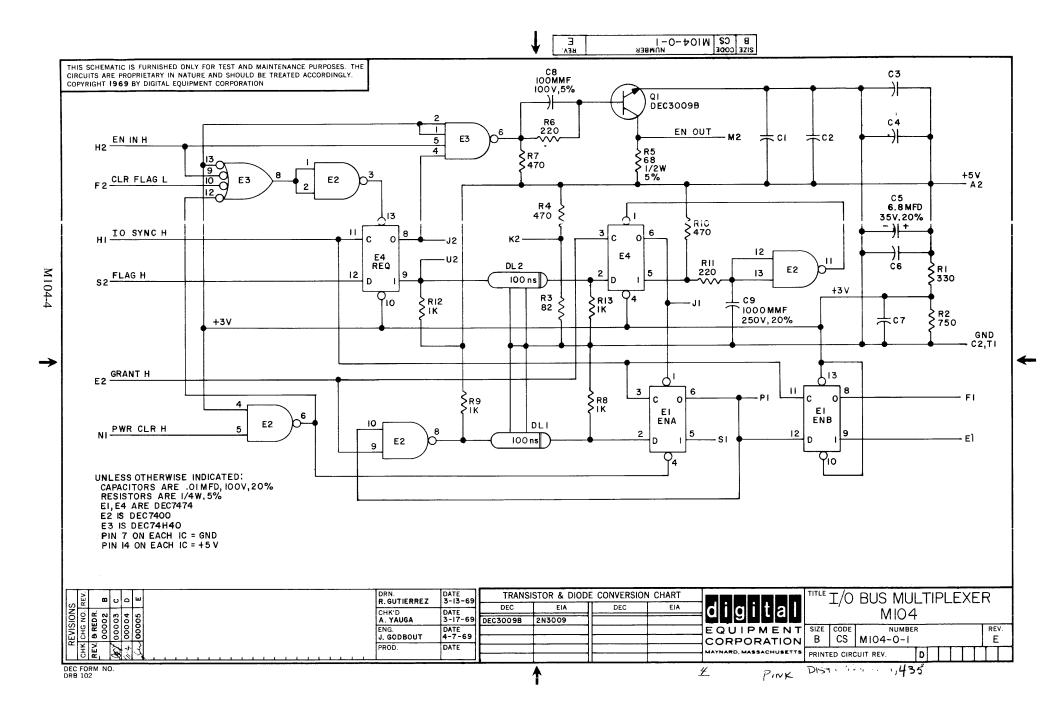

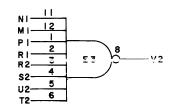

## M104 I/O Bus Multiplexer

The M104 module has been designed specifically for controllers of PDP-15 peripherals. It is used in all controllers that make use of the API or data channel facilities in the I/O processor. It accepts a request from the controller logic at its FLAG (1) H input and synchronizes this request to the I/O SYNC H pulses issued from the I/O processor. These pulses are fed into SYNC of the M104 and immediately set the REQ flip-flop. The REQ flip-flop can be monitored through pins J2 and U2. The I/O processor responds to a request with a GRANT, and ENA is set. This flip-flop is generally used to gate any address information onto the bus; e.g., the API trap address or the word count address of the multicycle data break. The next SYNC pulse sets ENB.

The REQ flag can be reset through pin F2 (CLR RQ) by the controller logic. Pin N1 should be tied to power clear or its equivalent.

The Enabling level ENABLE IN holds REQ off if ENABLE IN arrives as a negative level. When REQ is set (if ENABLE IN is positive), ENABLE OUT goes negative; and the next peripheral on the bus receives this level as a negative ENABLE IN. In this way, the M104 establishes priorities among devices on the same API level or among devices that use the data channel. See the timing diagram for additional information.

The following are the input, output, and power characteristics of the M104 module.

**INPUTS:** The inputs are standard TTL voltages and have the following input pins and loads:

| Input Pin | Load (Units)           |  |  |

|-----------|------------------------|--|--|

| H2        | 2.5                    |  |  |

| S2        | 1                      |  |  |

| H1        | 6                      |  |  |

| E2        | 3                      |  |  |

| N1        | 1                      |  |  |

| F2        | 1-1/4                  |  |  |

| K2        | $68\Omega$ Termination |  |  |

| S2        | 1                      |  |  |

**OUTPUTS**: The output gates can drive as follows:

| Output Pin | Number of Loads Pin Can Drive |

|------------|-------------------------------|

| U2         | 5                             |

| J2         | 8                             |

| P1         | 9                             |

| S1         | 10                            |

| E1         | 10                            |

| F1         | 10                            |

| <b>M</b> 2 | PDP-15 I/O Bus                |

|            | Compatible (30 units)         |

| J1         | 7                             |

**POWER:** The power dissipation of the M104 module is 1W at 5V.

\$ J1 IS ASSUMED TO BE WIRED TO F2

15 - 0087

M104 Timing Diagram

This page intentionally left blank.

09-0408

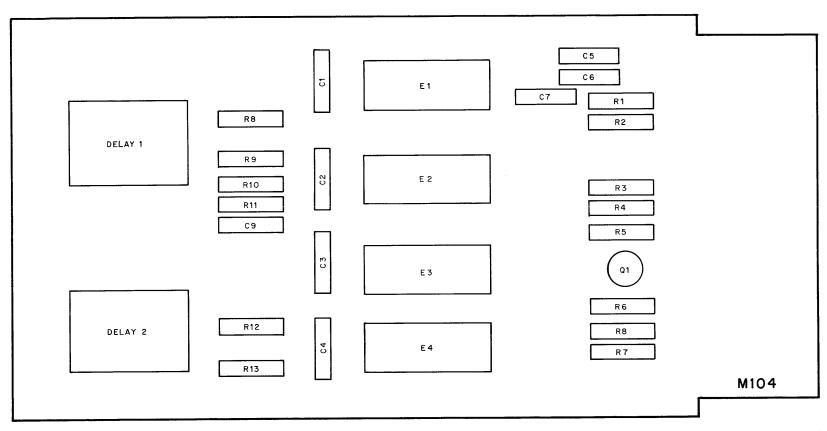

#### M111 Inverters

The M111 module contains sixteen inverters with input/output connections as shown on the circuit schematic. Propagation delay is 22 ns (maximum).

The following are the input, output, and power characteristics of the M111 module.

INPUT:

Each input presents one unit load.

OUTPUT:

Each output can drive up to ten unit loads.

POWER:

The power dissipated in the M111 module is +5V at 87 mA (maximum).

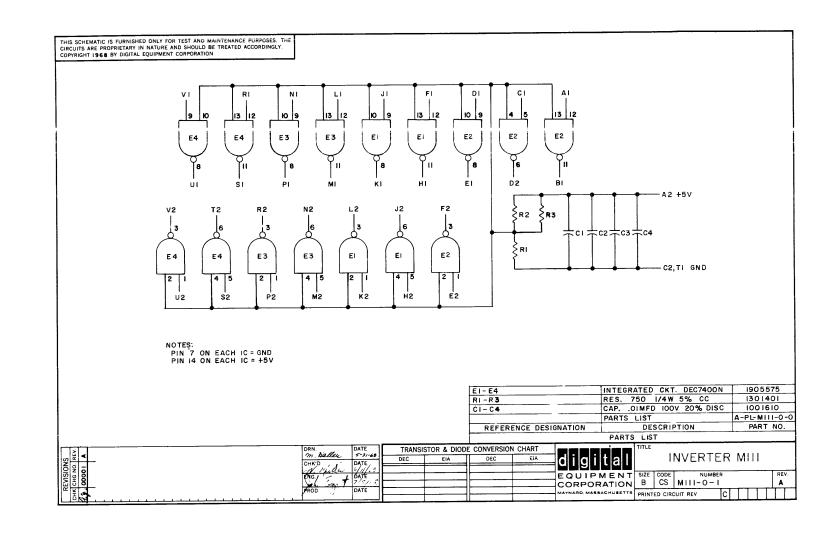

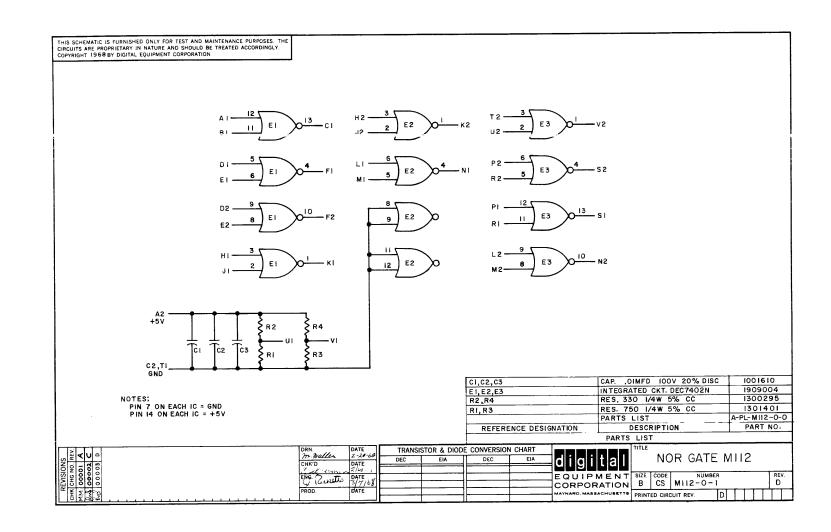

#### M112 NOR Gates

The M112 module contains ten 2-input NOR gates, each performing the function NOT (A + B). Pins U1 and V1 provide +3V, and each are capable of holding HIGH (logic 1) up to 40 unused M-series inputs. Propagation delay is 22 ns (maximum).

The following are the input, output, and power characteristics of the M112 module.

INPUT:

Each input presents one unit load.

**OUTPUT**:

Each output can drive up to ten unit loads.

POWER:

The power dissipated in the M112 module is +5V at 50 mA (maximum).

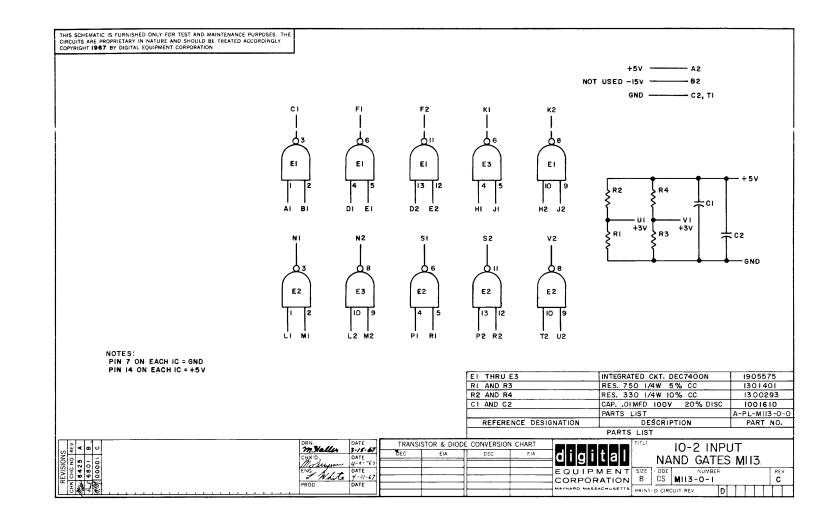

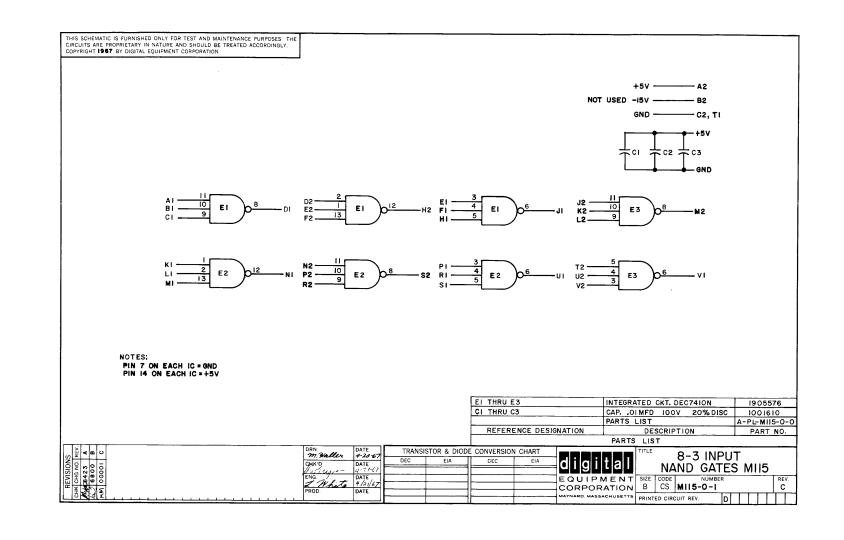

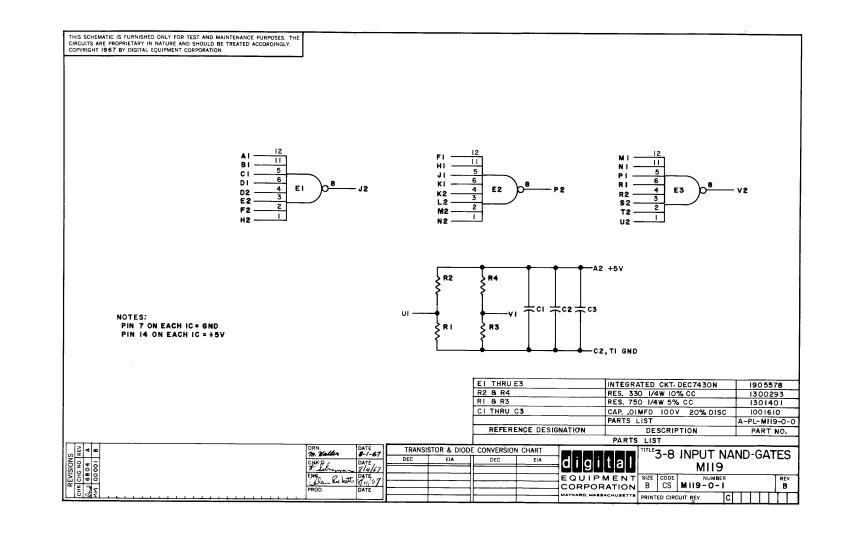

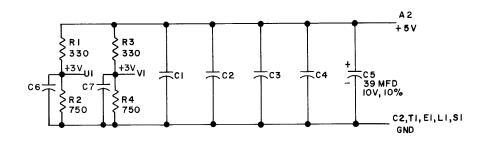

#### M113, M115, M117, M119 NAND Gates

The M113, M115, M117, and M119 modules provide general purpose gating for the M-series. They are most commonly used for decoding, comparison, and control. Each module performs the NAND function NOT (A · B - - - - - N), depending upon the number of inputs.

The modules and their descriptions are as follows:

M113 - Ten 2-input NAND gates that also can be used as inverters;

M115 - Eight 3-input NAN D gates;

M117 - Six 4-input NAN D gates;

M119 - Three 8-input NAN D gates.

Unused inputs on any gate must be returned to a source of logic 1 for maximum noise immunity. In the M113, M117, M119, M121, M617, and M627 modules, two pins (U1 and V1) are provided as a source of +3V for noise immunity. Each pin can supply up to 40 unit loads. Modules M103, M111, and M002 provide additional sources of logic 1 level. Typical propagation delay of these gates is 15 ns, and maximum propagation delay is 22 ns.

The following are the input, output, and power characteristics of these modules.

**INPUTS:** Each input presents one unit load.

**OUTPUTS:** Each output is capable of supplying 10 unit loads.

**POWER:** Power dissipation for the respective modules is:

M113: 71 mA M115: 41 mA M117: 41 mA M119: 9 mA +maximum current at 5V

| THIS SCHEMATIC IS FURNISHED ONLY FOR TEST AND MAINTENANCE PURPOSES. THE<br>IRCUITS ARE PROPRIETARY IN NATURE AND SHOULD BE TREATED ACCORDINGLY<br>DOPYRIGHT 1967 BY DIGITAL EQUIPMENT CORPORATION |           |                              |               |                                  |                           |                                                       |                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------|---------------|----------------------------------|---------------------------|-------------------------------------------------------|-------------------------------------|

|                                                                                                                                                                                                   |           |                              |               |                                  | N                         | +5V                                                   | - A 2<br>B 2                        |

|                                                                                                                                                                                                   |           |                              |               |                                  |                           | GND                                                   | - C2 , Ti                           |

| AI 13<br>BI 12<br>CI 10<br>DI 9                                                                                                                                                                   |           | HI 12<br>HI 10<br>JI 9       | )o <u>#</u> ' | MI — NI — PI — RI —              | 13<br>12<br>10<br>9<br>E3 | SI                                                    |                                     |

| 02 5<br>E2 4<br>F2 2<br>H2 I                                                                                                                                                                      | — J2 L    | 62 5<br>-2 4<br>12 2<br>12 1 | 5 <u>6</u> F  | R2 —<br>S2 —<br>T2 —<br>U2 —     | 1<br>2<br>4<br>5<br>E3    | v2                                                    |                                     |

| NOTES:                                                                                                                                                                                            |           |                              |               |                                  | C3 R2                     | N3 VI VI +3V                                          | +5V                                 |

| PIN 7 ON EACH IC=GND<br>PIN 14 ON EACH IC=+5V                                                                                                                                                     |           |                              |               |                                  | L                         |                                                       | GND                                 |

|                                                                                                                                                                                                   |           |                              |               | EI THRU E3<br>RI & R4<br>R2 & R3 | RES. 75<br>RES. 33        | ATED CKT. DEC7420N<br>50 1/4W 5% CC<br>30 1/4W 10% CC | 1905577<br>1301401<br>1300293       |

|                                                                                                                                                                                                   |           |                              |               | CI THRU C3 REFERENCE DES         | PARTS                     | DESCRIPTION                                           | 1001610<br>A-PL-MII7-0-<br>PART NO. |

| 0 N N N N N N N N N N N N N N N N N N N                                                                                                                                                           | CHK'D DAT | DEC DEC                      | STOR & DIODE  | CONVERSION CHART DEC EIA         | digital                   | TITLE 6-4 INPL                                        | JT<br>S <b>M</b> II7                |

| NNSIC                                                                                                                                                                                             | ENG DAT   |                              |               |                                  | EQUIPMENT<br>CORPORATION  |                                                       | RE'                                 |

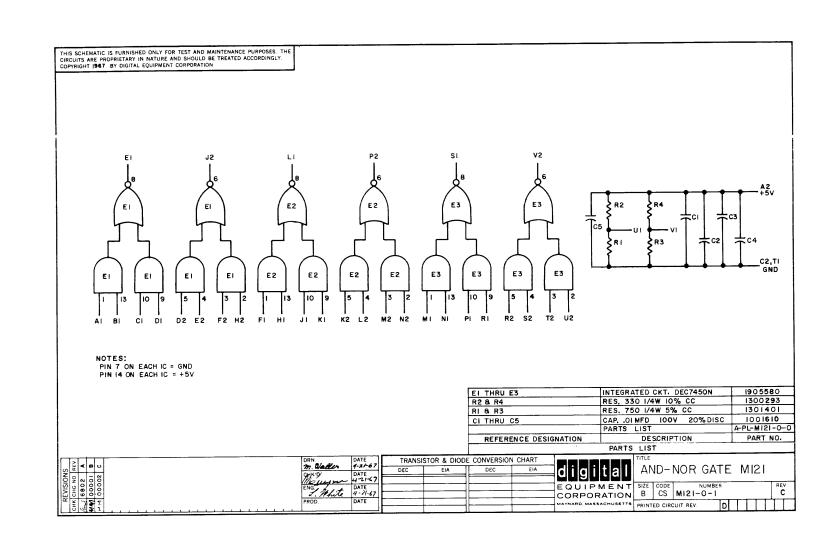

#### M121 AND/NOR Gates

The M121 module contains six AND/NOR gates that perform the function NOT (AB + DC). The exclusive OR, coincidence, and NOR functions can be performed by proper connection of signals to the AND inputs. Maximum propagation delay of an M121 gate is 22 ns.

The following are the input, output, and power characteristics of the M121 module.

**INPUTS**: Each input presents one unit load to the driving module.

**OUTPUTS**: Each output is capable of driving up to 10 unit loads.

**POWER:** Power dissipation of the M121 module is +5V at 50 mA (maximum).

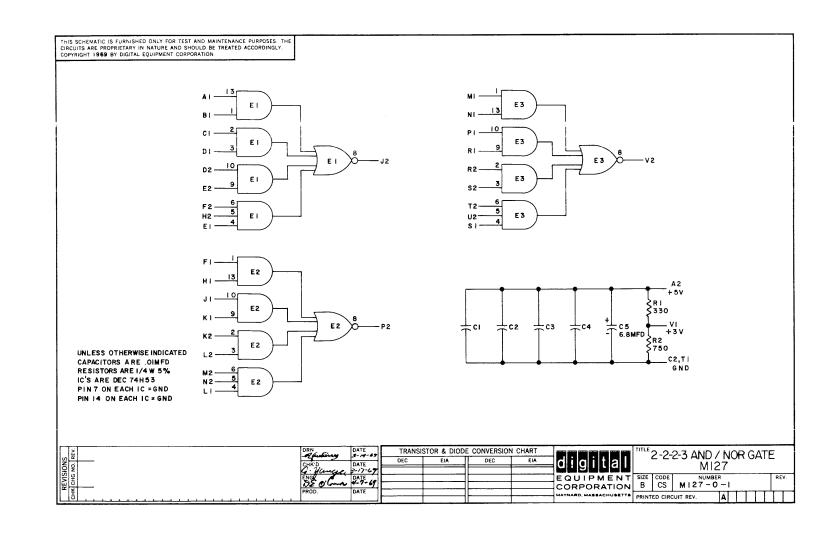

### M127 AND/NOR Gates

The M127 module contains three general purpose AND/NOR gates that perform functions similar to the M121 module. By connecting signals to the AND inputs, these gates can be used to select and to place on a single output any of several input signals. Propagation delay of an M127 gate is 11 ns (maximum).

The following are the input, output, and power characteristics of the M127 module.

**INPUTS:** Each input presents 1.25 unit loads.

**OUTPUTS:** Each output is capable of driving 12.5 unit loads.

**POWER:** Power dissipation of the M127 module is 5V at 100 mA (maximum).

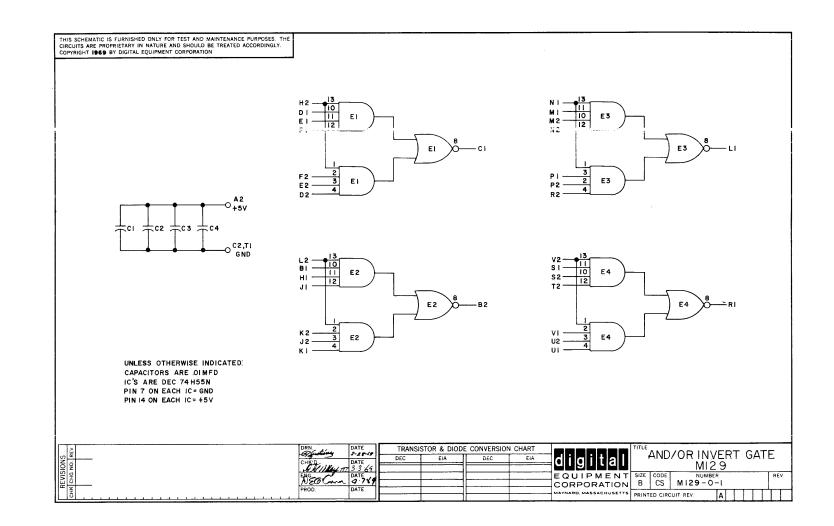

# M129 AND/NOR Gates

The M129 module contains four general purpose AND/NOR gates that perform functions similar to the M121 module. By connecting signals to the AND inputs, these gates can be used to select and to place on a single output any of several input signals. Propagation delay of an M129 gate is 11 ns (maximum).

The following are the input, output, and power characteristics of the M129 module.

INPUTS: Inputs H2, L2, N1, and V2 present 2.5 unit loads, and the remaining inputs present

1.25 unit loads.

**OUTPUTS:** Each output is capable of driving 12.5 unit loads.

**POWER:** Power dissipation of the M129 module is 5V at 50 mA (maximum).

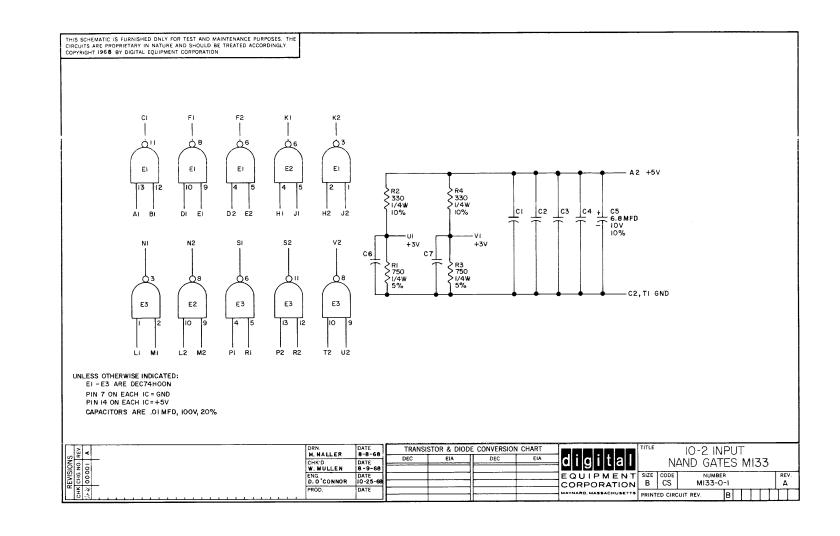

### M133 NAND Gates

The M133 module contains ten 2-input NAND gates, each performing the function NOT (A·B). The module is used for general purpose high-speed gating. Maximum output propagation delay to a logic 1 or 0 is 10 ns. The high-speed characteristic of these gates frequently solves tight timing problems in complex systems. Unused inputs on any gate must be returned to a source of logic 1 for maximum speed and noise immunity.

The following are the input, output, and power characteristics of the M133 module.

**INPUTS**: Each input presents 1.25 unit loads.

**OUTPUTS:** Each output is capable of driving 12.5 unit loads.

**POWER:** Power dissipated in the M133 module is +5V at 130 mA (maximum).

### M135 NAND Gates

The M135 module contains eight high-speed 3-input NAND gates that perform the function NOT (A·B·C). These gates are most commonly used for decoding, comparison, and control. Unused inputs on any gate must be returned to a source of logic 1 for maximum speed and immunity. Propagation delay of an M135 gate is 10 ns (maximum).

The following are the input, output, and power characteristics of the M135 module.

INPUTS:

Each input presents 1.25 unit loads.

**OUTPUTS**:

Each output is capable of driving 12.5 unit loads.

**POWER:**

Power dissipated in the M135 module is 5V at 90 mA (maximum).

THIS SCHEMATIC IS FURNISHED ONLY FOR TEST AND MAINTENANCE PURPOSES. THE CIRCUITS ARE PROPRIETARY IN NATURE AND SHOULD BE TREATED ACCORDINGLY. COPYRIGHT 1969 BY DIGITAL EQUIPMENT CORPORATION O<sub>+5V</sub> +6.8MFD + C2 + C3 + C4 + C5 35V -O C2,TI UNLESS OTHERWISE INDICATED: IC'S ARE DEC74HIO PIN 7 ON EACH IC = GND PIN 14 ON EACH IC = +5V CAPACITORS ARE .OI MFD 50 V TRANSISTOR & DIODE CONVERSION CHART TITLE 3 INPUT NAND GATE DEC MI35 EQUIPMENT SIZE CODE NUMBER CORPORATION B CS MI35-0-1

MAYNARD, MASSACHUSETTS PRINTED CIRCUIT REV.

# M139 NAND Gates

The M139 module contains three high-speed 8-input NAND gates that perform the NAND function NOT (A•B...N), depending on the number of inputs. These gates are most commonly used for decoding, comparison, and control. Unused inputs on any gate must be returned to a source of logic 1 for maximum speed and noise immunity. Propagation delay of an M139 gate is 10 ns (maximum).

The following are the input, output, and power characteristics of the M139 module.

**INPUTS:** Each input presents 1.25 unit loads.

**OUTPUTS:** Each output is capable of driving 12.5 unit loads.

**POWER:** Power dissipated in the M139 module is 5V at 40 mA (maximum).

UNLESS OTHERWISE INDICATED: IC'S ARE DECIO74H30 PIN 7 ON EACH IC = GND PIN 14 ON EACH IC =+5V CAPACITORS ARE .OI MFD, 100V, 20% RESISTORS ARE 1/4W,5%

| 1 | S       | REV.    | 8     | ပ     | ۵     |   |  |  |      |   |  |      |      |  |       |

|---|---------|---------|-------|-------|-------|---|--|--|------|---|--|------|------|--|-------|

|   | EVISION | CHG NO. | 10000 | 00002 | 00003 |   |  |  |      |   |  |      |      |  |       |

|   | L       | S.<br>Ž | P.    |       | MIL   | L |  |  | <br> | _ |  | <br> | <br> |  | <br>_ |

| • | DEC     | 50      | DM    | NC    |       |   |  |  | _    |   |  |      |      |  | <br>_ |

| DRN.              | DATE<br>3-4-69 |

|-------------------|----------------|

| CHK'D<br>C. Yanga | DATE<br>3-6-49 |

| DEO Com           | DATE<br>4-7-69 |

| PROD.             | DATE           |

| , | TRANSISTOR & DIODE CONVERSION CHART |     |     |     |                    |  |  |  |

|---|-------------------------------------|-----|-----|-----|--------------------|--|--|--|

| 4 | DEC                                 | EIA | DEC | EIA |                    |  |  |  |

| Ł |                                     |     |     |     |                    |  |  |  |

| 9 |                                     |     |     |     | -JΕ (              |  |  |  |

| 4 |                                     |     |     |     | $\dashv$ c $\circ$ |  |  |  |

| ┚ |                                     |     | -   |     | MAY                |  |  |  |

|           |    |   |    |   |     |   | יין |

|-----------|----|---|----|---|-----|---|-----|

| Ы         | H  | g | Н  | П | а   | П |     |

|           | H  | ۲ | ¥  | Ľ | ۳   | ۳ | L   |

| EQUIPMENT |    |   |    |   |     |   |     |

| lcc       | )R | P | )R | A | ric | N |     |

3-8 INPUT NAND GATE MI39 SIZE CODE NUMBER REV. В CS M139-0-1 PRINTED CIRCUIT REV.

DIST: 324, 434, 4352

PINK

DEC FORM NO. DRB 102

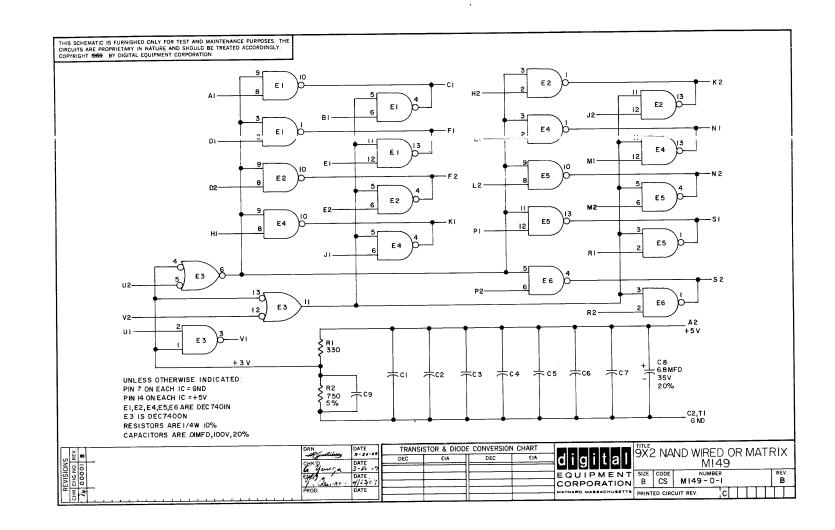

## M149 NAND Wired OR Matrix

The M149 module contains two sets of nine open-collector NAND gates. The NAND gates are OR wired together onto nine output pins having the standard TTL output levels. Each set of NAND gates is connected to operate in conjunction with a separate enable gate. The M149 module is used to gate desired signals onto an open-collector bus. (Refer to Engineering Drawings D-BS-KP15-0-38 through D-BS-KP15-0-43, and D-BS-KP15-0-60 through D-BS-KP15-0-62).

The following are the input, output, and power characteristics of the M149 module.

**INPUTS**: Each input presents 1 unit load.

OUTPUTS: Gate outputs are all open-collector and can sink 16 mA (maximum). The pulse amplifier

output is capable of driving 10 unit loads.

**POWER:** Power dissipation of the M149 module is 5V at 130 mA (maximum).

#### M159

### 4-Bit Arithmetic Logic Unit

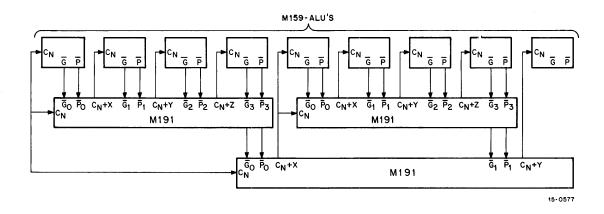

The M159 4-Bit Arithmetic Logic Unit (ALU) module contains a single DEC74181 integrated circuit. Nine of these ALU modules are used in the FP15 Floating-Point Processor to perform 36-bit arithmetic and logic operations, as shown on D-BS-FP15-0-19 through -28 of the FP15 drawings.

The integrated circuit is capable of performing 16 4-bit arithmetic operations when the MODE control and CN inputs are low and 16 logic functions when the MODE control input is high. The functions are selected by applying combinations of function select inputs S0 through S3. For FP15 applications, the function select and MODE control inputs are generated by the adder control logic shown on D-BS-FP15-0-33 of the FP15 drawings.

Only two arithmetic operations, A plus B and A minus B minus 1, are selected. Five logic functions, A, -A, B, -B, and logical 0, are performed. The combined ALU truth table for FP15 arithmetic operations and logic functions is listed as follows:

| MODE    | Func       | tion Sele | ect Inp    | uts | _                                        |

|---------|------------|-----------|------------|-----|------------------------------------------|

| Control | <b>S</b> 3 | S2        | <b>S</b> 1 | S0  | Output Function                          |

| 0       | 1          | 0         | 0          | 1   | A plus B (arithmetic operation)          |

| 0       | 0          | 1         | 1          | 0   | A minus B minus 1 (arithmetic operation) |

| 0       | 0          | 0         | 0          | 0   | A (logic function)                       |

| 1       | 0          | 0         | 0          | 0   | -A (logic function)                      |

| 1       | 1          | 0         | 1          | 0   | B (logic function)                       |

| 1       | 0          | 1         | 0          | 1   | -B (logic function)                      |

| 1       | 0          | 0         | 1          | 1   | Logical 0 (logic function)               |

In addition, a comparator output, A=B, is provided when the four A inputs are equal to the four B inputs. A full carry look ahead capability is provided for fast, simultaneous carry generation.

INPUTS:

Each input presents 1 unit load.

**OUTPUTS**:

All outputs are capable of driving 10 unit loads.

POWER:

M129-0-1

B CZ SISE CODE

# M161 Binary to Octal/Decimal Decoder

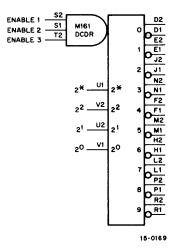

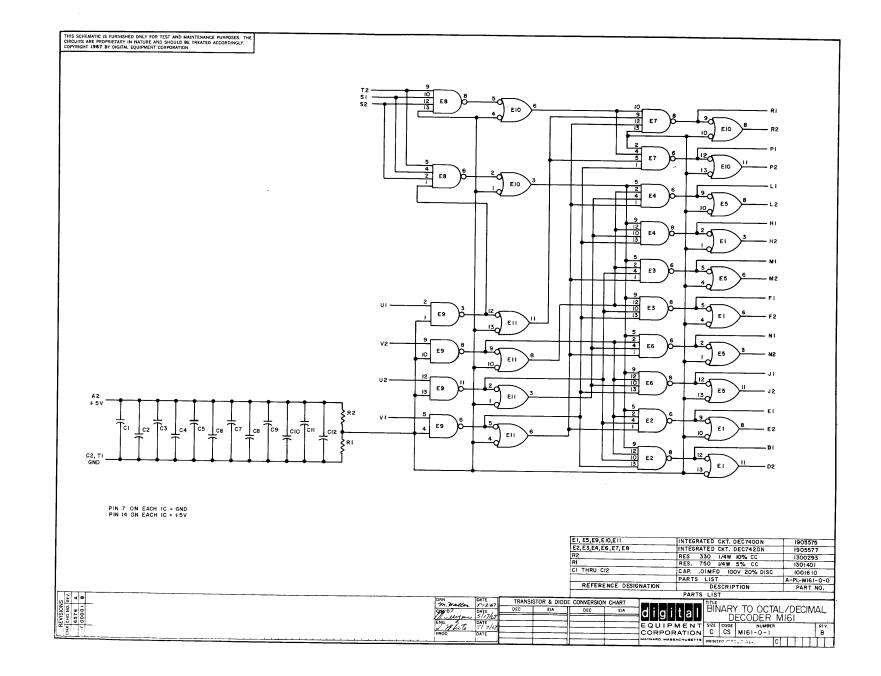

The M161 is a functional decoding module that can be used as a binary-to-octal or binary-coded decimal-(8421 or 2421 codes)-to-decimal decoder. In the binary-to-octal configuration, up to eight M161s can be linked together to provide decoding of up to six bits. Three ENABLE inputs are provided for selective enabling of modules in decoders of more than one digit. In the octal mode, the bit 2\* input is connected to ground, which automatically inhibits the 8 and 9 outputs. Connections for a 5-bit binary/octal decoder (4 modules) are shown in DEC's **Digital Logic Handbook**, 1970 edition. The figure assumes that the inputs to the decoder are the outputs of flip-flops such as FF2° (1), 1 output side; and FF2° (0), 0 output side.

M161 Simplified Diagram

The propagation delay through the decoder is typically 55 ns in the binary-to-octal mode and 75 ns in the BCD-to-decimal mode. The maximum delay in the BCD-to-decimal mode is 120 ns, thereby frequency-limiting this module to 8 MHz when used in this fashion. The ENABLE inputs can be used to strobe output data, if inputs  $2^{\circ}$  -  $2^{*}$  have settled at least 50 ns prior to the input pulse.

<sup>\*</sup>The 2-bit input may be of decimal value 2, 4, 6, or 8 if illegal combinations are inhibited before connections to the inputs, and the 4-2-1 part of the code is in binary.

The following are the input, output, and power characteristics of the M161 module.

INPUTS: The inputs to the M161 are: 2° through 2\*, 1 unit load each; ENABLE 1 through

ENABLE 3, 2 unit loads each.

**OUTPUTS:** Each positive output is capable of driving 10 unit loads, and each negative output is

capable of driving 9 unit loads.

**POWER:** Power dissipation of the M161 module is 5V at 120 mA (maximum).

<sup>\*</sup>The 2-bit input may be of decimal value 2,4,6, or 8 if illegal combinations are inhibited before connections to the inputs, and the 4-2-1 part of the code is in binary.

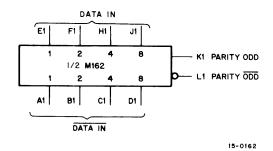

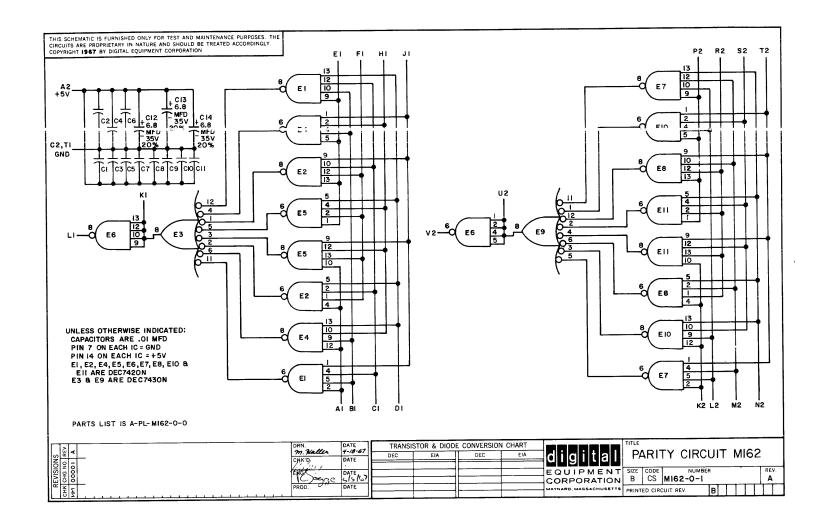

# M162 Parity Circuit

The M162 module is a parity detector and contains two parity circuits. Each circuit indicates whether the binary data presented to it contains an odd or even number of 1s. The requirements of the data and its complement are shown in the illustration.

Indication of odd parity is given by a HIGH level at pins K1 and U2. Pins L1 and V2, when HIGH, indicate even parity or no input.

The following are the input, output, and power characteristics of the M162 module.

**INPUTS:** Each input presents four unit loads.

OUTPUTS: Pins L1 and V2 can each supply up to ten unit loads. Pin K1 and U2 can each supply up to

six unit loads.

**POWER:** Power dissipation of the M162 module is +5V at 102 mA (maximum).

M162 Simplified Diagram

### M164 6-Bit Parallel Adder

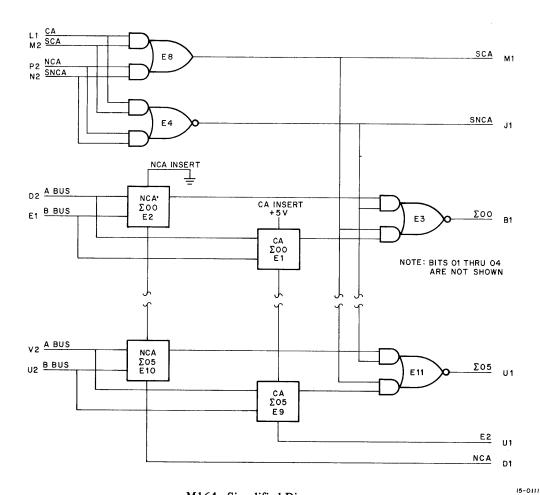

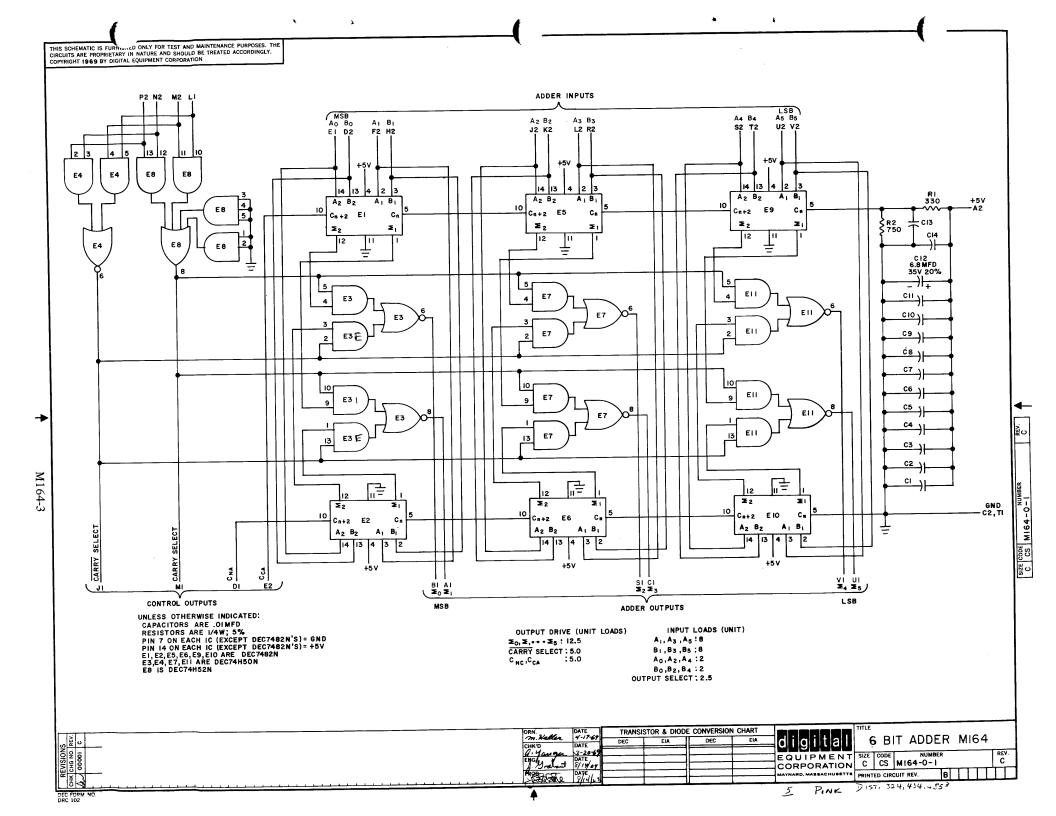

The M164 module contains a 6-bit conditional sum adder. Three of these modules are connected in tandem to form the 18-bit adder used in the central processor of the PDP-15. (Refer to Engineering Drawings D-BS-KP15-0-1 through D-BS-KP15-0-18.) The adder can generate an 18-bit sum in 82 ns. This high speed is available because there is no carry propagated from one adder module to the next. Instead of having the carry propagated from module to module, which takes 48 ns per module, each 6-bit sum is performed twice simultaneously (see illustration). One sum, CA (carry anticipated), is formed with a carry inserted, while the other sum, NCA (no carry anticipated), is formed without a carry inserted. Combinational logic in each adder module

M164 Simplified Diagram

provides the control inputs SCA (select carry anticipated) or SNCA (select no carry anticipated) to the module handling the next six most significant bits. The sum from the first adder module during normal addition is always a sum without a carry inserted because the combinational logic is strapped to select the adder that has no carry inserted.

The following are the input, output, and power characteristics of the M164 module.

INPUTS: The M164 adder module is unbuffered; and all inputs must, therefore, remain stable for the entire add cycle. The following list shows all input connections and the TTL unit loading they present:

| Name          | Pin | Loading | True 1 |

|---------------|-----|---------|--------|

| 10            | E1  | 2.0     | +2.0   |

| 30            | D2  | 2.0     | +2.0   |

| $\mathbf{A}1$ | F2  | 8.0     | +2.0   |

| 81            | H2  | 8.0     | +2.0   |

| 42            | J2  | 2.0     | +2.0   |

| 82            | K2  | 2.0     | +2.0   |

| <b>A</b> 3    | L2  | 8.0     | +2.0   |

| 33            | R2  | 8.0     | +2.0   |

| <b>4</b> 4    | S2  | 2.0     | +2.0   |

| 84            | T2  | 2.0     | +2.0   |

| <b>A</b> 5    | U2  | 8.0     | +2.0   |

| 85            | V2  | 8.0     | +2.0   |

| CA            | L1  | 2.5     | +2.0   |

| SCA           | M2  | 2.5     | +2.0   |

| SNCA          | N2  | 2.5     | +2.0   |

| NCA           | P2  | 2.5     | +2.0   |

**OUTPUTS:** The M164 adder module generates a 6-bit sum in 78 ns and a carry in 42 ns. All output connections and TTL driving capabilities are shown below.

| Name | Pin | Drive | True 1 |

|------|-----|-------|--------|

| ΣΟ   | B1  | 12.5  | 0.4    |

| Σ 1  | A1  | 12.5  | 0.4    |

| Σ 2  | S1  | 12.5  | 0.4    |

| Σ 3  | C1  | 12.5  | 0.4    |

| Σ4   | V1  | 12.5  | 0.4    |

| Σ 5  | U1  | 12.5  | 0.4    |

| SNCA | J1  | 5.0   | 2.4    |

| SCA  | M1  | 5.0   | 2.4    |

| CA   | E2  | 5.0   | 0.4    |

| NCA  | D1  | 5.0   | 0.4    |

**POWER:** Power dissipated in the M164 module is 5V at 118 mA (maximum).

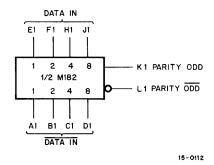

# M182 Parity Circuit

The M182 module is a parity detector and contains two high-speed parity circuits. Each circuit indicates whether the binary data presented to it contains an odd or even number of 1s. The data and its complement are required for inputs as shown by the illustration. Indication of odd parity is given by a HIGH level at pins K1 and V1. Pins L1 and V2, when HIGH, indicate even parity or no input.

The following are the input, output, and power characteristics of the M182 module.

**INPUTS:** Each input presents 5 unit loads.

OUTPUTS: Pins L1 and V2 can each drive up to 12.5 unit loads. Pins K1 and U2 can each drive up to

7.5 unit loads.

**POWER:** Power dissipated in the M182 module is 5V at 200 mA (maximum).

M182 Simplified Diagram

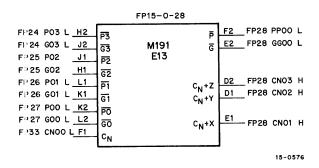

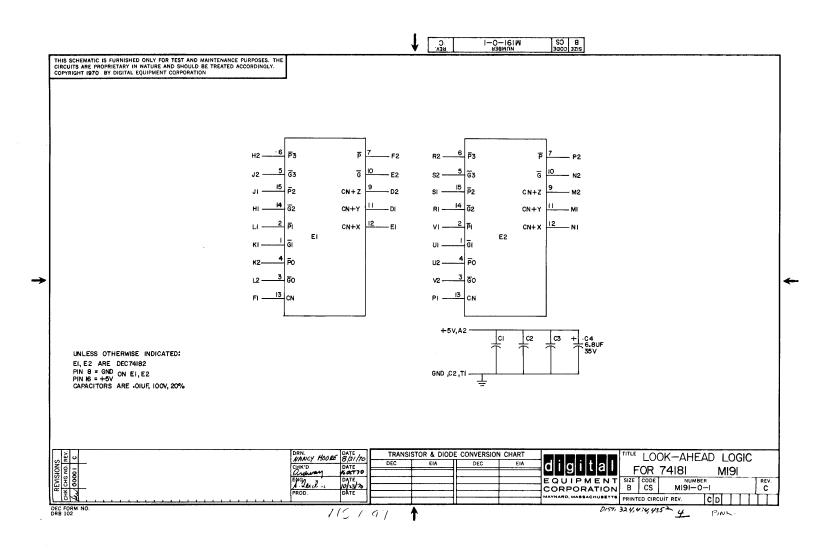

#### M191

### **Carry Look-Ahead Generator**

The M191 Carry Look-Ahead Generator, consisting of two DEC 74182 integrated circuits, is a high-speed generator capable of anticipating a carry through a group of ALUs. A 13-ns delay occurs for each look-ahead level.

Input Voltage:

5.5 volts (with respect to network grand terminal).

Supply Voltage:

4.75 - 5.25 (5 v. nominal)

Normalized Fan Out

High logic level 20

from Each Output:

Low logic level 10