PDP-10 Maintenance Manual

# KA10 CENTRAL PROCESSOR

Volume I

PDP-10 KA10 CENTRAL PROCESSOR MAINTENANCE MANUAL VOLUME I Copyright © 1968, 1970 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

FOCAL

DIGITAL

COMPUTER LAB

## CONTENTS

| CHAPTER | GENERAL INFORMATION                        |    | Page        |

|---------|--------------------------------------------|----|-------------|

| 1.1     |                                            |    | •           |

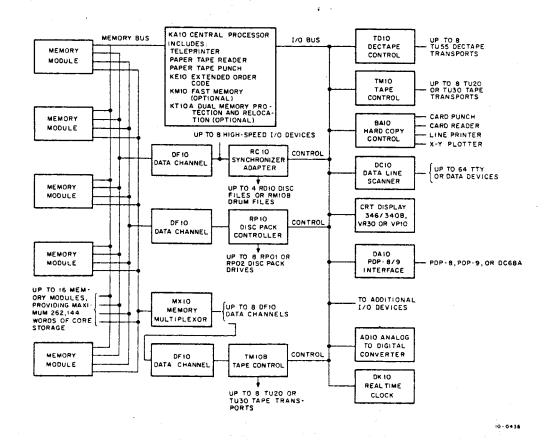

| 1.1.1   | Description                                |    | 1-1         |

|         | Physical Description                       |    | 1-1         |

| 1.1.2   | System Configurations                      | •  | 1-1         |

| 1.2     | Characteristics                            |    | 1-1         |

| 1.3     | Installation                               |    | 1-2         |

| 1.4     | Related Documents                          | مس | 1-2         |

| CHAPTER | 2 SYSTEM DESCRIPTION                       | 9  |             |

| 2.1     | Arithmetic Processor                       |    | 0.0         |

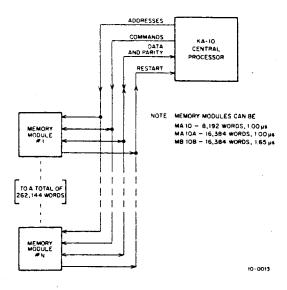

| 2.2     | Memory                                     |    | 2-2         |

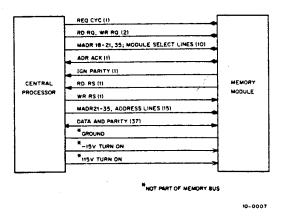

| 2.2.1   | Memory Bus                                 |    | 2-2         |

| 2.2.2   | Memory Priority                            |    | 2-3         |

| 2.2.3   | Memory Cycles                              |    | 2-3         |

| 2.2.3.1 | Read Cycle                                 |    | 2-3         |

| 2.2.3.2 | Write Cycle                                |    | 2-3         |

| 2.2.3.3 | Read-Modify-Write Cycle                    |    | 2-4         |

| 2.2.4   | Parity                                     |    | 2-4<br>2-4  |

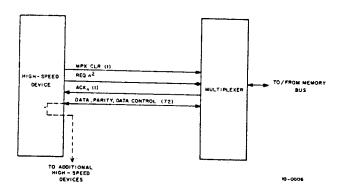

| 2.2.5   | Multiplexor                                |    | 2-4         |

| 2.3     | Input/Output                               |    |             |

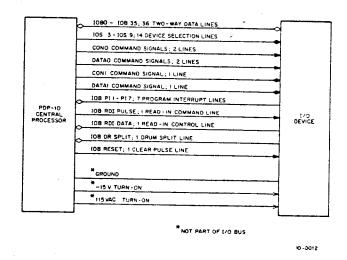

| 2.3.1   | I/O Bus and Control Device                 |    | 2-5         |

| 2.3.2   | I/O Transfers                              |    | 2-5         |

| 2.3.3   | Basic Input Transfers                      |    | 2-5         |

| 2.3.4   | Basic Output Transfers                     |    | 2-6         |

| 2.3.5   | Priority Interrupt in a Time-Shared System |    | 2-6         |

| 2.3.6   | Hardware Read-In                           |    | 2-6         |

| 2.3.7   | Drum Split Signal                          |    | 2-6         |

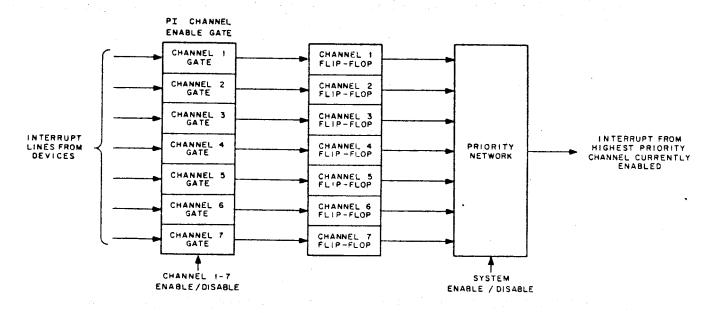

| 2.4     | Priority Interrupt System                  |    | 2-7         |

| 2.5     | Programming                                |    | 2-7         |

| 2.5.1   | Time Allotment (Simplified Description)    |    | 2-8         |

| 2.5.2   | Memory Protection and Relocation           |    | 2-8         |

| 2.5.3   | Input/Output                               |    | 2-8         |

| 2.5.4   | Conditions Storage                         |    | 2-9         |

| 2.6     | Instructions                               |    | 2-9<br>2-9  |

|         |                                            |    | <i>,</i> –, |

|           |                                             | Page |

|-----------|---------------------------------------------|------|

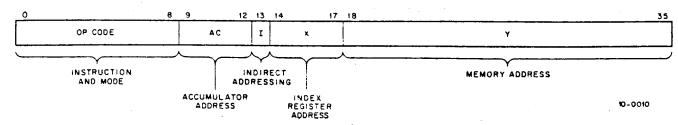

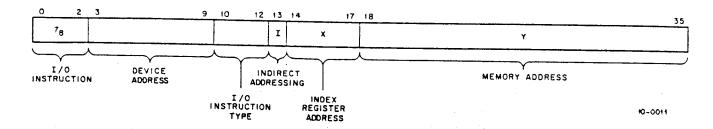

| 2.6.1     | Instruction Word Formats                    | 2-9  |

| 2.6.2     | Unimplemented User Operations - UUOs        | 2-10 |

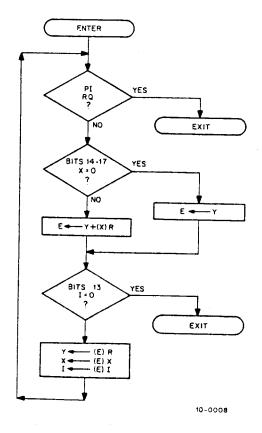

| 2.6.3     | Effective Address Calculations              | 2-10 |

| 2.6.4     | Instruction Classes                         | 2-11 |

| 2.6.4.1   | Data Transmission                           | 2-11 |

| 2.6.4.2   | Arithmetic and Logical                      | 2-12 |

| 2.6.4.3   | Executive Instructions                      | 2-12 |

| 2.6.4.4   | Push-down Instructions                      | 2-12 |

| 2.6.4.5   | I/O Instructions                            | 2-12 |

| 2.6.5     | Instruction Execution                       | 2-12 |

|           |                                             |      |

| CHAPTER 3 | OPERATING PROCEDURES                        |      |

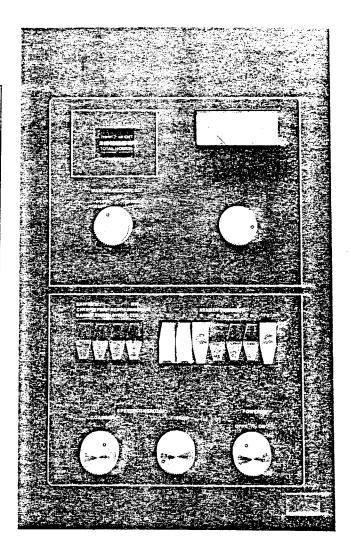

| 3.1       | Operator's Console                          | 3-1  |

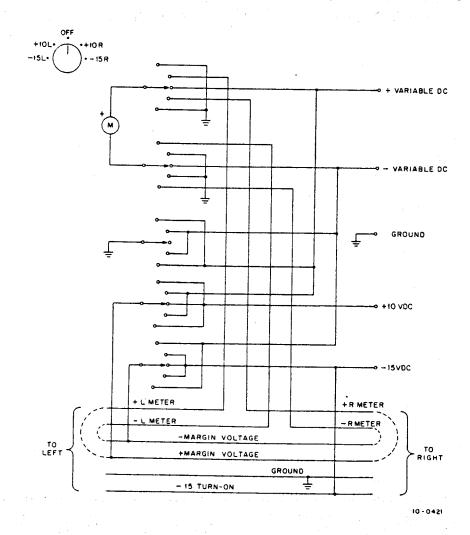

| 3.2       | Margin Check and Maintenance Panel          | 3-5  |

| 3.3       | Bay 1 and 2 Indicators                      | 3-6  |

| 3.4       | Paper Tape Reader/Punch and DECtape         | 3-6  |

| 3.5       | Teleprinter                                 | 3-6  |

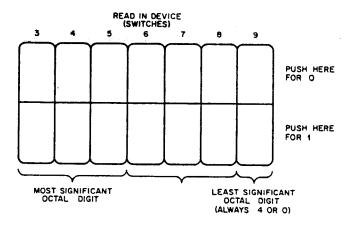

| 3.6       | Read In                                     | 3-10 |

|           |                                             |      |

| CHAPTER 4 | CENTRAL PROCESSOR ORGANIZATION              |      |

| 4.1       | KA10 Registers and Adders                   | 4-1  |

| 4.1.1     | AR (Arithmetic Register, 36 bits)           | 4-1  |

| 4.1.2     | BR (Buffer Register, 36 bits)               | 4-1  |

| 4.1.3     | MQ (Multiplier Quotient, 36 bits)           | 4-1  |

| 4.1.4     | AD, ADR (Adder, 36 bits)                    | 4-1  |

| 4.1.5     | MI (Memory Indicator, 36 bits)              | 4-1  |

| 4.1.6     | PB (Parity Buffer, 37 bits)                 | 4-1  |

| 4.1.7     | MA (Memory Address, 18 bits)                | 4-1  |

| 4.1.8     | PC (Program Counter, 18 bits)               | 4-1  |

| 4.1.9     | IR (Instruction Register, 18 bits)          | 4-1  |

| 4.1.10    | SC (Shift Counter, 9 bits)                  | 4-2  |

| 4.1.11    | SCAD (Shift Counter Adder, 9 bits)          | 4-2  |

| 4.1.12    | FE (Floating Exponent, 9 bits)              | 4-2  |

| 4.1.13    | PR, PR2 (Protection Registers, 8 bits each) | 4-2  |

| 4.1.14    | RL, RL2 (Relocation Registers, 8 bits each) | 4-2  |

|         |                                    | Pag                | je |

|---------|------------------------------------|--------------------|----|

| 4.1.15  | PIH, PIR, PIO                      | 4-2                | )  |

| 4.2     | KA10 Basic Cycles                  | 4-2                | )  |

| 4.2.1   | Instruction Cycle                  | 4-2                | )  |

| 4.2.2   | Address Cycle                      | 4-3                | }  |

| 4.2.3   | Fetch Cycle                        | 4-3                | j  |

| 4.2.4   | Execute Cycle                      | 4-4                | Ļ  |

| 4.2.5   | Store Cycle                        | 4-4                | ļ  |

| 4.3.    | KA10 Basic Instructions            | 4-5                | į  |

| 4.3.1   | Boolean                            | .∵<br>4 <b>-</b> 5 | ;  |

| 4.3.2   | Add, Sub                           | 4-5                | i  |

| 4.3.3   | Full Word Transfer (FWT)           | 4-5                | ;  |

| 4.3.4   | Half-Word Transfer (HWT)           | 4-5                |    |

| 4.3.5   | Exchange (EXCH)                    | 4-6                |    |

| 4.3.6   | Unimplemented User Operation (UUO) | 4-6                |    |

| 4.3.7   | Jump                               | 46                 |    |

| 4.3.7.1 | Jump to Subroutine (JSR)           | 4-6                | ,  |

| 4.3.7.2 | Jump and Save PC (JSP)             | 4-6                | ,  |

| 4.3.7.3 | Jump and Save AC (JSA)             | 4-7                |    |

| 4.3.7.4 | Jump and Restore AC (JRA)          | 4-7                |    |

| 4.3.7.5 | Jump on Flags and Clear (JFCL)     | 4-7                |    |

| 4.3.7.6 | Jump and Restore (JRST)            | 4-7                |    |

| 4.3.8   | Test                               | 4-7                |    |

| 4.3.9   | Add One to Both and Jump (AOBJ)    | 4-7                |    |

| 4.3.10  | Skips                              | 4-8                |    |

| 4.3.11  | Jumps                              | 4-8                |    |

| 4.3.12  | Compare                            | 4-8                |    |

| 4.3.13  | PUSH                               | 4-8                |    |

| 4.3.14  | Push and Jump                      | 4-8                |    |

| 4.3.15  | POP                                | 4-8                |    |

| 4.3.16  | POPJ                               | 4-9                |    |

| 4.3.17  | Execute (XCT)                      | 4-9                |    |

| 4.4     | KA10 Additional Instructions       | 4-9                |    |

| 4.4.1   | Extended Instructions              | 4-9                |    |

| 4.4.1.1 | Shift and Rotate                   | 4-9                |    |

| 4.4.1.2 | Shift and Count Subroutine         | 4-9                |    |

|         |                                    | Page |

|---------|------------------------------------|------|

| 4.4.1.3 | Fixed-Point Multiply               | 4-10 |

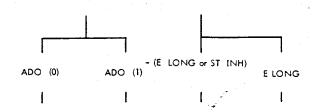

| 4.4.1.4 | Fixed-Point Divide                 | 4-10 |

| 4.4.2   | Block Transfer                     | 4-11 |

| 4.4.3   | Byte Manipulation                  | 4-12 |

| 4.4.4   | Floating Point                     | 4-13 |

| 4.4.4.1 | Floating Add and Subtract          | 4-13 |

| 4.4.4.2 | Floating-Point Multiply            | 4-16 |

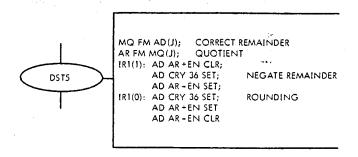

| 4.4.4.3 | Floating-Point Divide              | 4-17 |

| 4.4.4.4 | Floating Scale                     | 4-18 |

| 4.4.4.5 | Double-Floating Negate             | 4-18 |

| 4.5     | KA10 Console Key Logic             | 4-19 |

| 4.5.1   | STOP Key                           | 4-19 |

| 4.5.2   | RESET Key                          | 4-19 |

| 4.5.3   | REPEAT Key                         | 4-19 |

| 4.5.4   | START Key                          | 4-19 |

| 4.5.5   | CONTINUE Key                       | 4-20 |

| 4.5.6   | EXAMINE, DEPOSIT, and EXECUTE Keys | 4-20 |

| 4.5.7   | READ IN Key                        | 4-20 |

| 4.6     | KA10 Memory Control                | 4-20 |

| 4.6.1   | Memory Subroutine                  | 4-20 |

| 4.6.2   | Read Cycles                        | 4-21 |

| 4.6.3   | Write Cycles                       | 4-22 |

| 4.6.4   | Read/Write Cycles                  | 4-22 |

| 4.6.5   | Memory Indicator Register          | 4-23 |

| 4.6.6   | Address Stop or Break              | 4-23 |

| 4.6.7   | Input/Output System                | 4-23 |

| 4.6.8   | I/O Instructions                   | 4-24 |

| 4.7     | KA10 Priority Interrupt System     | 4-24 |

| 4.7.1   | User Mode Logic                    | 4-25 |

|         |                                    |      |

| CHAPTER | 5 BASIC I/O DEVICES                |      |

| 5.1     | Paper Tape Reader                  | 5-1  |

| 5.2     | Paper Tape Punch                   | 5-1  |

| 5.3     | Teleprinter Control                | 5-2  |

| CHAPTER 6 KA10 TROUBLE SHOOTING AND MAINTENANCE  6.1 Troubleshooting  6.2 Test Equipment  6.3 Processor Test Programs  6.3.1 Description  6.3.2 Recognizing an Error  6.3.3 Typical Diagnostic Check  6.3.4 Troubleshooting with Test Programs A through C  6.3.5 Troubleshooting with Diagnostic D  6.3.6 Troubleshooting with Test Programs E through M and P  6.3.7 Troubleshooting with Test Program N  6.4 Margin Check System  6.4.1 Considerations for Running Margins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |    |       |              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|-------|--------------|

| 6.2 Test Equipment 6.3 Processor Test Programs 6.3.1 Description 6.3.2 Recognizing an Error 6.3.3 Typical Diagnostic Check 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |    |       |              |

| 6.3 Processor Test Programs 6.3.1 Description 6.3.2 Recognizing an Error 6.3.3 Typical Diagnostic Check 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | •  |       | 6-1          |

| 6.3.1 Description 6.3.2 Recognizing an Error 6.3.3 Typical Diagnostic Check 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |       | 6-1          |

| 6.3.2 Recognizing an Error 6.3.3 Typical Diagnostic Check 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |    |       | 6-1          |

| 6.3.3 Typical Diagnostic Check 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |    |       | 6-1          |

| 6.3.4 Troubleshooting with Test Programs A through C 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |    |       | 6-3          |

| 6.3.5 Troubleshooting with Diagnostic D 6.3.6 Troubleshooting with Test Programs E through M and P 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |    |       | 6-4          |

| <ul> <li>6.3.5 Troubleshooting with Diagnostic D</li> <li>6.3.6 Troubleshooting with Test Programs E through M and P</li> <li>6.3.7 Troubleshooting with Test Program N</li> <li>6.4 Margin Check System</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | •  |       | 6-4          |

| 6.3.7 Troubleshooting with Test Program N 6.4 Margin Check System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |    | :*    | 6-6          |

| <ul><li>6.3.7 Troubleshooting with Test Program N</li><li>6.4 Margin Check System</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |    |       | 6-6          |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |    |       | 6 <b>-</b> 7 |

| 6.4.1 Considerations for Running Margins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |    |       | 6-9          |

| The state of the s |            |    |       | 6-9          |

| 6.4.2 Using the Margin Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |    |       | 6-10         |

| 6.4.3 Altered Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |    |       | 6-10         |

| 6.5 Troubleshooting Read In (RDI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |    | •     | 6-12         |

| 6.5.1 No Data Read In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |       | 6-12         |

| 6.5.2 Wrong Data Read In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            |    |       | 6-13         |

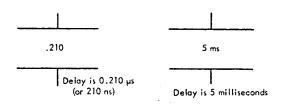

| 6.6 Delay Checks and Adjustments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ٠          |    |       | 6-14         |

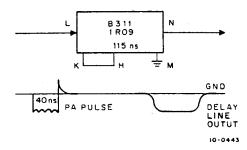

| 6.6.1 SCT3 Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |    |       | 6-14         |

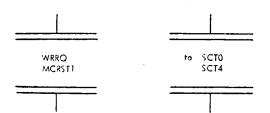

| 6.6.2 SCT2 Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |    |       | 6-14         |

| 6.6.3 FDT1 Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |    |       | 6-14         |

| 6.6.4 DST1 Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |    |       | 6-14         |

| 6.6.5 MC RQ SET Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |       | 6-14         |

| 6.6.6 MR PWR CLR ENB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |    |       | 6-14         |

| 6.6.7 MC NON EX MEM Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            |    |       | 6-15         |

| 6.6.8 IOT T2 and IOT RESTART Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |    |       | 6-15         |

| 6.6.9 IOT T4 and IOT RESET Delays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |    |       | 6-15         |

| 6.6.10 KEY REPT DLY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |    | 10.87 | 6-15         |

| 6.6.11 PTP SCR DRIVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |    |       | 6-15         |

| 6.7 Indicator Checks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |    |       | 6-15         |