| KKK       | KKK | 0000000000 | 11111111 | 00000 | 0000  |

|-----------|-----|------------|----------|-------|-------|

| KKK       | KKK | CCCCCCCCCC | 11111111 | 00000 | 0000  |

| KKK       | KKK | CCCCCCCCCC | 11111111 | 00000 | 0000  |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | FFI      | COO   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKKKKKKKK |     | CCC        | 111      | 000   | 000   |

| KKKKKKKKK |     | CCC        | 111      | 000   | 000   |

| KKKKKK    | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCC        | 111      | 000   | 000   |

| KKK       | KKK | CCCCCCCCCC | 11111111 | 00000 | 0000  |

| KKK       | KKK | CCCCCCCCCC | 11111111 | 00000 | 0000  |

| KKK       | KKK | 2222222222 | 11111111 | 00000 | 00000 |

| MMM    |       | MMM  | EEEEEEEEEEEEE | MMM    | MMM    |

|--------|-------|------|---------------|--------|--------|

| MMM    |       | MMM  | EEEEEEEEEEEEE | MMM    | MMM    |

| MMM    |       | MMM  | EEEEEEEEEEEEE | MMM    | MMM    |

| MMMM   | MM MM | MMMM | EEE           | MMMMMM | MMMMMM |

| MMIM   | MM MM | MMMM | EEE           | MMMMMM | MMMMMM |

| MMP MI | MM MM | MMMM | EEE           | MMMMMM | MMMMMM |

| MMM    | MMM   | MMM  | EEE           | MMM MM | MMM MI |

| MMM    | MMM   | MMM  | EEE           | MMM MM | MMM MI |

| MMM    | MMM   | MMM  | EEE           | MMM MM | MMM NI |

| MMM    |       | MMM  | EECEEEEEEEE   | MMM    | MMM    |

| MMM    |       | MMM  | EEEEEEEEEE    | MMM    | MMM    |

| MMM    |       | MMM  | EEEEEEEEEEE   | MMM    | MMM    |

| MMM    |       | MMM  | EEE           | MMM    | MMM    |

| MMM    |       | MMM  | EEE           | AMM    | MMM    |

| MMM    |       | MMM  | EEE           | MMM    | MMM    |

| MMM    |       | MMM  | EEE           | MMM    | MMM    |

| MMM    |       | MMM  | EEE           | MMM    | MMM    |

| MMM    |       | MMM  | EEE           | MMM    | Mrim   |

| MMM    |       | MMM  | EEEEEEEEEEEEE | MMM    | MMM    |

| MMM    |       | MMM  | EEEEEEEEEEEEE | MMM    | MMM    |

| MMM    |       | MMM  | ESEEEEEEEEEEE | MMM    | MMM    |

|        |       |      |               |        |        |

\*START\* Job ETHER Req #83 for TARL [10,5535] Date 26-Jul-83 0:52:11 Monitor: RL152A DEC10 Dev File DSKA:KCIO.MEM[5,100], created: 7-Mar-82 21:17:00, printed: 26-Jul-83 0:52:25 Job parameters: Request created:26-Jul-83 0:52:07 Page limit:3033 Forms:XEROX Account:1'd r File parameters: Copy: 1 of 1 Spacing:SINGLE File format:ASCII Print mode:ASCII

# !digital! INTEROFFICE MEMORANDUM

TO: List

DATE: 07 Mar 82

FROM: R. McLean

G. M. Uhler

DEPT: L.S.E.G

LOC: MR1-2/E85

EXT: 231-6113

DISTRIBUTED:

07 Mar 82

FILE: KCIO.RNO

REVISION: 6

SUBJ: KC10 Exec Mode

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this socument.

Digital Equipment Corporation assumes no responsibility for the use or reliability of its software on equipment that is not supplied by DIGITAL.

Copyright (C) 1980, 1981, 1982 by Digital Equipment Corporation

The following are trademarks of Digital Equipment Corporation:

DIGITAL DECsystem-10 DEC DECtape PDP DIBOL DECUS EDUSYSTEM UNIBUS FLIP CHIP COMPUTER LABS FOCAL COMTEX INDAC TDD LAB-8 DECCOM DECSYSTEM-20 MASSBUS

OMNIBUS

OS/8

PHA

RSTS

RSX

TYPESET-8

TYPESET-10

TYPESET-11

Changes made to revision 5 of KCIO to create revision 6 on 08-Mar-82.

- 1. Declare XBLT to be legal in section 0.

- 2. Document the differences between the KL and KC implementation of JRST n,. Allow SFM in any section. Add the XJRST (JRST 15,) instruction.

- Document the occurrance of an IBOX flush on WRCTX, WREBR, CLRPT, and SWPIA.

- 4. Redesign the WRTMB and RDTMB instructions. Add the WRACT, RDACT instructions.

- 5. Remove the 18 bit EA restriction from PMOVE and PMOVEM in section 0.

- 6. Document the changes to the legal PXCT bits.

- 7. Change SETCU from 700100,,0 to 701000,,0.

- 8. Change RDUBR from 700040,,0 to 701400,,0.

- Change the format of E+1 of the WRCTX, RDCTX, and RDUBR blocks to match that of the first word of the flags/PC double word.

- 10. Make UMOVE/UMOVEM generate an illegal instruction trap if executed in user mode.

- 11. Add functional descriptions for WRCTX, WREBR, WRTMB, and WRACT.

- 12. Change the polarity of bit 10 returned in the MAP instruction Ac.

- 13. Remove function code 3 from the trap function word.

- 14. Remove the "do not load current AC block values" bit from the interrupt vector word.

- 15. Move the control bits around in word E of the WRCTX (and RDCTX and RDUBR) block to make it easier to implement.

- 16. Remove the "do not load AC block values" bit from the WRCTX block.

- 17. Move the mapping for exec pages 0-337 with TOPS-10 paging from words 600-757 in the EPT to 0-157 in the EPT.

- 18. Remove the "FPA present" from the hardware options field in APRID and put it in the microcode options field.

- 19. Remove the JEN instruction.

- 20. Redefine the algorithm used to compute a physical address for PMOVE, PMOVEM, and the queue instructions.

- 21. Redefine words 453-454 in the UPT (page fail block) to be "additional data" returned on a page fail. These words will be different for each type of page fail code and will be documented as such.

- 22. Modify MUUO, page fail, I/O page fail, and traps (MUUO function) to "load" PAB instead of "setting" it.

- 23. Make super section pointer types 1 (immediate) and 3 (indirect) legal.

- 24. Start the page fail block in the UPT at offset 451 instead of 450.

- Change the page number field in an immediate pointer from bits 20-35 to 18-35.

- 26. Document the format of the "page address word" encountered in pointer traces.

- 27. Add a description of the debugging instruction implemented by the microcode.

- 28. Describe the paging information cache.

- 29. Change the format of the page fail word to include the "level" at which the page fail was detected.

- 30. Describe the CST update operation.

- 31. List the processor flags in the description of the Flags/PC double word.

- 32. Define the page fail codes for TOPS-20 paging.

- 33. Describe bits 0-10 of the page fail PMA as "reserved" instead of zeros. They come back undefined from the MBOX and it didn't seem particularly necessary to mask them since the monitor probably won't use the word anyway.

- 34. Note that the trap 1 and trap 2 flags are never stored in the LUUO/MUUO block when a trap that specifies function code 1 (MUUO) or 2 (LUUO) is processed.

- 35. Note that an instruction that references multiple words (e.g., BLT) will not cause an address break for every word in the address break range if the monitor restarts the instruction with the "inhibit address break" flag set.

- Add the trap enable bit to WREBR and RDEBR and explain how it works.

- Add descriptions for the debugging instructions RDTRAX and WRTRAX.

- 38. Add a new chapter for miscellany and start it by describing the halt status codes.

- 39. Change the format of the I/O page fail block to make it more consistent with the normal page fail block.

- 40. Document the effect of a write reference for the various combination of written and modified bits in the translation buffer.

Changes made to revision 4 of KCIO to create revision 5 on 18-Aug-81.

- 1. Add the definition of the bits returned by the MAP instruction.

- 2. Define bit 0 of the microcode options field in APRID as "diagnostic microcode loaded".

- 3. Move the remaining APR flag bits in WRAPR and RDAPR to bits 30 and 31 to right justify them in the field and make them contiguous

- 4. Add the "VM mode" state bit as bit 10 in word E for WRCTX, RDCTX, and RDUBR. Also use UPT location 431 as the VM mode new PC MUUO dispatch.

- 5. Add a statement that pager clears caused by CLRPT and WREBR ignore the keep me bit.

- Declare the results of executing a UMOVE or UMOVEM in user mode as undefined.

- 7. Define bit 19 in the RNGB? instructions to perform a port init for the port specified by bits 33-35.

- Put all the accounting meter stuff under an "available with the accounting meter option only" disclaimer.

- 9. Remove the "Port interrupt logout word" from the 1/0 page and add 8 "port interrupt PI status words".

- 10. Remove the SWPVA instruction from the instruction set.

- 11. Change the spec to indicate that no flags are loaded on a LUUO.

- 12. Move the address break condition bits from 0-7 to 10-17 in the WRCTX/RDCTX argument.

- Require that paging be turned on to load the address break conditions with WRCTX or to read them with RDCTX.

- 14. Rearrange the WRCTX control bits.

- 15. Rearrange the bits in RNGB and RNGBW one more time.

- 16. Remove the cache look and load bits from WREBR and RDEBR and the TB cacheable bit from the page table pointer and add cache on/off controls bits to WREBR and RDEBR.

- Do not cause an IBOX flush as the result of a cache sweep instruction.

- 18. Remove time base 1 completely and remove the time base 2 words in the EPT (they're now kept strictly in EBOX scratchpad locations).

- 19. Redesign the time base and interval timer instructions.

- 20. Add the RDURTM instruction to read the user runtime meter.

- 21. Add the page fail formats.

- Remove the discussion of the UBA from the interrupt vector definitions.

Changes made to revision 3 of KCIO to create revision 4 on 30-Apr-81.

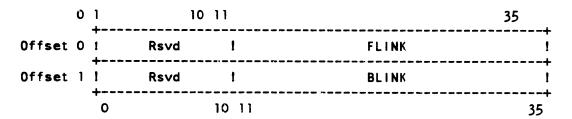

- 1. Reserve bits 0-10 of the link words of physical queues.

- 2. Change the console reload bit in RNGB and RNBBW from bit 19 to bit 18.

- 3. Describe the relationship between the effective address calculation and the reference address for those instructions that use the EA as a physical address.

- 4. Reserve bits 0-10 of AC for the queue instructions and define the action on bit 0 in the AC on an empty/non-empty queue.

- 5. Document the MUUO block and the new PC dispatch vectors. Change the spec to reflect the new dispatch algorithm approved by the architecture committee. Move the page fail locations from location starting at 440 to locations starting at 450 to make room for the new MUUO dispatch.

- 6. Document the LUUO block format and the action of the processor to an LUUO.

- 7. Clean up the trap function word definitions and change functions 1 and 2 to agree with the decisions of the architecture committee.

- 8. Clean up the interrupt vector description and document the format of the I/O page fail block in the I/O page.

- Clean up the queue instruction explanations. Thank you Judy Hall.

- 10. Redo the entire chapter on virtual addressing (and rename it "paging") to add much more information.

- 11. Describe the changes to the MAP instruction.

Changes made to revision 2 of KCIO to create revision 3 on 19-Mar-81:

- Add the SETCU instruction to set the CST update needed bit in each page table entry.

- 2. Note that PMOVE, PMOVEM and the physical queue instructions do not cause the CST to be updated.

- Remove the INSQUE and REMQUE instructions and the references to virtual queues.

- 4. Add pictures for the EPT, UPT and I/C page. Also provide separate picture for TOPS-10 and TOPS-20 for the first two.

- 5. Change the format of the trap function word that simulates a LUUO to specify the opcode of the LUUO to be used in the function word.

6. Change the definition of the queue manipulation instructions to skip return if the entry has been successfully added to the queue with bit 0 in the AC set if the entry was added to an empty queue. The instruction will not skip if the secondary interlock was timed out.

Changes made to revision 1 of KCIO to create revision 2 on 9-Mar-81:

- 1. Add definition of "reserved" fields of instruction operands and data.

- 2. Define all bits of instruction operands and data.

- 3. Add "KL/KS compatibility" section to each instruction description.

- 4. Add an enable bit to load the CPU PIA in WRAPR.

- 5. Change the page number field for WRCTX, WREBR and WRIOP from bits 18-35 to bits 20-35

- 6. Remove the commitment to make a PXCT of a CLRPT work.

- 7. Define what "TOPS-10" paging really means.

- 8. Change the "Interrupt 2080 console" bit in RNGB and RNBGW from bit 18 to bit 32.

- 9. Change the description of the operation of PMOVE and PMOVEM to do a normal effective address calculation and use the result as a physical address.

- 10. Change the definition of WRIOP from an immediate mode instruction to one which takes its data from the word addressed by E.

| CHAPTER | 1                                                            | INTRODUCTION                               |

|---------|--------------------------------------------------------------|--------------------------------------------|

| CHAPTER | 2                                                            | INTERNAL I/O INSTRUCTIONS                  |

| CHAPTER | 3                                                            | EXTERNAL I/O INSTRUCTIONS                  |

| CHAPTER | 4                                                            | OTHER I/O INSTRUCTIONS                     |

| CHAPTER | 5                                                            | OTHER FUNCTIONAL CHANGES                   |

| CHAPTER | 6                                                            | SPECIAL DEBUGGING INSTRUCTIONS             |

| CHAPTER | 7                                                            | QUEUES AND QUEUE MANIPULATION INSTRUCTIONS |

|         | 7.2<br>7.2.1<br>7.2.2<br>7.3<br>7.3.1<br>7.3.2<br>7.4<br>7.5 | INTRODUCTION                               |

| CHAPTER | 8                                                            | PAGING                                     |

|         | 8.2<br>8.3<br>8.4                                            | INTRODUCTION                               |

|         |                                                      | Page Fail Conditions And Formats $\delta$ -22                                                                                                          |

|---------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER | 9                                                    | PROCESS CONTEXT VARIABLES                                                                                                                              |

|         | 9.1<br>9.1.1<br>9.1.2                                | INTRODUCTION                                                                                                                                           |

| CHAPTER | 10                                                   | SYSTEM TIMERS                                                                                                                                          |

|         | 10.1<br>10.2<br>10.2.1<br>10.2.2<br>10.3             | SUMMARY       10-1         TIME CLOCKS       10-1         Time Base       10-2         User Runtime Meter       10-2         INTERVAL TIMER       10-2 |

| CHAPTER | 11                                                   | TRAP, UUO AND INTERRUPT HANDLING                                                                                                                       |

|         | 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7 | INTRODUCTION                                                                                                                                           |

| CHAPTER | 12                                                   | MISCELLANY                                                                                                                                             |

|         | 12.1                                                 | HALT STATUS CODES 12-1                                                                                                                                 |

| CHAPTER | 13                                                   | SPECIAL SYSTEM PAGES (EPT / UPT / 10P)                                                                                                                 |

| CHAPTER | 14                                                   | ADDRESS BREAK                                                                                                                                          |

Index

## CHAPTER 1

#### INTRODUCTION

This document describes the operation of the Exec Mode and 1/0 instructions on the KC10. It also describes the differences between the instruction set implementation on the KL and KS processors and that implemented by the KC10. All 1/0 instructions are ordinary instructions with the same format as normal instructions (opcode, AC and effective address). The opcodes are in the range 700 thru 777.

Any operation code in the range 700 thru 777, AC number, field or bit not described in this document should be considered reserved to DEC.

Instructions with opcodes between 700 and 737, inclusive, are legal in exec mode or in user 1/0 mode. Instructions with opcodes between 740 and 777, inclusive, are legal in both exec and user modes.

INTRODUCTION Page 1-2

## OPCODE Assignment Map

|     | 0      | 1      | 2       | 3       | 4       | 5       | 6       | 7      |

|-----|--------|--------|---------|---------|---------|---------|---------|--------|

| 700 | APRO   | APR1   | APR2    | _       | UMOVE   | UMOVEM  | PMGVE   | PMOVEM |

| 710 | RNGB   | RNGBW  | SNBSY   | -       |         | -       | -       | -      |

| 720 | INSQHI | INSQTI | REMQHI  | REMQTI  | -       | -       | -       | -      |

| 730 | -      | -      | RDTRAX* | WRTRAX* | READTB* | WRITTB* | DUMPTB* | ~      |

| 740 | -      | -      | -       | -       | -       | -       | -       | -      |

| 750 | -      | -      | -       | -       | -       | -       | -       | -      |

| 760 | -      | -      | -       | -       | -       | -       | -       | -      |

| 770 | -      | -      | -       | -       | -       | -       | -       | -      |

<sup>\* -</sup> Debug instructions. Not in production machine.

# AC Field Assignments

| AC | 700   | <b>70</b> 1 | 702    |

|----|-------|-------------|--------|

| 00 | APRID | SETCU       | RDSPB  |

| 01 | -     | RDCTX       | RDCSB  |

| G2 | -     | CLRPT       | RDPUR  |

| 03 | -     | WRCTX       | RDCSTM |

| 04 | WRAPR | WREBR       | RDTMB  |

| 05 | RDAPR | RDEBR       | RDINT  |

| 06 | SZAPR | WRIOP       | RDTIME |

| 07 | SNAPR | RDIOP       | RDURTM |

| 10 | -     | RDUBR       | WRSPB  |

| 11 | -     | SWPIA       | WRCSB  |

| 12 | -     | -           | WRPUR  |

| 13 | -     | SWPUA       | WRCSTM |

| 14 | WRPI  | -           | WRTMB  |

| 15 | RDPI  | -           | WRINT  |

| 16 | SZ71  | -           | WRACT  |

| 17 | SNPI  | -           | RDACT  |

## CHAPTER 2

## INTERNAL I/O INSTRUCTIONS

These instructions control the CPU. They transfer no data between the outside world and the CPU or memory.

## \*\*\*\*\* WARNING \*\*\*\*\*

In some instances, fields of operands of an instruction or fields of the values returned by an instruction are described as "reserved". This means simply that no guarantee is made of the correct operation of an instruction whose "reserved" fields are set non-zero by the program or of the state of the bits in the "reserved" fields returned by an instruction. If you wish to experiment and find a result to your liking, you are hereby warned that your program may well not be compatible with any other processor, with any other model of your processor, with the same model of your processor at some other installation, or even with your own processor running at some other time with a different version of the microcode or Monitor.

#### Conventions

When the definition of a bit is given in this document, that definition applies when the bit is set to a l (unless explicitly stated otherwise). If the bit is set to a zero, the logical complement of the definition applies. For example, bit l in word E in APRID below is described as "FPA present". This means that the FPA is present in the machine if the bit is a l and not present if the bit is a 0.

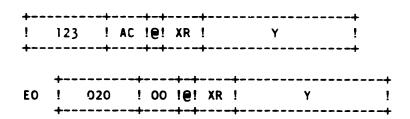

## APRID

| +- |     | -+- |    | -+-+ |    | -+- |   | + |

|----|-----|-----|----|------|----|-----|---|---|

| !  | 700 | !   | 00 | !@!  | УR | !   | Y | ! |

| +- |     | -+- |    | -+-+ |    | -+- |   | + |

This instruction stores the microcode version number, CPU serial number, and processor options in the words addressed by E and E+1. The format of the first word (E) is:

0-8 Reserved for microcode options.

O Diagnostic microcode loaded

1 FPA present

9-17 Hardware options

18-35 Processor serial number

The format of the second word (E+1) is:

0-35 Microcode version number

## KL/KS compatibility

The KL and KS returned microcode options, microcode version number, hardware options and processor serial number in one word. The KC returns two words and defines different hardware and microcode option bits.

#### WRAPR

| + |     | +- |    | -+-+         |    | +-  |   | + |

|---|-----|----|----|--------------|----|-----|---|---|

| ! | 700 | !  | 04 | ! <b>e</b> ! | XR | !   | Y | ! |

| + |     | +- |    | -+-+         |    | -+- |   | + |

This immediate mode instruction decodes its effective address to control the processor. The effective address bits are used as follows:

- 18 Load the PIA for the CPU from bits 33-35.

- 19 I/O reset. When this bit is set, "reset" is asserted on the KC10 I/O bus. This will reset all the port micromachines (but affects no internal devices, such as the pager and processor flags).

- 20 Enable conditions selected by bits 24 thru 31 to cause interrupts.

- Disable interrupts for conditions selected by bits 24 thru 31.

- 22 Clear flags indicated by bits 24 thru 31.

- 23 Set flags indicated by bits 24 thru 31.

## WARNING

The action of the processor is not defined when both bits 20 and 21 or 22 and 23 are set in the same instruction.

- 24-31 Selected flags

- 24-29 Reserved

- 30 Console attention

- 31 Power failure

- 32 Reserved

- 33-35 PIA for CPU

## KL/KS compatibility

The KL and KS unconditionally set the CPU PIA. The KC only sets the PIA if bit 18 is on. The KC also defines different flags in bits 24-31.

## RDAPR

|                                |   | + |     | +- |    | -+-+ |    | -+ |   | + |

|--------------------------------|---|---|-----|----|----|------|----|----|---|---|

| ! 700 ! 05 ! <b>@</b> ! XR ! Y | ! | ! | 700 | !  | 05 | !@!  | XR | !  | Y | ! |

This instruction stores the APR status in the word addressed by E. The status is as follows:

| 0-5   | Reserved                                 |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

| 6-13  | interrupts enabled                       |  |  |  |  |  |  |  |

| 6-11  | Reserved                                 |  |  |  |  |  |  |  |

| 12    | Console attention enabled                |  |  |  |  |  |  |  |

| 13    | Power failure enabled                    |  |  |  |  |  |  |  |

| 14-23 | Reserved                                 |  |  |  |  |  |  |  |

| 24-31 | Interrupts pending                       |  |  |  |  |  |  |  |

| 24-29 | Reserved                                 |  |  |  |  |  |  |  |

| 30    | Console attention                        |  |  |  |  |  |  |  |

| 31    | Power failure                            |  |  |  |  |  |  |  |

| 32    | Interrupt requested (IOR of bits 24-31). |  |  |  |  |  |  |  |

## KL/KS compatibility

33-35 PIA for CPU

The KC defines different flags in bits 24-31.

## SZAPR

| +   |     | -+- |    | -+-+         |    | -+- |   | + |

|-----|-----|-----|----|--------------|----|-----|---|---|

| !   | 700 | !   | 06 | ! <b>@</b> ! | XR | !   | Y | ! |

| +~- |     | -+- |    | -+-+         |    | -+- |   | + |

This instruction tests the input conditions from the APR right 18 bits. If all condition bits selected by 1s in E are 0s, skip the next instruction in sequence.

KL/KS compatibility

Functionally identical to CONSZ APR, E.

## SNAPR

| + |     | +-  |    | -+-+-        |    | -+- |   | + |

|---|-----|-----|----|--------------|----|-----|---|---|

| ! | 700 | !   | 07 | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | -+- |    | -+-+-        |    | -+- |   | + |

This instruction tests the input conditions from the APR right 18 bit. If any condition bit selected by 1 in E is 1, skip the next instruction in sequence.

KL/KS compatibility

Functionally identical to CONSO APR, E.

#### WRPI

| + |     | -+- |    | -+-+         |    | +- |   | + |

|---|-----|-----|----|--------------|----|----|---|---|

| ! | 700 | !   | 14 | ! <b>@</b> ! | XR | !  | Y | ! |

| + |     | -+- |    | -+-+         |    | +- |   | + |

This immediate mode instruction decodes its effective address to control the priority interrupt system. The effective address bits are used as follows:

| 18-21 | Reserved                                                                                                                                                                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22    | Turn off program requests on the levels selected by is in bits 29-35.                                                                                                                                                                             |

| 23    | Clear PI system.                                                                                                                                                                                                                                  |

| 24    | Initiate interrupts on the levels selected by 1s in bits 29-35. Such interrupts vector through the software interrupt vector words in the I/O page. An interrupt is not initiated on a level unless the PI system and the requested level are on. |

| 25    | Turn on the levels selected by ls in bits 29-35.                                                                                                                                                                                                  |

| 26    | Turn off the levels selected by 1s in bits 29-35.                                                                                                                                                                                                 |

## WARNING

The action of the processor is not defined when both 25 and 26 or 22 and 24 are set in the same instruction.

| 27    | Turn off PI system                         |

|-------|--------------------------------------------|

| 28    | Turn on PI system                          |

| 29-35 | Select levels for bits 22, 24, 25, and 26. |

## KL/KS compatibility

The KL used bits 18-20 to force parity errors. The KL initiated an interrupt on a level as the result of a lin bit 24 even if the specified level was off. Although the KS is documented to act in the same manner, it did not initiate the interrupt unless the level was on.

RDPI

| ! | 700 | ! | 15 | ! <b>@</b> ! | XR | ! | Y |  |

|---|-----|---|----|--------------|----|---|---|--|

|---|-----|---|----|--------------|----|---|---|--|

This instruction stores the PI status in the word addressed by E. The status is a follows:

| 0-10  | Reserved                        |

|-------|---------------------------------|

| 11-17 | Program requests on levels.     |

| 18-20 | Returned as zeroes              |

| 21-27 | Interrupt in progress on levels |

| 28    | PI system on.                   |

| 29-35 | Levels on.                      |

## KL/KS compatibility

The KL returned the state of the forced parity error bits in bits 18-20. Otherwise, it is functionally equivalent to CONI PI,E on the KL and RDPI E on the KS.

SZPI

| + |     | -+- |    | -+-+         |    | -+- |   | + |

|---|-----|-----|----|--------------|----|-----|---|---|

| ! | 700 | !   | 16 | ! <b>@</b> ! | XR | ļ   | Y | ! |

| + |     | -+- |    | -+-+         |    | -+- |   | + |

This instruction tests the input conditions from the PI right 18 bits. If all condition bits selected by 1s in E are 0s, skip the next instruction in sequence.

KL/KS compatibility

Functionally equivalent to CONSZ P!,E.

SNPI

| +- |     | -+- |    | -+-+ |    | -+- |   | + |

|----|-----|-----|----|------|----|-----|---|---|

| !  | 700 | !   | 17 | !@:  | XR | !   | Y | ! |

| +- |     | -+- |    | -+-+ |    | -+- |   | + |

This instruction tests the input conditions from the PI right 18 bit. If any condition bit selected by 1 in E is 1, skip the next instruction in sequence.

KL/KS compatibility

Functionally equivalent to CONSO PI,E.

## WRCTX

| +- |     | -+- |    | -+-+         |    | -+- |   | + |

|----|-----|-----|----|--------------|----|-----|---|---|

| !  | 701 | !   | 03 | ! <b>e</b> ! | XR | !   | Y | ! |

| +- |     | -+- |    | -+-+         |    | +-  |   | + |

This instruction loads user process context from a variable number of words addressed by E through E+4 depending on the flag bits in the first word. The process context includes previous and current AC blocks, previous context section, user base register, virtual machine simulation mode enable, and address break enable and conditions.

The format of the first word (E) is:

- O Load current and previous AC block numbers (CAB, PAB) from bits 18-23 of word E+1.

- 1 Load previous context section (PCS) from bits 24-35 of word E+1.

- 2 Load the user base register (UBR) from bits 20-35 of this word.

- Clear all pages from the hardware page table (include "kept" pages) when the pager clear is done.

- Do not change the state of the user runtime meter (nether update it into the old PT or load it from the new UPT).

- 5 Load VM-moue enable from bit 6 of this word.

- 6 Enable virtual machine (VM-mode) simulation mode for this user context.

- 7 Inhibit all address break conditions for the next instruction executed. The effect of setting this bit is to set the inhibit address break PC flag for the next instruction.

- 8 Load address break conditions from the words at E+2 through E+4.

- 9 Load address break enable from bit 10 of this word.

- 10 Enable address break using the existing conditions (the conditions may be also be changed with the same instruction).

| 11-19 | Reserved |

|-------|----------|

|-------|----------|

20-35 Physical page number of UPT.

## The format of the second word (E+1) is:

| 0-17 | Reserved |

|------|----------|

|------|----------|

18-20 Current AC block

21-23 Previous AC block

24-35 Previous Context Section

## The format of the third word (E+2) is:

## 0-9 Reserved

- Enable address break for a normal fetch of an instruction in the program under control of PC.

- Enable address break for any reference that reads except the normal fetch of an instruction.

- 12 Enable address break for any reference that writes.

- Enable address break for a reference made in user virtual address space. (0 selects executive space).

- Enable address break for a reference made by the CPU to memory.

- 15 Enable address break for a reference made by a port to memory.

- Enable address break for a physical memory reference. (0 selects virtual memory references).

- 17 Compare only bits 18 through 35 of the reference address with the address range when doing address compares.

## 18-35 Reserved

The format of the fourth word (E+3) is:

0-5 Reserved

6-35 The lower bound break address.

The format of the fifth word (E+4) is:

0-5 Reserved

6-35 The upper bound break address.

In word E, bits 0-2, 5, and 7-9 control the action of this instruction; when a bit is 0, the corresponding action is ignored. The actions are as follows:

- 1. If bit 0 is on, load CAB and PAB from bits 18-20 and 21-23, respectively, from word E+1. If bit 0 is off, do not change CAB and PAB.

- 2. If bit 1 is on, load PCS from bits 24-35 of word E+1. If bit 1 is off, do not change PCS.

- 3. If bit 2 is on, perform the following functions:

- If bit 3 in E is 0, clear all pages except those marked "kept" in the page table. If bit 3 is 1, clear all entries.

- 2. Load bits 20-35 of E into the User Base Register

- 3. If bit 4 in E is 0, perform the following functions:

- Update the user runtime meter into the previous UPT by simulating a RDURTM instruction and storing the resulting dou<sup>1</sup> eword in the previous UPT in locations 504-505.

- 2. Load the user runtime meter kept in the EBOX internal registers from locations 504-505 of the new UPT.

If bit 4 is a 1, do not update the user runtime meter into the previous UPT and do not reload it from the new UPT.

4. Clear the internal cache of paging information kept by the EBOX and re-initialize it with the first super section pointer from the EPT and the UPT (offset 520).

- 5. If bit 5 is on, perform the following functions:

- If bit 6 is on, enable virtual machine simulation mode (VM-mode) for this user context. If bit 6 is off, disable VM-mode for this user context.

If bit 5 is off, do not change the state of VM-mode.

- 6. If bit 7 is on, inhibit all address break traps for the next instruction executed after the WRCTX. If bit 7 is off, do not inhibit address break traps.

- 7. If bit 8 is on, load the address break conditions from the words at E+2 through E+4. If bit 8 is off, the address break conditions remain unchanged.

#### NOTE

Paging must be enabled (with WREBR bit 4) to load the address break conditions. If paging is not enabled, the result of loading the address break conditions is undefined.

- 8. If bit 9 is on, perform the following functions:

- If bit 10 is on, turn on address break using the existing break conditions (which may be set in the same instruction by setting bit 8 to a one). If bit 10 is off, turn off address break but leave the break conditions unchanged.

If bit 9 is off, do not change the state of address break enable.

9. Flush and restart the IBOX.

See the chapter on Address Break for a functional description.

## KL/KS compatibility

The KL set current and previous AC blocks, previous context section, and the physical page number of the UPT with a DATAO PAG, E. Address break conditions and address were set with a DATAO APR, E. The KS set current and previous AC blocks, and the physical page number of the UPT with a WRUBR E. The KC WRCTX instruction combines the functions of these instructions.

## RDCTX

| + |      | -+- |    | -+-+ |    | -+- |   | + |

|---|------|-----|----|------|----|-----|---|---|

| ! | 70 i | !   | 01 | !@!  | XR | !   | Υ | ! |

| + |      |     |    | -+-+ |    | -+- |   | + |

This instruction stores the user process context in the five words addressed by E through E+4 in exactly the same format as used by WRCTX. In order to allow these words to be used directly in a WRCTX instruction, bits 0-2, 5, 8, and 9 are set to 1 and bits 3, 4, and 7 are set to 0 in E.

#### NOTE

Paging must be enabled (with WREBR bit 4) to read the address break conditions. If paging is not enabled, the values returned in words E+2 through E+4 (address break conditions, lower and upper address bounds) are undefined.

### KL/KS compatibility

The KL returned current and previous AC blocks, previous context section, and the physical page number of the UPT with a DATAI PAG,E. Address break conditions were returned with a DATAI APR,E. The KS returned current and previous AC blocks, and the physical page number of the UPT with a RDUBR E. The KC RDCTX instruction combines the functions of these instructions.

## RDUBR

| + |             | +- |    | +-+- |    | +- |   | -+ |

|---|-------------|----|----|------|----|----|---|----|

| ! | <b>7</b> 01 | !  | 10 | 10!  | XR | !  | Υ | !  |

| + |             | +- |    | +-+- |    | +- |   | -+ |

This instruction stores the user process context in the two words addressed by E and E+1 in exactly the same format as the first two words used by WRCTX. In order to allow these words to be used directly in a WRCTX instruction, bits 0-2, 5, and 9 are set to 1 and bits 3,4,7, and 8 are set to 0 in E.

## KL/KS compatibility

The KL returned current and previous AC blocks, previous context section, and the physical page number of the UPT with a DATAI PAG,E. The KS returned current and previous AC blocks, and the physical page number of the UPT with a RDUBR E.

SETCU

| + |     | +-  |    | -+-+- |    | +-  |   | + |

|---|-----|-----|----|-------|----|-----|---|---|

| ! | 701 | !   | 00 | !@!   | XR | !   | Y | ! |

| + |     | -+- |    | +-+-  |    | -+- |   | + |

This instruction causes the "CST update needed" bit to be set in each entry in the hardware page table so that the next virtual reference to each page will cause the EBOX to update the CST entry for the page. This instruction blocks further CPU activity until all bits are set in the page table. Upon completion of the operation, the IBOX is flushed and restarted. The indirect, index register, and Y fields of this instruction are not used and are reserved.

KL/KS compatibility

No functional equivalent on the KL or KS.

CLRPT

| + |     | +- |    | -+-+- |    | -+- |   | + |

|---|-----|----|----|-------|----|-----|---|---|

| ! | 701 | !  | 02 | !@!   | XR | i   | Y | ! |

| + |     | +- |    | -+-+- |    | -+- |   | + |

This immediate mode instruction clears the hardware page table entry for the virtual page addressed by E so that the next virtual reference to a word in that page will cause an EBOX page fail trap to occur. The page table "keep me" bit is ignored by this instruction and an uncoditional clear is done. The actions performed by this instruction are as follows:

- 1. Clear the translation buffer entry for the virtual page addressed by E.

- Clear the internal cache of paging information kept by the EBOX (but do not clear the first exec and user super section pointer).

- 3. Flush and restart the IBOX.

KL/KS compatibility

Functionally equivalent to CLRPT E on the KL.

#### WREBR

| + |     | -+- |    | -+-+ |    | -+- |   | + |

|---|-----|-----|----|------|----|-----|---|---|

| ! | 701 | !   | 04 | 10!  | XR | !   | Y | ! |

| + |     | -+- |    | -+-+ |    | -+- |   | + |

This instruction loads the exec mode context from the word addressed by E. The exec mode context includes cache enable, type of paging, pager enable, trap enable, and the exec base register. The format of the word is:

- Load the cache enable bit from bit 1. This bit should never be set by the monitor. The cache will only be turned off as the result of a serious error and should remain off until the problem is fixed. The ability to enable and disable the use of cache is provided strictly for diagnostics.

- Enable use of the cache for all references. Enabling the use of the cache with this bit does not enable the use of all four cache quadrants if one has been turned off because of an error. It simply causes the cache to be used for any quadrants that are on.

- 2 Reserved

- 3 TOPS-20 paging (See the chapter on Paging)

- 4 Pager enable.

- 5-7 Reserved

- 8 Load trap enable from bit 9

- 9 Enable full processing of traps, LUUOs, MUUOs, and page fails

- 10-19 Reserved

- 20-35 Physical page number of EPT.

The actions performed by this instruction are as follows:

- 1. If bit 8 is a 1, perform the following functions:

- 1. If bit 9 is a 1, enable full processing of traps, LUU0s, MUU0s, and page fails by the monitor as described in the appropriate sections below.

- 2. If bit 9 is a 0, change the processing of certain processor conditions as follows:

- 1. Traps. Treat trap 1, 2, and 3 conditions as if the trap function word had specified "ignore trap".

- 2. LUUOs. Process section O LUUOs in the normal manner. Halt the machine on LUUOs executed in non-zero sections.

- 3. MUUOs. Halt the machine.

- 4. Page fails. Process page fails that can be resolved by the EBOX microcode alone in the normal manner. Halt the machine on page fails that must be processed by the monito.

If bit 8 is a 0, do not change the state of trap enable

- 2. If bit 0 is a 1, perform the following functions:

- 1. If bit 1 is a 1, enable the use of the cache as described above. If bit 1 is a 0, disable the use of the cache.

If bit 0 is a 0, do not change the state of the cache enable.

- 3. If bit 4 is a 1, perform the following functions:

- Enable the use of the paging hardware for virtual-to-physical translations for memory references and select the type of paging to be used.

- 2. If bit 3 is a 1, select TOPS-20 style paging. If bit 3 is a 0, select TOPS-10 style paging.

## NOTE

The type of paging referred to as "TOPS-10 paging" is really that implemented by the KI10 and used by the TOPS-10 monitor prior to the 7.02 release. It is used here for historical reasons only.

If bit 4 is a 0, disable paging so that all memory references are to physical locations unpaged. Note that disabling the pager does not mean there can be no page failures, as these can be caused by conditions that have nothing to do with paging.

## CAUTION

Paging can be disabled only for kernel mode. A user mode process will not run correctly unless the pager is turned on.

- 4. Load bits 20-35 into the Exec Base Register.

- Clear the internal cache of paging information kept by the EBOX and re-initialize it with the first super section pointer from the EPT and UPT (offset 520).

- 6. Invalidate all entries in the MBOX translation buffer, ignoring the state of the "keep-me" bits.

- 7. Flush the IBOX and restart it.

## KL/KS compatibility

The KL set exec mode context with the IMMEDIATE MODE instruction CONO PAG, E. The KS set exec mode context with the IMMEDIATE MODE instruction WREBR E.

## **RDEBR**

| ++ |     |      |              |    |   |   |   |  |  |

|----|-----|------|--------------|----|---|---|---|--|--|

| !  | 701 | ! 05 | ! <b>⊜</b> ! | XR | ! | Y | ! |  |  |

| ++ |     |      |              |    |   |   |   |  |  |

This instruction stores the exec mode context in the word addressed by E. The format of the word is:

- 0 Returned as zero

- The use of cache is enabled for all references. This bit being set does not imply that all four cache quadrants are in use. It simply means that the cache will be used for any quadrants that are on.

- 2 Reserved

- 3 TOPS-20 paging (See the chapter on Paging)

- 4 Pager enable.

- 5-7 Reserved

- 8 Returned as 0

- 9 Full processing of traps, LUUOs, MUUOs, and page fails is enabled

- 10-19 Reserved

- 20-35 Physical page number of EPT.

## KL/KS compatibility

The KL and KS returned the exec mode context with CONI PAG,E and RDEBR E, respectively. The KC returns the same fields as the KL CONI PAG,E but the bit positions have changed because of the increased size of the EPT page number.

WRIOP

| <b>T</b> – – – |     |   |    | +-+-         |    | -+ |   |  |

|----------------|-----|---|----|--------------|----|----|---|--|

| !              | 701 | ! | 06 | ! <b>@</b> ! | XR | !  | Y |  |

This instruction loads the 1/0 page base register from the word addressed by E. The format of the word is:

0-19 Reserved

20-35 Physical page number of the 1/0 page

The 1/0 page base register is set to physical page 1 by the console under the following conditions:

1. TBS

See the chapter on Special System Pagers for a description of the layout of this page.

KL/KS compatibility

No functional equivalent on the KL or KS.

RDIOP

| •           | 701 |   |          | •      | Υ | - |

|-------------|-----|---|----------|--------|---|---|

| <b>+-</b> - |     | + | <br>-+-+ | <br>-+ |   | + |

This instruction returns the value of the 1/0 page base register and stores it in the word addressed by E. The format of the word is:

0-19 Reserved

20-35 Physical page number of the I/O page

KL/KS compatibility

No functional equivalent on the KL or KS.

#### SWPIA

| +- |             | -+- |    | -+-+ |    | -+- |   | + |

|----|-------------|-----|----|------|----|-----|---|---|

| !  | <b>7</b> 01 | !   | 11 | !⊜!  | XR | !   | Y | ! |

| +- |             | -+- |    | -+-+ |    | -+- |   | + |

## Sweep Cache, Invalidate All Pages

Clear the valid and written state in all cache entries. This instruction blocks further CPU activity until the cache sweep is complete. Upon completion of the operation, the IBOX is flushed and restarted. The indirect, index register, and Y fields of this instruction are not used and are reserved.

## KL/KS compatibility

The KS had no cache sweep instructions. The KL allowed other requests to happen in parallel with the sweep, setting sweep busy and sweep done in the APR status to indicate the sweep-in-progress interval.

### **SWPUA**

| +- |     | -+- |    | -+-+-        |    | -+- |   | + |

|----|-----|-----|----|--------------|----|-----|---|---|

| į  | 701 | !   | 13 | ! <b>e</b> ! | XR | !   | Y | ! |

| +- |     | -+- |    | -+-+         |    | -+- |   | + |

# Sweep Cache, Unload All Pages

Write into storage all cache entries that are in the written state. Invalidate all entries (i.e. clear valid and written state). This instruction blocks further CPU activity until the cache sweep is complete. The indirect, index register, and Y fields of this instruction are not used and are reserved.

### KL/KS compatibility

The KS had no cache sweep instructions. The KL allowed other requests to happen in parallel with the sweep, setting sweep busy and sweep done in the APR status to indicate the sweep-in-progress interval.

## **WRSPB**

| + |     | +- |    | -+-+- |    | +- |   | -+ |

|---|-----|----|----|-------|----|----|---|----|

| ! | 702 | !  | 10 | !@!   | XR | !  | Υ | !  |

| + |     | +- |    | -+-+- |    | +- |   | -+ |

# Write SPT Base Register

This instruction loads the SPT base register from the word addressed by E. The word format is:

0-10 Reserved

11-35 Physical address of the start of the SPT.

## BASE REGISTER FORMAT

The SPT base register is loaded with a physical word address. The address need not be on a page boundary and may be any location in physical memory. There is no range check on SPT offsets. The monitor is assumed to always put correct data into the SPT base register.

## KL/KS compatibility

Functionally identical to the KS WRSPB E instruction. The KL kept the SPT address in AC block 6.

## RDSPB

| + |     | -+- |    | -+-+-      |    | -+- |   | + |

|---|-----|-----|----|------------|----|-----|---|---|

| ! | 702 | !   | 00 | <b>!@!</b> | XR | !   | Y | ! |

| + |     | -+- |    | -+-+       |    | -+- |   | + |

# Read SPT Base Register

This instruction stores the SPT base register in the word addressed by E. The format of the word is:

0-10 Reserved

11-35 Physical addresss of the SPT

KL/KS compatibility

Functionally identical to the KS RDSPB E instruction. The KL kept the address of the SPT in AC block 6.

WRCSB

| + |     | -+- |    | -+-+ |    | -+- |   | + |

|---|-----|-----|----|------|----|-----|---|---|

| ! | 702 | !   | 11 | !@!  | XR | !   | Y | ! |

| + |     | -+- |    | -+-+ |    | -+- |   | + |

Write Core Status Table Base Register

This instruction loads the CST base register from the word addressed by E. The word format is:

0-10 Reserved

Physical address of the start of the CST. If this address is zero, the microcode will make no CST references.

#### BASE REGISTER FORMAT

The CST base register is loaded with a physical word address. The address need not be on a page boundary and may be anyplace in physical memory. There is no range check on CST offsets. The monitor is assumed to always put correct data into the CST base register.

# KL/KS compatibility

Functionally identical to the KS WRCSB E instruction. The KL kept the CST address in AC block 6.

### **RDCSB**

! 702 ! 01 !@! XR ! Y !

Read Core Status Table Base Register

This instruction stores the CST base register in the word addressed by E. The format of the word is:

0-10 Reserved

11-35 Physical addresss of the CST

KL/KS compatibility

Functionally identical to the KS RDCSB E instruction. The KL kept the address of the CST in AC block 6.

WRPUR

| + |     | -+- |    | -++- |    | +- |   | + |

|---|-----|-----|----|------|----|----|---|---|

| ! | 702 | !   | 12 | !@!  | XR | !  | Y | ! |

| + |     | -+- |    | -+-+ |    | +- |   | + |

Write Process Use Register

This instruction loads the process use register from the word addressed by E. The microcode updates a CST entry by ANDing the CST mask word (see below) with the entry and ORing the process use register into the entry.

See the chapter on paging for the format of the process use register.

KL/KS compatibility

Functionally identical to the KS WRPUR E instruction. The KL kept the process use register in AC block 6.

RDPUR

| + |     | +-  |    | -+-+  |    | -+- |   | + |

|---|-----|-----|----|-------|----|-----|---|---|

| ! | 702 | !   | 02 | !@!   | XR | !   | Y | ! |

| + |     | -+- |    | -+-+- |    | -+- |   | + |

Read Process Use Register

This instruction stores the process use register in the word addressed by  ${\bf E}_{\star}$

KL/KS compatibility

Functionally identical to the KS RDPUR E instruction. The KL kept the process use register in AC block 6.

WRCSTM

| + |     | +- |    | -+-+ |    | -+- |   | + |

|---|-----|----|----|------|----|-----|---|---|

| ! | 702 | !  | 13 | !@!  | XR | !   | Y | ! |

| + |     | +- |    | -+-+ |    | -+- |   | + |

Write CST Mask Register

This instruction loads the CST mask register from the word addressed by E. The microcode updates a CST entry by ANDing the CST mask word with the entry and ORing the process use register into the entry.

See the chapter on paging for the format of the CST mask register.

KL/KS compatibility

Functionally identical to the KS WRCSTM E instruction. The KL kept the CST mask register in AC block 6.

### RDCSTM

| + |     | -+- |    | -+-+ |    | -+- |   | + |

|---|-----|-----|----|------|----|-----|---|---|

| ! | 702 | !   | 03 | !@!  | XR | !   | Y | ! |

| + |     |     |    | +-+  |    | -+- |   | + |

# Read CST Mask Register

This instruction stores the CST mask register in the word addressed by  ${\sf E.}$

KL/KS compatibility

Functionally identical to the KS RDCSTM E instruction. The KL kept the CST mask register in AC block 6.

#### **WRTMB**

| +- |     | -+- |    | -+-+- |    | -+- |   | + |

|----|-----|-----|----|-------|----|-----|---|---|

| •  | 702 | i   | 14 | iai   | ΧR | i   | ٧ | , |

|    | -   |     |    | _     |    |     |   | • |

| +- |     |     |    | -+-+- |    | -+- |   | + |

#### Write Time Base Controls

This immediate instruction decodes its effective address to control the time base and the inverval timer. The effective address bits are used as follows:

18 Load Pl assignment for interval timer from bits 33-35.

19 Load time base controls from bits 20 and 23.

20 Clear time base.

21-22 Reserved

23 Turn on time base.

24-32 Reserved

33-35 PIA for interval timer.

### The actions of this instruction are as follows:

- 1. If bit 18 is a 1, load the interval timer PI assignment from bits 33-35. If bit 18 is a 0, do not change the interval timer PIA.

- 2. If bit 19 is a 1, perform the following operations:

- 1. If bit 23 is a 1, turn on the time base. If bit 23 is a 0, turn off the time base.

- 2. If bit 20 is a 1, clear the time base. If bit 20 is a 0, it is ignored.

If bit 19 is a 0, do not change the state of the time base.

KL/KS compatibility

The KL CONO MTR, instruction controls the time base and the interval timer PIA in a manner very analogous to this instruction. The KS had no equivalent instruction.

#### RDTMB

| + |     | +- |    | -+-+-        |    | +-  |   | + |

|---|-----|----|----|--------------|----|-----|---|---|

| ! | 702 | !  | 04 | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | +- |    | -+-+-        |    | -+- |   | + |

## Read Time Base Enables

This instruction reads the status of the time base and the interrupt level assigned to the interval timer into the word addressed by E. The status is as follows:

0-22 Reserved

Time base on.

24-32 Reserved

33-35 PIA for interval timer.

## KL/KS compatibility

The KL CONI MTR, instruction returned the time base enable and interval timer PIA in a manner very analogous to this instruction. The KS had no direct equivalent.

### RDTIME

| + |     | +- |    | -+-+ |    | -+- |   | + |

|---|-----|----|----|------|----|-----|---|---|

| ! | 702 | !  | 06 | !@!  | XR | !   | Y | ! |

| + |     | +- |    | -+-+ |    | +-  |   | + |

## Read Time Base Value

This instruction updates the time base double word from the hardware counter and returns the updated double word in the words addressed by E and E+1. The double word is double precision integer in ! microsecond units with the following format:

| ! =: |               |                          | ==!      |

|------|---------------|--------------------------|----------|

| !    |               | High order part of count | !        |

| !    |               |                          | <u>!</u> |

| 10   | !             | Low order part of count  | !        |

| ļ =: | 8 <b>3</b> 21 |                          | ==!      |

| 0    | 1             |                          | 35       |

# KL/KS compatibility

The KL RDTIME instruction also updated the time base double word kept in EPT locations 510 and 511. The KS RDTIM instruction returned the double word in the same manner as this instruction.

### RDACT

| + |     | -+- |    | -+-+ |    | -+- |   | + |

|---|-----|-----|----|------|----|-----|---|---|

| ! | 702 | !   | 17 | !@!  | XR | !   | Y | ! |

| + |     | +-  |    | -+-+ |    | -+- |   | + |

# Read accounting information

This instruction reads the status of the user runtime meter into the word addressed by E. The status is as follows:

| 0-18  | Reserved                                                                  |

|-------|---------------------------------------------------------------------------|

| 19    | The user runtime meter has been enabled to count during exec PI time.     |

| 20    | The user runtime meter has been enabled to count during exec non-PI time. |

| 21    | User runtime meter on.                                                    |

| 22-35 | Reserved                                                                  |

# KL/KS compatibility

The KL CONI MTR, instruction returned the accounting meter controls in a manner very analogous to this instruction. The KS had no direct equivalent.

#### WRACT

| +- |     | -+- |    | -+-4.        |    | -+- |   | + |

|----|-----|-----|----|--------------|----|-----|---|---|

| !  | 702 | !   | 16 | ! <b>@</b> ! | XR | !   | Y | ! |

| +- |     | -+- |    | -+-+         |    | -+- |   | + |

### Write accounting information

This immediate instruction decodes its effective address to control the user runtime meter. The effective address bits are used as follows:

- 18 Load user runtime meter controls from bits 19-21.

- 19 Enable user runtime meter count during exec PI time.

- 20 Enable user runtime meter count during exec non-PI time.

- 21 Turn on user runtime meter

- 22-35 Reserved

The actions of this instruction are as follows:

- 1. If bit 18 is a 1, perform the following operations:

- If bit 19 is a 1, enable the user runtime meter to count during exec PI processing. If bit 19 is a 0, disable the user runtime meter from counting during exec PI processing.

- If bit 20 is a 1, enable the user runtime meter to count during exec non-PI processing. If bit 20 is a 0, disable the user runtime meter from counting during non-PI processing.

- 3. If bit 21 is a 1, turn on the user runtime meter. If bit 21 is a 0, turn off the user runtime meter.

If bit 18 is a 0, do not change the state of the user runtime meter.

# KL/KS compatibility

The KL CONO MTR, instruction controls the accounting meters in a manner very analogous to this instruction. The KS had no equivalent instruction.

## RDURTM

| + |     | +  |    | -+-+ |    | +- |   | + |

|---|-----|----|----|------|----|----|---|---|

| ! | 702 | !  | 07 | !@!  | XR | !  | Υ | ! |

| + |     | -+ |    | -+-+ |    | +- |   | + |

## Read User Runtime Meter

This instruction updates the user runtime meter double word from the hardware counter and returns the updated double word in the words addressed by E and E+1. The double word is double precision integer in 1 microsecond units with the following format:

| ! == | *** |     |       | ******  |       |                 | ======! |

|------|-----|-----|-------|---------|-------|-----------------|---------|

| !    |     | _   |       | •       |       | in microseconds | !       |

| 10   | !   | Low | order | part of | count | in microseconds | . !     |

| 0    | 1   |     |       |         |       |                 | 35      |

# KL/KS compatibility

The KL and KS had no comparable instructions.

WRINT

! 702 ! 15 !@! XR ! Y !

### Write Interval Timer

This immediate mode instruction decodes its effective address to setup the interval timer. The effective address bits are used as follows:

18 Clear interval timer.

19-20 Reserved

21 Turn interval timer on.

22 Clear interval flags.

23 Reserved

24-35 Interval period.

A 1 in bit 18 clears the counter and can be given simultaneously with a 1 or 0 in bit 21 to turn the counter on or off. A 1 in bit 22 clears both Interval Done and Interval Overflow. If the counter is on, Interval Done will set when the count reaches the value specified by bits 24-35.

# KL/KS compatibility

This instruction is functionally equivalent to the KL CONO TIM, instruction.

### RDINT

| + |     | -+- |    | -+-+         |    | -+- |   | + |

|---|-----|-----|----|--------------|----|-----|---|---|

| ! | 702 | !   | 05 | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | -+- |    | -+-+-        |    | -+- |   | + |

# Read The Interval Register

Read the status of the interval timer into the word addressed by E. The status is as follows:

| 0-5   | Reserved                                          |

|-------|---------------------------------------------------|

| 6-17  | Interval count (current contents of the counter). |

| 18-20 | Reserved                                          |

| 21    | Interval timer on.                                |

| 22    | Interval timer done (causes interrupt).           |

| 23    | Overflow (implies bit 22).                        |

| 24-35 | Interval period.                                  |

Bits 22 and 23 are the counter flags; note that interval timer done can be set alone, but a 1 in bit 23 implies a 1 in bit 22 as well. Bits 24-35 are the period supplied by WRINT, and bits 6-17 are the current contents of the counter.

# KL/KS compatibility

This instruction is functionally equivalent to the KL CONI TIM, instruction

### CHAPTER 3

#### EXTERNAL I/O INSTRUCTIONS

The external I/O instructions on the KClO allow a program to communicate with the 1/0 ports and the console. In particular they will manipulate the I/O Command/Response Queues and Port Doorbell mechanism. See the "I/O Bus Spec." in the 2080 EFS for a complete description of the Queue and Doorbell features. The interface to the KC10 ports is primarily data areas called "mailboxes" and a doorbell. It is the doorbell mechanism that the following instructions manipulate. The Command/Response Queues will be covered by the queue instructions in the next section. In general the BUSY and RING signals work as follows: The CPU can assert RING on the I/O Bus if BUSY is clear. Upon setting RING and a port number, the CPU must observe BUSY setting and then clearing before it can assume that the 1/0 Port has seen its command. The following 2 instructions (RNGB and RGNBW) will be skipping instructions if no bus timeouts occur. The Console does not use this protocol and therefore RING and BUSY signals are ignored if any console functions are requested by RNGB or RNGBW.

#### **RNGB**

| + |     | +- |    | -+-+         |    | -+- |   | + |

|---|-----|----|----|--------------|----|-----|---|---|

| ! | 710 | !  | 00 | ! <b>@</b> ! | XR | .!  | Y | ! |

| + |     | +- |    | -+-+         |    | -+- |   | + |

#### Ring Doorbell

This immediate mode instruction will assert a port or console number on the KClO I/O bus and set RING ("doorbell"). If no bus timeout errors occur the next instruction is taken from PC+2 (ie. the instruction skips). The EA of this instruction is the port number and is interpreted as follows:

| 18 | Cause c | onsole t | o reload | (electronic | boot 1 | finger) |

|----|---------|----------|----------|-------------|--------|---------|

|----|---------|----------|----------|-------------|--------|---------|

19 Initialize the port specified by bits 33-35 to the power-up state.

20 Interrupt KC10 Console

21-32 Reserved

33-35 Port number (Must be zero if bit 18 or bit 20 is set)

Setting both bits 18 and 20 in a single instruction will produce unspecified results.

### NOTE

This instruction waits for BUSY to be clear before asserting RING on the KC10 I/O bus. If for any reason BUSY does not set or clear in ??ms, the CPU takes the next instruction from PC+1 rather than PC+2.

## **RNGBW**

| +- |     | -+- |    | -+-+         |    | -+- |   | + |

|----|-----|-----|----|--------------|----|-----|---|---|

| !  | 711 | !   | 00 | ! <b>e</b> ! | XR | !   | Y | ! |

| +- |     | -+- |    | -+-+         |    | -+- |   | + |

Ring Doorbell and Wait (for BUSY to clear).

This immediate mode instruction will assert a port or console number on the KC10 I/O bus and set RING ("doorbell"). The instruction then waits for BUSY to clear. If no bus timeout errors occur the next instruction is taken from PC+2 (ie. the instruction skips). The EA of this instruction is the port number and is interpreted as follows:

- 18 Cause console to reload (electronic boot finger)

- 19 Initialize the port specified by bits 33-35 to the power-up state.

- 20 Interrupt KC10 Console (does not wait for BUSY- same function as RNGB)

- 21-32 Reserved

- 33-35 Port number (Must be zero if bit 18 or bit 20 is set)

Setting both bits 18 and 20 in a single instruction will produce unspecified results.

## NOTE

This instruction waits for BUSY to be clear before asserting RING on the KC10 I/O bus. If for any reason BUSY does not set or clear in ??ms, the CPU takes the next instruction from PC+1 rather than PC+2.

## SNBSY

| + |     | + |    | -+-+         |    | +-  |   | + |

|---|-----|---|----|--------------|----|-----|---|---|

| ! | 712 | ! | 00 | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | + |    | -+-+         |    | -+- |   | + |

Skip if BUSY not set

This instruction skips to PC+2 if the BUSY line of the KC10 I/O bus is not set. When used in combination with the RNGB instruction, one can achieve the identical effect of RNGBW as follows:

RNGB pn ; Assert RING to port "pn" SNBSY ; Busy set?

JRST .-1 ; Yes, wait. ... ; No - proceed

### CHAPTER 4

## OTHER 1/0 INSTRUCTIONS

This chapter describes other instructions with opcodes in the range 700-737 that cannot be considered as either internal 1/0 or external 1/0 instructions.

Like all instructions whose opcode is in the range 700-737, inclusive, these instructions may only be executed in user mode if user 1/0 is set. If these instructions are executed in user mode without user 1/0, they execute as an MUUO, trapping through the user undefined 1/0 opcode dispatch in location 435 of the UPT.

UMOVE

! 704 ! AC !@! XR ! Y !

User Move from Memory

Load previous context memory location addressed by E into AC.

NOTE

This is just a replacement instruction for XCT 4, [MOVE AC, MEMORY].

## UMOVEM

! 705 ! AC !@! XR ! Y !

User Move to Memory

Store AC into previous context memory location addressed by E.

NOTE

This is just a replacement instruction for XCT 4, [MOVEM AC, MEMORY].

**PMOVE**

! 706 ! AC !@! XR ! Y !

Physical Move from Memory

Perform a physical EA-calc using the word addressed by E, then load the physical memory location addressed by the result of the EA-calc into the AC.

See the chapter on queues and queue manipulation instructions for a discussion of the physical EA-calc algorithm.

NOTE

Effective addresses 0-17 will reference physical memory 0-17, not the ACs.

No CST update will be performed as the result of this instruction

## **PMOVEM**

| + |     | -+- |    | -+-+-        |    | -+- |   | + |

|---|-----|-----|----|--------------|----|-----|---|---|

| ! | 707 | !   | AC | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | -+- |    | -+-+         |    | -+- |   | + |

Physical Move to Memory

Perform a physical EA-calc using the word addressed by E, then store AC into the physical memory location addressed by the result of the EA-calc.

See the chapter on queues and queue manipulation instructions for a discussion of the physical EA-calc algorithm.

### NOTE

Effective addresses 0-17 will reference physical memory 0-17, not the ACs.

No CST update will be performed as the result of this instruction.

# CHAPTER 5

# OTHER FUNCTIONAL CHANGES

This chapter describes non-1/0 instructions and other operations whose functionality has changed from previous machines.

MAP

| + |     | +- | <br>-+-+ | <br>-+- | <br>+ |

|---|-----|----|----------|---------|-------|

|   | 257 | -  |          | •       | !     |

| + |     | +- | <br>-+-+ | <br>-+- | <br>+ |

### Map an address

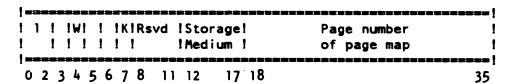

If the pager is on and the processor is in executive or user 1/0 mode, this instruction reads the hardware page table location corresponding to the effective address. If the page table contains a valid mapping for that page, the mapping is returned in the format described below. If the page table does not contain a valid mapping for the page, the EBOX microcode does a page refill pointer chase to compute the mapping and returns that in the format described below. The result of the mapping is returned in the AC.

This instruction does not change the hardware page table mapping for the page specified by the effective address calculation.

This instruction cannot be performed in a user program unless user 1/0 is set. Instead of mapping the address, it executes as an MUUO, dispatching through the user undefined 1/0 opcode dispatch in location 435 of the UPT. If the pager is off, the results of the instruction are undefined.

The format returned by the MAP instruction in the AC is as follows:

| ***************         | *************** |

|-------------------------|-----------------|

| !H!K!?!V!C!W!M!?!K!U!T! | Physical!       |

| !D!1!?!L!U!T!D!?!2!S!B! | Address !       |

| ********************    |                 |

| 0 1 2 3 4 5 6 7 8 9 1 1 | 3               |

| 0 1                     | 5               |

#### The fields are as follows:

This bit is a one if the instruction failed to generate a valid mapping because of a hardware error. In this case, bits 1-4 contain a failure code instead of the bits described below. These codes are the same as those returned for a page fail with bit 0 set in the page fail word.

- See the description of bit 8 below.

- The state of this bit is undefined.

- If this bit is a one, the rest of the information returned, including the physical address is valid. If this bit is a zero, there is no valid mapping for the virtual address and bits 18-35 contain the reason the microcode couldn't find a valid mapping. This information has the same format as bits 18-35 of the page fail word that would be returned if the specified page was referenced.

- If this bit is a one, the next virtual reference to the page being mapped will cause the EBOX microcode to perform a CST update operation for the page.

- If this bit is a one, the page being mapped is writable. If this bit is a zero, the page being mapped is write protected.

- If this bit is a one, the page being mapped has been modified since being brought into memory, i.e., the page is newer than any backup copy. If this bit is a zero, the page has not been modified since being brought into memory.

- 7 The state of this bit is undefined.

- If bit 1 or this bit is a one, the hardware virtual-to-physical mapping for the page being mapped will not be invalidated on a conditional pager clear. If both bit 1 and this bit are zeros, the mapping will be invalidated on all pager clears.

- If this bit is a one, the mapping for this page is in user space. If this bit is a zero, the mapping for this page is in executive space.

- If this bit is a zero, the microcode found valid information in the hardware page table for this mapping. If this bit is a one, the microcode performed a pointer trace to compute the mapping.

- 11-35 The physical address corresponding to the virtual address of the effective address calculation.

### KL/KS compatibility

The KL and KS returned different bits describing the mapping.

**JRST**

| + |     | -+- |   | -+-+         |    | -+- |   | + |

|---|-----|-----|---|--------------|----|-----|---|---|

| ! | 254 | !   | F | ! <b>@</b> ! | XR | !   | Y | ! |

| + |     | +-  |   | -+-+         |    | -+- |   | + |

#### Jump and Restore

The KC10 implementation of JRST is very similar to the KS10 and extended KL10 implementation with several exceptions. The exceptions are as follows:

#### F Mnemonic Function

- O5 XJRSTF Restore the program flags (as appropriate for the mode of the processor) and PC from the flag-PC double word in locations E and E+1 and continue performing instructions in normal sequence beginning at the location then addressed by PC. If the instruction is executed in exec mode, also restore CAB, PAB, and PCS from the first word of the flag-PC double word.

- O6 XJEN Restore the level on which the highest priority interrupt is currently being held and then perform an XJRSTF.

- Save the program flags, CAB, PAB, PCS, and PC in a flag PC double word in locations E and E+1. Then restore the program flags, CAB, and PC from the flag-PC double word in locations E+2 and E+3 and continue performing instructions in normal secretaric beginning at the location then addressed by PC. Do not restore PAB or PCS from E+2.

- Always execute as an MUUO through the I/O undefined opcode new PC words in the UPT.

- 12 JEN

Always execute as an MUU0 through the I/O undefined opcode new PC words in the UPT. Since the KC10 always stores flag-PC double words in XJEN format, there is no need for JEN.

- Save the program flags in bits 0-12 of the word addressed by E and clear bits 13-17. If the instruction is executed in exec mode, store CAB, PAB, and PCS in bits 18-20, 21-23, and 24-35, respectively, of the same word. If the instruction is executed in user mode, clear bits 18-35. This instruction is legal in any section.

- 15 XJRST Restore the PC from bits 6-35 of the word addressed by E and continue performing instructions in normal sequence beginning at the location then addressed by PC. Do not

change the program flags, CAB, PAB, or PCS.

For each of the 16 possible JRST functions, the table given below indicates where each form of the instruction is legal. The meanings of the symbols used to define the legal domains of the functions are as follows:

```

Yes Legal everywhere

Z Legal only in section zero

K Legal only in kernel (executive) mode

No Legal nowhere

-H Legal where indicated by first symbol but causes a halt

```

If the JRST function is illegal in the mode or context in which it is executed, the instruction traps as an MUUO through the I/O undefined opcode new PC words in the UPT.

| Function | <b>Mnem</b> on i c | Legal | domain |

|----------|--------------------|-------|--------|

| JRST 0,  | <b>JRST</b>        | Yes   |        |

| JRST 1,  | PORTAL             | Yes   |        |

| JRST 2,  | <b>JRSTF</b>       | Z     |        |

| JRST 3,  |                    | No    |        |

| JRST 4,  | HALT               | K-H   |        |

| JRST 5,  | XJRSTF             | Yes   |        |

| JRST 6,  | XJEN               | K     |        |

| JRST 7.  | XPCW               | K     |        |

| JRST 10, |                    | No    |        |

| JRST 11. |                    | No    |        |

| JRST 12, |                    | No    |        |

| JRST 13, |                    | No    |        |

| JRST 14, | SFM                | Yes   |        |

| JRST 15, | XJRST              | Yes   |        |

| JRST 16. |                    | No    |        |

| JRST 17. |                    | No    |        |

| • •      |                    |       |        |

XBLT

Extended Block Transfer

Move a block of words from one area of memory to another. The block size and the locations of the source and destination areas are defined by the contents of a block of three accumulators as described in the Hardware Reference Manual. This instruction may be exectued in both section zero and non-zero sections and may be used to transfer data between any arbitrary sections.

## KL/KS compatibility

The KL and KS exectued this instruction as an MUUO if it was exectuted in section zero.

**PXCT**

| + |     | +   | -+-+ |    | + |   | + |

|---|-----|-----|------|----|---|---|---|

| ! | 256 | ! F | 19!  | XR | ! | Y | ! |

| + |     | +   | -+-+ |    | + |   | + |

## Previous Context Execute

This instruction executes another instruction with certain specified references in the previous context. The operations performed in the previous context are determined by the bits in the AC field. The KC10 changes the legal bits that may be set for PXCTed stack and MOVSLJ instructions. The following table gives the only legal combinations for each type:

| Instructions | 9 | 10 | 11 | 12 | References          |

|--------------|---|----|----|----|---------------------|

| Stack        | 0 | 1  | 0  | o  | Memory data         |

|              | 1 | 1  | 0  | 0  | E, memory data      |

| MOVSLJ       | 0 | 0  | 0  | 1  | Destination         |

| 7101320      | _ | -  | -  |    |                     |

|              | O | 0  | 1  | 0  | Source              |

|              | 0 | 0  | 1  | 1  | Source, destination |

# CHAPTER 6

# SPECIAL DEBUGGING INSTRUCTIONS