decsystemio

Maintenance Manual

# KI10 CENTRAL PROCESSOR

# decsystemo KI10 CENTRAL PROCESSOR MAINTENANCE MANUAL

### Copyright © 1973 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

FLIP CHIP

**DECtape**

UNIBUS

DECsystem-10

PDP

DECmagtape

# CONTENTS

| :         |                            | Page |

|-----------|----------------------------|------|

| CHAPTER 1 | INTRODUCTION               |      |

|           |                            |      |

| 1.1       | PHYSICAL CHARACTERISTICS   | 1-1  |

| 1.2       | ELECTRICAL CHARACTERISTICS | 1-5  |

| CHAPTER 2 | LOGICAL ORGANIZATION       |      |

| 2.1       | CONTROL                    | 2-1  |

| 2.2       | MEMORY INTERFACE           | 2-1  |

| 2.3       | ARITHMETIC LOGIC           | 2-3  |

| 2.4       | INPUT-OUTPUT               | 2-3  |

| CHAPTER 3 |                            | 2-4  |

|           | OPERATION                  |      |

| 3.1       | CONTROL PANELS             | 3-1  |

| 3.1.1     | Indicators                 | 3-2  |

| 3.1.2     | Operating Keys             | 3-4  |

| 3.1.3     | Operating Switches         | 3-6  |

| 3.1.4     | Panel Maintenance          | 3-8  |

| 3.2       | CONSOLE IN-OUT EQUIPMENT   | 3-9  |

| 3.2.1     | Reader                     | 3-9  |

| 3.2.2     | Punch                      | 3-9  |

| 3.2.3     | Teletypewriter             | 3-10 |

| CHAPTER 4 | CONVENTIONS AND NOTATION   |      |

| 4.1       | DESIGN CONVENTIONS         |      |

| 4.2       | LOCIC DRAWINGS             | 4-1  |

| 4.2.1     | LOGIC DRAWINGS             | 4-4  |

| 4.3       | Signal Notation            | 4-6  |

| 4.3.1     | FLOW CHARTS                | 4-7  |

|           | Terminology                | 4-10 |

| CHAPTER 5 | CONTROL                    |      |

| 5.1       | BASIC CONTROL ELEMENTS     | 5-1  |

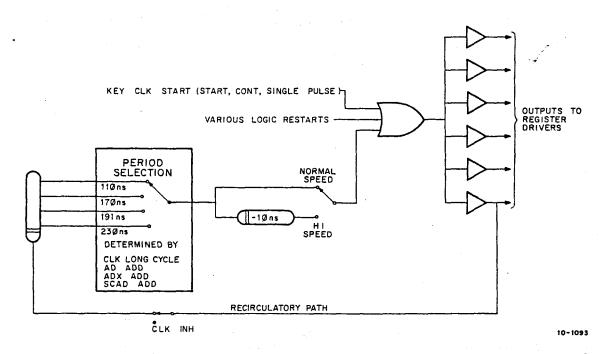

| 5.1.1     | Clock                      | 5-2  |

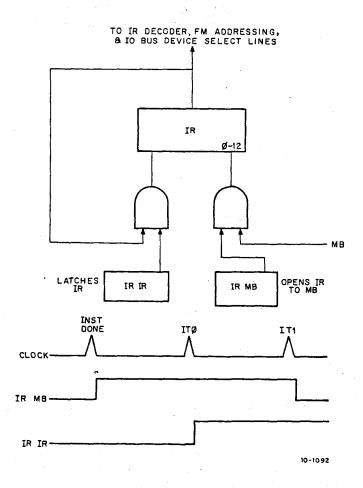

| 5.1.2     | Instruction Decoding       | 5-3  |

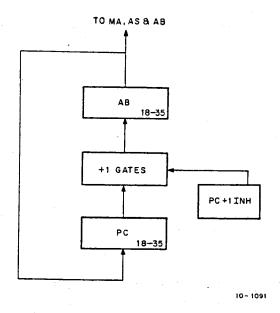

| 5.1.3     | Program Counting           | 5-5  |

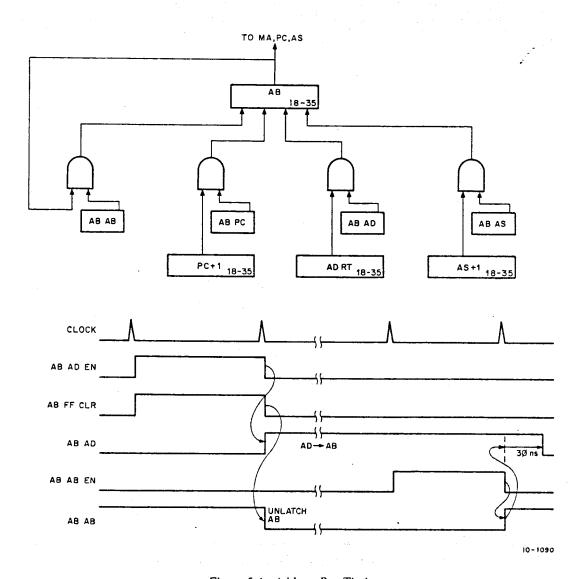

| 5.1.4     | Address Bus                | 5-6  |

| 5.2       | FAST MEMORY                | 5-7  |

| 5.3       | PROCESSOR CYCLES           | 5.9  |

| 5.3.1     | Instruction Cycle          | 5-10 |

| 5.3.2     | Fetch Cycle                | 5.11 |

| 5.3.3     | Execute Cycle              | 5.13 |

| 5.3.4     | Store Cycle                | 5-13 |

| 5.3.5     | Page Fail Cycle            | 5-15 |

| 5.4       | TRAP LOGIC                 | 5-16 |

| 5.5       | MODE CONTROL               | 5-17 |

| 5.5.1     | User Paging                | 5-12 |

|           |                            | 7-10 |

## CONTENTS (Cont)

|              |                                          | Page   |

|--------------|------------------------------------------|--------|

| 5.6          | CONSOLE CONTROL                          | C 10   |

| 5.6.1        |                                          |        |

| 5.6.2        | Address Switches                         |        |

| 5.6.3        | Master Clear and Restart                 |        |

|              | Memory Indicators and Address Comparator |        |

| 5.6.4        | Key Logic                                | . 5-21 |

| CHAPTER 6    | MEMORY LOGIC                             |        |

| 6.1          | MEMORY DATA                              | 6-1    |

| 6.2          | MEMORY ADDRESSING                        | 6.2    |

| <b>6.3</b> . | ASSOCIATIVE MEMORY                       |        |

| 6.4          | PAGE CHECKING                            |        |

| 6.5          | MEMORY CONTROL                           |        |

| 6.5.1        | Memory Subroutine Logic                  |        |

| 6.6          | MEMORY SUBROUTINE                        |        |

| 6.6.1        | Subroutine Call and Page Delay           |        |

| 6.6.2        |                                          |        |

| 6.6.3        | Page Check, Memory Go, and Recycle       |        |

| 6.6.4        | Request Cycle and Read Restart           |        |

| 6.6.5        | Read Return and Refill Reentry           |        |

|              | Write Restart                            |        |

| 6.6.6        | AC Reference                             |        |

| 6.7          | KI10-M MEMORY BUS ADAPTER                | 6-20   |

| CHAPTER 7    | ARITHMETIC LOGIC                         |        |

| 7.1          | ADDER AD                                 | 7-1    |

| 7.1.1        | Adder Mixers                             |        |

| 7.1.2        | Adder Gating                             |        |

| 7.1.3        | Adder Zero Logic                         |        |

| 7.2          | ARITHMETIC REGISTER AR                   |        |

| 7.2.1        |                                          |        |

| 7.3          | AR Flags                                 | 7-10   |

| 7.4          | ADDER AND AR EXTENSIONS                  |        |

| 7.4<br>7.5   | BUFFER REGISTER BR                       | 7-11   |

|              | MULTIPLIER-QUOTIENT REGISTER MQ          |        |

| 7.6          | SHIFT-COUNT LOGIC                        |        |

| 7.6.1        | Shift-Count Subroutine                   | . 7-13 |

| CHAPTER 8    | INSTRUCTION FLOW                         |        |

| 8.1          | INSTRUCTION FETCHING                     | 8-1    |

| 8.2          | DATA TRANSMISSION                        |        |

| 8.3          | CONTROL AND TEST INSTRUCTIONS            | 8-5    |

| 8.3.1        | Jump Instructions                        |        |

| 8.3.2        | Push-Pop Instructions                    |        |

| 8.3.3        | Logical and Arithmetic Testing           |        |

| 8.3.4        | UUOs and MAP                             |        |

| 8.4          | LOGIC AND FIXED POINT ARITHMETIC         |        |

| 8.4.1        | Shift-Rotate                             |        |

| 8.4.2        |                                          |        |

| 8.4.3        | Multiply                                 | 8-10   |

| U.T.J        | LANGE                                    | X_! !  |

## CONTENTS (Cont)

|            |                                            |     | Page     |

|------------|--------------------------------------------|-----|----------|

| 8.5        | SINGLE PRECISION FLOATING POINT ARITHMETIC |     | 8-13     |

| 8.5.1      | Floating Add-Subtract                      |     |          |

| 8.5.2      | Floating Multiply                          |     | 8-14     |

| 8.5.3      | Floating Divide                            | •   | 8-15     |

| 8.5.4      | Miscellaneous Floating Point Instructions  |     | 8-15     |

| 8.5.5      | Floating Normalize and Round               |     |          |

| 8.6        | DOUBLE PRECISION FLOATING POINT ARITHMETIC |     | 8-17     |

| 8.6.1      | Double Floating Add-Subtract               |     |          |

| 8.6.2      | Double Floating Multiply                   |     | 8-18     |

| 8.6.3      | Double Normalize                           |     |          |

| 8.6.4      | Double Floating Divide                     |     | 8-20     |

| 8.6.5      | Double Moves                               |     |          |

| CHAPTER 9  | INPUT-OUTPUT                               |     |          |

| 9.1        | IN-OUT CONTROL                             |     | <b>.</b> |

| 9.1.1      |                                            |     |          |

| 9.1.2      | IO Instruction Flow Basic IO Logic         | -   |          |

| 9.2        |                                            |     |          |

| 9.2.1      |                                            |     |          |

| 9.2.2      | PI Request Sequence                        | • • | 9-4      |

| 9.3        | PI Cycle                                   |     |          |

| 9.4        | _ = = = = = = -                            |     | 9-7      |

| 9.5        | PROCESSOR DEVICE LOGIC                     |     |          |

| 9.5.1      | BASIC IO EQUIPMENT                         |     |          |

| 9.5.2      | Paper Tape Reader                          |     |          |

|            | Paper Tape Punch                           |     | 9-9      |

| 9.5.3      | Teletypewriter                             |     | 9-10     |

| CHAPTER 10 | MAINTENANCE                                |     |          |

| 10.1       | CUSTOMER PRINT SET                         |     | 10-2     |

| 10.2       | MAINTENANCE OPERATION                      |     |          |

| 10.2.1     | Margin Check System                        |     |          |

| 10.3       | MAINTENANCE LOGIC                          | • • | 10-4     |

| 10.4       | ADJUSTMENTS                                | • • | 10-4     |

| 10.5       | DIAGNOSTIC PROGRAMS                        |     | 10-5     |

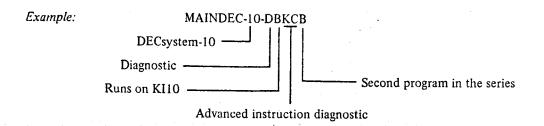

| APPENDIX A | INSTRUCTION AND DEVICE MNEMONICS           |     |          |

| APPENDIX B | •                                          |     |          |

| WILCHAIY R | PROCESSOR CONTROL PANELS                   |     | B-1      |

## CONTENTS (Cont)

|            |                                            | Page |

|------------|--------------------------------------------|------|

| 8.5        | SINGLE PRECISION FLOATING POINT ARITHMETIC | Q 11 |

| 8.5.1      | Floating Add-Subtract                      |      |

| 8.5.2      | Floating Multiply                          | 9 1/ |

| 8.5.3      | Floating Divide                            | 0 14 |

| 8.5.4      | Miscellaneous Floating Point Instructions  | 0 14 |

| 8.5.5      | Floating Normalize and Round               | Q 14 |

| 8.6        | DOUBLE PRECISION FLOATING POINT ARITHMETIC | 2.17 |

| 8.6.1      | Double Floating Add-Subtract               | 8.17 |

| 8.6.2      | Double Floating Multiply                   | 8-18 |

| 8.6.3      | Double Normalize                           | R-10 |

| 8.6.4      | Double Floating Divide                     | 8-20 |

| 8.6.5      | Double Moves                               | 8-21 |

|            |                                            | 0-21 |

| CHAPTER 9  | INPUT-OUTPUT                               |      |

| 9.1        | IN-OUT CONTROL                             | 0_1  |

| 9.1.1      | IO Instruction Flow                        | 0.0  |

| 9.1.2      | Basic IO Logic                             |      |

| 9.2        | PRIORITY INTERRUPT                         |      |

| 9.2.1      | PI Request Sequence                        |      |

| 9.2.2      | PI Cycle                                   |      |

| 9.3        | READ IN                                    | 9-7  |

| 9.4        | PROCESSOR DEVICE LOGIC                     | 9-8  |

| 9.5        | BASIC IO EQUIPMENT                         | 9-9  |

| 9.5.1      | Paper Tape Reader                          | 9-9  |

| 9.5.2      | Paper Tape Punch                           | 9-9  |

| 9.5.3      | Teletypewriter                             | 9-10 |

|            |                                            | )-10 |

| CHAPTER 10 | MAINTENANCE                                |      |

| 10.1       | CUSTOMER PRINT SET                         | 10-2 |

| 10.2       | MAINTENANCE OPERATION                      |      |

| 10.2.1     | Margin Check System                        |      |

| 10.3       | MAINTENANCE LOGIC                          | 10-4 |

| 10.4       | ADJUSTMENTS                                | 10-5 |

| 10.5       | DIAGNOSTIC PROGRAMS                        | 10-6 |

| APPENDIX A | INSTRUCTION AND DEVICE MNEMONICS           |      |

| APPENDIX B | PROCESSOR CONTROL PANELS                   | R-1  |

## ILLUSTRATIONS

| Figure No. | Title                                     | Page   |

|------------|-------------------------------------------|--------|

|            |                                           | 1.2    |

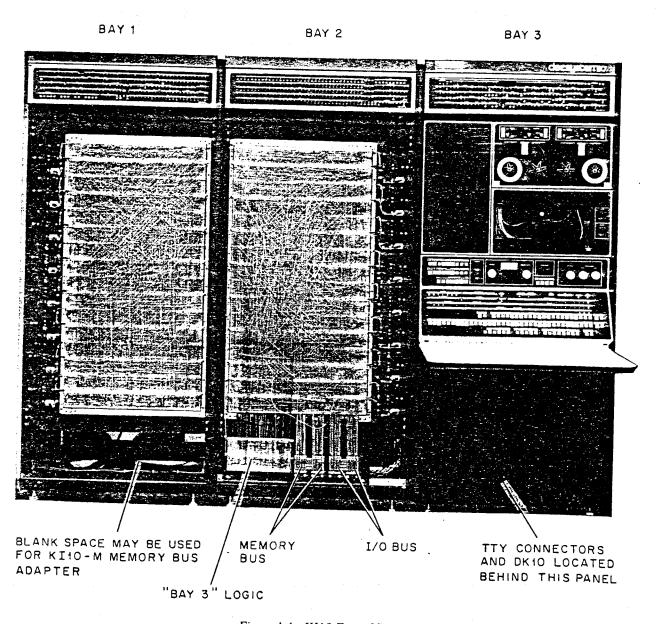

| 1-1        | KI10 Front View                           | . 1-2  |

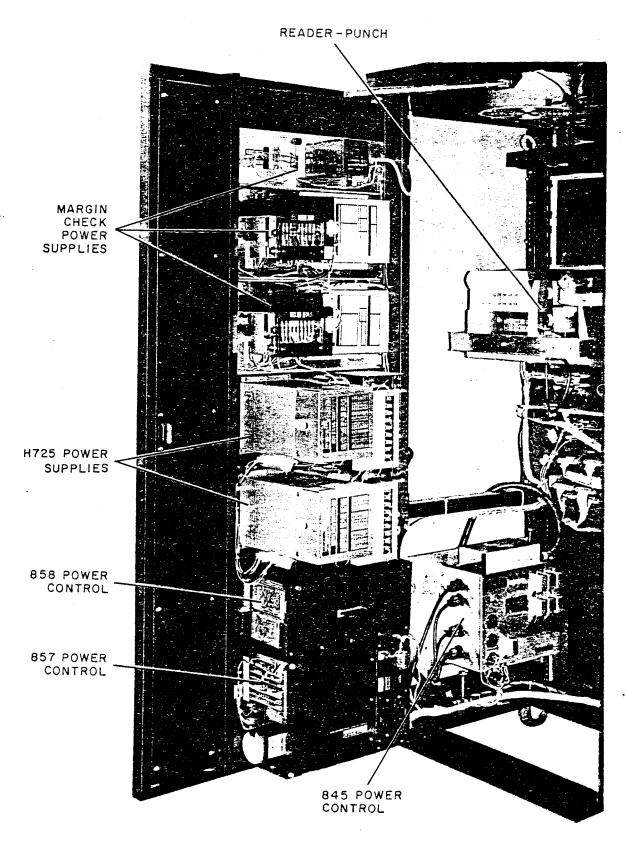

| 1-2        | KI10 Rear View, Bay 3                     | . 1-3  |

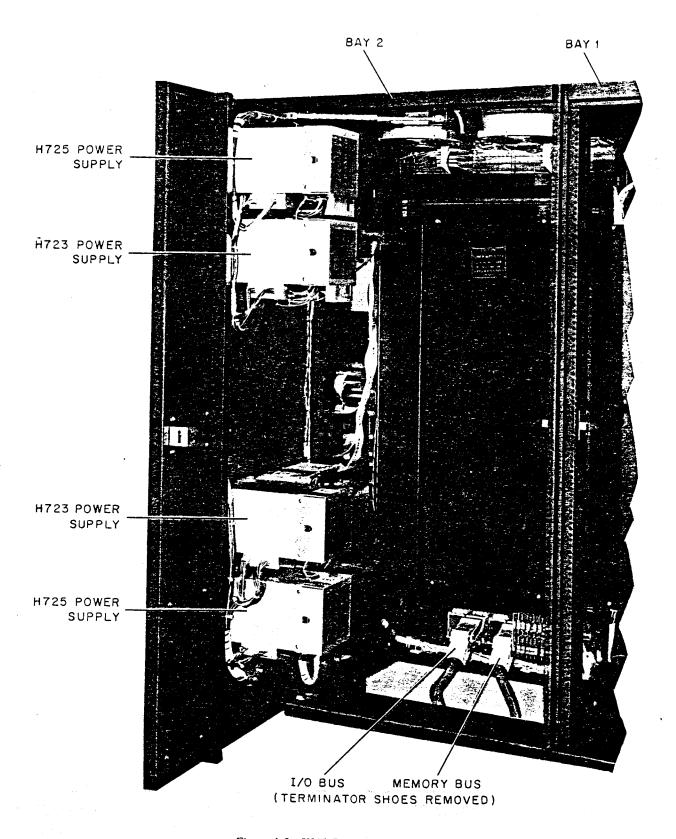

| 1-3        | KI10 Rear View, Bay 2                     | . 1-4  |

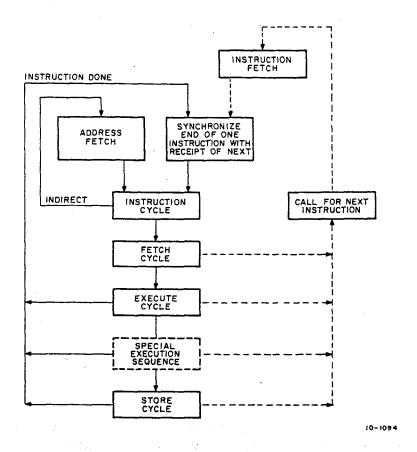

| 2-1        | Basic Cycles                              | . 2-2  |

| 3-1        | Console Teletypewriter Panel              | . 3-11 |

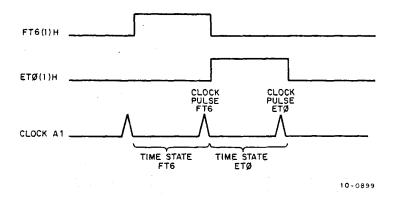

| 4-1 -      | Time State/Clock Relationship             | . 4-2  |

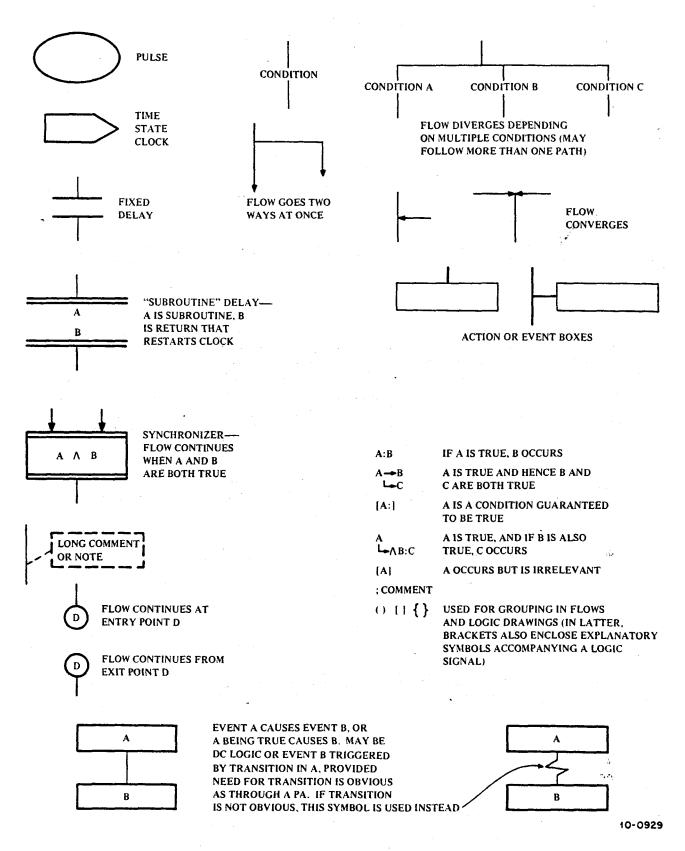

| 4-2        | Flow Chart Conventions                    | . 4-8  |

| 4-3        | Flow Chart Events                         | . 4-10 |

| 5-1        | Clock                                     | . 5-2  |

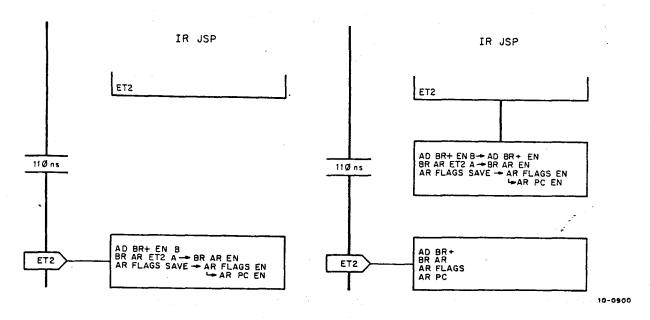

| 5-2        | IR Control                                | . 5-4  |

| 5-3        | Program Count Loop                        | . 5-6  |

| 5-4        | Address Bus Timing                        | . 5-7  |

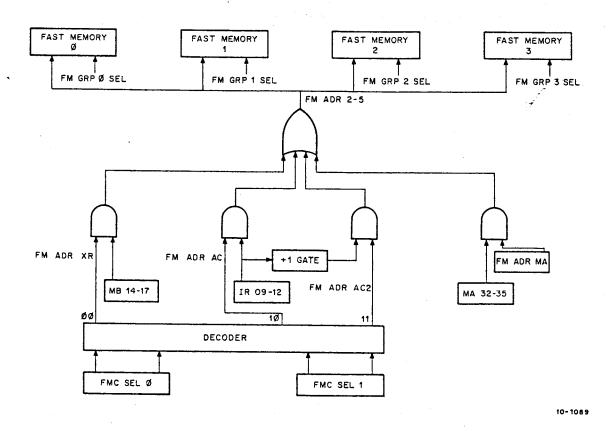

| 5-5        | Fast Memory Control                       | . 5-8  |

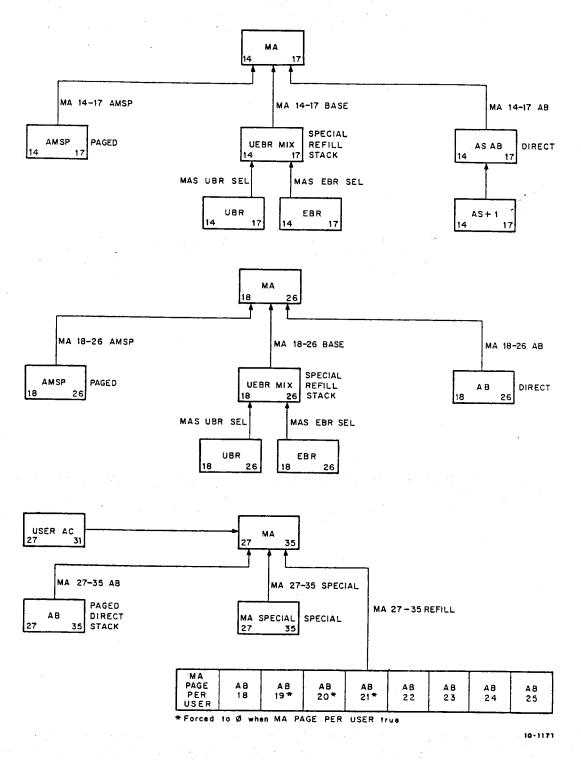

| 6-1        | Memory Address Sources                    | . 6-3  |

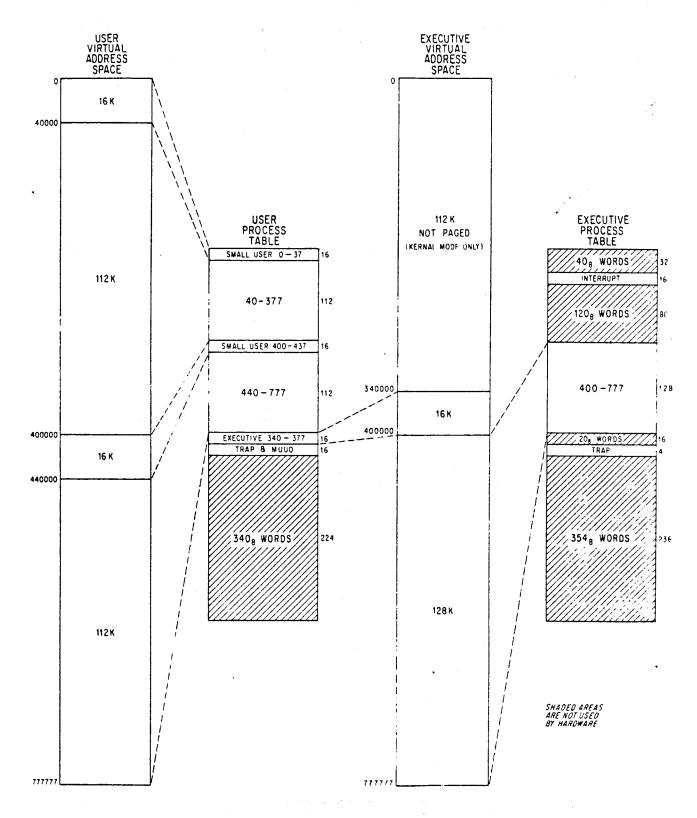

| 6-2        | Virtual Address Space and Page Map Layout | . 6-5  |

| 6-3        | Process Table Configuration               | . 6-6  |

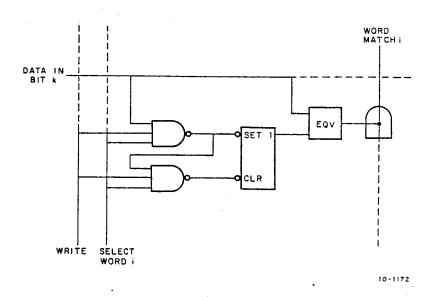

| 6-4        | Typical Associative Memory Cell           | . 6-7  |

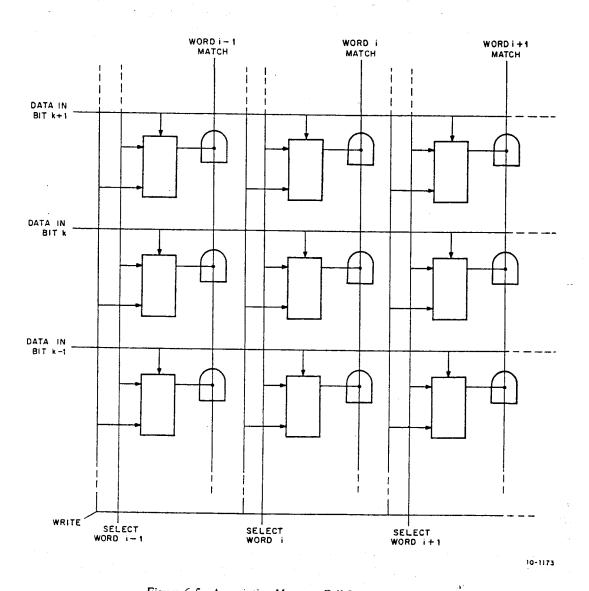

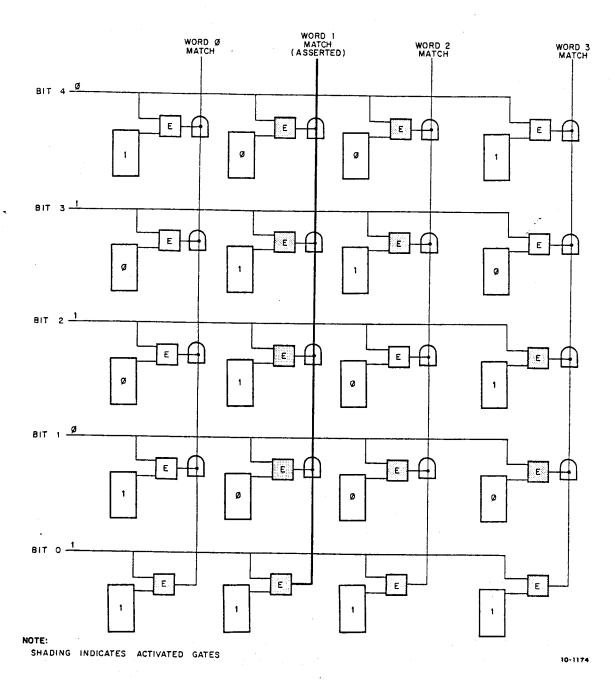

| 6-5        | Associative Memory Cell Interconnections  | . 6-8  |

| 6-6        | Example of Match                          | . 6-9  |

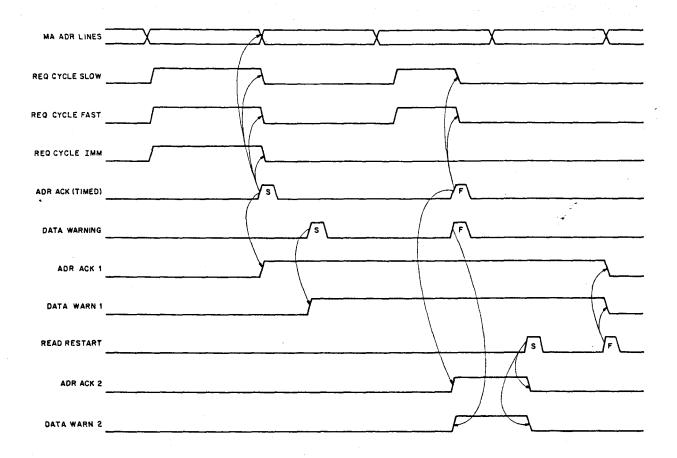

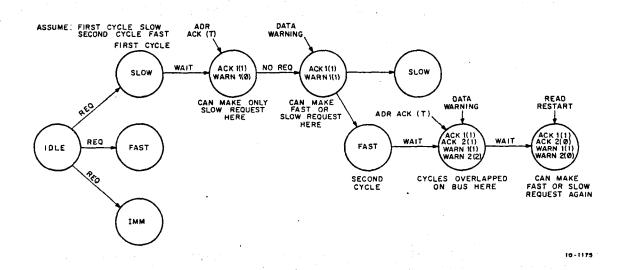

| 6-7        | Memory Cycle Overlapping                  | . 6-12 |

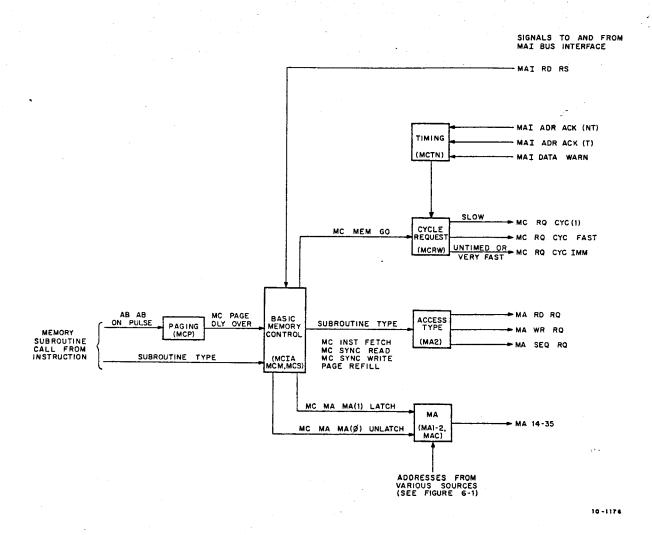

| 6-8        | Memory Subroutine and Bus Control         | . 6-14 |

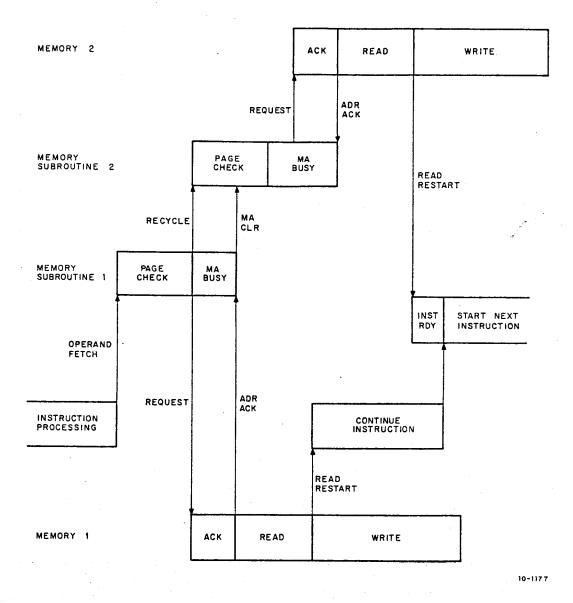

| 6-9        | Pipelining, Overlapping, Prefetching      | . 6-17 |

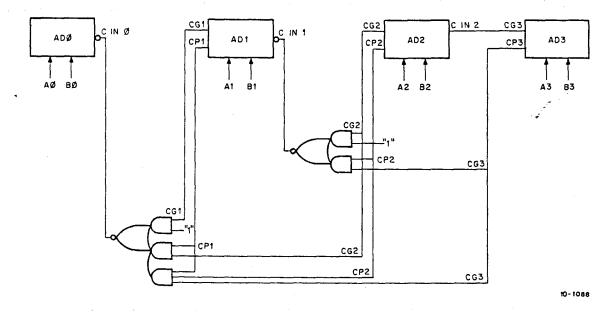

| 7-1        | Carry Skipping Adder, Simplified          | . 7-4  |

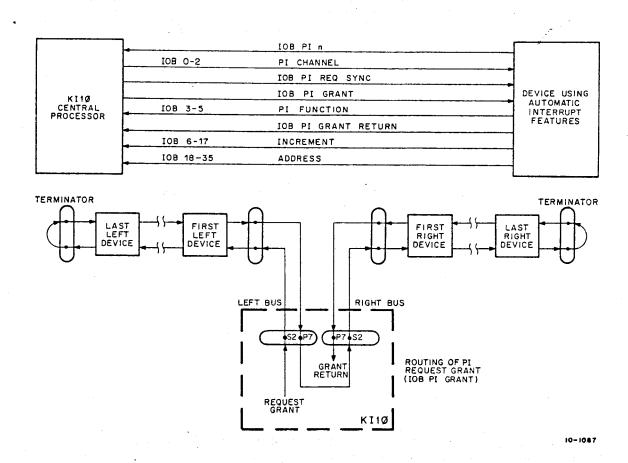

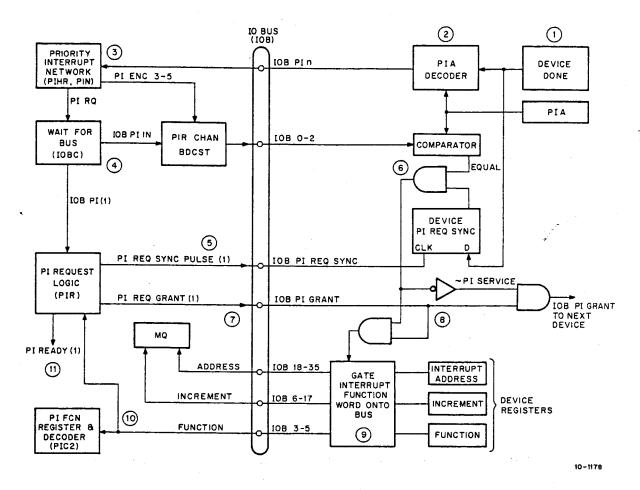

| 9-1        | PIR Bus Signals                           | . 9-5  |

| 9-2        | Basic PI Routing and Control              | . 9-6  |

## FOREWORD.

The DECsystem-10 is a general purpose, stored program computing system consisting of processors, memories, and input-output devices, each of which has independent internal timing. Every system must have at least one PDP-10 central processor but may contain several such processors, each of which is the control unit for a large-scale subsystem with its own memories and peripheral equipment. A system may also include direct-access processors, which provide for direct communication between memory and peripheral equipment. Individual processors in a system may share memories and in-out equipment, and different processors and memories may have different speeds and operating characteristics.

Extensive information on the overall system is given in Chapter 1 of the DECsystem-10 System Reference Manual; the reference manual also describes the operation and machine-level programming for the entire system. Maintenance documentation for the system is provided by a series of manuals. This manual discusses the logic and maintenance of the KI10 central processor and its basic in-out devices (reader, punch and teletypewriter). Other maintenance manuals cover the other types of processors, the several types of memories that may be used in a DECsystem-10, the various interfaces and control units for peripheral equipment, and the numerous in-out devices themselves. Drawings for any unit are available as the Customer Print Set. Information for connecting peripheral equipment of the customers own design is provided in the DECsystem-10 Interface Manual, which includes the necessary information on the circuits used in interfacing. Information on all other circuits is contained in the two-volume set of DECsystem-10 Replacement Schematics.

## PREFACE

This manual is published to aid service personnel in the operation and maintenance of the KI10 central processor and the basic in-out devices associated with it. Maintenance information for the in-out equipment is confined primarily to those portions integrated into the processor logic; separate manuals for the devices themselves are furnished with the system.

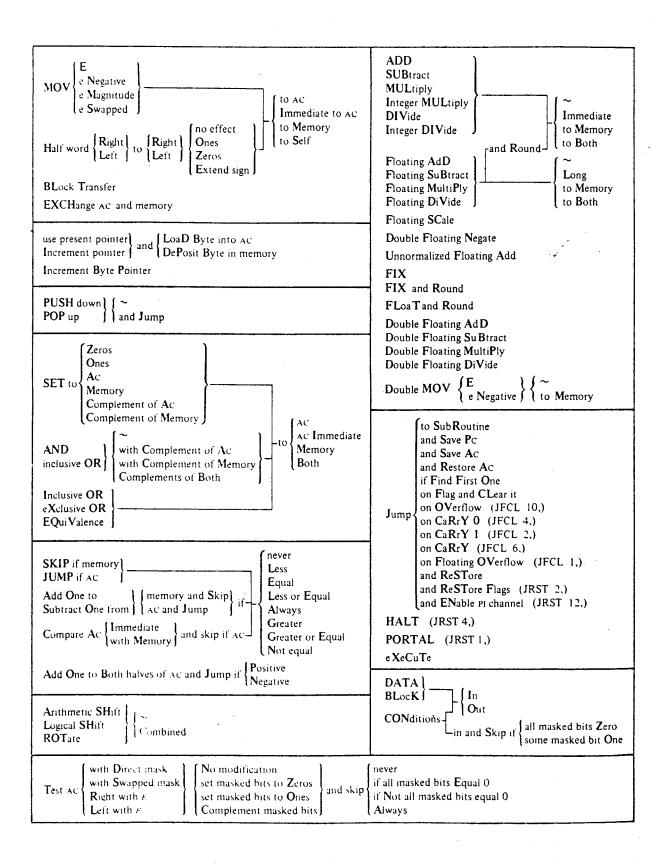

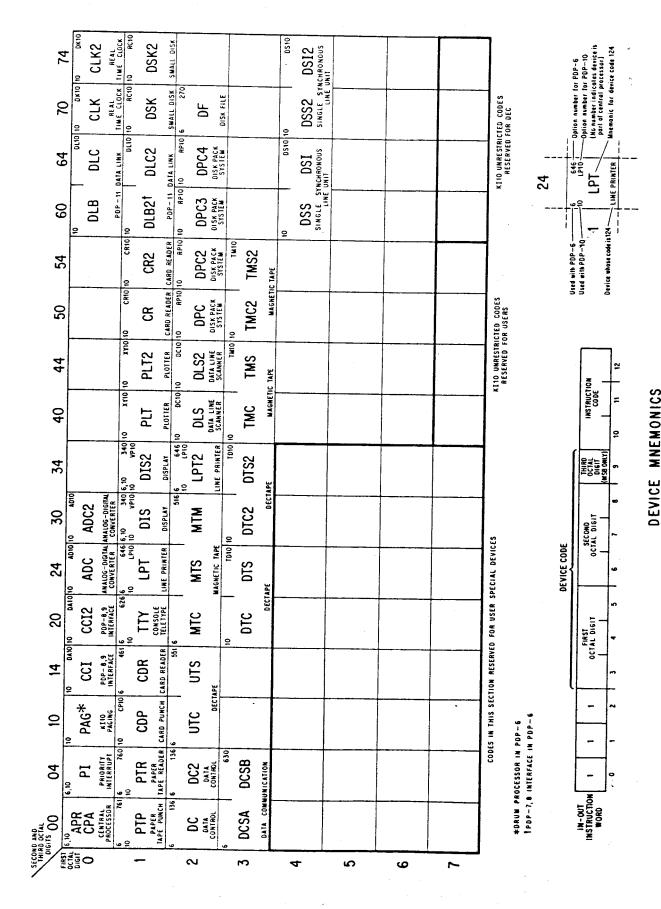

The first three chapters present a general description of the system and its operation. Chapter 1 discusses physical and electrical characteristics. Chapter 2 treats the logical organization of the system in terms of registers and data flow; the treatment is at the intermediate block diagram level to serve as a bridge between the basic system information given in Chapter 1 of the reference manual and the detailed treatment of the hardware in later chapters of this manual. There is no information here on programming, the number system, or instruction formats (which are found in the reference manual), but the entire Appendix A of the reference manual, with its tables of instructions and device mnemonics and its complete list of instruction operations in symbolic form, is included in Appendix A of this manual. The appendix also contains diagrams of the DECsystem-10 ASCII code and the formats of the words used as instructions, numbers and pointers. Chapter 3 explains the operation of the processor and the basic IO devices, including all the information given on this subject in the reference manual. Although the chapter does contain some information of a maintenance nature, it is limited to a discussion of the controls and indicators that are visible to the operator. Photographs of the various panels are printed on foldouts in Appendix B.

The next six chapters present a complete, detailed description of the system logic. Chapter 4 describes the elements used in implementing the processor logic and discusses the basic engineering documentation, including the symbols and terminology used in the logic drawings and flow charts. The next three chapters describe the hardware for main control, including control registers, fast memory, processor cycles and the console, for interfacing with memory, and for logical and arithmetic processing. Chapter 8 explains the sequences of events, with reference to the flow charts, through which the processor performs all of the basic instructions. Chapter 9 covers input-output, including IO instructions, the IO bus, priority interrupt, and the interfaces for the basic IO equipment. This chapter also describes the readin function, which makes significant use of elements in all parts of the processor, especially in-out logic and console. The reader is strongly advised not to embark upon any logic chapter in this or any other DECsystem-10 maintenance manual without first gaining a thorough understanding of the material presented in Chapter 4.

Chapter 10 contains information useful in maintaining the system, including a description of the engineering drawings, maintenance operation, maintenance programming, adjustments, and a list of diagnostics.

All engineering drawings referred to in the text may be found in the front two-thirds of the KI10 Customer Print Set. Documents of particular use to the reader are the following.

DECsystem-10 System Reference Manual DECsystem-10 Site Preparation Guide DECsystem-10 Layout Kit DECsystem-10 Interface Manual KI10 Customer Print Set DECsystem-10 Replacement Schematics DEC-10-HGAD-D

DEC-10-SITE-D

DEC-10-KITB-D

DEC-10-HIFC-D

B-DD-KI10-0

B-MN-PDP10-0-MOD1

B-MN-PDP10-0-MOD2

# CHAPTER 1 INTRODUCTION

Before reading this manual, service personnel should be familiar with the organization and function of the KI10 central processor and the DECsystem-10 as a whole to the extent covered in the System Reference Manual. It is unnecessary at first to be familiar with the details of every instruction, but begin by reading thoroughly the following parts of the reference manual: all of Chapter 1, the text portions (consisting mostly of introductory remarks to the instruction groups) in sections 2.1 to 2.10 and 2.14, and all of sections 2.12, 2.13 and 2.15 treating input-output, priority interrupt, and machine modes including paging. Effective maintenance however requires adeptness at programming, so in the long run one should be thoroughly familiar with the entire contents of the first three chapters in the reference manual (the last two pages of section 2.14 and all of sections 2.16 and 2.17 can be skipped, as they apply only to the KA10).

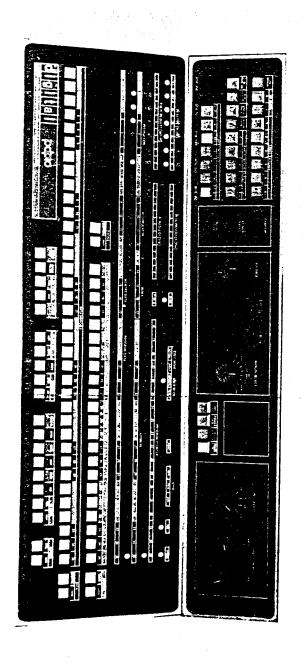

#### 1.1 PHYSICAL CHARACTERISTICS

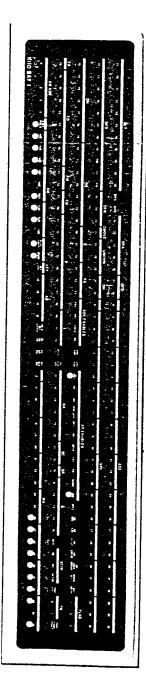

Most DECsystem-10 equipment is housed in steel cabinets or bays, each of which has an indicator panel at the top. The KI10 has three such bays numbered from left to right (Figure 1-1). Complete physical dimensions, clearance requirements, and the like are listed in the Site Preparation Guide. At the center of bay 3 (the console bay) are the console operator panel and a small maintenance panel. Behind the door below the console shelf is a vertical panel for connections to the console teletypewriter. A DK10 real time clock is ordinarily mounted in this space as well. Above the maintenance panel are the paper tape reader and punch. The space between these and the indicator panel at the top is often used for a DECtape transport. The vacant panel at the left of the reader is sometimes used for a telephone.

Behind the doors on the front of bays 1 and 2 is the module wiring, which is on mounting panels into which modules are inserted from the rear. Each bay has sixteen horizontal rows lettered A to T from the top (skipping G, I, O and Q), and each row has forty-four module connectors or slots numbered left to right. An individual row is identified by the bay number followed by the row letter, but for checking margins, rows 1A-1T are addressed as 00-17 octal and rows 2A-2T are addressed as 20-37. Both designations are printed at the outer ends of the rows (the left end in bay 1, the right end in bay 2). An individual slot is identified by the row designation followed by the slot number. Each slot has two columns of eighteen wire-wrap pins protruding through the panel from the module connector pins on the rear. The pins are lettered A to V in pairs from the top (skipping G, I, O and Q) and an individual pin is identified by the pin letter and column number (1 left, 2 right) appended to the row designation. At the outside end of each pair of rows is a small panel containing circuit breakers and margin check switches. At the bottom of bay 2 are the sockets for the memory and IO buses and two half rows of logic modules designated 3A and 3B.

Inside the doors at the rear of the bays are inner mounting doors, which are used for mounting the power equipment. At the bottom of the bay 3 mounting door are the 857 and 858 power controls (Figure 1-2), but the main 845 power control is mounted at the bottom on the side of the bay (against the end panel). The three power supplies at the top of the bay door are for margin checking only; dc voltages for the logic are supplied by the remaining power supplies in the middle of the bay 3 door and on the mounting doors on bays 1 and 2.

Looking into bay 1 or bay 2 from the rear (Figure 1-3) one can see yet another door, the cooling assembly door, which completely encloses the modules mounted at the front of the bay. Each cooling assembly contains six thermistors, and at the top and bottom are small fans that cool the logic modules by drawing air down through them.

Figure 1-1 KI10 Front View

Figure 1-2 KI10 Rear View, Bay 3

Figure 1-3 KI10 Rear View, Bay 2

The processor is connected to the other units in its subsystem (memories, direct-access processors, and peripheral equipment) by five buses, the IO bus, memory bus, DEC standard power control bus, margin check bus, and +5 margin bus. Each bus actually has two cables, right and left, where the right cable is for equipment at the right of the processor, and the left cable is for equipment at the left of the processor. As mentioned above, the memory and IO buses originate at the bottom of bay 2. (The basic IO devices and the parts of the processor that are treated like IO are connected directly into the processor logic without using the IO bus cables at all.) Both cables in the power control bus originate at the 857 power control; the cables in the +5 margin bus originate at the console maintenance panel, as does the right margin check bus. But for margin checking (other than +5 V dc), the first unit at the left is the processor itself, and the left margin check cable originates at a distribution point at the left end of the processor frame (at the bay 1 end panel).

#### 1.2 ELECTRICAL CHARACTERISTICS

Complete information on line voltage, ac power, and types of external wiring and receptacles is given in the Site Preparation Guide. The ac input to the processor is at the 845 power control at the bottom of the console bay. This control has the main circuit breakers and supplies switched ac through power cables to the several bays; it also has convenience outlets and other switched and unswitched outputs for various uses, including connections to the other power controls and a 6.3 V ac signal to the logic for the line frequency clock. Of the two power controls at the bottom of the bay 3 mounting door, the 857 (the lower one) provides timing for power on and off, controls the failure lights on the maintenance panel, has sensors for the six thermistors in bay 1, and has an override switch; the 858 contains the restart logic, the overvoltage detector, and sensors for the six thermistors in bay 2.

The H725 power supply provides a floating 15 volts; those at the bottom of the mounting doors on bays 1 and 2 are connected for -15 volts, the remaining ones at the tops of those doors and in the middle of the bay 3 door are connected for +15 volts. The H723 units in bays 1 and 2 supply +8 volts. The dc voltages required by the logic are +5 and -15 volts. The +5 volts for each pair of logic rows is provided by a pair of regulators (series pass elements) in the small panel at the outside end of the rows; these regulators use +15, +8 and -15 volts. The +15 volts is also used by the lights and the EIA teletypewriter.

The KI10 logic is special TTL circuitry with high noise immunity. The low and high logic levels are 0 and +3 volts do with tolerances of 0 to +.4 volt and +2.6 to +5 volts. Voltage levels may go outside these limits during transient conditions, but must be within the limits in the steady state. Any gate is guaranteed to hold the appropriate output when a low gate input goes as high as 1.0 volt or a high input goes as low as 2.0 volts. Pulses from pulse amplifiers in the logic are 70 ns nominal width but some are adjustable; specifications are the same as for levels, ie a pulse is simply a very short level. Rising edges are used for all edge-triggered circuits, such as the clock inputs of the D-type flipflops that are used extensively throughout the logic. Levels used on the IO and memory buses and in a very small portion of the punch logic are nominally -3 and 0 volts; memory bus pulses are 70 to 100 ns width. The logic symbology used in the drawings is essentially that of MIL-STD-806B.

The reader and punch are wired into the tap on the primary of the upper H725 power supply in bay 3 so that they operate on 115 volts regardless of the line voltage at the site. Power and signal connections to the console teletypewriter are through the panel under the console shelf (this panel has one switched and two unswitched convenience outlets for terminals, scopes, etc). All external units must have their own line power sources, but all can be controlled from the processor console. Memories and peripheral equipment designed specifically for the KI10 (such as the MF10 memory) are placed in operation by a ground remote turnon signal on the power control bus; this bus also has an emergency shutdown signal that turns off all equipment regardless of the state of the turnon signal and even if the power control in an external unit is in local mode. Older memories designed for use with the PDP-6 or KA10 (161, 163, 164, MA10, MB10, MD10, ME10) are controlled by a -15 volt turnon signal on the margin check bus. Turnon relays in older peripheral equipment may be controlled via the margin check bus or even by switched ac voltage from the 845 power control, although the latter cannot be used as a power source.

# CHAPTER 2 LOGICAL ORGANIZATION

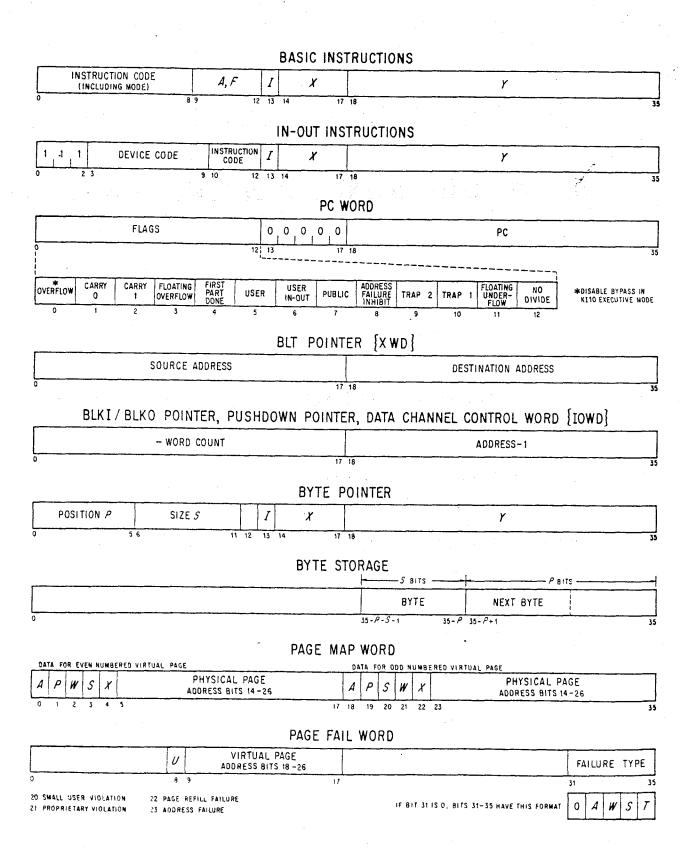

Logically the processor can be viewed as comprising four areas: basic control logic, memory logic, arithmetic logic, and input-output, although there is some crossover among them. The detailed hardware description of these areas is presented respectively in Chapters 5, 6, 7 and 9 (there is also some special maintenance logic discussed in Chapter 10). In some cases the material presented in the reference manual serves as an adequate introduction to the detailed treatment of the hardware, especially for an IO interface, where an understanding of the machine-level programming usually requires a greater understanding of the hardware that implements it. The block diagram on page 1-3 of the reference manual does show the registers that are of significance to the programmer, but a very large amount of detail is hidden not only in the box labeled "arithmetic logic," but in the boxes representing the registers as well. A much more detailed diagram of the processor is available in the Customer Print Set as drawing FD-KI10-0-REG. Here we see all of the processor registers, the data paths connecting them, and much of their associated gating. A circle containing a plus sign indicates a mixer through which information can pass from one of a number of different sources; numbers in parentheses by the data paths indicate the number of bits. The left section of the drawing shows the control and memory areas combined, the small section at the lower right shows the fast memory selection, and the rest of the drawing is devoted to the arithmetic logic. The in-out logic appears only to the extent of connections to the IO bus. The fast memory (FM) appears with the arithmetic logic, reflecting its function as a set of accumulators. However it is also a part of memory, and as a set of index registers it is part of basic control, although in the latter case its output goes to the adder - the control logic performs the effective address calculation through the arithmetic logic (the discussion of fast memory control and addressing is in Chapter 5).

#### 2.1 CONTROL

The most fundamental control circuit is a clock that times processor operations. The clock regulates a sequence of time states, which vary in length depending upon the operations that must be set up in them. Each clock pulse triggers the events that result from enabling levels set up during the previous time state and also triggers the events that set up the next time state. These states are grouped into cycles that carry out the different actions necessary for performing instructions and other special operations. The four basic cycles are instruction, fetch, execute and store (Figure 2-1). In the first of these the processor handles the instruction word and calculates the effective address, where each level of indirect addressing requires a repetition of the cycle. In the remaining cycles the processor fetches the operands, executes the instruction, and stores the result. Execution of the simpler instructions requires only the basic execute cycle, but other instructions require special execution sequences of varying complexity between the execute cycle and the store cycle.

To begin each instruction the control logic supplies an address to the memory interface and requests that an instruction be fetched. Initially these events are triggered from the console, but as the program progresses each instruction triggers the fetching of the next. The instruction address is supplied to the address bus AB as shown at C5 in the block diagram. Initially an address comes from the console address switches, and for a jump a new address comes from the adder AD, but for the normal sequence PC supplies an address through a +1 gate to reference the next location in sequence. The address from the bus goes to the memory address register MA with appropriate modification by the paging hardware. The address also goes to PC, which may therefore receive a new address, but usually receives its previous contents incremented by one (a location is skipped by sending a PC address around the loop without referencing memory).

Figure 2-1 Basic Cycles

At the beginning of the instruction cycle, the instruction word from memory is received by the memory buffer MB (at the lower left), from which the instruction code and accumulator fields are latched into IR; this latter register can also be set up from the console for initial read in. A large network associated with IR decodes the instruction code to determine what operations to perform. If indexing is called for, the address part of the instruction word from MB is added in AD to the contents of an index register from FM; and if the address is indirect, the result is sent to AB to retrieve an address word. This also comes to MB but without affecting IR.

The instruction cycle is repeated until the effective address E is in AD, whereupon the fetch cycle sends it to AB for fetching the memory operand, which comes into AR from the memory bus. At the same time the AC address is used to select a fast memory register to supply the AC operand. After the various actions necessary for the execution of an instruction are done, the result is stored in memory, an accumulator, or both, as required. The FM selection (shown at the right) includes two bits supplied by a DATAO PAG, to select the fast memory block (user only) and four bits for the address of the location in the selected block. The 4-bit address is from MB for addressing an index register, from MA when FM is addressed for a memory operand (when fast memory is treated as part of memory), from IR for addressing an accumulator, and from IR through a +1 gate for addressing a second accumulator.

Also covered as part of basic control in Chapter 5 are trapping, machine modes, the response to a page failure, and console operations (except the readin function, which uses the in-out logic and is treated in Chapter 9). The mode logic includes control over switching from one mode to another, determination of the type of paging, detection of an illegal entry into a concealed area, and the base registers that point to the user and executive process tables. When the paging circuits in the memory logic detect a page failure, the processor enters a special page fail cycle in which it executes appropriate recovery procedures, constructs a page fail word by means of the so-called magic numbers, and generally enters a page fail trap.

The memory indicators MI on the console can display information from memory via MB, but the program can also load them with an IO instruction. The operator can load the data and address switches from MI; with IO instructions, the program can load the address switches and read the data switches.

#### 2.2 MEMORY INTERFACE

Most of the interface between the processor and the memory bus comprises control circuits for the memory subroutine; this includes page checking, timing the sequence of events for calling and responding to memory, overlapping memory subroutines, and overlapping calls on the memory bus. However the interface does include the MB and MA registers and the associative memory, which supplies the information for constructing physical addresses from the virtual addresses supplied by the program. For a direct, unpaged reference MA receives the 18-bit address from the address bus, and this is expanded to 22 bits for an absolute address from the console. Otherwise the left nine bits of the virtual address are compared with the entries in the virtual part of the page table for the type of paging in effect; and if there is a match, the physical part of the table supplies the three bits for checking the type of reference and the most significant thirteen bits of the physical address. If there is no match, memory control performs a refill cycle in which a half word from the page map via MB supplies new mapping data to the associative memory at the location specified by the associative memory address counter. This reload counter can be loaded and read by IO instructions, and it increments automatically whenever the location to which it points is used for a mapping.

Associated with MB is a net that checks the parity of each word received from memory and generates the parity bit for each word being sent to memory. Another interface element is the MA special logic, which supplies low order address bits to MA for special references to the process tables (trap, page failure, MUUO, interrupt, auto restart).

#### 2.3 ARITHMETIC LOGIC

The arithmetic logic is in two major parts, the smaller of which contains the shift counter SC. Computations on exponents and computing position in byte manipulation are done in SC and its adder SCAD. SC is also used as a counter to control operations that require a sequence of steps, such as shifting, multiplying and dividing. Special numbers needed for particular manipulations and for counting steps are supplied through the SCAD data net as listed at the right. While SC is controlling a floating point operation, the exponent is saved in the floating exponent register FE.

The major part of the arithmetic logic is based on the full-word adder AD and three full-word registers, the arithmetic register AR, the selected location in fast memory used as a passive register, and a buffer register BR. Almost all of the simpler instructions are performed using only these elements and often only some of them. AD is the receiving point for input from the IO bus and special words are constructed in it from the magic numbers. It can be enabled to produce the equivalence function or the arithmetic sum of its inputs, but otherwise its output is the AND function of the inputs. AR can directly receive information from PC, IR, MA and the flags for the construction of PC words, UUO words and MAP words.

Operations at an intermediate level of complexity require the multiplier-quotient register MQ. This register holds the mask in byte manipulation (received via AD from the mask generator), but in all other operations acts as a right extension of AR even though it holds the multiplier in multiplication and the quotient is built up in it in division. The AR-MQ combination is used in a straightforward manner in double length shift and rotate instructions and in floating point add and subtract. In multiplication the multiplier is shifted out of it at the right as bits of the double length product are shifted in at the left (partial products are added into AR). In division it supplies bits of the low order part of the double length dividend to AR as bits of the quotient are brought in at the right.

Double precision floating point operations require the full capacity of the arithmetic logic with 28-bit left extensions of AD and AR. ADX and AD act together as a double precision adder, ARX and AR hold one double operand with MQ acting as a right extension for triple length manipulation, and FM and BR together hold the other double operand. Such operations even make arithmetic use of MB for temporary storage of the high part of the multiplier while the low part is being used in MQ and the high part of the quotient while the low part is being built up in MQ.

#### 2.4 INPUT-OUTPUT

The basic elements of the processor in-out are in-out transfer control (IOT) and the interface to the IO bus (IOB). Together they control the movement of device codes, control signals and data over the IO bus. The timing of in-out operations is derived from the main clock but uses a special IOT timer to control a sequence of stretched time states, as operations over the bus are much slower than operations in the processor.

The requesting of interrupts by peripheral devices is handled and synchronized by a PI request sequence that uses both the main clock and a special PIR asynchronous clock. Some events in the sequence are timed by the main clock, but it makes no difference which time states the processor happens to be in. In responding to requests over the bus, the PIR sequence determines the channel and then sends out a request grant signal so the nearest device that is requesting an interrupt on that channel can send back an interrupt function word. Upon receiving the word, the PIR logic synchronizes the request to the processor clock in order to wait for the processor to interrupt the program and begin a PI cycle, which is simply a set of basic processor cycles devoted to executing an interrupt function. If an interrupt instruction produces overflow, the processor executes a second PI cycle. Upon completing one or two PI cycles, the processor may return to the interrupted program or may hold an interrupt by beginning an interrupt service routine. The hardware contains four sets of seven flags, two sets of which are used for synchronizing requests and holding interrupts on the seven channels. The other sets are used by the program for turning individual channels on and off and for forcing interrupts on individual channels.

The IO hardware in the processor includes interfaces for the basic IO equipment – reader, punch and teletypewriter. The information provided in section 2.12 and Chapter 3 of the reference manual is quite sufficient as an introduction to the detailed descriptions of the hardware for these interfaces.

# CHAPTER 3 OPERATION

This chapter describes the processor controls and indicators that are readily accessible to the operator and discusses the normal operation of the processor, reader, punch, and console teletypewriter. Some maintenance information is included, but descriptions of any controls and indicators mounted behind the doors of the processor bays and the detailed discussion of operation for maintenance purposes are in section 10.2.

#### 3.1 CONTROL PANELS

Photographs of the various processor control panels are printed on foldouts in Appendix B. Most of the controls and indicators used for normal operation of the processor and for program debugging are located on the console operator panel and the small maintenance panel just above it; these are shown together in Figure B-1. The panels at the tops of the bays contain only indicators, most of which are for maintenance (Figures B-2 to B-4).

In the upper half of the operator panel are four rows of indicators, and below them are three rows of two-position keys and switches. Physically both are pushbuttons, but the keys are momentary contact whereas the switches are alternate action. Relative to the internal logic, the switches are actually flipflops that are controlled by the buttons but which in many cases can also be "operated" by the program. A switch is on or represents a 1 when it is illuminated. Buttons that actually trigger operating sequences in the processor are the operating keys, which are located in the right half of the bottom row. Operating switches are those that supply control levels for governing various processor operations; these include the buttons in the left half of the bottom row (except SINGLE PULSER), the paging switches at the left end of the third row, and the buttons at the left in the top two rows at the left end of the maintenance panel. The remaining buttons are sense switches, groups that constitute switch registers, and various other special keys and switches that supply information to the program or to specific hardware functions, or perform special functions of various sorts separate from the normal processor operating sequence.

The thirty-six numbered switches in the second row from the bottom on the operator panel and the twenty-two numbered switches in the row above them are the data and address switches through which the operator can supply words and addresses for the program and for use in conjunction with the operating keys and switches. At the right end of each of these switch registers is a pair of keys that clear or load all the switches in the register together. The load button sets up the switches according to the contents of the corresponding bits of the memory indicators (MI) in the fourth row. At the left end of the maintenance panel are switches to select the device for readin mode and a set of sense switches, which can be interrogated by the program.

The center section of the maintenance panel contains a voltmeter and controls for margin checking, and the right section contains speed controls for slowing down the program. Between these is a counter that registers the total time processor power has been on (the counter reads hours if the line frequency is 50 Hz, but at 60 Hz it counts six for every five hours). Below the counter are four special buttons, two of which are locks that are used to prevent inadvertent manipulation of the keys and switches while the processor is running: the console data lock disables the data and sense switches; the console lock disables all other buttons except those that are mechanical, which group comprises the four under the counter and the readin device switches.

Power is supplied to the system by means of the switch at the right end in the group under the counter. This switch is lit while power is on, but the power light in the upper right corner of the operator panel is lit only when the

system is actually in operation or is ready for operation; after power turnon the light does not come on until power is stabilized in the correct range. At the left of the margin check controls are three red lights that indicate an overtemperature condition somewhere in the processor logic, a tripped circuit breaker, or a coding assembly door open. Whenever any of these lights goes on the Power Failure flag sets and power automatically shuts down.

#### 3.1.1 Indicators

When any indicator is lit the associated flipflop is 1 or the associated function is true. Some indicators display useful information while the processor is running, but many change too frequently and can be discussed only in terms of the information they display when the processor is stopped. The program can stop the processor only at the completion of the HALT instruction; the operator can stop it at the end of every instruction, in certain memory references, or following every clock pulse (the last allows extremely slow speed operation with the clock running slowly or each clock pulse triggered individually by the operator).

Of the large groups of lights on the operator panel, the right half of the second row displays the contents of PC, the third row displays the instruction being executed or just completed, and the fourth row is the memory indicators. The left third of the third row displays IR; in an IO instruction the left three instruction lights are on, the remaining instruction lights and the left accumulator light are the device code, and the remaining accumulator lights complete the instruction code. The right half of the row displays the virtual address on the address bus, and the I and index lights reflect the states of the corresponding bits of the memory buffer. Hence the right two thirds of the row changes with every memory reference, and the I and index lights actually display the indirect bit and the index register address only following an instruction fetch or an indirect reference in an effective address calculation.

Above the memory indicators appear two pairs of words, PROGRAM DATA and MEMORY DATA. If the triangular light beside the former pair is on, the indicators display a word supplied by a DATAO PI; if any other data is displayed the light beside MEMORY DATA is on instead. While the processor is running, the addresses used for memory reference are compared with the contents of the address switches in a manner determined by the paging switches and the User Address Compare Enable flag. Whenever the two addresses are equal and the comparison is enabled, the contents of the addressed location are displayed in the memory indicators. However, once the program loads the indicators, they can be changed only by the program until the operator turns on the MI program disable switch, executes a key function that references memory, or presses the reset key (see below).

The four sets of seven lights at the left display the state of the priority interrupt channels. The PI ACTIVE lights indicate which channels are receiving request signals over the in-out bus; the PI REQUEST lights indicate channels on which the processor has accepted requests. Except in the case of a program-initiated interrupt, a REQUEST light can go on only if the corresponding ACTIVE light is on. The PI IN PROGRESS lights indicate channels on which interrupts are currently being held; the channel that is actually being serviced is the lowest-numbered one whose light is on. When an IN PROGRESS light goes on, the corresponding REQUEST goes off and cannot go on again until IN PROGRESS goes off when the interrupt is dismissed. PI ON indicates the priority interrupt system is active, so interrupts can be started (this corresponds to CONI PI, bit 28). PI OK 8 indicates that there is no interrupt being held and no channel waiting for an interrupt; this signal is used by the real time clock to discount interrupt time while timing user programs.

Note: If a REQUEST light stays on indefinitely with the associated IN PROGRESS light off and PC is static, check the PI CYC light on the indicator panel at the top of the console. If it is on, a faulty program has hung up the processor. Press RESET.

The four lights at the center of the top row indicate the processor mode. One and only one of these lights can be on and they represent the combined states of the User and Public flags. The rest of the top row contains the power light and the following control indicators.

#### **RUN**

The processor is in normal operation with one instruction following another (although the light remains on at a stop in a memory reference). When the light goes off, the processor stops.

#### STOP MAN

The operator has stopped the processor by pressing STOP or RESET.

#### STOP PROG

The processor has been stopped by a HALT instruction. At the completion of the instruction the address lights display the jump address (the location from which the next instruction will be taken if the operator presses the continue key), and the AR lights at the top of bay 2 display an address one greater than that of the location containing the instruction that caused the halt.

#### STOP MEM

The processor has stopped at a memory reference. This can be due to satisfaction of an address condition selected at the console, reference to a nonexistent memory location, or detection of a parity error.

#### **KEY MAINT**

One of the following switches is on (this light is equivalent to CONI APR, bit 8): FM MANUAL, MEM OVERLAP DIS, SINGLE PULSE, MARGIN ENABLE, SINGLE INST, STOP PAR. Any one of these switches being on implies that the processor is being operated for maintenance purposes, and is not running at maximum speed.

#### KEY PG FAIL

A key function has caused a page failure. No page fail trap is executed in response to a key-induced failure; if the processor is running, it continues the program.

The remaining processor lights are on the indicator panels at the tops of the bays. No attempt is made here to explain the meanings of these lights, as that is effectively the objective of the next five chapters — the lights reflect the logic of the machine. The large groups of lights on the panel at the top of bay 2 (Figure B-3) display the contents of the adder, the AR, BR and MQ registers, and the selected location in fast memory. At the right of the registers are a number of miscellaneous control signals, primarily enables for the shift counter, but also the enables for the IR latches and signals associated with the fetching and completion of an instruction. At the right end the upper four rows display the SC adder, its data inputs, and the shift counter and floating exponent register. The bottom row displays the AR flags, where FXU is Floating (exponent) Underflow and DCK is No Divide (divide check). FXU HOLD is a nonprogram flag that plays a role in determining underflow conditions. At the end are the flipflops that inhibit the clock and prolong its period.

The right halves of the top two rows of the bay 1 panel (Figure B-2) display the contents of the AD and AR extensions. Below these are three general flags used by the hardware and the enables for AD and ADX. The rest of the lights in the top four rows display all of the time state flipflops, flags and special control levels for the processor cycles, traps, and special sequences except those for in-out, priority interrupt, page fail and key functions. BYF6 in the top row is the First Part Done flag; the TN lights at the right end of the fourth row are the trap flags (TN 0 is Trap 2). The right half of the bottom row displays the physical address for each memory reference and the type of memory request. At the left are the lights for the associative memory. The AB 14-17 lights at the center are always either off or reflect the states of address switches 14-17.

The lights in the top row of the panel on the console bay (bay 3, Figure B-4) display either the contents of the in-out bus, the paper tape reader buffer, MB, or the information supplied by the last DATO PAG, as selected by the 4-position switch in the right section of the maintenance panel. The rest of the panel displays the user and executive base registers, and a multitude of signals for memory control, fast memory control, the key logic, paging, priority interrupt, in-out, the basic in-out devices (reader, punch, teletypewriter) and the processor flags. Note that the TRAP ENABLE light at the center of the second row is the Page Enable flag, which also enables overflow traps (DATAI PAG, bit 22). PAGE LAST MUUO PUB at the very center of the panel is the Disable Bypass flag. The User IOT flag is in the middle of the third row, and COMP ADR BRK INH near the left end of the bottom row is Address Failure Inhibit.

#### 3.1.2 Operating Keys

The operating keys can be used whether RUN is on or off. If the processor is running when a key is pressed, it simply pauses at an appropriate point in the program to perform a key cycle to execute the function. These key functions are effectively of three types. The first three keys on the left are for the initiating functions, read in, start, and continue: these functions place the processor in operation under conditions determined primarily by the function itself. The next two keys are for the terminating functions, stop and reset: if the processor is running, these functions stop it. The last five keys are for the independent functions, execute, examine, examine next, deposit, and deposit next. These functions have no inherent effect on processor operation: if the processor is not running it simply performs a key cycle and stops; if it is running, it pauses to perform a key cycle and continues the program. (However the data deposited or the instruction executed may have an effect.) Moreover the independent functions are affected by the setting of the paging switches, which determine the address space in which the function is performed.

The logic responds to the keys in two stages. When a key is pressed or several are pressed simultaneously, the logic latches them. From among the buttons latched, the processor then accepts the request for the function that has priority; the priority order is the same as the order of the keys from left to right on the panel except that reset has first priority. As soon as a function request is accepted, the corresponding button lights up and remains lit until the function is completed. If the processor is not already in operation, it performs the accepted function immediately; otherwise it saves the function until it can be performed. While any button is lit, however, no function request can be accepted; in other words, although the processor will interrupt the program to perform a key function, it will not interrupt one key function for another. It will however do one key latch while a key is lit and accept the highest priority latched function once the current function is done. Provision is also made in the logic so that the RESET key can be used to stop the processor no matter what.

#### **READ IN**

Clear all IO devices and all processor flags. Turn on RUN and EXEC MODE KERNEL (trapping and paging will both be disabled as TRAP ENABLE at the top of the console bay will be off). Execute DATAI D, 0 where D is the device code specified by the readin device switches at the left end of the maintenance panel (the rightmost device switch is for bit 9 of the instruction and thus selects the least significant octal digit (which is always 0 or 4) in the device code). Then execute a series of BLKI D, 0 instructions until the left half of location 0 reaches zero. After storing the last word in the block, fetch that word as an instruction from the location in which it was stored as specified by PC. Since RUN has been set the processor begins normal operation at the location containing the last word. (For information on the data format refer to the System Reference Manual.)

Note that the key function lasts throughout the processing of the entire block. This means that readin cannot be interrupted for another key function. Hence if it must be stopped (eg because of a crumpled tape), press RESET.

#### **START**

Turn on RUN and EXEC MODE KERNEL, and begin normal operation by fetching the instruction at the location specified by address switches 18-35. The memory subroutine for the instruction fetch loads the address into PC for the program to continue. This function does not disturb the flags or the IO equipment.

#### CONT

If STOP MEM is on begin normal operation at the point at which the processor is stopped in a memory subroutine. Otherwise turn on RUN and begin normal operation by fetching an instruction from the location specified by PC.

#### **STOP**

Turn off RUN so the processor stops with STOP MAN on. At the stop PC points to the location of the instruction that will be fetched if CONT is pressed (this is the instruction that would have been done next had the processor not stopped). The processor may stop in the middle of a two-part instruction, but pressing CONT restarts the instruction without repeating any first-part actions that would adversely affect the result.

#### RESET

Clear all IO devices, disable auto restart, high speed operation and margin programming, clear the processor flags (lighting EXEC MODE KERNEL), turn on the triangular light beside MEMORY DATA (turn off the light beside PROGRAM DATA), turn off RUN and stop the processor.

If this function is not performed within 10 ms (eg because READ IN is lit), the key triggers a panic reset that produces all of the standard reset actions and also clears all but the mechanical console keys and switches. If STOP ever fails to stop the processor, pressing this key will, but not without destroying information. To save the processor state press SINGLE INST and SINGLE PULSE simultaneously.

#### XCT

Execute the contents of the data switches as an instruction without incrementing PC, even if a skip condition is satisfied in the instruction. If PAGING USER is on and PAGING EXEC is off, execute the instruction in user virtual address space; otherwise use executive address space. If the instruction is an XCT or LUUO, the instruction called by it is also executed.

Note that an instruction executed from the console can alter the processor state like any instruction in the program: it can halt the processor, can change PC by jumping, alter the flags, or even cause a non-existent memory stop (but not a page fail trap, even if it turns on the KEY PG FAIL light).

#### NOTE

The remaining key functions all reference memory. They can therefore light KEY PG FAIL and set such flags as Nonexistent Memory and Parity Error, and they all turn on the triangular light beside MEMORY DATA, turning off the light beside PROGRAM DATA. Performing one of these functions with the ADDRESS STOP switch on stops the processor in the memory subroutine (with STOP MEM on). These functions use an address supplied by the address switches, and the way that address is interpreted is determined by the paging switches. If both paging switches are off, the function uses a 22-bit absolute physical address supplied by address switches 14–35, and fast memory references are made to the block selected by the FM block switches at the left end of the maintenance panel. If either paging switch is set, the function uses a virtual address supplied by address switches 18–35 and the FM block switches have no effect (in other words the function has access to one of the virtual address spaces defined for a normal program). If PAGING EXEC is on, the function has access to user address space.

#### **EXAMINE THIS**

Display the contents of the location specified by the paging and address switches in the memory indicators.

#### **EXAMINE NEXT**

Add 1 to the address displayed in the address switches, and display the contents of the location then specified by the paging and address switches in the memory indicators.

#### **DEPOSIT**

Deposit the contents of the data switches in the location specified by the paging and address switches, and display the word deposited in the memory indicators.

#### **DEPOSIT NEXT**

Add 1 to the address displayed in the address switches, deposit the contents of the data switches in the location then specified by the paging and address switches, and display the word deposited in the memory indicators.

#### 3.1.3 Operating Switches

Besides defining the address space for the independent key functions, the paging switches also perform this service for address comparison and for the group of five switches just at the left of the operating keys. Whenever the processor references memory or an accumulator, it may compare the virtual address used with that specified by address switches 18–35 and may take some action if the two are identical. There are a number of conditions that affect the comparison. First, comparison can be made only for memory references and accumulator write references—there is never a comparison for an index register reference or an accumulator read reference. Given the proper type of reference, the comparison must be enabled. If PAGING EXEC is on and PAGING USER is off, the comparison is enabled for executive address space; if PAGING EXEC is off and PAGING USER is on, the comparison is enabled for user address space provided the program has turned on USER ADR COMP (User Address Compare Enable flag) in the upper left corner of the console indicator panel; if both paging switches are on, the comparison is enabled for executive address space, provided USER ADR COMP is on (in other words with both switches on, PAGING USER applies the flag condition to PAGING EXEC). In a reference of the correct type with the comparison enabled, if the virtual address on the address bus is identical to the address in switches 18–35, the processor displays the contents of the addressed location or accumulator in the memory indicators (unless the light beside PROGRAM DATA is on).

Except in an AC reference, the same situation that causes the word display can also be made to stop the processor or produce an address failure, depending upon the purpose for which the reference is made as selected by the three address condition switches. FETCH INST selects the condition that access is for retrieval of an instruction, including an instruction executed by an XCT, a user LUUO or a dispatch interrupt, but not a trap or standard interrupt instruction, nor one executed by an executive LUUO. FETCH DATA selects read-only access for retrieval of an operand or an address word in an effective address calculation, but not the PC word in an MUUO. WRITE selects access for writing, including read-modify-write, but not writing done by an MUUO or executive LUUO. Whenever a memory reference satisfies both the comparison condition and any selected address condition, the processor performs the action selected by the other two switches. ADDRESS STOP halts the processor with STOP MEM on and PC pointing to the instruction that was being performed (running with ADDRESS STOP on slows down the processor). ADDRESS BREAK causes an address failure except in an instruction performed while COMP ADR BRK INH is on. ADDRESS STOP also stops any examine or deposit function in the memory subroutine.

Conditions associated with the comparison are displayed by the COMP lights in the middle of the bay 3 indicator panel. From left to right these indicate an accumulator write reference, a memory read reference, equal addresses in a synchronous reference (an operand reference, but limited to the first in a double operand) and equal addresses in an asynchronous reference (an instruction fetch or the second in a double operand).

The description of each switch relates the action it produces while it is on.

#### SINGLE INST

Whenever the processor is placed in operation, clear RUN so that it stops at the end of the first instruction. Hence the operator can step through a program one instruction at a time, pressing START for the first one and CONT for subsequent ones. Each time the processor stops, the lights display the same information as when STOP is pressed. Note that read in cannot be done in single instruction mode, as the function extends over many instructions and there is thus no way to continue.

APR CLK FLAG (Clock flag) on the console indicator panel is held off to prevent clock interrupts while SINGLE INST is on. Otherwise interrupts would occur at a faster rate than the instructions.

#### **CAUTION**

It is not generally worthwhile to attempt to use the interrupt system in single instruction mode except with the slowest start-stop devices, such as reader, punch and teletypewriter. In any event an interrupt hangs up the processor, and the operator must dispose of it manually before single instruction operation can continue.

SINGLE INST will not stop the processor if a hangup prevents it from getting to the end of an instruction. Use STOP, RESET, or SINGLE PULSE.

#### SINGLE PULSE

Inhibit the clock so that a single clock pulse is generated each time SINGLE PULSER is pressed. If the processor is not already in operation, an operating key must be pressed before SINGLE PULSER can be used. If the processor is running, it converts to single pulse operation at the beginning of the instruction cycle; hence the clock will not stop if the processor does not reach the instruction cycle, say because it is hung up in a multiply or divide sequence. To force the processor into single pulse operation regardless of its position in the operating sequence, turn on both SINGLE INST and SINGLE PULSE; this stops the processor without destroying information, as would occur if RESET were pressed.

#### STOP PAR

Stop with STOP MEM on at the end of any memory reference in which even parity is detected in a word read. A parity stop is indicated by the following: PAR ERR FLAG (Parity Error flag) is on in the bottom row on the bay 3 indicator panel; and among the PAR lights in the third row from the bottom, ERR is on, IGN (ignore parity) is off, and BIT displays the parity bit for the word read.

If IGN is on (it displays a signal from the memory), parity errors are not detected and no stop can occur. Running with STOP PAR on slows down the processor.

#### STOP NXM

Stop with STOP MEM on if a memory reference is attempted but the memory does not respond within  $100 \mu s$ . This type of stop is indicated by FLAGS NXM (Nonexistent Memory flag) being on in the bottom row on the bay 3 indicator panel.

#### REPEAT

If SINGLE PULSE is on and the processor is placed in operation, slow down the clock so that the processor runs at a clock rate determined by the speed controls at the right end of the maintenance panel. If the processor is not already running, it can be placed in single-pulse repeat operation by pressing an operating key and then pressing SINGLE PULSER. If the processor is running and the switches are turned on in the order REPEAT/SINGLE PULSE, then it goes into single pulse operation automatically at the beginning of the instruction cycle. If the processor is running with REPEAT off, it stops at the beginning of the instruction cycle when SINGLE PULSE is turned on; to restart it, turn on REPEAT and then press SINGLE PULSER twice. In any event repetition ceases (and the light in the SINGLE PULSER button goes off) whenever the processor gets to a point where the clock would have stopped anyway had SINGLE PULSE not been on. To restart, simply press SINGLE PULSER. The lamp in the SINGLE PULSER button goes off at each clock pulse and turns back on each time the clock is retriggered; hence the button glows with an intensity that is relative to the clock duty cycle (eg for a given speed, the light will be dimmer for a program with many memory references). When either REPEAT or SINGLE PULSE is turned off, operation terminates after one more clock.

If SINGLE PULSE is off and any operating key is pressed, then every time the repeat delay can be retriggered, wait a period of time determined by the setting of the speed control and repeat the given key function. The point at which the processor can restart the repeat delay depends upon the type of key function being repeated as follows.

For an initiating function the delay starts when the processor stops with RUN off. This is either when the program gives a HALT instruction (STOP PROG) or following the first instruction if SINGLE INST is on.

For an independent function the delay starts every time the function is done whether RUN is on or off.

A terminating function stops the processor and the delay starts every time the function is repeated. Reset is generally used only to provide a chain of reset pulses on the IO bus, and stop is used to troubleshoot the clock.

In any case continue to repeat the function until REPEAT is turned off. (The function is often repeated once more, but this is noticeable only with very long repeat delays.)

The speed control includes a six-position switch that selects the delay range and a potentiometer for fine adjustment within the range. Delay ranges are as follows.

| Position | Range                     |  |

|----------|---------------------------|--|

| 1        | 200 ns to 2 μs            |  |

| 2        | 2 μs to 20 μs             |  |

| 3        | $20 \mu s$ to $500 \mu s$ |  |

| 4        | 500 $\mu$ s to 6 ms       |  |

| 5        | 6 ms to 160 ms            |  |

| 6        | 160 ms to 4 seconds       |  |

#### MI PROG DIS

Turn on the triangular light beside MEMORY DATA (turn off the light beside PROGRAM DATA) and inhibit the program from loading any switches or displaying any information in the memory indicators. The indicators will thus continually display the contents of locations selected from the console.

#### MEM OVERLAP DIS

Prevent memory control from overlapping cycles on the memory bus. (This has no effect on pipelining within memory control, such as overlapping the page checking of consecutive memory subroutines.)

#### MARGIN ENABLE

Enable maintenance operation, including writing with even parity in memory and checking speed or voltage margins. Maintenance actions attempted by the program are indicated by the last four lights on the left end of the second row from the bottom on the bay 3 indicator panel. With maintenance operation enabled, writing with even parity and checking speed margins are otherwise entirely under program control. Voltage margins may be checked by the program or the operator (for information on the margin select and manual margin address switches, refer to section 10.2).

#### **FM MANUAL**

All fast memory references for any purpose (index register, accumulator, memory) and under any conditions are made to the fast memory block selected by the FM block switches. When FM MANUAL is off, the block switches control fast memory references only in examine and deposit type key functions with both paging switches off (ie with the function using physical addressing). Turning on FM MANUAL overrides all other conditions so that all fast memory references are controlled by the block switches.

#### 3.1.4 Panel Maintenance

A panel indicator is worthless if the bulb is burned out. Before attempting to use the information presented by the panels, press the LAMP TEST button below the counter on the maintenance panel; this turns on all of the lamps so any that are burned out can easily be detected. To replace a lamp in a button, pull out the button cap. The bulb will come with the cap, so remove it, put a new one in the cap, and push the cap back into the panel.

#### **CAUTION**

The lamp test checks not only the bulbs but also indicator driver transistors and indicator cables. Hence after changing a bulb always repeat the test. If the replacement bulb will not light, the problem is probably more serious and requires more significant corrective maintenance.

Replacing a bulb for an indicator requires removal of the panel. To remove the operator panel on early units, place your hands at the bottom corners and press in on the flush catches that are underneath the ends of the panel. On later units, remove the panel by grasping the small black latches on either side; then remove the inner aluminum lamp shield by lifting it out. The panel will snap free and can be pulled away. Pull out the bad bulb and insert a fresh one, but exercise some care in doing this – the bulb has a pair of pins that must be inserted in the socket, and shorting the terminals will burn out a transistor. After replacing the bad bulbs, snap the panel back in place.

The indicator panels are hinged at the bottom. Grasp the panel at the top and pull down. It is unnecessary to return to the console to find the bad bulb, as each bay has its own lamp test button, located at the left of the lights behind the panel.

On the maintenance panel the only lamps not in buttons are those for the failure indicators. To remove the panel, first remove the four switch knobs, each of which is held to its shaft by a pair of Allen set screws. The panel is held in place by Velcro strips at the ends and can be removed simply by pulling it out. Since handling the maintenance panel is somewhat of a chore, it is probably best to replace all three bulbs whenever one burns out. Press the panel back in place, then put on the knobs oriented so that the set screws are against the flats of the shafts. Tighten the screws lightly, rock each switch to make sure it is oriented properly, and then tighten the screws thoroughly.

#### 3.2 CONSOLE IN-OUT EQUIPMENT

The console teletypewriter is generally on a stand by the console. The reader and punch are located in a drawer above the maintenance panel, but the face of the reader is available on the front of the drawer, and at its right are a slot for removing tape from the punch and a pair of rocker switches for feeding tape through reader or punch. Indicators for all three devices are on the panel at the top of the console.

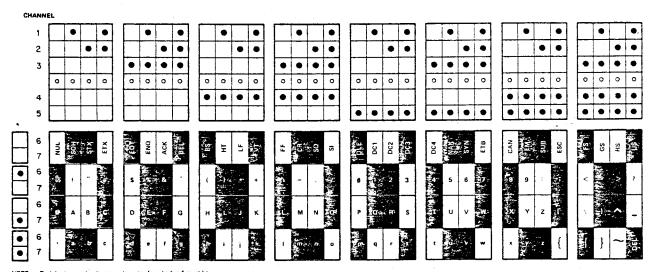

The ASCII code used with all console teletypewriters and generally used for alphanumeric data on paper tape is shown on page A21. The main part of the diagram shows the configuration of bits 1-5 or channels 1-5 for the various characters in four sets, where a dot represents a 1 or a hole (the orientation of the tape is indicated by the little circles, which represent feed holes). At the left end is the configuration for channels 6 and 7 for the four sets of characters. Channel 8 (which is not shown) is ordinarily used for parity. For the standard even parity of the teletypewriter, the eighth bit is 1 for the characters printed on the dark background.

#### 3.2.1 Reader

The contents of the reader buffer can be displayed in the top row of lights on the indicator panel by setting the IND SELECT switch on the maintenance panel to PTR. The remaining indicators for the reader are the PTR lights at the middle of the bottom row and near the left end of the second row.

Tapes for the reader must be unoiled and opaque. To load the reader, place the fanfold tape stack vertically in the bin at the right, oriented so that the front end of the tape is nearer the read head and the feed holes are away from you. Lift the gate, take three or four folds of tape from the bin, and slip the tape into the reader from the front. Carefully line up the feed holes with the sprocket teeth to avoid damaging the tape, and close the gate. Make sure that the part of the tape in the left bin is placed to correspond to the folds, otherwise it will not stack properly. If the program requires that the Tape flag be set and it is not, briefly press the feed switch at the right; setting the flag also sets Done to signal the program that the tape is loaded. After the program has finished reading the tape, run out the remaining trailer by pressing the feed switch.

#### 3.2.2 Punch

The punch is behind the reader in the console drawer. Fanfold tape is fed from a box at the rear of the drawer. After it is punched, the tape moves into a storage bin from which the operator may remove it through the slot on the front. Pushing the feed switch beside the slot clears the punch buffer and punches blank tape as long as it is held in. Busy being set prevents the switch from clearing the buffer, so pressing it cannot interfere with program punching.

To load tape, first empty the chad box behind the punch. Then tear off the top of a box of fanfold tape (the top has a single flap; the bottom of the box has a small flap in the center as well as the flap that extends the full length of