# KL10-Based DECSYSTEM-20 Installation Manual

# KL10-Based DECSYSTEM-20 Installation Manual

The drawings and specifications herein are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of equipment described herein without written permission.

Copyright © 1978 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DIGITAL | DECsystem-10 | MASSBUS |

|---------|--------------|---------|

| DEC     | DECSYSTEM-20 | OMNIBUS |

| PDP     | DIBOL        | OS/8    |

| DECUS   | EDUSYSTEM    | RSTS    |

| UNIBUS  | VAX          | RSX     |

| 01.1200 | VMS          | IAS     |

### **CONTENTS**

|           | Pa                                                        | ge            |

|-----------|-----------------------------------------------------------|---------------|

| CHAPTER 1 | INTRODUCTION                                              |               |

| CHAPTER 2 | DECSYSTEM-20 INSTALLATION PLAN                            |               |

| 2.1       | INTRODUCTION                                              | )_1           |

| 2.2       | PERSONNEL                                                 | ,-1<br>)_1    |

| 2.3       | SCHEDULING                                                | ,- 1<br>)_ 1  |

| 2.4       | PREREQUISITES AND ASSUMPTIONS                             | _ 1           |

| 2.5       | SYSTEM INSTALLATION AND CHECKOUT                          | -1            |

| 2.6       | SYSTEM SPARES                                             | 2<br>:-3      |

| CHAPTER 3 | UNPACKING AND INSPECTION                                  |               |

| 3.1       | SHIPPING AREA PROCEDURES3                                 | _1            |

| 3.2       | SEALED CONTAINERS                                         | - 1<br>- 1    |

| 3.3       | PACKING LIST                                              | - 1<br>- 1    |

| 3.4       | SHIPPING DAMAGES                                          | _ 1           |

| 3.5       | OPENING SHIPPING CONTAINERS                               | - 1<br>- 1    |

| 3.6       | EXTERNAL DAMAGE INSPECTION                                | - 1           |

| 3.7       | INTERNAL DAMAGE INSPECTION                                | _1            |

| 3.8       | INVENTORY                                                 | _6            |

| 3.9       | MISSING PARTS PROCEDURES                                  | -7            |

| 3.9.1     | Short Shipment Procedure                                  | -7            |

| 3.9.2     | Non-Short-Shipment Missing Items                          | ın            |

| 3.10      | COMPLETION                                                | n             |

| 3.11      | RETURNING DAMAGED EQUIPMENT                               | 1             |

| CHAPTER 4 | UNIT PLACEMENT                                            |               |

| 4.1       | EQUIPMENT MOVEMENT4                                       | . 1           |

| 4.2       | KL10-C (2040) CABINET HANDLING4                           | .2            |

| 4.3       | DESKIDDING ASSOCIATED EQUIPMENT4                          | <u>-</u><br>3 |

| 4.4       | REQUIRED TOOLS4                                           | .3            |

| 4.5       | FINAL CHECKS4                                             | 4             |

| CHAPTER 5 | UNIT INTERCONNECTION                                      |               |

| 5.1       | EQUIPMENT POSITIONING5-                                   | 1             |

| 5.2       | BOLTING FRAMES5-                                          | 1             |

| 5.3       | KL10-C (2040) CABINET INSTALLATION AND INTERCONNECTION 5- | 1             |

|                |                                                                  | Page |

|----------------|------------------------------------------------------------------|------|

| 5 2 1          | Cabinet 2 – Cabinet 3 Assembly                                   | 5-1  |

| 5.3.1<br>5.3.2 | Cabinet 2 – Cabinet 1 Assembly                                   | 5-11 |

|                | Memory 2 (Option) Cabling Interconnections                       | 5-12 |

| 5.3.3          | Cabinet 3 to Cabinet 2 and Cabinet 1 Cabling Connections         | 5-12 |

| 5.3.4          | Cabinet 1 – Cabinet 2 (Front End – I/O Cabling Interconnections) | 5-12 |

| 5.3.5          | Leveling Feet                                                    | 5-13 |

| 5.3.6          | Final KL10-C (2040) Central Processor Assembly                   | 5-13 |

| 5.3.7<br>5.4   | SYSTEM GROUNDING                                                 | 5-13 |

| 5.5            | CHECKING GROUND WIRES                                            | 5-14 |

| 5.6            | CUSTOMER VOLTAGE CHECKS                                          | 5-14 |

| 5.7            | COMPONENT CHECKS                                                 | 5-14 |

| 5.8            | FASTENER CHECKS                                                  | 5-14 |

| 5.9            | CABLING CHECKS                                                   | 5-14 |

| 5.10           | SHORT CIRCUIT CHECKS                                             | 5-14 |

| 5.11           | BACKPLANE CHECKS                                                 | 5-14 |

| 5.12           | VISUAL INSPECTION                                                | 5-14 |

| 5.13           | SYSTEM CABLES                                                    | 5-15 |

| 5.14           | CABLE INSTALLATION                                               | 5-15 |

| CHAPTER 6      | SYSTEM INTEGRATION                                               |      |

|                | INTRODUCTION                                                     | 6-1  |

| 6.1            | RP04/06 DISK DRIVES                                              | 6-1  |

| 6.2            | TU45 MAGNETIC TAPE DRIVES                                        | 6-2  |

| 6.3            | LP20 LINE PRINTER                                                | 6-2  |

| 6.4<br>6.5     | CARD READER                                                      | 6-2  |

|                | LA36 CONSOLE DEVICE                                              | 6-2  |

| 6.6            | DC20 COMMUNICATIONS                                              | 6-3  |

| 6.7            | GROUNDING                                                        | 6-3  |

| 6.8<br>6.9     | DN20 SUBSYSTEM                                                   | 6-3  |

| 0.9            | D1\20 5\CD5 1 5\1 \E\\1 \\ \\\\\\\\\\\\\\\\\\\\\\\               |      |

| CHAPTER 7      | POWER CHECKOUT                                                   |      |

| 7.1            | PREPOWER CHECKOUT PROCEDURES                                     | 7-1  |

| 7.1.1          | 11/40 CPU – Front End                                            | 7-4  |

| 7.1.2          | Peripheral Drawers                                               | 7-4  |

| 7.1.3          | 863 Power Control                                                | 7-5  |

| 7.1.4          | 861 Power Control                                                | 7-5  |

| 7.1.5          | H761 Regulated Power Supply                                      | 7-5  |

| 7.1.6          | H7420 Power Supplies and Associated Voltage Regulators           | 7-5  |

| 7.2            | SYSTEMS CHECKOUT                                                 | /-5  |

| 7.2.1          | Print Set Definitions                                            | /-:  |

| 7.2.2          | PDP-11/40 and Peripheral Drawer Power Harness                    | 7-6  |

| 7.2.3          | Power Checkout Procedures                                        | /-(  |

| A.        |                                                    | Page |

|-----------|----------------------------------------------------|------|

| CHAPTER 8 | SYSTEM CHECKOUT                                    |      |

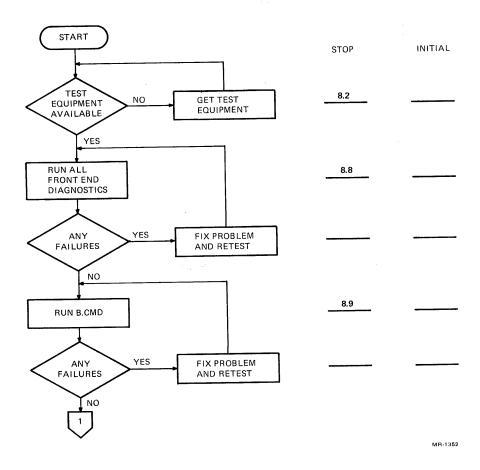

| 8.1       | INTRODUCTION                                       | 8-1  |

| 8.2       | TEST EQUIPMENT                                     |      |

| 8.3       | TEST SOFTWARE                                      |      |

| 8.3.1     | PDP-11 11/40 Front-End Diagnostics                 | 8-3  |

| 8.3.2     | Diagnostic Support Programs                        |      |

| 8.3.3     | KL10 Processor Hardware Diagnostics - Model B      |      |

| 8.3.4     | Processor Functional Diagnostics                   |      |

| 8.3.5     | Memory Diagnostics                                 |      |

| 8.3.6     | TM02/TU45 Magtape Diagnostics                      |      |

| 8.3.7     | RH20 Controller Diagnostics                        |      |

| 8.3.8     | RP04/RP06/(Massbus) Disk Diagnostics               | 8-6  |

| 8.3.9     | Disk Subsystem Reliability                         | 8-6  |

| 8.3.10    | System Exerciser Tests                             |      |

| 8.4       | DOCUMENTATION                                      |      |

| 8.5       | STANDARD CONSOLE SWITCHES                          |      |

| 8.6       | DIAGNOSTIC SOFTWARE REFERENCE                      |      |

| 8.7       | DIAGNOSTIC INPUT MEDIA                             | 8-7  |

| 8.8       | PHASE A - 11/40 FRONT END AND OPTIONS VERIFICATION | 8-8  |

| 8.8.1     | Load Medium: RX01 Floppy Disk                      |      |

| 8.8.2     | Applicable Diagnostics                             |      |

| 8.8.3     | CD20 Checkout                                      |      |

| 8.8.3.1   | Indicator Test                                     | 8-8  |

| 8.8.3.2   | Alpha and Binary Deck Tests                        | 8-8  |

| 8.8.4     | DC20 Verification                                  | 8-9  |

| 8.8.4.1   | Equipment Required                                 | 8-9  |

| 8.8.4.2   | DZDHK Modem Control Check                          |      |

| 8.8.4.3   | DZDHM/DZDHN Checkout                               | 8-9  |

| 8.9       | PHASE B - PDP-11-BASED KL10 AND KL10-BASED KL10    |      |

|           | DIAGNOSTIC VERIFICATION                            | 8-9  |

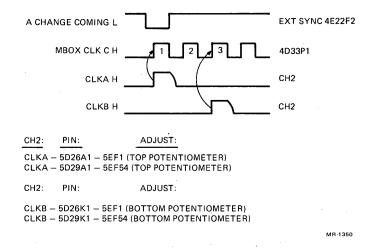

| 8.9.1     | Deskew Check                                       | 8-9  |

| 8.9.2     | Load Medium - RP KLAD Pack                         | 8-9  |

| 8.9.3     | DTE/CPU Checkout                                   | 8-10 |

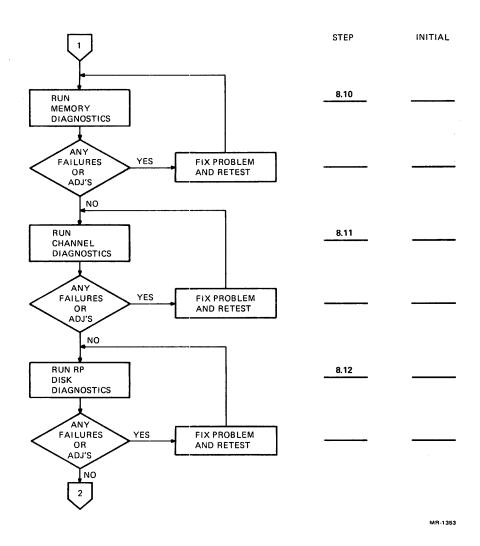

| 8.10      | PHASE C - MEMORY DIAGNOSTIC VERIFICATION           | 8-10 |

| 8.10.1    | Introduction                                       | 8-10 |

| 8.10.2    | DGMMA.A11                                          |      |

| 8.10.3    | DDMMD/DDMMG Memory Exerciser                       | 8-11 |

| 8.10.4    | DDMME BLT Test                                     |      |

| 8.10.5    | MB20 Option Diagnostics                            |      |

| 8.11      | PHASE D - RH20 CHANNEL DIAGNOSTIC VERIFICATION     |      |

| 8.12      | PHASE E - RP DISK DIAGNOSTIC VERIFICATION          |      |

| 8.12.1    | Formatting                                         |      |

| 8 12 2    | Error Rates                                        | 8-11 |

|            |                                                           | Page  |

|------------|-----------------------------------------------------------|-------|

| 8.12.3     | Head Alignment Verification (DFRPH or DFRPK)              | 8-12  |

| 8.12.4     | PTIME (DDRPI)                                             |       |

| 8.12.5     | Diagnostics                                               |       |

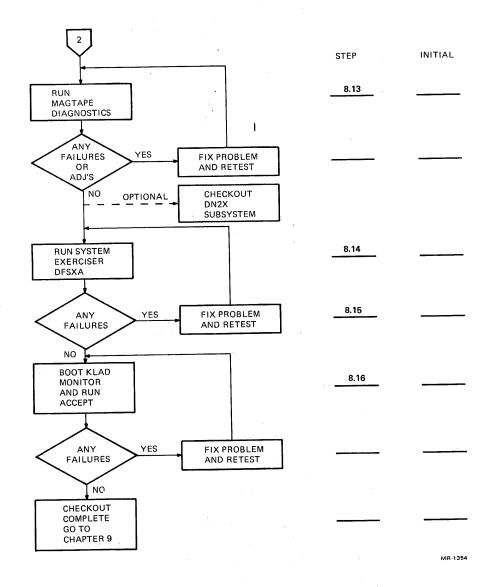

| 8.13       | PHASE F – TU45 MAGNETIC TAPE SYSTEM DIAGNOSTIC            |       |

|            | VERIFICATION                                              | 8-12  |

| 8.13.1     | DFTUE                                                     |       |

| 8.13.2     | DFTUK                                                     | 8-12  |

| 8.13.3     | DFTUF                                                     | 8-12  |

| 8.13.4     | Errors                                                    | 8-13  |

| 8.13.5     | Adjustment                                                | 8-13  |

| 8.13.6     | DFTUE Compatibility Test                                  |       |

| 8.14       | DN2X COMMUNICATIONS SUBSYSTEM                             |       |

| 8.15       | PHASE G - SYSTEM EXERCISER DFSXA                          | 8-14  |

| 8.16       | PHASE H - KLAD-20 MONITOR CHECK                           | 8-14  |

| 8.16.1     | Introduction                                              |       |

| 8.16.2     | KLDCP Disk Boot Check                                     |       |

| 8.16.3     | KLAD Monitor Disk Boot Check                              |       |

| 8.16.4     | General Rules                                             |       |

| 8.16.5     | KLAD-20 Backup                                            |       |

| 8.17       | DECX/11 PROCEDURE/MAP LISTINGS                            |       |

| 8.18       | MA20 - MB20 DESKEW PROCEDURE                              |       |

| 8.19       | RH20 DESKEW PROCEDURE                                     |       |

| CHAPTER 9  | HARDWARE ACCEPTANCE PROCEDURES                            |       |

| 9.1        | PURPOSE                                                   | 9-1   |

| 9.2        | GENERAL INFORMATION                                       |       |

| 9.3        | REQUIREMENTS                                              |       |

| 9.4        | TEST VERIFICATION                                         |       |

| 9.5        | COMPLETION                                                |       |

| <b>7.0</b> |                                                           |       |

| CHAPTER 10 | SYSTEM ADD-ON AND ADJUSTMENT PROCEDURES                   |       |

| 10.1       | MA20/MB20 ADD-ON MEMORY INSTALLATION, CHECKOUT,           |       |

|            | AND ACCEPTANCE PROCEDURE                                  |       |

| 10.1.1     | Introduction                                              |       |

| 10.1.2     | MA20/MB20 Add-On Parts List                               |       |

| 10.1.2.1   | Various MA20 System Components                            |       |

| 10.1.2.2   | M B20 System Components                                   |       |

| 10.1.3     | Applicable Documentation, Diagnostics, and Required Tools |       |

| 10.1.4     | MA20/MB20 Preinstallation (Skidded) Checkout              |       |

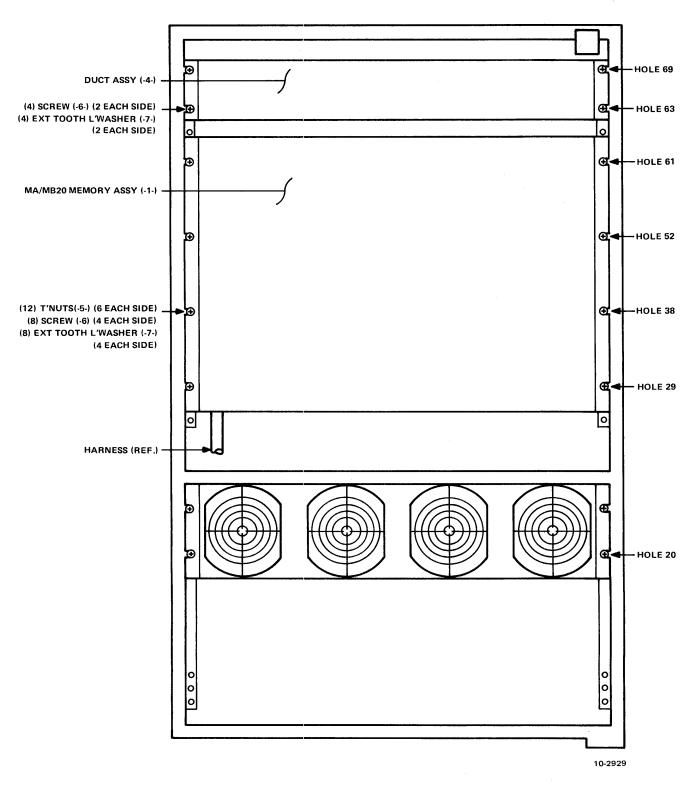

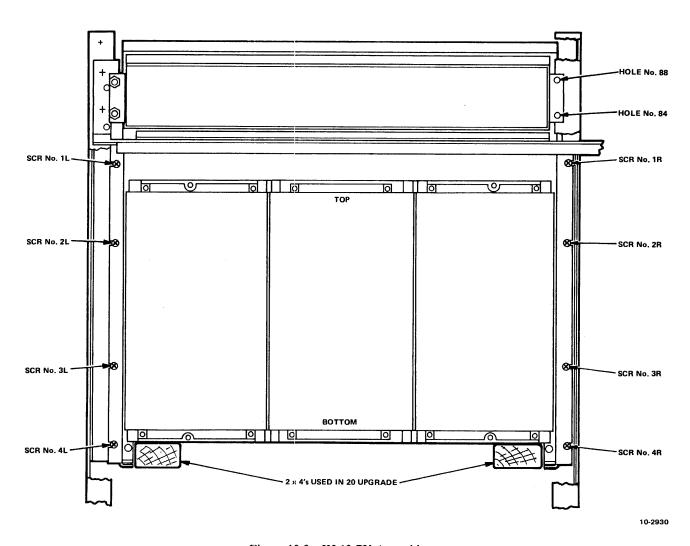

| 10.1.5     | Mounting Procedures                                       | 10-7  |

| 10.1.6     | Checkout and Acceptance Procedure                         | 10-13 |

| 10.2       | KL10-PV UPGRADE PROCEDURE FOR KL10-C                      |       |

| 10.2.1     | PV Upgrade Resources                                      | 10-24 |

|            |                                                  | Page  |

|------------|--------------------------------------------------|-------|

| 10.2.1.1   | On-Site or Locally Supplied Resources            | 10-24 |

| 10.2.1.2   | Resources To Be Supplied (Shipped)               | 10-24 |

| 10.2.2     | Diagnostic Test Programs                         | 10-24 |

| 10.2.2.1   | Model A CPU System                               | 10-24 |

| 10.2.2.2   | Model B CPU System                               | 10-25 |

| 10.2.3     | PDP-10 KL10 Instruction Timing Test (DFKFB)      | 10-26 |

| 10.3       | CACHE UPGRADE PROCEDURE                          | 10-28 |

| 10.3.1     | Introduction                                     |       |

| 10.3.2     | Test Equipment Required                          | 10-28 |

| 10.3.3     | Upgrade Procedure                                |       |

| 10.3.4     | Power Tab Identification Notes                   | 10-29 |

| CHAPTER 11 | REPORTING PROCEDURES                             |       |

| 11.1       | INTRODUCTION                                     | 11-1  |

| 11.2       | LARS REPORT FORM                                 |       |

| 11.3       | DECSYSTEM-20 INSTALLATION REPORT                 | 11-3  |

| 11.4       | DAILY LOG                                        | 11-4  |

| 11.5       | LCG INSTALLATION WARRANTY ACTIVITY SUMMARY FORMS | 511-4 |

| APPENDIX A |                                                  |       |

| APPENDIX B | B SAMPLE DIAGNOSTICS                             |       |

| B.1        | 11/40 FRONT END DIAGNOSTICS                      | R_3   |

| B.2        | FLOPPY BOOT OF KLDCP                             | R-16  |

| B.3        | BB. CMD                                          |       |

| B.4        | DGMMA                                            |       |

| B.5        | DIAGNOSTIC BOOT                                  |       |

| B.6        | DDMME                                            |       |

| B.7        | DDMMD                                            |       |

| B.8        | DFRHD                                            |       |

| B.9        | DFRPK                                            |       |

| B.10       | DDRPI (FORMAT BEFORE ACCEPT)                     |       |

| B.11       | DFTUE                                            |       |

| B.12       | DFSXA                                            | B-46  |

| B.13       | KLDCP BOOT VIA SW REG                            | B-49  |

| B.14       | MONITOR LOAD SAMPLE                              | B-50  |

| APPENDIX C | HARDWARE ACCEPTANCE TESTS                        |       |

| APPENDIX D | DECSYSTEM-20 INSTALLATION REPORT                 |       |

|            | FIGURES                                          |       |

| Figure No. | Title                                            | Page  |

| 3-1        | Unpacking and Inspection Flowchart               | 3-2   |

## FIGURES (Cont)

| Figure No. | Title                                                              | Page  |

|------------|--------------------------------------------------------------------|-------|

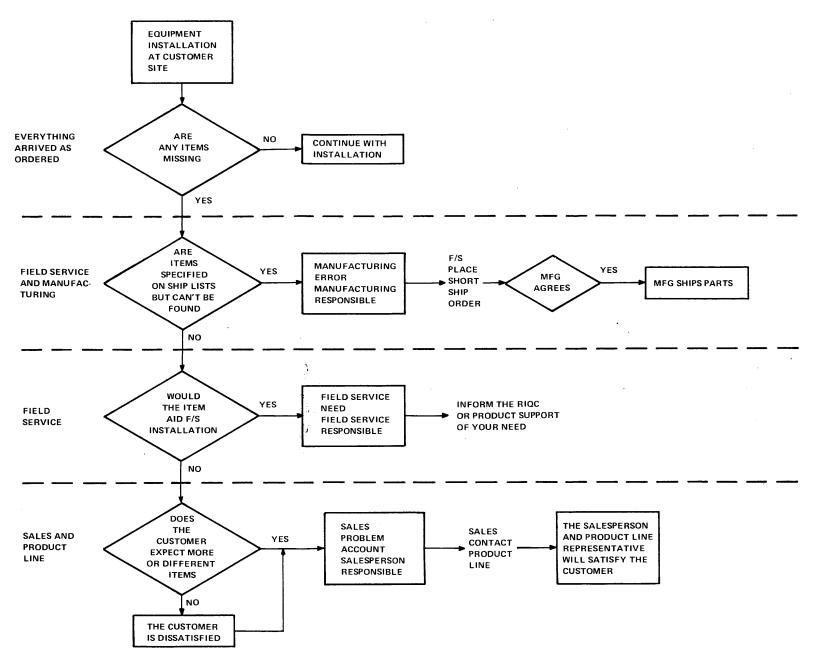

| 3-2        | Installation Short Shipment Procedures - Overview                  | 3-8   |

| 3-3        | Detailed Short Shipment Flowchart                                  | 3-9   |

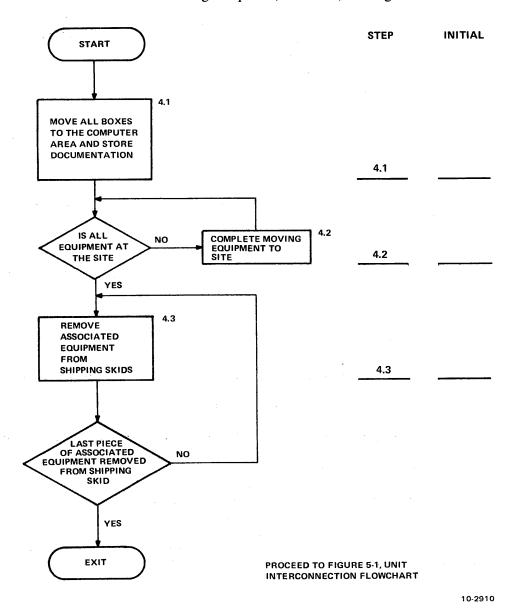

| 4-1        | Unit Placement Flowchart                                           |       |

| 4-2        | Unit Movement                                                      |       |

| 5-1        | Unit Interconnection Flowchart                                     |       |

| 5-2        | I/O Processor Cabinet (Rear View) - Cover and U.L. Shields Showing |       |

|            | Power Cable, Massbus, and Ground Cables                            | 5-5   |

| 5-3        | CPU Cabinet (Rear View) - Support Shield and U.L. Shields          | 5-6   |

| 5-4        | I/O Processor Cabinet (Front View) – Cover and U.L. Shields        | 5-7   |

| 5-5        | Arm Stabilizer Detail                                              | 5-7   |

| 5-6        | Leveling Foot Detail                                               | 5-8   |

| 5-7        | Exterior Assembly and Leveling Detail                              | 5-8   |

| 5-8        | Central Processor KL10-C Connections                               | 5-9   |

| 5-9        | Signal Interconnections (KL10-C)                                   | 5-10  |

| 7-1        | System Checkout Flowchart                                          | 7-1   |

| 7-2        | Sense Voltage Potentiometer Locations                              | 7-9   |

| 7-3        | Voltage Sense LEDs                                                 | 7-10  |

| 8-1        | Diagnostic Checkout Flowchart                                      | 8-1   |

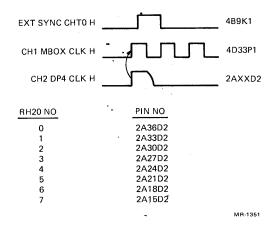

| 8-2        | MA20/MB20 Timing Diagram                                           |       |

| 8-3        | RH20 Deskew Timing Diagram                                         |       |

| 10-1       | MA20 Module Utilization                                            |       |

| 10-2       | MB20 Module Utilization                                            |       |

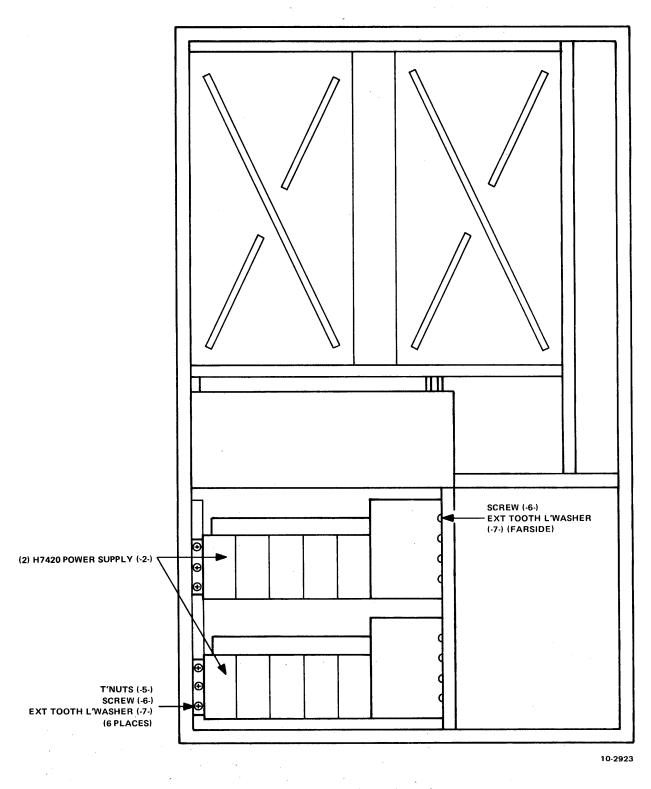

| 10-3       | I/O Processor Cabinet (Rear View – Doors Removed)                  | 10-8  |

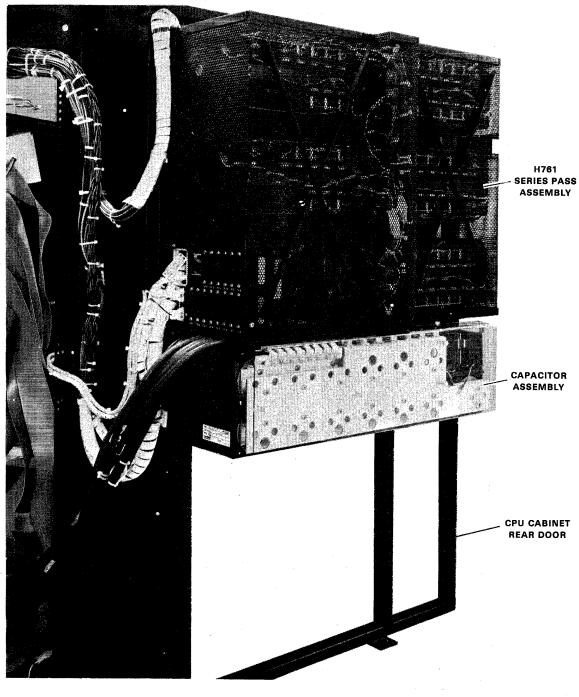

| 10-4       | CPU Cabinet (Inner Door)                                           | 10-9  |

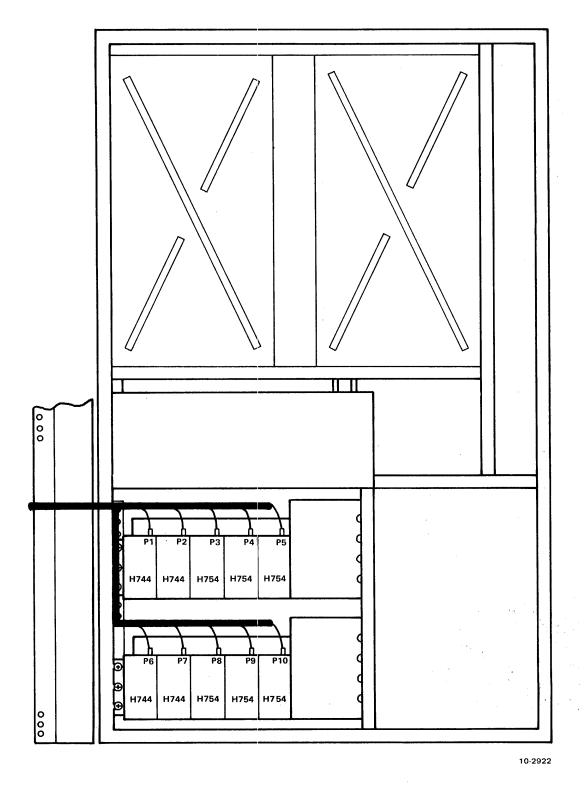

| 10-5       | DC Power Supplies and Regulators (I/O Processor Cabinet)           | 10-10 |

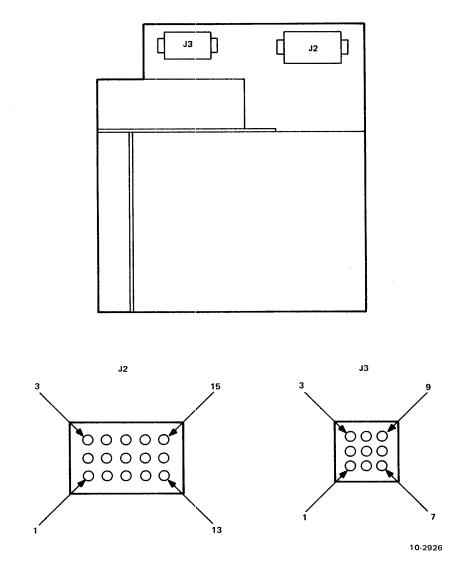

| 10-6       | Connector J2 and J3, Pin Identification                            | 10-12 |

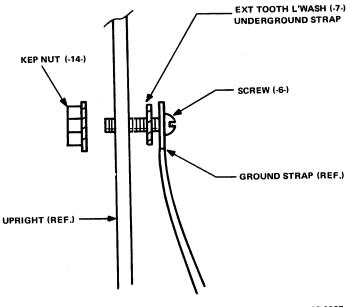

| 10-7       | Ground Strap Installation                                          |       |

| 10-8       | Memory Controller Jumper Installation                              |       |

| 10-9       | KL10-PV Assembly                                                   |       |

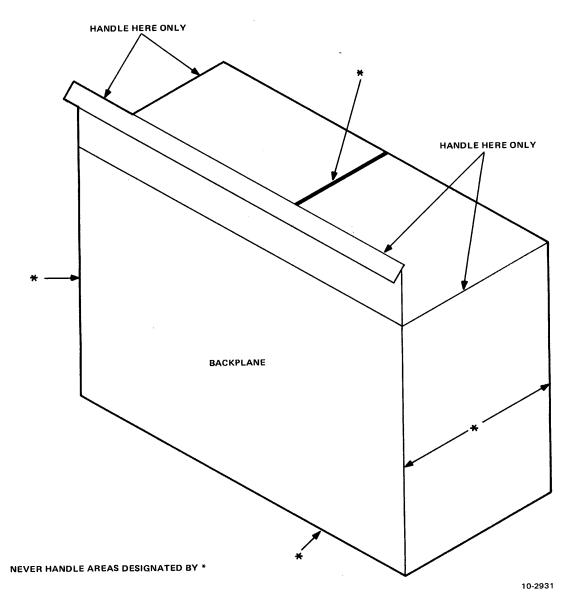

| 10-10      | Handling of CPU Assembly                                           |       |

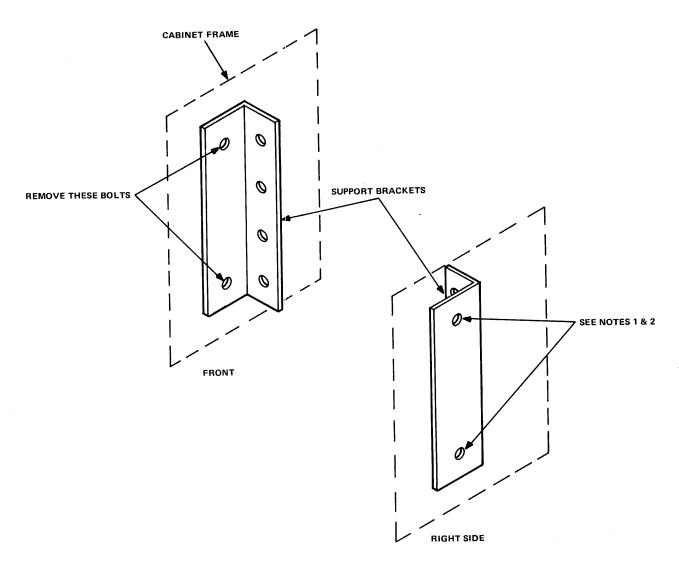

| 10-10      | Support Bracket Bolts                                              |       |

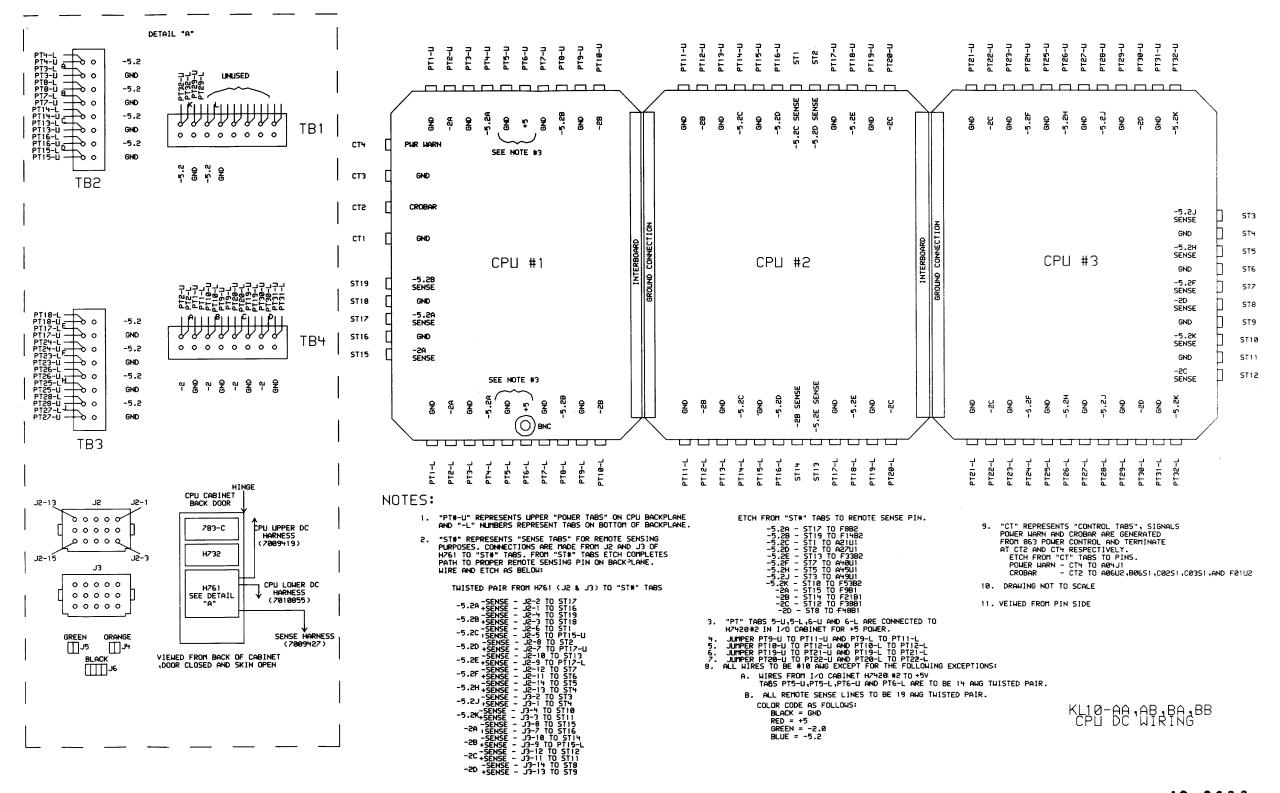

| 10-11      | KL10-PV CPU dc Wiring (Pin Side View)                              |       |

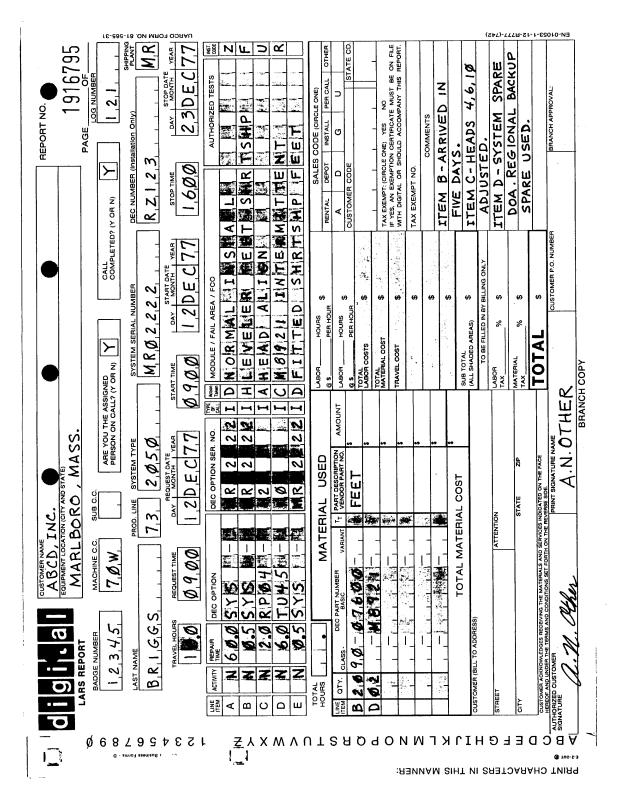

| 11-1       | Sample LARS Report Form                                            |       |

| 11-2       | LCG Installation Warranty Costs Summary Form (Sample Only)         | 11-5  |

|            | Ded instanction warranty costs building from (bumple omy)          |       |

|            | TABLES                                                             |       |

| Table No.  | Title                                                              | Page  |

| 1-1        | Related Documents                                                  | 1-2   |

| 5-1        | Parts Required to Assemble CPU Cabinets                            |       |

| 8-1        | Equipment for Diagnostic Checkout                                  |       |

| 10-1       | MA20/MB20 Add-On Parts List                                        |       |

| 10-2       | DDMMD: Right-Hand Switch Settings                                  |       |

|            |                                                                    |       |

#### CHAPTER 1 INTRODUCTION

The installation procedures contained in this manual provide for system checkout and acceptance of the DECSYSTEM-20. Adherence to these procedures ensures that both the system and the configuration conform to design specifications. Where applicable, flow diagrams complement specific procedures. Table 1-1 is a list of related documents.

Personnel involvement, scheduling, customer data, prerequisites and assumptions, a day-to-day installation plan, and spare parts checkout are contained in Chapter 2.

Unpacking and inspection procedures, Chapter 3, are intended to ensure that the proper system is received at the customer site, and all equipment is in good physical condition.

Chapter 4 contains unit placement information dealing with the transportation of equipment from loading dock to site location, and the procedures for deskidding.

Unit interconnection procedures in Chapter 5 provide installation and interconnection information for the DECSYSTEM-20. Included are system positioning and grounding, cable identification, and sequence of installation and routing. These procedures are designed to eliminate failures due to improper ac wiring, shorted power cables, etc.

The system integration procedure described in Chapter 6 is designed to ensure that all component parts of the DECSYSTEM-20 are connected properly.

Chapter 7 contains power checkout procedures required to verify that the power system is functioning properly.

Total system operation is checked via the standard diagnostic checkout procedures described in Chapter 8. Appendix B contains sample diagnostic printouts.

Standard field service hardware acceptance procedures are contained in Chapter 9 and Appendix C.

Chapter 10 describes system add-on and adjustment procedures, including those for cabling, cache upgrade, model B upgrade, and MB20 installation.

Reporting procedures such as LARS forms, installation reports, and daily logs are explained in Chapter 11.

Table 1-1 Related Documents

| Document No.  | Title                                                   |

|---------------|---------------------------------------------------------|

| EK-10/20-HR*† | Hardware Reference Manual                               |

| EK-20XX-PD*   | DECSYSTEM-20 Physical Description                       |

| EK-45/03-MM*  | TU45/TM03 Maintenance Manual                            |

| EK-BUS-ID*†   | DECSYSTEM-20 Bus System Interface Description           |

| EK-CD11-TM*   | CD20 Maintenance Manual                                 |

| EK-DATA-ID*   | DECSYSTEM-20 Data Channel Interface Description         |

| EK-DEC20-SD*  | DECSYSTEM-20 System Description                         |

| EK-DEC20-SP†  | DECSYSTEM-20 Site Preparation Guide                     |

| EK-DIA20-UD*  | DIA20 Unit Description                                  |

| EK-0DN2X-TM*  | DN2X-DNHXX Technical Manual                             |

| EK-DTE20-UD*† | DTE20 Unit Description                                  |

| EK-EBOX-UD*†  | EBox Unit Description                                   |

| EK-FE-ID*     | DECSYSTEM-20 Front End Channel Interface Description    |

| EK-KL10-HB†   | KL10 Maintenance Handbook                               |

| EK-KL10-TD*   | Introduction to KL10-Based System Technical Description |

| EK-KL10C-BD*  | KL10-C Field Maintenance Print Set Supplement           |

| EK-KL10C-IP*  | KL10-C Illustrated Parts Breakdown                      |

| EK-KLINI-UG*† | KLINIK User's Guide                                     |

| EK-LP20-MM*   | LP20 Maintenance Manual                                 |

| EK-MA020-UD*  | MA20 Unit Description                                   |

| EK-MB020-UD*† | MB20 Unit Description                                   |

| EK-MBOX-UD*†  | EBox Unit Description                                   |

| EK-METER-UD*  | Meter Board Unit Description                            |

| EK-PWR20-SD*  | DECSYSTEM-20 Power System Description                   |

| EK-RH20-UD*†  | RH20 Unit Description                                   |

| EK-TU45A-MM*  | TU45A/TM02 Maintenance Manual                           |

| EK-DEC20-LK†  | DECSYSTEM-20 Layout Kit                                 |

|               |                                                         |

<sup>\*</sup>Available on microfiche. For information concerning Microfiche Libraries, contact:

Digital Equipment Corporation Micropublishing Group PK3-2/T12 Maynard, Massachusetts 01754

Digital Equipment Corporation 444 Whitney Street Northboro, Massachusetts 01532

Attention: Printing and Circulation Services (NR2/M15)

Customer Service Section

<sup>†</sup>Available in hard copy. Hard copy reference documents may be ordered from:

# CHAPTER 2 DECSYSTEM-20 INSTALLATION PLAN

#### 2.1 INTRODUCTION

A critical factor in the predelivery phase is to develop an installation plan agreeable to all parties concerned. This chapter outlines personnel involvement, scheduling, customer data, prerequisites and assumptions, and a day-by-day hardware installation plan. An example of an installation planning sheet is shown in Appendix A.

#### 2.2 PERSONNEL

The DIGITAL personnel involved in the complete installation and acceptance plan are listed below and should be consulted before the customer receives the plan.

- 1. Account sales representative

- 2. Software representative

- 3. Field service account supervisor/manager

- 4. Field service account representative

- 5. Field service district support representative

- 6. Field service regional support (support engineer or installation specialist)

#### 2.3 SCHEDULING

The appropriate time to generate the final installation plan is approximately 30 days prior to delivery. This is close enough to installation time that people/resource commitments can be made with little chance of circumstances changing.

#### 2.4 PREREQUISITES AND ASSUMPTIONS

- 1. Environment: Stable and Clean

- a. Power: 120/208/240/380 V + 6%, -13%;  $50/60 \text{ Hz} \pm 1 \text{ Hz}$

- b. Temperature: 18° to 24° C (65° to 75° F) Rate of change 2° F/hr

- c. Humidity: 40 to 60 percent. Rate of change 2 percent/hr

- 2. System layout determined

- 3. Preinstallation site survey completed

- 4. System cables ordered

- 5. KLINIK modem installed (NORAM)

- 6. Installation team (2 hardware installers)

- 7. Work period (8 hours per day)

#### 8. System Contents

- a. Disk drive (1)

- b. Tape drive (1)

- c. Line printer (1)

- d. Card reader (1)

Add three (3) hours to total installation period per each additional unit.

#### 2.5 SYSTEM INSTALLATION AND CHECKOUT

- 1. Day 1: Preliminary

- a. Unpacking

- b. Inventory

- c. Quality control inspection of interior and exterior

- 2. Day 2: Cabinet assembly

- a. Cabinet positioning

- b. Cabinets bolted together

- c. Preliminary power checks

- d. Cable installation

- 3. Day 3: Power checkout

- a. Prepower checks

- b. Power-on checks (adjustments if necessary)

- 4. Day 4: PDP-11 front end checkout

- a. PDP-11 CPU and memory diagnostics

- b. PDP-11 communication diagnostic

- c. Hard copy diagnostics

- d. KLINIK link

- e. SY2040 system exerciser (12 hours or overnight)

- 5. Day 5: Unit checkout

- a. Memory deskew check

- b. KL10 CPU and memory diagnostics

- c. RH20 deskew

- d. RH20 channel loopback diagnostics

- e. DFKDA (12 hours or overnight)

- 6. Day 6: Disk and tape drive checkout

- a. Run appropriate diagnostics

- b. Alignment checks

- c. Reliability checks (one each hour)

- d. DFSXA (12 hours or overnight)

#### 7. Day 7:

- a. Monitor from KLAD-20 pack

- b. Acceptance script

- 8. Day 8: Reliability checks

- a. System reliability via SYSERR

- b. Software installation

- c. Initiate acceptance

#### 2.6 SYSTEM SPARES

For systems which are geographically remote or isolated from repair/replacement facilities, a spare parts checkout program should be considered prior to hardware acceptance. A quick go/no go, dead-on-arrival check extends installation time approximately one day. Following checkout, it is advisable to remove all spare modules from the system and to restore the originals prior to hardware acceptance.

When a spare parts checkout program is to be performed, care should be taken to tag all modules to be tested or removed. The sequence of insertion should be planned prior to starting the test. An appropriate time to cycle spares is after all diagnostic checkout procedures have been completed; i.e., following day 7 of the day-by-day installation plan (Paragraph 2.5).

A suitable sequence of diagnostics should be run after each module/module batch insertion. The particular sequence will depend on which part of the system the spares are being checked in.

# CHAPTER 3 UNPACKING AND INSPECTION

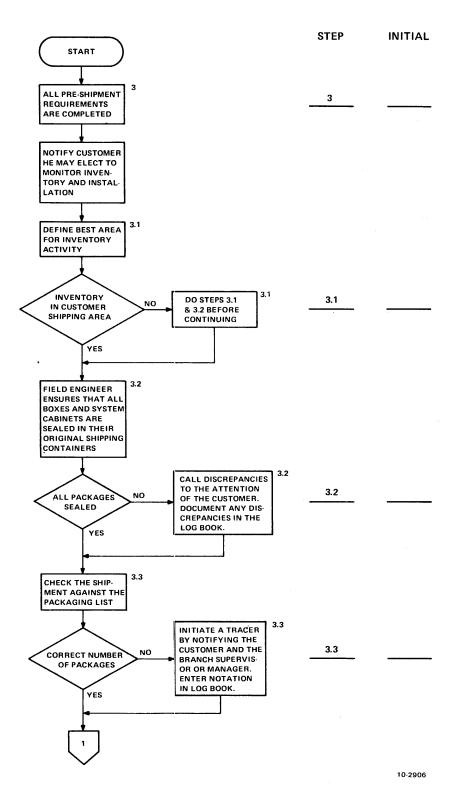

#### 3.1 SHIPPING AREA PROCEDURES (Refer to Figure 3-1.)

Because of dock or shipping area procedures and/or ease of performing inventory, the shipment may be moved from the customer's shipping area to the computer area. If so, follow the procedures in Paragraphs 4.1 and 4.2 at this time.

#### 3.2 SEALED CONTAINERS

Ensure that all boxes are sealed and that system cabinets and free-standing peripherals are in unopened shipping containers. If anything is opened, call it to the attention of the customer and document it on the installation report or field service report.

#### 3.3 PACKING LIST

Check the shipment against the packing list to ensure that the correct number of packages has been received. If an incorrect number of packages has been delivered notify the customer and the branch service manager or the branch supervisor. The customer should check with the carrier to locate the missing package(s) and have the missing package(s) delivered to the site. The branch service manager or branch supervisor may have to check with the traffic and shipping departments to locate missing packages if the carrier does not have them.

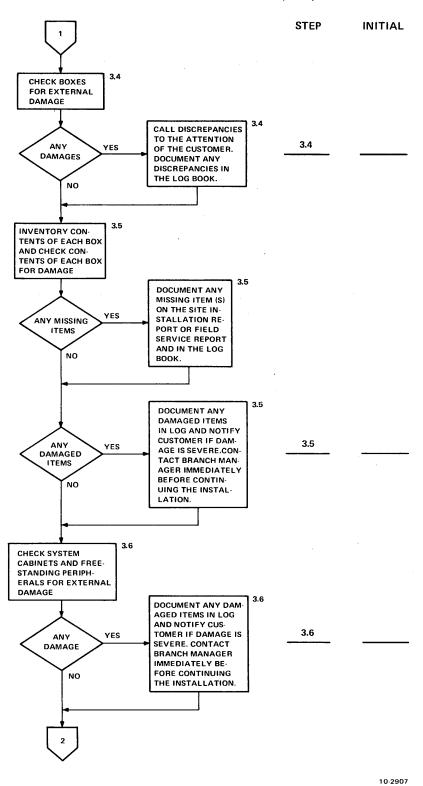

#### 3.4 SHIPPING DAMAGES

Check all boxes for external damages. Inspect for dents, protrusions, holes, smashed corners and pins, etc. If any boxes are damaged, notify the customer and document it on the installation report or field service report.

#### 3.5 OPENING SHIPPING CONTAINERS

Open each box, one at a time (starting with the READ ME FIRST box) and locate its packing slip. Inventory each box against the packing slip and note any missing items on the installation report or field service report. While performing inventory, inspect each item for damage. Note damaged items on the installation report or field service report and inform the customer immediately. If the damage is extensive, call the branch service manager immediately and report the damages.

#### 3.6 EXTERNAL DAMAGE INSPECTION

Check the system cabinets and free-standing peripherals for external damage to the shipping skid, covers, etc. Inspect the shipping containers for signs of stress or abusive handling. Remove the polyethylene covers and inspect external surfaces for scratches, holes, broken switches, broken panels, dented end panels, broken stabilizer feet, and any other damage or sign of abusive handling during shipment.

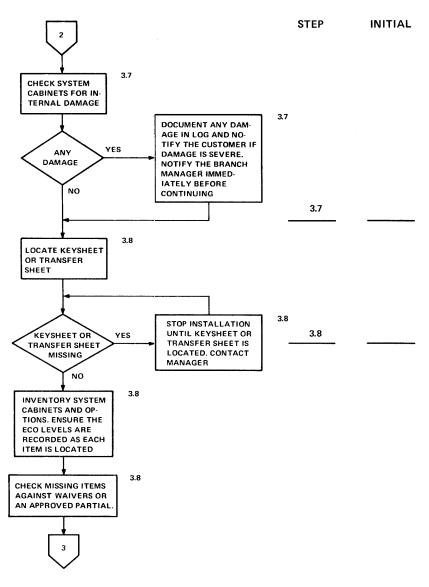

#### 3.7 INTERNAL DAMAGE INSPECTION

Inspect each cabinet and free-standing peripheral for internal damage as follows.

1. Remove the tape or plastic shipping pins from the rear access door(s) of the cabinet(s). Open the rear door(s) of the cabinet(s) and ensure that each option is secure in the cabinet. Inspect the cabinet for cable damage (ac and dc cables), loose mounting rails, loose fans or blower motors, loose nuts and bolts, screws, loose module clips and module retaining bars, broken switches, lights, breakers, connectors on the power controllers and power supplies, broken cable connectors, console switches, etc.

#### UNPACKING AND INSPECTION FLOW

Figure 3-1 Unpacking and Inspection Flowchart (Sheet 1 of 4)

#### **UNPACKING AND INSPECTION FLOW (Cont.)**

Figure 3-1 Unpacking and Inspection Flowchart (Sheet 2 of 4)

#### **UNPACKING AND INSPECTION FLOW (Cont)**

10-2908

Figure 3-1 Unpacking and Inspection Flowchart (Sheet 3 of 4)

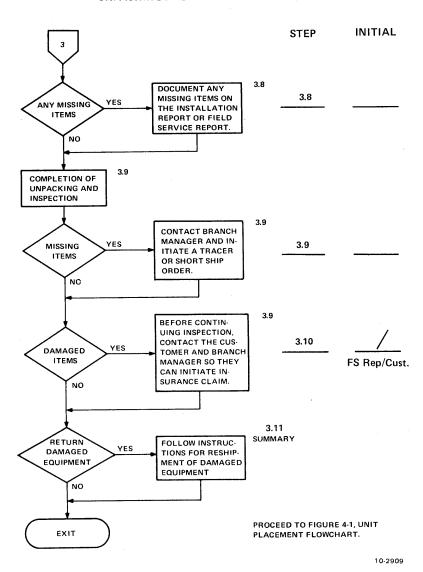

#### **UNPACKING AND INSPECTION FLOW (Cont)**

Figure 3-1 Unpacking and Inspection Flowchart (Sheet 4 of 4)

- 2. Remove the shipping retainer bolts of each expander chassis, or peripheral on slides, and inspect the internals of each box and peripheral for damage such as bent pins, and loose or broken modules, switches, lights, or backplanes, etc.

- 3. Document any damage and call it to the attention of the customer. If the damage is extensive, report the damage to the branch service manager immediately. DIGITAL is not responsible for shipping damage on systems that are FOB from the manufacturing facility. If reshipping equipment back to DIGITAL is required, follow the instructions in Paragraphs 3.10 and 3.11.

#### 3.8 INVENTORY

Inventory each system cabinet and free-standing peripheral to ensure that it contains the items identified on the keysheet or transfer sheet. Also, check the ECO REV level and serial numbers against the keysheet or ECO status sheets. Document any missing items, wrong serial-numbered item, or incorrect revision level item on the installation report or field service report. Ensure that the missing item is not covered by a waiver or an approved partial ship. Also, update the keysheet if ECO status does not appear on it.

#### NOTE

If the keysheet is missing, stop the installation and call the branch service manager to locate the keysheet or transfer sheet.

Documentation is provided in the customer envelope to allow the customer and the field service person to answer the following inventory questions.

1. Have all the cartons and boxes been received?

Using the shipper's waybill, the number of containers should be counted to ensure that none were lost in shipment. If any are missing, the shipper should institute a trace or insurance claim at the customer's request.

2. Are all of the options which the customer ordered present?

Using the Actual Cost Jobs Closes or Transfers sheet, the system configuration should be inventoried for correct content and quantities of options. This form indicates what was ordered from the manufacturing group.

3. Are all the accessories which should accompany the options and system present?

Using the accessory shipping lists, count and check as received every item contained in the boxes.

#### NOTE

Check the customer's envelope for waiver forms which indicate that items have been backordered and will be shipped separately. Do not order waivered or partialed items as short shipped.

If all items and parts have been received, inform the customer and continue with the installation following the installation and acceptance procedures (Paragraph 3.10).

#### 3.9 MISSING PARTS PROCEDURES

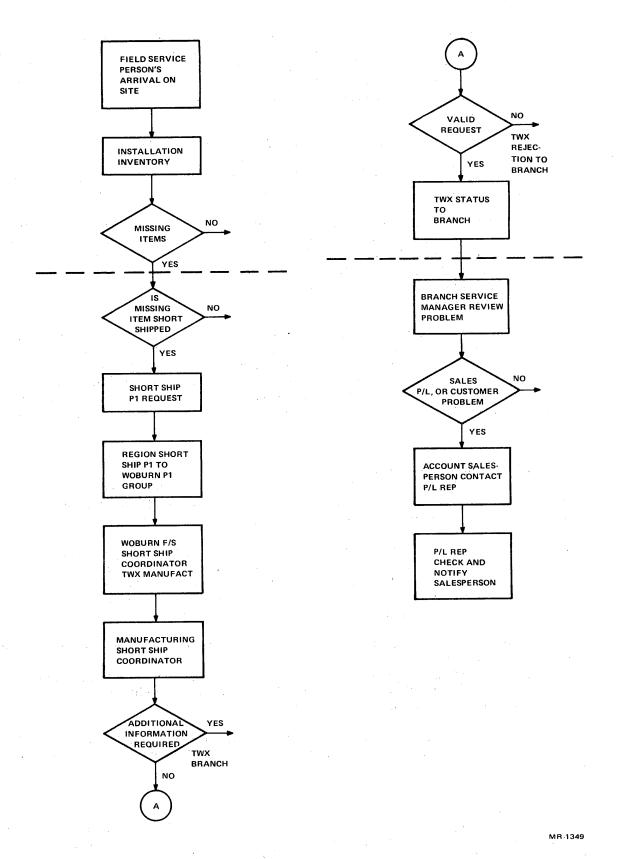

This paragraph defines an order short shipment, and the procedures for processing a short shipment P1 request through Field Service Logistics. It also outlines the procedures to follow when a missing item other than a short shipment is encountered, with the responsibilities identified for each organization. An overview of a short shipment is presented in Figure 3-2 and a detailed flowchart in Figure 3-3.

A short shipment is an item or items identified on the shipping document as required to ship with the order, but which inventory shows to be missing from the shipment. Paragraph 3.9.1 describes the procedures to follow in case of short shipment.

If a required item is missing and is not listed on one of the shipping documents as having been shipped or as required to ship, proceed to Paragraph 3.9.2.

#### NOTE

If the customer is performing the installation and finds material missing, then the customer should directly contact an account salesperson with the list of missing parts.

#### 3.9.1 Short Shipment Procedure

If an item is listed on one of the shipping documents as required to ship but it cannot be found when the installation inventory is performed, it is short shipped. Contact the branch logistics administrator and provide the following information.

DEC No.

Product Line

System Type

System Serial No.

Customer Name

Part No.

Part Description

Quantity

The branch logistics administrator will then assign an SBA number to the request and TWX it to the regional logistics center with the following additional information.

The branch office contact name and location The SBA No. Branch DECNET code

#### NOTE

When the materials requested are low cost and readily available in the branch or regional stockroom, they should be used and the short ship P1 request should be filled in at that point. The materials used should then be charged to the installation activity and product line. The intent is to ensure that the customer will be serviced efficiently.

The regional logistics center should check stock upon receipt of the short ship P1 request as noted above. If parts cannot be released due to cost or availability, retransmit the TWX to the Woburn P1 group immediately.

MR-1348

Figure 3-2 Installation Short Shipment Procedures - Overview

Figure 3-3 Detailed Short Shipment Flowchart

The Woburn P1 group will log the short ship request, and TWX directly to the responsible manufacturing short ship coordinator as listed by manufacturing within two hours of receipt. Each manufacturing group in each plant has a designated short ship coordinator in its facility who will receive the short ship request from Woburn and will verify the request. The responsibilities of the field service short ship coordinator, from this point, will be to monitor and log the status of the request as received from manufacturing until the SBA has been closed.

If the manufacturing short ship coordinator needs additional information, TWX questions should be sent directly to the requesting branch, with a copy going to the field service coordinator in Woburn for logging. A response from the branch should go directly to the individual requesting the information in manufacturing within 24 hours. When the branch responds, the request will resume processing.

The manufacturing short ship coordinator will check the request against the manufacturing records. If it is determined that the request is not valid a TWX will be sent to the branch rejecting the order with the reason why it is being rejected. A copy of the TWX will also be sent to the logistics coordinator who will then close the SBA. Appeals (when deemed necessary by the branch service manager) should go directly to the person sending the rejection TWX if there was miscommunication, or to the account salesperson for product line or customer resolution.

If the request is valid, the manufacturing short ship coordinator will TWX the P1 request status directly to the branch with a copy to the logistics coordinator, giving parts availability and an estimated time of arrival. If the parts will not be readily available within two days, the manufacturing coordinator will make the appropriate contact with the product line to authorize other priority acquisition procedures. In any case, status of the short ship P1 request should be sent by the manufacturing coordinator directly to the branch contact within 24 hours of the time manufacturing received the request.

#### 3.9.2 Non-Short-Shipment Missing Items

The installing field person should provide the branch service manager or branch supervisor with the details of the problem encountered. It should be made clear that this is not a short shipment but that it prevents continuation or completion of the installation or customer acceptance.

Having collected the complete information, the branch service manager should work with the customer's account salesperson to determine whether the item requested is a service aid or customer-required. A service aid is an item or tool that field service could use to improve the installation or checkout process. If the missing item is a service aid, information should be documented and sent to the proper support supervisor or the regional installation quality coordinator.

If the item is required by the customer, the account salesperson for the customer will gather all the relevant details and contact the appropriate product line representative. The product line representative will check the details and respond within 24 hours directly to the salesperson with the findings, the action to be taken and the time it will require. It is the salesperson's responsibility to notify the service manager and the customer of the information received.

The product line representative will arrange directly with manufacturing for all materials to be scheduled and shipped if it is determined to be the obligation of DIGITAL or in the best interest of the customer.

#### 3.10 COMPLETION

This completes the unpacking and inspection phase. Documentation of the entire system should be intact at this time. Notify the branch service manager or branch supervisor of any discrepancies noted during this phase. If no discrepancies exist, the customer should initial the last entry in Figure 3-1 signifying agreement with the inventory and inspection. Then continue to Chapter 4.

If discrepancies such as damage do exist, the branch supervisor may want the customer to initiate an insurance claim. For missing items, the branch service manager or branch supervisor should initiate a short ship request (Paragraph 3.9.1). All other problems should be discussed with the branch service manager or branch supervisor.

Customer claims on damaged equipment may be difficult to obtain if the equipment in question has been removed from the skid. Therefore, if any damage exists, the damaged equipment should not be deskidded or moved until authorized by the branch service manager. The customer is responsible for payment of the replacement or repair of damaged equipment. This arrangement will be discussed between the customer and the branch service manager. If damaged equipment is to be returned to Digital Equipment Corporation, the procedures in Paragraph 3.11 should be followed.

#### 3.11 RETURNING DAMAGED EQUIPMENT

Any piece of equipment to be shipped to Digital Equipment Corporation, as a return authorization from the field, must be transported on a proper skid or in the container in which it was shipped. If the equipment has been removed from a skid and the skid is not available, a replacement must be ordered from the Maynard traffic department or Stockroom 17.

Skids may also be manufactured in the locality of the customer site. All part numbers, specifications, and associated hardware are documented in print set D-PS-1210568-0-0.

Part of the customer's upgrade contract is that the customer is liable for all rigging and transportation charges; therefore, the customer can be billed for the skids and associated hardware.

A sample of various devices is listed below, along with the respective skid part numbers.

| Skid Part No. |  |

|---------------|--|

| 12-10568-2    |  |

| 9405651       |  |

| 12-10568-5    |  |

|               |  |

When a return authorization has been validated by DIGITAL and a skid has been procured, the procedure for loading a piece of equipment for reshipment to DIGITAL is as follows.

- 1. Remove the end panels and front and rear outer doors.

- 2. Raise the leveler feet.

- 3. Carefully place the equipment on skids.

- 4. Tighten the shipping bolts and lower the leveler feet. Also, lower any stabilizer feet levelers (if applicable).

- 5. Check to be sure that all shipping brackets for sliding chassis are in place and all module hold-down bars are secured.

- 6. Replace all end panels and doors, securing the doors with door holders.

- 7. Crate the cabinet appropriately; i.e., use a polyethylene bag, corrugated wraparound, etc.

#### CHAPTER 4 UNIT PLACEMENT

#### **4.1 EQUIPMENT MOVEMENT** (See Figure 4-1.)

Move all boxes to the computer area. If inventory is complete and Figure 3-1 is initialed by the DIGITAL representative and the customer, properly store the documentation (e.g., prints, manuals, diagnostics, write-ups, etc.) in the storage facility – preferably a cabinet with shelves. (A storage cabinet is usually supplied by the local field service branch.) This facilitates a smoother and more organized installation and eliminates searching for prints, manuals, or diagnostics in the various boxes.

Figure 4-1 Unit Placement Flowchart

#### **4.2 KL10-C** (**2040**) **CABINET HANDLING** (Figure 4-2)

Obtain the site layout sheet from the customer. Also, obtain the configuration sheet; some part lists include it in the shipping documentation. Move the system cabinets to the computer area.

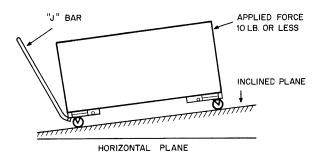

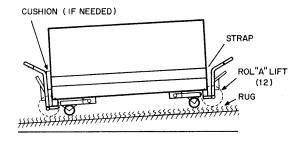

#### A. Movement on Smooth Inclined Plane

B. Movement on Rough Surface

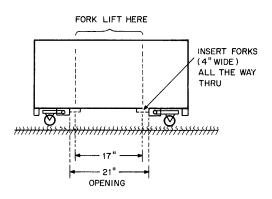

C. Fork-Lifting of Cabinet

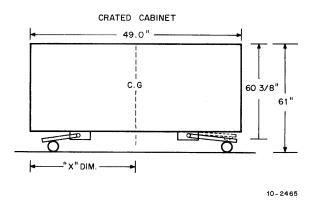

D. Dimensions of Crated Cabinet

Figure 4-2 Unit Movement

The following procedures should be followed for handling the double-width Hi Boy cabinets.

- 1. At least two workers are required to handle each cabinet.

- 2. When cabinets are to be pushed over steps (steel ramps over steps), riggers may be hired.

- 3. Cabinets are to be handled one at a time.

- 4. While loading or unloading cabinets on a ramp, a "come-along" (a type of block and tackle) should be used to prevent loss of control over cabinet.

- 5. A "J" bar or a "come-along" should be used in these situations: when moving cabinets on a smooth inclined plane having a pitch greater than 1 inch per foot (such as in corridors, hallways, etc.); or where a cabinet is at rest on an incline plane of less than 1.4 inch per foot but an applied horizontal force of less than 10 lb could move or slide the cabinet in either direction. See Figure 4-2A.

- 6. When moving such cabinets over any kind of carpet or rough floor, a "roller lift" is recommended to prevent damage to flooring or equipment. See Figure 4-2B.

- 7. If the cabinet is to be pulled over steps, or gaps or crevices greater than 1/4 inch between buildings, partitions, etc., a flat steel plate or ramp should be used.

- 8. Fork-lifting the cabinet can be accomplished if forks are inserted as shown in Figure 4-2C.

#### 4.3 DESKIDDING ASSOCIATED EQUIPMENT

Carefully deskid all equipment associated with the DECSYSTEM-20.

#### 4.4 REOUIRED TOOLS

The tools required to deskid and install a DECSYSTEM-20 computer system are listed below.

1. Basic Tool Kit (7606864)

| DEC Part No. | Description                           |

|--------------|---------------------------------------|

| 29-13456     | Nut driver set                        |

| 29-13457     | Adjustable wrench                     |

| 29-13460     | Diagonal cutting pliers (95ELH-EREM)  |

| 29-13462     | Miniature needle nose (UTICAB5317)    |

| 29-13463     | Pliers, 6-1/2 inch                    |

| 29-12573     | Ratchet offset screwdriver            |

| 29-13466     | Utility knife (Xacto no. 51ST)        |

| 29-13467     | Wire strippers                        |

| 29-13468     | 4 inch $\times$ 5/16 inch screwdriver |

| 29-13470     | No. 0 Phillips screwdriver            |

| 29-13471     | Trimpot screwdriver                   |

| 29-13472     | No. 2 Phillips screwdriver            |

| 29-13474     | 6 inch round smooth cut file          |

| 29-10779     | 6 inch half-round smooth cut file     |

| 29-13515     | Thickness gauge set                   |

| 29-13451     | Solder pullit                         |

| 29-10780     | Penlight                              |

| 29-13461     | Needle-nose pliers                    |

| 29-12574     | Phillips stubby screwdriver           |

| 29-13459     | Allen wrench set                      |

| 29-12559     | Tweezers, no. 151392                  |

| 29-12575     | Valve spout oiler no. 990034          |

| 29-12567     | Service case                          |

#### 2. Additional Tools Required

| DEC Part No. | Description                      |

|--------------|----------------------------------|

| 29-12529     | Screw holder                     |

| 29-12577     | Miniature combination wrench set |

| 29-13452     | Soldering iron                   |

| 29-19333     | Soldering iron tip               |

| 29-13512     | Burnishing blade                 |

| 29-13513     | Unwrapping tool – 24 gauge       |

| 29-18387     | Unwrapping tool – 30 gauge       |

| 29-13450     | Handwrap tool – 24 gauge         |

| 29-18301 | Handwrap tool – 30 gauge                        |

|----------|-------------------------------------------------|

| 29-10246 | IC clips (2)                                    |

|          | Large adjustable wrench                         |

|          | Hammer                                          |

| 29-13455 | Crimping tool for Faston connectors             |

|          | Tightening tool for Faston connectors           |

|          | 1/4 inch drive ratchet and socket set and level |

#### 4.5 FINAL CHECKS

When the equipment is situated in the site location, perform the following procedures in the order listed.

- 1. Check the pins on the backplane, making sure none of the pins is bent or smashed.

- 2. Check all Faston type connectors, making sure they are all tight.

- 3. Check all modules and cables, making sure they are properly seated and in their correct slots.

- 4. Beginning with the topmost circuit breaker on the main power box, check to ensure that each power cable is correctly labeled, both on the cable and at the box.

- 5. Use a digital voltmeter (DVM) to ensure that all power phases are correct.

- 6. Ensure that all circuit breakers within the main power box are in the OFF position.

# CHAPTER 5 UNIT INTERCONNECTION

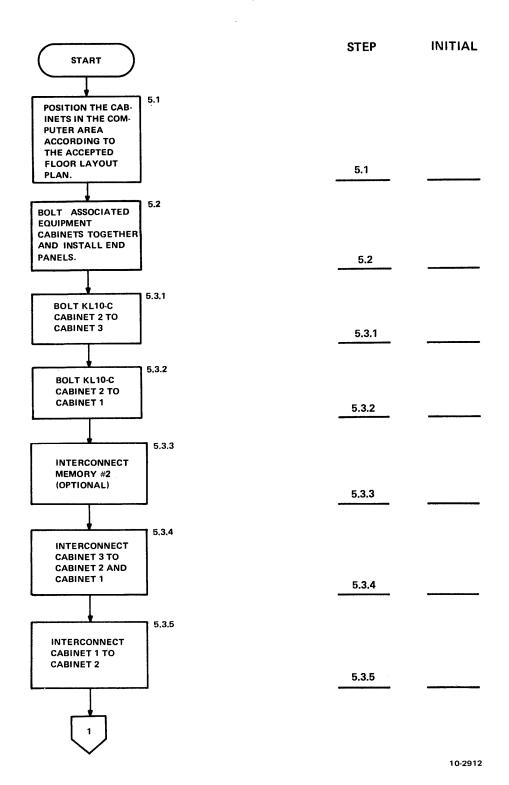

#### **5.1 EQUIPMENT POSITIONING** (Figure 5-1)

Starting with the KL10-C (2040) central processor and extending outward, position all the associated DECSYSTEM-20 equipment according to the accepted floor layout plan.

40.0

#### **5.2 BOLTING FRAMES**

Bolt all frames together (where applicable) and/or install end panels.

#### 5.3 KL10-C (2040) CABINET INSTALLATION AND INTERCONNECTION

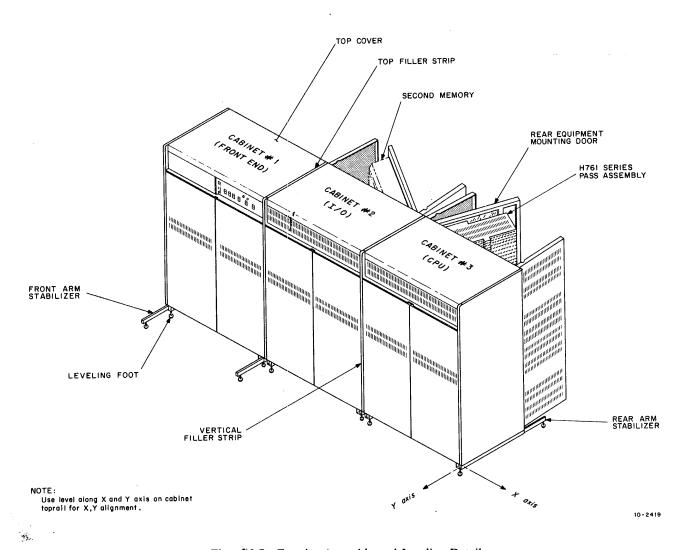

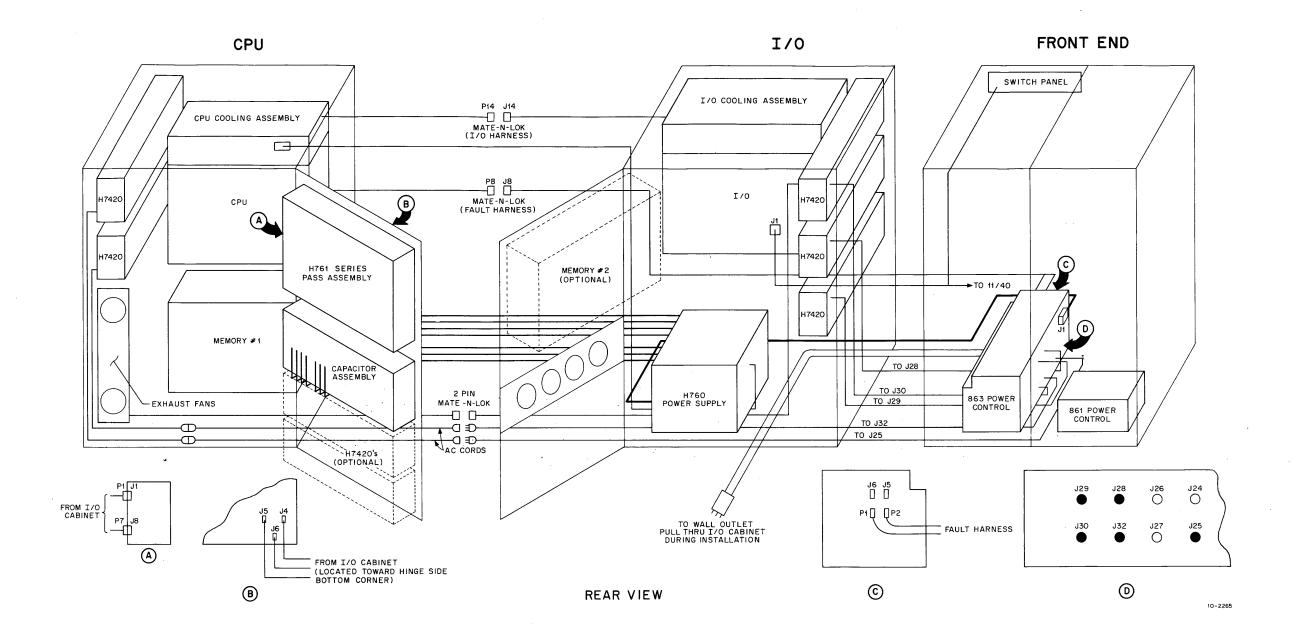

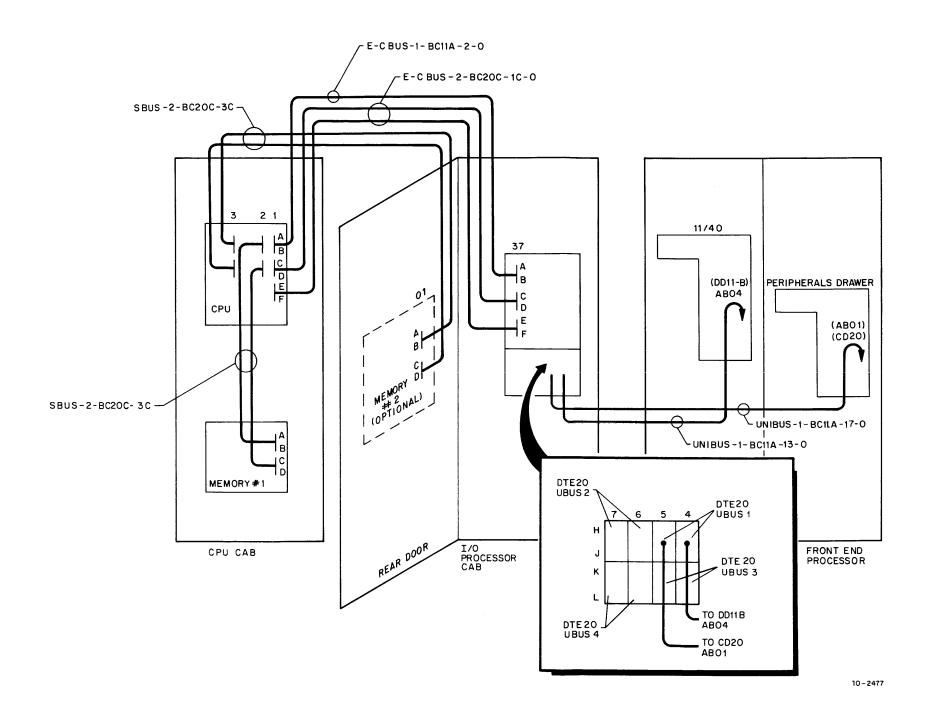

Paragraphs 5.3.1 through 5.3.5 list the procedures for interconnecting the KL10-C cabinets. See Figures 5-2 through 5-9. The cabinets are identified as follows.

Cabinet 1 - Front end

Cabinet 2 – I/O

Cabinet 3 - CPU

#### WARNING

Before beginning this set of instructions, ensure that the main power line cord is unplugged from the wall receptacle and no peripheral equipment is connected to the machine.

Table 5-1 lists the parts needed to assemble the three processor cabinets. These parts should be kept in a container and no parts should be discarded unless noted.

#### 5.3.1 Cabinet 2 – Cabinet 3 Assembly (Figures 5-2 – 5-4)

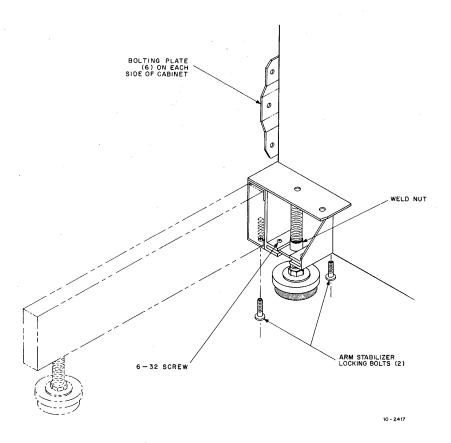

- 1. Place rear arm stabilizer on all cabinets (Figure 5-5).

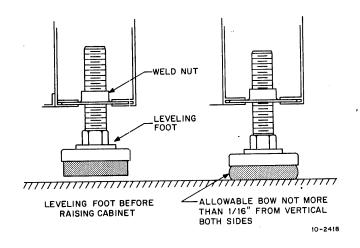

- 2. Place leveling feet under all cabinets and secure with screws (Figure 5-6).

- 3. Remove doors and air inlets, top covers, filler strips, and ground straps for ease of bolting cabinets together.

- 4. Place level on top rail of cabinet.

- 5. Level base of cabinet on x-y axis by adjusting leveling feet (Figure 5-7).

- 6. Bring CPU cabinet in contact with I/O right side as viewed from the front.

- 7. Raise CPU cabinet until lower bolting plate holes are in line with I/O cabinets by raising leveling feet (left front and rear as viewed front).

- 8. Bolt down the two lower bolting plates with lower plates of CPU cabinets.

- 9. Bolt middle and upper bolting plates.

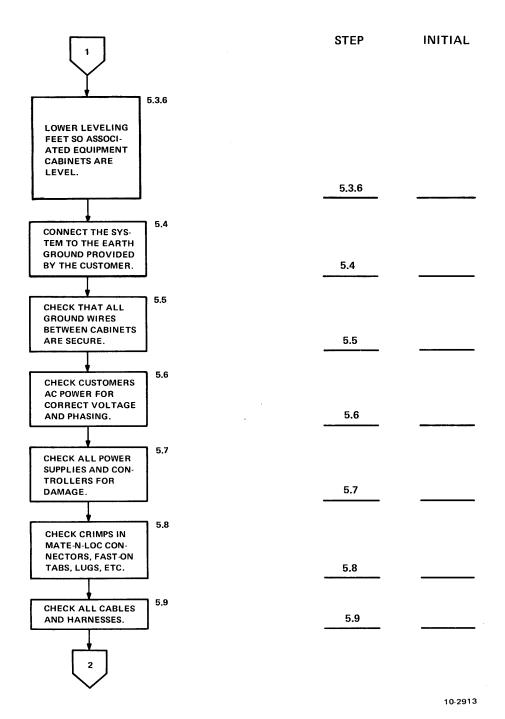

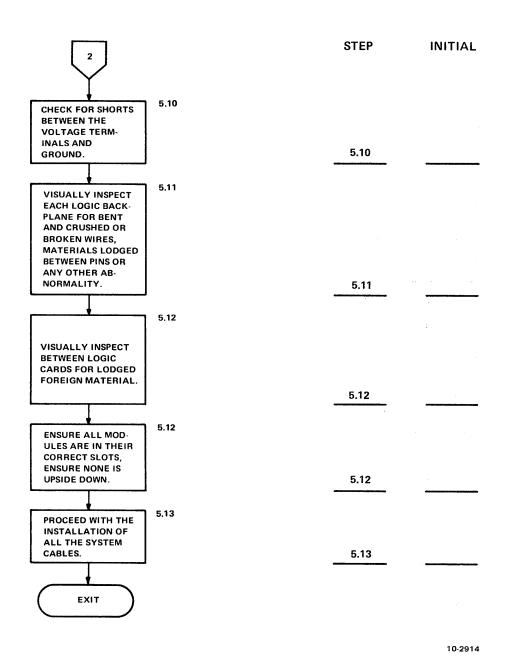

Figure 5-1 Unit Interconnection Flowchart (Sheet 1 of 3)

Figure 5-1 Unit Interconnection Flowchart (Sheet 2 of 3)

Figure 5-1 Unit Interconnection Flowchart (Sheet 3 of 3)

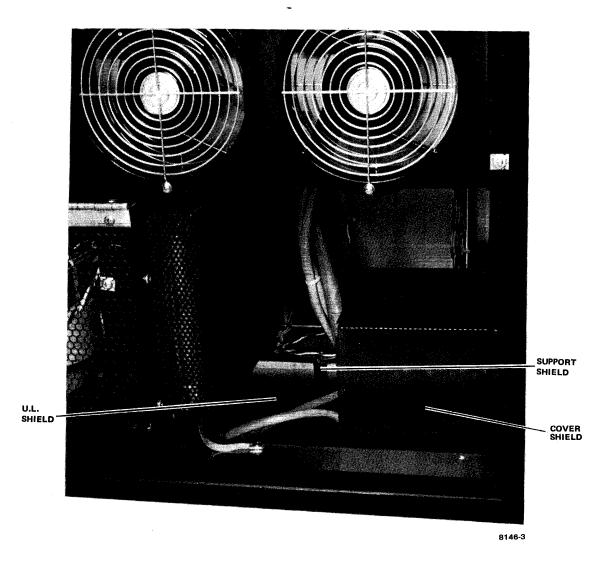

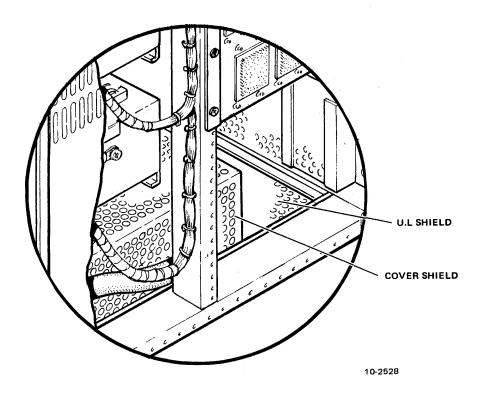

Figure 5-2 I/O Processor Cabinet (Rear View) – Cover and U.L. Shields Showing Power Cable, Massbus, and Ground Cables

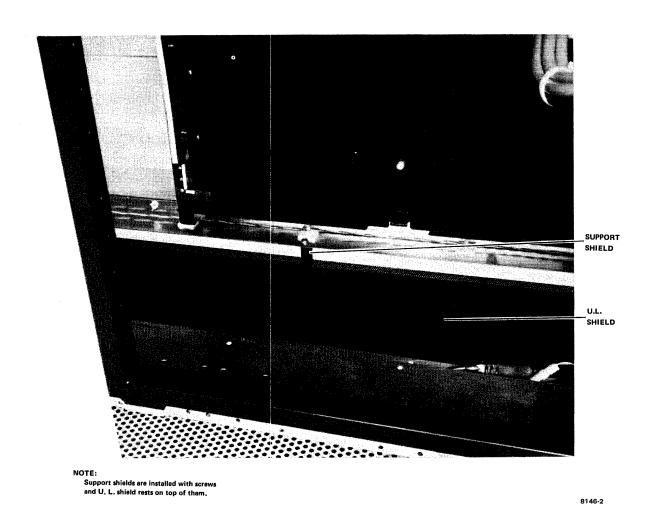

Figure 5-3 CPU Cabinet (Rear View) - Support Shield and U.L. Shields

5-6

Figure 5-4 I/O Processor Cabinet (Front View) - Cover and U.L. Shields

Figure 5-5 Arm Stabilizer Detail

Figure 5-6 Leveling Foot Detail

Figure 5-7 Exterior Assembly and Leveling Detail

Figure 5-8 Central Processor KL10-C Connections

Figure 5-9 Signal Interconnections (KL10-C)

Table 5-1 Parts Required to Assemble CPU Cabinets

| No. Needed | Part No.                                                       | Description                                                                                                                  |

|------------|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 4          | 70-11838                                                       | Filler bar assembly                                                                                                          |

| 2          | 74-14403                                                       | Top filler strip                                                                                                             |

| 1          | 70-12196                                                       | Shield weldment                                                                                                              |

| 3          | 74-15268                                                       | Support shield (Figures 5-2 - 5-4)                                                                                           |

| 5          | 74-15394                                                       | U.L. shield (Figures 5-2 - 5-4)                                                                                              |

| 1          | 74-15476                                                       | Cover shield (Figures 5-2 – 5-4)                                                                                             |

| 2          | Bolting package                                                | For Hi Boy cabinets                                                                                                          |

|            | (6) 9006241-9<br>(6) 9006724<br>(6) 9008203                    | No. 1/4-20 ±0.5 hex head screw No. 1/4 external-tooth lock washer No. 1/4-20 Kep nuts                                        |

| 2          | Hardware package                                               | For filler strips                                                                                                            |

|            | (20) 9006071-3<br>(20) 9007651                                 | No. 10-32 ±0.38 Phillips truss screw<br>No. 10 external-tooth lock washer                                                    |

| 1          | Hardware package                                               | For U.L. shields                                                                                                             |

|            | (4) 9006563<br>(6) 9006055-1<br>(6) 9009025<br>(6) 9006724     | No. 8-32 Kep nuts No. 1/4-20 ±0.38 Phillips pan head screw 0.281 ID ±0.873 OD flat washer No. 1/4 external-tooth lock washer |

| 2          | Hardware package                                               | Ground straps                                                                                                                |

|            | (1) 9008887<br>(2) 9006565<br>(2) 9006071-3<br>(4) 9007651     | 10 inch ground strap<br>No. 10-32 Kep nuts<br>No. 10-32 ±0.62 Phillips truss head<br>No. 10 external-tooth lock washer       |

| 6          | Hardware Package                                               | Leveling feet                                                                                                                |

|            | (12) 9007600<br>(12) 9008878<br>(24) 9008185<br>(24) 9006024-1 | Leveling feet Weld nuts Kep nuts Screws                                                                                      |

## 5.3.2 Cabinet 2 - Cabinet 1 Assembly

- 1. Repeat step 3 in Paragraph 5.3.1.

- 2. Place shield weldment in bottom of cabinet 2.

- 3. Slide main power cable from cabinet 1 through U.L. shield weldment on cabinet 2 (see Figure 5-2); at the same time wheel cabinet 1 close to cabinet 2.

- 4. Repeat steps 8, 9, 10, and 11 in Paragraph 5.3.1 for front-end cabinet (cabinet 1).

## 5.3.3 Memory 2 (Option) Cabling Interconnections (Figure 5-8)

- 1. Connect memory 2 harness to H7420 power supplies (2) on cabinet 3 rear door (Mate-N-Lok).

- 2. Tie wrap harness.

- 3. Connect pins 3 (white) and 7 (red) to Mate-N-Lok on both H7420 power supplies.

- 4. Connect memory 2 ac (H7420) cords on cabinet 2 from 863 power control to front-end cabinet (J24 and J26).

- 5. Tie wrap cords.

## 5.3.4 Cabinet 3 to Cabinet 2 and Cabinet 1 Cabling Connections (Figure 5-8)

- 1. Connect number 2 gauge cap wires at capacitor bank to their corresponding labels (5, 6, 7, 8, 9, 10, and 11). Torque to 132 in-lb.

- 2. Replace strain relief support plate (two screws only), cable routing bracket, and Dakota clamp cover at cabinet 2 3 interface.

- 3. Replace Lexan cover (cap box).

- 4. Remove U.L. Lexan shield of H761 on rear door of cabinet 3.

- 5. Attach Mate-N-Loks at H761 connections labeled P1 to J1 and P7 to J8, respectively.

- 6. Connect color-coded wires J4, J5, J6 to correspondingly color-coded terminals of H761 (Figure 5-8).

- 7. Tie wrap wires to cable harness.

- 8. Replace U.L. Lexan shield on H761.

- 9. Connect CPU blower ac plug (4-pin Mate-N-Lok at blower).

- 10. Connect BC20 and BC11 cables from CPU to memory 1, memory 2 (if present), and I/O.

- 11. Connect Mate-N-Lok P14 to J14.

- 12. Connect Mate-N-Lok P8 to J8.

- 13. Connect exhaust fans to 2-pin Mate-N-Lok located in bottom of CPU cabinet.

- 14. Connect ac cords for memory 1 H7420 power supplies.

## 5.3.5 Cabinet 1 – Cabinet 2 (Front End – I/O Cabling Interconnections)

- 1. Roll maintenance panel wires (R and B) and (W and B) from cabinet 2.

- 2. Connect maintenance panel wires (R and B) and (W and B) to DTE (J1 4-pin Mate-N-Lok).

- 3. Tie wrap wires to cabinet 2.

- 4. Roll H760 5-conductor extension cord at 863 power control (J1).

- 5. Connect to 863-J1.

- 6. Roll all H7420 power cords from cabinet 2 to 863 cabinet 1.

- 7. Connect all H7420 power cords to their respective 863 jacks (for phase balance) (Figure 5-8).

- 8. Tie wrap cords to cabinet 1 frame.

- 9. Unroll Unibus from cabinet 1 to cabinet 2.

- 10. Connect Unibus to respective DTE connectors as labeled (Figure 5-9).

- 11. Roll fault harness from cabinet 2 to cabinet 1.

- 12. Connect fault harness at cabinet 1, 863 power control Mate-N-Loks labeled P1 to J6 and P2 to J5.

- 13. Tie wrap harness onto cabinet 1.

## 5.3.6 Leveling Feet

Lower the leveling feet (see Figure 5-6). Ensure that all leveling feet are planted firmly on the floor and that the equipment is all kept level. Raise the I/O cabinet with the leveling feet until rubber grommets begin to bow out slightly (Figure 5-6).

## 5.3.7 Final KL10-C (2040) Central Processor Assembly

- 1. Replace cover shield of cabinet 2 with four 8-32 nuts (Figures 5-2 5-4).

- 2. Replace filler strips (6) for all three cabinets.

- 3. At this point, since all three cabinets are bolted together, there is no need to have the arm stabilizer extended. If traffic around the machine requires the removal of the arm stabilizer, unbolt rear arm stabilizers and slide them in. Arm stabilizers should never be discarded; they should remain on the site in the event there is a future need to break the machine apart.

- 4. Install U.L. shields and bracket in CPU cabinet (Figure 5-3).

- 5. Install U.L. shields and bracket in front end cabinet (Figure 5-3).

- 6. Remove PDP-11-type shipping brackets from front end cabinet.

- 7. Replace doors, air inlets, top covers, filler strips, and ground straps.

#### 5.4 SYSTEM GROUNDING

Refer to the system grounding scheme as laid out by the installation planner and connect the grounding accordingly.

#### NOTE

Planning of this ground should have been discussed with the customer during site preparation planning.

## 5.5 CHECKING GROUND WIRES

Check all ground wires that are connecting the system frames. Ensure that the ground lugs are making firm contact with the metal on the system cabinet frames (e.g., no paint between wire lugs and frames). All ground connections should have lock washers behind the ground strap lugs.

#### 5.6 CUSTOMER VOLTAGE CHECKS

Check the customer's ac power for proper voltage, proper phasing, correctly wired power receptacles, and to ensure that ac ground is connected to all ground pins in all power receptacles for this computer system. Use a DVM. Reference the DECSYSTEM-20 Site Preparation Guide individual option data sheets for ac requirements.

#### WARNING

It is very important that safety ground be obtained throughout the system to minimize the possibility of injury to personnel or damage to the equipment.

#### 5.7 COMPONENT CHECKS

Check each power supply and controller for damage, loose components, loose screws, or extra hardware that may be laying on or lodged into a component board. Check the fans for the supplies to ensure that cables and harnesses are clear of the fan blades and that the fans turn freely.

#### 5.8 FASTENER CHECKS

Check all the crimps that are in all Mate-N-Lok connectors, Faston tabs, lugs, etc., for solid connections. This can be accomplished by pulling on the wires. If a lug pulls out, reconnect it to its plug and/or jack. Also, ensure that all connectors are seated properly.

#### 5.9 CABLING CHECKS

Check all the cables and harnesses for crushed wires, cut wires, wires smashed together, etc. (especially under logic cabinet door hinges). If any exist, repair or replace the wire(s) or harness.

## 5.10 SHORT CIRCUIT CHECKS

Using a multimeter, check for short circuits between the voltage terminals and ground on all the power supplies.

#### NOTE

Usually resistance reading is low, approximately 5 ohms, depending on the load.

#### 5.11 BACKPLANE CHECKS

Visually inspect each logic backplane for bent pins, crushed or broken wires, foreign material lodged between pins, or any other abnormality.

## 5.12 VISUAL INSPECTION

Visually inspect between every module for any hardware (nuts, screws, washers, etc.) that may be lodged between them. Inspect the entire system including the free-standing peripheral devices. Ensure that all modules are in their correct slots and none are upside-down.

## 5.13 SYSTEM CABLES (Also refer to Chapter 7)

Refer to the detailed cabling diagram prepared before system delivery, and install the system cables in the order indicated, observing manufacturing cable tags (refer to Chapter 7).

#### NOTE

All cables should be run from point to point, keeping the following requirements in mind.

- 1. All cables (including ground cables) run under the flooring except RP04/06 cables, which run above floor between drives. Refer to the RP04/06 maintenance manual for further information.

- 2. All cables should be labeled on both ends, stating the device type and the slot numbers where they come from and go to.

- 3. Signal cables should not run parallel with power cables, but should cross them at a 90 degree angle.

- 4. Cables should not be drawn tight around cabinet corners or floor posts.

#### 5.14 CABLE INSTALLATION

Proceed as follows.

1. Install the power cables to all devices.

## **CAUTION**

Check to ensure that all circuit breakers in the main power box and internal to each device are in the OFF position. Also, ensure that all devices are in LOCAL until the system is fully checked out.

- 2. Connect all device cables (and terminators, if applicable).

- 3. Connect all the DIGITAL power control bus cables.

- 4. Recheck all power and system cabling and grounding before continuing.

- 5. Recheck to ensure that all shipping restraints have been removed.

# CHAPTER 6 SYSTEM INTEGRATION

#### 6.1 INTRODUCTION

At this point all internal cabling within the processor should be completed. The remainder of the installation consists of all peripheral devices and their associated interface and power cables.

All device interface cables will be routed into the CPU via a hole cut in a tile of the false floor, beneath the I/O cabinet. An exception is the modem cables which are routed through a hole in the false floor beneath the front end cabinet.

#### **NOTE**

All holes should be sealed following final cable placement.

## 6.2 RP04/06 DISK DRIVES

- 1. Refer to the ISS Service Manual and RP04 Disk Drive Installation Manual (EK-RP04-IN-001) for RP04 installation procedure, and to the Memorex 677-01/51 Technical Manual for RP06 drive installation procedure.

- 2. One 3-phase power source may supply up to two drives. If a third or fourth drive is to be used in the system, a separate supply source will be required. Ensure correct voltage settings in the drive.

- 3. The first drive (drive 0) is always dual-ported. The port switch on the control panel of the drive should be in the A/B position (except while running diagnostics). Additional drives are selected port A.

- 4. The Massbus cable from channel 0 should always be connected to port A; however, it can be connected to channel 1 during initial checkout.

- 5. The BC06S Massbus cable from the front end RH11 should be connected to port B. The plug connection at the front end is located below the 11/40 and to the right of the 863 power controller (as viewed from the front).

- 6. A Massbus terminator should be connected to the OUT slot for port B. If the system has one drive only, a Massbus terminator must be connected to the OUT slot of Port A. For additional drives continue the Massbus cabling and terminate port A of the last drive in the system. Check that W2 has been removed from the terminator (Enable MASSFAIL).

- 7. Check the drive number selection switches on the M7775 module in each DCL for correct setting (RP04). Set for 0 in RP06.

- 8. Remove red carriageway hold-down clip (RP04).

- 9. Remove the shipping hardware (RP06).

#### 6.3 TU45 MAGNETIC TAPE DRIVES

- 1. Refer to Pertec service manual for drive installation procedure.

- 2. Connect BC06S Massbus cable between channel 1 and the Massbus connector in the master TU45 drive (if more than one drive is on the system). This is the drive containing the TM02/3 controller. Connect Massbus terminator to the out slot of the Massbus connector. Check for W2 as in step 6 (Paragraph 6.2).

- 3. Ensure that the six resistor terminator chips on the M8921 are installed in the last drive on the system. Also check that other drives do not have the terminators installed.

- 4. With more than one drive the slave bus is connected between the MTAs in each TU45. These connections are as follows.

| MTA 1st TU45 |    | MTA 2nd TU45 |

|--------------|----|--------------|

| J6           | to | SB1          |

| Ј8           | to | SB2          |

| J10          | to | SB3          |

These cables have been twisted between output and input; i.e., rough side of the cable outermost from the Js and smooth side outermost into the SBs.

5. Connect single-phase power to each drive. Ensure drives are set for correct input voltage.

#### 6.4 LP20 LINE PRINTER

- 1. Refer to Data Products Service Manual for unit installation.

- 2. Connect interface cable from the line printer to the LP20 plate assembly connector located to the left of the 863 power controller (viewed from front).

- 3. Connect single-phase power. Ensure printer is set for correct voltage.

- 4. Remove the hammer bank shipping clip (located to the left of the bank) if it is on the LP05.

## 6.5 CARD READER

- 1. Refer to the appropriate documentation service manual for installation procedure.

- 2. Remove the two red painted shipping screws from the base of the reader (M200).

- 3. Connect interface cable from card reader to slot B02 of the CD20 controller in the peripheral expander box.

- 4. Connect single-phase power. Ensure reader is set for correct input voltage.

#### 6.6 LA36 CONSOLE DEVICE

- 1. Connect interface cable to 4-pin connector plug located to the right of the 863 power control.

- 2. Connect power lead to a single-phase power receptacle.

#### 6.7 DC20 COMMUNICATIONS

#### NOTE

# These cables can be connected after the diagnostic checkout for the DC20.

- 1. Connect the BC05D or BC03M cables to the H317B patch panel and dress the cables as per KL10C vol. I CPU assembly sheets 4, 11, and 12.

- 2. In many countries, fused barrier boxes are necessary for modem protection. Cables with this type of protection are normally obtained through CSS.

## 6.8 GROUNDING

Supplied with each system are several no. 4 gauge black ground cables. These cables are connected from earth lugs on the frames of peripheral devices back to the CPU frame. In general they should run parallel to the interface cables. The short (2.5 ft) no. 4 cables are used to connect adjacent devices such as multiple disk drives or multiple magnetic tape drives.

## 6.9 DN20 SUBSYSTEM

This is a complex subsystem and requires a separate section to cover its complete installation process. Refer to Chapter 2 of the DN2X Communications Subsystem Technical Manual (EK-0DN2X-TM-001) for system integration.

# CHAPTER 7 POWER CHECKOUT

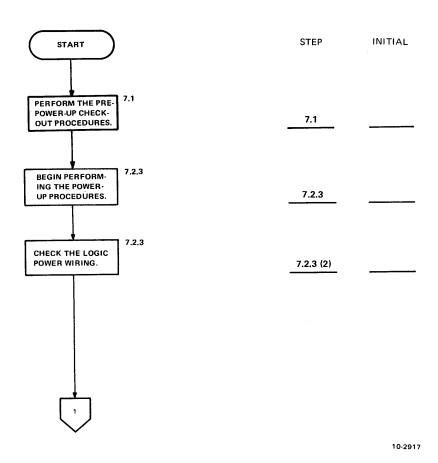

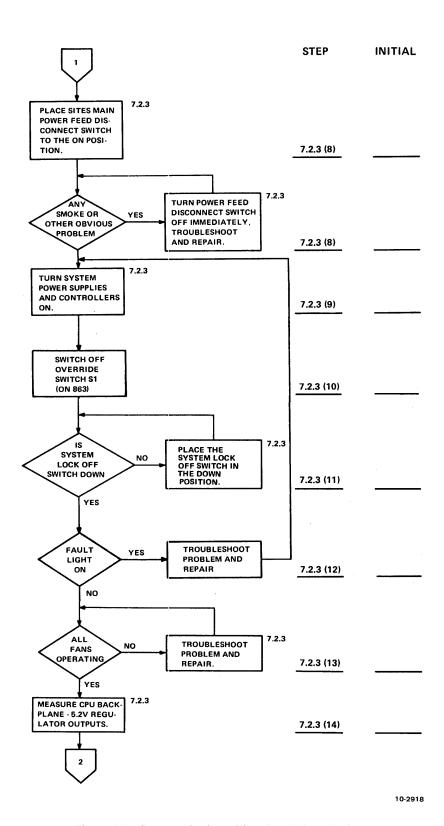

## 7.1 PREPOWER CHECKOUT PROCEDURES (Figure 7-1)

Perform the prepower-up procedures described in the following paragraphs.

## WARNING

The H760 power supply produces lethal current. Extreme caution should be observed whenever working with or near the power supply.

#### **NOTE**

Some emergency power systems are connected to fire alarm systems. If this is true, be sure the proper customer authorities are notified that power is being applied for the first time.

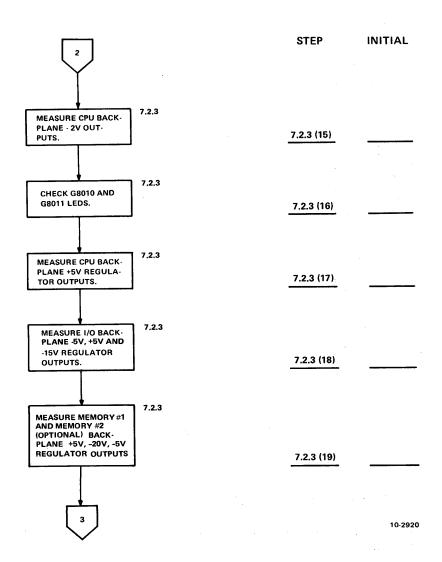

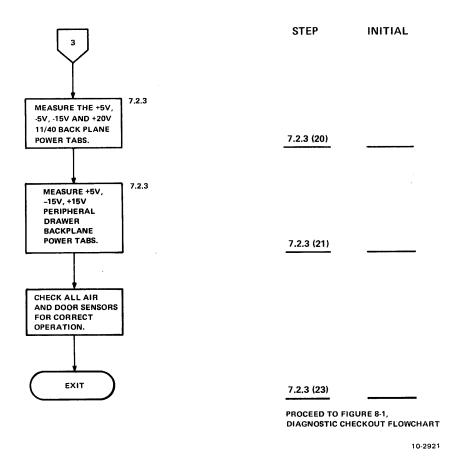

Figure 7-1 System Checkout Flowchart (Sheet 1 of 4)

Figure 7-1 System Checkout Flowchart (Sheet 2 of 4)

Figure 7-1 System Checkout Flowchart (Sheet 3 of 4)

Figure 7-1 System Checkout Flowchart (Sheet 4 of 4)

## 7.1.1 11/40 CPU - Front End

- 1. Pull out and fully extend the 11/40 CPU.

- 2. Check all connections from the H7420 power supply and voltage regulators to the 11/40 power distribution panel.

- 3. Check to ensure that all harnesses are secured and that all connections are properly made. Refer to the 2040 Console Processor Power Harness Distribution Print Set No. 7011448-0-0 (sheet 6 of 12).

- 4. Check to ensure that all modules are seated properly.

- 5. Ensure that the power distribution is correct (refer to the 2040 Console Processor Harness Distribution Print Set).

## 7.1.2 Peripheral Drawers

- 1. Pull and fully extend the peripherals drawer.

- 2. Check all connections from the H7420 power supply and H744 voltage regulators to the peripherals drawer.

- 3. Check to ensure that all harnesses are secured and that all connections are properly made. (Refer to Arithmetic Processor, D-UA-KL10-C-0, sheet 7 of 12.)

- 4. Check to ensure that all modules are seated properly.

- 5. Ensure that the power distribution is correct. (Refer to Arithmetic Processor, D-UA-KL10-C-0, sheet 7 of 12.)

#### **7.1.3 863 Power Control**

- 1. Check the connections of all the J plugs located on the front of the 863 power control.

- 2. Check the connections of the J2 and J3 plugs located on the rear of the 863 power control.

- 3. Place the 863 power control LOCAL-REMOTE switch to the LOCAL position.

- 4. Check to ensure that the OVERRIDE switch is in the OFF (down) position.

#### **7.1.4 861 Power Control**

- 1. Place the 861 power control LOCAL-REMOTE switch to the LOCAL position.

- 2. Ensure the J3 connection is secure.

## 7.1.5 H761 Regulated Power Supply

- 1. Remove screen assembly from H761.

- 2. Check all Faston tabs and terminal connections in power supply.

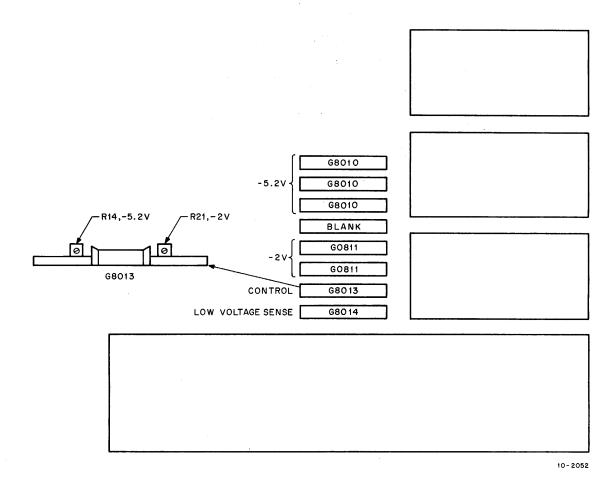

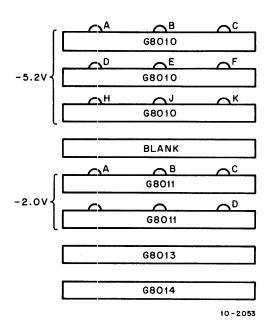

- 3. Ensure proper seating of G8010, G8011, G8013, and G8014.

- 4. Do not replace screen assembly until voltage checks and adjustments have been completed.

- 5. Ensure that the J1 and J8 plug connections are secure.

- 6. Verify that all harnesses and connections are secure and properly made. Refer to the KL10-C print set.

## 7.1.6 H7420 Power Supplies and Associated Voltage Regulators

- 1. The H7420 power supplies and associated voltage regulators are located in the CPU and I/O cabinet.

- 2. Verify that all harnesses and connections are secure and properly made.

## 7.2 SYSTEMS CHECKOUT

The systems checkout procedures flowchart is shown in Figure 7-1.

## 7.2.1 Print Set Definitions

The KL10 print set, entitled 2040 Console Processor (7011418-0-0 and D-UA-KL10C-0) contains the following information for each front-end option.

1. The option name, number, and wire list revision (if applicable; e.g., KD11A, 11/40 processor, wire list Rev. F).

- 2. Each option backplane revision, etch, and number (e.g., 5410904 etched backplane, Etch Rev. C, CS Rev. C, 11/40 CPU).

- 3. Every module of each option, listed individually with information pertaining to:

- a. The lowest acceptable revision (CS and etch)

- b. The status and use of each jumper (in or out)

- c. Any necessary cable information, e.g., cable type and connection locations

- d. Information relative to any other configurable component (e.g., crystal frequency, speed group, and potentiometer setting for DL11).

## 7.2.2 PDP-11/40 and Peripheral Drawer Power Harness