# LP20 LINE PRINTER SYSTEM MANUAL

1st Edition, January 1976 2nd Printing (Rev), April 1976 3rd Printing (Rev), August 1976 4th Printing (Rev), October 1977

#### Copyright © 1976, 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

#### **CONTENTS**

|           |                                            | Page              |

|-----------|--------------------------------------------|-------------------|

| CHAPTER 1 | INTRODUCTION                               |                   |

| 1.1       | SCOPE                                      | 1 1               |

| 1.2       | SPECIFICATIONS                             | 1-1<br>1 2        |

| 1.3       | FUNCTIONAL DESCRIPTION                     | 1-3-<br>/ 1       |

| 1.4       | PHYSICAL DESCRIPTION                       | 1-4<br>1 1        |

| 1.5       | APPLICABLE DOCUMENTS                       | 1-0               |

| CHAPTER 2 | INSTALLATION                               |                   |

| 2.1       | INTRODUCTION                               | 2-1               |

| 2.2       | EQUIPMENT UNPACKING                        | 7 <sub>-</sub> 1  |

| 2.2.1     | Unpacking the Line Printer                 | 2-1<br>2-1        |

| 2.2.2     | Unpacking the LP20 Controller              | 2-1<br>2-1        |

| 2.3       | INSPECTION                                 | 2 -1<br>2 1       |

| 2.4       | INSTALLATION PROCEDURES                    | 2-1<br>つつ         |

| 2.4.1     | Installing the Line Printer                | 2-2               |

| 2.4.2     | Installing the LP20 Controller             | 2-2               |

| 2.4.2.1   | Module Configuration                       | 2-2               |

| 2.4.2.2   | Installing a Single LP20 Controller        | 2.2               |

| 2.4.2.3   | Installing Two LP20 Controllers            | 2-2               |

| 2.5       | AC POWER CHECKOUT PROCEDURES FOR LP20 LINE | 2-3               |

|           | PRINTER SYSTEMS                            | 2.4               |

| 2.6       | SYSTEM CHECKOUT PROCEDURE                  | 2-4               |

| CHAPTER 3 | OPERATION                                  |                   |

| CHAPTER 4 | PROGRAMMING                                |                   |

| 4.1       | INTRODUCTION                               | 4-1               |

| 4.2       | OPERATIONAL MODES                          | 4-1               |

| 4.2.1     | Loading the RAM                            | 4-5               |

| 4.2.2     | Loading the DAVFU                          | 4-8               |

| 4.2.3     | Printing Characters                        | 4-10              |

| 4.2.4     | Test Mode                                  | 4-11              |

| 4.3       | DEVICE REGISTERS                           | 4_12              |

| 4.4       | TRANSLATION RAM                            | 4_12              |

| 4.5       | DIRECT ACCESS VERTICAL FORMAT UNIT (DAVFU) | Δ <sub>-</sub> 12 |

| 4.6       | LOCAL INITIALIZE                           | Δ-12<br>Δ-28      |

| 4.7       | ERROR RESET                                | 1 20<br>1 20      |

| 4.8       | DATA MULTIPLEXER                           | 4-20<br>1-20      |

| 4.8.1     | Control and Status Register A (CSRA)       | 4-20<br>1-29      |

| 4.8.2     | Control and Status Register B (CSRB).      | Δ-28              |

### CONTENTS (CONT)

|           |                                                        | Page |

|-----------|--------------------------------------------------------|------|

| 4.8.3     | Bus Address Register                                   | 4-28 |

| 4.8.4     | Byte Counter                                           | 4-28 |

| 4.8.5     | Page Counter                                           | 4-28 |

| 4.8.6     | RAM Data                                               | 4-28 |

| 4.8.7     | Character Buffer                                       | 4-29 |

| 4.8.8     | Column Counter                                         | 4-29 |

| 4.8.9     | Checksum                                               | 4-29 |

| 4.8.10    | Printer Multiplexer                                    | 4-29 |

| 4.9       | ESCAPE SEQUENCE                                        | 4-29 |

| 4.10      | ILLEGAL OR UNDEFINED CHARACTERS                        | 4-30 |

| 4.11      | MEMORY PARITY                                          | 4-30 |

| 4.12      | RAM PARITY                                             | 4-30 |

| 4.13      | PROGRAMMING EXAMPLE                                    | 4-30 |

| CHAPTER 5 | TECHNICAL DESCRIPTION                                  |      |

| 5.1       | INTRODUCTION                                           | 5-1  |

| 5.2       | GENERAL INFORMATION                                    | 5-1  |

| 5.2.1     | Logic Diagrams                                         | 5-1  |

| 5.2.2     | IC Complement                                          | 5-7  |

| 5.2.3     | Printer Interface Signals                              | 5-8  |

| 5.2.4     | Unibus Interface Signals                               | 5-8  |

| 5.2.5     | PDP-11 Word Structure                                  | 5-8  |

| 5.3       | DETAILED THEORY                                        | 5-8  |

| 5.3.1     | Modes of Operation                                     | 5-8  |

| 5.3.2     | System Power-Up Sequence                               | 5-8  |

| 5.3.3     | Controller Initialization                              | 5-9  |

| 5.3.4     | Printer Power-Up Sequence                              | 5-9  |

| 5.3.5     | Placing the Printer On-Line                            | 5-9  |

| 5.3.6     | Printer Demand                                         | 5-9  |

| 5.3.7     | Reading and Writing Controller Registers               | 5-10 |

| 5.3.8     | Non-Processor Request (NPR) Clock                      | 5-12 |

| 5.3.9     | Interrupts                                             | 5-13 |

| 5.3.10    | RAM Load (DMA)                                         | 5-15 |

| 5.3.10.1  | Setting Up Bus Address Register                        | 5-15 |

| 5.3.10.2  | Setting Up Byte Counter                                | 5-16 |

| 5.3.10.3  | Setting Up Control Bits for RAM Load                   | 5-16 |

| 5.3.10.4  | Setting Up GO Flip-Flop                                | 5-17 |

| 5.3.10.5  | Executing an NPR                                       | 5-17 |

| 5.3.10.6  | Writing the RAM                                        | 5-18 |

| 5.3.10.7  | Other RAM Load Mode Operations                         | 5-22 |

| 5.3.10.8  | Summary of DMA in RAM Load Mode of Operation           | 5-23 |

| 5 3 11    | Loading the Direct Access Vertical Format Unit (DAVFU) | 5-24 |

### **CONTENTS (CONT)**

|           |                                                        | Page |

|-----------|--------------------------------------------------------|------|

| 5.3.11.1  | Setting Up Bus Address Register and Byte Counter       | 5-25 |

| 5.3.11.2  | Determining Correct Byte Count for DAVFU Load          |      |

| 5.3.11.3  | DAVFU Load Control Bits                                |      |

| 5.3.11.4  | DAVFU Character Storage                                | 5-27 |

| 5.3.12    | Print Mode                                             |      |

| 5.3.12.1  | Printable Characters                                   |      |

| 5.3.12.2  | Print Mode Control Bits and Register Setup             |      |

| 5.3.12.3  | Character Processing                                   |      |

| 5.3.13    | Error Conditions                                       |      |

| 5.3.13.1  | Printer Off-Line                                       |      |

| 5.3.13.2  | Printer Parity Error (Printers with Parity Logic Only) |      |

| 5.3.13.3  | DAVFU Not Ready (DAVFU-Equipped Printers Only)         |      |

| 5.3.13.4  | Demand Time-Out Error                                  |      |

| 5.3.13.5  | GO Error, RAM Parity Error, or Memory Parity Error Set |      |

| 5.3.13.6  | Error Reset                                            |      |

| 5.3.14    | Test Mode                                              |      |

| 5.3.15    | Testing the Controller.                                |      |

| 5.3.15.1  |                                                        |      |

| 5.3.15.2  | DEMAND Time-Out Test                                   |      |

| 5.3.15.3  |                                                        |      |

| 5.3.15.4  | RAM Parity Test                                        |      |

|           | Memory Parity Test                                     |      |

| 5.3.15.5  | LPT Parity Test                                        |      |

| 5.3.15.6  | Page Counter Test                                      |      |

| 5.3.15.7  | Loading the Column Counter for Maintenance Purposes    | 5-33 |

| CHAPTER 6 | PREVENTIVE MAINTENANCE                                 |      |

| CHAPTER 7 | PRINTER DESCRIPTIONS                                   |      |

| 7.1       | LP05 LINE PRINTER                                      | 7-2  |

| 7.1.1     | LP05 Line Printer General Description                  | 7-2  |

| 7.1.2     | LP05 Interface Signals                                 | 7-4  |

| 7.1.3     | LP05 Printer Specifications                            | 7-5  |

| 7.1.4     | LP05 Space Requirements                                |      |

| 7.2       | LP07 LINE PRINTER                                      |      |

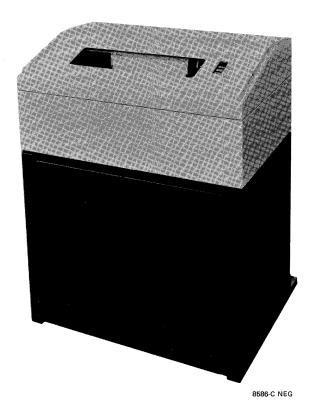

| 7.2.1     | LP07 Line Printer General Description                  |      |

| 7.2.2     | LP07 Interface Signals                                 |      |

| 7.2.3     | LP07 Printer Specifications                            |      |

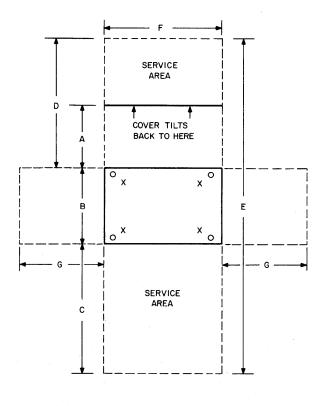

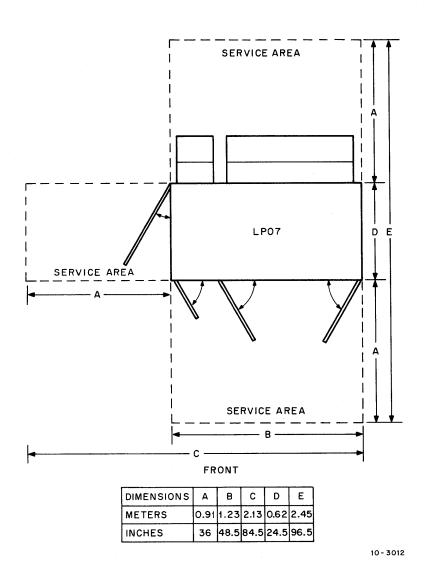

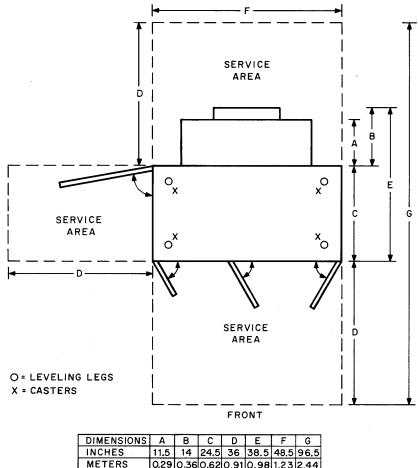

| 7.2.4     | LP07 Space Requirements                                |      |

| 7.3       | LP10 LINE PRINTER                                      |      |

| 7.3.1     | LP10 Line Printer General Description                  |      |

| 7.3.2     | LP10 Interface Signals                                 |      |

| 7.3.3     | LP10 Printer Specifications                            |      |

| 7.3.4     | LP10 Space Requirements                                |      |

|           | •                                                      |      |

### **CONTENTS (CONT)**

Page

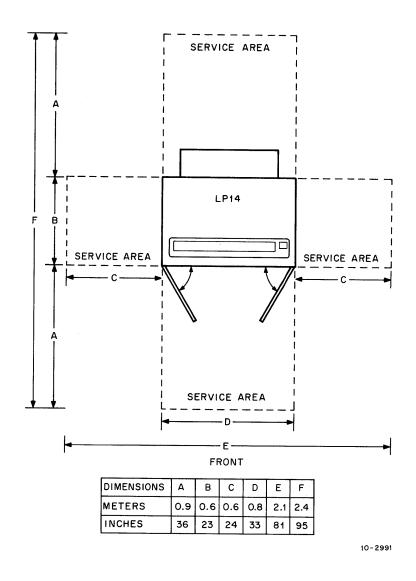

| 7.4<br>7.4.1<br>7.4.2<br>7.4.3<br>7.4.4 | LP14 LINE PRINTER  LP14 Line Printer General Description  LP14 Interface Signals  LP14 Printer Specifications  LP14 Space Requirements | 7-22<br>7-24<br>7-25 |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| APPENDIX A                              | ASCII CHARACTER SET                                                                                                                    |                      |

| APPENDIX B                              | 64 DATA PROCESSING (EDP) CHARACTER SET                                                                                                 |                      |

| APPENDIX C                              | 96 DATA PROCESSING (EDP) CHARACTER SET                                                                                                 |                      |

| APPENDIX D                              | PRINTER CODE CHART                                                                                                                     |                      |

|                                         | FIGURES                                                                                                                                |                      |

| Figure No.                              | Title                                                                                                                                  | Page                 |

| 1-1                                     | LP20 Line Printer System Simplified Functional Block Diagram                                                                           | 1-4                  |

| 1-2                                     | Typical LP20 Controller Assembly Mounting                                                                                              | 1-7                  |

| 4-1                                     | LP20 Line Printer System Block Diagram                                                                                                 |                      |

| 4-2                                     | Typical Bit Patterns in DAVFU Memory                                                                                                   |                      |

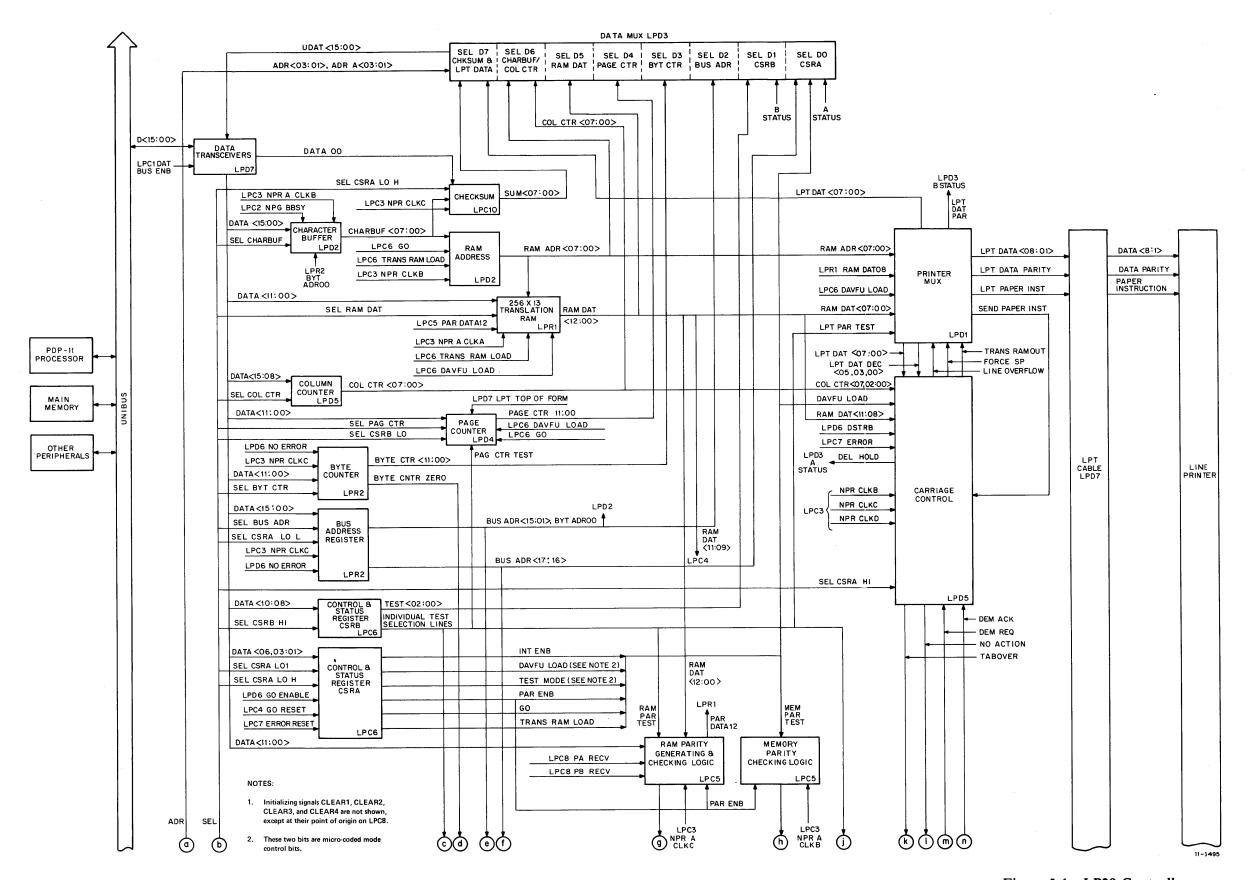

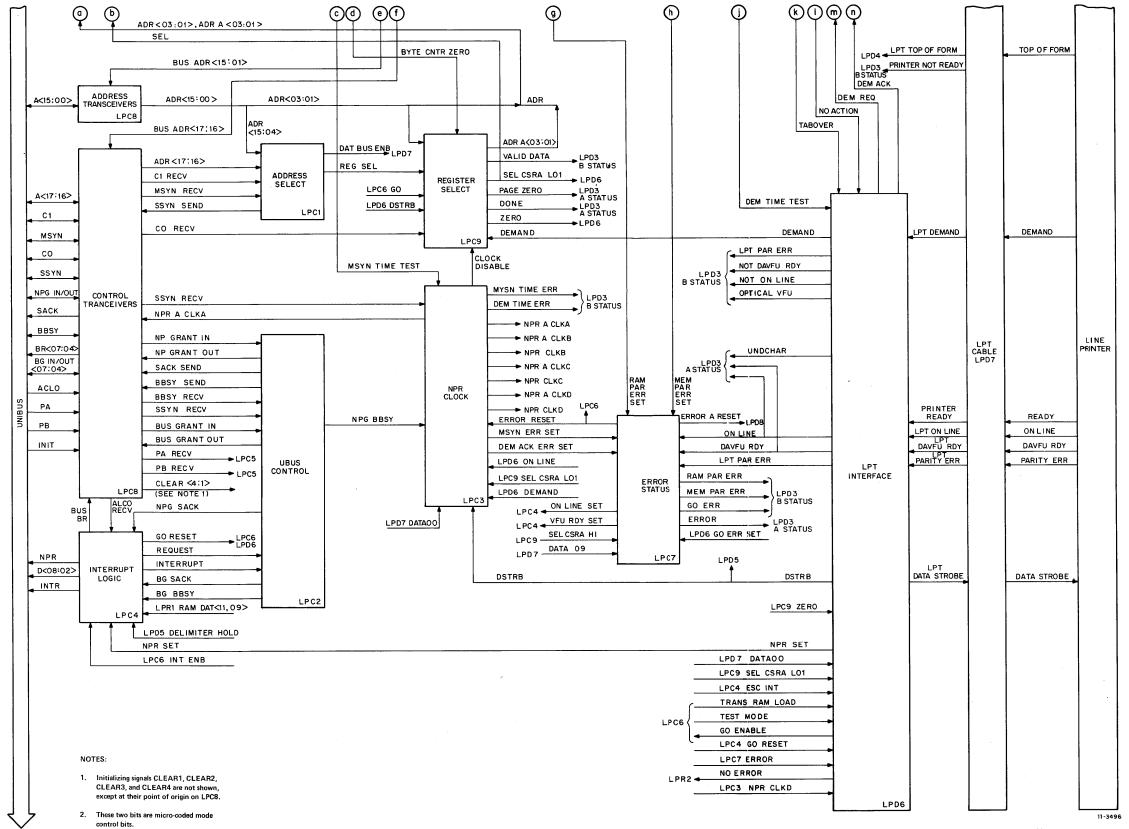

| 5-1                                     | LP20 Controller Detailed Block Diagram                                                                                                 |                      |

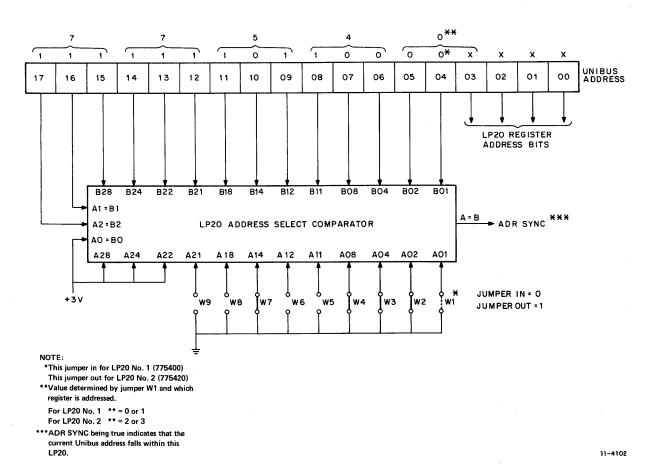

| 5-2                                     | LP20 Address Select Comparator                                                                                                         | 5-10                 |

| 5-3                                     | Addressable Registers                                                                                                                  |                      |

| 5-4                                     | Bus Request Priority Plug Jumper Connections                                                                                           | 5-14                 |

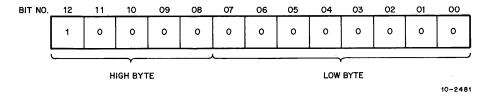

| 5-5                                     | Bit Configuration for Bus Address Register                                                                                             | 5-15                 |

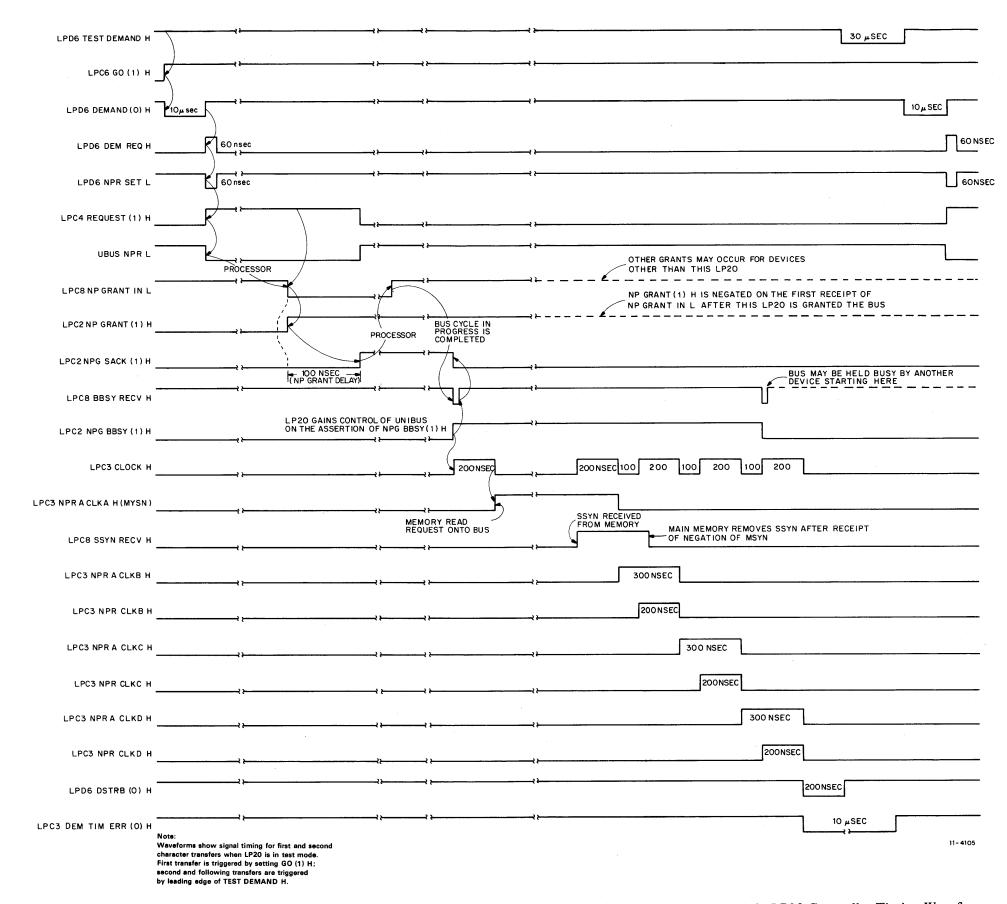

| 5-6                                     | LP20 Controller Timing Waveforms                                                                                                       |                      |

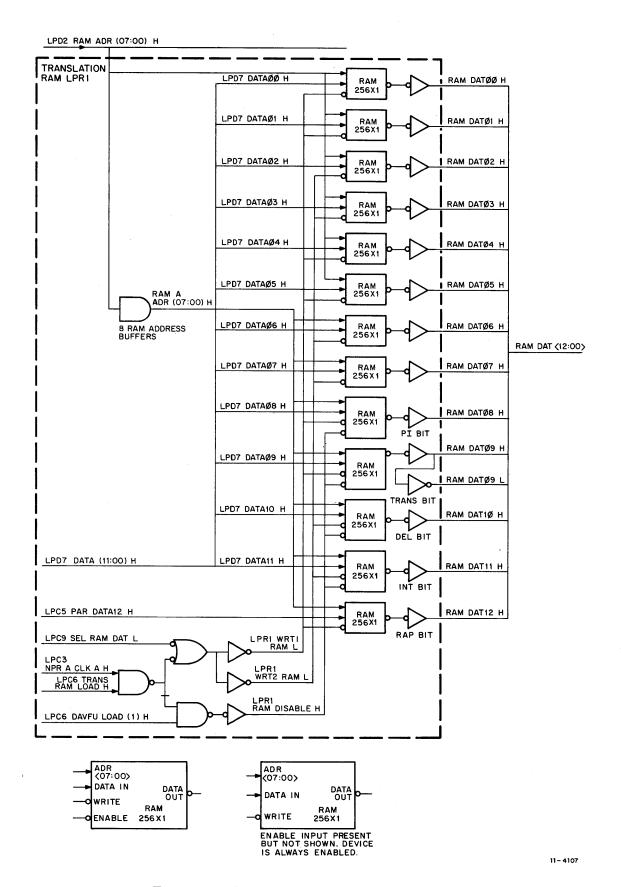

| 5-7                                     | Translation RAM Simplified Schematic                                                                                                   | 5-21                 |

| 7-1                                     | Printer Interface Signals                                                                                                              | 7-1                  |

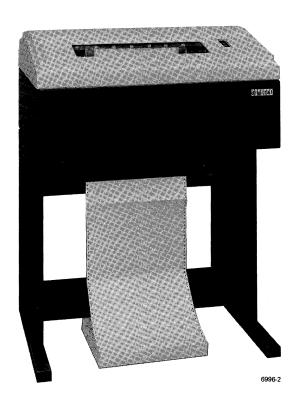

| 7-2                                     | Model LP05 Line Printer                                                                                                                |                      |

| 7-3                                     | LP05 Printer Space Requirements                                                                                                        | 7-7                  |

| 7-4                                     | Model LP07 Line Printer                                                                                                                | 7-8                  |

| 7-5                                     | LP07 Printer Space Requirements                                                                                                        |                      |

| 7-6                                     | Model LP10 Line Printer                                                                                                                |                      |

| 7-7                                     | LP10 Printer Space Requirements                                                                                                        |                      |

| 7-8                                     | Model LP14 Line Printer                                                                                                                |                      |

| 7-9                                     | LP14 Printer Space Requirements                                                                                                        |                      |

### **TABLES**

| Table No. | Title                                                         | Page |

|-----------|---------------------------------------------------------------|------|

| 1-1       | Basic Characteristics of LP20 Line Printer Systems            | 1-2  |

| 1-2       | LP20 Line Printer Controller Specifications                   | 1-3  |

| 1-3       | Applicable Documents                                          | 1-10 |

| 4-1       | LP20 Register Allocation Summary                              | 4-13 |

| 4-2       | CSRA Bit Interpretation                                       | 4-15 |

| 4-3       | CSRB Bit Interpretation                                       | 4-18 |

| 4-4       | Translation RAM Bit Interpretation                            | 4-21 |

| 4-5       | Permutations of LP20 Control Bits                             | 4-23 |

| 4-6       | Vertical Format Instruction—Data Code is Used to Control      |      |

|           | Duration of Slew (DAVFU or Optical VFU)                       | 4-26 |

| 4-7       | Vertical Format Instruction—DAVFU is Used to Control Duration |      |

|           | of Slew (DAVFU or Optical VFU)                                | 4-26 |

| 4-8       | Example of DAVFU Load                                         |      |

| 4-9       | LP20 Sample Program                                           | 4-31 |

| 5-1       | List of Module Logic Diagrams for LP20 Controller             | 5-1  |

| 5-2       | IC Complement in LP20 Controller                              | 5-7  |

| 7-1       | LP05 Applicable Documents                                     | 7-3  |

| 7-2       | LP05 Printer Interface Signals                                | 7-4  |

| 7-3       | LP05 Printer Specifications Summary                           | 7-5  |

| 7-4       | LP07 Applicable Documents                                     | 7-9  |

| 7-5       | LP07 Printer Interface Signals                                | 7-10 |

| 7-6       | LP07 Printer Specifications Summary                           |      |

| 7-7       | LP200 Charaband and Ribbon Options                            | 7-13 |

| 7-8       | LP10-J, -K Applicable Documents                               | 7-16 |

| 7-9       | LP10-J, -K Printer Interface Signals                          | 7-17 |

| 7-10      | LP10 Printer Specifications Summary                           | 7-18 |

| 7-11      | LP14 Applicable Documents                                     | 7-23 |

| 7-12      | LP14 Printer Interface Signals                                | 7-24 |

| 7-13      | LP14 Printer Specifications Summary                           | 7-25 |

|           |                                                               |      |

## CHAPTER 1 INTRODUCTION

#### 1.1 SCOPE

This manual covers the description, installation, operation, programming, theory, and maintenance of the LP20 Line Printer System. Reference is made, where applicable, to detailed information in other supporting technical documentation. A prerequisite is a basic understanding of PDP-11 processors and peripherals, with emphasis on Unibus operation.

The LP20 Line Printer System is a hard-copy printer system designed to interface with the PDP-11 Unibus. Each printer system comprises a self-contained, free-standing line printer and a separate, solid-state controller (LP20 Controller). The controller consists of three logic modules, a wired backplane assembly, and associated cabling.

Design of the LP20 Line Printer System provides for large amounts of formatted or unformatted text to be printed with minimum software intervention. This is accomplished by transferring characters under direct memory access (DMA) control and by using a random access memory (RAM) in the LP20 Controller to control actions taken on individual characters. Thus, software need only handle errors and situations that cannot be handled by data stored in the RAM.

Several types of line printers are supported by the LP20 Controller; the line printers are plug-for-plug compatible and use identical cabling.

Table 1-1 summarizes the basic characteristics of LP20 Line Printer Systems.

Table 1-1 Basic Characteristics of LP20 Line Printer Systems

| Printer<br>System<br>Model | Print<br>Rate | Character<br>Set | Font | Power          | Printer |

|----------------------------|---------------|------------------|------|----------------|---------|

| LP20-AA                    | 300 lpm       | 64               | EDP  | 120 Vac, 60 Hz | LP05-VK |

| LP20-AB                    | 300 lpm       | 64               | EDP  | 240 Vac, 50 Hz | LP05-VN |

| LP20-AC                    | 300 lpm       | 64               | SCI  | 120 Vac, 60 Hz | LP05-VP |

| LP20-AD                    | 300 lpm       | 64               | SCI  | 240 Vac, 50 Hz | LP05-VT |

| LP20-BA                    | 230 lpm       | 96               | EDP  | 120 Vac, 60 Hz | LP05-WK |

| LP20-BB                    | 230 lpm       | 96               | EDP  | 240 Vac, 50 Hz | LP05-WN |

| LP20-BC                    | 230 lpm       | 96               | SCI  | 120 Vac, 60 Hz | LP05-WP |

| LP20-BD                    | 230 lpm       | 96               | SCI  | 240 Vac, 50 Hz | LP05-WT |

| LP20-CA                    | 890 lpm       | 64               | EDP  | 120 Vac, 60 Hz | LP14-VK |

| LP20-CB                    | 890 lpm       | 64               | EDP  | 240 Vac, 50 Hz | LP14-VN |

| LP20-CC                    | 890 lpm       | 64               | SCI  | 120 Vac, 60 Hz | LP14-VP |

| LP20-CD                    | 890 lpm       | 64               | SCI  | 240 Vac, 50 Hz | LP14-VT |

| LP20-DA                    | 650 lpm       | 96               | EDP  | 120 Vac, 60 Hz | LP14-WK |

| LP20-DB                    | 650 lpm       | 96               | EDP  | 240 Vac, 50 Hz | LP14-WN |

| LP20-DC                    | 650 lpm       | 96               | SCI  | 120 Vac, 60 Hz | LP14-WP |

| LP20-DD                    | 650 lpm       | 96               | SCI  | 240 Vac, 50 Hz | LP14-WT |

| LP20-FA                    | 1250 lpm      | 64               | EDP  | 120 Vac, 60 Hz | LP10-JA |

| LP20-FB                    | 1250 lpm      | 64               | EDP  | 240 Vac, 50 Hz | LP10-JB |

| LP20-FC                    | 1250 lpm      | 64               | SCI  | 120 Vac, 60 Hz | LP10-JC |

| LP20-FD                    | 1250 lpm      | 64               | SCI  | 240 Vac, 50 Hz | LP10-JD |

| LP20-HA                    | 925 lpm       | 96               | EDP  | 120 Vac, 60 Hz | LP10-KA |

| LP20-HB                    | 925 lpm       | 96               | EDP  | 240 Vac, 50 Hz | LP10-KB |

| LP20-HC                    | 925 lpm       | 96               | SCI  | 120 Vac, 60 Hz | LP10-KC |

| LP20-HD                    | 925 lpm       | 96               | SCI  | 240 Vac, 50 Hz | LP10-KD |

| LP200-BA                   | 1220 lpm      | 64               | *    | 220 Vac, 60 Hz | LP07-BA |

| LP200-BB                   | 905 lpm       | 96               | *    | 220 Vac, 50 Hz | LP07-BB |

<sup>\*</sup>See Table 7-7.

#### 1.2 SPECIFICATIONS

The LP20 Controller is common to all LP20 Line Printer Systems. Performance specifications of the controller are listed in Table 1-2.

Table 1-2 LP20 Line Printer Controller Specifications

|                                | Table 1-2 | LF20 Line Printer Controller Specifications                                                                                                                                                                                                    |

|--------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Registers                      |           | Total of eight registers: Control and Status Register A (CSRA) Control and Status Register B (CSRB) Bus Address Byte Counter Page Counter RAM Data Character Buffer/Column Counter Checksum/LPT Data                                           |

| Character Dependent Operations |           | Controlled by internal 256-word RAM which is addressed by the incoming character.                                                                                                                                                              |

| Hardware Defined Functions     |           | Horizontal tab every eight spaces.                                                                                                                                                                                                             |

|                                |           | Line feed on line overflow after 132 columns are printed.                                                                                                                                                                                      |

| Parity                         |           | Memory parity RAM parity Line printer parity (may be disabled)                                                                                                                                                                                 |

| Character Transfer<br>Mode     |           | PDP-11 Unibus, Direct Memory Access (DMA) transfers.                                                                                                                                                                                           |

| Checksum                       |           | Non-rotated sum of bytes addressed by the bus address register. High-order carries are ignored. Checksum is set to zero each time DMA transfers are started.                                                                                   |

| Printer Interface<br>Format    |           | Parallel; single character via an ASCII interface. The interface permits the transfer of data at a maximum rate of $5 \times 10^5$ characters per second. All signals are differentially driven lines carrying complementary TTL logic levels. |

| Power Requirements             |           | 4.5 A nominal @ 5 Vdc $\pm$ 5% (derived from power supply in cabinet where controller is installed).                                                                                                                                           |

| Cables                         |           | One BC06R-10 Input/Output Cable Assembly, supplied with system.                                                                                                                                                                                |

|                                |           | One BC11A-02 Unibus Cable Assembly, supplied with system.                                                                                                                                                                                      |

|                                |           | One 7009563 Power Harness, supplied with system.                                                                                                                                                                                               |

| Software                       |           | PDP-11 compatible. One LP20 Controller supports only one printer.                                                                                                                                                                              |

| Physical<br>Characteristics    |           | Overall dimensions of wired assembly and modules are approximately 41.59 cm (16-3/8 in) high by 6.35 cm (2-3/4 in) wide by 25.4 cm (10 in) deep.                                                                                               |

#### 1.3 FUNCTIONAL DESCRIPTION

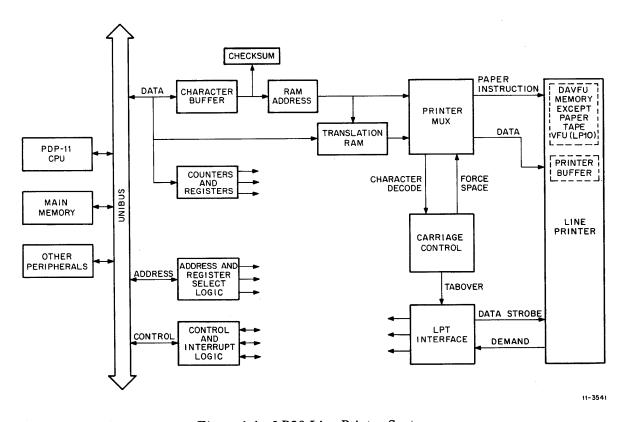

A simplified functional block diagram of an LP20 Line Printer System is shown in Figure 1-1. The controller comprises all the functional elements that interface between the Unibus and the line printer. Primary functions of the controller are to:

- 1. Indicate to the system the operational status of the printer.

- 2. Control the transfer of data characters and commands between the system and the printer (via DMA).

- 3. Perform code conversion and other character code dependent operations as required.

- 4. Provide hardware horizontal tab (every 8 spaces) and hardware line overflow (activated on the 133rd printable character in the current line).

- 5. Flag errors and special character conditions to the processor (via bus interrupts).

Figure 1-1 LP20 Line Printer System Simplified Functional Block Diagram

The LP20 Controller has four major operating modes: RAM load, DAVFU load, print, and test. RAM load and DAVFU load modes are used to load the contents of the RAM and DAVFU, respectively, from main memory. The DAVFU load mode is not used when the printer is an LP10-J or LP10-K model. Print mode uses the contents of the RAM to control operation of the controller and is the mode that actually prints data on the line printer. Test mode acts exactly like print mode, except that the operation of the physical output device is simulated by the controller and no data is sent to the physical line printer. This mode is used for diagnostic purposes. The LP10-J, -K VFU is not loaded by the controller as it is a paper tape VFU.

Code conversion and character code dependent operations are controlled by a 256- × 13-bit random access memory (RAM), which is loaded by the user. The 13-bit word stored at each RAM address contains one parity bit, four control bits (paper instruction, translation, delimiter, and interrupt), and eight data bits. Up to 256 such words can be stored in the RAM. Each RAM location is uniquely addressed by an 8-bit code. Hence, each character (in a character set as large as 256 characters) addresses a unique RAM location. This feature enables controller functions to be triggered on a character-specific basis.

The RAM is loaded via DMA by placing the controller in the RAM load mode. It may be loaded location-by-location under program control in RAM load mode, print mode, or test mode by depositing the RAM address into the character buffer (07:00) and then depositing the RAM data into the RAM data register (11:00).

The DAVFU is a programmable, solid-state replacement for the conventional tape reader (except LP10-J, K). It has 12 separate channels for user-definable vertical format control and can also slew paper from 0 to 15 lines on command. The DAVFU is loaded by the user under DMA only by operating the controller in the DAVFU load mode. Two of the DAVFU channels are reserved for specific functions: channel 1 (top-of-form) and channel 12 (bottom-of-form). These channels must always be loaded appropriately.

The print mode is entered after the RAM and DAVFU (or paper tape) have been loaded. In this mode, the controller reads a word from main memory and loads one byte of the word into the character buffer. The byte loaded is controlled by bit 00 of the bus address register. The controller uses this byte as an address for the RAM and decides, on the basis of the data in the addressed RAM location and various control bits, what to do with the character. Depending on the states of the four control bits in the RAM, the character may be converted (translated) to another character, converted to a paper motion command (translated to a paper instruction), flagged to the software as being an "undefined" character, or recognized as a delimiter character.

If the translation bit is set in the currently addressed RAM location, the character stored in the RAM data bits at that location is used as the current character rather than the contents of the character buffer.

If the paper instruction bit is also set, the controller asserts the paper instruction line, which causes the printer to interpret the character stored in the RAM as a carriage control character (vertical formatting instruction to the DAVFU) rather than as data to be printed.

Characters are transferred one at a time from main memory to the printer buffer in the line printer until a print command (carriage control character) is received. Printing is accomplished by first scanning the stored characters in synchronization with the rotating drum characters and then actuating the appropriate hammer as the desired characters move into the printing position.

The interrupt bit being set in the current RAM location causes the controller to interrupt the processor upon receipt of an illegal or undefined character (predetermined before loading of the RAM). The processor may then examine the illegal or undefined character, decide how to handle the situation, and continue printing.

The RAM can also be used to recognize a delimiter character (predetermined before loading the RAM). The controller will convert the delimiter character as well as the next following character to another code (defined by the contents of the RAM) to be sent to the printer. The delimiter feature is normally used to allow a dual definition of a single character, depending on whether or not the character follows an arbitrary but uniquely defined delimiter character. The dual-function character usually will have both a print and a paper motion definition. In this way, FORTRAN carriage control characters (which are also normal print characters that appear as the first rather than the last character in a line) can be handled directly by the controller hardware, rather than by software. Any 1-level escape sequence may be handled in this manner.

The controller has hardware-defined horizontal tab and automatic line-feed-on-line-overflow features. Upon receipt of a tab character, the printer will move to the next column in the sequence 9, 17, 25... 8N + 1. If a line contains more than 132 (decimal) printing characters, the controller will print 132 characters and send a line feed (LF) (ASCII 012<sub>8</sub>). The 133rd character will be printed as the first character of the next line. If the printer tries to tab beyond column 128, the line will be printed and the carriage will move to column 9 on the next line (column 1 being the first column).

The LP20 Controller, being a direct memory access (DMA) device, does not allow line printer data to be transferred under program control. Instead, the controller initiates DMA bus cycles to control the flow of data (on a character-by-character basis) to the printer. DMA bus cycles continue until all characters in the current line are stored in the printer buffer. A line is normally terminated by a carriage control character which may be an ASCII carriage return (CR), line feed (LF), form feed (FF), or any of 28 special carriage control commands to the DAVFU. Horizontal tab (HT) is converted into one to eight space characters, depending on the column count stored in the column counter at the time HT is decoded. Lines creating a line overflow condition are always terminated after 132 characters have been sent to the line printer by LF, which is forced onto the printer data lines by the controller hardware.

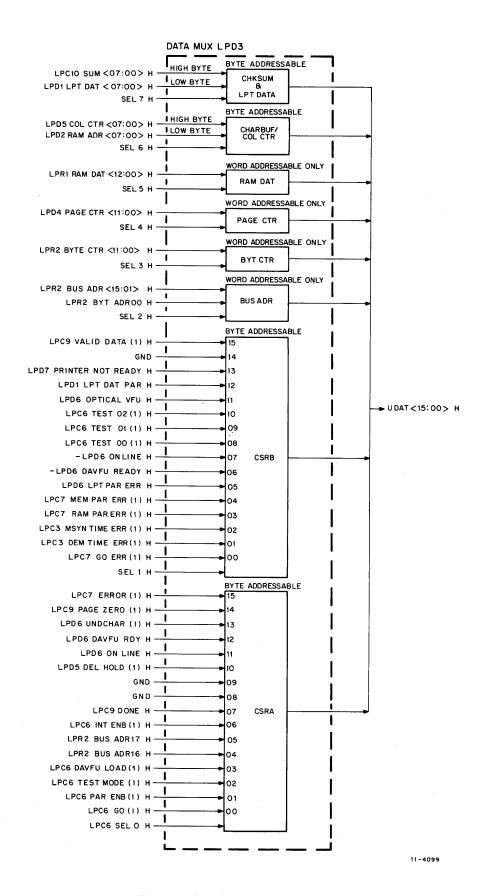

Communication between the LP20 Controller and the rest of the system is handled by standard PDP-11 control and interrupt logic. Transfer of status information between the LP20 Controller and the processor is accomplished by means of a data multiplexer in the controller through which the processor may examine the contents of any of the eight registers in the controller.

To maintain data integrity, RAM parity checking and generating logic is provided, as well as data transfer checksum computation.

Line printer parity is generated by the controller and is sent to the printer for checking. This feature can be disabled by a hardware jumper if the printer used does not check parity.

#### 1.4 PHYSICAL DESCRIPTION

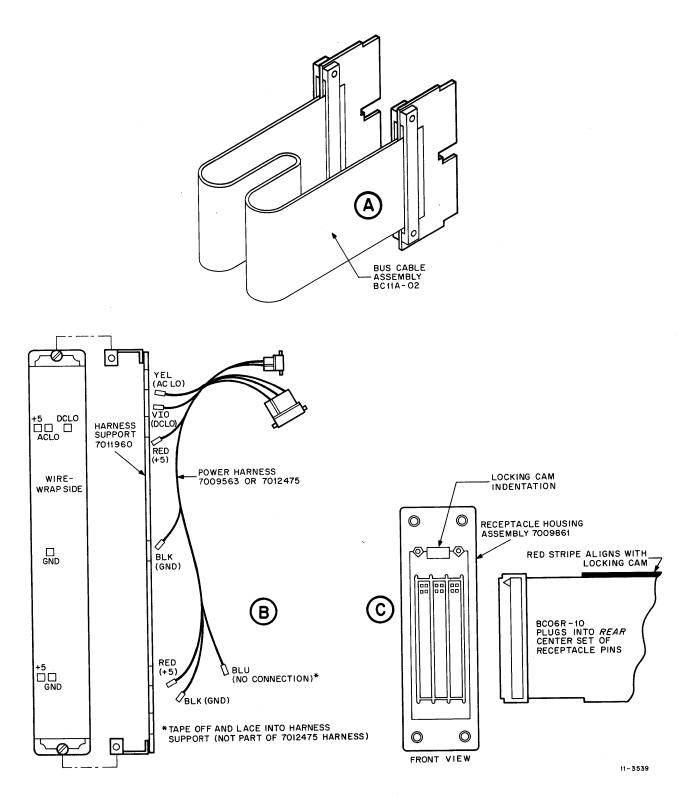

Figure 1-2 illustrates the basic assemblies that comprise the LP20 Controller. The three printed circuit boards (modules) are equipped with TTL integrated circuits. The modules are:

M8585 LP20 Translation RAM Module (LPR) M8586 LP20 Line Printer Control Module (LPC)

M8587 LP20 Line Printer Data Paths Module (LPD)

or

M8571 LP20 Line Printer Data Paths Module

Figure 1-2 Typical LP20 Controller Assembly Mounting (Sheet 1 of 2)

Figure 1-2 Typical LP20 Controller Assembly Mounting (Sheet 2 of 2)

M8586, M8587, and M8571 are hex-height modules and occupy slots A02-F02 and A03-F03 in the 4-slot LP20 wired assembly. The M8585 is a quad-height module and occupies slots C04-F04. BC11A-02 Unibus Cable Assemblies are used for interconnection to other system units. One BC11A-02 is supplied with the LP20 Controller and occupies slots A04 and B04 (Unibus Out). The BC11A from the previous option, option B in Figure 1-2, will occupy slots A01 and B01 (Unibus In).

# NOTE If this LP20 Controller is the last unit on the Unibus, the terminator module occupies slots A04 and B04.

The LP20 cable comes in four standard lengths:

| Part No.   | Length           |

|------------|------------------|

| 7011426-25 | 7.62 m (25 ft)   |

| 7011426-50 | 15.24 m (50 ft)  |

| 7011426-75 | 22.86 m (75 ft)  |

| 7011426-A0 | 30.48 m (100 ft) |

|            |                  |

Hardware jumpers on the M8586 module allow the controller to be configured for the correct base address and interrupt vector. A ONE is represented by removal of a base address selection jumper and by insertion of an interrupt vector selection jumper.

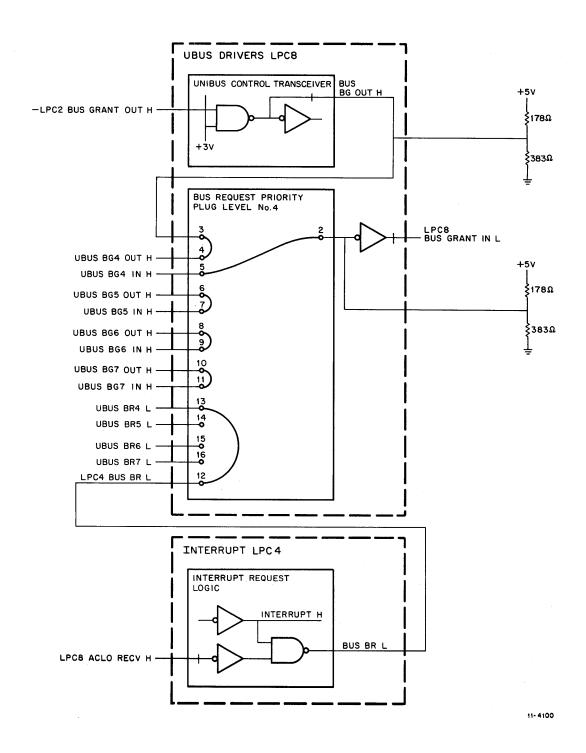

A Unibus priority plug sets the priority for bus requests. The plug normally used places bus requests at priority level No. 4 (BR4/BG4).

The LP20 power harness is tied to the harness support bracket on the wire-wrap side of the LP20 wired assembly. Six wires in the power harness connect to associated power terminals on the wired assembly. These wires are ACLO and DCLO (Unibus power supply status signals), two for +5 Vdc, and two for ground.

The 13-bit translation RAM is located on the M8585 module. The RAM storage consists of 13 RAM packages (256 words × 1 bit per package). The translation RAM and the printer DAVFU memory are both volatile memory devices which lose their stored contents when primary power is removed.

#### 1.5 APPLICABLE DOCUMENTS

This manual and the appropriate Dataproducts Corporation line printer manual must be used together for a complete understanding of the LP20 Line Printer System. The prime subject of this manual is the LP20 Controller. The line printers are described in detail in the Dataproducts Corporation manuals.

Table 1-3 lists the documents that are applicable to LP20 Line Printer Systems.

**Table 1-3** Applicable Documents

| Title                                                                    | Number        | Description                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LP20 Line Printer<br>Systems (Field<br>Maintenance Print<br>Set MP00006) | B-TC-LP20-0-1 | Detailed LP20 Controller module logic diagrams, backplane, and cable information.                                                                                                                                                                                 |

| PDP-11 Processor<br>and System<br>Manuals                                | *             | A series of maintenance and theory manuals that provide a detailed description of the basic PDP-11 System.                                                                                                                                                        |

| PDP-11 Processor<br>Handbook                                             | **            | A general handbook that discusses system architecture, addressing modes, the instruction set, programming techniques, and software.                                                                                                                               |

| PDP-11 Peripherals<br>Handbook                                           | *             | A handbook devoted to a discussion of the various peripherals used with PDP-11 Systems. It provides detailed theory, logic flow, and descriptions of the Unibus and external device logic; methods of interface construction; and examples of typical interfaces. |

<sup>\*</sup>Applicable manuals are furnished with the system at the time of installation. The document number depends on the specific PDP-11 family processor.

<sup>\*\*</sup>Use the processor handbook unique to the actual CPU.

## CHAPTER 2 INSTALLATION

#### 2.1 INTRODUCTION

This chapter is a guide for the installation of LP20 controllers and associated line printers. Detailed information required for installation of the line printer is contained in the appropriate line printer technical manual.

#### **CAUTION**

Although specific installation procedures are included in this and the referenced manuals, it is recommended that the equipment be installed by Digital Equipment Corporation field service personnel.

#### 2.2 EQUIPMENT UNPACKING

#### 2.2.1 Unpacking the Line Printer

Before removing the line printer from its shipping container, place it as close as possible to the final installation position. Unpack the equipment according to the detailed procedures in the appropriate line printer technical manual.

#### 2.2.2 Unpacking the LP20 Controller

- 1. Remove the LP20 Controller from its shipping carton.

- 2. Check all packing material before discarding to ensure that no components or hardware are accidentally discarded.

#### 2.3 INSPECTION

After removing the equipment, inspect all components according to the following procedure. Report any damage to the local DIGITAL field office.

- 1. Check the equipment received against the shipping checklist (A-PL-LP20-0-SL) to be certain that all equipment has been received.

- 2. Inspect the LP20 Controller modules for any signs of damage.

- 3. Inspect the LP20 wired assembly (7011427) for bent pins and verify that there is no short circuit between +5 V and ground by measuring with an ohmmeter between pins C02A2 and C02C2.

- 4. Inspect the line printer according to the detailed procedures in the appropriate line printer manual.

#### 2.4 INSTALLATION PROCEDURES

The following paragraphs describe the procedures required for installing an LP20 Line Printer System.

#### 2.4.1 Installing the Line Printer

Install the line printer according to the detailed procedures in the appropriate line printer technical manual.

#### 2.4.2 Installing the LP20 Controller

#### 2.4.2.1 Module Configuration

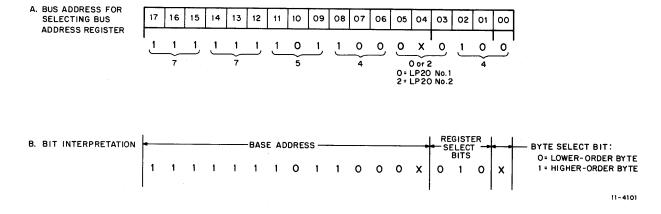

Device and Vector Addresses – One or two LP20 Controllers may be installed in the peripheral cabinet. When a system has one controller and one line printer, its base address (device address) will be 775400 and its corresponding vector address will be 754. However, when the system has two controllers and two line printers, the base address and vector address are assigned as follows:

| Unit No. 1 | Base address<br>Vector address | 775400<br>754 |

|------------|--------------------------------|---------------|

| Unit No. 2 | Base address<br>Vector address | 775420<br>750 |

Refer to drawings D-CS-M8586-0-LPC1 and D-CS-M8586-0-LPC4 in the LP20 print set for correct configuration information for the M8586 module.

**Priority Level** – The bus request/grant priority plug installed at the factory selects priority level BR4/BG4. Details of these jumper connections are provided in Chapter 5.

**Direct Access or Optical VFU** – All line printers except LP10-J, -K (LP20-F, -A) have a direct access vertical format unit (DAVFU). LP10 line printers have a paper tape (optical) vertical format unit. Refer to drawings D-CS-M8587-0-LPD0 and D-CS-M8571-0-LPD0 for correct jumper or dipswitch configuration for the printer in use.

Line Printer Parity – Refer to drawings D-CS-M8587-0-LPD0 and D-CS-M8571-0-LPD0 for correct jumper or dipswitch configuration based on the model of line printer in use.

**2.4.2.2** Installing a Single LP20 Controller – When the appropriate jumper wires on the modules have been removed, the next step is to install the controller. Refer to Figure 1-2 and proceed as follows for a typical installation:

# NOTE Refer to the LP20 Field Maintenance Print Set (MP00006) for cable drawings, circuit schematics, and a drawing of the wired assembly.

- 1. Determine the proper mounting position for the LP20 wired assembly (7011427).

- 2. Install the wired assembly and harness support in the mounting drawer. Before tightening the cap screws completely, insert a hex-height module into the wired assembly to check card guide alignment.

3. With a hex-height module in place, tighten the two cap screws securely and remove the hex-height module.

#### NOTE

Skip steps 4 and 5 if power harness 70-12475 is supplied.

4. Wrap the following unused Faston tabs of the power harness (70-09563) with tape:

Line clock (brown wire)

- +15 V (grey wire)

- -15 V (blue wire)

- 5. Tie back the loose wires. Then lace the entire power harness to the harness support.

- 6. Make the six electrical connections between the power harness and the wired assembly.

- 7. Make electrical connections between the power harness and the mounting drawer by plugging the two Mate-N-Lok connector plugs into available connector receptacles.

- 8. Install the Unibus cable assemblies according to Figure 1-2. If this LP20 is the last device on the Unibus, an M930 Unibus Terminator module, instead of the Unibus cable assembly, must be installed in slots A04 and B04.

- 9. Without modules installed, power up the system and measure  $\pm 5.0 \text{ V} \pm 5\%$  between either red wire (+5 V) and either black wire (ground) of the power harness at the Mate-N-Lok connector.

- 10. Power down the system and install the three LP20 modules according to Figure 1-2.

- 11. Connect the BC06R-10 cable to the Berg connector on the M8587 module with the wire (rib) side toward the module and the red line on the cable away from the handle.

- 12. Connect the other end of the BC06R-10 cable to the center slot of the receptacle housing assembly (7009861) with the red line on the cable toward the locking cam indentation as shown in Figure 1-2.

- 13. Connect the LP20 round cable (7011426-XX) to the receptacle housing assembly and connect the other end of the LP20 round cable to the line printer Winchester connector.

#### **CAUTION**

Route cables so that they do not bind or interface with other cables or modules. Do not overtighten the printer connector.

- 14. With modules and cables installed, power up the system and again measure  $+5.0 \text{ V} \pm 5\%$  as described in step 9.

- **2.4.2.3** Installing Two LP20 Controllers Installation of the second LP20 Controller is the same as that for the first controller, except for the configuration of address and vector jumpers.

#### 2.5 AC POWER CHECKOUT PROCEDURES FOR LP20 LINE PRINTER SYSTEMS

After an LP20 Line Printer System has been unpacked and installed at the site, perform the following checkout procedure before connecting the printer power cable to the power source. The power source may be either the receptacle in the system cabinet or a separate wall outlet.

- 1. Measure the ac source voltage to ensure that the proper voltage is present. Check that measured voltage is correct for the line printer power supply, as wired. If rewiring is necessary see appropriate line printer tehnical manual.

- 2. Plug line printer primary power cable into the power source receptacle.

- 3. Set the installation source power circuit breaker to the ON position.

- 4. Measure the potential between earth ground of the power source and the line printer frame. It should be 0 V with the processor on.

- 5. Power up the line printer according to the procedures in the appropriate line printer technical manual.

#### 2.6 SYSTEM CHECKOUT PROCEDURE

Perform a checkout of the line printer according to the procedures in the appropriate line printer technical manual then perform the following LP20 Line Printer System checkout procedures.

- 1. Refer to the LP20 Line Printer diagnostic listing for operational assistance and console switches used in debugging the controller.

- 2. Place the line printer on-line according to the appropriate line printer technical manual. Verify that the ON-LINE indicator lights. Run the following tests as specified. No errors are allowed.

#### NOTE

Steps a through e below may be performed with the LP20 Controller in the system but no line printer connected.

- a. Place the HALT/ENABLE switch on the processor in the HALT position.

- b. Load the appropriate start address as specified in the LP20 diagnostic listing.

- c. Set all processor data switches down. The controller will simulate the physical output device even if one is not connected. This is the Test mode.

- d. Place the HALT/ENABLE switch in the ENABLE position and press the START switch. Run the diagnostic for five error-free passes.

- e. Halt the processor.

- f. Load the appropriate start address.

- g. Set switch 0 up. The LP20 Controller will send characters to the line printer and printing will occur. This is the Print mode.

- h. Repeat steps c and d above. Verify that the line printer output is correct. This completes the system checkout.

# CHAPTER 3 OPERATION

The LP20 Controller does not have controls or indicators and there are no operating procedures applicable to the controller. All LP20 Line Printer System operator controls and indicators are on the associated line printer.

Refer to the appropriate line printer technical manual for detailed descriptions of the line printer controls, indicators, and operating procedures. The line printer technical manuals also contain descriptions of fault indicator and printer form controls, instructions for paper/forms installation and alignment, instructions for ribbon removal and replacement, and instructions for powering up and powering down the line printer.

The line printer technical manuals also contain troubleshooting procedures and corrective action for common problems that could be encountered when operating the line printer. If the corrective action specified does not correct the problem, or if the problem is not listed in the appropriate line printer technical manual, contact service/maintenance personnel.

If problems are attributable to the controller, it is necessary to run the LP20 diagnostic program.

#### NOTE

If an error in the LP20 Controller is detected during printer operation, the LP20 Controller will interrupt the processor and the print operation will be stopped. If the problem is corrected and the controller is functioning properly, the printer will then continue where it left off.

If an error occurs in the printer, on the other hand, the printer will automatically go off-line and cease printing until the problem is corrected.

Any power supply problem which causes the Unibus fault signal ACLO to be asserted will inhibit the NPR request and bus request logic. This prevents the LP20 Controller from requesting use of the bus during a power-fail or power-down condition.

# CHAPTER 4 PROGRAMMING

#### 4.1 INTRODUCTION

This chapter contains detailed information for programming the LP20 Line Printer System. Included is a condensed description of the different operational modes, followed by a tabulation of specific address assignments and bit definitions. A sample device routine program at the end of the chapter illustrates the different functions that can be programmed in a typical printing operation.

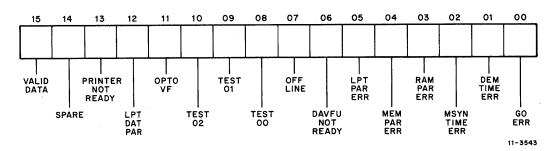

Registers and individual flip-flop states are available for examination by the processor. DMA is performed by setting up the correct register contents, setting up status and control bits to select the desired mode of operation in control and status registers A and B (CSRA and CSRB), and then bit-setting the GO bit (bit 00 of CSRA). The bit-set of bit 00 in CSRA is necessary due to timing constraints within the controller.

#### **CAUTION**

An attempt to set GO, and any other bits not previously set, in CSRA during the same instruction may produce unpredictable results in operation of the controller. Any attempt to modify bits in CSRA while GO is set may destroy the contents of the checksum register and produce other undesirable results.

#### 4.2 OPERATIONAL MODES

Figure 4-1 shows the block diagram of an LP20 Line Printer System, and also includes a summary of the four modes of operation:

- 1. Loading the RAM

- 2. Loading the DAVFU

- 3. Printing Characters

- 4. Test Mode

The four modes are microcoded in bit 02 (Test mode) and bit 03 (DAVFU Load) of control and status register A (CSRA). LP20 Line Printer Systems using printers not equipped with a DAVFU do not use the DAVFU Load mode of operation.

Assume initially that the line printer has been placed on-line and that the controller has been initialized by a UBUS INIT signal. (Initialization also occurs whenever the CPU is halted and the CPU START switch is depressed, or a RESET instruction is executed. It is also possible to clear the controller by sending a Local Initialize or Error Reset command\* to the LP20 Controller.)

<sup>\*</sup>See Sections 4.6 and 4.7 for details.

| UDAT <                                 | 5:00>                                                    | 1 MAX.                               | DATA                                             | MUX           |         | arangan .                           | ]                                                         | (IF SO EQUIPPED)                          |

|----------------------------------------|----------------------------------------------------------|--------------------------------------|--------------------------------------------------|---------------|---------|-------------------------------------|-----------------------------------------------------------|-------------------------------------------|

| (LC                                    | CHECKSUM CHECKSUM                                        | 00>                                  | RAM PARITY<br>CHECKING<br>LOGIC                  | <12:00        | >>      | LPT C                               | AT <07:00>                                                | PRINT                                     |

| D<15:00>                               |                                                          |                                      | < 07:0<br>6 x 13 BIT<br>SLATION RA<br>05 04 03 0 | м             | -       | PRINTER<br>MUX                      | LPT DATA <08:01>  LPT DATA PARITY  LPT PAPER INST.        | PRINT                                     |

| U                                      | RAM PARITY SENERATING A A P COUNTERS BYTE                | IDID                                 | GHT DATA B                                       |               | 00>     |                                     | CHARACTER                                                 |                                           |

| MEMORY U S                             | COLUMN PAGE  DAVFU LOAD or STATUS REGISTERS SRA CSRB  GO | nd TEST MODE                         |                                                  |               |         |                                     | - DECODE<br><07:00><br>FORCE<br>SPACE<br>LINE<br>OVERFLOW | LINE PRINTER (WITH DIRECT ACCESS VERTICAL |

| A <15:00> SEL                          | BUS<br>ADDRESS<br>REGISTER                               |                                      |                                                  | <07,          | COL CTR | CARRIAGE<br>CONTROL                 |                                                           | FORMAT UNIT)                              |

| A <17:16> ADDRE                        | 1                                                        |                                      |                                                  |               |         | TABOV                               | ER<br>LPT DATA<br>STROBE                                  |                                           |

| A <17:16>                              |                                                          |                                      | AAND<br>SET                                      |               | •       | LPT                                 | LPT<br>DEMAND                                             |                                           |

| D <08:02>                              |                                                          | OPERATIONAL SU                       |                                                  |               |         | INTERFACE                           | DAVFU<br>READY                                            |                                           |

| CO,CI CONTROL MYSN, SSYN AND INTERRUPT | OPERATION LOAD RAM                                       | ADDRESSING CONTRO                    | MODE                                             | DAVFU<br>LOAD |         |                                     | PRINTER<br>READY                                          |                                           |

| NPG IN/OUT LOGIC SACK                  | LOAD RAW                                                 | WORD :                               | ASSERTED                                         | ASSERTED      |         |                                     |                                                           |                                           |

| BBSY BR<07:04> BG<07:04> ACLO          | LOAD DAVFU<br>(IF SO<br>EQUIPPED)                        | NPR<br>NPR<br>WORD* :<br>:<br>INTR** | NEGATED                                          | ASSERTED      |         |                                     |                                                           |                                           |

| PA,PB<br>INIT                          | PRINT<br>CHARACTERS<br>ON PRINTER                        | WORD*  NPR NPR : : : INTR**          | NEGATED                                          | NEGATED       |         | ead from main mer<br>by byte ADR00) |                                                           | lower or upper byte                       |

| ~                                      | TEST MODE<br>(OUTPUT<br>DEVICE<br>IS                     | WORD* NPR                            | ASSERTED                                         | NEGATED       |         | n Byte counter ove                  |                                                           |                                           |

|                                        | SIMULATED)                                               | INTR**                               |                                                  |               |         |                                     |                                                           | 11-4106                                   |

|                                        |                                                          |                                      |                                                  |               |         |                                     |                                                           |                                           |

Figure 4-1 LP20 Line Printer System Block Diagram

4-3

When the printer is placed on-line, the printer DEMAND line is asserted, whereupon the DONE bit in CSRA is asserted. This indicates that the printer is on-line and ready to receive data on the bus.

#### 4.2.1 Loading the RAM

Before characters are actually sent to the line printer, it is normal procedure to first load the translation RAM in the controller. The device routine first checks the status of the ERROR and DONE bits in the CSRA. If the error flag is set (bit 15 of CSRA), the service routine first handles the error condition and then clears the error flag. The bus address register and the byte counter in the controller are then loaded, and the bits necessary for loading the RAM are set.

#### NOTE

The RAM can be loaded under program control or via DMA. This section discusses loading via DMA. See Section 4.3 for details on RAM load under program control.

The bus address register contains the 18-bit address of the first word to be loaded into the RAM. Bits (15:00) are loaded by depositing them into the bus address register. Bits (17:16) are deposited into bits (05:04) of CSRA.

The byte counter is a 12-bit binary counter and is loaded with the two's complement of the total number of bytes to be loaded into the RAM (2 bytes/word  $\times$  256 words = 512 bytes).

When the bus address register and the byte counter have been set up, control flip-flops in CSRA are set to establish the conditions for Interrupt Enable, Parity Enable, DAVFU Load, and Test mode. Asserting DAVFU Load and Test mode set up the condition for loading the translation RAM. In RAM Load or Test mode, the controller will fetch data from main memory, but no data will be sent to the printer.

The device routine then sets the GO flip-flop in CSRA to the one state. At this time, the RAM address register is cleared so that octal address 000 is selected in the RAM. When the GO flip-flop is set, a non-processor request (UBUS NPR) is initiated to request use of the bus for a DATI transfer into the LP20.

A DMA bus cycle follows to fetch the data contained in the main location specified by the contents of the bus address register. If the main memory receives and processes the memory request properly, it will return the requested data. Otherwise, the controller will time out, terminate UBUS MSYN, set an error flag in control and status register B (CSRB), and request an interrupt.

Assuming that the DATI transfer is successful, the least significant 12 bits of data, DATA (11:00), from main memory are clocked into octal address 000 of the RAM along with a parity bit for the data word in octal address 000 generated by the controller.

In this case, the parity bit is a 1 if there are an even number of 1s in bits (11:00), and a 0 if there are an odd number of 1s in bits (11:00). This is the condition for odd parity. The high-order bits of the DATI word, (15:12), are ignored by the controller during RAM Load. Even parity may be written or checked by setting the code for RAM Parity Test in the Test Type bits in control and status register B (CSRB).

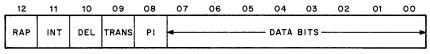

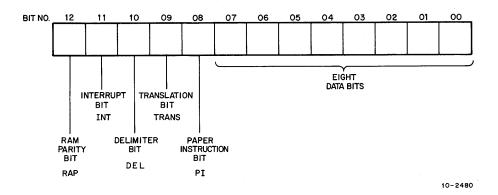

The RAM is capable of storing 256 13-bit words. Each word contains eight data bits, a paper instruction (PI) bit, a translation (TRANS) bit, a delimiter (DEL) bit, an interrupt (INT) bit, and a RAM parity (RAP) bit. Details of the RAM control bits are provided in Tables 4-4 and 4-5.

The eight data bits (07:00) are a data character. This character can be either a printable character or a non-printing character. Printable characters include letters of the alphabet, numerals, and special symbols, depending on the character set in use.\*

Carriage control characters-include carriage return (CR), line feed (LF), and form feed (FF). Horizontal tab (HT) is not recognized by the line printer. Instead, horizontal tab is decoded by the controller which then forces one to eight space codes onto the printer data lines depending on the current value of the column counter. The space codes produce 8-column fields, starting at columns 9, 17, 25, ... 8N + 1, where n = 1, 2, 3, etc. for a maximum of 16 fields per line.

| , + | Mnemonic<br>CR | Code<br>(Octal)<br>015 | Name<br>Carriage<br>Return | Function Causes the currently stored characters to be printed; then resets column counter to zero. Does not advance paper.                     |

|-----|----------------|------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|     | LF             | 012                    | Line<br>Feed               | Causes the currently stored characters to be printed; then resets column counter to zero and advances paper one line.                          |

|     | FF             | 014                    | Form<br>Feed               | Functions the same as LF above except paper is advanced to the next Top-of-Form position.                                                      |

|     | НТ             | 011                    | Horizontal<br>Tab          | Converted by the controller to 1-8 space codes. The number of spaces sent is determined by the column counter value at the time HT is decoded. |

If a line contains more than 132 decimal printing characters, hardware line overflow will occur. The controller will print 132 characters and begin a new line. The 133rd character will be printed as the first character of the next line. Trying the tab beyond column 128 causes the printer to automatically tab to column 9 on the next line.

If the 133rd character is CR, LF, or FF, there will be no hardware line overflow, and the specified function will be executed. If a translated Paper Instruction is programmed, the contents of the printer buffer will be printed and the paper will then slew 0 to 15 lines, or move according to the contents of the preselected DAVFU channel. See Tables 4-6 and 4-7.

The paper instruction (PI) bit is asserted when the character is to be recognized by the DAVFU or VFU as a code for vertical formatting. The PI bit is asserted only if translation is taking place (see Table 4-5). In this case, the signal LPT PAPER INST is asserted. Otherwise, the PI bit is a 0, and the character is routed directly to the printer buffer, either for printing or for print control (that is, CR, LF, or FF).

The translation (TRANS) bit is asserted when the character in that particular RAM location is to be routed to the printer. If translation is not taking place, the character in the character buffer will be routed to the printer (Table 4-5).

Setting the delimiter (DEL) bit to a 1 will cause the current character and the next incoming character to be translated (taken from the RAM instead of the character buffer) regardless of the state of the translation (TRANS) bit. The character with the delimiter bit asserted is normally translated into a no-action character (ASCII 000) (Table 4-5).

<sup>\*</sup>See Appendixes B, C, and D.

Asserting the interrupt (INT) bit will cause the controller to generate a bus request (BR) interrupt to the processor instead of generating a data strobe to the printer, provided Interrupt Enable is set in CSRA. Other RAM control bits being asserted may disable the bus interrupt (Table 4-5).

The least significant eight data bits, DATA (07:00), are also clocked into the character buffer. These bits, which represent the lower order byte of the data word, are then routed to the checksum generator and added to the binary sum currently in the checksum hold register. The data bits from the character buffer are not loaded into the RAM address register during this mode of operation.

Following checksum, both the bus address register and the byte counter are incremented by one. Shortly thereafter, the controller NPG BBSY flip-flop is cleared, which negates UBUS BBSY. At this point, the LP20 relinquishes control of the bus.

When the LP20 relinquishes control of the bus, the Data Strobe flip-flop in the LPT interface is asserted. However, because the controller is in the RAM Load mode (Test mode = 1, DAVFU Load = 1), a data strobe is not sent to the printer. Instead, a simulation of the line printer interface takes place within the controller. Also a Demand Timeout test is activated. If the DEMAND signal is not removed and the Data Strobe flip-flop is not cleared before the Demand Timeout test times out, a Demand Time error occurs. This sets the Error flip-flop and halts the controller.

If the byte count has not reached zero and no error conditions occur, another NPR is requested. Again, UBUS NPR is asserted, indicating that the LP20 is requesting use of the bus for another DATI transfer.

When the second UBUS NPR is asserted, the same data word is written into RAM location 000. All other operation is identical to the preceding, except that: the higher order data byte is clocked into the character buffer and then into the checksum generator; and the RAM address register is incremented by one. This means that, in the RAM Load mode, the bus address register and the byte counter are incremented by one on each NPR so that a total of two NPRs are required to transfer first the lower order byte and then the higher order byte of each RAM word to the character buffer and checksum register. The RAM address register, on the other hand, is only incremented once during the two NPR cycles since the RAM address register contains a RAM word address and each bus cycle is performed to transfer one byte only to the character buffer and checksum generator. Therefore, a total of 512 NPRs are required to fully load the RAM (256 words × 2 bytes/word × 1 NPR/byte = 512 NPRs).

From this point on, words are loaded from main memory into the translation RAM, one at a time, as previously described. The loading of words continues until the byte counter overflows (goes to zero). When this happens, the DONE bit is set to a 1, no further NPRs are requested, the GO flip-flop is cleared, and a bus interrupt is sent to the processor by the assertion of UBUS BR4. The processor responds by asserting UBUS BG4 IN, indicating that use of the bus has been granted for an interrupt. The controller responds by asserting UBUS SACK, thereby acknowledging receipt of the bus grant. The processor, in turn, responds to UBUS SACK by removing UBUS BG4 IN. When the bus becomes idle, the controller sets the BG BBSY flip-flop, which asserts UBUS BBSY. At this time, the interrupt vector address is forced onto the bus data lines.

The vector address is determined by jumpers on the M8586 module (vector address 754 for an installation with one line printer; vector addresses 754 and 750 for an installation with two line printers, No. 1 and No. 2 respectively). The vector address specifies the memory location that contains the starting address of the device routine.

The processor responds to UBUS BBSY by asserting UBUS SSYN. In effect, the controller BG BBSY flip-flop is cleared, so that UBUS INTR and the vector address lines are no longer asserted. The controller then removes UBUS BBSY. The processor responds by removing UBUS SSYN. This completes the RAM Load, and bus control is returned to the LP20 device routine in the processor.

#### 4.2.2 Loading the DAVFU (Not Applicable to LP10 Line Printers)

After the translation RAM has been loaded, it is normal procedure to initialize the LP20 Controller by a Local Initialize or Error Reset command, and then load the direct access vertical format unit (DAVFU) in the line printer. The data path module must be correctly configured for the type of VFU in use. Bit 11 of CSRB asserted indicates an optical VFU (Paragraph 2.4.2.1).

The steps in setting up the controller for DAVFU Load are identical to those for RAM Load except that the DAVFU Load flip-flop is set and the Test Mode flip-flop is cleared. The bus address register and byte counter are loaded and the GO bit is set as before.

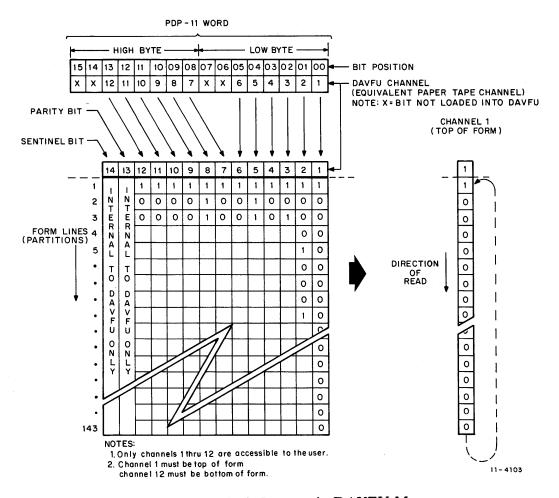

The value loaded in the byte counter depends on the maximum number of lines in a complete form (Figure 4-2). For example, an 11-inch form, at 6 lines per inch, is 66 lines long from one Top-Of-Form position to the next. Each line is represented by a bit position in all DAVFU channels. That is, there is one bit position per line in each channel. Bits from each channel that correspond to the same line are referred to as a DAVFU partition. Hence, a 66-line format has 66 partitions of one bit per line per channel each.

Figure 4-2 Typical Bit Patterns in DAVFU Memory

The bytes to be loaded are always preceded by a start code of 356 and terminated by a stop code of 357.\* It is normal procedure to write the program so that the byte counter overflows when a stop code is sent to the printer. Consider the case where the printer is to handle an 11-in. (27.94-cm) form, with a total of 66 lines at a setting of 6 lines per inch by means of the 6LPI switch on the printer. Since two bytes (characters) are loaded per DAVFU partition, the total number of bytes is  $2 \times 66$ , or 132. A DAVFU start code of 356 and a DAVFU stop code of 357 bring the total byte count to  $134_{10}$  or  $206_8$ . (The two's complement of  $134_{10}$  is  $7572_8$ , and this is the octal number loaded into the byte counter.)

When the bus address register and the byte counter have been set up, control flip-flops in control and status register A (CSRA) are set to establish the conditions for Interrupt Enable, Parity Enable, and DAVFU Load. The Test Mode flip-flop is not asserted so that incoming characters will be routed to the printer DAVFU.

The next step is to set the GO flip-flop in CSRA to the one state. The contents of the checksum register are destroyed when GO is set.

With the GO flip-flop set and the printer DEMAND line asserted, the controller will perform a non-processor request (NPR). This NPR indicates that the controller is requesting use of the bus for a DATI transfer.

Assuming that the NPR is completed, the first byte of data from main memory is clocked into the character buffer. The byte loaded is selected by bit 00 of the bus address register. The eight bits constitute one of the bytes of the data word on the bus, which in this case is the DAVFU start code (356<sub>8</sub>). The same eight bits are added to the binary sum currently in the checksum hold register.

At the appropriate clock time, the output of the character buffer is loaded into the RAM address register. This 8-bit byte is also applied to the data multiplexer and to the printer multiplexer. Reading of RAM control bits is disabled during DAVFU Load so no translation can occur and the output of the RAM address register (i.e., the DAVFU start code) is applied to the printer multiplexer. The least significant seven bits of the start code are then routed from the printer multiplexer to the line printer as LPT DATA (08:01). The LPT paper instruction is also asserted, causing the start code to be applied to the printer and initiating the DAVFU Load cycle.

The eight bits from the RAM address register are also applied to a parity generator in the printer multiplexer. The DAVFU start code has an even number of 1s, so LPT DATA PARITY is asserted.

Following checksum, both the bus address register and the byte counter are incremented by one. Shortly thereafter, the controller NPG BBSY flip-flop is cleared, negating UBUS BBSY. At this point, the LP20 relinquishes control of the bus.

When the LP20 relinquishes control of the bus, the Data Strobe flip-flop in the LPT interface is asserted. Since the controller is not in the Test mode, a data strobe is sent to the printer, thereby strobing in DAVFU start code 356. At the same time, a Demand Timeout test is activated, during which the printer must remove its DEMAND signal and cause the Data Strobe flip-flop to be cleared. If the printer fails to remove DEMAND before the end of the Demand Timeout test, the error flag is set and the controller halts. When the printer DEMAND signal is again asserted, NPR SET and UBUS NPR are asserted, indicating that the LP20 is requesting use of the bus for another DATI transfer.

<sup>\*</sup>See Section 4.5 for DAVFU details.