# RH20 MASSBUS CONTROLLER UNIT DESCRIPTION

The drawings and specifications herein are the property of Digital Equipment Corporation and shall not be reproduced or copied or used in whole or in part as the basis for the manufacture or sale of equipment described herein without written permission.

Copyright © 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

# **CONTENTS**

|           | Page                                          |

|-----------|-----------------------------------------------|

| SECTION 1 | OVERVIEW                                      |

| 1.1       | INTRODUCTION                                  |

| 1.2       | PHYSICAL DESCRIPTION                          |

| 1.3       | OPERATING CHARACTERISTICS                     |

|           |                                               |

| SECTION 2 | FUNCTIONAL DESCRIPTION                        |

| 2.1       | SYSTEM INTERFACE                              |

| 2.1.1     | EBus                                          |

| 2.1.2     | Massbus                                       |

| 2.1.3     | CBus                                          |

| 2.2       | DATA CHANNEL RESET AND LOGOUT AREAS 2-15      |

| 2.3       | INTERNAL/EXTERNAL REGISTERS                   |

| 2.4       | DRIVE COMMANDS                                |

| 2.5       | RH20 INSTRUCTION SET                          |

| 2.5.1     | CONO                                          |

| 2.5.2     | CONI                                          |

| 2.5.3     | DATAO                                         |

| 2.5.3.1   | Preparation Register Data                     |

| 2.5.3.2   | External Register (RS = $00-37_8$ ) Data 2-25 |

| 2.5.3.3   | SBAR (RS = 70) Data                           |

| 2.5.3.4   | STCR (RS = 71) Data                           |

| 2.5.3.5   | IVIR (RS = 74) Data                           |

| 2.5.3.6   | WR (RS = 76) Data                             |

| 2.5.3.7   | DCR (RS = 77) Data                            |

| 2.5.4     | DATAI                                         |

| 2.5.4.1   | External Register (RS = $00-37_8$ ) Data 2-28 |

| 2.5.4.2   | SBAR (RS = 70) and PBAR (RS = 72) Data 2-30   |

| 2.5.4.3   | STCR (RS = 71) and PTCR (RS = 73) Data 2-30   |

| 2.5.4.4   | IVIR (RS = 74) Data 2-30                      |

| 2.5.4.5   | RR (RS = 75) Data 2-30                        |

| 2.6       | CHANNEL COMMANDS                              |

| 2.7       | CHANNEL STATUS                                |

| 2.7.1     | Status Word 1                                 |

| 2.7.2     | Status Word 2                                 |

| 2.8       | PROGRAMMING THE RH20                          |

| 2.8.1     | Control Data Write/Read                       |

| 2.8.2     | Register Write/Read                           |

| 2.8.3     | Write/Read Data Transfer                      |

| SECTION 3 | LOGIC DESCRIPTION                             |

| 3.1       | ASYNCHRONOUS DATA TRANSFER CONTROL LOGIC      |

| 3.1.1     | EBus Function Decoder and Address Comparators |

| 3.1.2     | EBI Time-State Generator                      |

# **CONTENTS** (Cont)

Page

| 3.1.3                                                             | Control Data Load (CONO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-3                                                                |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 3.1.4                                                             | Control Status Read (CONI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 3.1.5                                                             | Register Data Load (DATAO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 3.1.6                                                             | Register Data Read (DATAI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 3.1.7                                                             | PI Request Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| 3.1.8                                                             | PI Operation (PI SERVED and PI ADR IN)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    |

| 3.1.9                                                             | Command File Operation and Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| 3.1.10                                                            | Massbus (Control Bus) Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| 3.1.11                                                            | Massbus Control Data Parity Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

| 3.2                                                               | SYNCHRONOUS DATA TRANSFER CONTROL LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                    |

| 3.2.1                                                             | CBI Clock Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |

| 3.2.2                                                             | Block Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |

| 3.2.3                                                             | Data Buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |

| 3.2.4                                                             | Data Transfer Startup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                    |

| 3.2.5                                                             | Write Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |

| 3.2.6                                                             | Read Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| 3.2.7                                                             | Normal Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                    |

| 3.2.8                                                             | Transfer Error Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

| 3.3                                                               | DIAGNOSTIC DATA TRANSFER CONTROL LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                 |

| 3.3.1                                                             | Diagnostic Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| 3.3.2                                                             | Asynchronous Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| 3.3.3                                                             | Synchronous Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |

| 3.3.3                                                             | Synchronous Data Transier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                                                                 |

|                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |

| APPENDIX A                                                        | ABBREVIATIONS AND MNEMONICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| APPENDIX A                                                        | ABBREVIATIONS AND MNEMONICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |

| APPENDIX A                                                        | ABBREVIATIONS AND MNEMONICS  ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |

| APPENDIX A Figure No.                                             | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ıge                                                                |

| Figure No.                                                        | ILLUSTRATIONS  Title Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                  |

| Figure No.                                                        | ILLUSTRATIONS  Title Pa  RH20 System Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1                                                                 |

| <b>Figure No.</b> 1-1 1-2                                         | ILLUSTRATIONS  Title Pa  RH20 System Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1<br>-2                                                           |

| Figure No. 1-1 1-2 2-1                                            | ILLUSTRATIONS  Title Pa  RH20 System Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1<br>-2<br>2-2                                                    |

| Figure No. 1-1 1-2 2-1 2-2                                        | ILLUSTRATIONS  Title Pa  RH20 System Interconnection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1<br> -2<br> 2-2<br> 2-3                                          |

| Figure No.  1-1 1-2 2-1 2-2 2-3                                   | ILLUSTRATIONS  Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1-1<br>1-2<br>2-2<br>2-3<br>2-3                                    |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4                               | ILLUSTRATIONS  Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-1<br>1-2<br>2-2<br>2-3<br>2-3<br>2-5                             |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5                           | ILLUSTRATIONS  Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2 RH20 API Function Word Format 2                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-1<br>1-2<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5                      |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6                       | ILLUSTRATIONS  Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2 RH20 API Function Word Format 2 PI SERVED/PI ADR IN Operation 2                                                                                                                                                                                                                                                                                                                                                                                               | 1-1<br>1-2<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6               |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7                   | Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2 RH20 API Function Word Format 2 PI SERVED/PI ADR IN Operation 2 Massbus Interface 2                                                                                                                                                                                                                                                                                                                                                                                          | 1-1<br>1-2<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-8        |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8               | Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2 RH20 API Function Word Format 2 PI SERVED/PI ADR IN Operation 2 Massbus Interface 2 Control Bus Write Operation 2                                                                                                                                                                                                                                                                                                                                                            | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-8<br>2-9        |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9           | Title Pa  RH20 System Interconnection 1 RH20 Module Utilization 1 RH20/Drive Functional Block Diagram 2 EBus Interface 2 CONO/DATAO Operation 2 CONI/DATAI Operation 2 RH20 API Function Word Format 2 PI SERVED/PI ADR IN Operation 2 Massbus Interface 2 Control Bus Write Operation 2 Control Bus Read Operation 2                                                                                                                                                                                                                                                                                                                               | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-8<br>2-9        |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10      | ILLUSTRATIONS           Title         Pa           RH20 System Interconnection         1           RH20 Module Utilization         1           RH20/Drive Functional Block Diagram         2           EBus Interface         2           CONO/DATAO Operation         2           CONI/DATAI Operation         2           RH20 API Function Word Format         2           PI SERVED/PI ADR IN Operation         2           Massbus Interface         2           Control Bus Write Operation         2           Control Bus Read Operation         2           Data Bus Write Operation         2                                             | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-8<br>2-9<br>2-9 |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10 2-11 | ILLUSTRATIONS           Title         Pa           RH20 System Interconnection         1           RH20 Module Utilization         1           RH20/Drive Functional Block Diagram         2           EBus Interface         2           CONO/DATAO Operation         2           CONI/DATAI Operation         2           RH20 API Function Word Format         2           PI SERVED/PI ADR IN Operation         2           Massbus Interface         2           Control Bus Write Operation         2           Control Bus Read Operation         2           Data Bus Write Operation         2           Data Bus Read Operation         2 | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-8<br>2-9<br>10  |

| Figure No.  1-1 1-2 2-1 2-2 2-3 2-4 2-5 2-6 2-7 2-8 2-9 2-10      | ILLUSTRATIONS           Title         Pa           RH20 System Interconnection         1           RH20 Module Utilization         1           RH20/Drive Functional Block Diagram         2           EBus Interface         2           CONO/DATAO Operation         2           CONI/DATAI Operation         2           RH20 API Function Word Format         2           PI SERVED/PI ADR IN Operation         2           Massbus Interface         2           Control Bus Write Operation         2           Control Bus Read Operation         2           Data Bus Write Operation         2                                             | 2-1<br>2-2<br>2-3<br>2-3<br>2-5<br>2-5<br>2-6<br>2-9<br>2-9<br>10  |

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                 | Page |

|------------|---------------------------------------|------|

| 2-14       | CBus Operation                        |      |

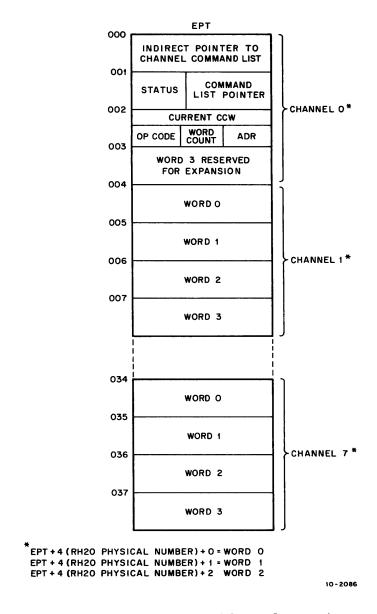

| 2-15       | Channel Reset and Status Logout Area  | 2-17 |

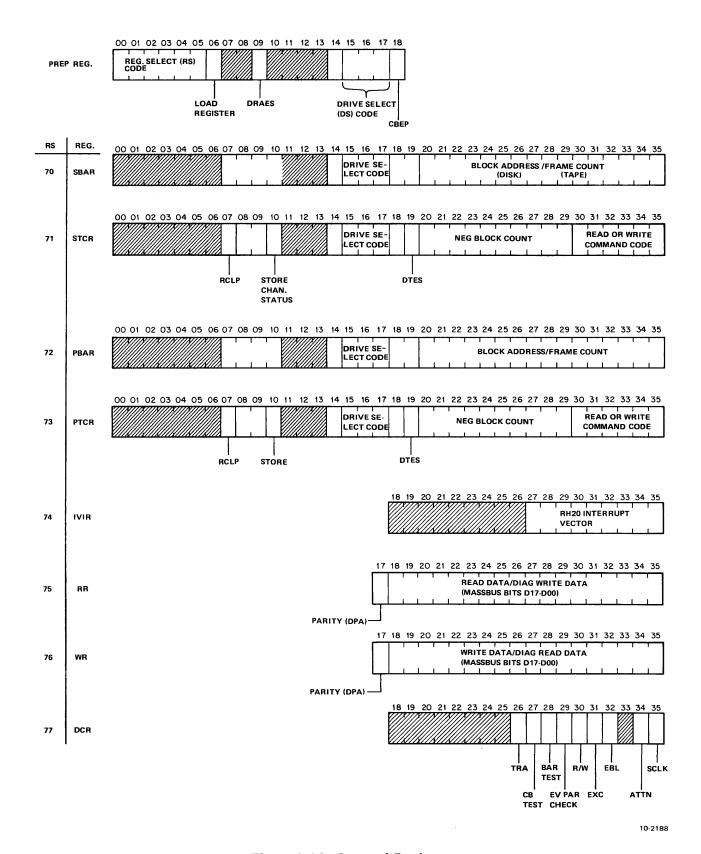

| 2-16       | Internal Registers                    | 2-18 |

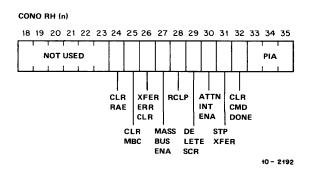

| 2-17       | CONO Command Format                   | 2-22 |

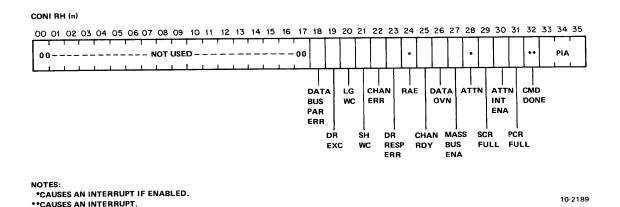

| 2-18       | CONI Command Format                   | 2-23 |

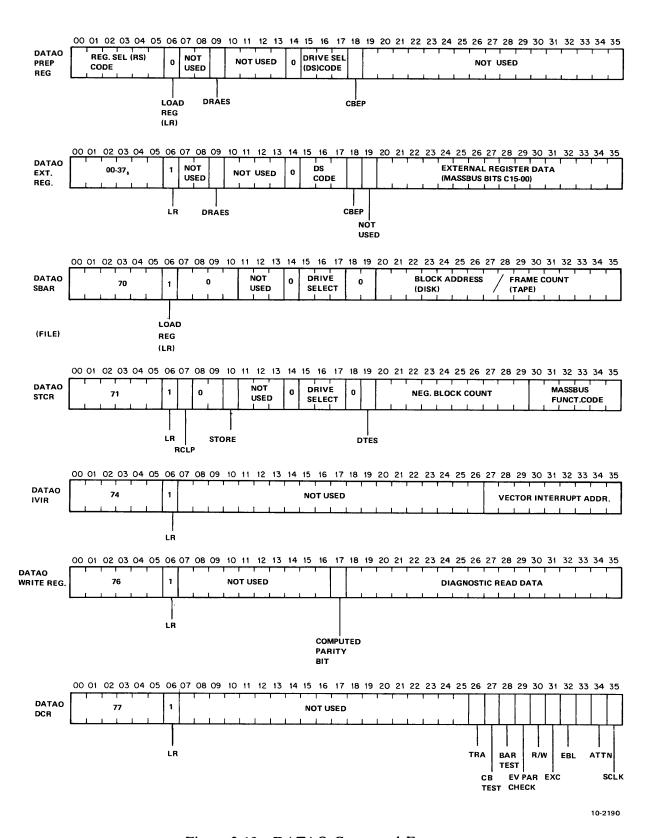

| 2-19       | DATAO Command Format                  | 2-26 |

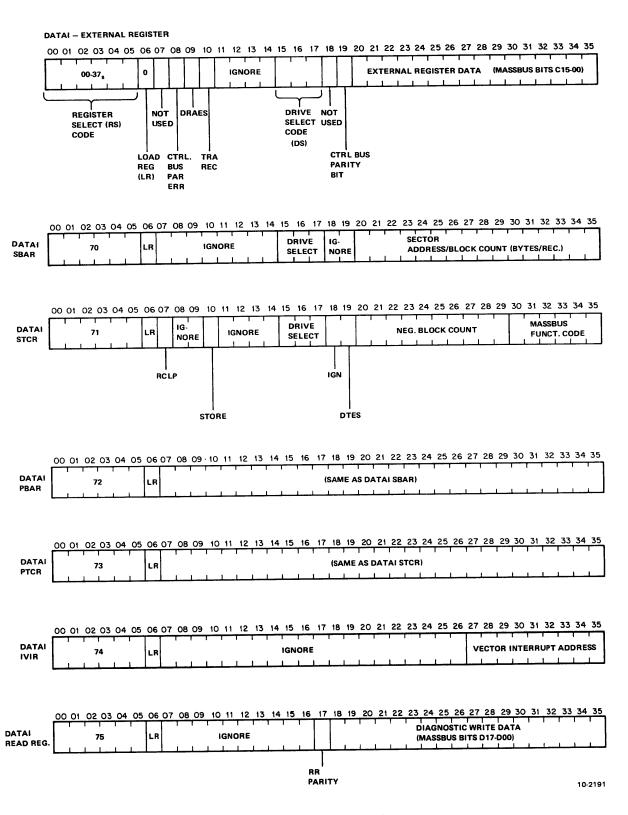

| 2-20       | DATAI Command Format                  | 2-29 |

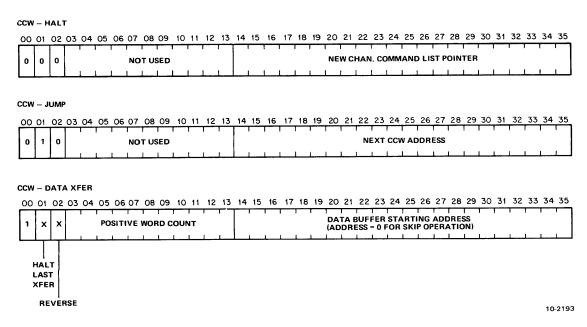

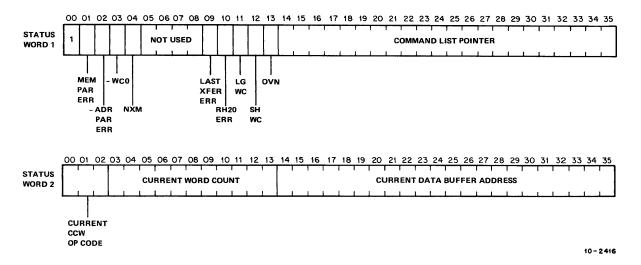

| 2-21       | Channel Command Word Format           | 2-31 |

| 2-22       | Channel Status Word Format            | 2-32 |

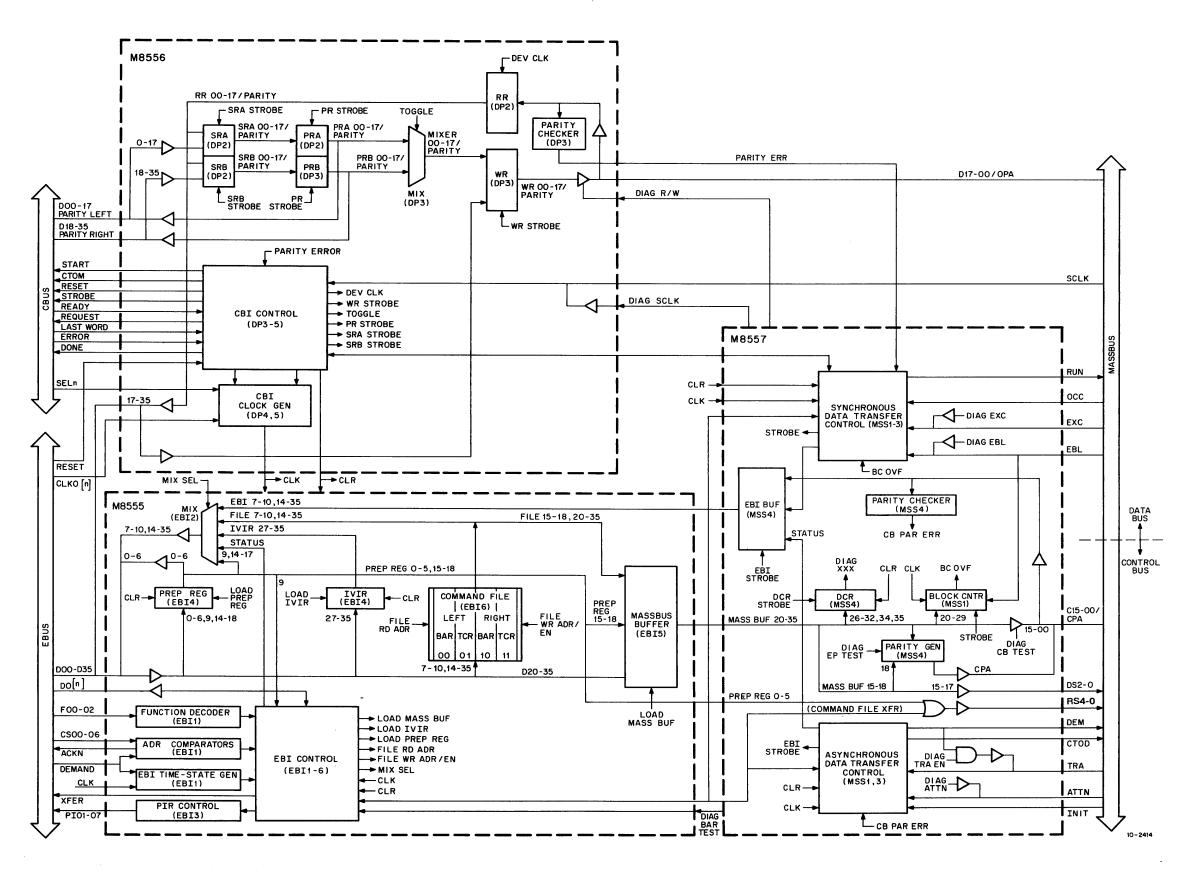

| 3-1        | RH20 Detailed Block Diagram           | 3-2  |

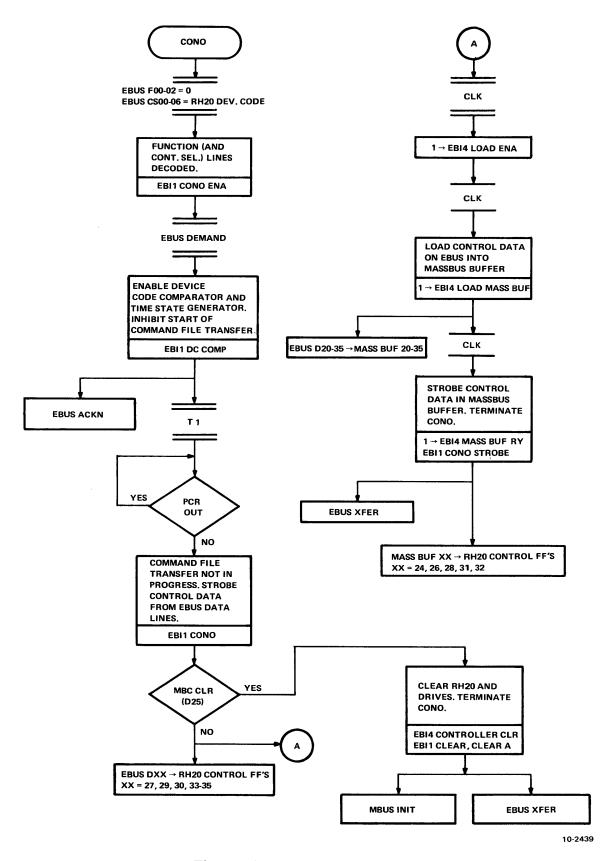

| 3-2        | CONO Flow Diagram                     | 3-4  |

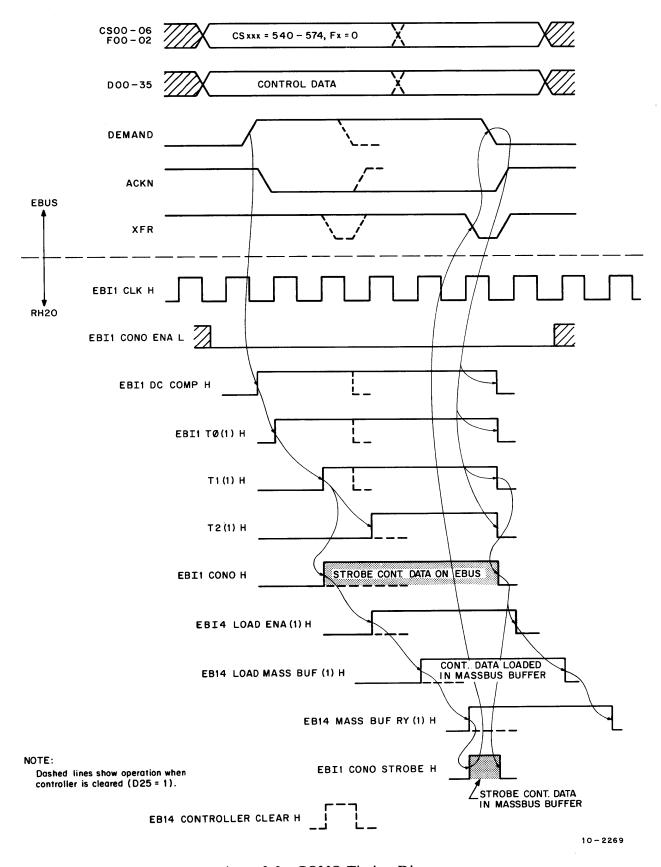

| 3-3        | CONO Timing Diagram                   | 3-5  |

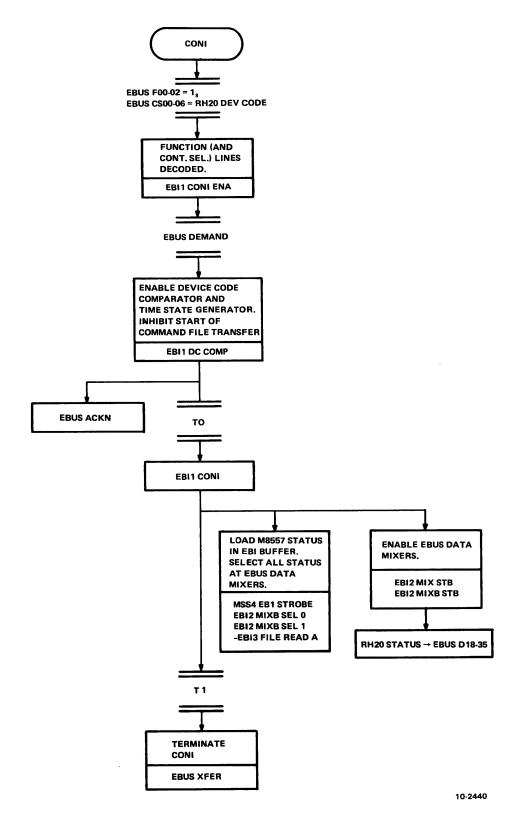

| 3-4        | CONI Flow Diagram                     |      |

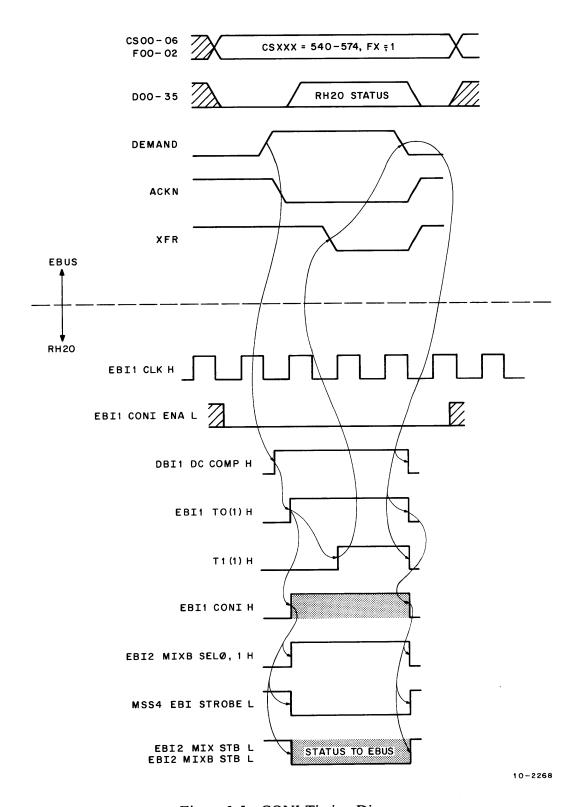

| 3-5        | CONI Timing Diagram                   |      |

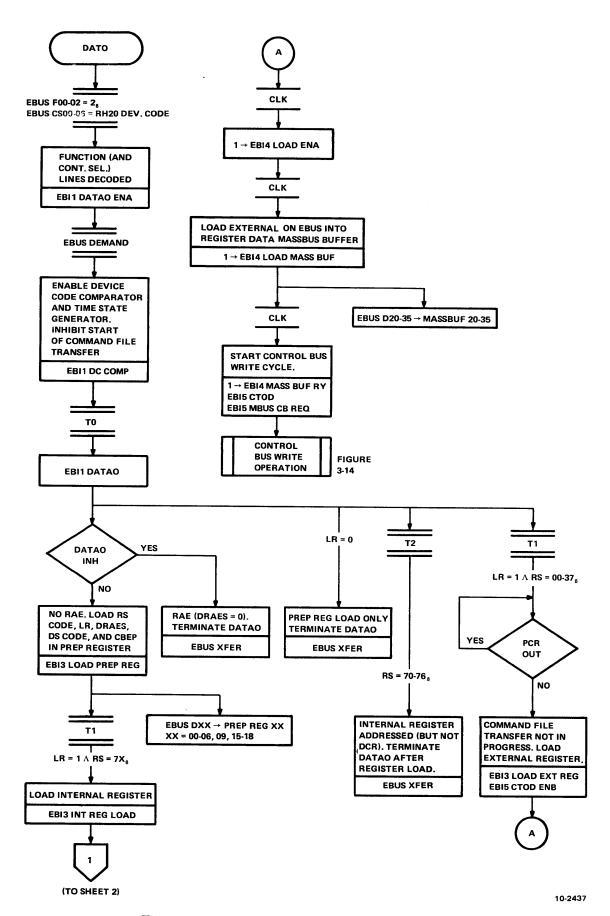

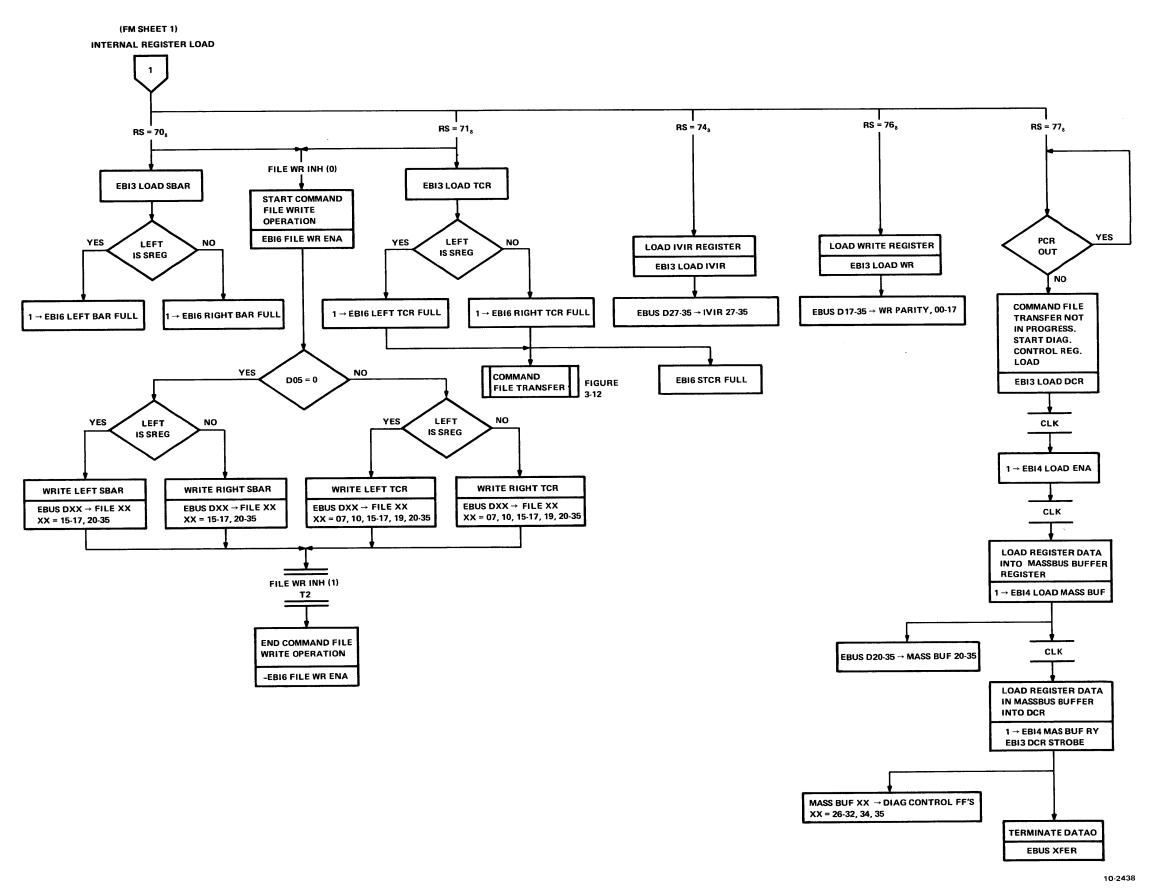

| 3-6        | DATAO Flow Diagram                    |      |

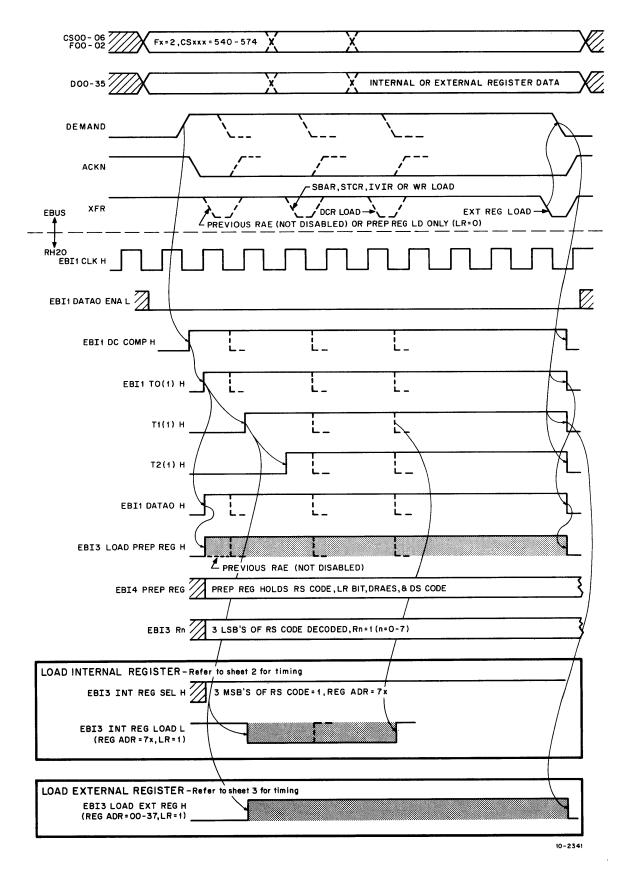

| 3-7        | DATAO Timing Diagram                  |      |

| 3-8        | DATAI Flow Diagram                    |      |

| 3-9        | DATAI Timing Diagram                  | 3-19 |

| 3-10       | PI SERVED/PI ADR IN Flow Diagram      |      |

| 3-11       | PI SERVED/PI ADR IN Timing Diagram    |      |

| 3-12       | Command File Transfer Flow Diagram    | 3-29 |

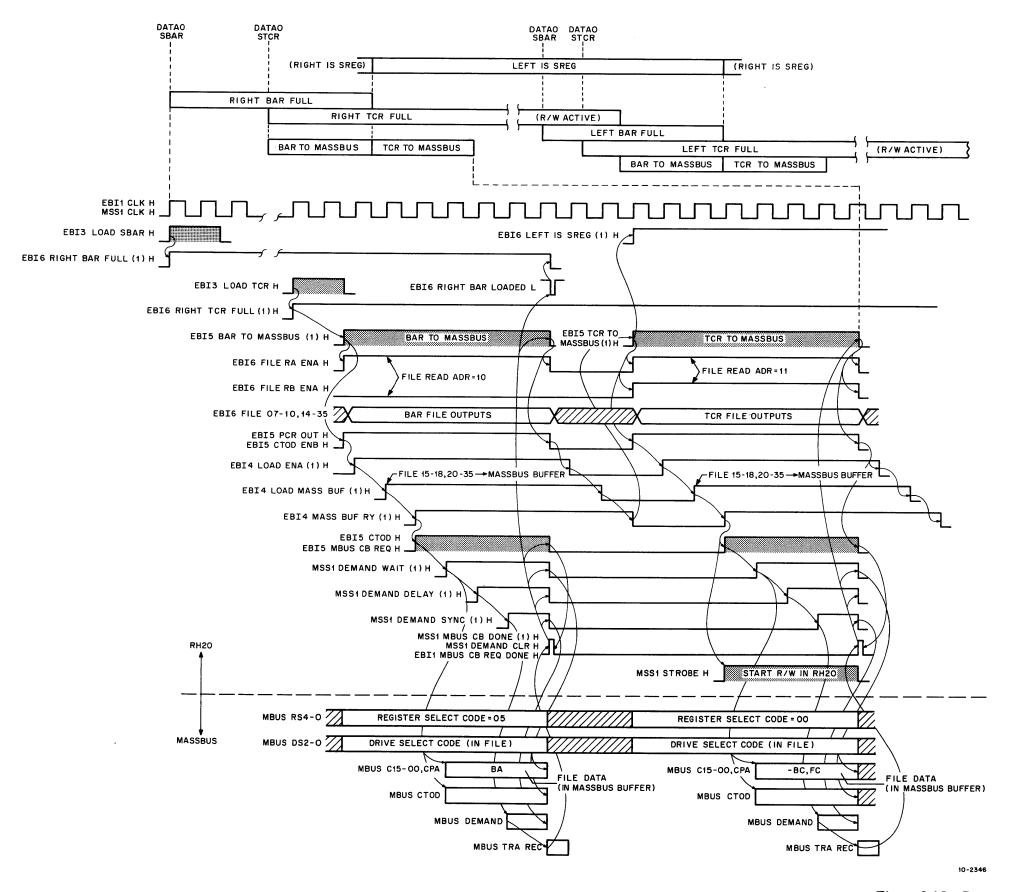

| 3-13       | Command File Transfer Timing Diagram  | 3-30 |

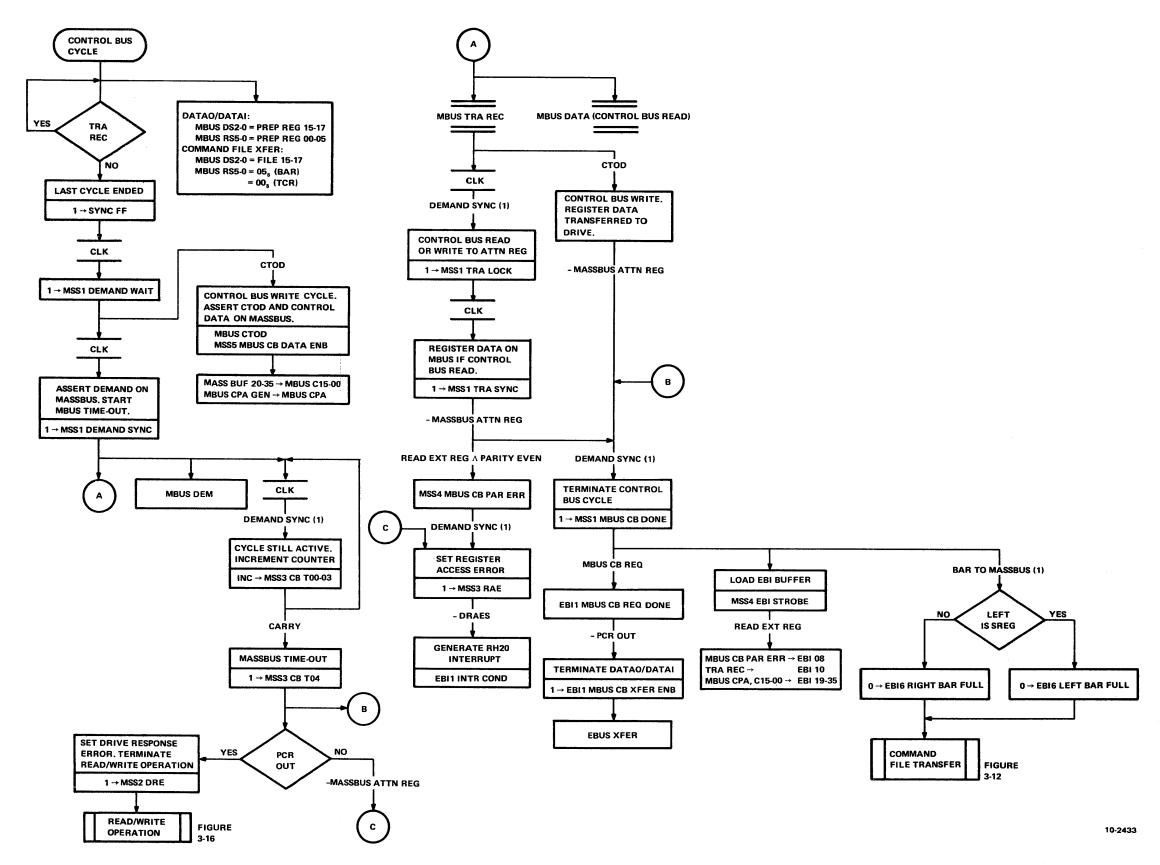

| 3-14       | Control Bus Cycle Flow Diagram        | 3-34 |

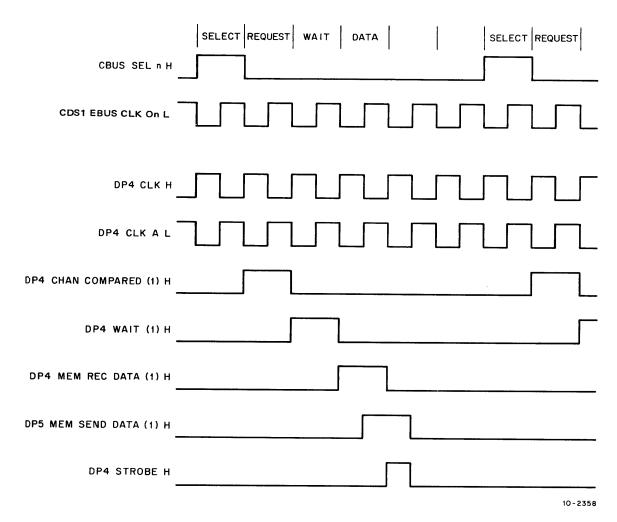

| 3-15       | CBI Clock Control Timing Diagram      |      |

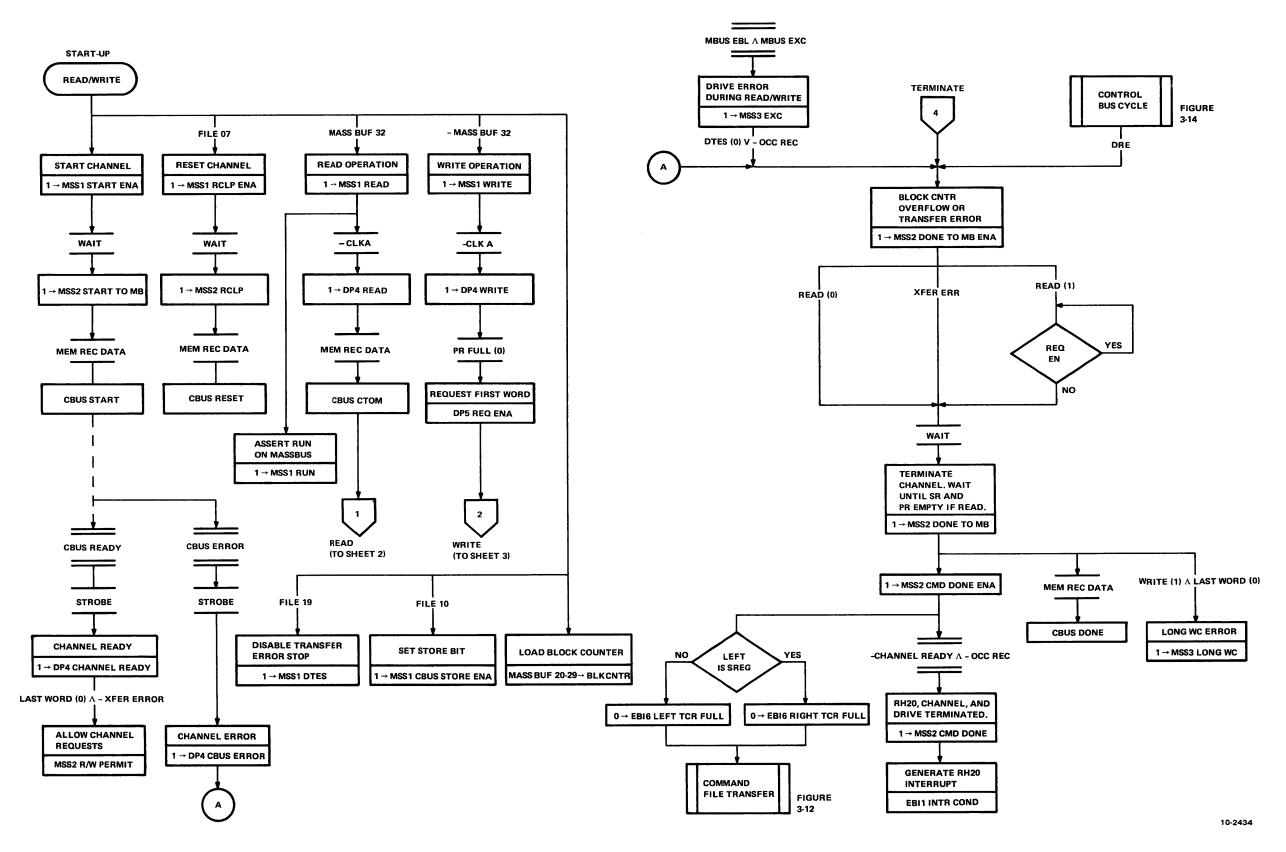

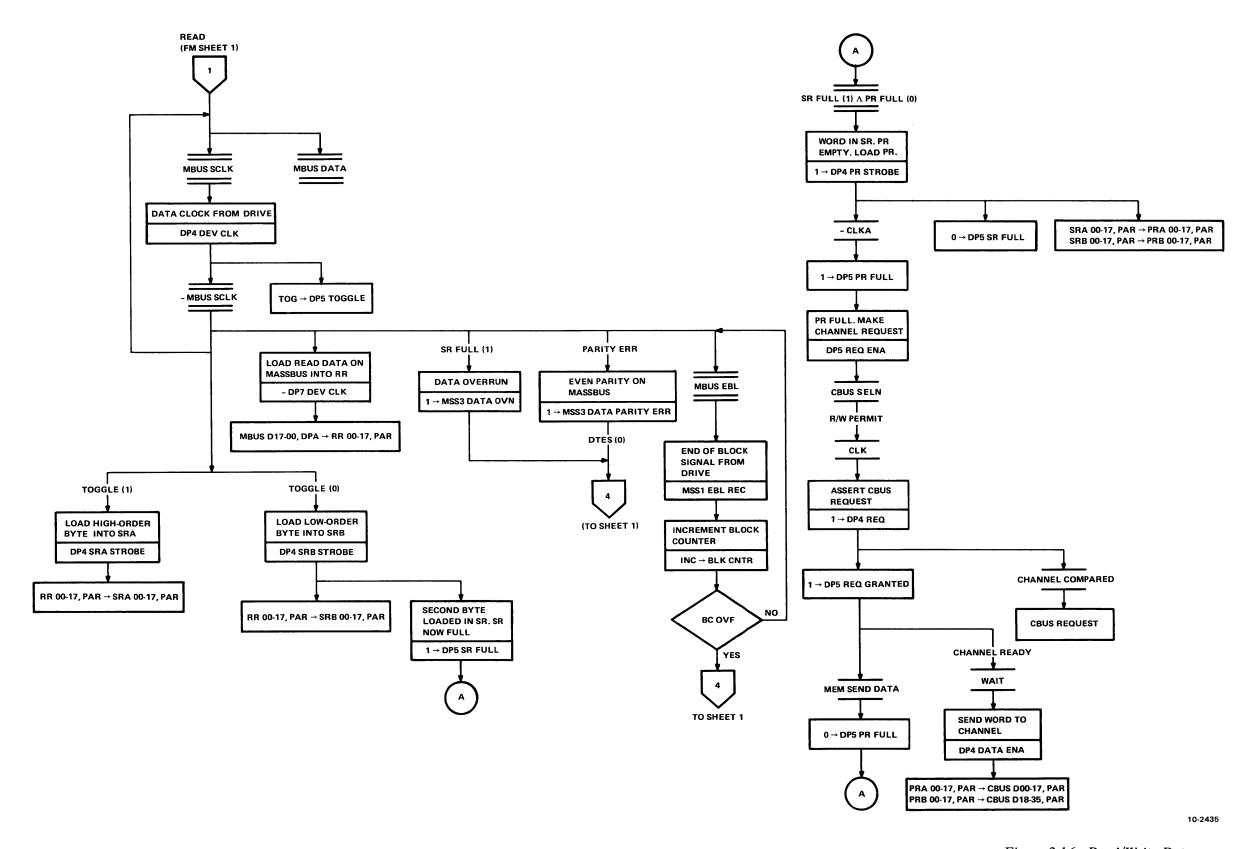

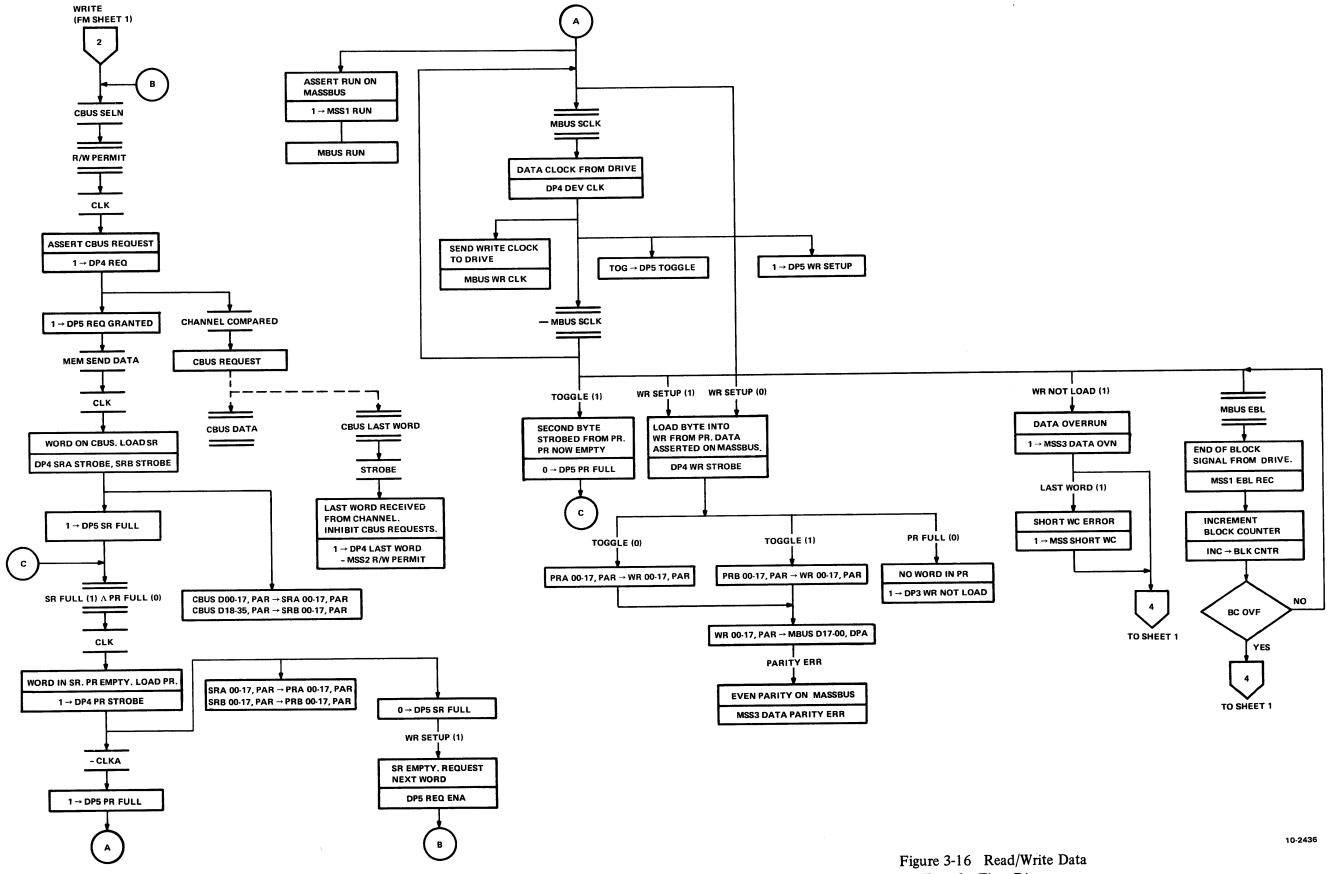

| 3-16       | Read/Write Data Transfer Flow Diagram | 3-40 |

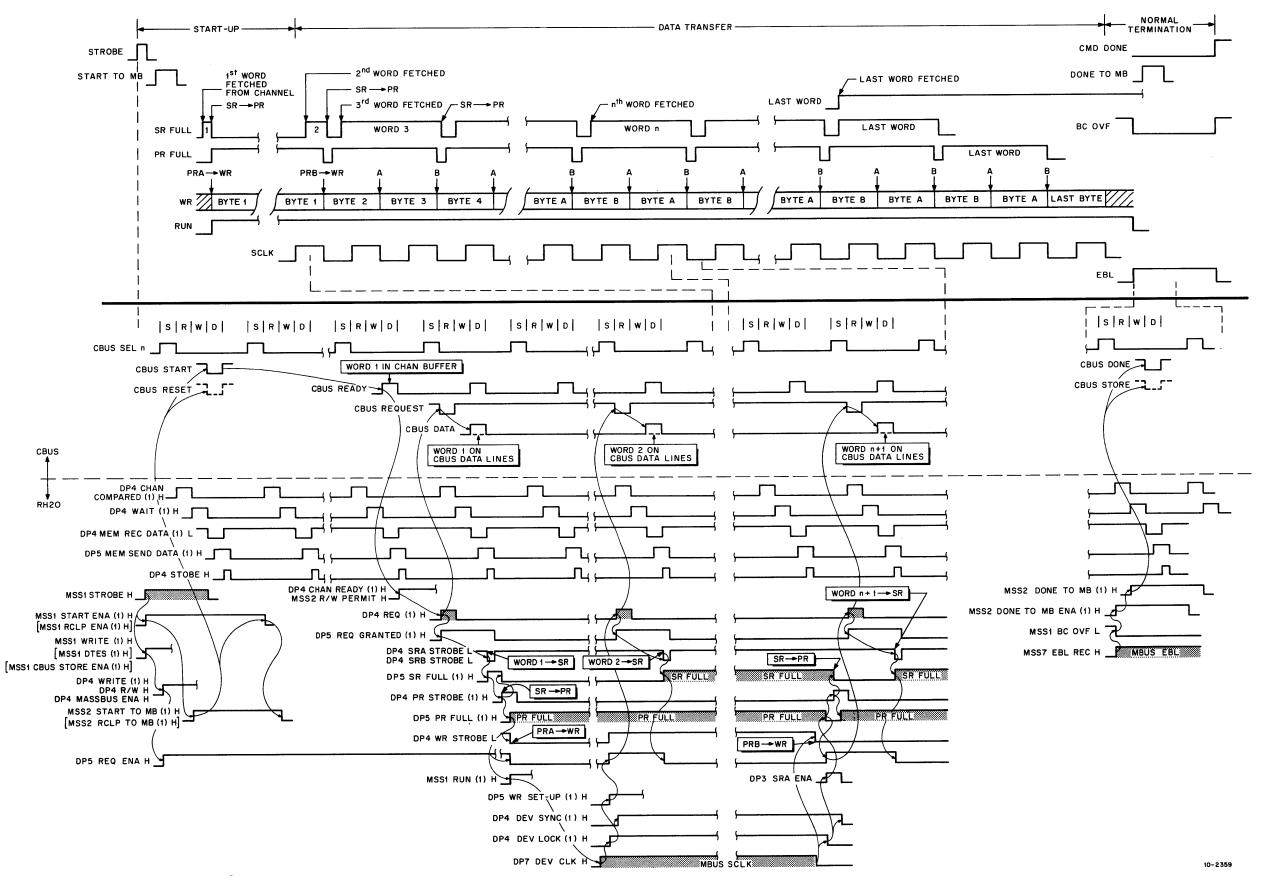

| 3-17       | Write Data Transfer Timing Diagram    | 3-44 |

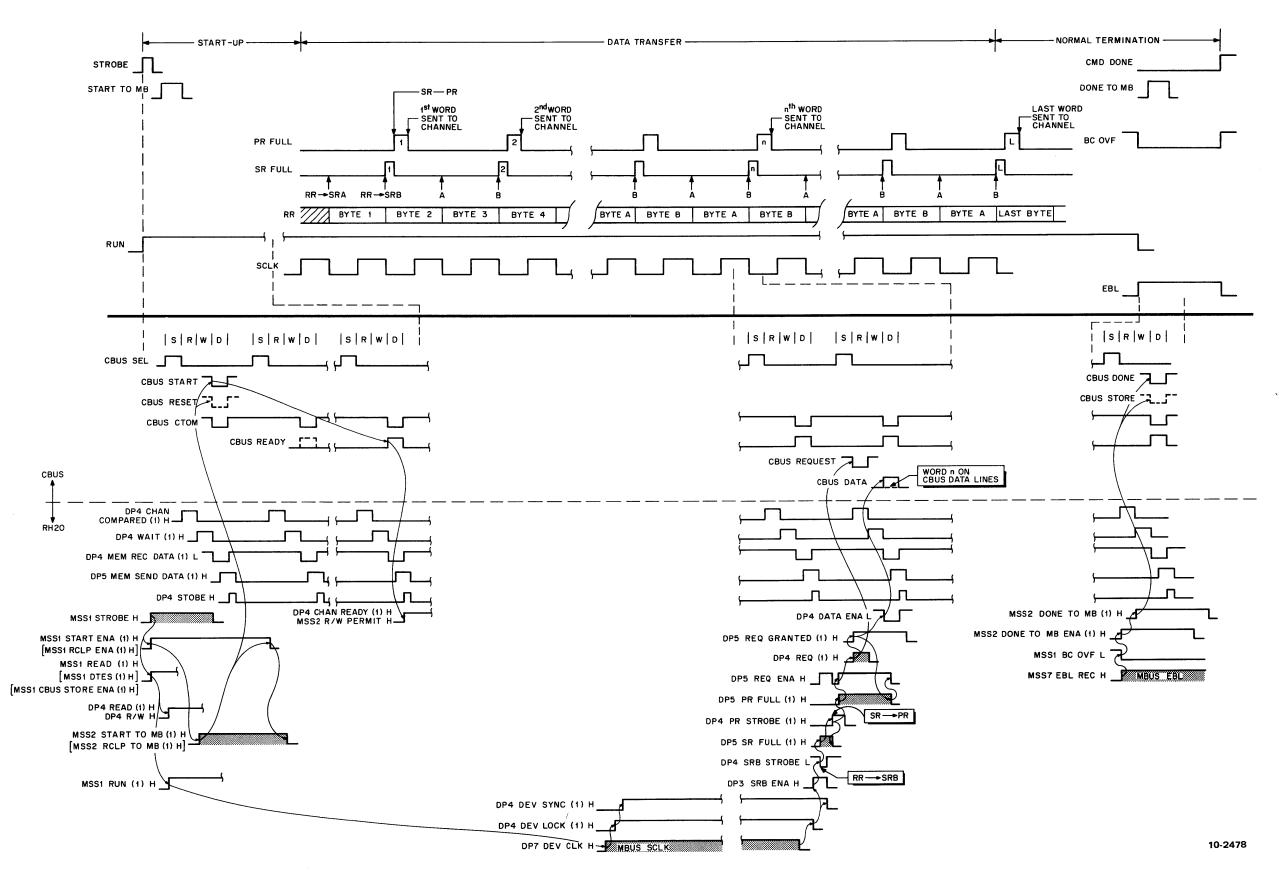

| 3-18       | Read Data Transfer Timing Diagram     | 3-46 |

|            | TABLES                                |      |

| Table No.  | Title                                 | Page |

| 1-1        | RH20 Device/Physical Select Codes     |      |

| 2-1        | EBus Signal Description               |      |

| 2-2        | Massbus Signal Descriptions           | 2-6  |

| 2-3        | CBus Signal Descriptions              | 2-11 |

| 2-4        | Internal Register Summary             | 2-19 |

| 2-5        | External Register Summary             | 2-20 |

| 2-6        | Drive Commands                        |      |

| 3-1        | Command File Locations                | 3-26 |

| 3-2        | RH20 Errors Caused By Channel Errors  | 3-50 |

# **PREFACE**

The RH20 Unit Description contains three levels of description:

- 1. Overview

- 2. Function Description

- 3. Logic Description

The Overview provides a physical description of the RH20 and describes basic operation. The Functional Description describes the RH20 system interface (EBus, CBus, Massbus), the RH20 instruction set, and the MBox channel commands. Controller and drive registers are discussed and basic programming steps are outlined. The logic description is the most comprehensive part of the RH20 Unit Description. With the aid of flowcharts and timing diagrams, RH20 operation is described in terms of its basic logic elements. Print prefixes are also used, thus providing a direct index into the Field Maintenance Print Set.

#### 1.1 INTRODUCTION

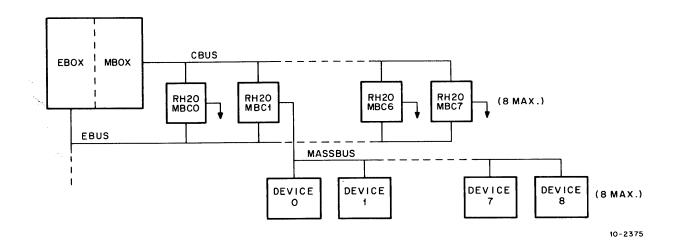

The RH20 Massbus Controller (MBC) provides a high-speed synchronous data transfer interface between any of up to eight Massbus-compatible devices (disk-pack drives, tape drives, etc.) and one of eight data channels located in the system MBox. It also allows asynchronous data transfers to/from device registers. Figure 1-1 shows interconnection of the RH20 in a system.

Figure 1-1 RH20 System Interconnection

Data is transferred between the RH20 and the associated data channel over the CBus. Asynchronous control of the RH20 is exercised by the EBox over the EBus. The Massbus connection provides an interface to both single- and dual-ported drives. Up to eight MBCs can be installed in a single processor system and two or more MBCs can transfer data simultaneously over the multiplexed CBus.

#### 1.2 PHYSICAL DESCRIPTION

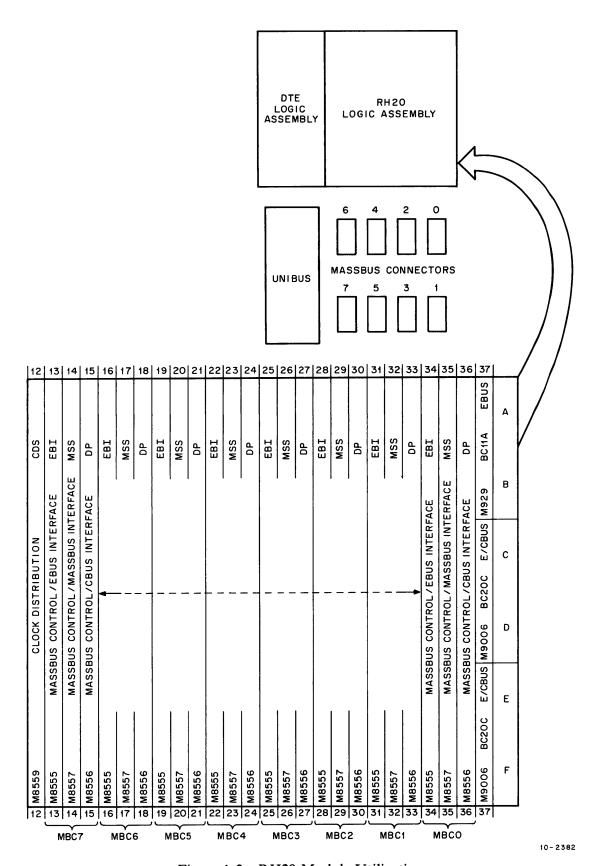

The RH20 consists of three double-height hexboards (one M8555, one M8556, and one M8557) that are located in the system I/O cabinet. Twenty-four slots are allocated to provide space for eight MBCs. The Massbus cable connector slots for each RH20 are physically located on a (cable connector) PC board beneath each of the corresponding MBC locations (MBC0, MBC1, MBC2, etc.) and are provided with ZIF (zero-insertion-force) connectors which will accept either a BC06S round device cable or a special Massbus terminator. Using a bus terminator instead of a device cable at an MBC cable connector permits diagnostic loop operations to be performed on the Massbus with all devices disconnected. A connector is provided for each MBC, allowing eight separate chains of Massbus devices to be connected. The EBus and CBus cable connections are made through module slots in the backplane and are interconnected with the system by means of cables within the I/O cabinet. RH20 module utilization and Massbus connector locations are shown in Figure 1-2.

Figure 1-2 RH20 Module Utilization

## 1.3 OPERATING CHARACTERISTICS

For addressing purposes, each RH20 has been assigned a unique device code and physical number. Both addresses are dependent upon the physical location of the RH20 and are hardwired on the backplane. CONO, DATAO, CONI, and DATAI commands address the RH20 by device code. The physical address is used during execution of the PI ADR IN command. Table 1-1 lists the device codes and physical numbers assigned to each controller.

Although each R H20 controls up to eight drives in parallel on the Massbus, only one drive at a time can transfer data. However, non-data transfer commands (Seek, Rewind, etc.) can be issued when a data transfer is active, provided that the addressed drive is not executing the read/write.

Table 1-1 RH20 Device/Physical Select Codes

| Controller | Device Code<br>(Octal) | Symbol | Physical<br>Number |

|------------|------------------------|--------|--------------------|

| 1st        | 540                    | MBC0   | 0                  |

| 2nd        | 544                    | MBC1   | 1                  |

| 3rd        | 550                    | MBC2   | 2                  |

| 4th        | 554                    | MBC3   | 3                  |

| 5th        | 560                    | MBC4   | 4                  |

| 6th        | 564                    | MBC5   | 5                  |

| 7th        | 570                    | MBC6   | 6                  |

| 8th        | 574                    | MBC7   | 7                  |

# SECTION 2 FUNCTIONAL DESCRIPTION

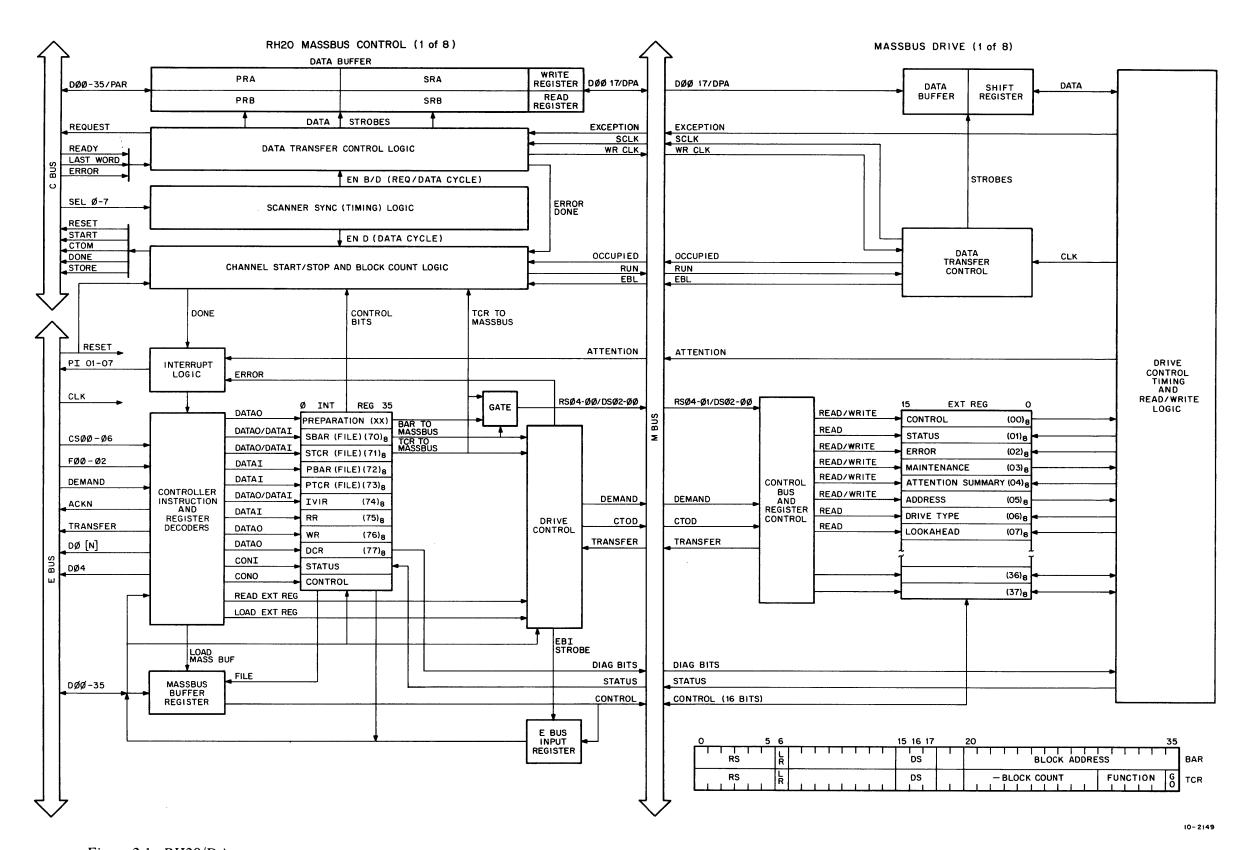

A simplified functional block diagram of the RH20 and a Massbus device is shown in Figure 2-1. The system interface and the addressable registers in both the controller and a typical device are indicated.

#### 2.1 SYSTEM INTERFACE

The RH20 interfaces to the EBus, Massbus, and CBus. A general discussion of bus operation follows. A tabulated signal summary for each bus is provided.

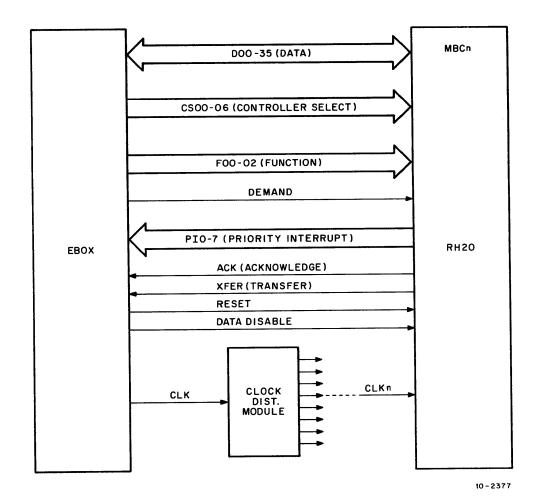

#### 2.1.1 EBus

The EBus interconnects all peripheral device controllers, including the RH20, with the system EBox. EBus commands transfer control data to the RH20 (CONO/DATAO), transfer control status information from the RH20 (CONI/DATAI), and service RH20 interrupts (PI SERVED/PI ADR IN). EBus interface signals and information flow are shown in Figure 2-2. The EBus signals are described in Table 2-1.

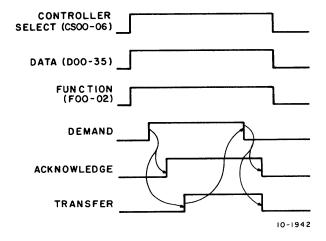

During a CONO or DATAO command, the EBox places the device code on the CS lines, the control data on the data lines, and asserts a 0 or 2<sub>8</sub> (CONO/DATAO) on the F lines. The EBox then allows a deskew and decode delay time, and asserts DEMAND. The RH20 decodes the F and CS lines. If the device code matches its hard-wired address when DEMAND is received, the controller asserts ACKN, strobes the control data from the EBus, and executes the command by performing the specified control function (CONO) or by loading the addressed register (DATAO). The addressed register can be in the RH20 (an internal register) or in a Massbus device (an external register). XFER is then asserted by the RH20 to signal that the command has been executed. After receiving XFER, the EBox negates DEMAND. The trailing edge of DEMAND negates ACKN and XFER in the RH20 to terminate bus operation. Timing is shown in Figure 2-3.

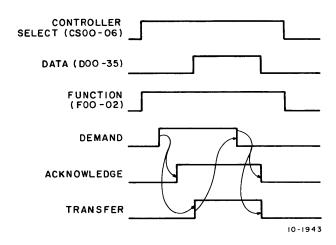

During a CONI or DATAI command, the EBox places the device code on the CS lines, asserts a 1<sub>8</sub> or 3<sub>8</sub> on the F lines (CONI/DATAI), and asserts DEMAND after a delay time that allows the RH20 to decode the CS and F lines. If addressed (i.e., CS lines match hard-wired address), and after receiving DEMAND, the controller asserts ACKN and executes the command by placing either the control status information (CONI) or the register data (DATAI) on the EBus data lines. It then asserts XFER. (Both internal and external registers can be read by the DATAI.) When the EBox receives XFER, it strobes the data lines and negates DEMAND. In the RH20, the trailing edge of DEMAND negates ACKN, XFER, and the data lines to end the operation on the EBus. Timing is shown in Figure 2-4.

Figure 2-1 RH20/Drive Functional Block Diagram

Figure 2-2 EBus Interface

Figure 2-3 CONO/DATAO Operation

Table 2-1 EBus Signal Description

| Signal                                  | Direction     | Description                                                                                                                                                                                                                                                 |  |  |

|-----------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data Lines<br>(D00-35)                  | Bidirectional | Transfer control data and status information between the EBox and the RH20.                                                                                                                                                                                 |  |  |

| Function Lines (F00–02)                 | EBox to MBC   | Specify the EBus command to be executed.                                                                                                                                                                                                                    |  |  |

|                                         |               | F00 F01 F02 Command                                                                                                                                                                                                                                         |  |  |

|                                         |               | 0 0 0 CONO                                                                                                                                                                                                                                                  |  |  |

|                                         |               | 0 0 1 CONI                                                                                                                                                                                                                                                  |  |  |

|                                         |               | 0 1 0 DATAO                                                                                                                                                                                                                                                 |  |  |

|                                         |               | 0 1 1 DATAI                                                                                                                                                                                                                                                 |  |  |

|                                         |               | 1 0 0 PI SERVED                                                                                                                                                                                                                                             |  |  |

|                                         |               | 1 0 1 PI ADR IN                                                                                                                                                                                                                                             |  |  |

| Controller Select<br>Lines<br>(CS00–06) | EBox to MBC   | CS00-06 select the RH20 by device code (Table 1-1) during a CONO, DATAO, CONI, or DATAI. CS04-06 specify the interrupting channel number during a PI SERVED (and PI ADR IN). CS00-03 select the RH20 by its physical number (Table 1-1) during a PI ADR IN. |  |  |

| DEMAND                                  | EBox to MBC   | Causes RH20 to execute command specified by F lines.                                                                                                                                                                                                        |  |  |

| Acknowledge (ACKN)                      | MBC to EBox   | Indicates RH20 has been selected and is executing EBus command. (ACKN is not asserted during PI SERVED.)                                                                                                                                                    |  |  |

| Transfer (XFER)                         | MBC to EBox   | Indicates RH20 has executed EBus command. (XFER is not asserted during PI SERVED.)                                                                                                                                                                          |  |  |

| PI Request Lines (PI01–07)              | MBC to EBox   | Signals an RH20 interrupt. The line asserted depends on the PI channel assignment (PIA) loaded in the RH20 by a CONO.                                                                                                                                       |  |  |

| DATA DISABLE                            | EBox to MBC   | Disables EBus data line transmitters in RH20. (Asserted to allow transfer of diagnostic control data over the data lines during diagnostic operations.)                                                                                                     |  |  |

| RESET                                   | EBox to MBC   | Initializes RH20 and asserts INIT on Massbus to initialize Massbus devices connected to RH20.                                                                                                                                                               |  |  |

| Clock<br>(CLK n)                        | EBox to MBC   | Sequences RH20 Control logic. CLK n connects to MBC n (n = $00-07$ ) from clock distribution module, where it is adjusted to synchronize RH20 and MBox channel operation.                                                                                   |  |  |

Figure 2-4 CONI/DATAI Operation

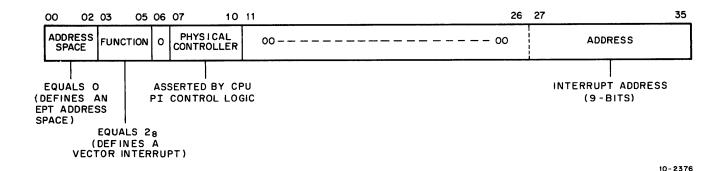

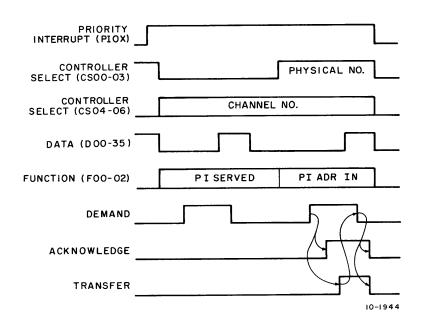

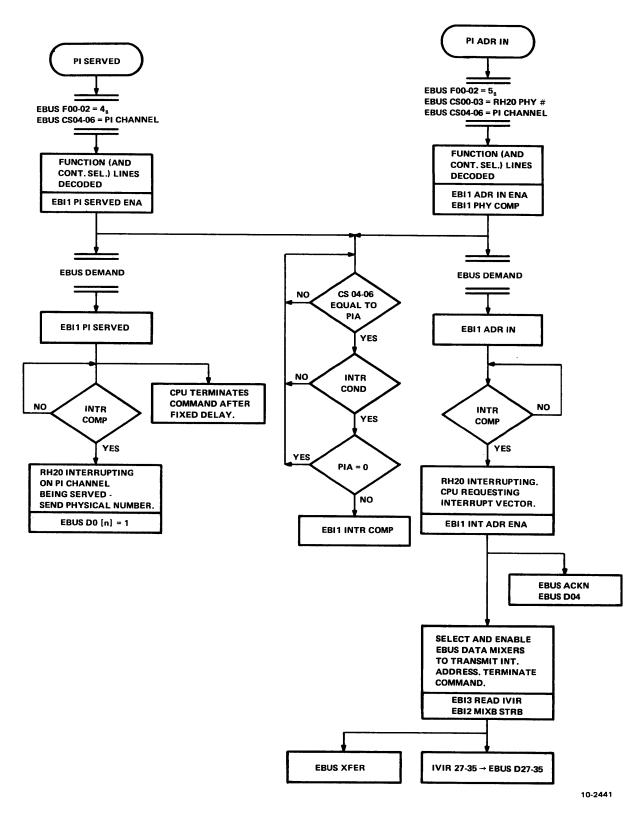

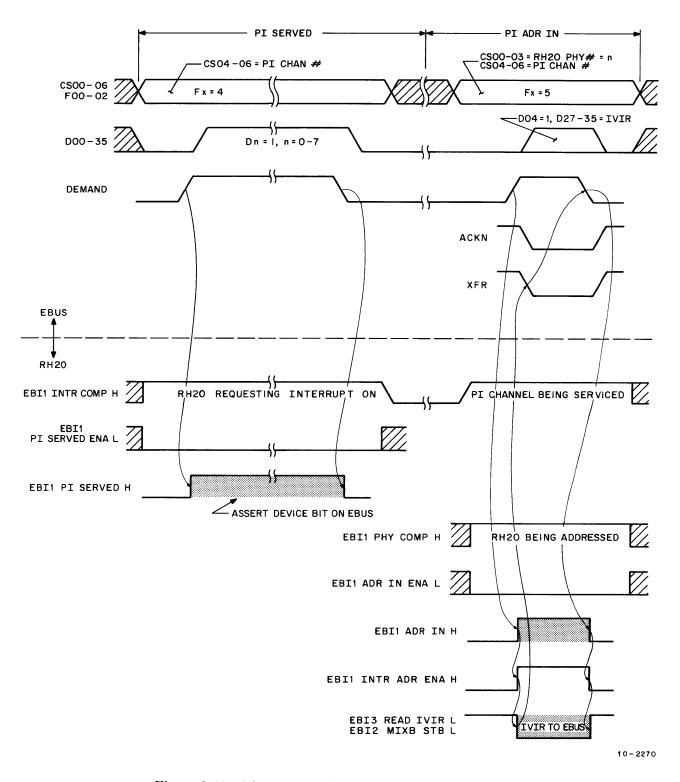

The PI SERVED command is issued by the EBox if one or more PI request lines is asserted on the EBus. The channel number corresponding to the highest priority PI request line is placed on CS04-06, 48 is encoded on the F lines, and DEMAND is asserted after a time delay. The RH20 (and other EBus controllers), after decoding the F lines and receiving DEMAND, asserts the data line corresponding to its physical number if it is interrupting on the PI channel being served. After a specified delay time, which allows all controllers on the bus to respond, the EBox strobes the data lines and negates DEMAND to end EBus operation. The data lines remain asserted until DEMAND clears. After determining which of the responding controllers has the highest priority, the EBox issues a PI ADR IN command. The channel number is again asserted on CS04-06, the physical number of the controller is asserted on CS00-03, and a function code of 58 is asserted on the F lines. DEMAND is then asserted after a delay to allow the controllers to decode the F lines. When an RH20 is addressed; that is, when the physical number asserted on the CS lines matches the RH20's hard-wired address, it asserts ACKN, places an API function word on the data lines, and asserts XFER. Bit format for the API function word is shown in Figure 2-5. The RH20 asserts an EPT address space code (0), a vector interrupt function code (28), and a 9-bit interrupt address (IVIR register contents) that is loaded prior to the PI ADR IN command by a DATAO. When XFER is received by the EBox, it strobes the function word from the data lines and negates DEMAND. In the RH20, the trailing edge of DEMAND negates ACKN, XFER, and the data lines to end the operation on the EBus. Timing for both the PI SERVED and PI ADR IN commands is shown in Figure 2-6.

Figure 2-5 RH20 API Function Word Format

Figure 2-6 PI SERVED/PI ADR IN Operation

#### 2.1.2 Massbus

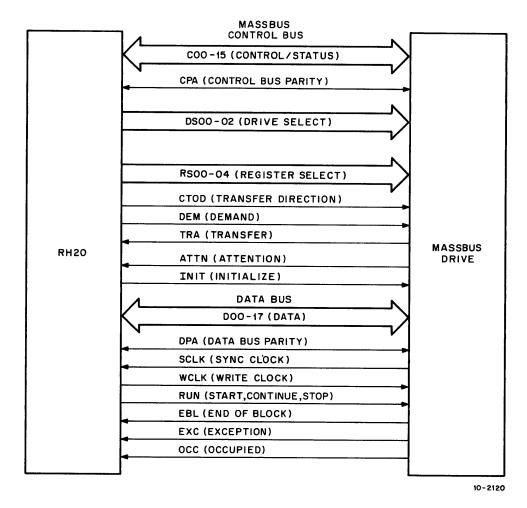

The Massbus provides a standard interface between controllers and mass-storage devices, such as disks, tapes, and other magnetic or cyclic storage media. It consists of two separate and independent buses, a control bus and a data bus, that allow both asynchronous and synchronous communication between the R H20 and its drives. Bus signals are described in Table 2-2. Information flow is shown in Figure 2-7.

Table 2-2 Massbus Signal Descriptions

| Signal                               | Direction     | Description                                                                                                                                                                                                                              |

|--------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTROL BUS Data Lines (C15-00, CPA) | Bidirectional | Transfer control data and status information between the RH20 and Massbus device (drive). Odd parity (CPA) is simultaneously transferred with the control bus data.                                                                      |

| Drive Select Lines (DS2-0)           | MBC to drive  | Select one of eight (maximum) drives connected to the RH20. These lines are ignored by drives when RS lines = 04 <sub>8</sub> ; that is, when the attention summary register is referenced. All drives respond to this register address. |

| Register Select<br>Lines<br>(RS4-0)  | MBC to drive  | Select a register in the drive addressed by the DS lines.                                                                                                                                                                                |

| Controller to Drive (CTOD)           | MBC to drive  | Specifies which direction data is to be transferred on the control bus. CTOD = 1 specifies a control bus write cycle; CTOD = 0 specifies a control bus read cycle.                                                                       |

| Demand<br>(DEM)                      | MBC to drive  | Causes a transfer of control data to take place between the RH20 and drive.                                                                                                                                                              |

Table 2-2 Massbus Signal Descriptions (Cont)

| Signal                            | Direction     | Description                                                                                                                                                                                                                                                                  |

|-----------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transfer<br>(TRA)                 | Drive to MBC  | Asserted in response to DEM. Indicates data has been strobed from the data lines if CTOD = 1. Indicates data has been placed on the data lines if CTOD = 0.                                                                                                                  |

| Attention (ATTN)                  | Drive to MBC  | Indicates a change in drive status or an abnormal condition (end of seek, error, etc.). Can be asserted by more than one drive at a time.                                                                                                                                    |

| Initialize<br>(INIT)              | MBC to drive  | Initializes all drives on the bus.                                                                                                                                                                                                                                           |

| Power Fail<br>(FAIL)              | MBC to drive  | Indicates a power-up fail condition in the RH20.                                                                                                                                                                                                                             |

| DATA BUS Data Lines (D17–00, DPA) | Bidirectional | Transfers synchronous data between the RH20 and drive. Odd parity (DPA) is simultaneously transferred with the data.                                                                                                                                                         |

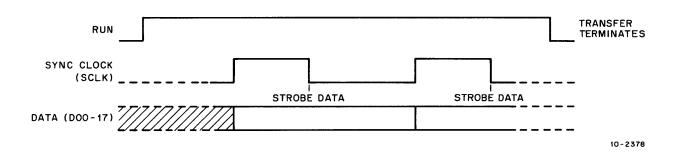

| Sync Clock<br>(SCLK)              | Drive to MBC  | Data clock. The RH20 gates and strobes data at the trailing edge. The drive gates data at the leading edge.                                                                                                                                                                  |

| Write Clock<br>(WCLK)             | MBC to drive  | Returning SCLK. Controls the strobing of data during a data bus write cycle. Drive strobes data at the leading edge.                                                                                                                                                         |

| RUN                               | MBC to drive  | Enables the drive to perform a read/write operation. During the data transfer, the drive samples RUN at the end of each data block (trailing edge of EBL). If RUN is still asserted, the drive continues the transfer; if RUN is negated, the drive terminates the transfer. |

| End of Block<br>(EBL)             | Drive to MBC  | Normally indicates the end of the data block. It must be asserted at least once after a read/write command has been accepted by a drive. Thus, it is asserted following an error that terminates a data transfer in mid-data block.                                          |

| Exception (EXC)                   | Bidirectional | When asserted by a drive, indicates that an error was detected during a read/write operation. NOT asserted by the RH20 during normal operation.                                                                                                                              |

| Occupied (OCC)                    | Drive to MBC  | Indicates that a drive has accepted a read/write command. Negated at the trailing edge of the last EBL pulse.                                                                                                                                                                |

Figure 2-7 Massbus Interface

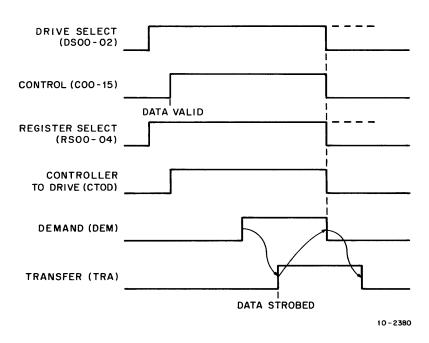

During a control bus write operation, the RH20 asserts the C lines, the DS lines, the RS lines, and CTOD. After these signals have settled on the bus, the controller asserts DEM to cause the drive to load the control data on the C lines into the addressed register in the selected drive. When the register data has been loaded, the drive asserts TRA. The RH20 then negates DEM, which negates TRA in the drive to end the handshaking sequence. Timing is shown in Figure 2-8.

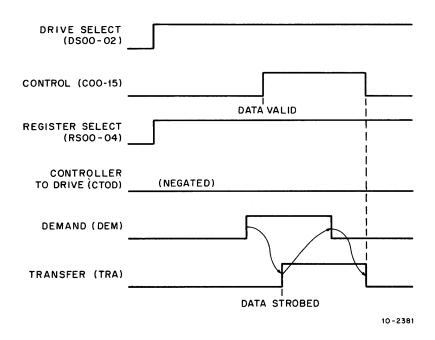

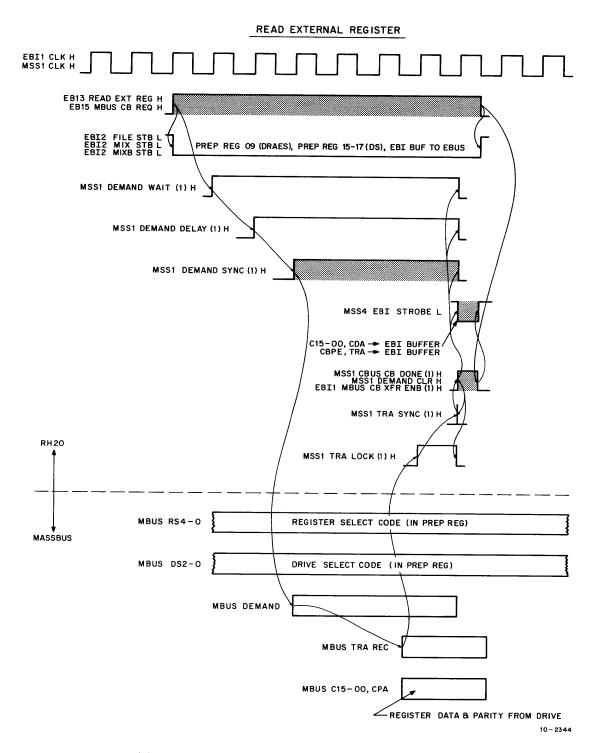

During a control bus read operation, the RH20 asserts only the DS and RS lines before asserting DEM. When DEM is received by the selected drive, it places the contents of the addressed register on the C lines and asserts TRA. The RH20 uses TRA to strobe the C lines and negate DEM. The trailing edge of DEM then negates TRA to complete the handshake. Timing is shown in Figure 2-9.

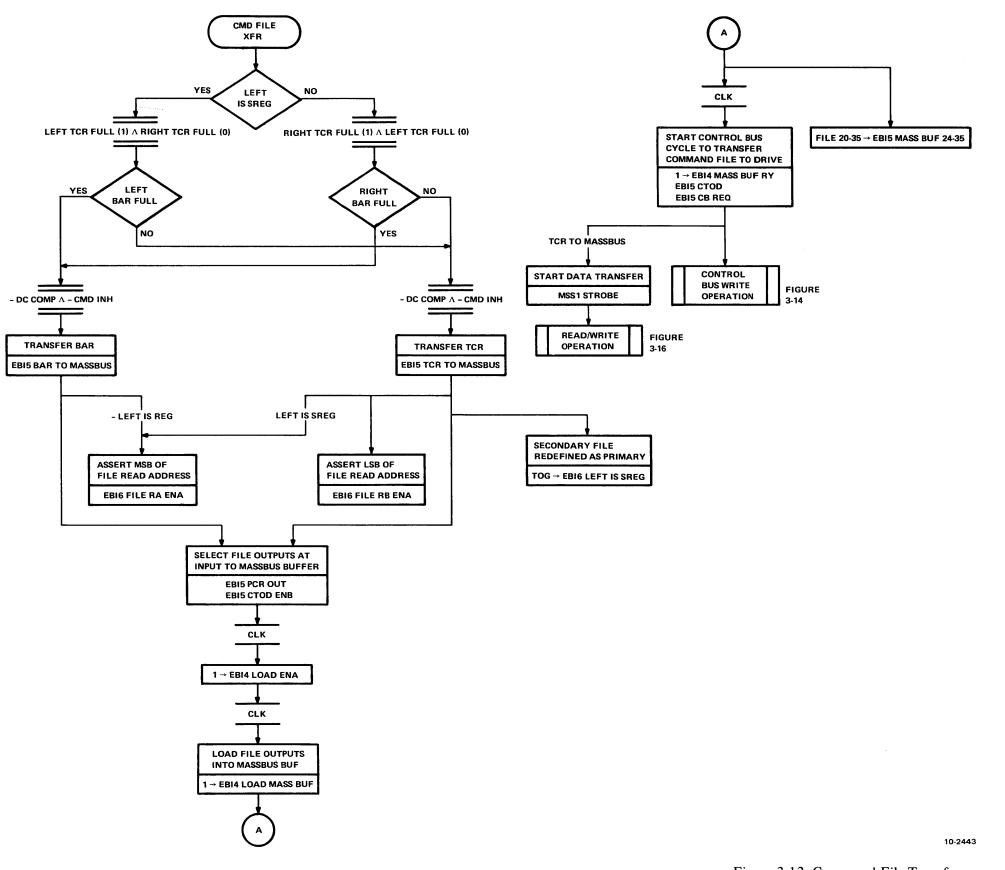

The control bus read cycle is initiated by the RH20 as a result of a DATAI command (external register address). The control bus write cycle is initiated by a DATAO (external register address) or by a command file transfer. The hardware-initiated command file transfer provides the means for starting a synchronous data transfer (read/write) in a drive (and RH20). It first loads the drive's data block address register (RS = 05<sub>8</sub>). It then loads the drive's control register (RS = 00) with a read/write command to start the data transfer. Non-data transfer commands (e.g., Seek, Search, etc.) are loaded in a drive's control register by a DATAO, not by a command file transfer. Once a read/write command is loaded in a drive, it asserts OCC and begins a search for the specified block address (disks) or starts up the recording medium (tapes). With RUN asserted by the RH20, SCLKs are generated on the data bus portion of the Massbus when the drive search operation completes (disks) or the recording medium is up to speed (tapes).

Figure 2-8 Control Bus Write Operation

Figure 2-9 Control Bus Read Operation

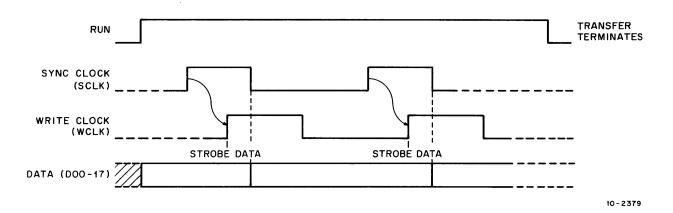

During the data bus write operation, data is placed on the data lines by the RH20 at the trailing edge of SCLK and strobed by the drive at the leading edge of WCLK. (WCLK is generated in the RH20 by the received SCLK signal.) Timing is shown in Figure 2-10. During the data bus read operation, data is placed on the data lines by the drive at the leading edge of SCLK and strobed from the bus at the trailing edge. Timing is shown in Figure 2-11.

Figure 2-10 Data Bus Write Operation

Figure 2-11 Data Bus Read Operation

During the write and read operations, the drive asserts EBL after the last word of each data block is transferred. The RH20 terminates the data transfer by negating RUN at the leading edge of the EBL signal corresponding to the last data block.

EXC is asserted by the drive to signal the RH20 that an error condition has occurred during a data transfer. In addition, the ATTN line is asserted to indicate the error condition or status change in the drive. ATTN may be asserted for any of the following conditions:

- a. An error is detected while no data transfer is taking place (asserted immediately).

- b. At the completion of a data transfer command if an error occurred during the data transfer.

- c. At the completion of a non-data transfer command (e.g., Search).

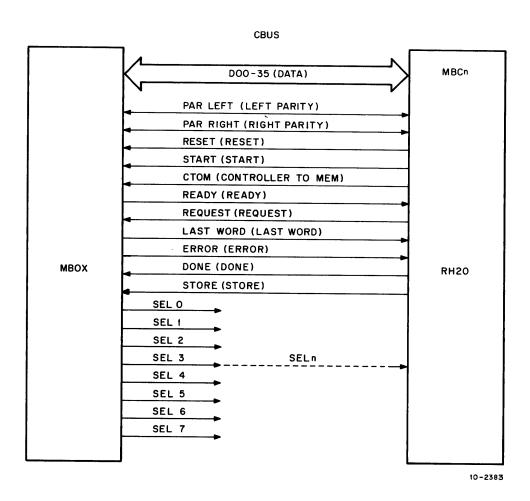

#### 2.1.3 CBus

The Channel Bus (CBus) is a synchronous bus that connects the integral data channel logic of the MBox to a maximum of eight RH20 mass-storage controllers. The CBus is composed of a 36-bit wide data path and its associated control lines. It transfers high-speed data between the MBox channels and the RH20 controllers. Each CBus line is described in Table 2-3. Figure 2-12 illustrates the CBus configuration.

Table 2-3 CBus Signal Descriptions

| Signal                            | Direction     | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data Lines (D00-35)               | Bidirectional | Transfers high-speed data. The lines are valid only during a data cycle. The MBox will place zeros on the data lines for an RH20 (during its data cycle) whenever there is no data transfer request from that RH20.                                                                                                                                                           |

| Parity Left/<br>Parity Right      | Bidirectional | Transfers the computed parity for the left- and right-half words on the data lines.                                                                                                                                                                                                                                                                                           |

| Select Lines (SEL 0-7)            | MBox to MBC   | Continuously select the RH20 on the bus. Define the beginning of the four channel cycles (Select, Request, Wait, Data) associated with each controller.                                                                                                                                                                                                                       |

| RESET                             | MBC to MBox   | Asserted by an RH20 during its data cycle. Causes the MBox to:                                                                                                                                                                                                                                                                                                                |

|                                   |               | Clear the data buffers associated with the selected RH20.                                                                                                                                                                                                                                                                                                                     |

|                                   |               | Reset the command list pointer associated with the selected RH20 to the initial control word address.                                                                                                                                                                                                                                                                         |

|                                   |               | Negate all status and data lines associated with the selected RH20 after the above two steps are completed.                                                                                                                                                                                                                                                                   |

| START                             | MBC to MBox   | Asserted by an RH20 to begin a transfer. START is asserted once during its data cycle, and only when READY is negated.                                                                                                                                                                                                                                                        |

| Controller to<br>Memory<br>(CTOM) | MBC to MBox   | Asserted by an RH20 to indicate the transfer direction to the MBox. For a read data transfer, CTOM is asserted; for a write data transfer, CTOM is negated.                                                                                                                                                                                                                   |

| READY                             | MBox to MBC   | Asserted by the MBox (during the data cycle) after it detects START from the RH20, and after the MBox is ready for a data transfer. For a write data transfer, the MBox is required to have at least one data word from memory in its buffer before asserting READY. READY will be negated only after sensing DONE, and after the MBox is prepared to start another transfer. |

Table 2-3 CBus Signal Descriptions (Cont)

| Signal  | Direction   | Description                                                                                                                                                                                                                          |

|---------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQUEST | MBC to MBox | Asserted by an RH20 during its request cycle when:                                                                                                                                                                                   |

|         |             | One of its data buffers is full, during a read data transfer.                                                                                                                                                                        |

|         |             | One of its data buffers is empty, during a write data transfer.                                                                                                                                                                      |

|         |             | An RH20 will not assert REQUEST if:                                                                                                                                                                                                  |

|         |             | READY is not asserted by the MBox.                                                                                                                                                                                                   |

|         |             | ERROR has been asserted by the MBox during the current transfer.                                                                                                                                                                     |

|         |             | LAST WORD has been asserted by the MBox during the current transfer.                                                                                                                                                                 |

|         |             | DONE has been asserted by the RH20 during the current transfer.                                                                                                                                                                      |

|         |             | For a read data transfer, the RH20 places data (during its data cycle) on the data lines and the MBox will strobe the lines at the trailing edge of the same data cycle. For a write data transfer, the above operation is reversed. |

| DONE    | MBC to MBox | Asserted by an RH20 during its data cycle to terminate a data transfer. No further data requests will be made after DONE is asserted.                                                                                                |

| STORE   | MBC to MBox | Asserted by an RH20 together with DONE to cause channel status to be stored in the channel's assigned reset and status logout area. Asserted when:                                                                                   |

|         |             | The current transfer is terminated due to errors detected in the RH20.                                                                                                                                                               |

|         |             | The current transfer command in the RH20 specifies that STORE be sent to the MBox at the conclusion of the transfer.                                                                                                                 |

Table 2-3 CBus Signal Descriptions (Cont)

| Signal    | Direction   | Description                                                                                                                                                                                                                                                                                   |  |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LAST WORD | MBox to MBC | Asserted by the MBox during the data cycle (for write data transfer only) at the same time the last data word is sent to a controller. No further data requests will be made by the RH20 after detecting LAST WORD.                                                                           |  |

| ERROR     | MBox to MBC | Asserted by the MBox (during the data cycle) to inform the RH20 that the current data transfer must terminate due to an error in the MBox. On sensing ERROR, the RH20 terminates the transfer by not issuing any further requests. The RH20 also asserts DONE during a subsequent data cycle. |  |

Figure 2-12 CBus Interface

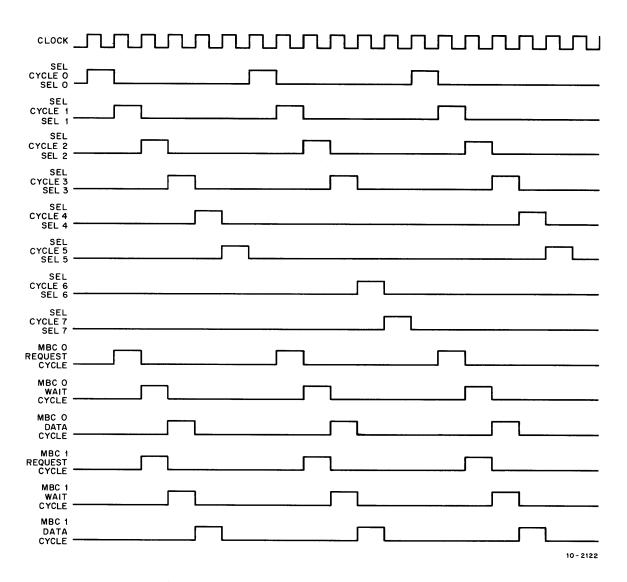

The RH20 selection order is on a set priority basis using a time division multiplexing technique. Selection is of the following order: 0, 1, 2, 3, 4, 5; 0, 1, 2, 3, 6, 7. Each channel associated with an RH20 is assigned a specific time slot within a fixed repetition rate and the corresponding RH20 is selected during the same time slot in successive repetition cycles. Selection is by the CBUS SEL n level (n = 0-7), which defines the first of four channel cycles (Select, Request, Wait, Data) that are used by the MBox and the controller to transfer control information and data during the synchronous data transfer. (Figure 2-13 illustrates RH20 selection and timing.)

- a. Select Cycle The select line for a particular controller is asserted during this cycle.

- b. Request Cycle The selected controller will assert its request line (if data request is needed) during this cycle.

Figure 2-13 Basic RH20 Selection and Timing

- c. Wait Cycle This cycle is used by the MBox to prepare data and status for transmission. Neither data nor control lines are asserted during this cycle.

- d. Data Cycle Data is placed on the data lines by either the MBox or the controller during this cycle. The receiver will strobe the data lines at the trailing edge. All control lines, except the REQUEST line, are asserted during the data cycle.

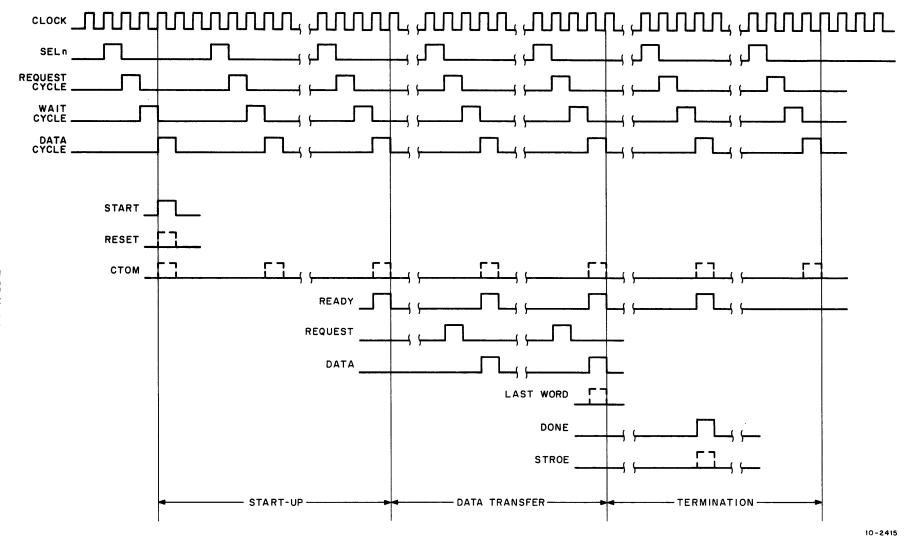

Figure 2-14 shows CBus timing during a data transfer. If READY is negated, the RH20 starts the channel by asserting START during the data cycle. At the same time, it asserts the RESET line if the channel is to be initialized and it asserts CTOM if the data transfer is a device read operation. When the channel is ready to transfer data over the CBus, it asserts READY during the data cycle. For a device write operation, the channel will have at least one word in its data buffers.

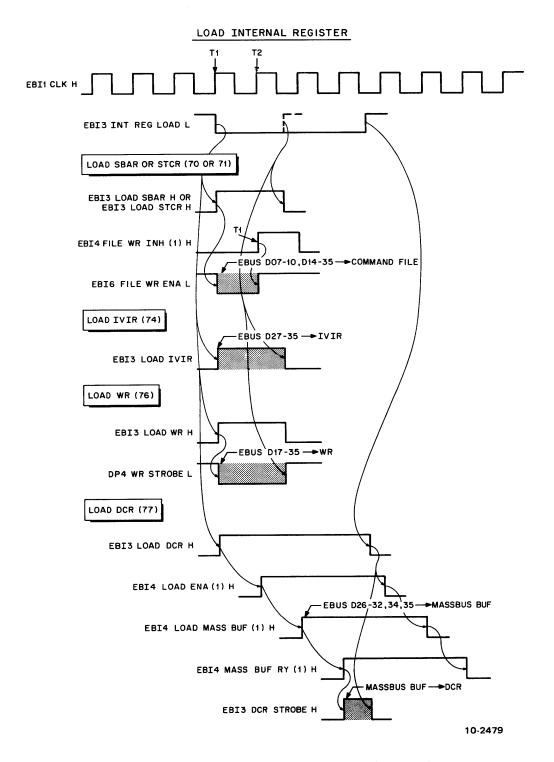

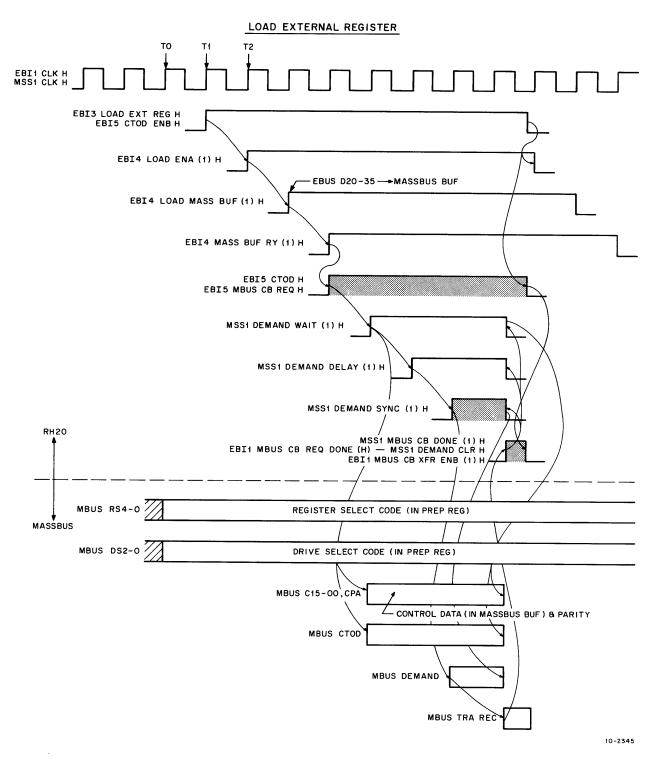

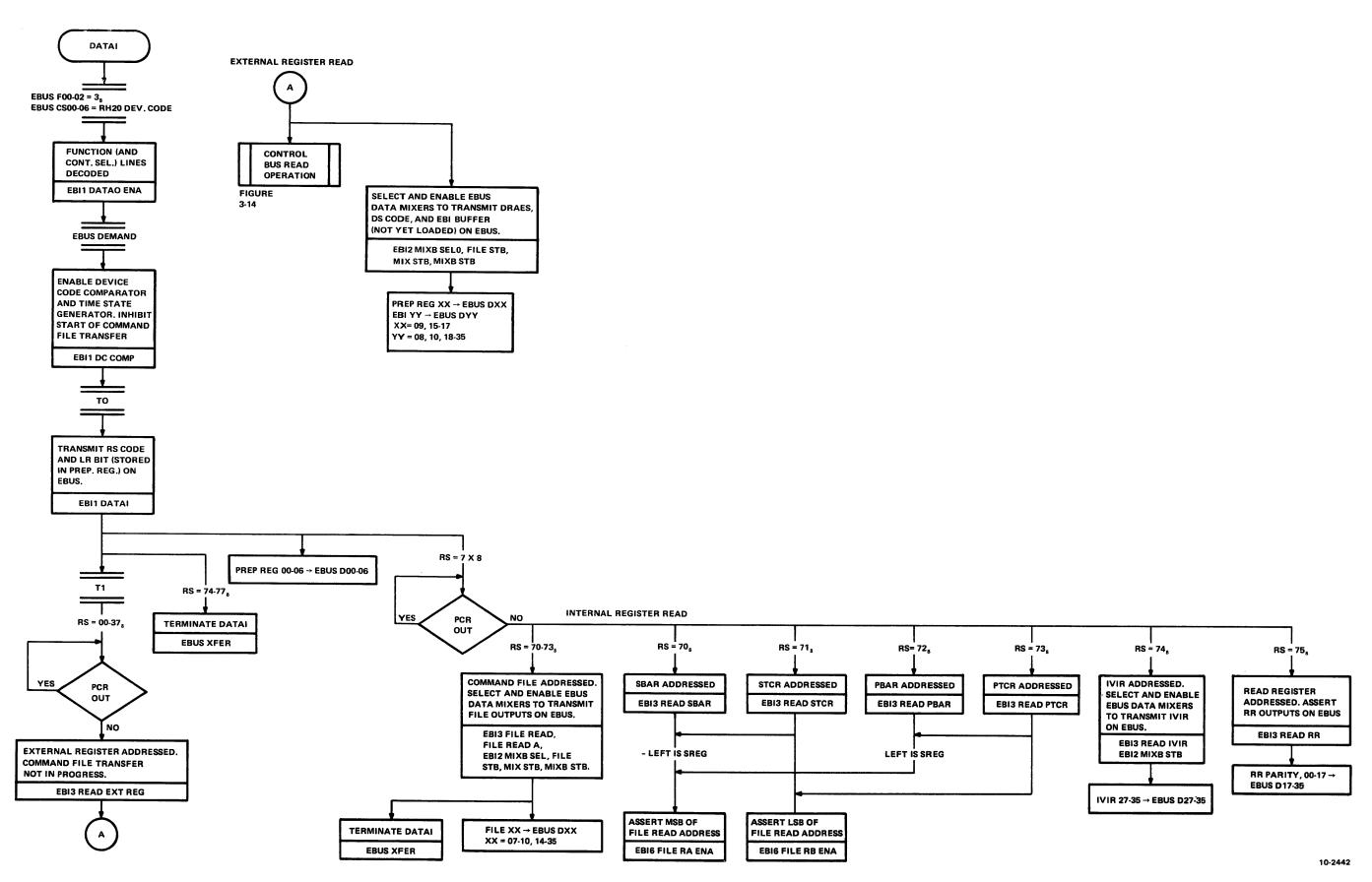

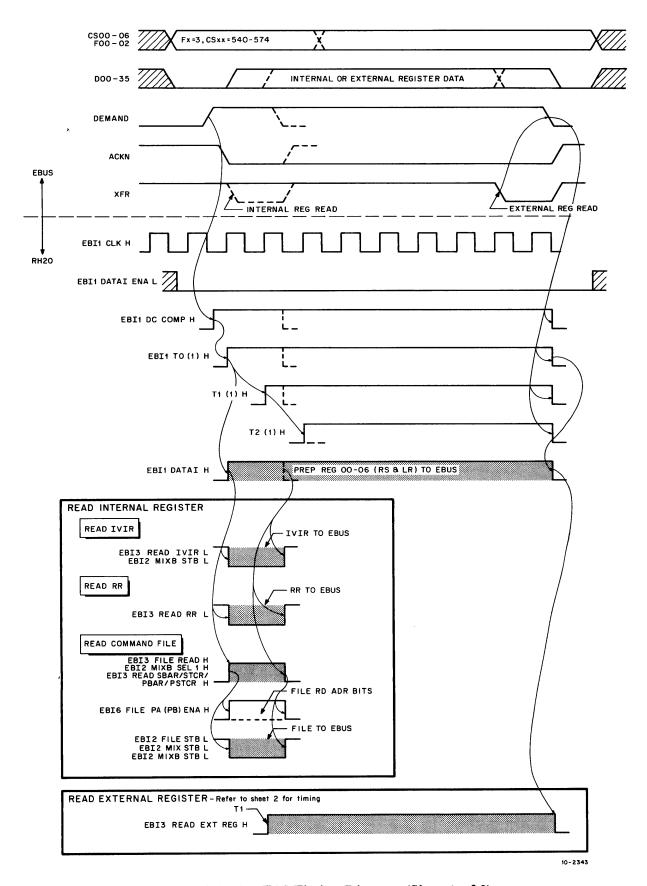

After receiving READY, the RH20 asserts REQUEST during the request cycle whenever it requires a data word from the channel (device write) or whenever it requires that the channel accept a data word (device read). The words are asserted on the DATA lines following the corresponding REQUEST signal. When the channel places the last word on the CBus during a device write operation, it asserts LAST WORD. In response, the RH20 makes no more data requests and asserts DONE during a subsequent data cycle. The RH20 also asserts DONE when it has transferred all data over the CBus during a device read operation and when a transfer error is detected during a read or write. (CBUS ERROR causes DONE to be asserted by the RH20 when the transfer error is detected in the channel.) DONE causes the channel to terminate the operation. READY is negated when the channel is prepared to begin another data transfer.