REFILL ILL - MICRO HANDLES PAGE

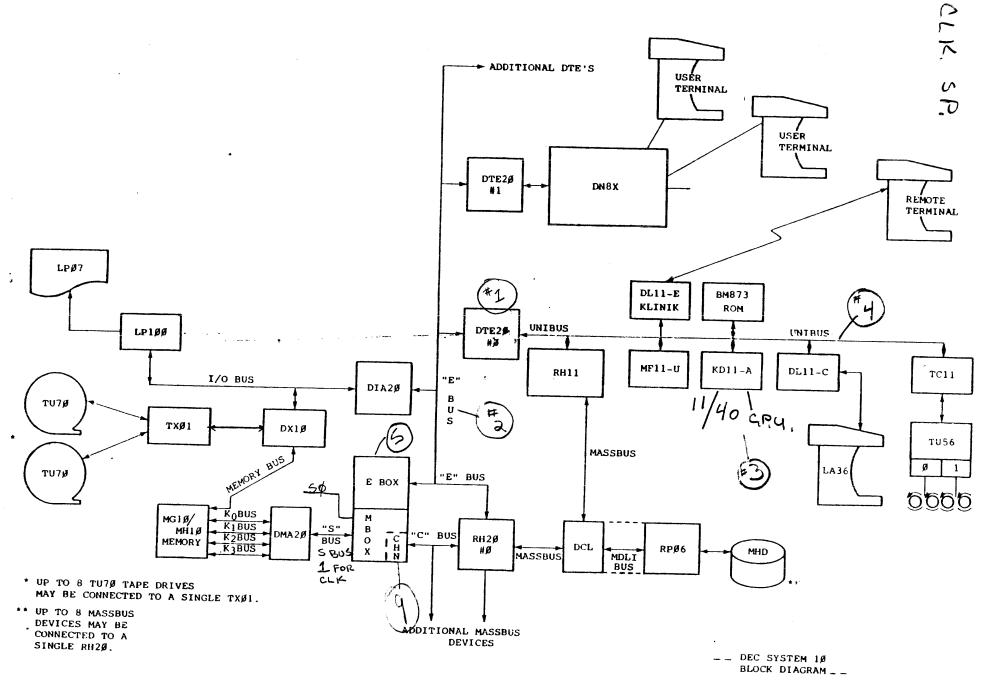

Figure 3. DECsystem-10 Block Diagram ToPS 10 ShFTWARE

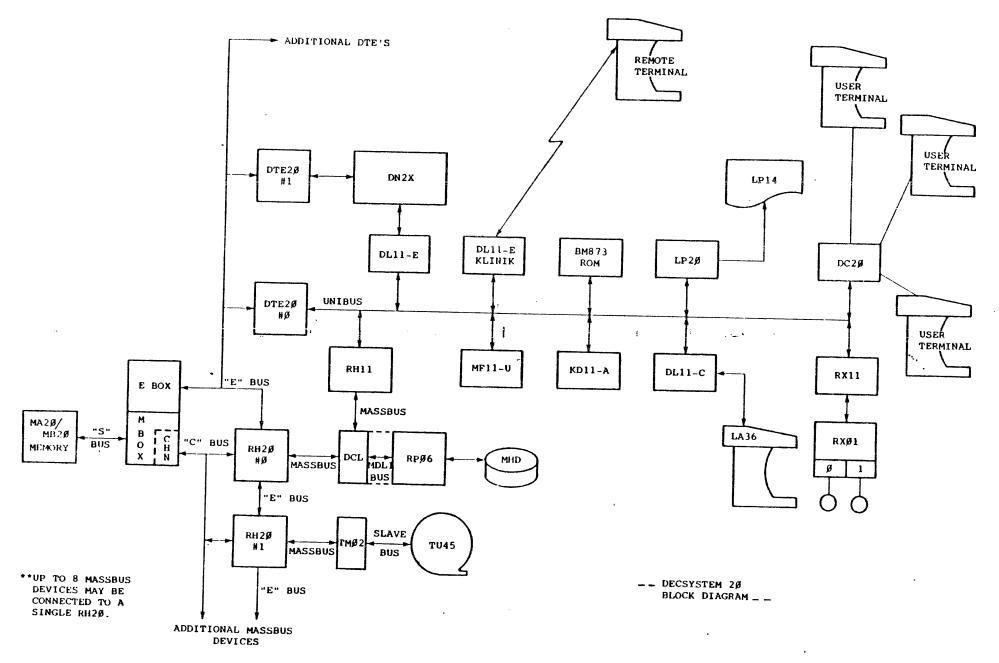

Figure 2. DECSYSTEM-20 Block Diagram

- 3. The accounting meter which counts EBox clock ticks and MBox references with two separate counters

- 4. The performance analysis counter which is used in evaluating the performance of the system.

# 4.2.15 External and Internal I/O Controllers and Devices (Typical)

Every device controller on the EBus and I/O bus has a 7-bit device selection network, a priority interrupt assignment, and at least two flags, busy and done, or some equivalent. The selection network decodes bits 3-9 of the instruction so that only the addressed device responds to signals sent by the KL10 Central Processor over the EBus. To use the device with the priority interrupt system, the program must assign a channel to it. Then whenever an appropriate event occurs in the device, it requests an interrupt on the assigned channel.

The busy and done flags together denote the basic state of the device. When both are clear the device is idle. To place the device in operation, a CONO or DATAO sets busy. If the device will be used for output, the program must give a DATAO that sends the first unit of data – a word or character depending on how the device handles information. When the device has processed a unit of data, it clears busy and sets done to indicate that it is ready to receive new data for output, or that it has data ready for input. In the former case, the program would respond with a DATAO to send more data; in the latter, with a DATAI to bring in the data that is ready. If an interrupt channel has been assigned to the device, the setting of done signals the program by requesting an interrupt; otherwise the program must keep testing done to determine when the device is ready.

#### 4.2.16 Machine Instructions

Two basic types of instruction are implemented for the KL10 Central Processor. They are those that reference memory and execute a particular operation such as data transmission, logical operations, arithmetic operations, or program control operations and those that reference memory and perform I/O operations for internal devices and for devices connected to the EBus (refer to Section 3, System Features).

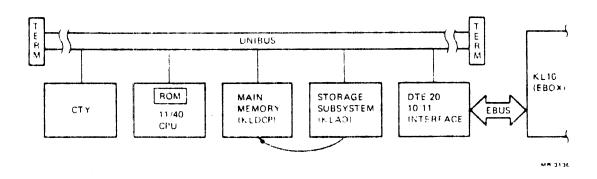

#### 4.3 CONSOLE PROCESSOR SUBSYSTEM

The console processor is a unified hardware/software subsystem that replaces the KA10/KI10 based standard console I/O equipment (which is used for read-in operations), the computer operator console, and the three arithmetic processor indicator panels. To replace this hardware, the console processor provides an automatic bootstrap mechanism and a console command facility. The console processor which incorporates a PDP-11 minicomputer system interfaces with the central processor through the <u>DTE20 Ten-Eleven Interface</u> which is set up to operate in its privileged mode.

The bootstrap facility automatically initializes the dispatch and control RAMs in the EBox, places a small sequence of KL10 code into KL10 memory, and starts its execution to load the system. Several bootstrap options including an operator/software dialogue are available. The console command facilities are available through the console terminal (CTY) to permit the operator to examine or deposit KL10 memory locations and otherwise control and monitor the processor in the same way previously provided by the replaced operator console and indicator panels.

The PDP-11, used as the console processor, is a 16-bit, general purpose, microprogrammed minicomputer which uses single- and double-operand instructions and 2's complement arithmetic. Included in the console processor are the associated PDP-11 controllers and peripheral devices.

The instruction word format is such that the processor can directly address up to 32K words (64K bytes) of core memory. Only 28K are available for program storage. The remaining 4K are reserved for peripheral and register addresses. All communication among system components (including processor, core memory, and peripherals) is performed over the Unibus. Because of the Unibus concept, all peripherals are compatible, and device-to-device transfers can be accomplished at the rate of 2.5 million 16-bit words or 8-bit bytes per second. All system components and peripherals are linked by the Unibus and all peripherals are in the basic system address space. Most instructions applied to data in memory can also be applied to data in peripheral device registers, enabling peripheral device registers to be manipulated as flexibly as memory.

#### 4.3.1 Devices

The following paragraphs provide a brief description of each component that is part of the console processor subsystem.

- **4.3.1.1** KD11-A Central Processor This device is the basic component of the console processor. The KD11 is connected to the Unibus as a subsystem and controls time allocation of the Unibus for peripheral devices and performs arithmetic and logic operations through instruction decoding and execution. The instruction set is implemented through a group of hardware subroutines stored within the 256- by 56-bit read-only memory (ROM).

- **4.3.1.2** KY11-D Programmer's Console This device is an integral part of PDP-11 system and provides the operator with a direct system interface through the control switches and display indicators. The control switches provide the operator with real-time control of normal program and diagnostic operations, thus allowing the operator to start, stop, load, modify, or continue a program.

- 4.3.1.3 KW11-L Line Clock Option This device provides a method of referencing real-time intervals by generating a repetitious interrupt request to the KD11. The rate of interrupt is derived from the acline frequency.

- 4.3.1.4 MF11-UP Memory This device is a read/write, random access, coincident current, magnetic core type memory with a maximum cycle time of 980 ns and a maximum access time of 425 ns. It is organized in a 3D, 3-wire planar configuration. Storage capacity is 16,384 words (32,768 bytes), having an 18-bit word length (16 data bits plus two parity bits).

- 4.3.1.5 MM11-UP Memory This device is a 16K word expansion memory having characteristics identical to the MF11-UP.

- 4.3.1.6 BM873-YD/YG ROM Loader Module This module is an essential part of the console processor. It provides 256 words of read-only memory which are blasted to contain a number of routines to facilitate bootstrap, power fail, and dump operations. In addition to these routines, the ROM module contains four locations which serve as entry points for these routines. The routines in the ROM facilitate bootstrapping and dump operations to be initiated from the KL10 via the DTE20 10/11 Interface and by pressing a physical LOAD pushbutton on the margin check panel (refer to Power System Description Manual).

Either the PDP-11 based DECtape or the PDP-11 based RJP04/06 disk may be specified for the bootstrap or dump procedure.

NOTE

These storage devices are not supported as system devices.

- 4.3.1.7 DL11-C Asynchronous Line Interface This device provides simultaneous 2-way transmission between the console terminal and the Unibus. The DL11-C is a character-buffered interface which controls and translates serial bit stream data from the terminal to parallel character data for transfer over the Unibus. The interface also provides parallel to serial translation from the Unibus to the terminal.

- 4.3.1.8 DL11-E Asynchronous Line Interface This device has the same general characteristics as the DL11-C, and in addition provides control functions for a communication modem (e.g., Bell Model 103) that interfaces with the KLINIK diagnostic facility.

- 4.3.1.9 LA36 Keyboard Terminal This device is a 30-character per second, serial upper/lowercase character printer with a 132-column format. The terminal interfaces to the Unibus through the DL11-C and is used as the main console terminal (CTY).

- 4.3.1.10 RJP04/06 Disk File System This system consists of an RP04/06 disk drive and an RH11 device controller. The RP04/06 is a dual Massbus port, moveable head, disk pack drive used as the prime storage media for KL10 and PDP-11 diagnostic and bootstrap load routines. The RH11 provides the control and parallel data path interface between the Unibus and RP04/06 through the Massbus. In addition to communicating with the KD11, the controller has access to PDP-11 memory to fetch and store data.

#### NOTE

The drive is not supported as a system device from the PDP-11 side but is supported as a system storage device from the KL10 side. (Refer to Secondary Memory Subsystem Description.)

- 4.3.1.11 TC11-G Magnetic Tape System This system consists of a TC11 control unit and TU56 tape transport. The TC11 controls transport selection and tape motion and direction. In addition it controls transport read and write operations, and buffers data transferred in either direction. The TU56 is a dual unit, bidirectional tape transport which handles 3/4-inch magnetic DECtape. The transport uses the Manchester-phase recording technique with redundant recording. The tape serves as an auxiliary storage media for KL10 and PDP-11 diagnostic and bootstrap load routines; it is not supported as a KL10 system device.

- 4.3.1.12 BC11-A Unibus The Unibus is a 120-conductor ribbon cable connecting the console/frontend processor system components. The Unibus consists of 56 signal and 64 ground lines assembled alternately within the cable to minimize crosstalk.

- 4.3.1.13 DTE20 Ten-Eleven (Console/Front-End Processor) Interface This device connects the KL10 central processor with the PDP-11 console/front-end processor to provide the system with interprocessor interrupt, examine, deposit, byte transfers, diagnostic, and boot facilities.

On the EBus, the DTE20 appears in some respect as a KL10-based DECsystem-10 device controller. On the Unibus it connects as a standard PDP-11 peripheral device, using the direct memory access and vector interrupt features of the PDP-11.

# Introduction to Maintenance Software

# GENERAL DESCRIPTION AND USE

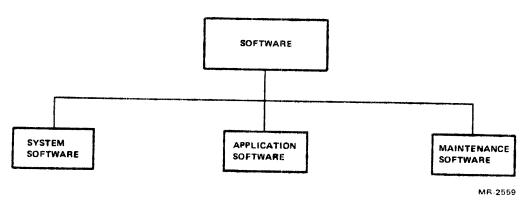

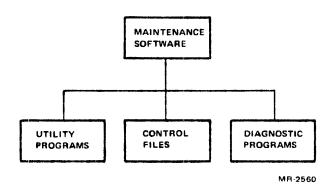

Computer software is divided into three major categories: system software, application software, and maintenance software. Refer to Figure 1.

Figure 1. Three Major Categories of Software

The term maintenance software refers to a group of programs specifically designed to aid engineering, manufacturing, and field personnel in determining the operational status of system hardware. In this respect maintenance software is used:

- During the prototype stages of hardware design to determine if the system, subsystem, or unit under development operates properly and as expected. During this time both the hardware and the maintenance software may undergo any number of changes or revisions.

- During manufacturing and final system integration to assure that the product functions properly before shipment.

- During installation to double check manufacturing and to correct any faults that may have occurred during shipment.

- 4. During customer acceptance to demonstrate to the customer that the hardware is operating properly.

- 5. During preventive maintenance to assure that the system is fully (100%) operational. Maintenance software is also used at this time to identify potential problems and problems that can be deferred to a later, more convenient, date for correction.

- 6. During corrective maintenance to detect and isolate the cause of the hardware fault.

- 7. Following corrective maintenance to verify that all problems have been identified and resolved and that the system is fully (100%) operational.

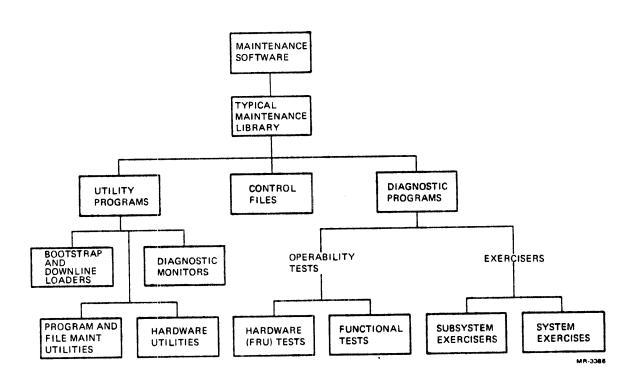

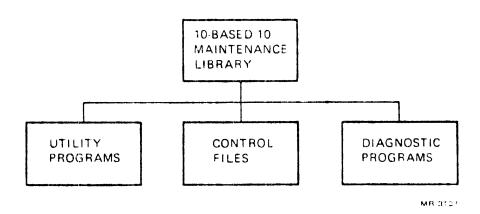

# MAINTENANCE LIBRARIES

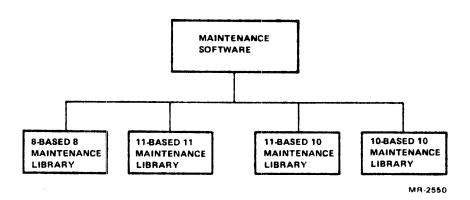

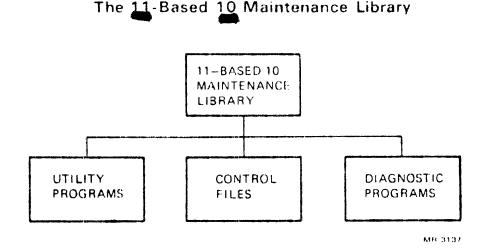

Maintenance software is organized into maintenance libraries. The libraries are identified by the base processor that executes the programs and by the type of system the programs are designed to maintain. This course, for example, describes three maintenance libraries. Refer to Figure 2.

Figure 2. Maintenance Libraries

ll-Based ll Maintenance Library - The ll-Based ll Maintenance Library is written in PDP-11 machine language and is used to diagnose faults in PDP-11 based systems and subsystems.

- 11-Based 10 Maintenance Library The 11-Based 10 Maintenance Library is written in PDP-11 machine language and is executed by the KL10 console front-end subsystem. It is used to diagnose faults in the KL10 processor, main memory, and channels.

- 10-Based 10 Maintenance Library The 10-Based 10 Maintenance Library is written in PDP-10 machine language and is used to diagnose faults in the PDP-10 processor, storage, and I/O subsystems.

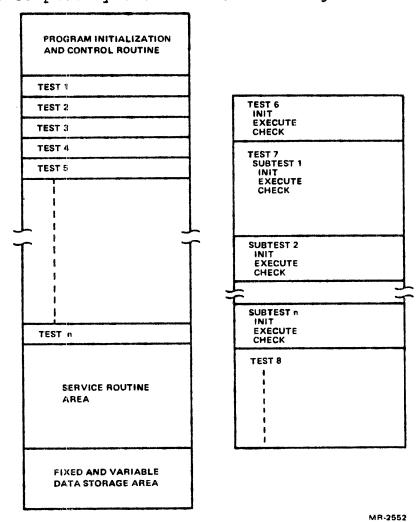

Maintenance libraries have three component parts: utility programs, control files, and diagnostic programs. Utility programs and control files simplify loading, running, and maintaining the diagnostic programs and the diagnostic storage media. The diagnostic programs are used to detect and isolate hardware faults and to verify the operational status of the system. Refer to Figure 3.

Figure 3. Component Parts of a Maintenance Library

# **Utility Programs**

There are six basic types of utility programs.

1. Bootstrap Loaders - A bootstrap loader is a short, two-part program. The first part either resides permanently in a read-only memory (ROM) or is manually deposited into memory. The second part resides in the boot block (block 0) of the input

device. The first part consists of a few instructions which, when executed, will read in and start the second part. Once started, the bootstrap loader can be used to load and start a larger, more sophisticated program such as a diagnostic monitor.

- Downline Loaders A downline loader is a program that is used to transfer a utility or diagnostic program from the host system to another system or subsystem for execution.

- 3. Diagnostic Monitors A diagnostic monitor is a special purpose loader that enables the user to:

- Directly load and run a single utility or diagnostic program

- b. Indirectly (via a control file) load and run a sequence or hierarchy of diagnostic programs.

- 4. Program Maintenance Utilities This type of utility program is used to construct and modify (patch, update, etc.) control files and diagnostic programs.

- 5. File Maintenance Utilities This type of utility program is used to duplicate and update diagnostic storage media (e.g., disk, tape, etc.).

- 6. Hardware Utilities A hardware utility is a utility program that supports maintenance or diagnostic functions. The Il-Based 10 Maintenance Library, for example, uses utilities of this type to configure the main memory subsystem and to read and change the internal status of the KL10 processor, memory, and channels. Although this type of utility program performs maintenance and diagnostic operations, it is not a diagnostic in the true sense of the word. That is, it does not automatically detect and isolate hardware faults.

Utility programs are relatively easy to use because they are controlled by task-oriented commands. And, because the commands are task-oriented, they can easily be summarized in tables similar to those used in the KL10 Maintenance Guide. (See example below). The table lists the base commands in alphanumeric order, provides an example which illustrates the proper command format, and briefly describes the task

the command performs. A cross reference may be used when a more detailed description of the command is necessary. This example is from TRACON, an 11-based 10 utility program.

#### **EXAMPLE:**

| 4 .     | Table 1 TRACON Control Function Summary                                                        |               |

|---------|------------------------------------------------------------------------------------------------|---------------|

| Command | Description                                                                                    | Cross<br>Ref. |

| A       | A <cr> Auto insert - automatically builds an internal command file as commands are typed.</cr> | 1             |

| Е       | E <cr> Edit or create a command buffer. Refer to Table 2.</cr>                                 | N/A           |

# TRACON COMMAND DESCRIPTION (Cross Reference)

This section describes in detail each of the commands summarized in Table 1.

1. A<CR> - The A command opens the control buffer for input. All commands typed following the A command are entered into the buffer until a KA command is typed. The commands in the buffer are executed via the X, L or M command. The buffer may be saved for future reference with the DC command.

#### ----NOTE ----

For further information about TRACON commands, refer to the 10-Based 10 section of the KL10 Maintenance Guide.

#### Control File

A control file (sometimes referred to as a chain or script) is an ASCII text file. It is generated using a standard editor program, and contains a list of commands to be executed by another program, usually a utility program. When directed to do so, the program will read the control file into a memory buffer and begin executing the commands it contains as though they were entered directly from the user's terminal.

The following is a typical example of a control file. The file is from the 11-Based 10 Maintenance Library. In the example, KLDCP, an 11-based 10 utility program, is directed to sequence through a series of diagnostic programs (i.e., run two passes of DGDTE, one pass of DGKAA, one pass of DGKAB, etc.). Note that lines preceded by a semicolon are considered comments and are ignored by KLDCP.

#### **EXAMPLE:**

```

;B.CMD, KL10 PROCESSOR DIAGNOSTIC BOOT, 9-JUN-78;PROCESSOR HARDWARE

;DTE20 INTERFACE

P DGDTE.All

SED 2

;EBOX PART 1

P DGKAA.All

SED 1

;EBOX PART 2

P DGKAB.All

SED 1

;MBOX BASIC

etc.

```

Frequently during preventive and corrective maintenance, control files are used to automatically direct a utility program to sequence through a series (hierarchy) of diagnostic programs. Control files used in this manner assure that the proper programs are run in the correct order and for the prescribed period of time.

In most cases the standard control files shipped with a maintenance library are limited to testing the processor, main memory, and channels. Shipping standard control files for the rest of the system is usually not feasible because of the variety of storage and I/O subsystems that could be used in the final system configuration. Therefore, the control files for testing these subsystems should be generated locally, usually at the site during installation. Once the control files are generated, they can be transferred to the maintenance software storage media and used as necessary.

# **Diagnostic Programs**

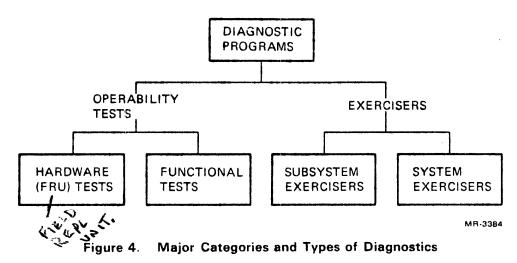

There are two major categories of diagnostics: operability tests, which include hardware (FRU) tests and functional tests, and exercisers, which include subsystem exercisers and system exercisers. Refer to Figure 4.

- Operability tests are intended to detect and isolate solid hardware malfunctions. That is, they are designed to test the basic ability of the hardware to operate.

- Exercisers are intended to detect and isolate intermittent hardware malfunctions; that is, they test for system and subsystem reliability, priority arbitration, and interaction faults that only occur when the system is operating at or near full capacity.

Both of these categories will be discussed in detail later.

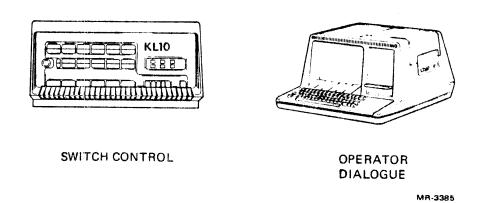

Operational Control - There are two principal methods of controlling the operation of a diagnostic program. One is switch control and the other is operator dialogue. Many diagnostics use a combination of both. Refer to Figure 5.

Figure 5. Two Methods of Controlling the Operation of Diagnostic Programs

Switch control is usually implemented through the console data switches. Each switch is assigned a fixed binary program control function (e.g., inhibit printouts, loop on test, halt on error, etc.). The switches are read at the start of the program and may be read periodically by the program while it is running. The program uses the state of the control switches to determine operating parameters and its reaction to various error conditions.

Operator dialogue takes place between the diagnostic and your terminal. It enables the diagnostic to query you and enables you to specify program parameters such as the subsystems and device units to be tested, the type of test to be run, and the data patterns to be used during testing.

The flexible control offered by operator dialogue complements the more rigid control offered by switches. Thus many diagnostics, particularly those in the exerciser category, use the switches to specify standard binary control functions and the operator dialogue to specify variable control functions.

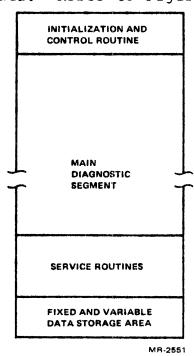

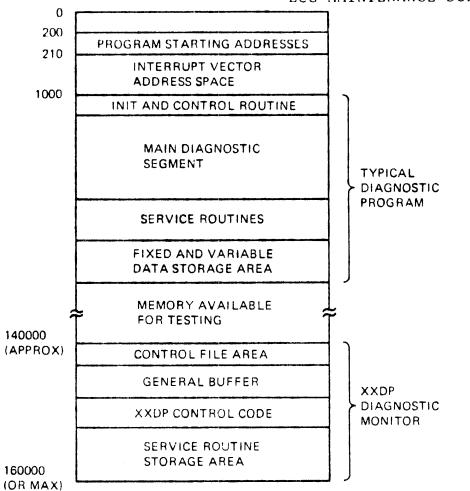

Internal Structure - Although no rule states that all diagnostic programs must use a standard internal structure, most do. The structure consists of four parts: a program initialization and control routine, a main diagnostic segment, a set of service routines, and a storage area for fixed and variable data. Refer to Figure 6.

Figure 6. Internal Structure of Diagnostic Programs

- Program Initialization and Control Routine This routine initializes the system, reads and stores the state of the program control switches, performs operator dialogue, and dispatches to the main diagnostic segment of the program.

- Main Diagnostic Segment The main diagnostic segment consists of a set or series of exerciser or test routines. The set of exerciser routines that make up exercisers are inextricably intertwined (complex, to say the least). This is particularly true at the machine language level. On the other hand, the series of test routines that constitute operability tests are relatively easy to understand. This is true both at the conceptual level and at the machine language level. The internal organization and structure of operability tests will be discussed later.

- Service Routines Service routines are used by both the program initialization and control routine and the routines that make up the main diagnostic segment. Service routines are used to handle keyboard input and printer output, generate data patterns, load and unload memory buffers, format error messages, etc. Separating service routines from the main program and making them available to both the initialization and test routines has several advantages. For example, it simplifies programming, eliminates redundancies, helps standardize the diagnostics, and makes it significantly easier to read the program listing, should that become necessary.

- Fixed and Variable Data Storage Area The fixed storage area is used to store program constants such as fixed ASCII messages and test operands. variable data storage area provides temporary buffer areas for storage of terminal input and output, program stack operations, various test data patterns, and so forth.

Operability Tests - Again, hardware (FRU) and functional operability tests are designed to detect and isolate solid hardware faults. That is, they are designed to test the basic ability of the hardware to operate. The major difference between these two types of diagnostics is their degree of fault resolution or isolation.

- Hardware (FRU) Tests Hardware (FRU) tests attempt, through a logical analysis of the symptoms, to isolate the faults to the specific field replaceable unit (FRU) causing the failure. Thus, in most cases, the need to analyze hardware (FRU) tests at the machine language level is eliminated. exception, of course, is when the test detects a fault but is unable to identify the failing FRU. In this case an analysis of the test would be required.

- Functional Tests Functional tests, on the other hand, only isolate to the failing function (i.e., instruction or operation). From that point the technician must analyze the failing test or subtest at the machine language level and determine which component or field replaceable unit is causing the failure.

Main Diagnostic Segment The main diagnostic segment of an operability diagnostic (as mentioned earlier) consists of a series of individual test routines. Each test routine is designed to check one specific hardware function. When a function can be checked in more than one way (e.g., an adder or multiplexer with several data and gating inputs) then the test routine for that function is usually divided into subtests. Each subtest will in turn, test one aspect of the function until the function is completely tested. Refer to Figure 7.

Figure 7. Internal Structure of Operability Tests

Each test or subtest in the main diagnostic segment of an operability diagnostic is composed of three major sections of machine language code.

- 1. INIT The INIT or initialization code preconditions the hardware for testing. This may involve tasks such as resetting the hardware, checking to assure that no error conditions already exist, setting and clearing status bits, generating test operands, and building channel command lists and data buffers. Service routines are frequently used to accomplish many of the tasks involved in test initialization.

- 2. EXECUTE The execute code usually consists of a machine language instruction that will cause the function or operation under test to activate. Occasionally two or more instructions may be required for this purpose.

- 3. CHECK The checking code determines if the hardware responded properly. Most often this involves reading hardware status registers and checking buffers for correct data. Typically, an error checking service routine is used for this purpose. The expected results of the test are passed to the error checking service routine by the test INIT code. The actual test results are passed to the routine by the CHECK code. The error checking service routine compares the expected results with the actual results and determines if an error has been detected.

ERROR - If an error is detected, the program may respond in a number of ways. For example, it may print an error message, ring the bell on the user's terminal, halt, go on to the next test, or loop on the failing test. How a program responds to an error depends largely upon the state of the program control switches and initial operator dialogue.

NO ERROR - If no errors are detected, program control will generally proceed to the next test or subtest in the sequence. The program will continue in this manner until either an error is detected, or until each hardware function or FRU has been completely tested for solid faults.

In summary, operability tests are designed to systematically test each individual instruction, operation, or function that the hardware is capable of executing. Thus, they are best suited to detect solid hardware faults and isolate the cause to the failing function or field replaceable unit (FRU).

Exercisers - As mentioned earlier, subsystem exercisers and system exercisers are similar both in design and in use.

- Subsystem Exercisers Subsystem exercisers are designed to generate maximum subsystem interaction by operating the control unit, data channel (if present), and one or more storage or I/O devices at or near full capacity. They may be used to localize a subsystem failure to the control unit, channel, or device causing the failure. However, they are primarily intended to troubleshoot (intermittent) reliability, internal priority arbitration, and device and device bus interaction faults.

- System Exercisers System exercisers are designed to generate maximum system interaction by operating the processor, storage, and I/O subsystems at or near full capacity. They may be used to localize a system malfunction to the subsystem or device causing the failure. However, system exercisers are primarily intended to troubleshoot (intermittent) reliability, priority arbitration, and subsystem interaction faults.

In summary, when using exercisers keep these points in mind:

- Exercisers are designed to troubleshoot the so-called intermittent class of failure. They should never be used to troubleshoot solid faults or faults that can be detected and isolated using an operability test.

- 2. Exercisers operate on the assumption that certain hardware error checking logic is functional (e.g., parity checking networks, time-out logic, etc.). In many cases exercisers use this logic as an indication that an error has occurred. Therefore, before using an exerciser for troubleshooting purposes, use the appropriate operability test to verify that no solid hardware malfunctions exist in the error checking logic.

3. Exercisers typically provide extensive operator dialogues and comprehensive error message reports. They do this because the internal structure and control of exercisers tends to be complex. When an exerciser must be used for troubleshooting, use the flexibility of the operator dialogue, the information provided by each error message, and deductive reasoning to determine the cause of the problem. In other words when possible, avoid using troubleshooting techniques that require analyzing the exerciser at the machine language level.

Figure 8 summarizes the overall external structure of maintenance software.

Figure 8. The Big Picture

- Product code

- Product name

- Version of the listing

- Date the program was released

- Name of the group responsible for maintaining the program

- Author(s) of the program.

- Text Section The text section consists of the: 2.

- Abstract (a brief description of the program)

- System requirements and prerequisite programs

- Switches used to control the operation of the program

- Loading, starting, and operating procedures

- Command or test descriptions.

The text section may also include additional information that the author feels is necessary to use or maintain the program.

- 3. History Section - The history section describes each change or revision made to the program since its initial release.

- Document Section The document section outlines the internal organization of the program.

The document section is generated by a program called DECDOC. DECDOC searches through the machine language listing and extracts the subtitle statements and pertinent comments pertaining to each subroutine or section of the program. The listing line number associated with each statement or comment is also extracted. Thus you can review the document file to grasp the big picture. Then, if you need more detail, the listing line number can be used to index into the machine language listing.

Flowcharts - Flowcharts may also be included to describe some of the more complex routines.

The Machine Language Listing - The machine language listing consists of the following six sections:

- Program Title and Definition Section The program title and definitions section defines the assembly switches, program address options, Unimplemented User Operations (UUOs), EMulator Traps (EMTs), accumulators (ACs), macro statements, device codes, I/O bit assignments, and registers.

- Program Parameters (PARAM) Section PARAM defines program operating parameters such as control switches, special subroutine linkages, and OPDEFs.

- 3. Fixed Control and Dispatch Storage (FIXED) - FIXED contains ASCII messages, dispatch tables, push down list control information, various flag definitions, etc.

- Main Code Section This is the main diagnostic program. It contains the program initialization routine, the dispatch routine, and the test or exerciser routines. The service routines are usually located at or near the end of this section.

- 5. Fixed and Variable Storage Area (STOR) The STOR area is reserved for patches, channel lists, error messages, input and output buffers, data patterns, etc.

- 6. Cross Reference (CREF) The CREF lists, alphabetic order, each symbol or symbolic address used by the program. It lists every listing line number which references the symbol as well as the line number at which the symbol is defined.

In esense, the program description tends to be quite detailed because it must meet the needs of both the users (i.e., manufacturing and field maintenance personnel) and the diagnostic programmer responsible for maintaining the program after it is released. Typically, the text section fulfills the needs of the user, and the history, document, and flowcharts fulfill the needs of the program maintainer. The machine language listing fulfills the needs of anyone requiring a detailed understanding of the internal operation of the program.

NOTE-

Do not confuse the organization of the diagnostic listing with the internal structure of the diagnostic program described earlier.

# Diagnostic Hierarchies

The diagnostic programs in a maintenance library are organized into hierarchies. A hierarchy defines the order in which a set of related diagnostics must be run in order to assure that a unit or subsystem is thoroughly tested. There is a diagnostic hierarchy for the central processing unit as well as one for each of the storage and I/O subsystems. Refer to Figure 10.

Figure 10. Typical Diagnostic Hierarchies

Ideally each diagnostic hierarchy consists of a:

- Hardware (FRU) test to verify that the FRUs (i.e., gates, storage elements, flip-flops, MOS memory, etc.) work independently. (There are no solid faults.)

- Functional test to verify that the individual gates and storage elements, etc., work collectively to perform their assigned functions. (Again, there are no solid faults.)

- Unit or subsystem exerciser to verify that the functions work together reliably to:

- Process data and control the overall operation of the system (CPU exerciser).

- b. Store and retrieve data (storage subsystem exercisers).

- Input and output information to the user (I/O subsystem exercisers).

At the top the system exerciser ties all the hierarchies together by verifying that CPU, storage, and I/O subsystems work together reliably as a computer.

This, of course, is an ideal diagnostic hierarchy. practice, the hierarchy may vary from library to library. For example:

- Some libraries do not support a full-fledged system exerciser. Instead, they rely on the operating system to perform this function. Each time the operating system detects an error, it captures the error information and records it in an error file. Later using a system library program, the error file can be printed out and the information analyzed. Thus, the operating system becomes, in part, an on-line system exerciser.

- Sometimes the hardware (FRU) test and the functional test will be combined in one program. Occasionally, the exerciser will also be included in the program. Thus it may appear that there is only one diagnostic program for a particular subsystem. This combining technique is frequently used with small I/O

subsystems (i.e., line printers, card readers, terminals, etc.). Since these types of subsystems support a limited number of functions, it is generally more efficient to merge all testing into one program.

- 3. Frequently, large operability tests such as those for the central processing unit, disk, and tape subsystems, are divided into several parts. Sometimes this is done to accommodate systems with a limited amount of main memory. Other times the diagnostics are divided into functional areas of logic for convenience (For example, Part 1 of a processor diagnostic may test the internal word and byte transfers, Part 2 may test boolean instructions, Part 3 may test arithmetic instructions, etc.). In many cases, dividing diagnostics into parts accounts for the seemingly large number of individual diagnostic programs in many maintenance libraries.

- Most maintenance libraries do not support a full set of hardware (FRU) tests. There are two reasons for this. First, hardware (FRU) tests require a working processor to analyze symptoms and isolate the field replaceable unit causing the failure. hardware (FRU) tests for processors are generally restricted to those systems that have a separate maintenance console subsystem (i.e., KL10s, VAX11/780s, etc.). Secondly, because some storage and I/O subsystems are composed of a limited number of field replaceable units (three or four), their size does not warrant hardware (FRU) diagnostics.

- Finally, it is worth mentioning that the title or name given a particular diagnostic does not necessarily conform to the four generic types of diagnostics mentioned earlier (i.e., system exerciser, subsystem exerciser, functional test, and hardware FRU test). The title given a diagnostic attempts instead to describe what the diagnostic does. For example, the following are some typical titles given diagnostics:

Basic Instructions #1 CPU/PI/Memory Reliability Memory Port Interaction DQll Basic Logic Test Part 2 KGll Communications CRC Test

Note that the title of a diagnostic does not explicitly state its relative position in a hierarchy. For this reason either the diagnostic listing or a table of diagnostic hierarchies must be consulted in order to assure that the proper tests are run in the proper order. Refer to the  $10/10~\mathrm{STD}$  module in the  $10\mathrm{-Based}$  10 section of the KL10 Maintenance Guide for some examples of diagnostic hierarchy tables.

11- BASED 11 **MAINTENANCE** LIBRARY UTILITY CONTROL DIAGNOSTIC PROGRAM FILES **PROGRAMS** MR-3450

The 11-Based 11 Maintenance Library

#### GENERAL DESCRIPTION

The 11-Based 11 Maintenance Library is a standard maintenance software library. The library is written in PDP-11 machine language and is designed to detect and isolate faults in PDP-11 based systems and subsystems.

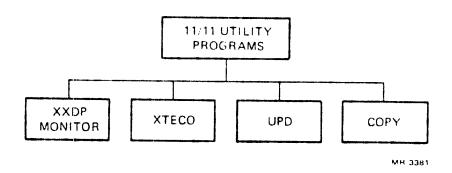

# 11-BASED 11 UTILITIES PROGRAMS

The library contains four major utility programs: XXDP, XTECO, UPD, and COPY. See Figure 1.

Figure 1. The Four Major 11-Based 11 Utility Programs

XXDP - XXDP is the basic diagnostic monitor, where XX is the input media designator, (e.g., RPDP uses an RPll and disk pack for input, RXDP uses an RXll and floppy for input, TCDP uses a TCll and DECtape

for input etc.). Basically the monitor allows you to load and run either a single diagnostic or utility program (via direct commands) or a sequence of programs (via a control or chain file).

- XTECO XTECO is an editor program. It enables you to construct and modify ASCII text files. Primarily the editor is used to construct and modify control files and short test programs.

- UPD UPD is a utility program used to update 11-based 11 utility and diagnostic programs.

- COPY COPY is a utility program used to duplicate maintenance software storage media.

Like most utility programs, the 11-based 11 utility programs are relatively easy to use because they are controlled by task-oriented commands.

STOP-

Before proceeding further, review the summary modules for XXDP, XTECO, UDP and COPY in the 11-Based 11 section of the KL10 Maintenance Guide.

# 11-BASED 11 DIAGNOSTIC PROGRAMS

There are very few hardware (FRU) tests in the 11/11 maintenance library. Most of the diagnostics are either functional tests or exercisers.

# INTERNAL STRUCTURE AND CONTROL

The internal structure of the 11-Based 11 Maintenance Library is illustrated in Figure 2.

Figure 2. 11-Based 11 Memory Utilization Map

- LOC 0 through 776 With the exception of locations 200 through 210, locations 0 through 776 are reserved for interrupt vector addresses. Location 200 contains a jump to the starting address of the diagnostic. Locations 201 through 210 are optional starting addresses.

- LOC 1000 Most diagnostics begin around location 1000. Each diagnostic consists of the standard program initialization and control routine, the main diagnostic segment, the service routines and the fixed and variable data storage area.

- Monitor The diagnostic monitor (XXDP) consists of approximately 2000 words and resides in the upper 2K of memory. The memory between the end of the diagnostic and the beginning of the diagnostic monitor is available for use by the diagnostic.

Peripheral and Register Addresses - These locations address the standard PDP-11 registers and peripheral devices. This area is always in the uppermost 4K of PDP-11 addresses.

The standard control flow described earlier in the introductory module are applies to the 11-based 11 diagnostics. That is, the program control and initialization routine initializes the system, reads and diagnostics. stores the state of the program control switches, performs operator dialogue, and dispatches to the test routines. The test or exerciser routines perform the testing using the various service routines as necessary. Faults are reported as they are detected. When testing is complete, control is returned to the diagnostic monitor or calling program.

# 11-BASED 11 SYSTEM EXERCISER

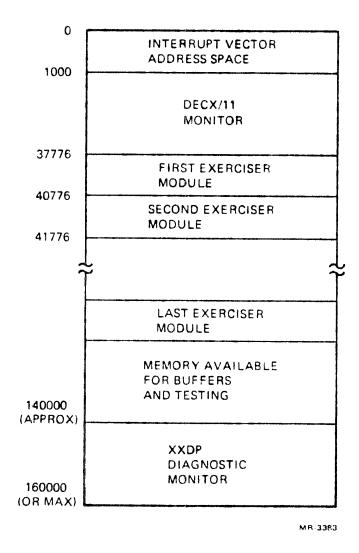

Because of the wide range of options available on a PDP-11 system a single common system exerciser is not practical. Instead, the 11/11 Library uses a modular exerciser referred to as DECX/ll. The exerciser may be assembled in the field to match any standard PDP-11 system configuration.

The exerciser consists of a monitor or control module and a set of individual exerciser modules. Refer to Figure 3 for a detailed view of the memory utilization map.

The exerciser is assembled using a utility program referred to as the Configurator. Via operator dialogue, the Configurator will request that you specify the version of the monitor module to use and the name of each exerciser module to be included in the final version of the DECX/11 exerciser. There are five basic monitors to choose from, each of which supports different features and internal CPU options (e.g., Unibus mapping, memory parity checking, memory management, and cache, etc.). In addition, there are approximately 95 individual exerciser modules, one for each major storage and I/O subsystem available on a PDP-11 system.

Figure 3. DECX/11 System Exerciser Memory Utilization Map

After all the modules are specified, the Configurator will link them together and automatically save the newly assembled exerciser. The exerciser can now be run under the XXDP diagnostic monitor any time the need arises. Keep in mind, however, that all the appropriate operability tests should be run before using an exerciser for fault isolations.

# GENERAL DESCRIPTION

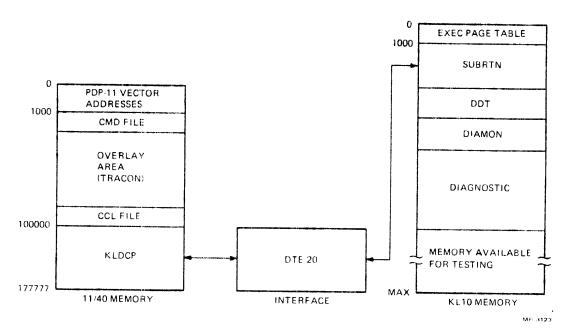

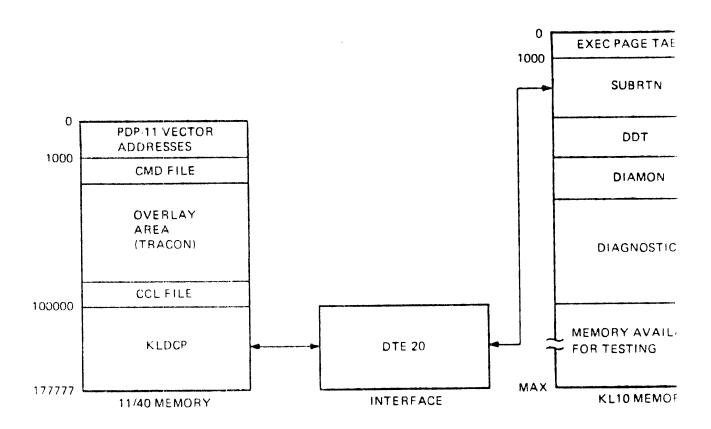

The 11-Based 10 Maintenance Library is written in PDP-11 machine language and converts the KL10 operator console subsystem into a diagnostic console subsystem. The KL10 Diagnostic Console Program (KLDCP) performs the conversion. KLDCP is loaded from an 11/40 storage subsystem, DECtape, floppy, or disk (KLAD-10 or KLAD-20). The load operation is controlled by the BM873 ROM in the 11/40 processor. to Figure 1, which illustrates the 11/40 maintenance console front-end subsystem.

Figure 1. 11/40 Maintenance Console Front-End Subsystem

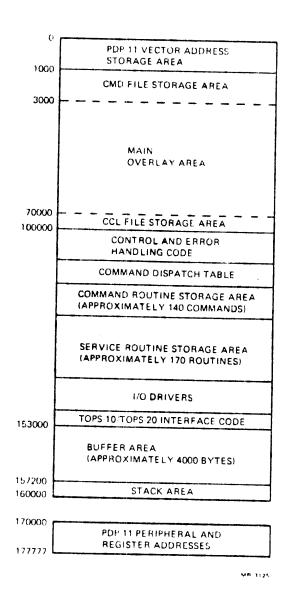

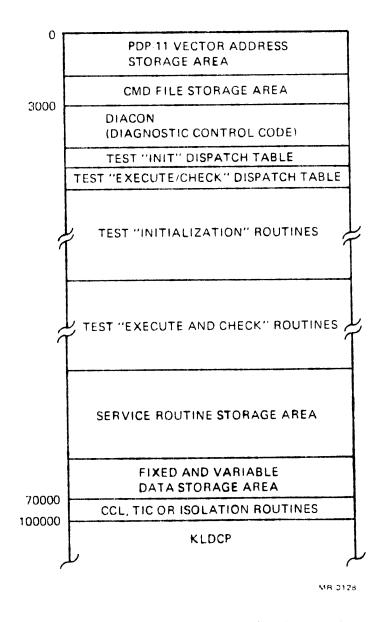

Figure 2. 11/40 KLDCP Memory Utilization Map CONSOLE

- PDP-11 Vector Address Storage Area This area is used to store the vector addresses associated with the DTE20 and other PDP-11 storage and I/O devices.

- CMD File Storage Area This section of the overlay area is used to store and execute double-indirect control files. A double-indirect control file is It may be used to execute single unrestricted. 11/10 utility commands, call indirect control files (CCL files), and to load and run 11/10 or 10/10 utility and diagnostic programs.

- Main Overlay Area This area is used for loading and running 11-based 10 utility and diagnostic programs.

- CCL File Storage Area This section of the overlay area is used to store and execute indirect control files. Indirect control files are restricted to certain types of 11/10 utility commands. example, they should not contain commands that will load and run other indirect control files, utility programs, or diagnostic programs. A double-indirect control file should be used for this purpose. This section of the overlay area is also used for storing and executing TIC files and isolation routines. This will be discussed later.

- Control and Error Handling Code This code initializes the system, controls command processing, and handles errors.

- Command Dispatch Table Base commands are compared to this table. The table provides the starting address of the command routine.

- Command Routine Storage Area Approximately 140 command routines are stored here, one for each KLDCP command.

- Service Routine Storage Area These routines are used by the command routines to perform various tasks (number conversions, checksum operations, message formatting and printing, etc.).

- I/O Drivers This code handles the 11/40 storage and I/O subsystem input and output operations.

- TOPS10/20 Interface Code This code interfaces the CTY with the operating system that is directing and monitoring the KL10 (TOPS-10 or TOPS-20). Nothing fancy goes on here. KLDCP simply passes the characters it receives from the CTY to operating system and, conversely, prints operating system responses on the CTY.

- Buffer Area This is a general buffer area used for temporary storage of input and output information. It can handle approximately 4000 (octal) 8-bit bytes.

- Stack Area This area is used to keep track of EMTs, TRAPs and PDP-11 priority interrupts.

- PDP-11 Peripheral and Register Addresses These locations address the standard PDP-11 registers and peripheral devices including the DTE20. This area is always the uppermost 4K of PDP-11 addresses.

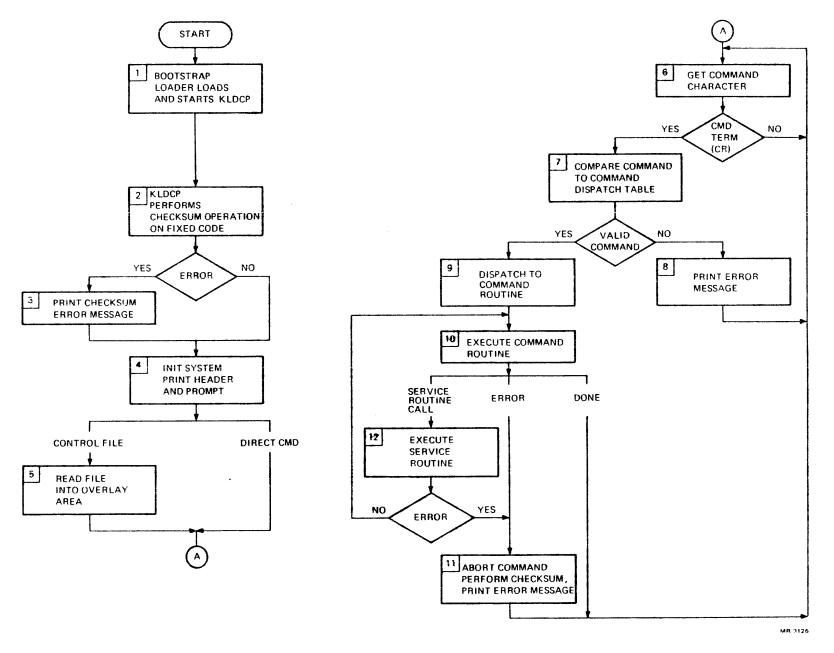

Once loaded, KLDCP performs a checksum operation on its fixed code, initializes the system, prints its header and prompt, and waits for a command to be typed on the CTY or KLINIK line. Refer to Figure 3.

FOR

INTERNAL

USE

ONLY

Figure 3. KLDCP Direct and Indirect Command Processing

The following text explains the basic flow illustrated in Figure 3. The numerals in the text correspond to the numerals in the figure.

- 1. You initiate a read-in operation. The bootstrap loader automatically loads and starts KLDCP.

- 2. KLDCP performs a checksum operation on its fixed code. The result is compared to a precalculated checksum value.

- 3. If—there—is a checksum discrepancy an error message is printed. The newly calculated checksum value replaces the original precalculated value, and KLDCP continues. Checksum errors are not considered fatal. Therefore, you may modify the code, and KLDCP will still run.

- Independent of a checksum error, KLDCP will initialize the system, and print its header and prompt for a command.

- 5. If a control file is used, KLDCP will read it into the appropriate section of the overlay area. It will then get its commands (indirectly) from the control file.

- 6. KLDCP deposits each character of a command in the buffer area. When the command terminator (i.e., carriage return <CR>) is detected, KLDCP will begin processing the command. If a control file is being used, the commands are taken sequentially from the control file.

- 7. KLDCP compares the base command to each entry in the command dispatch table. The entry that matches the base command provides the starting address of the command routine.

- 8. If no match for the base command is found, an error message is printed and KLDCP returns to command input mode.

- 9. KLDCP dispatches to the appropriate command routine.

- 10. The command routine is executed. Unless an error occurs, the command is completed, and control is returned to KLDCP command input mode.

- 11. If an error is detected (i.e., KLDCP is unable to complete the command), the command is aborted. KLDCP then performs a checksum operation on itself to determine if the error caused any code to be modified. If so, a checksum error message will be printed before KLDCP returns to command input mode.

- 12. If the command routine uses service routines, they are called via EMTs and executed. Unless an error occurs, the service routine returns control to the command routine when it is finished. If an error does occur during the execution of a service routine, then the command is aborted, an error message is printed, a checksum is performed, and control is returned to KLDCP command input mode.

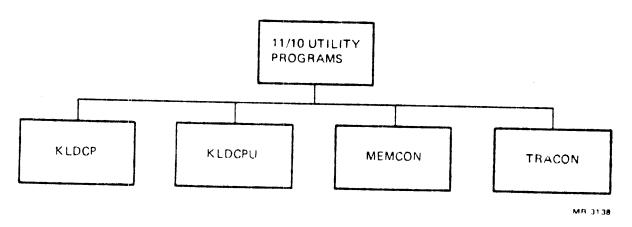

# 11-BASED 10 UTILITY PROGRAMS

In addition to KLDCP there are three other major utility programs in the 11-Based 10 Maintenance Library. Refer to Figure 4.

Figure 4. 11/10 Utility Programs

- KLDCPU A utility program designed to simplify duplicating and maintaining the 11/10 storage media (DECtape, floppy and KLAD-10 packs).

- MEMCON A utility program designed to simplify configuring KL10 internal and external main memory.

- TRACON A hardware utility program designed to aid in troubleshooting KL10 processor, memory, and channel faults.

KLDCP loads these programs into the overlay area of 11/40 memory. Only one utility program may be co-resident with KLDCP at any given time.

#### -----STOP

Before proceeding further, review the summary modules for KLDCP, MEMCON and TRACON in the 11-Based 10 section of the KL10 Maintenance Guide.

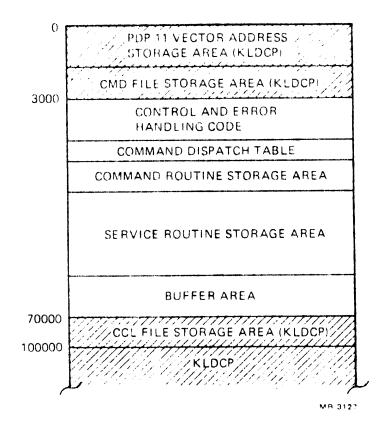

# Internal Structure and Control

The internal structure of the utility programs is similar to the internal structure of KLDCP. See Figure 5.

The method these utility programs use to process commands is also similar to the method used by KLDCP to process commands. That is:

- 1. Once loaded and started, the utility prints its header and prompt.

- 2. You type a command or submit a control file for execution.

- 3. The utility program compares the base command to its command dispatch table and dispatches to the appropriate command routine.

- 4. The command routine executes the command using service routines, if necessary, and returns to the utility program's command input mode when finished.

Figure 5. Internal Structure of 11/10 Utility Programs

If a utility program is unable to find the base command in its command dispatch table, control is returned to KLDCP. KLDCP will then attempt to execute the command and return control to the utility. If KLDCP is unable to execute the command, an error message will be printed. Then control will be returned to the utility.

# 11-BASED 10 DIAGNOSTIC PROGRAMS

The ll-based 10 diagnostics are predominantly hardware (FRU) tests. They load into the overlay area and are designed to detect faults in the DTE, EBox, cache, MBox, main memory and channels. They are also designed to isolate the cause of the fault to the smallest field replaceable unit (i.e., module, cable or backplane). In order to achieve this level of fault isolation the diagnostics frequently use TIC files and isolation routines.

----- STOP --

Before proceeding further, review several of the diagnostic summary modules contained in the 11-Based 10 section of the KL10 Maintenance Guide.

#### TIC Files

TIC files (sometimes referred to as clock scan routines) are used by some 11-based 10 diagnostics to isolate a fault to the failing clock tick. TIC files are generated during the development of the diagnostic by single-stepping the execute phase of each test and subtest in the diagnostic. (Recall that tests and subtests have three parts: the init, the execute and the check.) The machine state change at each clock tick is read (via diagnostic read functions) and saved in a TIC file. Later, when the diagnostic is being used to isolate a fault, the appropriate TIC file is read into the CCL file storage area of memory. Then the execute phase of the test that detected the fault is single-stepped, and each machine state is compared to the machine state stored in the TIC file until a difference is found. many 11-based 10 diagnostics are able to isolate a fault to a specific clock tick.

## **Isolation Routines**

Isolation routines are also loaded into the CCL file storage area of memory, and they are used to isolate the cause of a hardware fault. They use the 11/40 processor to analyze the symptoms detected by a failing test in order to isolate the cause to the faulty field replaceable unit (FRU). Typically, an isolation routine will perform some additional testing using key symptoms and a look-up table to determine the most probable failing FRU. A typical isolation routine output is illustrated below.

## EXAMPLE: A Typical Isolation Routine Output

CABLE LOC:04-1. M8519. LOC:04-7.\*\*

M8515. LOC:04-28. M8538. LOC:04-33.

M8512. LOC:04-43. M8528. LOC:04-44. M8537. LOC:04-20. M8525. LOC:04-35. M8530. LOC:04-47.

\*\*HIGHEST PROBABILITY OF FAILURE

EBUS BIT 20. IS STUCK AT 1.

ANY ONE OF THE ABOVE LIST OF BOARDS MAY BE AT FAULT. ANY ONE OF THE ABOVE LIST OF BOARDS MAY BE AT FAULT. THIS FAULT IS BEST ISOLATED BY LOOKING AT THE EBUS LINE AND PULLING BOARDS ONE AT A TIME UNTIL THE BOARD WHICH IS HANGING THE BUS IS FOUND. IF THIS FAILS, THE EBUS WIRING IN THE BAKPLANE SHOULD BE CHECKED. HC TO CONTINUE CONVERGENCE OR LOOP ON ERROR. SED TO RESTART

PRG HALT AT 006222

PRG HALT AT 006222

# Internal Structure and Control

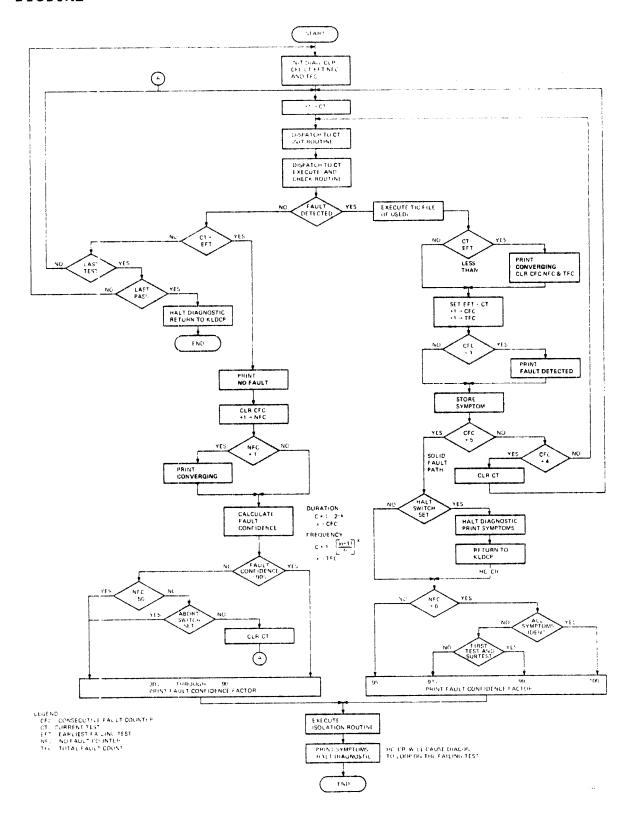

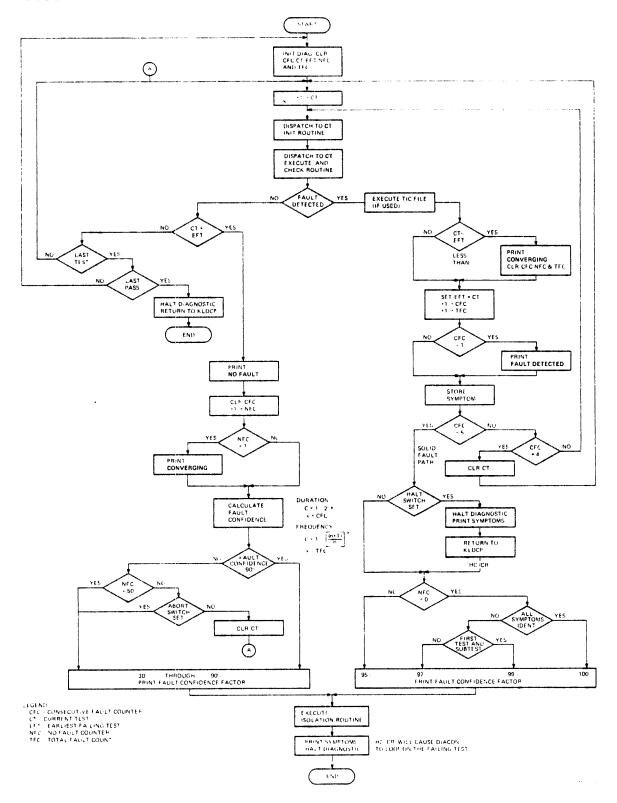

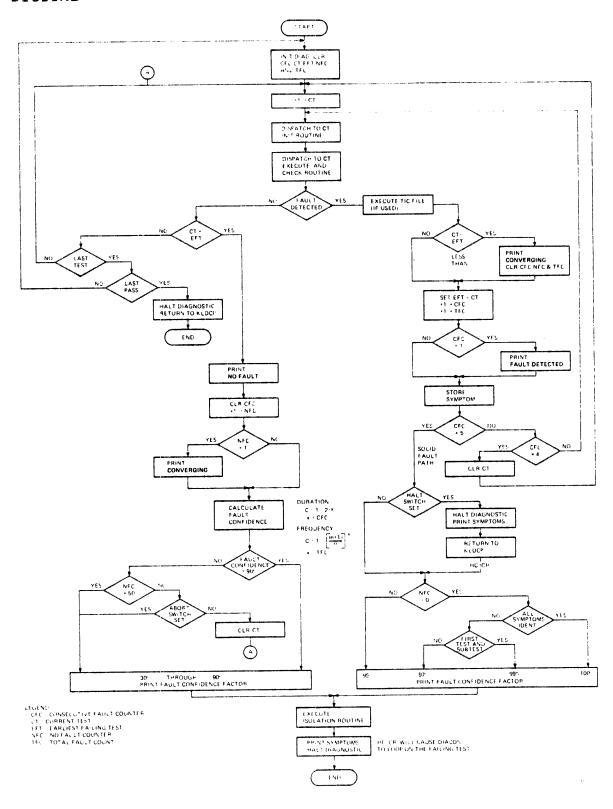

As mentioned earlier, 11-based 10 diagnostics are predominantly of the hardware (FRU) type. That is, they consist of a series of independent tests designed to isolate a fault to the failing FRU. Their internal structure, however, differs in two ways from the basic hardware (FRU) structure described earlier in the introductory module. First, the initialization section of each test is separate from the execute and check section. And secondly, each diagnostic is assembled with a common DIAgnostic CONtrol code, referred to as DIACON. See Figure 6.

DIACON provides both external and internal diagnostic control. Externally, DIACON (via operator dialogue) provides for test selection and test looping. Internally, DIACON handles:

Figure 6. Internal Structure of 11/10 Diagnostics

- Program initialization

- Test dispatching

- Error reporting

- TIC file and isolation routine execution, if they are external to the main diagnostic

- Fault convergence

- Fault confidence calculation

\_\_\_\_\_ STOP \_\_\_\_

Before proceeding further, review the DIACON summary module in the 11-Based 10 section of the KL10 Maintenance Guide.

Fault convergence and fault confidence calculation are concerned with intermittent hardware faults. convergence is a method used to establish that the test reporting the fault is also the earliest test in the diagnostic that is able to detect the fault. confidence calculation on the other hand is a method of establishing that the symptoms (which are intermittent) are the best indication of the fault. That is, fault confidence is the percentage of probability that the symptoms reported by the failing test are the same as they would have been, had the fault been solid. For further clarification refer to Case Studies 5 and 7, which follow Figure 7.

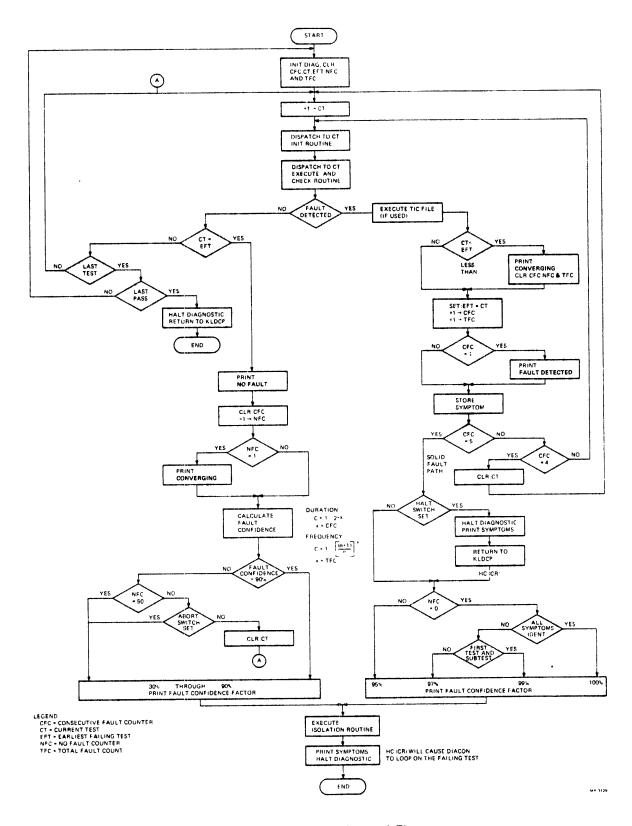

Figure 7 illustrates the major control functions performed by DIACON. The case studies following Figure 7 describe how DIACON handles various solid and intermittent fault conditions.

Figure 7. DIACON Control Flow

Case 1: No Faults - Assume a diagnostic runs error-free. No faults are detected.

- 1. DIACON initializes the diagnostic, clearing the major software registers and counters.

- 2. The current test (CT) is incremented by one. DIACON dispatches to the initialization routine for Test 1. Then DIACON dispatches to the execute and check routine for Test 1. No faults are detected.

- 3. The current test (CT) does not equal the earliest failing test (EFT) because EFT was initialized to zero and has not changed.

- 4. Is this the last test? No. Increment CT and repeat the processes.

- 5. Is this the last test? Yes. Last pass? No. Clear the major software registers and counters (CT is reset to 0). Rerun the entire diagnostic.

- 6. Is this the last test? Yes. Last pass? Yes. Halt the diagnostic and return control to KLDCP.

Figure 7. DIACON Control Flow

11/10-21 FOR INTERNAL USE ONLY

Case 2: 100% Confidence - Assume that a solid fault is detected by Test 8.

- 1. The diagnostic runs as described in Case 1 until Test 8 detects a fault. If a TIC file is used, it will be executed at this time.

- The current test (CT) is not less than the earliest failing test (EFT) because CT = 8 and EFT was initialized to zero and has not changed.

- 4. EFT is now set equal to CT (both = 8), and the consecutive fault counter (CFC) and the total fault counter (TFC) are both incremented. CFT now equals one. FAULT DETECTED is printed, and the fault symptoms are stored.

- 5. Test 8 is executed three more times. Then CT is reset to zero and Tests 1 through 8 are run one more time. (CFC should now equal 5, one count for each time Test 8 detected the fault.)

- 6. Assume the HALT ON ERROR program control switch is set. The diagnostic is halted, and the fault symptoms are printed. Then control is returned to KLDCP. The KLDCP Halt Continue command (HC<CR>) will continue the diagnostic; fault confidence will be calculated and fault isolation performed. A second HC<CR> at this time will cause DIACON to loop on the failing test (TEST 8).

- 7. Assume that the HALT ON ERROR switch is reset, that the no fault counter (NFC) equals zero (from program initialization) and that all five consecutive fault symptoms associated with Test 8 are identical. The probability that Test 8 is the earliest test able to detect the fault, that the symptoms are indicative of a solid fault, and that the output of the isolation routine will be accurate is calculated to be 100%.

- 8. The fault confidence factor is printed and the isolation routine run. Then the results are printed, the diagnostic is halted, and control returned to KLDCP. The KLDCP HC<CR> command may be used at this time to cause DIACON to loop on the failing test (Test 8).

Figure 7. DIACON Control Flow

Case 3: 99% Confidence - Assume that the first test and subtest in the diagnostic detected five consecutive faults, but that in all five cases the fault symptoms were not identical. The probability that this (Test 1, Subtest 1) is the earliest test able to detect the fault, that symptoms are indicative of a solid fault, and that the output of the isolation routine will be accurate, is calculated to be 99%. A 1% probability of inaccuracy is introduced because all five symptoms were not identical.

Case 4: 97% Confidence - Assume that Test 8 detected five consecutive faults but that in all five cases the fault symptoms were not identical. The probability that this testis the earliest test able to detect the fault, that the symptoms are indicative of a solid fault, and that the output from the isolation routine will be accurate, is calculated to be 97%. A 3% probability of inaccuracy is introduced because Test 8 is not the first test in the diagnostic and because all five fault symptoms were not identical.

Figure 7. DIACON Control Flow

11/10-25 FOR INTERNAL USE ONLY

Case 5: Converging - An Intermittent Failure - Assume that Test 8 is the first test in the series to detect a fault. However, when it was being run for the fifth time, an earlier test, Test 4, detected the fault. This has to be an intermittent fault because Test 4 did not initially detect the fault. In this case, the following occurs:

- The diagnostic runs as described in Case 2 until the consecutive fault counter (CFC) equals four. the current test (CT) is cleared, and the diagnostic is restarted at Test 1.

- 2. Tests 1 through 3 run, but Test 4 detects a fault. At this point the current test (CT) is less than the earliest failing test (EFT) (CT = 4 and EFT = 8). Therefore, CONVERGING is printed and the consecutive fault counter (CFC) is cleared (Formerly it contained a count of four from Test 8). addition, the total fault count (TFC) is cleared because this is a new failing test. The no fault counter (NFC) is also cleared, although it was already clear as a result of program initialization.

- 3. The earliest failing test is then set equal to the current test (4), and the consecutive fault counter is incremented to one. FAULT DETECTED is printed and the new symptoms for Test 4 are stored.

- 4. Next Test 4 is run three more times. Then once again tests 1 through 4 are run. Assuming that test 4 fails solid and that no earlier test detects a failure, DIACON proceeds as described in Case 2, steps 6, 7, and 8.

- The only apparent difference between the results 5. produced in this case and the results produced in Case 2 is that the message CONVERGING is printed. This message alerts you to the fact that the fault which now appears to be solid was at one time intermittent.

Figure 7. DIACON Control Flow

Case 6: 95% Confidence - An Intermittent Fault - Suppose Test 8 detected three consecutive faults but on the fourth try the fault went undetected. Then at the FAULT DETECTED decision block the path to the left would be taken.

1. At the decision block, current test (CT) equals the earliest failing test (EFT), the answer is Yes (both CT and EFT equal 8). Therefore, NO FAULT is printed, the consecutive fault counter (CFC) is cleared, and the no fault counter (NFC) incremented to one. Finally CONVERGING is printed and fault confidence is calculated.

Note that the NFC is incremented each time the earliest failing test is unable to detect the original fault.

- 2. Assume that a 90% fault confidence has not been established. In addition, the no fault counter (NFC) has not reached a count of 50 and the ABORT TEST program control switch is not set. Then the current test (CT) is cleared and Tests 1 through 8 are repeated.

- 3. Now assume that Test 8 detects five consecutive faults. Then the answer to the decision block "no fault count (NFC) equals zero" (located in the lower right section of the flow) is No. In this case NFC equals 1.

- 4. Now the probability that this (Test 8) is the earliest test able to detect the fault, that the symptoms are indicative of a solid fault, and that the output of the isolation routine will be accurate is calculated to be 95%. A 5% probability of inaccuracy exists because Test 8 is not the first test in the diagnostic and because at least once Test 8 was unable to detect the fault.

- 5. With the fault confidence calculated, the fault isolation routine is run and the results printed. Then the diagnostic is halted, and control is returned to KLDCP. The KLDCP HC<CR> command may be used at this time to cause DIACON to loop on the failing test (Test 8).

Case 7: 30% Through 90% Confidence - An Intermittent Fault. DIACON will attempt to establish a 90% fault confidence factor for intermittent failures unless interrupted by:

- The no fault counter (NFC) reaching a count of 50 indicating that the fault has gone away.

- The operator setting the ABORT TEST program control switch.

In both cases DIACON will print the fault confidence factor calculated up to that point and cease further calculation. In the second case, however, the operator may type HC<CR> to continue calculation.

DIACON uses two methods to calculate the percentage of fault confidence. The first method is based upon fault duration. The following formula is used:

$$C = 1-2^{-x}$$

where x is the value of the consecutive fault counter (CFC).

Applying this formula, DIACON will calculate the following:

| 1 | CFC              | Percentage                | of | Fault | Confidence |

|---|------------------|---------------------------|----|-------|------------|

|   | 2<br>3<br>4<br>5 | 50%<br>75%<br>88%<br>99%+ |    |       |            |

The second method used by DIACON to calculate fault confidence is based upon the frequency of the fault. following formula is used:

$$C = 1 - \left[ \frac{(n-1)}{n} \right]^{-x}$$

where x is the value of the total fault count (TFC) (i.e., the total number of nonconsecutive faults), and n is the number of the earliest failing test (EFT).

Applying this formula, suppose Test 3 detected 2 nonconsecutive failures before fault confidence was interrupted. Then:

$$56\% = 1 - \left[ \frac{2}{3} \right]^2$$

Had Test 3 detected four nonconsecutive failures, then:

$$80\% = 1 - \left[\frac{2}{3}\right]^4$$

It should be clear that when DIACON prints CONVERGING, it is doing very useful work. That is, it is attempting to converge on an intermittent fault. Depending on both the length and complexity of a particular diagnostic and the nature of the fault, fault convergence may range from several minutes to nearly a half-hour.

#### ----STOP---

Before taking the following module test, refer to the 11-Based 10 section of the KL10 Maintenance Guide. Review the 11/10 STD module and the summary modules for the 11/10 utility and diagnostic programs. Doing so will expand your current understanding and provide some practical insight into the overall organization and structure of the 11-Based 10 Maintenance Library.

The 10-Based 10 Maintenance Library

## GENERAL DESCRIPTION

The 10-Based 10 Maintenance Library is written in PDP-10 machine language and is designed to detect and isolate faults in the PDP-10 processor, storage and I/O subsystems. The majority of these maintenance programs will run in either user mode (for on-line maintenance) or executive mode (for stand-alone maintenance). Both modes of operation will be discussed later.

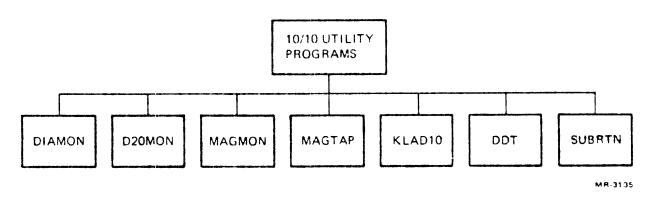

## 10-BASED 10 UTILITY PROGRAMS

The 10-Based 10 Maintenance Library supports seven major utility programs. Their purpose is to simplify both using and maintaining the maintenance library. Refer to Figure 1.

Figure 1. Major 10/10 Utility Programs

- DIAMON DIAMON is the basic diagnostic monitor. It can handle three types of input media: paper tape, DECtape, and disks having a TOPS-10 file structure. The monitor allows you to load and run a single diagnostic program (via direct commands) or to load and run a series or hierarchy of diagnostic programs (via a control file).

- D20MON D20MON is a variation of DIAMON. D20MON supports the same features as DIAMON; however, it is designed to handle disks having a TOPS-20 file structure.

- MAGMON MAGMON is another variation of DIAMON.

MAGMON also supports the same features as DIAMON;

however, it is designed to handle magtape as an input medium.

- MAGTAP MAGTAP is a utility program designed to generate diagnostic magtapes for use with MAGMON.

MAGTAP also supports the command necessary to transfer files from magtape to disk.

- KLAD10 KLAD10 is a program used to construct the 6,11 maintenance area on KLAD-10 disk packs. KLAD10 reads the files in the 6,10 maintenance area of the KLAD-10 pack, converts them to 16-bit PDP-11 format, and writes them into the 6,11 area.

- KLDDT DDT is a modified version of the system software Dynamic Debugging Technique (DDT) program. The 10/10 version of DDT is a very powerful maintenance tool. It enables you to modify and dynamically control the operation of 10-based 10 programs while they are running.

- SUBRTN SUBRTN is a collection of commonly used service routines. Technically, SUBRTN is not a utility program. It is a package of subroutines that are automatically loaded in conjunction with the 10-Based 10 Maintenance Library. Note that the use of SUBRTN is transparent to you as the user. You have no control of its use or operation.

SUBUSA.

Before proceeding further, review the DIAMON, D20MON, MAGMON, MAGTAP, KLAD10, DDT and SUBRTN summary modules in the 10-Based 10 sections of the KL10 Maintenance Guide.

Normally, utility programs are also required to maintain the control files, diagnostic programs, and maintenance storage media. The 10-based 10 library, however, uses system software programs for this purpose in the following manner:

- Storage media (DECtape, floppies, disk, etc.) are maintained by system programs such as COPY and the Peripheral Interchange Program (PIP).

- Program maintenance is provided for by the system editor program. The editor also may be used to generate or modify maintenance control files.

System software can be used for storage media and program maintenance because both the 10-Based 10 Maintenance Library and the system software use the same file structure and program format.

# LOADING AND STARTING METHODS

Systems prior to the KL10 use a conventional hardware read-in switch and a set of I/O device select switches to initially load the 10/10 Maintenance Library. The read-in switch causes the boot program on the selected I/O device to load into memory and start. Once started, the boot program can be directed to load and start either a single diagnostic program or one of the diagnostic monitors.

KL10-based systems, however, use the KLDCP BT command to boot the 10/10 Maintenance Library. KLDCP reads the necessary files from the PDP-11 load device in blocks containing 512 eight bit bytes. The blocks are buffered in eleven memory, then transferred (deposited) through the DTE20 into ten memory. Because the maintenance console (KLDCP) is, in effect, a programmable load device, it can also be directed to load and run (via a control file) a sequence or series of 10/10 programs. The KLDCP B command

is used for this purpose. The B command automatically loads a control file into the CMD overlay area in eleven memory. The control file first directs KLDCP to load and run the ll/l0 diagnostic hierarchy. Then, after it has set up ten memory, it directs KLDCP to load and run the l0-based l0 processor and memory functional tests.

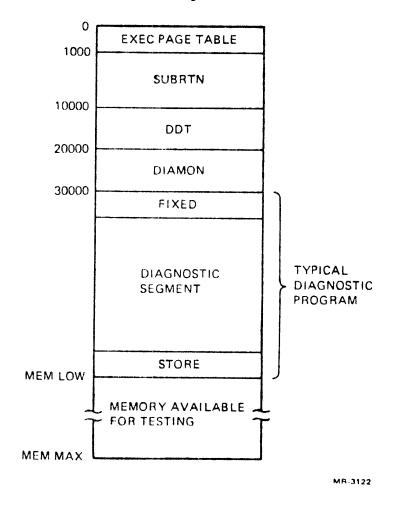

# Internal Structure and Control

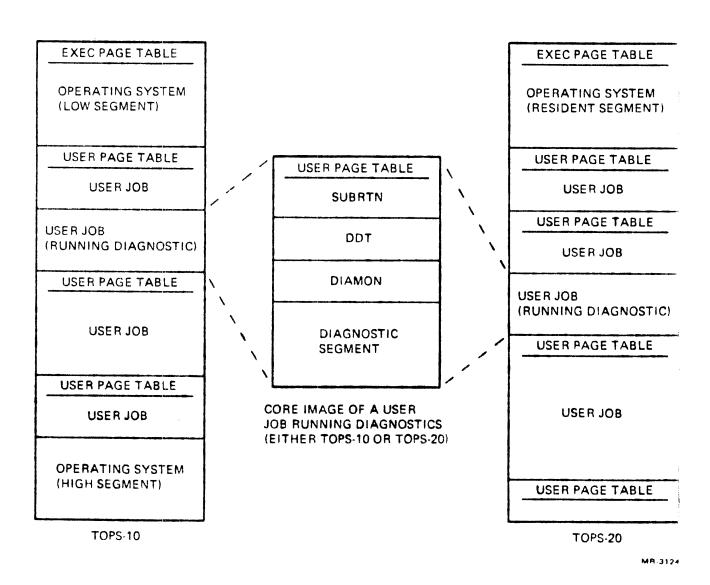

Regardless of the type of processor involved (KA10, KI10 or KL10), the internal structure and control of the 10-Based 10 Maintenance Library is basically the same. This structure is illustrated in Figure 2.

Figure 2. 10-Based 10 Memory Utilization Map

Assuming that a diagnostic monitor (DIAMON) is used, ten memory is structured as follows. First DIAMON is loaded and started. Then DIAMON loads the subroutine package (SUBRTN). If paging is enabled, DIAMON will call a routine in the subroutine package that will construct the executive page The page table consists of the necessary trap handlers (i.e., NXM, APR overflow, etc.) and a page map of all available memory.

After the page table is constructed, DIAMON will load DDT and enter command mode. When directed to do so, DIAMON will load and start a 10-based 10 diagnostic. diagnostic includes the FIXED area, the diagnostic segment, and the STORE area.

The FIXED area contains addresses and other linkages necessary for the diagnostic to communicate with the other program components in ten memory (i.e., DIAMON, DDT, and SUBRTN).

The diagnostic segment and STORE area contain the program initialization and control routine, the test or exerciser routines, any special service routines not available in the subroutine package, and the fixed and variable data storage area.

The 10-based 10 diagnostics use the standard control flow described earlier in the introductory module. That is, the program initialization and control routine initializes the system, reads and stores the state of the program control switches, performs operator dialogue, and dispatches to the test routines. The test or exerciser routines perform the testing using the various service routines as necessary. Faults are reported as they are detected. When testing is complete, control is returned to the diagnostic monitor or calling program.

## 10-BASED 10 DIAGNOSTICS AND KLDCP

In order to run diagnostics in executive mode on a KL10 based system, KLDCP must be resident in the console front-end subsystem. Refer to Figure 3.

Figure 3. Relationship of KLDCP to the 10/10 Maintenance Library

MYXCOU

Once KLDCP has structured ten memory, either the diagnostic monitor (DIAMON) or KLDCP can be used to load and run the 10-based 10 diagnostics. If DIAMON is chosen, the diagnostic will be loaded from the DIAMON load device, usually disk. If KLDCP is chosen, then the KLDCP load devices will be used.

In either case, KLDCP plays an important roll in running First, KLDCP performs all input 10-based 10 diagnostics. and output operations to the console terminal. For example, as you type a command or reply on the terminal, KLDCP builds a buffer in 11 memory. When the command or reply it to the appropriate software complete, KLDCP transfers Conversely, when a 10-based 10 component in ten memory. program wants to output information to you, it builds a KLDCP handles buffer in ten memory and notifies KLDCP. printing the message on the console or KLINIK terminal.

Secondly, KLDCP allows the software components in ten memory to execute console operations (via calls to KLDCP). Thus the 10-based 10 diagnostics running on a KL10-based system have a significant advantage over those running on KA10 and KI10 based systems that use a traditional hardware console. That is, they do not require operator intervention to perform console operations. This greatly increases their ability to diagnose and isolate hardware malfunctions.

Finally, TRACON, the 11-based 10 hardware utility, may be co-resident with KLDCP. Thus when a 10-based 10 diagnostic detects a fault, TRACON can be used to examine the internal status of the processor, main memory, and channels.

# 10-BASED 10 MAINTENANCE SOFTWARE AND USER MODE OPERATION

10-based 10 maintenance software uses the same basic internal structure in user mode as it does in executive mode. This is true for both the TOPS-10 and the TOPS-20 operating systems. Refer to Figure 4.

Diagnostics that run in user mode, however, have one major advantage over diagnostics that run only in executive mode; that is, they do not require the system to run stand alone. Thus, system availability to the customer(s) is never seriously affected.

In fact, relative to the operating system (TOPS-10 or TOPS-20), a diagnostic running in user mode is, in most cases, no different than any other job (program) running in user mode. This, is however, both an advantage and a disadvantage to some user mode diagnostics.

Figure 4. Running 10/10 Diagnostics in User Mode

The advantage is that normally the operating system performs all input and output operations for user mode jobs. This means that if a user mode diagnostic wants to read a file or output a message it need only make the appropriate call to the operating system. Thus, the complexity of writing a user mode diagnostic is reduced somewhat.

The disadvantage, however, is that some user mode diagnostics require direct control over certain I/O operations in order to complete testing. Usually this situation can be avoided by obtaining user mode IOT privileges and then assigning the device to the job. However, this solution is not satisfactory for shared system resources such as disk and tape subsystems since assigning an entire disk or tape subsystem to a single job would, in most cases, seriously affect the performance of the system.

To get around this problem, both the TOPS-10 and the TOPS-20 operating systems support a special diagnostic monitor call called DIAG. DIAG allows the diagnostic to request direct control over a physical channel and either one or all of the devices on that channel. While the DIAG is in effect (usually for less than a second) the operating system will not attempt to access or use the assigned channel. Instead all requests for access will be put in a queue until the diagnostic is finished. As soon as the diagnostic completes its I/O, including reading the status of the device registers, it returns the channel and device to the operating system. The check portion of the test is almost always done after the channel is returned. Thus DIAG makes certain that the user mode diagnostic causes minimal interference of normal system operation.

In summary, then, the major difference between a diagnostic running in executive (stand alone) mode and the same diagnostic running in user mode is that in exec mode the diagnostic must perform all I/O operations by itself but in user mode, the same diagnostic must request privileges in order to perform direct I/O operations. A diagnostic does not request privileges to swap. Swapping is characteristic of any job running in user mode. Its occurance has no effect on the actual execution of the diagnostic.

## SYSTEM AND SUBSYSTEM EXERCISERS

Although the 10-Based 10 Maintenance Library does support some subsystem interaction tests, it does not support a standard system exerciser. Instead, the operating (TOPS-10 or TOPS-20) performs this function. Essentially, each time the operating system detects an error it records the information in a system error file called ERROR.SYS. Later, during preventive or corrective maintenance, a system software program referred to as SYSERR SYSERR reads, formats, and outputs the information is run. in the ERROR.SYS file. The information can then be analyzed, and potential faults can be identified and corrected before the performance of the system is seriously affected.

Using an operating system in this way has two distinct advantages. First, no time is lost running a stand alone system exerciser. And secondly, the error symptoms and conditions reported are real as opposed to simulated. (Remember the objective of a maintenance software system exerciser is to simulate the environment experienced by the system during normal operation).

---STOP-

Before taking the following module test, review the 10/10 STD module and several of the diagnostic summary modules in the 10-Based 10 section of the KL10 Maintenance Guide. Doing so will increase your current understanding and provide some practical insight into the organization structure, and use of the library.

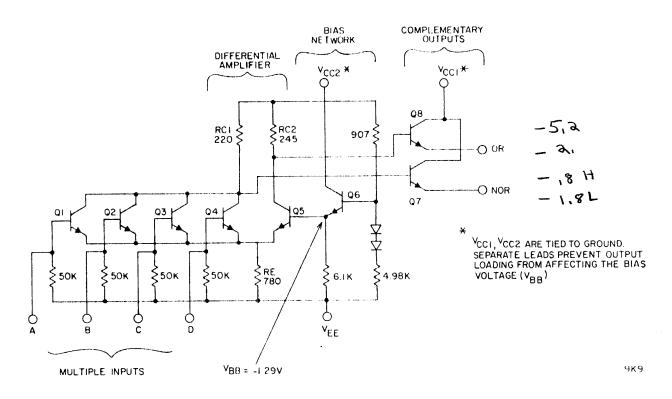

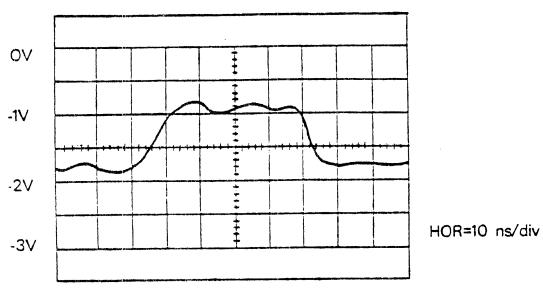

#### EMITTER-COUPLED-LOGIC (ECL)

The emitter-coupled-logic (ECL) microcircuit is, by design, nonsaturating, and therefore avoids transistor storage time and its attendant speed limitation, characteristic of transistor-transistor logic (TTL). The high speed of ECL microcircuits has either or both of two characteristics; switching rates of over 50 megahertz and/or gate propagation delays of less than 6 nanoseconds. In general, the gate propagation delays of ECL logic are approximately 2 nanoseconds.

Some of the salient features of ECL microcircuits are as follows:

- High input impedance/low output impedance properties enable large fanout and versatile drive characteristics.

- Minimal power supply noise generation due to differential amplifier design.

- Nearly constant power supply current drain.