CI20 HARDWARE PORT SPECIFICATION

(REV 03 - MAY 19, 1983) BY: ELBERT BLOOM

# INDEX

| 1.0   | GENERAL OVERVIEW                                                                       |

|-------|----------------------------------------------------------------------------------------|

| 1.1   | REFERENCE DOCUMENTS                                                                    |

| 1.2   | SPECIFIC GOALS                                                                         |

| 1.3   | SPECIFIC NON-GOALS                                                                     |

| 1.4   | BLOCK DIAGRAM                                                                          |

| 1.5   | MECHANICAL DESCRIPTION                                                                 |

| 1.6   | GENERAL LOGICAL OVERVIEW                                                               |

| 1.7   | MICROCODE DESCRIPTION                                                                  |

| 1.8   | COOLING REQUIREMENTS                                                                   |

| 1.9   | MTBF                                                                                   |

| 1.10  | RAMP FEATURES                                                                          |

| 1.11  | PERFORMANCE                                                                            |

| 1.12  | SUBSYSTEM DOCUMENTATION                                                                |

| 1.13  | SYSTEM SOFTWARE                                                                        |

| 1.14  | STANDARDS COMPLIANCE                                                                   |

| 2.0   | EBUS INTFC/PORT ALU MODULE                                                             |

| 2.1   | EBUS CONTROL LOGIC                                                                     |

| 2.1.1 | PI LEVEL 00 INTERRUPTS                                                                 |

| 2.1.2 | PI LEVEL 01 THROUGH 07 INTERRUPTS                                                      |

| 2.2   | MICROPROC TO EBUS REGISTER (EBUF)                                                      |

| 2.3   | EBUS CONTROL AND STATUS REGISTER (CSR)                                                 |

| 2.3.1 | DEFINITION OF THE CONTROL AND STATUS (CSR) REGISTER BITS FOR THE EBUS INTERFACE MODULE |

| 2.4 | EBUS        | TO MICROPROC MUX (EMUX)        |

|-----|-------------|--------------------------------|

| 2.5 | MICE        | OPROC TO EBUS MUX (KMUX)       |

| 2.6 | EBUS        | PARITY GENERATOR               |

| 2.7 | EBUS        | PARITY CHECKER                 |

| 2.8 | EBUS        | TRANSCEIVERS                   |

| 2.9 | ARIT        | HMETIC LOGIC UNIT              |

|     | 2.9.1 CONST | ANT MUX                        |

| 3.0 | CBUS        | -PLI INTERFACE MODULE (CMVR)   |

| 3.1 | CBUS        | TIMING DESKEW PROCEDURE        |

| 3.2 | CMVR        | CONTROL LOGIC                  |

| 3.3 | MICR        | OPROC TO CMVR REGISTER (CBUF)  |

| 3.4 | DATA        | FORMATTER and MOVER (MVR/FMTR) |

| 3.5 | CBUS        | INPUT BUFFER                   |

| 3.6 | CBUS        | OUTPUT BUFFER                  |

| 3.7 | CBUS        | CONTROL LOGIC                  |

| 3.8 | CBUS        | OUT PARITY GENERATOR           |

| 3.9 | CBUS        | IN PARITY CHECKER              |

| 3.1 | O DATA      | INPUT MUX (DMUX)               |

| 3.1 | l PLI       | OUTPUT BUFFER                  |

| 3.1 | 2 PLI       | INPUT BUFFER                   |

| 3.1 | 3 PLI       | PARITY OUT GENERATOR           |

| 3.1 | 4 PLI       | PARITY IN CHECKER              |

| 3.1 | 5 PLI       | CONTROL LOGIC                  |

| 3.1 | 6 PLI       | SERIAL UP MUX (SUMUX)          |

|     |             |                                |

| 3.17         | PLI SERIAL DOWN MUX (SDMUX)    |

|--------------|--------------------------------|

| 3.18         | PLI OUTOUT MUX (PMUX)          |

| 3.19         | CMVR TO MICROPROC MUX (CMUX)   |

| 3.20         | PARITY PREDICTOR               |

| 4.0          | PORT MICROPROCESSOR            |

| 4.1          | CONDITION CODE MUX             |

| 4.1.1        | CONDITION CODE DEFINITIONS     |

| 4.2          | MICROSEQUENCER                 |

| 4.3          | RAM ADDRESS REGISTER           |

| 4.4          | ADDRESS MUX                    |

| 4.5          | LATCH ADDRESS REGISTER (LAR)   |

| 4.6          | CONTROL STORE RAM              |

| 4.7          | CONTROL STORE REGISTER         |

| 4.7.1        | MICROWORD FIELD DEFINITIONS    |

| 4.8          | JMP MUX                        |

| 4.9          | MICROWORD OUTPUT MUX           |

| 4.10         | CRAM LOAD BUFFERS              |

| 4.11         | CRAM PARITY CHECKER            |

| 4.12         | LOCAL STORAGE RAM              |

| 4.13         | LOCAL STORAGE ADDRESS REGISTER |

| 4.14         | RAM MODE MUX                   |

| 4.15         | COND/SKIP FIELD DECODER        |

| 4.16         | MICROPROC CONTROL LOGIC        |

| APPENDIX "A" | DETAILED BLOCK DIAGRAMS        |

### 1.0

### GENERAL OVERVIEW

The KL10 CI PORT ADAPTER (CI20) is the unique HARDWARE/FIRMWARE option required in order to interface a KL10 based operating system to the Corporate high speed serial line CI Bus.

With a CI20 installed, and with the necessary software drivers and Port Microcode implemented the KL10 will be capable of communications, through a STAR COUPLER, over the Corporate CI Bus.

The primary functions of the CI20 are:

- a) To enable multiple KL10s to be configured in a loosely coupled environment via the CI.

- b) To enable KL10s to be configured to HSC50s via the CI.

#### 1.1 REFERENCE DOCUMENTS

The below documents contain details of all the topics necessary for a thorough understanding of the CI20 and may be referenced, should additional information be required:

- a) CBUS and EBUS INTERFACES "RH20 MASSBUS CONTROLLER UNIT DESCRIPTION" (EK-RH20-UD-001).

- b) PLI INTERFACE "PILA HARDWARE SPECIFICATION" by: Shu-Shia Chow

- c) AM2901, AM2902, AM2910 "THE AM2900 FAMILY DATA BOOK".

- d) CI MICROCODE ARCHITECTURE "COMPUTER INTERCONNECT SPECIFICATION" By: D. THOMPSON / J. BUZYNSKI / J. HUTCHISON

- e) UNIQUE CI20 MICROCODE ARCHITECTURE "LCG CI PORT ARCHITECTURE SPECIFICATION" By: Don Dossa

Appendix "A" consists of three detailed block diagrams, one for each of the three PORT modules (EBUS.DRW, PROC.DRW and CBUS.DRW).

DEFINITION OF THE CONTROL AND STATUS (CSR) REGISTER BITS FOR THE EBUS INTERFACE MODULE (section 2.3.1) contains detailed descriptions of the CONTROL and STATUS REGISTER bits.

CONDITION CODE DEFINITIONS (section 4.1.1) contains detailed descriptions of the microprocessor's CONDITION CODE sense inputs.

MICROWORD FIELD DEFINITIONS (section 4.7.1) contains detailed descriptions of the microprocessor's CRAM CONTROL WORD decodes.

Reference should be made to these sections throughout this specification whenever further explanation is required.

## 1.2 SPECIFIC GOALS

- 1) FIELD UPGRADABILITY The CI20 is designed as a FIELD INSTALLABLE upgrade kit for KL10 model Bs.

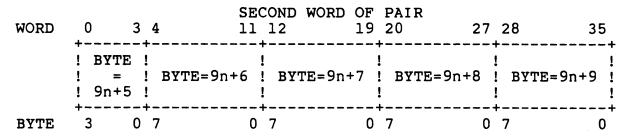

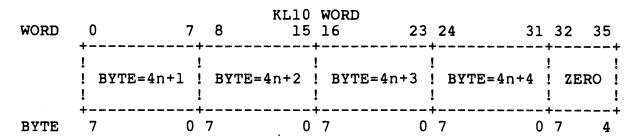

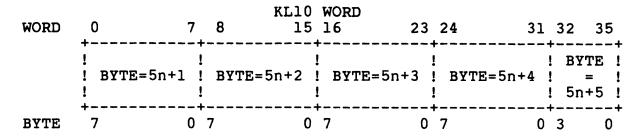

- 2) DATA FORMAT MODES The CI20 supports three data format modes; HIGH DENSITY, CORE DUMP and INDUSTRY COMPATIBLE.

- 3) CI COMPATIBILITY- The CI20 is designed to meet the corporate CI specification. Therefore, it is able to interface with other CI devices that also meet the corporate CI specification.

- 4) SMP COMPATIBILITY CI20s may be installed on SMP systems. However, external memory must be configured in FOUR BUS MODE only. Data Over-runs will frequently occur in a TWO BUS MODE configuration.

## 1.3 SPECIFIC NON-GOALS

- 1) No KL10 based device diagnostics are required other than those uniquely required to test the CI20.

- 2) The CI20 is not supportable by KL10 model "A"s. This is due to additional microcode requirements for the KL10 which may only be implemented on model "B" versions.

- 3) The CI20 does not support SEVEN BIT ASCII data format mode.

- 4) Two or more CI20s installed on one KL10 is not supported as a valid configuration.

- 5) Parity generation/checking is not implemented on the internal data path of the PORT. Instead, parity is checked and re-generated at all external busses to the PORT.

- 6) The CI20 does not have the ability to be powered down and up separately from the KL10.

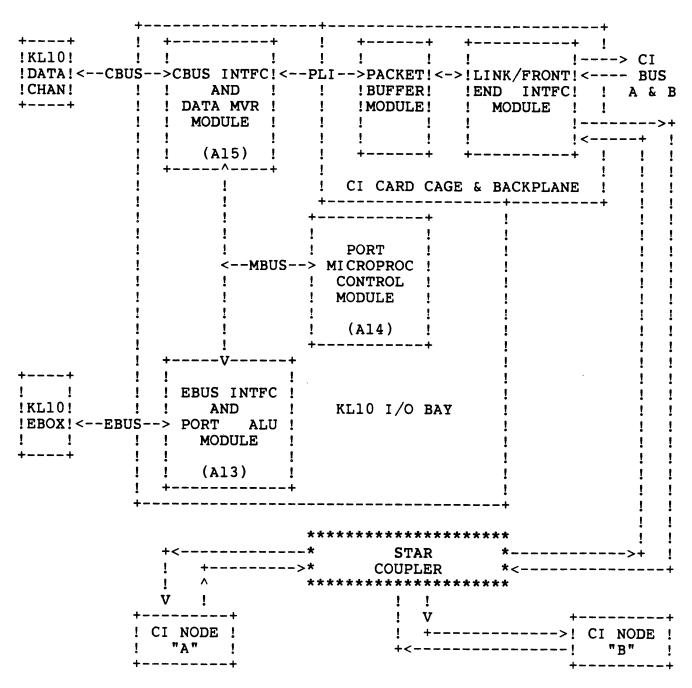

The CI20 interfaces the KL10 to the CI BUS via the KL10'S DATA CHANNEL and EBUS. The following block diagram illustrates the basic architecture of the CI20.

SIMPLIFIED CI20 PORT/LINK INTERFACE BLOCK DIAGRAM

## 1.5 MECHANICAL DESCRIPTION

The CI20 consists of an upgrade kit for KLlOs. The kit includes:

- A) 3 STANDARD HEX MODULES AS FOLLOWS:

- 1) M3001 EBUS INTFC MODULE

- 2) M3002 MPROC CONT MODULE

- 3) M3003 CBUS INTFC MODULE

- B) 2 EXTENDED TRI-BOARDS AS FOLLOWS:

- 1) L0109 PACKET BUFFER MODULE

- 2) L0100 LINK INTERFACE MODULE

- C) 1 +5.0V POWER REGULATOR (H7440)

- D) 1 POWER HARNESS

- E) 1 FLAT RIBBON CABLE FOR PLI INTFC (BC06R-08)

- F) 1 CI CARD CAGE & BACKPLANE

- G) 4 INTERNAL CI CABLES

- H) 2 BULKHEAD CONNECTORS

- I) 1 FLAT RIBBON CABLE FOR MBUS CONNECTOR

- J) 1 DUMMY MODULE WHICH PLUGS INTO RH20 POSITION #6 AND ACTS AS A CABLE STRAIN RELIEF

- K) 30 AWG WIRE (GREEN)

- L) ASSORTED MTG HDWR

- M) INSTALLATION PROCEDURES

- N) PRINT SET AND MANUALS

- P) STANDARD MICROCODE PACKAGE

- R) CI20 DIAGNOSTICS

Extender cables for the MBUS are not included as part of the CI20 UPGRADE KIT. however, they are available separately in order to enable manufacturing and field service to troubleshoot the CI20 PORT modules on an extender board.

The EXTERNAL CI CABLES and STAR COUPLERS, which are also required to configure a CI20, are not included in the CI20 kit. They must be ordered separately according to the desired configuration. The following list identifies these components.

| SC008-AA | STAR COUPLER control hub which connects CI nodes (single path). Provides electrical isolation between nodes. Consists of: 1 8 node STAR COUPLER 1 H9642-CA/CB CABINET |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC008-AB | Same as SC008-AA except without cabinet. Used as the control hub of the second path in a redundant path configuration.                                                |

| BNCI-10  | EXTERNAL CI CABLE PAIR for single path connection. Consists of 1 pair of 10 meter coaxial cables.                                                                     |

| BCNI-20  | Same as BCNI-10 except 20 meter length.                                                                                                                               |

| 3CNI-45  | Same as BCNI-10 except 45 meter length.                                                                                                                               |

The three STANDARD HEX modules (M3001, M3002 & M3003) comprise the PORT section of the CI20. They are uniquely designed for the CI20. The modules are housed in RH20 position # 7 of the KL10's RH20-DTE20 backplane. RH20 position # 6 must have only the dummy cable strain relief module installed. No RH20 is permitted in slot # 6 when a CI20 is installed. Any KL10 which houses a CI20 will be restricted to a maximum of 6 RH20s and one CI20. Reference the below diagram:

## RH20-DTE20 I/O BACK-PLANE SLOTS

| _         |             |     |             |          |   |     | 18          |    |   |                |   |    |   |    |     |    |   |    |     |

|-----------|-------------|-----|-------------|----------|---|-----|-------------|----|---|----------------|---|----|---|----|-----|----|---|----|-----|

| !         | E<br>B<br>U | !!! | M<br>P<br>R | !!!      | С | !!! | D<br>U<br>M | !  |   | !              | ! | !  |   | !  | !   |    |   | !  | !   |

| ! + ! + ! |             | !   | С           | !<br>-+- |   | !   | M           | NO | 5 | !<br>! NO<br>! | 4 | NO | 3 | NO | 2 ! | NO | 1 | NO | 0 ! |

The "DUMMY" position is required due to the high current requirements of the CI20. It requires nearly as much current as two RH20s.

Control signals between modules utilize existing backplane wiring for the RH20s which normally occupy these slots. 12 wires must be added to the backplane, however, in order to obtain sufficient interconnects between modules and to bus across five EBUS INTERFACE signals which are are not used by RH20s. 30 AWG wire (green) is used to add these wires to the BACK-PLANE.

The following chart lists the the RH20 BACK-PLANE point to point wire adds:

| SIGNAL NAME          | FROM  | TO    |

|----------------------|-------|-------|

|                      | -     |       |

| EBUS D11 L           | Cl2Fl | B13B1 |

| EBUS D12 L           | C12D1 | B13B2 |

| EBUS D13 L           | Cl2F2 | B13U1 |

| EBUS PI00 L          | C12H2 | Cl3Nl |

| EBUS PARITY L        | C12E2 | C13B1 |

| EBUS PARITY ACTIVE L | C12L1 | C13B2 |

| MPR7 MWBUSCTLFLD01 H | C14H2 | Al5R2 |

| MPR7 MWMGCFLD08 H    | Cl4Fl | F15A1 |

| MPR7 MWTIMEFLD H     | A14J2 | Al5El |

| CBI1 CLK2 L          | Cl4Pl | A15D2 |

| CBI1 CLK4 L          | C14K2 | A15S2 |

| CBI2 CCCHANERR L     | Bl4Jl | B15A1 |

Once the back-plane for RH20 position # 7 has been modified to house a CI20 an RH20 should never be re-inserted in the position. The RH20 will no longer work properly.

the CI CARD CAGE and BACKPLANE are required for housing the two EXTENDED TRI-BOARDS. For DECsystem-20 style cabinets they are mounted in the CPU BAY of the KLl0 next to the memory unit. For DECsystem-10 style cabinets they are mounted in the I/O BAY. Both are uniquely designed for the CI20.

The two EXTENDED TRI-BOARDS (L0100 & L0109) comprise the LINK/FE and PACKET BUFFERS respectively. They are designed by other engineering groups within DEC and are integrated into the CI20 as standard off-the-shelf items.

The BC06R-08 CABLE is used as the PLI INTERFACE CABLE. It connects from a BERG connector on the CBUS INTFC MODULE (M3003) to a BERG connector mounted on the CI CARD CAGE BACK-PLANE. This cable is a standard off-the-shelf item.

The four internal CI CABLES route from the CI CARD CAGE BACK-PLANE to the internal BULKHEAD CONNECTORS.

The two BULKHEAD CONNECTORS are also off-the-shelf items, but require a special mounting plate for installation into the KL10.

The H7440 REGULATOR is inserted in slot 5 of power supply # 2 in the KL10's I/O BAY. It is used to supply +5.0V to the CI CARD CAGE and BACK-PLANE.

The POWER HARNESS is used to route +5.0 volts from the H7440 REGULATOR and -5.2 volts from the KL10's CPU POWER SUPPLY to the CI CARD CAGE and BACK-PLANE.

The flat ribbon cable used as the MBUS CONNECTOR consists of a 50 wire 18 inch long conductor with three 50 pin BERG connectors mounted to it, one at each end and one in the center. It is uniquely designed for the CI20.

Mostly OFF-THE-SHELF technology is used for the portion of the KL10 CI PORT uniquely designed for the CI20. The three PORT modules use a combination of SHOTTKY and LOW POWER SHOTTKY logic.

## 1.6 GENERAL LOGICAL OVERVIEW

The CI20 consists of three logical sub-groups; a) LINK/FRONT END INTERFACE; b) PACKET BUFFER; c) PORT

This document is intended to describe the PORT hardware function. The LINK/FE and PACKET BUFFER functions are described in their associated specifications. therefore, only a brief description of them will be included here.

Detailed block diagrams of each of the three PORT modules are included in appendix "A" of this specification. They should be continuously referenced as this specification is reviewed.

a) LINK/FRONT END INTERFACE MODULE (L0100) - This module is the standard corporate LINK/FE module. Physically it consists of an EXTENDED TRI PRESS-PIN type module. Its primary function is to interface the PACKET BUFFER MODULE to the serial CI BUS. It is responsible for such functions as:

- a. CRC generation/checking

- b. Arbitration for information tramsmission

- c. Moving information between the buffers and the CI BUS

- d. Encoding/decoding of the bit stream

- e. Header decoding and recognition

- f. Acknowledge generation and transmission

- g. the PARALLEL/SERIAL bit stream conversion.

This module uses a combination of Shottky TTL and ECL logic. Its power requirements are as follows:

- +5.0 Volts at 8.5 Amps

- -5.2 Volts at 8.2 Amps

- b) PACKET BUFFER MODULE (L0109) This module is the standard PACKET BUFFER module used by the HSC50 system. Physically it consists of an EXTENDED TRI PRESS-PIN type module. Logically it consists of four 1K deep by 8-bit wide RAM buffers, along with the necessary control logic for loading and reading the buffers. Its primary function is to act as a temporary storage interface between the LINK/FE and the PORT.

Its power requirements are as follows:

+5.0 Volts at 10.5 Amps

c) PORT - The port functions as an AM2901 based microprocessor which handles the CI PORT protocol in much the same manner as other CI PORTS. Control and status information is passed between the PORT and the KL10 via the KL10's EBUS INTERFACE. DMA data transfers are passed between the PORT and the KL10 via the KL10's CBUS INTERFACE.

The PORT consists of three STANDARD HEX FINE LINE ETCH modules which are inserted into a dedicated low priority RH20 slot in the KL10 RH20-DTE20 BACKPLANE.

They are linked together by a 36-bit tri-state data path called the MBUS. All data is passed between modules via this bus.

The functions of the three modules may be further divided into three logical subgroups as follows: (reference attached block diagrams in appendix "A" of this specification)

## 1) EBUS INTERFACE/PORT ALU MODULE (M3001)

The EBUS INTERFACE/PORT ALU MODULE acts as a low-speed asynchronous control interface between the KL10 EBOX and the PORT MICROPROCESSOR. It performs all of the functions required for passing data between the EBUS and the MICROPROCESSOR. It also contains a 36 bit CONTROL AND STATUS register which enables the PORT to control and monitor the EBUS operations. Most of the PORT PROTOCOL is processed over the EBUS through this interface.

In addition, this module houses the PORT MICROPROCESSOR ALU. The ALU consists of nine AM2901 bit slice ICs (36 bit data path) and four AM2902 high speed look-ahead carry generators. A CONSTANT MUX is also included, which allows the PORT MICROPROCESSOR to pass pre-assigned constants from the CRAM (CONTROL STORE RAM) to the ALU.

The module's power requirements are as follows:

+5.0 Volts at 8.5 Amps

### 2) PORT MICROPROCESSOR CONTROL MODULE (M3002)

The PORT MICROPROCESSOR consists of a horizontally programmed bit slice microprocessor controller. It is responsible for control of the CBUS/MOVER and the EBUS/PORT ALU INTERFACES. It performs such functions as data mapping, CI PACKET interpretation and some PACKET BUFFER manipulations. It consists of a 2910 type MICROSEQUENCER, a 4K deep by 60 bit wide CONTROL RAM (CRAM), a 1K deep by 36 bit wide SCRATCH PAD RAM, a CRAM CONTROL REGISTER and other associated control logics.

Once the CRAM is loaded and the MICROPROCESSOR is started the PORT is entirely under control of the microwords which are strobed from the CRAM into the CRAM CONTROL REGISTER at the beginning of each clock cycle.

The module's power requirements are as follows:

+5.0 Volts at 10.0 Amps

### 3) CBUS-PLI INTERFACE MODULE (M3003)

The CBUS-PLI INTERFACE (CMVR) module acts as a high-speed synchronous DMA data transfer path and data formatter between the PACKET BUFFER and the KL10 CBUS CHANNEL. It uses a 4-bit

parallel by 12-bit serial shift register for the data formatter, which is capable of mapping 8-bit bytes into 36-bit words, and vice versa. It also contains the necessary control logic for performing data transfers between the shift register, the CBUS and the PLI interfaces.

In addition, the module supports a 36-bit read/write data path between the PORT MICROPROCESSOR and the data formatter, and an 8-bit read/write data path between the PORT MICROPROCESSOR and the PLI INTERFACE. This enables the PORT MICROPROCESSOR to directly transfer data to/from the CBUS or the PLI INTERFACES.

The module's power requirements are as follows:

+5.0 Volts at 8.0 Amps

The PORT is controlled by a four phase master clock generator which is located on the CBUS/DATA MOVER MODULE. One microcycle normally requires 270ns (see CMVR CONTROL LOGIC for details).

### 1.7 MICROCODE DESCRIPTION

The hardware of the three CI20 PORT modules (EBUS, MICROPROC & CBUS INTFCS) supply all of the necessary data paths to enable the PORT to efficiently communicate between the KL10 and the CI. They also supply a uniquely designed, horizontally programmed microprocessor to enable the PORT to control and process the data which passes across these data paths.

The port hardware is incapable of functioning as a CI20 without the PORT MICROCODE. Therefore, the PORT MICROCODE must be considered an integral part of the CI20.

The KL10 must load the PORT MICROCODE into the microprocessor's CONTROL RAM (CRAM) before it starts the PORT. Once the KL10 has loaded the MICROCODE and started the PORT it will be capable of functioning as a CI20.

The primary functions of the PORT MICROCODE are to:

- a) Control all data transfers between the PLI INTERFACE and the KL10

- b) Process all CI PROTOCOL PACKETS in conformance with the CI ARCHITECTURE SPECIFICATION

- c) Provide a FIRMWARE INTERFACE between the CI20 and the KL10's microcode and software operating systems.

- d) Provide an adequate ERROR MONITORING/REPORTING interface between the CI20 and the KL10's operating system.

The PORT MICROCODE enables the CI20 to conform to the CI ARCHITECTURE SPECIFICATION.

Recovery of errors that do not compromise the integrity of the CI20 also conforms to the CI ARCHITECTURE SPECIFICATION. The operating system is informed of all errors, either through the RESPONSE QUEUE or the INTERRUPT mechanisms.

The CI20 microcode resides in the following areas:

- a) System area of the MONITOR DISK PACK

- b) KLAD DISK PACK

Reference the "LCG CI PORT ARCHITECTURE SPECIFICATION" By: Don Dossa for detailed explanations of the microcode functionality.

## 1.8 COOLING REQUIREMENTS

The present cooling system in the RH20-DTE20 CARD CAGE is adequate for cooling the three PORT MODULES (EBUS, MPROC and CBUS).

Fans are installed in the CI CARD CAGE to assure adequate cooling for the PACKET BUFFER and LINK/FE MODULES.

# 1.9 MTBF

The CI20 is designed to conform to the following failure rates and repair times.

MTBF = 10,000 Hrs

MTTR = 3/4 Hrs.

MTTD = 1/4 Hrs.

## 1.10

### RAMP FEATURES

Some of the CI20's RAMP FEATURES include:

- a) Parity Generation/Checking on all external busses to the PORT

- b) CRAM Parity Checking

- c) The ability to recover from CRAM PARITY errors with minimal user interruption.

- d) A microcode test routine which periodically verifies the data path and control logic.

- e) Diagnostic loop-back capability at major data path boundries.

- f) Diagnostic ability to generate incorrect parity

- g) A SINGLE-CYCLE mode for test and debug

- h) Ability to latch the CRAM ADDRESS for diagnosability of failures.

- i) A microcode routine which will periodically verify the data integrity of the Local Storage Rams

- j) Ability to predict correct parity across the DMA data path between the PLI INTERFACE and the CBUS.

### 1.11 PERFORMANCE

BANDWIDTH - The CI20, excluding monitor software overhead, provides a realizable data transfer rate capability of approximately 300 pages/sec. This figure, for convenience, may also be translated into other bases such as 0.7 megabytes/sec, 154 kilowords/sec, 3.2 ms/page, etc.

The CI20's realizable bandwidth, excluding monitor software overhead, depends on two factors:

a) THE ACTUAL HARDWARE DMA DATA TRANSFER RATE

The CI20 hardware provides the capability of DMA data transfer rates of 1.6 ms/page (1.4 megabytes/sec)

This bandwidth is highly dependent on the microcode's ability to move the data through the DMA DATA TRANSFER PATH.

The calculation is derived from the following considerations:

- 1) On the average 11.5 microcycles are required per DMA WORD TRANSFER.

- 2) Each microcycle requires 270ns execution time

- 3) One 36 bit KL10 word consists of 4.5 bytes

#### THEREFORE:

### b) THE MICROCODE PROTOCOL PROCESSING OVERHEAD

The CI20 protocol processing overhead also takes approximately 1.6 ms/page (measured value).

Therefore, the aggregate realizable bandwidth is simply the sum of the two values derived from (a) and (b) above, or 3.2 ms/page (300 pages/sec).

## 1.12 SUBSYSTEM DOCUMENTATION

Documentation for the CI20 includes:

- a) CI20 HARDWARE MAINTENANCE MANUAL supplies all information required to enable an CI20 to be easily installed and repaired.

- b) KL10 MAINTENANCE GUIDE updates to reflect necessary information about the CI20.

- c) SITE PREPARATION GUIDES

- d) ILLUSTRATED PARTS BULLETIN

- e) CI20 FIELD PRINT SET

- f) MANUFACTURING TEST SPECIFICATIONS

- q) TEST & ACCEPTANCE PROCEDURE

- h) All KL10 PRINT SET ECO's if any are required

- i) Revision control for KL10 systems will be inclusive of CI20s for any future KL10 ECOs which may be required.

### 1.13 SYSTEM SOFTWARE

TOPS-20 includes all necessary drivers to support a CI20. These drivers include, but are not necessarily limited to:

- a) An MSCP DRIVER

- b) An SCA DRIVER

- c) A CI20 PORT DRIVER

A software microcode loader for loading the PORT MICROCODE.

Software hooks for accurately reporting CI20 error conditions to SPEAR.

## 1.14 STANDARDS COMPLIANCE

The CI20 meets DEC-102 TEMP/HUMIDITY standards.

The increase in the current EMI-RFI profile of the KL10 is less than 6 DB average above its current level with a CI20 installed.

# 2.0 EBUS INTFC/PORT ALU MODULE

The EBUS INTERFACE occupies about 2/3rds of this module and consists primarily of:

a) A CONTROL and STATUS REGISTER (CSR) which is used for passing control and status parameters between the PORT MICROPROCESSOR and the HOST.

- b) A data path, via the MBUS, between the PORT MICROPROCESSOR and the EBUS

- c) Control logic for loading and starting the PORT'S MICROCODE

- d) An EBUS parity generator/checker

- e) All necessary control logic for interfacing to and executing the KL10's EBUS protocol, including the "EBUS INTERRUPT" sequence.

- f) Diagnostic logic for executing various loop-back and other test functions.

The KL10 accesses the EBUS INTFC by executing DATAO, DATAI, CONO and CONI commands.

The PORT MICROPROCESSOR accesses the EBUS INTFC by executing microprocessor commands. These commands are decoded functions of the MWBUSCTLFLD field and the MWMGCFLD field of the CRAM CONTROL WORD.

The PORT MICROPROCESSOR monitors the EBUS INTFC LOGIC status by sensing CONDITION CODES (see section CONDITION CODE DEFINITIONS for details).

The MICROPROCESSOR ALU is also located on the EBUS INTERFACE MODULE. It consists of:

- a) Nine AM2901 type FOUR-BIT BIPOLAR MICROPROCESSOR SLICES (36-bit wide data path) which interfaces to the MBUS.

- b) Four AM2902 type HIGH-SPEED LOOK-AHEAD CARRY GENERATORS

- c) Five 74LS157 type MULTIPLEXERS (CNST MUX) used by the MICROPROCESSOR CONTROL to input a CONSTANT NUMBER FIELD from the CRAM CONTROL REGISTER into data bits 00 thru 09 and data bits 26 thru 35 of the ALU.

# 2.1 EBUS CONTROL LOGIC

The EBUS CONTROL LOGIC arbitrates the EBUS protocol, the PORT MICROPROCESSOR protocol for interfacing to the EBUS and the synchronization functions between the two.

The KL10 has full control of the PORT only when the PORT is not in the "MPROC RUN" state (CSR32 reset). In this state the PORT MICROPROCESSOR is not running. The KL10's primary functions are to:

- a) load and read verify the PORT'S MICROCODE

- b) initially set up the correct CSR REGISTER functions

- c) check for error conditions should the PORT halt unexpectedly

Secondary diagnostic functions also exist in this state which enables the KL10 to perform such functions as writing and read/verifying the EBUF, generating bad parity, single cycling, etc.

The KL10 performs these functions by executing CONOs, CONIs, DATAOs, and DATAIs. The PORT's EBUS INTERFACE processes these functions via the normal EBUS protocol.

- A brief description of these sequences follows:

- a) DATOLOADRAR If the KL10 executes a DATAO with bit 00 equal to "1" a DATOLOADRAR signal will be generated. This will cause bits EBUS D01-13 to be loaded, via the MBUS, into the PORT'S "RAM ADDRESS REGISTER" located on THE MICROPROCESSOR CONTROL MODULE.

- b) DATOLOADMW If the KL10 executes a DATAO with bit 00 equal to zero a DATOLOADMW signal will be generated. This will cause the 30 least significant bits on the EBUS to be loaded, via the MBUS, into the selected half of the PORT'S "CRAM" location as specified by the "RAM ADDRESS REGISTER".

- c) DATIREADMW If the KL10 executes a DATAI with CSR21=0 a DATIREADMW signal will be generated. This will cause the contents of the selected half of the PORT'S CRAM location, as specified by the contents of the "RAM ADDRESS REGISTER", to be placed on the EBUS.

- d) DATIREADLAR If the KL10 executes a DATAI with CSR21=1 a DATIREADLAR signal will be generated. This will cause the contents of the LAR REGISTER to be placed on EBUS D01-12

- e) CONOLOADCSR If the KL10 executes a CONO a CONOLOADCSR signal will be generated. This will cause the contents of the EBUS to be loaded into all CSR REGISTER bits which are writeable by the KL10.

- f) CONIREADCSR If the KL10 executes a CONI a CONIREADCSR signal will be generated. This will cause the contents of all CSR REGISTER bits which are readable by the KL10 to be placed on the EBUS.

- g) TESTLOADEBUF If the KL10 executes a DATAO with CSR19=1 a TESTLOADEBUF signal will be generated. This will cause EBUS D00-35 to be loaded, via the MBUS, into the EBUF.

h) TESTREADEBUF - If the KL10 executes a DATAI with CSR19=1 a TESTREADEBUF signal will be generated. This will cause the contents of the EBUF to be placed on the EBUS.

When the PORT is in the "MPROC RUN" state (CSR32 set) the KL10 is permitted only to access the CSR REGISTER by executing CONO or CONI commands.

In the "MPROC RUN" state CONO and CONI commands operate in the same manner as described above.

DATAO and DATAI commands executed by the KL10's software when the PORT is RUNNING (CSR32 set) will cause the condition code CCEBUSRQST to be asserted. Since this is an unexpected illegal function the condition will usually be ignored by the PORT. Thus, an EBUS TIMEOUT will occur since "TRANSFER" will never be returned over the EBUS.

When the PORT is RUNNING the PORT MICROPROCESSOR controls the EBUS by generating EBUS INTERRUPTS. There are two types of interrupts generated by the port:

- a) Non-Vectored (40 + 2n) software interrupts (IOP WORD = 0)

- b) Microcode interrupts in which a non-zero IOP WORD is passed to the KL10's microcode for decode and execution of specific KL10 microcode functions.

A list of the types of interrupts which may be generated by the port are listed below. All of them may be generated by the hardware, even though the PORT MICROCODE does not currently use many of them. Those which are currently used by the PORT are marked by an "\*":

- \* FUNCTION 0 = STANDARD (40 + 2N) INTERRUPT (IOP WORD = 0)

- FUNCTION 2 = INCREMENT OR DECREMENT

- FUNCTION 3 = DATAO (EXAMINE AND INCREMENT)

- \* FUNCTION 4 = DATAO (EXAMINE)

- \* FUNCTION 5 = DATAI (DEPOSIT)

- FUNCTION 6 = BYTE TRANSFER (DEPOSIT)

- \* FUNCTION 7 = DATAO (EXAMINE AND INCREMENT). This is a new function which is being added specifically for the CI20.

### 2.1.1

## PI LEVEL 00 INTERRUPTS

If the EBUS INTERRUPT is a function 2 through 7 interrupt, the PORT MICROPROCESSOR requests the INTERRUPT on PI LEVEL 00 by executing the command "MPEXORDEP" (EXAMINE OR DEPOSIT).

PI LEVEL 00 type INTERRUPTS are always processed by the KL10 as first priority, even when the KL10 has its interrupt enable system turned off. Therefore, the CI20 is capable of executing these interrupts regardless of the state of the KL10's interrupt enable system.

This sequence is executed as follows:

- a) The PORT's microcode builds an IOP FUNCTION CONTROL WORD and loads it into the EBUF, via an MPLOADEBUF (LOAD EBUF) command. With the same microword it executes an "MPEXORDEP" (REQUEST EXAMINE OR DEPOSIT) command.

- b) The MPEXORDEP command will cause RQST EXAM OR DEP (CSR04) to be set. This will cause the PORT's EBUS INTERFACE to assert the PI REQUEST line PI00 on the EBUS.

- c) When the KL10's EBOX recognizes the PI00 REQUEST it responds by asserting

- 1) the PORT's channel number on CS04-06 of the EBUS

- 2) PI SERVED (4 octal) on the "F" lines of the EBUS

- 3) DEMAND, after a sufficient delay

- d) The PORT's EBUS INTERFACE responds by asserting the EBUS DATA line which corresponds to its physical device number.

- e) The KL10's EBOX, after a sufficient delay, reads the EBUS DATA lines and negates DEMAND

- f) The KL10's EBOX then asserts

- 1) the PORT's channel number on CS04-06

- 2) the PORT's physical number on CS00-03

- 3) PI ADR IN (5 octal) on the "F" lines of the EBUS

- 4) DEMAND, after a sufficient delay

- g) The PORT's EBUS INTERFACE responds by asserting on the EBUS

- 1) ACKN

- 2) The IOP FUNCTION CONTROL WORD which was previously loaded in the EBUF by the PORT MICROPROCESSOR.

- 3) XFER, after a sufficient delay

- h) When the KL10's EBOX detects XFER it strobes the data from the EBUS DATA lines and negates DEMAND

- i) The trailing edge of DEMAND causes the PORT'S EBUS INTERFACE to negate ACKN, XFER and the DATA lines, thus ending the interrupt sequence

The KL10 microcode in turn decodes the IOP FUNCTION CONTROL WORD and executes the appropriate function. If the "IOP FUNCTION CONTROL WORD" specifies that an EBUS CYCLE is required (I.E. EXAMINE or DEPOSIT) the very next EBUS CYCLE following the "IOP FUNCTION CONTROL WORD" read will be addressed to the PORT. This sequence occurs as follows:

- a) The KL10's EBOX asserts

- a device code of "ZERO" on CS00-06 of the EBUS

- 2) DATAO or DATAI (2 or 3 octal) on the "F" lines of the EBUS

- 3) Data on the EBUS DATA lines, if the function is a DATAO.

- 4) DEMAND, after a sufficient delay

- b) The PORT'S EBUS INTERFACE responds by asserting ACKN on the EBUS. It also flags the PORT MICROPROCESSOR by asserting the CONDITION CODE, CCEBUSRQST.

Since the device code on CS00-06 returned by the KLlO is "ZERO", not the PORT'S device code, the PORT does not examine the device code. Instead the PORT assumes that the very next EBUS CYCLE is intended for it and, therefore, takes the appropriate action as soon as it senses DEMAND asserted on the EBUS.

c) When the PORT's microcode detects CCEBUSRQST it responds by executing an MPLOADEBUS or MPREADEBUS command, whichever is applicable.

If the PORT's microcode executes an MPLOADEBUS it must have previously loaded the EBUF, via an MPLOADEBUF command, with valid data to be transferred to the KL10.

- If the PORT's microcode executes an MPREADEBUS the EBUS DATA will be placed on the MBUS. The PORT's microcode must also execute another command on the same microcycle to strobe the data from the MBUS into one of its internal storage media.

- d) After a sufficient delay the PORT's EBUS INTERFACE asserts XFER on the EBUS

- e) When the KL10's EBOX detects XFER it negates DEMAND

- If the function was an EXAMINE (DATAI) it strobes the data from the EBUS DATA lines

- If the function was a DEPOSIT (DATAO) it de-asserts the data from the EBUS DATA lines

- f) The trailing edge of DEMAND causes the PORT'S EBUS INTERFACE to negate ACKN, XFER, CCEBUSRQST and the DATA lines (if applicable), thus ending the interrupt sequence.

- g) The PORT's MICROCODE must be prepared to respond promptly to the CONDITION CODE, CCEBUSRQST, in order to prevent EBUS TIMEOUTS. The PORT MICROPROCESSOR should not attempt to execute any additional EBUS transfers until it detects the negation of CCEBUSRQST.

# 2.1.2 PI LEVEL 01 THROUGH 07 INTERRUPTS

- If the EBUS INTERRUPT is a function 0 interrupt, the PORT MICROPROCESSOR requests the INTERRUPT on PI LEVEL 01 through 7, depending on the assigned PI LEVEL in CSR33-35, by executing the command "MPRQSTINTR" (REQUEST INTERRUPT). This sequence is executed as follows:

- a) The PORT's microcode first checks the CONDITION CODE, "CCINTRACTIVE". If it is asserted the microcode must wait until it is de-asserted before continuing the below sequence.

- b) The PORT's microcode then executes an "MPRQSTINTR" command. The MPRQSTINTR command will cause RQST INTERRUPT (CSR05) to be set. This will cause the PORT's EBUS INTERFACE to assert the PI REQUEST line (PI01-07) as specified by PIA00-02 (CSR33-35) on the EBUS.

- c) When the KL10's EBOX recognizes the PI01 through 7 REQUEST it responds by asserting

- 1) the PORT's channel number on CS04-06 of the EBUS

- 2) PI SERVED (4 octal) on the "F" lines of the EBUS

- 3) DEMAND, after a sufficient delay

- d) The PORT's EBUS INTERFACE responds by asserting the EBUS DATA line which corresponds to its physical device number.

- e) The KL10's EBOX, after a sufficient delay, reads the EBUS DATA lines and negates DEMAND

- f) The KL10's EBOX then asserts

- 1) the PORT's channel number on CS04-06

- 2) the PORT's physical number on CS00-03

- 3) PI ADR IN (5 octal) on the "F" lines of the EBUS

- 4) DEMAND, after a sufficient delay

- g) The PORT's EBUS INTERFACE responds by asserting on the EBUS

- 1) ACKN

- A hardware generated IOP FUNCTION CONTROL WORD of all zeros

- 3) XFER, after a sufficient delay

- h) When the KL10's EBOX detects XFER it strobes the data from the EBUS DATA lines and negates DEMAND

- i) The trailing edge of DEMAND causes the PORT'S EBUS INTERFACE to negate ACKN, XFER and the DATA lines.

- j) When the KL10 microcode decodes the IOP WORD of all zeros it will generated a standard Non-Vectored (40 + 2n) interrupt to the KL10's software.

# 2.2 MICROPROC TO EBUS REGISTER (EBUF)

The "MICROPROCESSOR TO EBUS REGISTER" (EBUF) is a 36-bit register normally used by the PORT MICROPROCESSOR to pass data from the MBUS (Internal tri-state MICROPROCESSOR BUS) to the EBUS, or to the CSR REGISTER. The PORT MICROPROCESSOR generally loads data into this

register from the MBUS. This data may then be strobed by the next microcycle of the PORT MICROPROCESSOR to either the CSR REGISTER or to the EBUS.

The PORT MICROCODE uses the EBUF for the following two functions:

- 1) To load the CSR REGISTER. Data is first strobed into the EBUF, then to the CSR REGISTER.

- 2) To transmit an IOP FUNCTION CONTROL WORD over the EBUS for execution of EXAMINE or DEPOSIT functions on PI LEVEL 00.

The command, MPLOADEBUF (LOAD EBUF), causes the data currently on the MBUS to be loaded into the EBUF at CLK3 time.

A diagnostic loop-back path exists, however, which enables the KL10 to load and read this buffer. This loop-back path is controlled by DIAG TEST EBUF (CSR19). If CSR19 is set and the PORT is not in the "MPROC RUN" state (CSR32 re-set):

- a) A DATAO executed by the KL10 will cause the date asserted on the EBUS to be loaded, via the MBUS, into the EBUF

- b) A DATAI executed by the KL10 will cause the data in the EBUF to be asserted on the EBUS.

# 2.3 EBUS CONTROL AND STATUS REGISTER (CSR)

The "EBUS CONTROL and STATUS REGISTER" (CSR) is a 36 bit register which resides in the EBUS INTERFACE.

The KL10 accesses the CSR REGISTER by executing CONO and CONI commands.

The PORT MICROPROCESSOR, when in the "MPROC RUN" state, accesses the CSR REGISTER by executing the following sequence.

- a) The PORT MICROPROC loads the EBUF with the desired CSR data, if it is writing to the CSR, by executing an MPLOADEBUF command. On the same microcycle it executes an MPRQSTCSR (Request CSR) command.

- b) The PORT MICROPROC then senses for the CONDITION CODE, CCGRNTCSR (CSR GRANTED)

c) Once CCGRNTCSR is valid the PORT MICROPROC may execute either an MPLOADCSR (LOAD CSR) or MPREADCSR (READ CSR) command. If an MPLOADCSR command is executed the contents of the EBUF will be strobed into the CSR REGISTER at CLK3 time.

If an MPREADCSR command is executed the contents of the CSR REGISTER will be asserted on the MBUS. The PORT MICROPROC must then strobe the MBUS data into one of its internal storage media on the same microcycle.

The CSR REGISTER is read/write interlocked to prevent the PORT and the KL10 from accessing it simultaneously. This is accomplished by the CONDITION CODE, CCGRNTCSR. When the PORT wishes to access the register it executes an MPRQSTCSR command. If the register is available CCGRNTCSR will be asserted by the EBUS INTERFACE LOGIC. If the KL10 is accessing the register at the time via a CONI or a CONO, CCGRNTCSR will not be asserted until the CONI or CONO function is complete.

The PORT MICROPROCESSOR must wait until it senses the asserted state of CCGRNTCSR before it attempts to access the CSR REGISTER.

Likewise, if the PORT MICROPROC is accessing the register when a CONI or a CONO is executed by the KL10 the EBUS INTERFACE LOGIC will cause the command to wait until the PORT has completed its access.

Race conditions between the PORT and the KL10 are prevented by granting access to the KL10 at CLK1 time and granting access to the PORT (asserting CCGRNTCSR) at CLK3 time.

The below chart briefly describes the CRS REGISTER bits. A more thorough description follows:

- "\*" indicates that the bit is not defined

- "R" indicates that the bit is readable

- "W" indicates that the bit is writeable

"C" indicates that the bit may be cleared only as a single bit

"S" indicates that the bit may be set only

"H" indicates that the bit is hardware controlled

| <br>BIT           | +      | DEFINITION   | תם ו       | <br>/WD    |

|-------------------|--------|--------------|------------|------------|

| NO.               |        | DEFINITION   | <b>.</b>   | L          |

| +                 |        |              | ! R        |            |

| +                 | +      |              | +          |            |

| +                 | +      | CSR CHNG     | +          | +          |

| . 02<br>+<br>! 03 | +      |              | +<br>! *   | +<br>! *   |

| +<br>!04          | !RQST  | EXAM OR DEP  | +<br>! R/H | +<br>! R/S |

| +                 | +      | INTERRUPT    | +          | +          |

| +<br>!06          | !CRAM  | PARITY ERR   | +<br>! R/C | +<br>! H   |

| +<br>!07          | ! MBUS | ERROR        | +<br>! R   | +<br>! H   |

| +<br>!08          | !      |              | +<br>! *   | +<br>! *   |

| !09               |        |              |            | +·<br>! *  |

| !10               | •      |              | ! *        | ! *        |

| !11               | !IDLE  |              | ! R        | ! R/W      |

| !12               | !DISA  | BLE COMPLETE | ,          | ! R/W      |

| !13               | !ENAB  | LE COMPLETE  | ! R        | ! R/W      |

| !14               | !      |              | ! *<br>+   | ! *<br>+   |

| !15               | ! PORT | ID CODE 00   | ! R        | ! H        |

| !16<br>+          | ! PORT | ID CODE 01   | ! R        | ! Н<br>+   |

| !17               | ! PORT | ID CODE 02   | ! R        | •          |

# 2.3.1 DEFINITION OF THE CONTROL AND STATUS (CSR) REGISTER BITS

BIT # NAME DEFINITION

CSR00 PORT PRESENT INDICATES THAT THE PORT IS PRESENT.

READ/WRITE STATUS: KL10 = "R" PORT = "H"

THE KL10 ALWAYS READS THIS BIT AS "1" IF THE PORT IS PRESENT (INSTALLED AND POWERED UP).

THE PORT ALWAYS READS THIS BIT AS "0"

CSR01 DIAG RQST CSR

DIAGNOSTIC BIT WHICH INDICATES THE STATUS OF "CCRQSTCSR".

READ/WRITE STATUS: KL10 = "R" PORT = "H"

## SET BY:

1) THE PORT MICROPROC REQUESTING ACCESS TO THE CSR (ASSERTING MPRQSTCSR).

### CLEARED BY:

- 1) THE PORT MICROPROC READING THE CSR (ASSERTING MPREADCSR).

- 2) THE PORT MICROPROC WRITING THE CSR (ASSERTING MPLOADCSR).

- 3) THE KL10 SETTING CLEAR (CSR18)

- 4) A GENERAL EBUS RESET.

## CSR02 DIAG CSR CHNG

DIAGNOSTIC BIT WHICH INDICATES THAT THE CONTENTS OF THE CSR REGISTER HAS CHANGED SINCE THE LAST TIME IT WAS READ BY THE PORT MICROPROCESSOR.

READ/WRITE STATUS: KL10 = "R/H"

PORT = "H"

## SET BY:

- 1) THE KL10 WRITING THE CSR (EXECUTING A CONO FUNCTION)

- 2) DETECTION OF AN "EBUS PARITY ERROR" (CSR24 SETTING).

## CLEARED BY:

- 1) THE PORT MICROPROC READING THE CSR (ASSERTING MPREADCSR)

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR03 UNUSED

THIS BIT IS NOT USED BY EITHER THE PORT MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

CSR04 ROST EXAM OR DEP

USED BY THE PORT MICROPROCESSOR TO REQUEST AN EBUS INTERRUPT FUNCTION ON PI LEVEL 00 (EXAMINE OR DEPOSIT FUNCTION). A "PI LEVEL 00 INTERRUPT" WILL BE IMMEDIATELY GENERATED WHEN THIS BIT IS SET.

READ/WRITE STATUS: KL10 = "R/H" PORT = "R/S"

### SET BY:

1) THE PORT MICROPROC REQUESTING AN EBUS EXAMINE OR DEPOSIT INTERRUPT ON PI LEVEL 00 (ASSERTING MPEXORDEP)

## CLEARED BY:

- 1) SUCCESSFUL COMPLETION OF THE EXAMINE OR DEPOSIT SEQUENCE.

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

## CSR05 ROST INTERRUPT

USED BY THE PORT MICROPROCESSOR TO REQUEST AN EBUS NON-VECTORED (40 + 2n) INTERRUPT ON PI LEVELS 01 THRU 07. A "PI LEVEL 01 THRU 07 INTERRUPT" WILL BE IMMEDIATELY GENERATED WHEN THIS BIT IS SET.

READ/WRITE STATUS: KL10 = "R/H"

PORT = "R/S"

## SET BY:

- 1) THE PORT MICROPROC REQUESTING AN EBUS INTERRUPT ON PI LEVELS 01 THRU 07 (ASSERTING MPRQSTINTR)

- 2) CRAM PAR ERR (CSR06) SETTING

- 3) MBUS ERR (CSR07) SETTING

### CLEARED BY:

- 1) SUCCESSFUL COMPLETION OF THE INTERRUPT SEQUENCE.

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR06 CRAM PAR ERR

INDICATES THAT A CONTROL RAM PARITY ERROR HAS BEEN DETECTED.

IF THIS BIT IS SET THE PORT MICROPROC WILL BE HALTED IMMEDIATELY AND RQST INTERRUPT (CSR05) WILL BE SET. A HARDWARE NON-VECTORED (40 + 2n) INTERRUPT WILL BE FORCE GENERATED.

THE PORT MICROPROCESSOR CANNOT BE RESTARTED (CSR32 SET) UNTIL THIS BIT IS CLEARED.

OCCASIONALLY A "CRAM PARITY ERROR" MAY BE INTENTIONALLY FORCED IN ORDER TO HALT THE PORT MICROPROC AT A SPECIFIC LOCATION (BREAK POINT).

READ/WRITE STATUS: KL10 = "R/C" PORT = "H"

## SET BY:

1) THE DETECTION OF A CONTROL RAM PAR-ITY ERROR

### CLEARED BY:

- 1) THE KL10 STORING A "1" IN CSR24 (EBUS PARITY ERR)

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR07 MBUS ERR

INDICATES THAT MORE THAN ONE MBUS DRIVER HAS BEEN TURNED ON AT THE SAME TIME.

IF THIS BIT IS SET THE PORT MICROPROC WILL BE HALTED IMMEDIATELY AND RQST INTERRUPT (CSR05) WILL BE SET. A HARDWARE NON-VECTORED (40 + 2n) INTERRUPT WILL BE FORCE GENERATED.

THE PORT MICROPROCESSOR CANNOT BE RESTARTED (CSR32 SET) UNTIL THIS BIT IS CLEARED.

READ/WRITE STATUS: KL10 = "R"

PORT = "H"

## SET BY:

1) THE DETECTION OF MORE THAN ONE MBUS DRIVER BEING TURNED ON AT THE SAME TIME

### CLEARED BY:

- 1) THE KL10 SETTING CLEAR (CSR18)

- 2) A GENERAL EBUS RESET.

CSR08 UNUSED THIS BIT IS NOT USED BY EITHER THE PORT

MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

CSR09 UNUSED THIS BIT IS NOT USED BY EITHER THE PORT MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

CSR10 UNUSED THIS BIT IS NOT USED BY EITHER THE PORT MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

#### CSR11 IDLE

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO INFORM THE KL10 OPERATING SYSTEM THAT THE PORT MICROPROC IS IN THE MICROCODE "IDLE" LOOP. THE PORT MICROCODE SETS THIS BIT EACH TIME IT ENTERS THE "IDLE" LOOP AND CLEARS THE BIT EACH TIME IT LEAVES THE "IDLE" LOOP.

READ/WRITE STATUS: KL10 = "R"

PORT = "R/W"

#### SET BY:

1) THE PORT STORING A "1" IN THE BIT.

### CLEARED BY:

- 1) THE PORT STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

### CSR12 DISABLE COMPLETE

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO INFORM THE KL10 OPERATING SYSTEM THAT THE PORT MICROPROC HAS PLACED ITSELF IN THE "DISABLED" STATE.

READ/WRITE STATUS: KL10 = "R"

PORT = "R/W"

### SET BY:

1) THE PORT STORING A "1" IN THE BIT.

### CLEARED BY:

- 1) THE PORT STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR13 ENABLE COMPLETE

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO INFORM THE KL10 OPERATING SYSTEM THAT THE PORT MICROPROC HAS PLACED ITSELF IN THE "ENABLED" STATE.

READ/WRITE STATUS: KL10 = "R"

PORT = "R/W"

SET BY:

1) THE PORT STORING A "1" IN THE BIT.

CLEARED BY:

1) THE PORT STORING A "0" IN THE BIT

2) THE KL10 SETTING CLEAR (CSR18)

3) A GENERAL EBUS RESET.

CSR14 UNUSED

THIS BIT IS NOT USED BY EITHER THE PORT MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

CSR15 PORT ID CODE 00

THIS BIT REPRESENTS BIT "00" OF THE THREE BIT "PORT IDENT CODE" FIELD.

READ/WRITE STATUS: KL10 = "R"

PORT = "H"

THE KL10 ALWAYS READS THIS BIT AS "0" IF THE PORT IS PRESENT (INSTALLED AND POWERED UP).

THE PORT ALWAYS READS THIS BIT AS "0"

CSR16 PORT ID CODE 01

THIS BIT REPRESENTS BIT "01" OF THE THREE BIT "PORT IDENT CODE" FIELD.

READ/WRITE STATUS: KL10 = "R"

PORT = "H"

THE KL10 ALWAYS READS THIS BIT AS "1" IF THE PORT IS PRESENT (INSTALLED AND POWERED UP).

THE PORT ALWAYS READS THIS BIT AS "0"

CSR17 PORT ID CODE 02

THIS BIT REPRESENTS BIT "02" OF THE THREE BIT "PORT IDENT CODE" FIELD.

READ/WRITE STATUS: KL10 = "R" PORT = "H"

THE KL10 ALWAYS READS THIS BIT AS "1" IF THE PORT IS PRESENT (INSTALLED AND POWERED UP).

THE PORT ALWAYS READS THIS BIT AS "0"

CSR18 CLEAR PORT

THIS BIT, WHEN SET BY THE KL10, CAUSES THE PORT TO BE RESET. THE MICROPROC IS HALTED AND ALL PERTINENT REGISTERS AND CONTROL LOGIC IS PLACED IN A RESET STATE.

READ/WRITE STATUS: KL10 = "W"

PORT = "\*"

SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

CLEARED BY:

1) CLEARS ITSELF AFTER IT HAS COMP-LETED ITS RESET FUNCTION

CSR19 DIAG TEST EBUF

DIAGNOSTIC BIT WHICH ENABLES THE KL10 TO PERFORM A LOOPBACK FUNCTION OF THE EBUS INTERFACE BY LOADING AND READING THE EBUF.

IF THE PORT IS NOT RUNNING (CSR32 IS RESET) AND CSR19 IS SET:

- 1) A "DATAO" FROM THE KL10 WILL CAUSE THE DATA ON THE EBUS TO BE LOADED INTO THE EBUF.

- 2) A "DATAI" FROM THE KL10 WILL CAUSE THE DATA IN THE EBUF TO BE PLACED ON THE EBUS.

READ/WRITE STATUS: KL10 = "R/W"

PORT = "\*"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

## CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

## CSR20 DIAG GEN EBUS PE

DIAGNOSTIC BIT WHICH ENABLES THE KL10 TO TEST THE EBUS PARITY CHECKER BY FORCING IT TO DECODE AN EBUS PARITY ERROR.

When this bit is set EBUS PAR ERR (CSR24) will be set on the same CONO, assuming that EBUS PARITY was actually correct.

READ/WRITE STATUS: KL10 = "R/W" PORT = "\*"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

- 1) THE KL10 STORING A "O" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR21 DIAG SEL LAR

DIAGNOSTIC BIT WHICH ENABLES THE KL10 TO READ THE "LAR" REGISTER.

IF THIS BIT IS SET, THE PORT IS NOT RUNNING (CSR32 RESET) AND "DIAG TEST EBUF" (CSR19) IS RESET A DATAI EXECUTED BY THE KL10 WILL CAUSE THE LATCH ADDRESS REG (LAR) TO BE ASSERTED ON EBUS BITS D01-D12. ALL OTHER EBUS BITS ARE UNDEFINED.

READ/WRITE STATUS: KL10 = "R/W"

PORT = "\*"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

## CLEARED BY:

- 1) THE KL10 STORING A "O" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR22 DIAG SINGLE CYC

DIAGNOSTIC BIT WHICH ENABLES THE PORT MICROPROC TO BE SINGLE CYCLED.

IF THIS BIT IS SET AND THE KL10 SETS MPROC RUN (CSR32) THE PORT MICROPROC WILL EXECUTE ONE MICROCYCLE AND HALT. MPROC RUN WILL BE CLEARED WHEN THE MICROPROC HALTS.

THE CURRENT ADDRESS TO BE EXECUTED IS FETCHED FROM THE "RAR" REGISTER.

THE NEXT MICROPROC ADDRESS TO BE EXECUTED IS STORED IN THE "LAR" REGISTER AT THE COMPLETION OF THE MICROCYCLE. THE KL10 MUST READ THIS ADDRESS AND LOAD IT INTO THE "RAR" REGISTER BEFORE EXECUTING THE NEXT SINGLE CYCLE.

NOTE: THIS BIT MUST BE RESET IN ORDER FOR THE KL10 TO CORRECTLY READ AND WRITE THE CRAM

READ/WRITE STATUS: KL10 = "R/W"

PORT = "\*"

## SET BY:

- 1) THE KL10 STORING A "1" IN THE BIT. CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR23 SPARE

RESERVED FOR FUTURE SOFTWARE USE.

READ/WRITE STATUS: KL10 = "R/W"

PORT = "\*"

## SET BY:

- 1) THE KL10 STORING A "1" IN THE BIT. CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

# CSR24 EBUS PARITY ERR

WHEN READ BY THE KL10 THIS BIT INDICATES THAT AN EBUS PARITY ERROR HAS BEEN DETECTED.

WHEN WRITTEN AS A "1" BY THE KL10 THIS BIT WILL CLEAR ITSELF AND "CRAM PARITY ERR" (CSR06).

READ/WRITE STATUS: KL10 = "H/R/C"

PORT = "R"

## SET BY:

THE DETECTION OF AN EBUS PARITY ERROR WHILE THE PORT IS READING DATA FROM THE EBUS.

#### CLEARED BY:

- 1) THE KL10 STORING A "1" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

## CSR25 FREE QUEUE ERR

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO INFORM THE KL10 OPERATING SYSTEM THAT THERE ARE NO FREE QUEUE ENTRIES AVAILABLE ON THE FREE QUEUE. THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/C" PORT = "R/S"

## SET BY:

1) THE PORT STORING A "1" IN THE BIT.

- 1) THE KL10 STORING A "1" IN THE BIT.

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

## CSR26 DATA PATH ERR

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO REPORT TO THE KL10 OPERATING SYSTEM THAT IT HAS DETECTED AN ERROR IN THE "DMA DATA PATH", INCLUDING THE MOVER/FORMATTER. THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/C" PORT = "R/S"

## SET BY:

1) THE PORT STORING A "1" IN THE BIT.

### CLEARED BY:

- 1) THE KL10 STORING A "1" IN THE BIT.

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

#### CSR27 CMD QUEUE AVAIL

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE KL10 OPERATING SYSTEM TO INFORM THE PORT THAT IT HAS PLACED A COMMAND QUEUE ENTRY ON A PREVIOUSLY EMPTY COMMAND QUEUE. THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/S" PORT = "R/C"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

- 1) THE PORT STORING A "1" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR28 RESP QUEUE AVAIL

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE PORT TO INFORM THE KL10 OPERATING SYSTEM THAT IT HAS PLACED A RESPONSE QUEUE ENTRY ON A PREVIOUSLY EMPTY RESPONSE QUEUE. THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/C"

PORT = "R/S"

### SET BY:

1) THE PORT STORING A "1" IN THE BIT.

#### CLEARED BY:

- 1) THE KL10 STORING A "1" IN THE BIT.

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR29 UNUSED

THIS BIT IS NOT USED BY EITHER THE PORT MICROPROC OR THE KL10.

READ/WRITE STATUS: KL10 = "\*"

PORT = "\*"

CSR30 DISABLE

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE KL10 OPERATING SYSTEM TO INFORM THE PORT TO PLACE ITSELF IN THE "DISABLED" STATE (SET CSR12). THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/S" PORT = "R/C"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

- 1) THE PORT STORING A "1" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR31 ENABLE

THIS IS A MICROCODE-SOFTWARE DEFINED BIT USED BY THE KL10 OPERATING SYSTEM TO INFORM THE PORT TO PLACE ITSELF IN THE "ENABLED" STATE (SET CSR13). THE STATE OF THE BIT HAS NO HARDWARE FUNCTION.

READ/WRITE STATUS: KL10 = "R/S" PORT = "R/C"

#### SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

## CLEARED BY:

- 1) THE PORT STORING A "1" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR32 MPROC RUN

THIS BIT, WHEN SET BY THE KL10, ENABLES THE PORT MICROPROCESSOR CLOCKS. THE PORT WILL START CYCLING AT THE ADDRESS CONTAINED IN THE "RAM ADDRESS REGISTER" (RAR). THE NEXT AND SUBSEQUENT ADDRESSES WILL BE FETCHED FROM THE "Y" OUTPUTS OF THE AM2910 SEQUENCER.

WHEN RESET FOR ANY REASON THE BIT CAUSES THE CRAM CONTROL REGISTER TO BE RESET, THUS PREVENTING ANY FURTHER PORT ACTIVITY AS A RESULT OF THE LAST MICROWORD.

READ/WRITE STATUS: KL10 = "R/W"

PORT = "R/H"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

#### CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) AFTER EACH MICROWORD CYCLE IF "DIAG SINGLE CYC" (CSR22) IS SET.

- 4) CRAM PAR ERR (CSR06) OR MBUS ERR (CSR07) SETTING.

- 5) A GENERAL EBUS RESET.

THIS BIT REPRESENTS BIT "0" OF THE THREE BIT PHYSICAL INTERRUPT ASSIGNMENT FIELD (PI LEVEL 01 THRU 07) OF THE KL10'S EBUS.

READ/WRITE STATUS: KL10 = "R/W"

PORT = "R"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

## CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR33 PIA00

CSR34 PIA01

THIS BIT REPRESENTS BIT "1" OF THE THREE BIT PHYSICAL INTERRUPT ASSIGNMENT FIELD (PI LEVEL 01 THRU 07) OF THE KL10'S EBUS.

READ/WRITE STATUS: KL10 = "R/W" PORT = "R"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

#### CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

THIS BIT REPRESENTS BIT "2" OF THE THREE BIT PHYSICAL INTERRUPT ASSIGNMENT FIELD (PI LEVEL 01 THRU 07) OF THE KL10'S EBUS.

READ/WRITE STATUS: KL10 = "R/W" PORT = "R"

## SET BY:

1) THE KL10 STORING A "1" IN THE BIT.

## CLEARED BY:

- 1) THE KL10 STORING A "0" IN THE BIT

- 2) THE KL10 SETTING CLEAR (CSR18)

- 3) A GENERAL EBUS RESET.

CSR35 PIA02

# 2.4 EBUS TO MICROPROC MUX (EMUX)

The EMUX is a two input by 36-bit wide multiplexer which takes data from either the EBUS, or the CSR REGISTER and passes it to the MBUS. The PORT MICROPROCESSOR may then strobe the data into one of its own storage medias.

When the PORT is in the "MPROC RUN" state (CSR32 set) this mux is normally enabled by the microprocessor commands, MPREADEBUS (READ EBUS) or MPREADCSR (READ CSR).

MPREADEBUS causes the contents of the EBUS to be passed to the MBUS. The PORT MICROPROC may strobe this data to one of its internal storage media.

MPREADCSR causes the contents of the CSR REGISTER to be passed to the MBUS. The PORT MICROPROC may strobe this data to one of its internal storage media.

When the PORT is not in the "MPROC RUN" state the KL10 may enable the MUX by executing DATAO commands in order to:

- a) write the CRAM

- b) write the RAR

- c) write the EBUF via the diagnostic loop-back path.

The below diagram illustrates the bit mapping of the EMUX.

| ! 00<br>! | EBUS D00-D35<br>OR<br>CSR00-35 | 35!<br>!<br>35! |

|-----------|--------------------------------|-----------------|

| !00       | MBUS D00-35                    | 35!             |

## 2.5 MICROPROC TO EBUS MUX (KMUX)

The KMUX is a two input by 36-bit wide multiplexer which takes data from either the EBUF, or the CSR REGISTER and passes it to the EBUS. The KL10 may then read the data from the EBUS.

When the PORT is not in the "MPROC RUN" state (CSR32 reset) the KL10 may enable the MUX by executing DATAI or CONI COMMANDS in order to (a) read the CRAM, (b) read the LAR, (c) read the EBUF, or (d) read the CSR.

When the PORT is in the "MPROC RUN" state (CSR32 set) the KL10 may enable the MUX by executing CONI COMMANDS in order to read the CSR, or by executing a "PI ADR IN" command during an interrupt sequence in order to read the IOP word.

The PORT MICROPROCESSOR may enable the MUX by executing the microprocessor command, MPLOADEBUS (LOAD EBUS). This command will cause the data currently asserted on the MBUS to be passed to the EBUS.

The below diagram illustrates the bit mapping of the KMUX.

| ! 00<br>! | EBUF00-35<br>OR<br>CSR00-35 | 35!<br>!<br>35! |

|-----------|-----------------------------|-----------------|

| !00       | KMUX00-35                   | 35!             |

## 2.6 EBUS PARITY GENERATOR

The EBUS PARITY GENERATOR generates odd parity for every 36-bit data word which the PORT passes to the EBUS.

The signals EBUS PARITY and EBUS PARITY ACTIVE are inhibited from being asserted on the EBUS during the transmission of an IOP FUNCTION CONTROL WORD. This is because the KL10 architecture does not permit parity checking on an IOP WORD.

## 2.7 EBUS PARITY CHECKER

The EBUS PARITY CHECKER normally checks every 36-bit data word which the PORT reads from the EBUS for odd parity. If parity is incorrect the EBUS PARITY ERROR bit (CSR24) in the CSR REGISTER will be set.

If CSR20 (DIAG GEN EBUS PE) is set, however, the EBUS PARITY CHECKER will check for even parity. This will cause EBUS PARITY ERROR (CSR24) to be set on the same CONO command. This feature is useful for diagnostic purposes.

### 2.8 EBUS TRANSCEIVERS

The EBUS Transceivers consist of OPEN-COLLECTOR 8838 type transceivers, as are currently used by other devices which interface to the EBUS.

#### 2.9 ARITHMETIC LOGIC UNIT

The PORT MICROPROCESSOR ALU is also located on the EBUS INTFC/PORT ALU module. Therefore, even though it is logically part of the PORT MICROPROCESSOR, it will be discussed here.

The ALU may be sub-divided into:

- 1) Nine AM2901 type FOUR-BIT BIPOLAR MICROPROCESSOR SLICES

- 2) Four AM2902 type HIGH-SPEED LOOK-AHEAD CARRY GENERATORS

- 3) Five 74LS157 type MULTIPLEXERS used by the MICROPROCESSOR CONTROL to input a CONSTANT NUMBER FIELD into the ALU

The nine AM2901s and four AM2902s are configured in a standard parallel manner so as to form a 36-bit wide word with high speed carry look-ahead capability.

The "Y" outputs and "D" inputs of the ALU are connected directly to the MBUS, except for bits 00-09 and 26-35 of the "D" inputs. These 20 bits are connected through a two input multiplexer, the CNST MUX, to the 2901s' "D" inputs (see CONSTANT MUX for details).

The clock input to the ALU is the CPUCLOCK (CLK4 gated by MPROC RUN).

For shift operations the ALU will always shift 0s into either the MSB or the LSB, depending on the direction of the shift.

The PORT MICROPROCESSOR controls the ALU by executing the following microprocessor commands:

1) MWSORCEFLD<00-02> (ALU SOURCE INPUT FIELD (I2-I0)) - This field is the SOURCE INPUT FIELD (I2-I0) of the AM2901 ALU. Its function is defined by "THE AM2900 FAMILY DATA BOOK" as follows:

| OCTAL CODE            | R   | S |

|-----------------------|-----|---|

| MWSORCEFLD<00:02> = 0 | A   | 0 |

| MWSORCEFLD<00:02> = 1 | Α   | B |

| MWSORCEFLD<00:02> = 2 | Z   | 0 |

| MWSORCEFLD<00:02> = 3 | Z   | ã |

| MWSORCEFLD<00:02> = 4 | Z   | Ā |

| MWSORCEFLD<00:02> = 5 | D   | A |

| MWSORCEFLD<00:02> = 6 | D   | 0 |

| MWSORCEFLD<00:02> = 7 | D D | Ž |

2) MWFUNCTFLD<00-02> (ALU FUNCTION FIELD (I5-I3)) - This field is the FUNCTION INPUT FIELD (I5-I3) of the AM2901 ALU. Its function is defined by "THE AM2900 FAMILY DATA BOOK" as follows:

| OCTAL CODE                                                                                                                | SYMBOL                                       |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| MWFUNCTFLD<00:02> = 0<br>MWFUNCTFLD<00:02> = 1<br>MWFUNCTFLD<00:02> = 2<br>MWFUNCTFLD<00:02> = 3<br>MWFUNCTFLD<00:02> = 4 | R + S<br>S - R<br>R - S<br>R or S<br>R and S |

| MWFUNCTFLD<00:02> = 5<br>MWFUNCTFLD<00:02> = 6                                                                            | R and S                                      |

| MWFUNCTFLD<00:02> = 7                                                                                                     | R xor S                                      |

3) MWDESTFLD<00-02> (ALU DESTINATION OUTPUT FIELD (18-16)) - This field is the DESTINATION FIELD (18-16) inputs to the AM2901 ALU. Its function is defined by "THE AM2900 FAMILY DATA BOOK" as follows:

| TAL CODE     | MNEMONIC                                      |

|--------------|-----------------------------------------------|

|              |                                               |

| = 0          | QREG                                          |

| <del>_</del> | NOP                                           |

|              | RAMA                                          |

| = 3          | RAMF                                          |

| = 4          | RAMOD                                         |

| = 5          | RAMD                                          |

| = 6          | RAMQU                                         |

| = 7          | RAMU                                          |

|              | = 0<br>= 1<br>= 2<br>= 3<br>= 4<br>= 5<br>= 6 |

- 4) MWPORTAFLD<00-03> (ALU PORT "A" (A3-A0) ADDRESS FIELD) This field is the PORT "A" (A3-A0) ADDRESS FIELD inputs to the AM2901 ALU (see "THE AM2900 FAMILY DATA BOOK")

- 5) MWPORTBFLD<00-03> (ALU PORT "B" (B3-B0) ADDRESS FIELD) This field is the PORT "B" (B3-B0) ADDRESS FIELD inputs to the AM2901 ALU (see "THE AM2900 FAMILY DATA BOOK")

- 6) MWCARRY (MICROWORD CARRY INPUT BIT TO ALU) This bit is the carry input to the least significant bit of the AM2901 ALU.

MWCARRY = 0 Carry "ZERO" into the LSB of the ALU MWCARRY = 1 Carry "ONE" into the LSB of the ALU

The PORT MICROPROCESSOR monitors the ALU status by sensing the following CONDITION CODES:

- 1) CCFEQL0 This CONDITION CODE indicates that the result of the last ALU operation produced all "ZEROS".

- 2) CCMBSIGN This CONDITION CODE indicates that the SIGN (MSB or bit 00) was set as the result of the last ALU operation.

### 2.9.1 CONSTANT MUX

The CNST MUX is a two input multiplexer which allows either MBUS D00-D09 and D26-D35, or MWMGCFLD00-09 of the MICROWORD to be loaded into the ten MSBs and the ten LSBs of the "D" inputs to the MICROPROC ALU (AM290ls). This enables the MICROPROCESSOR to load a CONSTANT NUMBER VALUE into the ALU's 10 most significant and 10 least significant bits. MBUS D10-D25 are always loaded into the corresponding "D" inputs.

The PORT loads the MWMGCFLD field of the CRAM CONTROL WORD, instead of the MBUS DATA bits, into the ALU's "D" inputs by executing the microprocessor command, SELCNSTFLD (SELECT CONSTANT FIELD) (setting the MWSKIPFLD to 24 or 34).

The below diagram illustrates the bit mapping of this MUX.

| ! 00 | MBUS D00-D09  | 09!   | MBUS D10-D25 | !26   | MBUS D26-D35  | 35! |

|------|---------------|-------|--------------|-------|---------------|-----|

| !    | OR            | !10   |              | 25!   | OR            | !   |

| ! 00 | MWMGCFLD00-09 | 09!   |              | !00   | MWMGCFLD00-09 | 09! |

| !00  | "D" INPUTS    | 09!10 | "D" INPUTS   | 25!26 | "D" INPUTS    | 35! |

## 3.0 CBUS/DATA MOVER INTFC MODULE (CMVR)

The CBUS/DATA MOVER INTFC MODULE (CMVR) consists primarily of:

- a) A data path between the KL10's CBUS and the PACKET BUFFER'S PLI INTERFACE, which may be further sub-divided into:

- 1) CBUS INTERFACE BUFFERS, CBUS PARITY GEN/CHKRS and associated CBUS CONTROL LOGIC

- 2) PLI INTERFACE BUFFERS, PLI PAR GEN/CHKR and associated PLI CONTROL LOGIC

- 3) A DATA FORMATTER and MOVER which resides between the CBUS and the PLI INTERFACE, and has the function of mapping 8-bit PLI bytes into 36-bit KL10 words, and vice versa.

- b) A data path between the CBUS/DATA MOVER INTFC MODULE (CMVR) and the PORT MICROPROCESSOR which enables the MICROPROCESSOR to:

- 1) Load or read the DATA FORMATTER and MOVER (MVR/FMTR)

- Load or read the PACKET BUFFERS via the PLI INTERFACE

- C) CMVR CONTROL LOGIC which decodes and executes the commands specified by the MICRPPROCESSOR CONTROLLER'S microword.

The PORT MICROPROCESSOR accesses the CMVR MODULE by executing microprocessor commands. These commands are decoded functions of the MWBUSCTLFLD field and the MWMGCFLD field of the CRAM CONTROL WORD.

The PORT MICROPROCESSOR monitors the CMVR CONTROL LOGICS status by sensing CONDITION CODES.

## 3.1 CBUS TIMING DESKEW PROCEDURE

The following deskew procedure should be performed before CBUS TRANSFERS are attempted.

- a) Equipment required Tektronics 475 or equivalent (100 MHz) scope with identical probes and short ground clips.

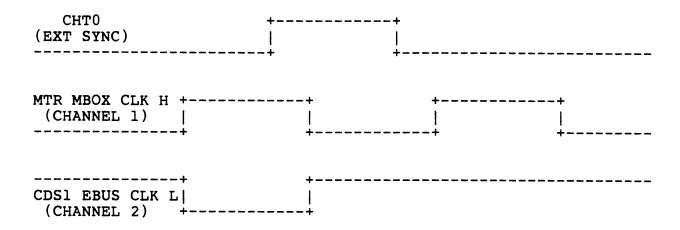

- b) Objectives To deskew the CI20 to the MBOX clock that produces channel time zero, CHT0.

- c) Notes Recheck skew whenever the CBUS cable is replaced.

- d) Adjustment procedure -

- 1) Attach a probe (either ext, sync or channel 3) to CHTO H, 4B09Kl

- 2) Sync positive external

- 3) Attach channel 1 probe to MTR MBOX CLK H, 4D33P1

- 4) Push TRIGGER VIEW and verify that the MBOX CLK that occurs just prior to CHTO can be seen on the scope. See diagram below:

- 5) Attach channel 2 probe to CDS1 EBUS CLK L, 2A15F1

- 6) Align clock pulse on channel 2 with the MBOX clock that occurs approximately 10 nanoseconds before CHTO.

## 3.2 CMVR CONTROL LOGIC

The CMVR CONTROL LOGIC decodes and executes the commands specified by the MICRPPROCESSOR CONTROLLER'S microword.

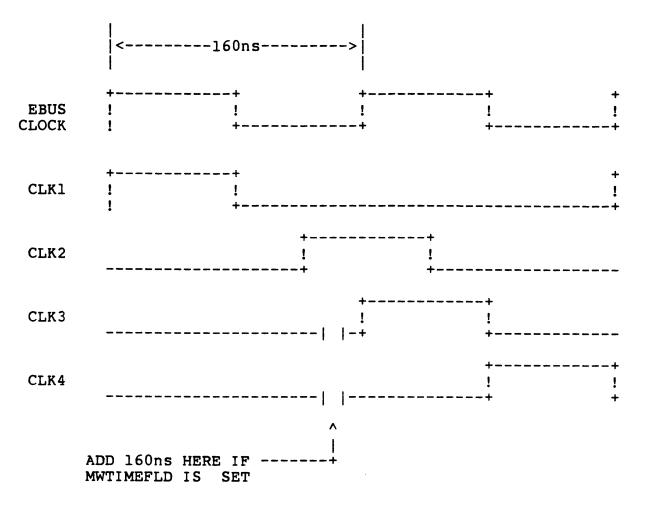

It also generates and distributes the PORT clocks (CLK1, CLK2, CLK3 and CLK4) to all three PORT modules.

The timing for the clocks is derived from the KL10's EBUS CLOCK. The below diagram illustrates the timing relationship of the clocks when the KL10's EBUS CLOCK is operating at the normal 160ns cycle time.

CLK1 normally strobes the next MICROWORD into the PORT'S MICROWORD CONTROL REGISTER. It also has several other timing functions, depending on the specific operation being executed.

CLK2, CLK3 & CLK4 are generally used by the various control logics to execute the function which is specified by the MICROWORD.

All four clocks are gated by control logic on the PORT MICROPROC CONTROL module. The gated clocks are known as RUNCLK1, RUNCLK2, RUNCLK3 and RUNCLK4 respectively. CLK4 also generates CPUCLOCK, which is used as the clock input to the AM2901 ALU. The gating of these clocks allows the PORT to be started, stopped and single cycled in an orderly manner.

A microword bit, MWTIMEFLD (TIME EXTENTION FIELD), may be set on any specific microcycle. Setting this bit will cause CLK3 and CLK4 to occur 135ns later than normal for that microcycle, thus lengthening the microcycle from 270ns to 405ns. This feature allows more execution time for the microcycle, thus offering an easy solution for timing problems which may arise due to insufficient microcycle execution time on any specific micro-instruction.

## 3.3 MICROPROC TO CMVR REGISTER (CBUF)

The "MICROPROCESSOR TO CMVR BUFFER" (CBUF) is a 36-bit buffer normally used by the PORT MICROPROCESSOR to pass data from the MBUS (Internal tri-state MICROPROCESSOR BUS) to the CBUS/DATA MOVER INTFC MODULE (CMVR).

The CBUF acts only as an isolation buffer to the tri-state MBUS and is logically transparent to the PORT MICROPROCESSOR.

# 3.4 DATA FORMATTER and MOVER (MVR/FMTR)

The MVR/FMTR consists of a series of parallel/serial shift registers and their associated control. It may be:

- a) Parallel loaded and read as a 36-bit register from the PORT MICROPROCESSOR.

- b) Parallel loaded and read as a 36-bit register from the CBUS.

- c) Parallel read as an 8-bit register by the PLI INTERFACE.

- d) Serially loaded and left shifted (from LSB to MSB), four or eight bits at a time, from the PLI INTERFACE. In this mode data is not wrapped around, but is shifted out of and lost from the MSB.

- e) Serially loaded and right shifted (from MSB to LSB), four or eight bits at a time, from the PLI INTERFACE. In this mode the data may be wrapped around from LSB to MSB. Additional shifts may be used to re-align the data in the desired format.

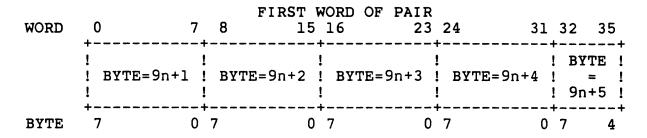

Four bit nibbles from the PLI INTERFACE are shifted up from the bottom or down from the top of the MVR/FMTR. Two shifts load one 8-bit byte. Logic hardware enables the PORT MICROPROCESSOR to execute one shift or two shifts on a single microcycle. By loading four bit nibbles from the PLI INTFC and shifting either up or down 36-bit KL10 words may be formed and parallel transferred to the CBUS.

If the PLI INTERFACE is loaded from the bottom of the MVR/FMTR and shifted up the data is not wrapped around, but is shifted out and lost from the 4 MSBs of the MVR/FMTR.

If the PLI INTERFACE is loaded from the top and shifted down the data may be wrapped around such that the 4 LSBs of the MVR/FMTR feed back into the 4 MSBs of the MVR/FMTR. In this manner data may be shifted indefinitely around the MVR/FMTR and re-aligned in the desired manner.

The PORT MICROPROCESSOR has the ability to select either the four MSBs or the four LSBs of the PLI byte to input first to the MVR/FMTR.

36-bit KL10 words may be loaded into the MVR/FMTR from the CBUS. Once a word is loaded the PORT MICROPROC can shift it, either up or down, into the PLI OUT REG for transfer to the PLI INTERFACE.

The associated commands which are used to control the MVR/FMTR are as follows:

- 1) MPSHFTFMTR8 (SHIFT FORMATTER BY 8 BITS) causes the contents of the MVR/FMTR to be shifted eight bits to the left or right, depending on the state of the command "MPSHIFTRIGHT".

- 2) MPSHFTFMTR4A (SHIFT FORMATTER BY 4 BITS) causes the contents of the MVR/FMTR to be shifted four bits to the left or right, depending on the state of the command "MPSHIFTRIGHT".

- 3) MPSHFTFMTR4B (SHIFT FORMATTER BY 4 BITS) causes the contents of the MVR/FMTR to be shifted four bits to the left or right, depending on the state of the command "MPSHIFTRIGHT".

- 4) MPCBUFTOFMTR (CBUF TO FORMATTER) causes the data which has been previously stored in the CBUF to be loaded into the MVR/FMTR REGISTER

- 5) MPPLINTOFMTR (PLI INPUT BUFFER TO FORMATTER) causes the 8-bit data byte which is currently stored in the PLI INPUT BUFFER to be shifted into the serial input lines of the MVR/FMTR, four bits at a time. This command must be executed in conjunction with MPSHFTFMTR4A or MPSHFTFMTR8. If MPSHFTFMTR4A is executed, then only four bits from the PLI INPUT BUFFER will be shifted into the

serial input lines of the MVR/FMTR. If MPSHFTFMTR8 is executed, then all 8 bits from the PLI INPUT BUFFER will be shifted into the serial input lines. Either the four MSBs or the four LSBs are shifted in first, depending on the state of the command, MPRHTNIBFIRST. If an MPSHFTFMTR4A is executed, then only the first four bits specified by the state of MPRHTNIBFIRST will be shifted into the serial input lines. If MPSHIFTRIGHT is asserted the 4-bit nibbles will be shifted into the four MSBs of the MVR/FMTR and shifted right. Otherwise, they will be shifted into the four LSBs of the MVR/FMTR and shifted left.

- 6) MPFMTRTOPLOUT (FORMATTER TO PLI OUTPUT BUFFER) causes the 8-bit data byte which is currently stored in the PLI OUTPUT REG of the MVR/FMTR to be loaded into the PLI OUTPUT BUFFER.