PDP-10 Maintenance Manual

# VP10 DISPLAY CONTROL

## PDP-10 VP10 DISPLAY CONTROL MAINTENANCE MANUAL

1st Printing June 1969 2nd Printing (Rev) November 1969

Copyright © 1969 by Digital Equipment Corporation

Instruction times, operating speeds and the like are included in this manual for reference only; they are not to be taken as specifications.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC

PDP

FLIP CHIP

**FOCAL**

DIGITAL

**COMPUTER LAB**

## CONTENTS

|       |                                              | Page |

|-------|----------------------------------------------|------|

|       | CHAPTER 1 GENERAL INFORMATION                |      |

| ,1.1  | Scope                                        | 1-1  |

| 1.2   | General Description                          | 1-1  |

| 1.3   | Specifications                               | 1-2  |

| 1.3.1 | Module Utilization                           | 1-4  |

| 1.4   | Mnemonics                                    | 1-4  |

| 1.5   | Levels and Pulses                            | 1-5  |

| 1.6   | Major Logic Sections, Simplified Description | 1-6  |

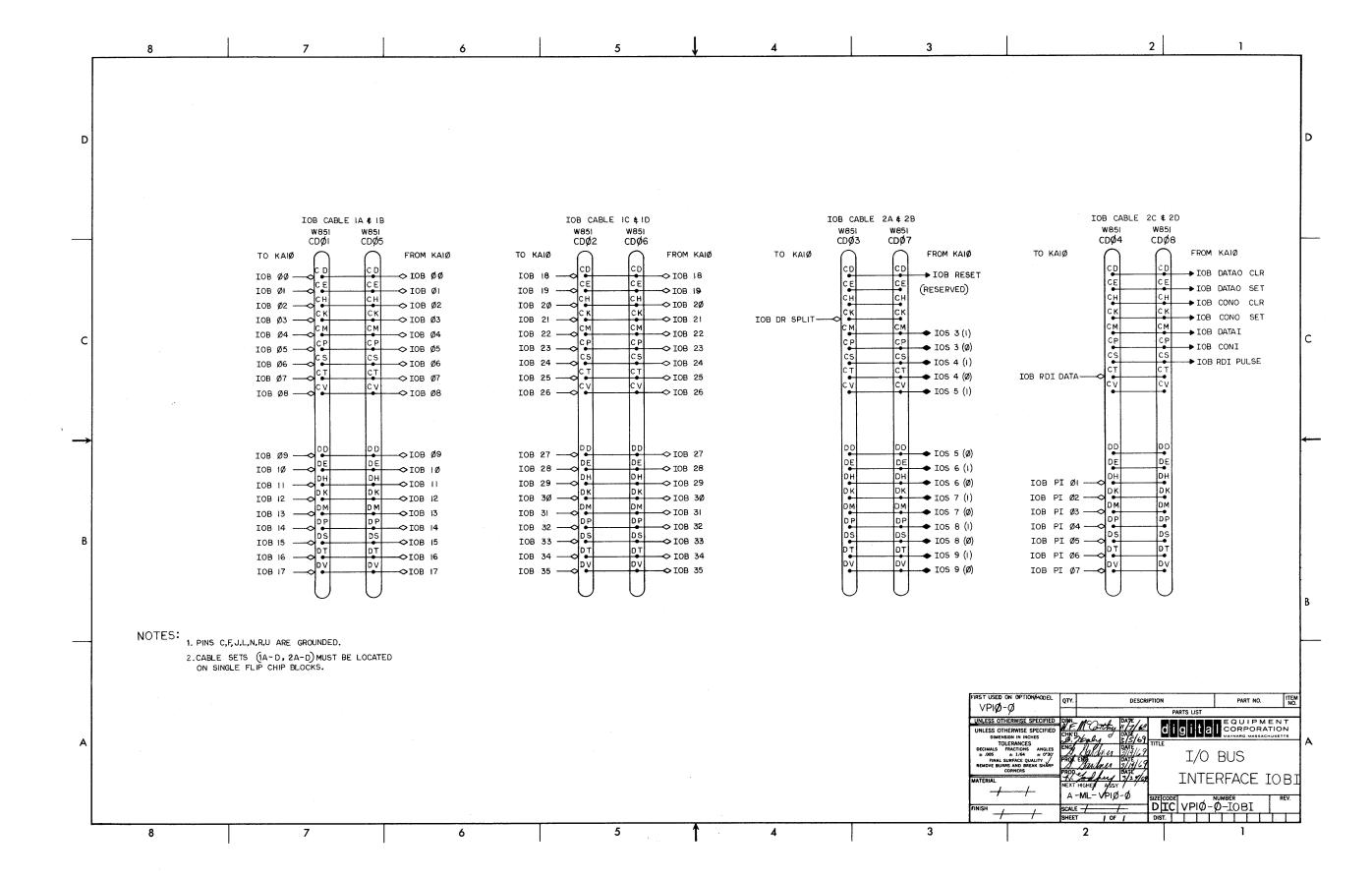

| 1.6.1 | I/O Bus Interface                            | 1-7  |

| 1.6.2 | I/O Bus Control                              | 1-7  |

| 1.6.3 | Display Control                              | 1-7  |

| 1.6.4 | XY Buffers and Digital-to-Analog Converters  | 1-7  |

| 1.6.5 | Status Control                               | 1-8  |

| 1.6.6 | Reference Material                           | 1-8  |

|       | CHAPTER 2 INSTALLATION                       |      |

| 2.1   | Scope                                        | 2-1  |

| 2.2   | Unpacking                                    | 2-1  |

| 2.3   | Site Selection                               | 2-1  |

| 2.4   | Installation Specifications                  | 2-3  |

| 2.4.1 | Interconnection                              | 2-3  |

|       | CHAPTER 3 OPERATION AND PROGRAMMING          |      |

| 3.1   | Scope                                        | 3-1  |

| 3.2   | VP10 Controls and Indicators                 | 3-1  |

| 3.2.1 | Indicator Panel                              | 3-1  |

| 3.2.2 | Switch Panel                                 | 3-2  |

| 3.2.3 | Type 844 Power Control                       | 3-3  |

| 3.2.4 | Margin Switches                              | 3-4  |

| 3.3   | I/O Information                              | 3-4  |

| 3.3.1 | VP10 I/O Conditions                          | 3-4  |

| 3.4   | VP10 Operations                              | 3-5  |

## CONTENTS (Cont)

|       |                                    | Page |

|-------|------------------------------------|------|

| 3.5   | Sample Program                     | 3-6  |

|       | CHAPTER 4 PRINCIPLES OF OPERATION  |      |

| 4.1   | Scope                              | 4-1  |

| 4.2   | Conditions Out Instruction - CONO  | 4-1  |

| 4.3   | Data Out Instruction - DATAO       | 4-3  |

| 4.4   | Conditions in Instruction CONI     | 4-5  |

| 4.5   | Data In Instruction - DATAI        | 4-6  |

| 4.6   | Other Logic                        | 4-6  |

| 4.6.1 | CROBAR                             | 4-6  |

| 4.6.2 | HI SPEED                           | 4-6  |

| 4.6.3 | TEST MODE                          | 4-7  |

| 4.6.4 | IOBC RESET                         | 4-8  |

| 4.6.5 | LP STROBE                          | 4-8  |

|       | CHAPTER 5 MAINTENANCE              |      |

| 5.1   | Scope                              | 5-1  |

| 5.2   | Preventive Maintenance             | 5-1  |

| 5.2.1 | Mechanical Inspection and Cleaning | 5-1  |

| 5.2.2 | Electrical Inspection              | 5-2  |

| 5.3   | Corrective Maintenance             | 5-3  |

| 5.3.1 | Preliminary Investigation          | 5-3  |

| 5.3.2 | Diagnostic Program                 | 5-4  |

| 5.3.3 | Test Mode                          | 5-4  |

| 5.3.4 | Signal Tracing                     | 5-5  |

| 5.3.5 | Validation Test                    | 5-5  |

| 5.3.6 | Log Entry                          | 5-5  |

|       | CHAPTER 6 PARTS LIST               |      |

| 6.1   | Scope                              | 6-1  |

| 6.2   | Modules                            | 6-1  |

| 6.2.1 | Semiconductors                     | 6-2  |

## CONTENTS (Cont)

|              |                                              | rage |  |  |  |

|--------------|----------------------------------------------|------|--|--|--|

| 6.2.2        | Power Supplies                               | 6-3  |  |  |  |

| 6.2.3        | Indicator Lamps                              | 6-3  |  |  |  |

|              | CHAPTER 7 ENGINEERING DRAWINGS               |      |  |  |  |

| 7-1          | Scope                                        | 7-1  |  |  |  |

|              | APPENDIX A<br>LIGHT PEN 370 TECHNICAL MANUAL |      |  |  |  |

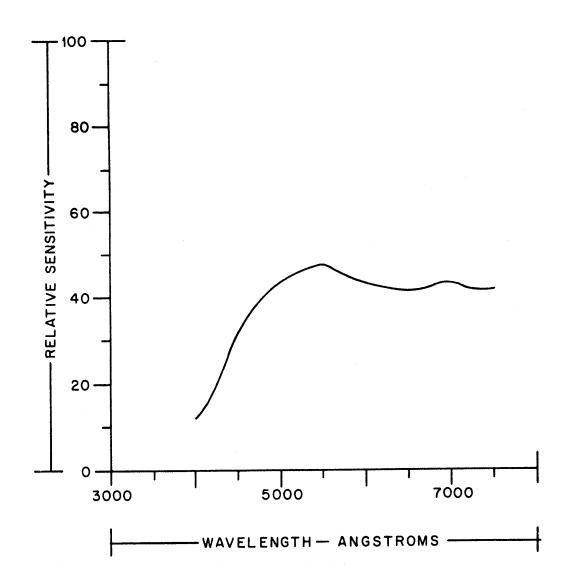

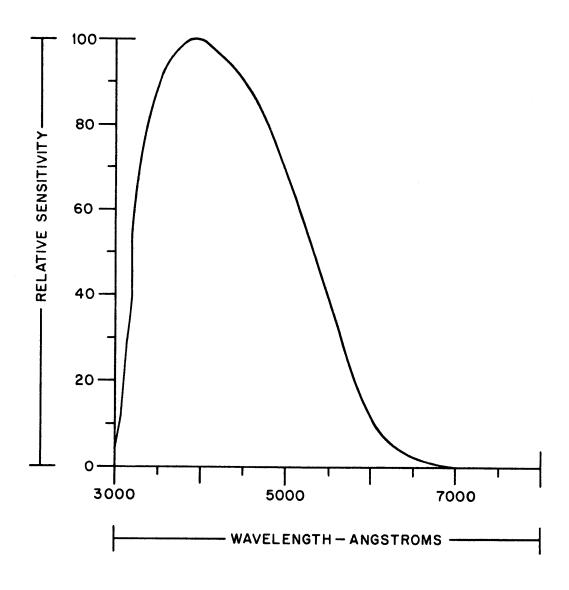

| A-1          | Introduction                                 | A-1  |  |  |  |

| A-2          | Specifications                               | A-2  |  |  |  |

| A-3          | Theory of Operation                          | A-3  |  |  |  |

| A-4          | Maintenance                                  | A-6  |  |  |  |

|              | ILLUSTRATIONS                                |      |  |  |  |

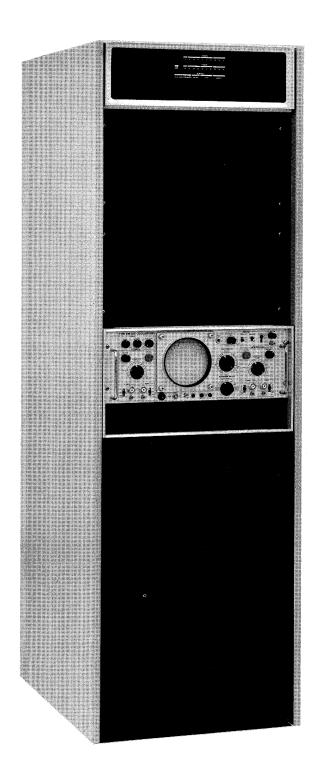

| Frontispiece | VP10 Point Plot Display Control              |      |  |  |  |

| 1-1          | VP10 Front View                              | 1-3  |  |  |  |

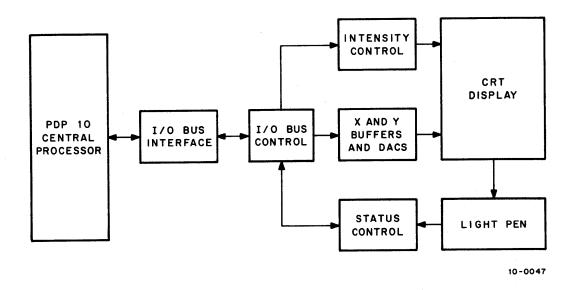

| 1-2          | Simplified Block Diagram                     | 1-7  |  |  |  |

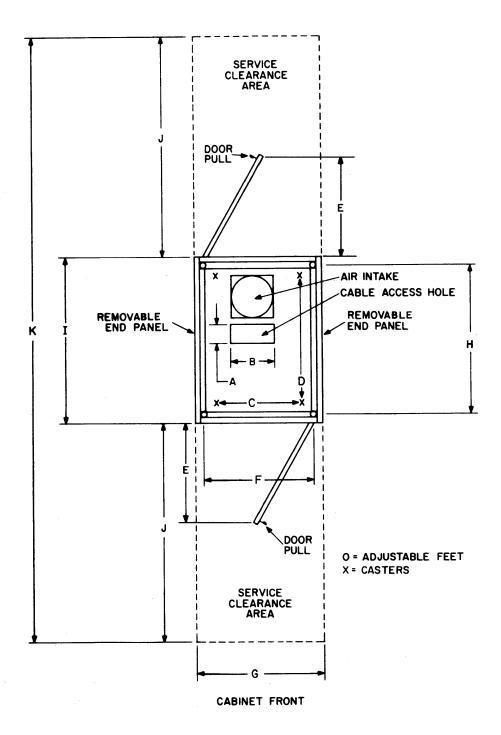

| 2-1          | VP10 Area Requirements                       | 2-2  |  |  |  |

| 3-1          | Indicator Panel                              | 3-2  |  |  |  |

| 3-2          | Switch Panel                                 |      |  |  |  |

| 3-3          | Power Control Panel                          | 3-3  |  |  |  |

| 3-4          | Sample Program Display                       | 3-9  |  |  |  |

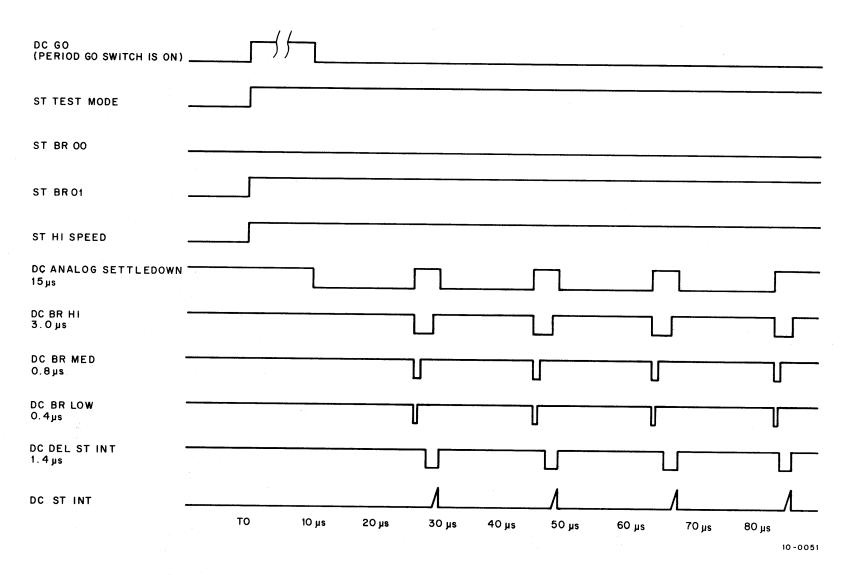

| 4-1          | TEST MODE Timing Diagram                     | 4-2  |  |  |  |

| 5-1          | Plenum Door Layout                           | 5-2  |  |  |  |

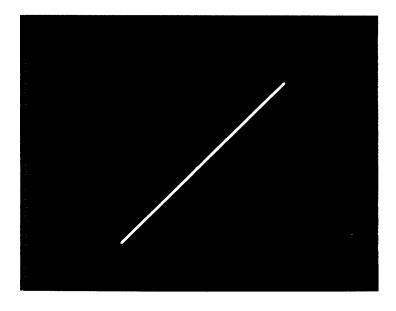

| 5-2          | Test Mode Display                            | 5-4  |  |  |  |

|              | TABLES                                       |      |  |  |  |

| 1-1          | DEC FLIP CHIP Modules for VP10               | 1-4  |  |  |  |

| 1-2          | Mnemonics                                    | 1-4  |  |  |  |

| 1-3          | VP10 Levels and Pulses                       | 1-5  |  |  |  |

| 2-1          | General Specifications                       | 2-3  |  |  |  |

| 2-2          | Cable Interconnections                       |      |  |  |  |

| 3-1          | Data/Status Register Monitoring              |      |  |  |  |

| 3-2          | Switches/Connectors                          | 3-3  |  |  |  |

## CONTENTS (Cont)

|     |                                 | Page |

|-----|---------------------------------|------|

| 3-3 | Power Control Functions         | 3-4  |

| 3-4 | Sample Program                  | 3-8  |

| 6-1 | VP10 Module Requirements        | 6-1  |

| 6-2 | VP10 Semiconductor Requirements | 6-2  |

| 7-1 | Engineering Drawing Index       | 7-1  |

VP10 Point Plot Display Control

## 1.1 SCOPE

This manual provides the necessary information for installation, operation, and maintenance of the VP10 Point Plot Display Control. The VP10 is intended for use with the PDP-10 Computer System.

Reference documents which supplement the material presented in this manual are listed in Section 1.6.6.

## 1.2 GENERAL DESCRIPTION

The VP10 is housed in a DEC cabinet, Type CAB 9-B, which can accommodate up to 12 horizontal 5-3/16 in. x 19 in. panels. Two locations are utilized for the logic, which is contained in DEC Type 1943B mounting panels. The indicator panel occupies one location as illustrated in Figure 1-1. A half-height single door, mounted on the lower front of the cabinet, provides access to the wiring side of the logic panels. A DEC Type 728 Power Supply and Type 844 Power Control are mounted in the bottom two locations on the hinged full-width plenum door at the rear of the cabinet. Ventilation is provided by a single fan, mounted on the floor of the cabinet, which draws in filtered air. Three blower fans, below the logic panels, circulate the filtered air around the modules.

The VP10 accepts coordinate address words from the PDP-10 Central Processor. These words are converted to appropriate analog levels and applied to the horizontal and vertical deflection inputs of an oscilloscope (Tektronix Type RM503, or equivalent) or an appropriate CRT Display (DEC Type VR12) to provide a point plot of the coordinate address words. The program can designate a variable duration pulse to the Z axis input of the display, to produce an intensity modulated plot. The VP10 is program-compatible with the DEC Type 30E Display Control.

The following information can be displayed on the cathode-ray tube (CRT) display:

- a. mathematical curves

- b. line drawings

c. in general, any graphic which can be written in binary form and stored in the PDP-10 Memory.

Most stored data is in a form that requires mathematical operations within the computer, specified by the program, before transmission to the VP10 for display.

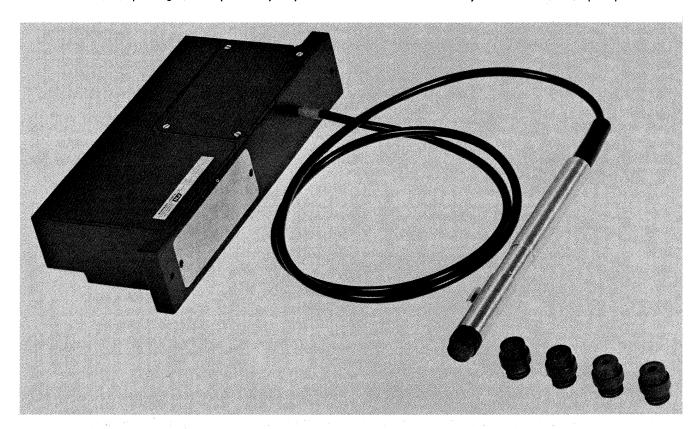

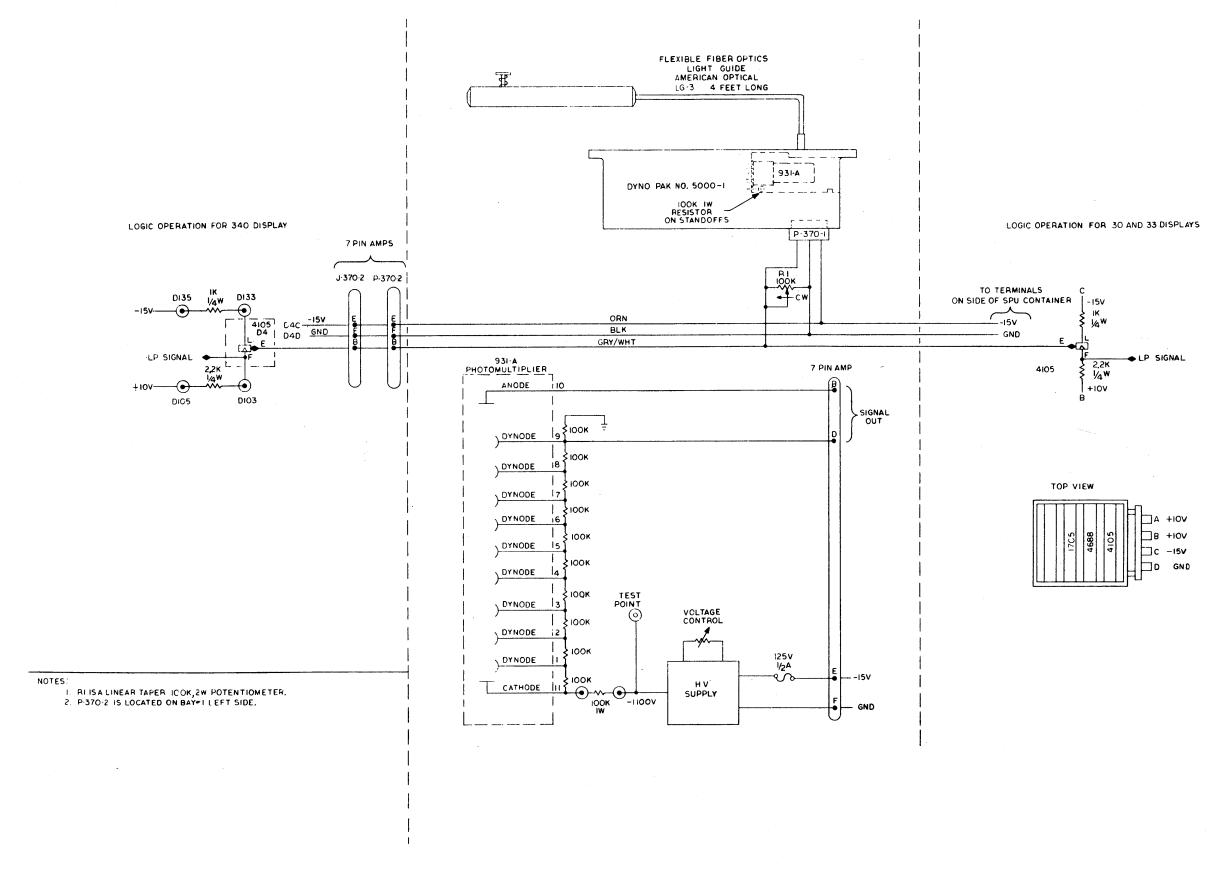

The VP10 contains logic which allows a light pen to control or communicate with the program by use of a priority interrupt channel selection system. The DEC Type 370 Light Pen is described in Appendix A.

## NOTE

The light pen and light pen power supply, as well as the Tektronix Type RM503, with mounting hardware for adaptation to the DEC CAB 9B cabinet, are offered as options to the VP10.

## 1.3 SPECIFICATIONS

Size: 69-1/2 in. h, 21-1/4 in. w, 27-1/16 in. d

(1763 mm h, 540 mm w, 690 mm d)

Weight: (260 lb, 118 kg)

Voltage Requirements:  $115V \pm 10\%$ , 60 Hz  $\pm 2\%$

$230V \pm 10\%$ , 50 Hz  $\pm 2\%$

Current Consumption: 2.0A

Power Dissipation: 230W

Temperature: 16°C to 32°C Ambient (operating)

61°F to 90°F

4°C to 43°C Ambient (storage)

39°F to 110°F

Humidity: 20% to 80% (relative)

X 0V to -10V Y 0V to -10V

Z -15V to +10V

Logic Levels 0V, -3V

Output Levels:

Figure 1-1 VP10 Front View

## 1.3.1 Module Utilization

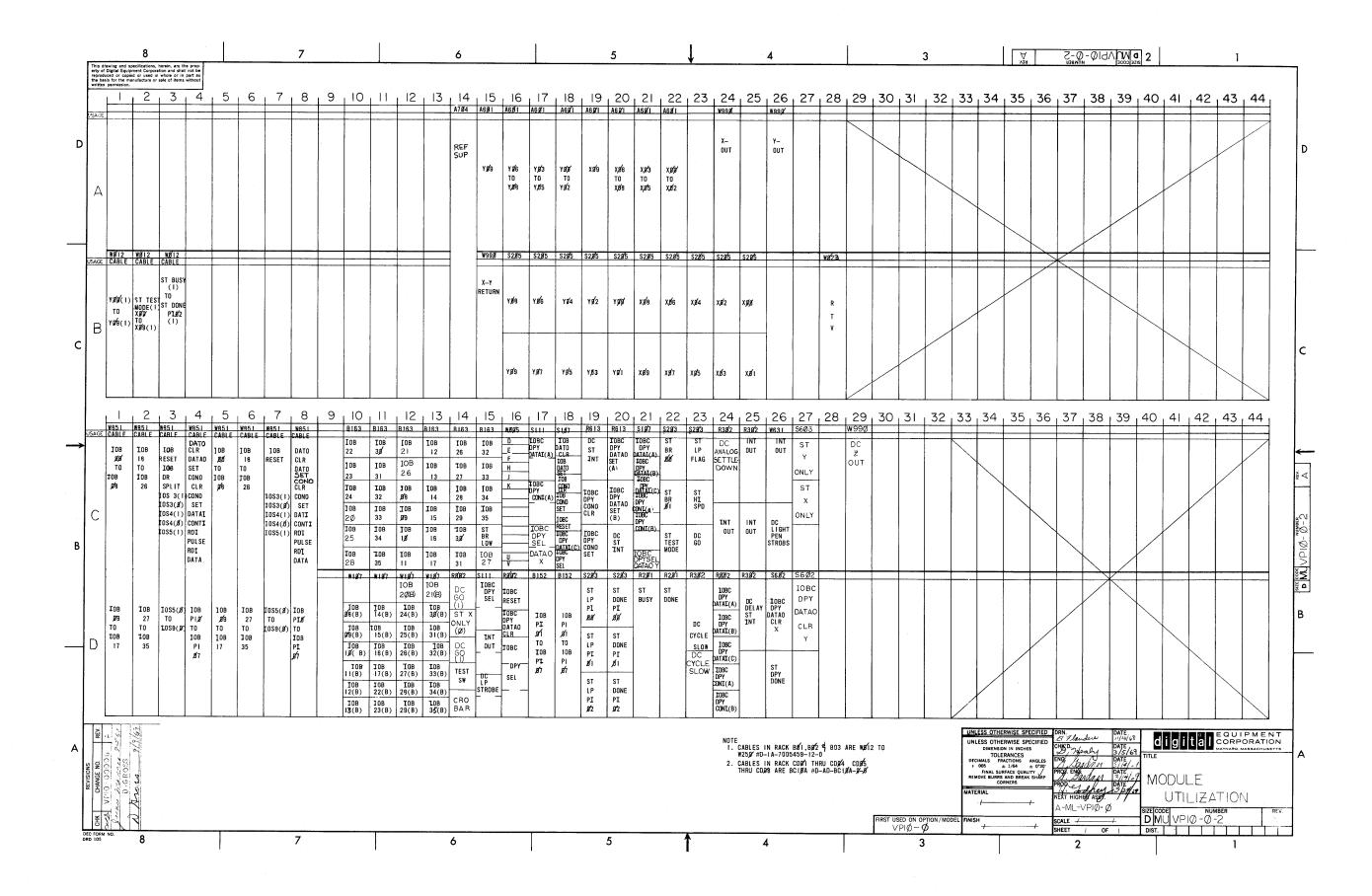

Table 1-1 is a list of the DEC FLIP CHIP Modules used in the VP10. Refer to drawing D-MU-VP10-0-2 in Chapter 7 of this manual for the location within the display and the logical function of each module.

Table 1-1

DEC FLIP CHIP Modules for VP10

| DEC<br>Number | Description                 | DEC<br>Number | Description                |

|---------------|-----------------------------|---------------|----------------------------|

| A601          | Digital-to-Analog Converter | S203          | Triple Flip-Flop           |

| A704          | Reference Supply            | S205          | Dual Flip-Flop             |

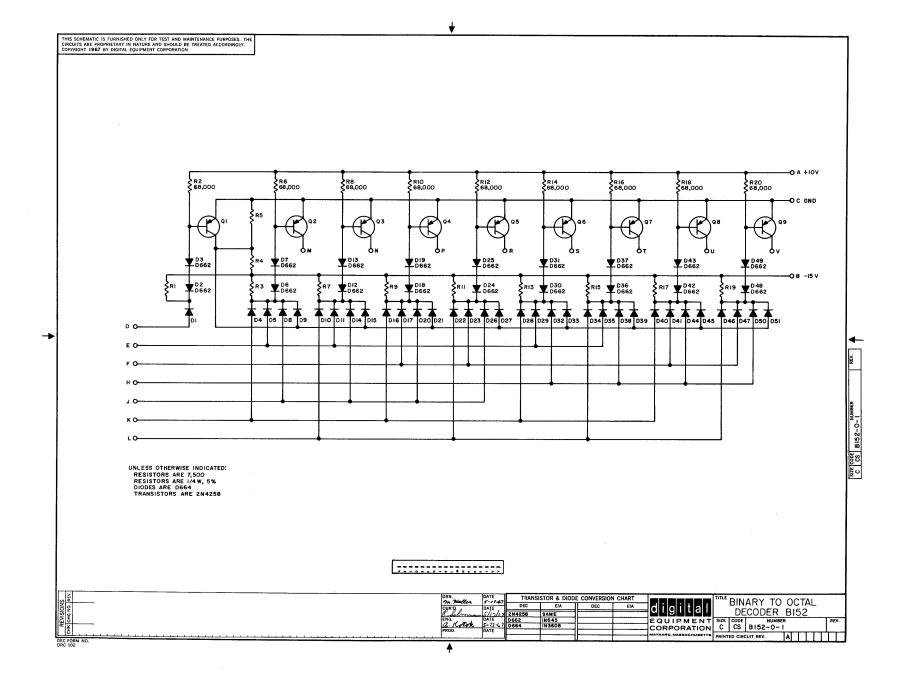

| B152          | Binary-to-Octal Decoder     | W005          | Clamped Load               |

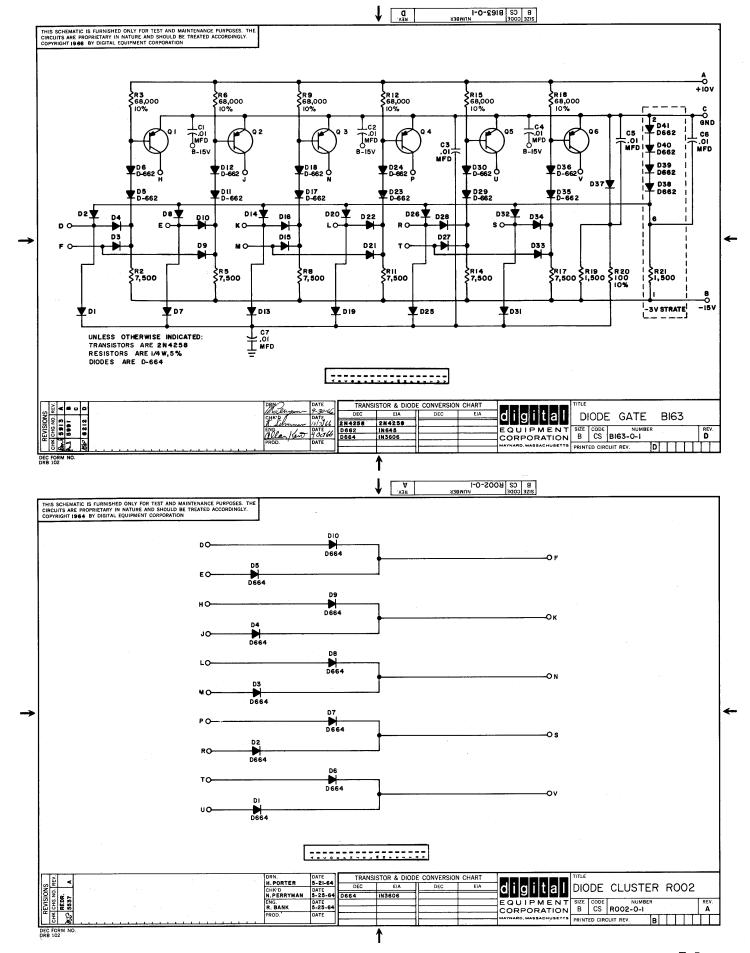

| B163          | Diode Gate                  | W012          | Indicator Cable Connector  |

| R002          | Diode Network               | W023          | Cable Connector            |

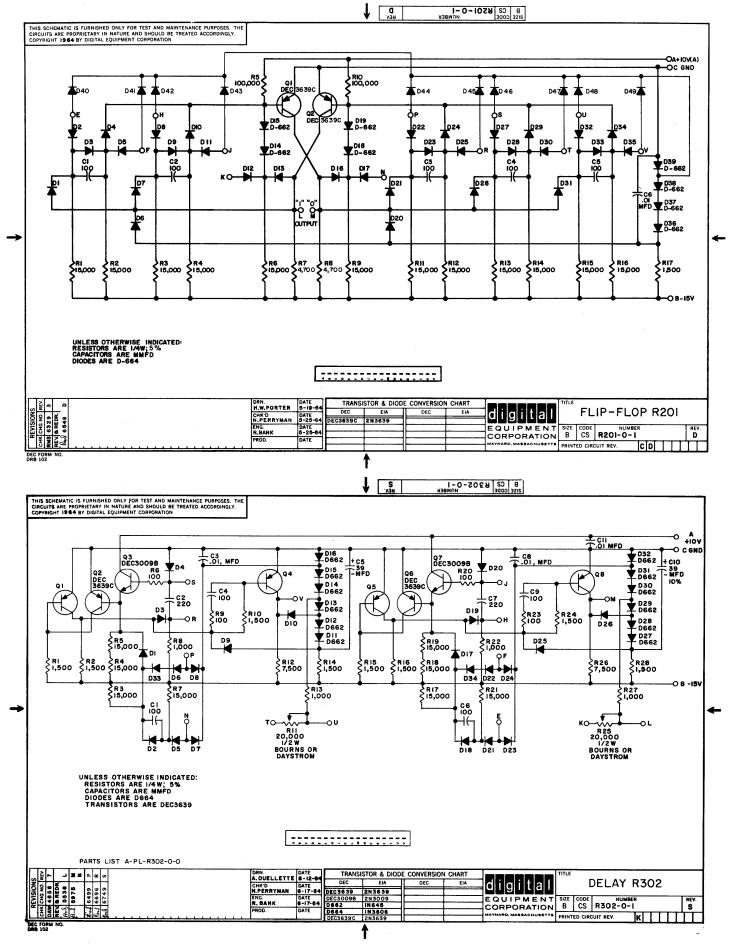

| R201          | Flip-Flop                   | W107          | I/O Bus Receiver           |

| R302          | Dual Delay Multivibrator    | W250          | Indicator Cable Connector  |

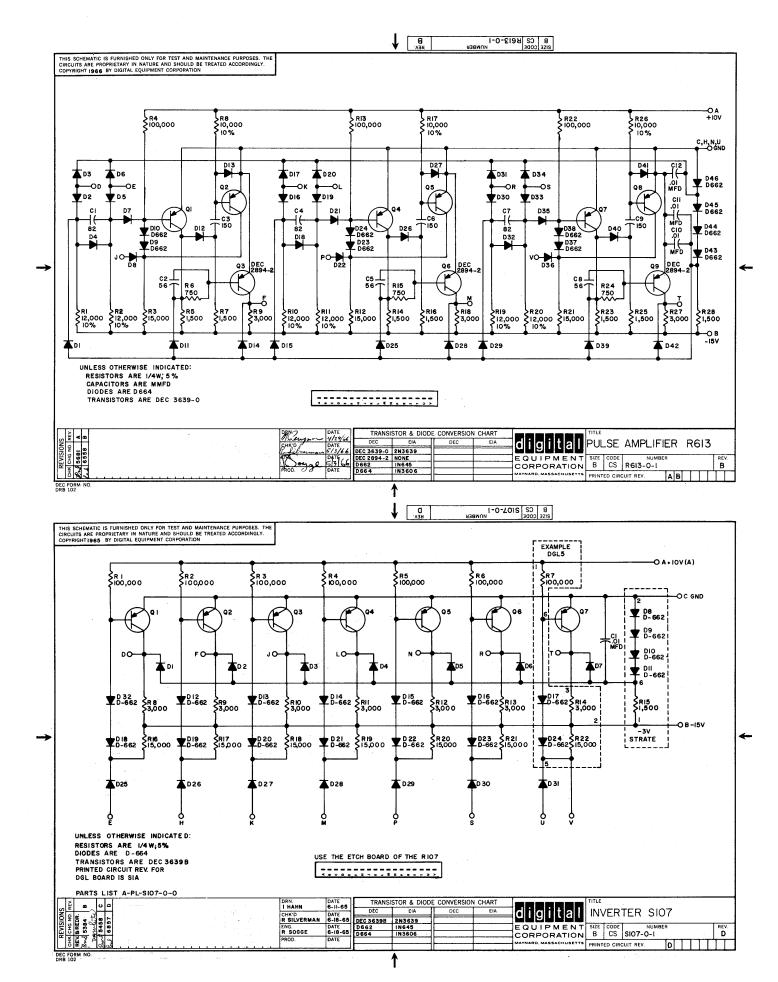

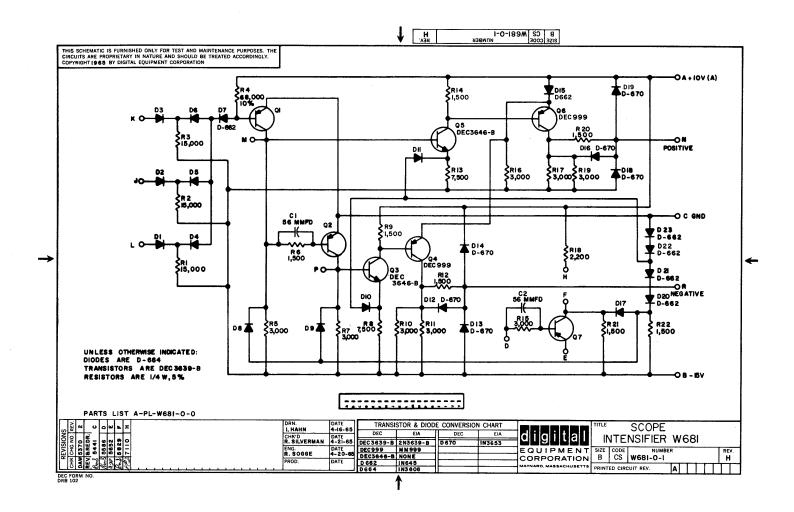

| R613          | Pulse Amplifier             | W681          | Oscilloscope Intensifier   |

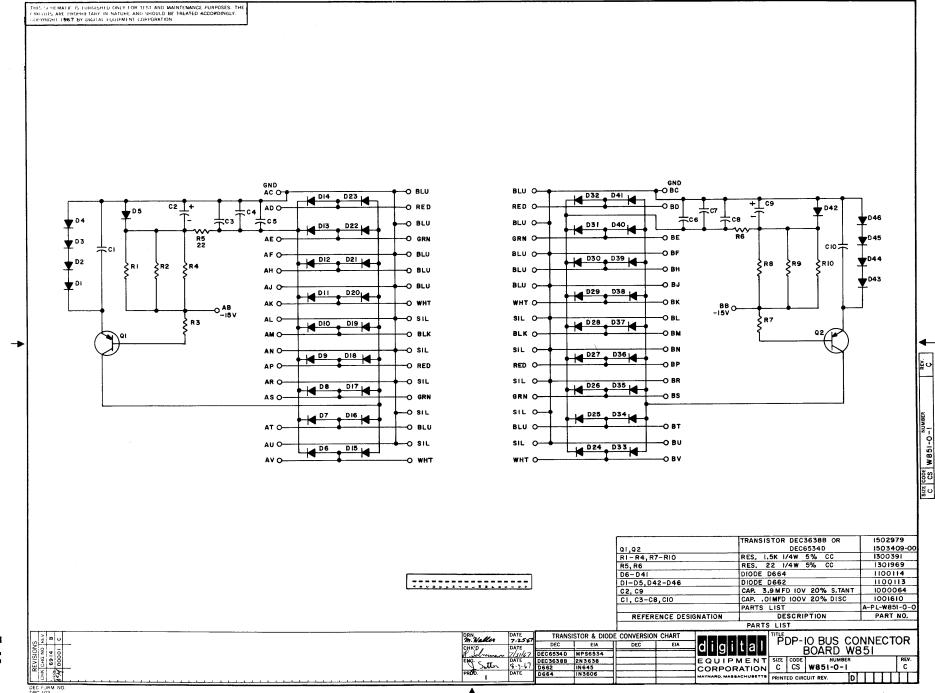

| S107          | Inverter                    | W851          | PDP-10 Bus Connector Board |

| S111          | Diode Gate                  | W990          | Blank Module/18 pins       |

## 1.4 MNEMONICS

Table 1-2 is a list of the mnemonics used in this manual.

Table 1-2 Mnemonics

| Mnemonic | Meaning                     | Mnemonic | Meaning                  |

|----------|-----------------------------|----------|--------------------------|

| BR       | Brightness                  | DEL      | De lay                   |

| CLR      | Clear                       | DPY      | Display                  |

| CONI     | Conditions in Instruction   | INT      | Intensity                |

| CONO     | Conditions Out Instruction  | IOB      | I/O Bus Interface        |

| DAC      | Digital-to-Analog Converter | IOBC     | Input/Output Bus Control |

| DATAI    | Data In Instruction         | LP       | Light Pen                |

| DATAO    | Data Out Instruction        | PI       | Priority Interrupt       |

| DC       | Display Control             | ST       | Status                   |

| DCDR     | Decoder                     |          |                          |

## 1.5 LEVELS AND PULSES

Table 1-3 is a listing of the levels and pulses utilized or developed in the VP10, including a brief description of the function of each.

Table 1–3 VP10 Levels and Pulses

| Level/Pulse              | Function                                                                                                                                                                            |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CROBAR                   | This level is generated in the 844 Power Control for 4 seconds during power up and down conditions, precluding data transfers or interrupt requests during the period of assertion. |  |  |  |

| DC ANALOG SETTLE<br>DOWN | The delayed level, generated by DC ST INT and applied to the inputs of the three display brightness delays in the DC logic.                                                         |  |  |  |

| DC BR LOW                | The delayed level generated by DC ANALOG SETTLE DOWN when ST BR00 (1) and ST BR 01 (1) are asserted. This level establishes the low brightness CRT display.                         |  |  |  |

| DC BR MED                | The delayed level generated by DC ANALOG SETTLE DOWN when ST BR 00 (0) and ST BR 01 (0) are asserted. This level established the medium brightness CRT display.                     |  |  |  |

| DC BR HI                 | The delayed level generated by DC ANALOG SETTLE DOWN when ST BR 00 (0) and ST BR 01 (1) are asserted. This level establishes the high brightness CRT display.                       |  |  |  |

| DC ST INT                | This pulse initiates the logic in the display control which will determine the CRT display intensity.                                                                               |  |  |  |

| IOB CONI                 | From the PDP-10 Central Processor, this level causes generation of IOBC CONI(A) and (B) in the VP10 if ~CROBAR and IOB DPY SEL are asserted.                                        |  |  |  |

| IOB CONO CLR             | From the PDP-10 Central Processor. When IOBC DPY SEL is asserted, this pulse generates IOBC DPY CONO CLR in the VP10.                                                               |  |  |  |

| IOB CONO SET             | From the PDP-10 Central Processor. When IOBC DPY SEL is asserted, this pulse causes generation of IOBC DPY CONO SET in the VP10.                                                    |  |  |  |

| IOB DATAI                | From the PDP-10 Central Processor. When ~CROBAR and IOB DPY SEL are asserted, this level causes generation of IOBC DPY DATAI (A), (B), and (C) in the VP10.                         |  |  |  |

| IOB DATAO CLR            | From the PDP-10 Central Processor. When IOBC DPY SEL is asserted, this pulse generates IOB DPY DATAO CLR X and Y in the VP10.                                                       |  |  |  |

## Table 1-3 (Cont) VP10 Levels and Pulses

| Level/Pulse            | Function                                                                                                                                                                 |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOB DPY DATAI (A)      | This level causes the contents of Y00-09 to be read into IOB 08-17 and IOB 08(B)-17(B).                                                                                  |

| IOB DPY DATAI (B)      | This level causes the contents of X00-09 to be read into IOB 26-35 and IOB 26(B)-35(B).                                                                                  |

| IOBC DATAO SET         | From the PDP-10 Central Processor. When IOBC DPY SEL DATAO X and Y is asserted, this pulse causes generation of IOBC DPY DATAO SET (X) and (Y) in the VP10.              |

| IOBC DPY CONI (A)      | This level causes the status of the Status Register flip-flops to be placed on IOB 20, 22-25 and 27, 28.                                                                 |

| IOBC DPY CONI (B)      | This level causes the status of the Status Register flip-flops to be placed on IOB 21, 26, and 30–35.                                                                    |

| IOBC DPY CONO CLR      | This pulse clears all VP10 Status Register flip-flops.                                                                                                                   |

| IOBC DPY CONO SET      | This pulse causes 1s from IOB 20–28 and 30–35 to be read into the Status Register flip–flops.                                                                            |

| IOBC DPY DATAO CLR X   | Clears X register, sets ST BUSY, and clears ST DONE flag.                                                                                                                |

| IOBC DPY DATAO CLR Y   | Clears Y register simultaneously with IOBC DPY DATAO CLR X; therefore ST BUSY is set and ST DONE cleared on the IOBC DPY DATAO CLR Y pulse (except in X or Y ONLY mode). |

| IOB DPY DATAO SET (X)  | This pulse causes the contents of IOB 26(B)-35(B) to be readinto X00-09 and causes generation of DC ST INT.                                                              |

| IOBC DPY DATAO SET (Y) | This pulse causes the contents of IOB 08(B)-17(B) to be read into Y00-09.                                                                                                |

| IOBC DPY SEL           | Developed as a result of decoding the VP10 Device Select Code (1348); also dependent on the ~CROBAR condition, this level must be present to set the VP10 in operation.  |

## 1.6 MAJOR LOGIC SECTIONS, SIMPLIFIED DESCRIPTION

The VP10 contains five major logic sections. Figure 1–2 is a simplified block diagram illustrating the relative logical position of each section. Detailed descriptions of the logic functions are contained in Chapter 4, Principles of Operation.

Figure 1-2 Simplified Block Diagram

## 1.6.1 I/O Bus Interface

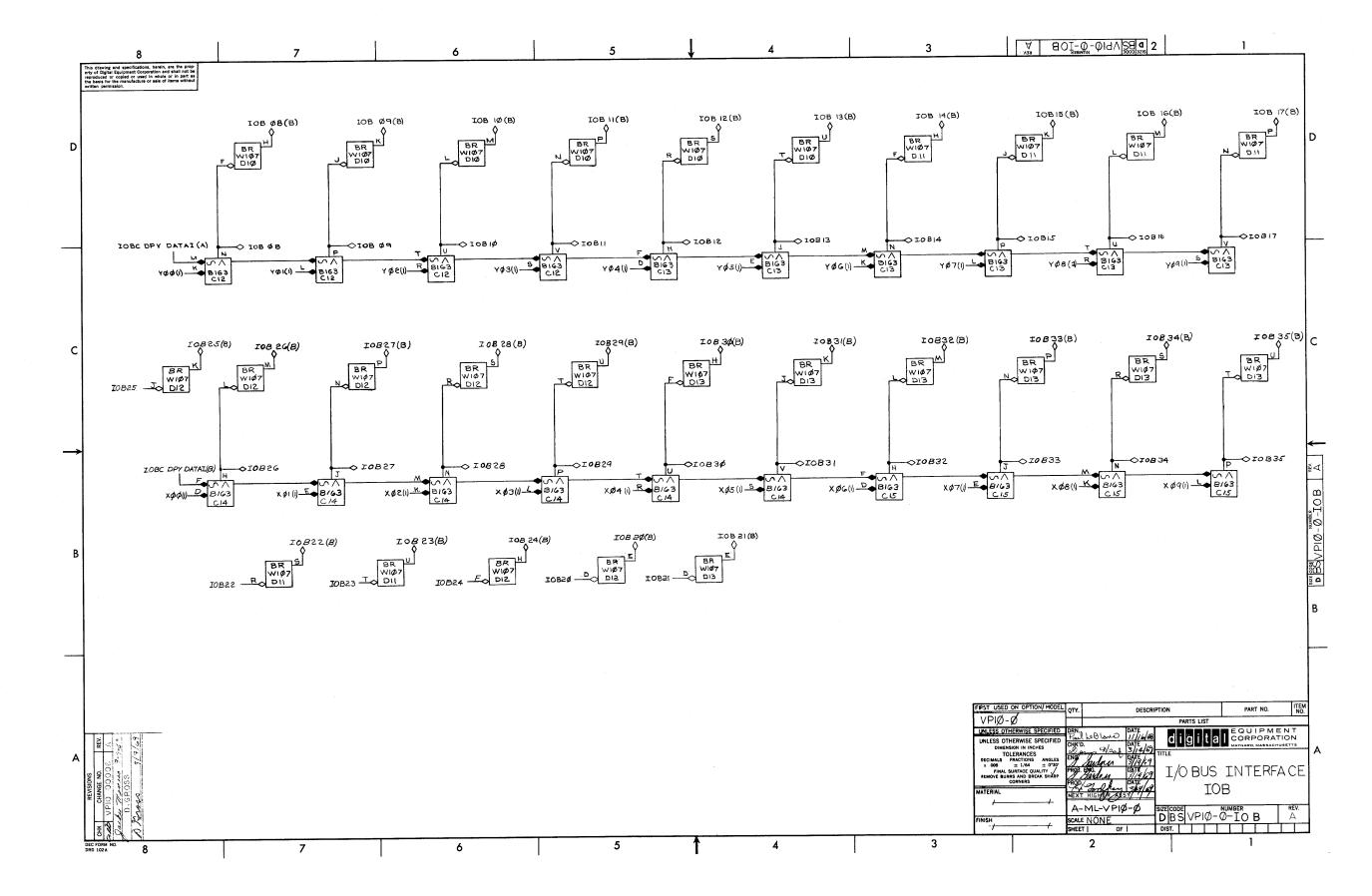

The I/O Bus (IOB) Interface contains circuitry for information transfers to and from the PDP-10 over the I/O Bus.

## 1.6.2 I/O Bus Control

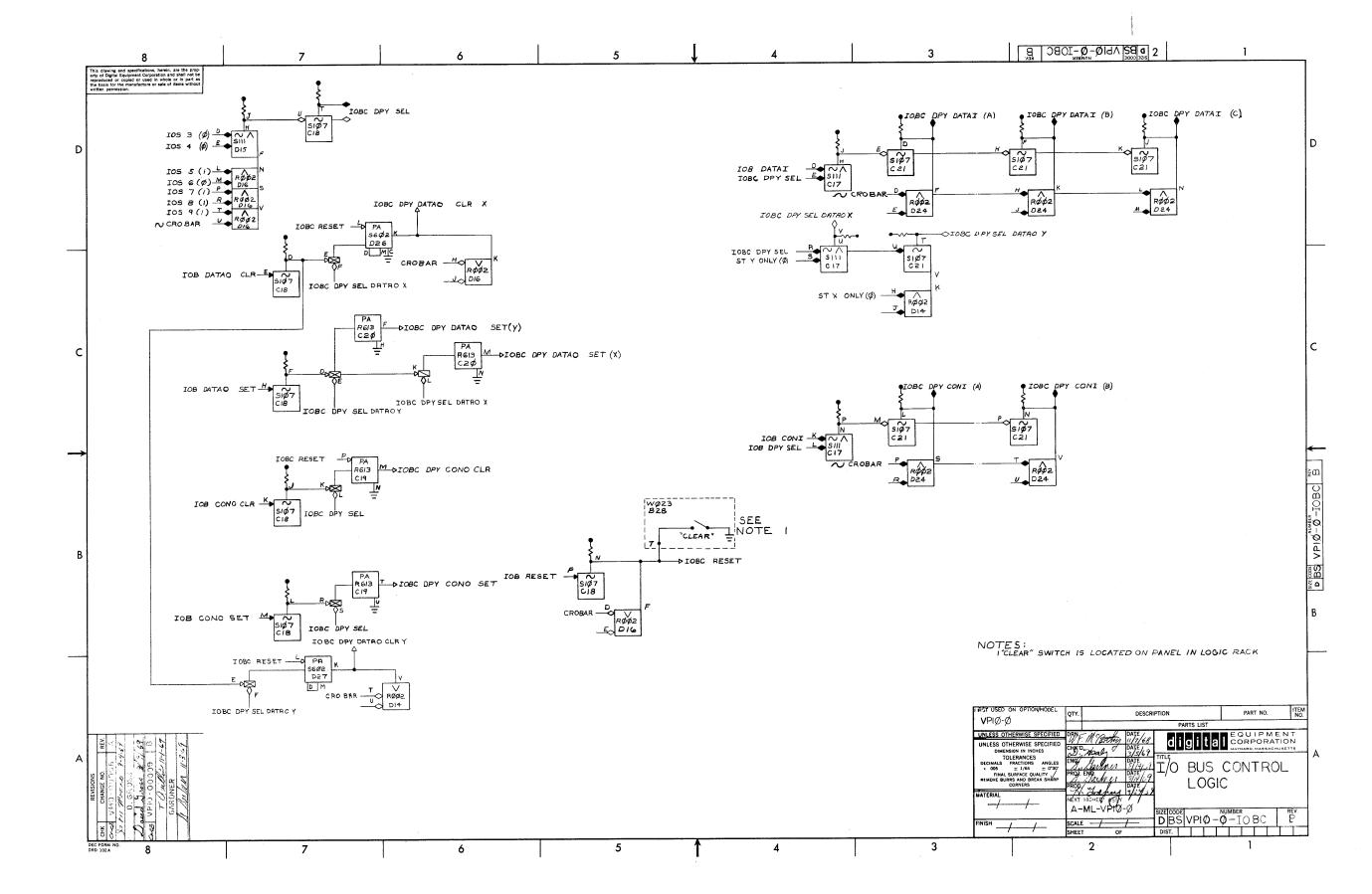

The I/O Bus Control contains the logic for decoding device commands, thereby providing the basic activating signal for display functions. The Display Control internal instruction pulses and levels are triggered by pulses generated in the PDP-10 Central Processor by the four basic instructions; CONI, DATAI, CONO, and DATAO.

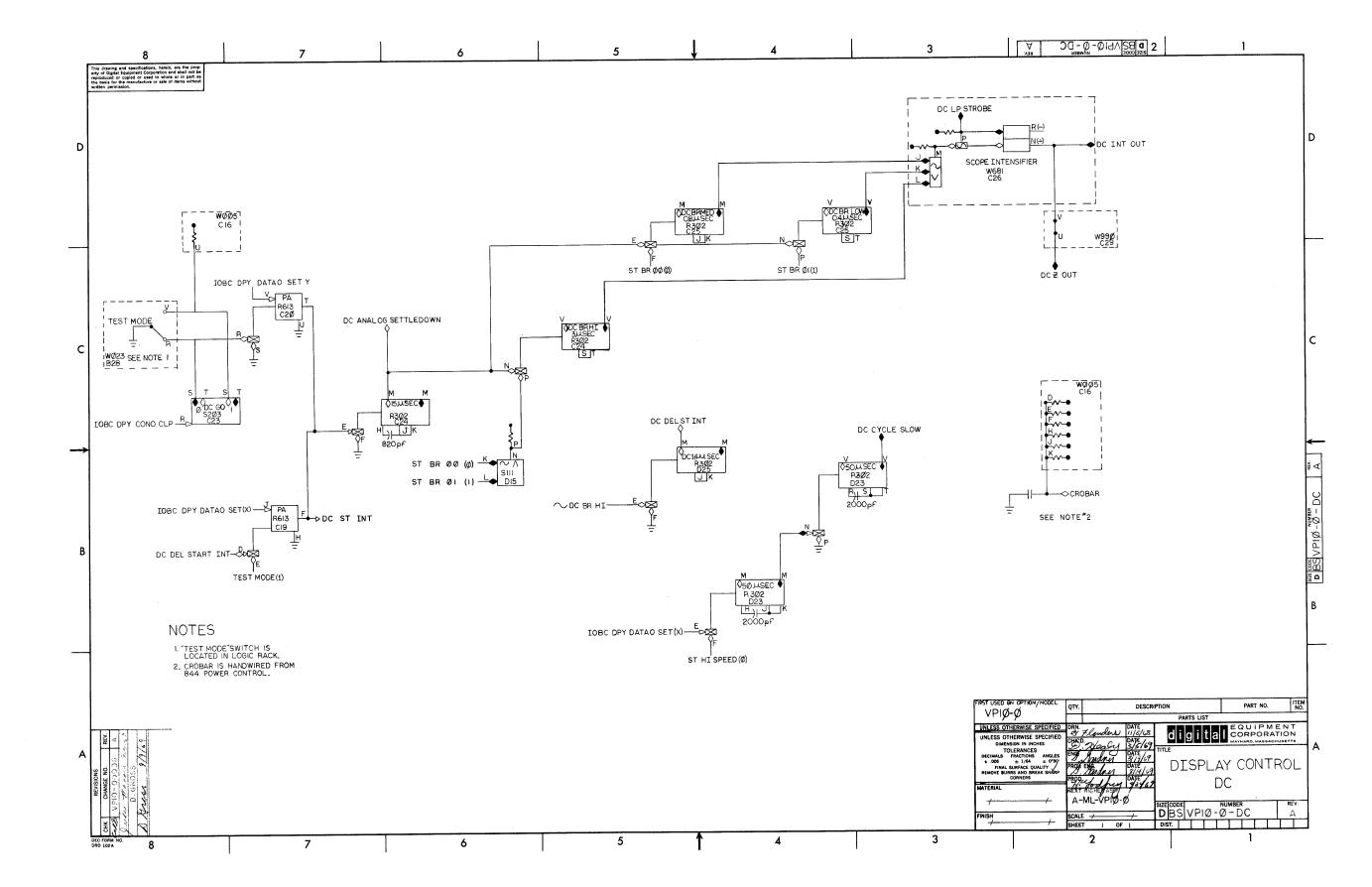

## 1.6.3 Display Control

The Display Control (DC) contains the circuitry which determines the brightness of the CRT display. Delayed pulses for initiating the Test Mode are also developed in this section of the logic.

## 1.6.4 XY Buffers and Digital-to-Analog Converters

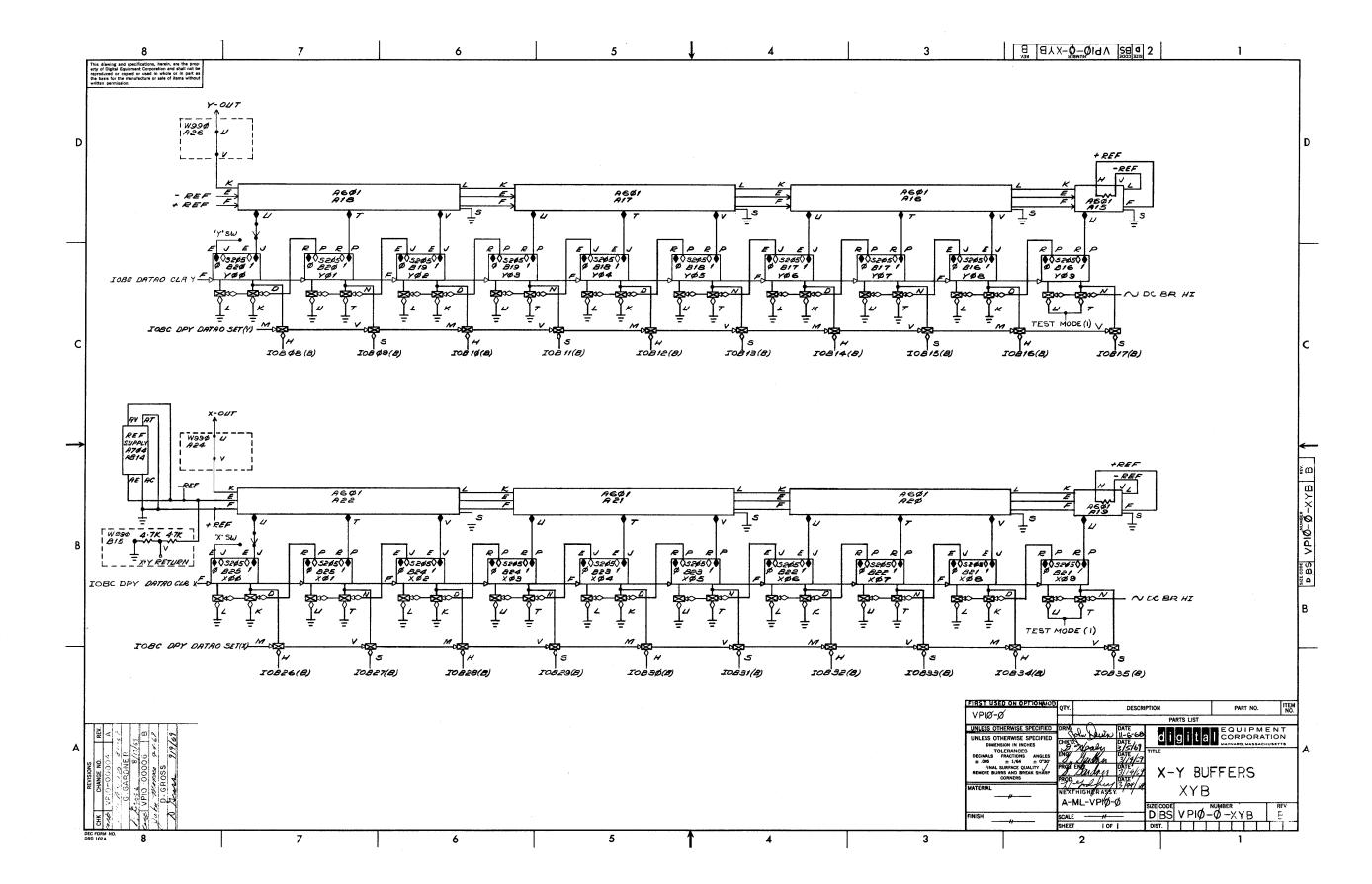

This section of the logic contains the X and Y registers where the data word is applied to the Digital-to-Analog conversion (DAC) circuitry. The DACs provide analog output levels to the CRT horizontal and vertical deflection inputs.

## 1.6.5 Status Control

This section contains the logic for: all flags; the registers for selecting the Priority Interrupt channels through binary-to-octal decoders; the register for the brightness control; and the buffers for reading the display conditions into the IOB Bus.

## 1.6.6 Reference Material

The following documents contain information pertinent to the operation and maintenance of PDP-10/VP10 system:

KA10 Maintenance Manual (two volumes)

PDP-10 System Reference Manual

Digital Logic Handbook, C-105

PDP-10 Interface Manual

PDP-10 Site Preparation Guide

Documents published by DEC are available from Digital Equipment Corporation, 146 Main Street, Maynard, Mass. 01754, or from the nearest DEC District Office. The technical documents applicable to the particular oscilloscope or CRT display in use should be obtained from the manufacturer.

## 2.1 SCOPE

This chapter contains the basic requirements for installation of the VP10 Display Control.

## 2.2 UNPACKING

The VP10 is crated for shipment and mounted on a skid. Remove all crating and strapping material, and all protective padding. Ensure that the equipment is not scratched or otherwise damaged during unpacking. The plenum door at the rear of the equipment has spring catches. To reinforce the door during shipment, two screws are used to hold the door shut. Remove these screws and store them in the plastic loops provided. Remove any packing material, shipping blocks, etc., from the interior of the equipment. The plug-in modules are taped-in during shipment; carefully remove the tape. Determine that all modules are properly seated and make a careful inspection of the cabinet interior. If relocation or reshipment of the equipment is anticipated, save the special packing materials for reuse.

## 2.3 SITE SELECTION

There are no special site requirements other than the floor space dimensions and service clearances shown in Figure 2-1. Both cabinet end-panels are removable. If possible, allow sufficient area for their removal to facilitate cleaning and maintenance. No sub-flooring is required. Casters on the bottom of the cabinets permit easy positioning and provide clearance for cable entry. The installation site should be as free as possible from excess dirt and dust; corrosive fumes and vapors; and strong magnetic fields.

The cabinet is equipped with cooling fans, therefore, no additional cooling is required in a normal installation.

| DIMENSIONS | Α    | В    | С     | D     | Е     | F     | G     | Н     | ı     | J     | к     |

|------------|------|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| INCHES     | 3.50 | 7.25 | 12.50 | 17.25 | 19.25 | 20.00 | 21.25 | 25.50 | 27.00 | 36.00 | 99.00 |

| METERS     | 0.08 | 0.18 | 0.32  | 0.44  | 0.49  | 0.51  | 0.54  | 0.65  | 0.68  | 0.91  | 2.51  |

10-0147

Figure 2-1 VP10 Area Requirements

## 2.4 INSTALLATION SPECIFICATIONS

Table 2-1 lists the general specifications of the VP10 which pertain to the installation of the equipment.

## 2.4.1 Interconnection

The maximum length for all interconnecting cables is 150 ft. Table 2-2 contains the information necessary for interconnecting the system. The cables supplied with the VP10 are terminated on both ends with the proper connectors. All cables enter through access cutouts in the bottom of the cabinet.

Table 2–1 General Specifications

| Voltage<br>(AC)                                                | Current<br>(Nominal) | Power<br>Dissipation | Ambient<br>Temperature                                             | Relative<br>Humidity | Dimensions                                                                         | Service<br>Clearance | Cable<br>Lengths<br>(Max.) |

|----------------------------------------------------------------|----------------------|----------------------|--------------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------|----------------------|----------------------------|

| 115V ± 10%<br>60 Hz ± 2 Hz<br>or<br>230V ± 10%<br>50 Hz ± 2 Hz | 2.0A<br>1.0A         | 230W                 | Operating:<br>16-32°C<br>61-90°F<br>Storage:<br>4-43°C<br>37-110°F | 20% to 80%           | 69-1/2 in. h<br>1753 mm h<br>21-1/4 in. w<br>540 mm w<br>27-1/16 in. d<br>687 mm d | 36 in<br>910 mm      | 150 ft<br>45 m             |

Table 2–2

Cable Interconnections

| VP10 Location                            | Oscilloscope<br>Location<br>(RM503)                                    | Cable Type                                                           | Function                               |

|------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------|

| 844 Power Control                        |                                                                        | #14 (3 Cond.)                                                        | Power                                  |

| 844 Power Control                        |                                                                        | #16 (3Cond.)                                                         | Remote Power<br>Control                |

| Power Distribution Strip                 |                                                                        | BC10B                                                                | Margin Voltage                         |

| CD01-CD08<br>(See Dwg. No. D-MU-VP10-02) |                                                                        | BC10A                                                                | I/O Bus                                |

| BNC Female Connectors on<br>Switch Panel | +Horizontal = X<br>+Vertical = Y<br>-Horizontal XY<br>-Vertical Return | RG-59/U, termin-<br>ated at both ends<br>with male BNC<br>connectors | X, Y and X+Y<br>Return Scope<br>inputs |

| BNC Female Connector on Switch Panel     | Z Input                                                                | RG-59/U<br>BNC → Banana Plug                                         | Z Scope Input                          |

| B28                                      |                                                                        | 7006212-0-0                                                          | Light Pen                              |

## 3.1 SCOPE

This chapter describes the VP10 controls and indicators and discusses the operation and programming of the VP10 Point Plot Display Control. VP10 operation on receipt of an I/O instruction and step by step operation of a sample program are described.

## 3.2 VP10 CONTROLS AND INDICATORS

## 3.2.1 Indicator Panel

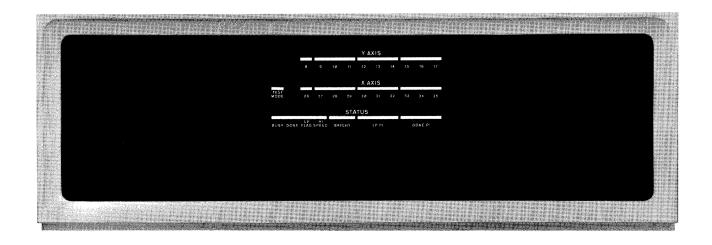

The indicator panel is shown in Figure 3-1. Lamps are provided to monitor the data and status registers, as shown in Table 3-1.

Table 3-1

Data/Status Register Monitoring

| Lamp                    | Flip-Flop               |

|-------------------------|-------------------------|

| Y AXIS                  | Y00 through 09          |

| X AXIS                  | X00 through 09          |

| TEST MODE               | ST TEST MODE            |

| BUSY                    | ST BUSY                 |

| DONE                    | ST DONE                 |

| LP FLAG                 | ST LP FLAG              |

| HI SPEED                | ST HI SPEED             |

| BRIGHTNESS              | ST BROO and 01          |

| LP PRIORITY INTERRUPT   | ST LP PIOO through O2   |

| DONE PRIORITY INTERRUPT | ST DONE PI00 through 02 |

Figure 3-1 Indicator Panel

## 3.2.2 Switch Panel

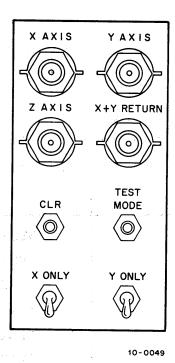

The Switch Panel is shown in Figure 3-2. Switches and connectors are described in Table 3-2.

Figure 3-2 Switch Panel

Table 3-2 Switches/Connectors

| Switch           | Function                                                                                                                                                                                                                                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR              | The CLR switch, when depressed, momentarily asserts IOBC RESET, which generates IOBC DPY DATAO CLR X and Y. IOBC DPY DATAO CLR X and Y clears the X and Y Registers; and resets the ST DONE flag. IOB RESET also generates IOBC DPY CONO CLP which clears the ST BUSY Flag.                                   |

| X ONLY           | When in the up position prohibits changes in the Y register.                                                                                                                                                                                                                                                  |

| Y ONLY           | When in the up position prohibits changes in the X register.                                                                                                                                                                                                                                                  |

| TEST MODE        | The TEST MODE switch, when depressed, collector sets DC GO, BR01, ST TEST MODE, and ST HI SPEED. Releasing the TEST MODE switch generates DC ST INT, which sets the DC ANALOG SETTLEDOWN delay. The recovery of DC ANALOG SETTLEDOWN triggers the DC BR HI delay which enters the display into the Test Mode. |

| CONNECTOR        |                                                                                                                                                                                                                                                                                                               |

| X AXIS           | BNC connector for the X level output to the CRT display.                                                                                                                                                                                                                                                      |

| Y AXIS<br>Z AXIS | BNC connector for the Y level output to the CRT display.  BNC connector for the Z level (intensity) output to the CRT display.                                                                                                                                                                                |

| X+Y RETURN       | BNC connector for the X and Y returns to the CRT display.                                                                                                                                                                                                                                                     |

## 3.2.3 Type 844 Power Control

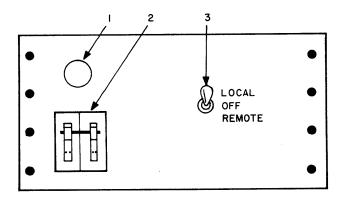

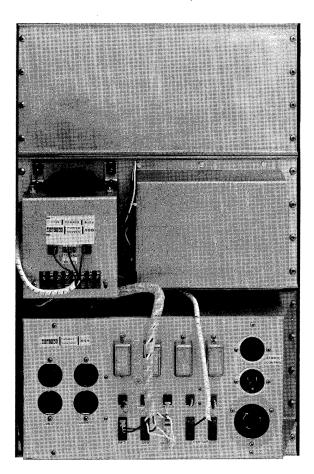

Remote turn-on and local power to the VP10 is controlled from the Type 844 Power Control Panel. The panel is illustrated in Figure 3-3. Table 3-3 lists the functions of the controls and indicators.

Figure 3-3 Power Control Panel

Table 3–3

Power Control Functions

| Number | Nomenclature         | Item              | Function                                            |

|--------|----------------------|-------------------|-----------------------------------------------------|

| 1      |                      | Indicator – White | Illuminated when line power is applied.             |

| 2      | 30 AMP               | Circuit Breaker   | Controls the line power to, and protects, the VP10. |

| 3      | REMOTE/OFF/<br>LOCAL | Toggle Switch     | Selects the Local, Off, or Remote Turn-On mode.     |

## 3.2.4 Margin Switches

Margin switches are provided for performance of margin checks in each section of the logic. As shown in Figure 1-1, the switches are located on the left, front side of the logic panels and are accessible when the cabinet front door is open.

## 3.3 I/O INFORMATION

Input/output instructions govern all transfers of data to and from the VP10 and also perform many operations within the processor. Section 2.12 of the PDP-10 System Reference Manual illustrates the I/O instruction format and contains descriptions of each instruction.

## 3.3.1 VP10 I/O Conditions

Bits 20 to 35 of the instruction word designate the following conditions when they contain a 1:

| Bit | CONO Display | Function                                                                                                                                       |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 20  | Hi Speed     | When 0, the DONE flag is set $100  \mu s$ after each DATAO operation. When 1, the DONE Flag is set approximately $20  \mu s$ after each DATAO. |

| 21  | TEST MODE    | Enables the VP10 to plot a diagonal line on the CRT screen. One point is plotted every $19.4~\mu s$ .                                          |

| 22  | BUSY Flag    | Display in operation                                                                                                                           |

| <u>Bit</u> | CONO Display | <u>Function</u>                                                                                                                     |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 23         | LP Flag      | The light pen has sensed light and caused an interrupt on the channel selected by bits 30–32.                                       |

| 24         | DONE Flag    | A set of coordinate points has been displayed on the oscilloscope. An interrupt is requested on the channel selected by bits 33-35. |

| 25         | YONLY        | Prevents X Register from changing.                                                                                                  |

| 26         | X ONLY       | Prevents Y Register from changing.                                                                                                  |

| 27,28      | Brightness   | Selects brightness level by allowing the time of the intensity output level to be selectable.                                       |

|            |              | 10 – No Intensity<br>11 – Low<br>00 – Medium<br>01 – High                                                                           |

| 29         | Not used     |                                                                                                                                     |

| 30-32      | LP PI        | Selects interrupt channel for LP Flag.                                                                                              |

| 33-35      | DONE PI      | Selects interrupt channel for DONE Flag.                                                                                            |

## 3.4 VP10 OPERATIONS

The VP10 contains a 7-bit device selection network and three flags; BUSY, DONE, and LP. The device selection code, 134<sub>8</sub>, contained in bits 3 through 9 of the instruction word, is decoded so that the VP10 responds only to signals sent to it by the processor over the in-out bus. For priority interrupt operation, the program must assign an interrupt channel. Channels are designated by bits 30 through 32 for Light Pen Priority Interrupt and bits 33 through 35 for Done Priority Interrupt.

The BUSY and DONE flags together denote the basic state of the VP10. When both are clear, the VP10 is idle. To place the display in operation, a CONO instruction conditions the logic which determines:

- a. selection of PI Channels

- b. brightness of the CRT plot

- c. mode (HI or ~HI SPEED)

The program must give a DATAO to send the first unit of data. This unit consists of 10X and 10Y bits. When this data has been converted to appropriate analog levels and a point has been displayed, BUSY is cleared and DONE is set to indicate that the VP10 is again ready to receive new data. The program

responds with a DATAO to send more data for conversion and display. If a point displayed is in the field of vision of the Light Pen, the VP10 sets the LP Flag. The setting of DONE or LP signals the program by requesting an interrupt.

Interrupt requests are handled through seven channels arranged in a priority chain within the Central Processor. The selection of channels is left entirely at the discretion of the programmer. To assign the Light Pen Interrupt or Done Interrupt to a channel, the program sends the number of the channel to the VP10 Control Register as part of the conditions by a CONO (bits 30 through 32 for LP PI and bits 33 through 35 for DONE PI). Channels are designated 1 through 7 with 1 having the highest priotity. A zero assignment disconnects the VP10 from the interrupt channels altogether. In this situation, the program must continue testing DONE to determine when the display is ready.

## 3.5 SAMPLE PROGRAM

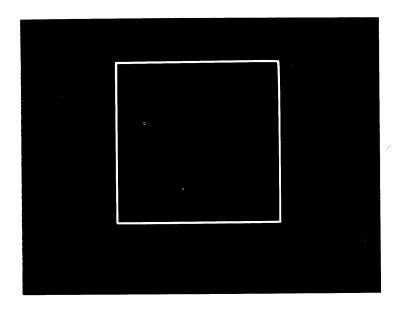

The following is a discussion of VP10 operations during a sample program (refer to Table 3-4) which results in the plotting of a square on the CRT screen, as shown in Figure 3-4. The program steps, designated 1 through 28, do not refer to memory locations.

The program first gives CONO 134, 104200 where 134<sub>8</sub> is the Device Code which selects the VP10. The value 104200<sub>8</sub> sets HI SPEED, DONE, and ST BR01, specifying the high brightness level (refer to Section 3.3.1). The second step (SETZ 1, 0) sets AC 1 = 0. Step 3 (MOVEI 2, 400) puts the size of the square (400), selected for convenience, into AC 2. Step 4, CONSO 134, 4000, tests the VP10 and will skip the next instruction if the DONE flag is up. CONSO can test only the right 18 bits and since the specified bit is 24, the program is testing for the DONE flag. The instruction in Step 5 (JRST. -1) will only be executed if the DONE flag is not up. The program will continue to test for DONE and jump back until the flag goes up and Step 5 will be skipped. Step 6 (DATAO 134, 1) loads the VP10 X and Y Registers with the contents of AC 1, which was set to 0 in Step 2. The VP10 will now plot one point corresponding to the X and Y coordinates 0, 0.

Step 7, MOVSS 1, swaps the left and right halves of the word in AC 1. This is actually an X and Y swap because the Y data was originally in the left half of the word and the X data in the right half. Steps 8 and 9 are identical to Steps 4 and 5 (the DONE flag is tested), in this case following the DATAO to determine if the VP10 is ready to accept more data. The program could specify a DONE Priority Interrupt Channel, thereby eliminating the requirement for the program to test for the DONE condition. Central Processor time would be more economically utilized, if a PI were designated.

Step 10 (DATAO 134, 1) causes the point 0, 0 to be plotted again, as the contents of the AC 1, although swapped, were not changed and remain all 0s.

Step 11 (SOJE 2, SQ) subtracts one from the contents of AC 2 (400) and jumps to SQ if the subtraction leaves AC 2 containing all 0s. When AC 2 goes to all 0s, the square is half plotted (the base and left side), and the program goes to SQ where the AC's are loaded in preparation for plotting the right half of the square.

In Step 12, MOVSS 1 swaps the two halves of the word in AC 1 as before. Step 13 (ADDI 1, 4) increments AC 1 by 4, thereby adding 4 to the value of the X half of the word in AC 1. Step 14 (JRST SQUARE) jumps the program back to Step 4 where the sequence is repeated. In step 6, the VP10 X and Y registers are loaded with X = 4 and Y = 0, and the point 4, 0 is plotted, followed by the plotting of 0, 4 after the swapping in Step 7. This sequence, Step 4 through Step 7, will continue until AC 2 goes to 0 and the program skips to SQ because of the SOJE 2, SQ instruction, Step 11. At this time,  $1000_{\rm Q}$  points have been plotted and the square is half complete.

In Step 15 (MOVEI 2, 400), the size of the square, 400, is loaded into AC 2 as before. Step 16 (MOVSI 1, 1777<sub>8</sub>) loads 1777<sub>8</sub> into the left half of AC 1. Steps 17, 18, and 19 ready the VP10 and test for the DONE flag.

In Step 20, the point 0,  $1777_8$ , is plotted. The MOVSS 1 instruction in Step 21 swaps  $1777_8$  into the X (right) half of the word in AC 1. Steps 22 and 23 test for the DONE flag. In Step 24 the point  $1777_8$ , 0, is plotted. The SOJE 2, instruction in Step 25 will cause a jump back to SQUARE when the contents of AC 2 go to zero (after  $400_8$  subtractions).

Step 26 (MOVSS 1) swaps the X and Y halves of the word in AC 1 resulting in 1777<sub>8</sub> being contained in the left (Y) half, and 0s in the right (X) half. Step 27 (ADDI 1, 4) adds 4 to the X half of the word. The program now jumps back to SQ + 3, and after testing for DONE, the point 4, 1777<sub>8</sub>, is plotted. The sequence continues until the final point 1777<sub>8</sub>, 1774<sub>8</sub> is plotted; at which time (Step 25) the program jumps back to SQUARE, and the plotting of another square begins.

Table 3-4 Sample Program

| Step | Instruction |                 | Description                                                                                                    |

|------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| 1    | SQUARE/     | CONO 134,104200 | Select VP10 and set DONE, HI SPEED, BR01                                                                       |

| 2    |             | SETZ 1.0        | Set AC1 = 0                                                                                                    |

| 3    |             | MOVEI 2,400     | Load size of square into AC 2                                                                                  |

| 4    | SQUARE+3/   | CONSO 134,4000  | Is VP10 DONE flag up? If so, skip next instruction.                                                            |

| 5    |             | JRST •-1        | No. Jump back 1                                                                                                |

| 6    |             | DATAO 134,1     | Yes, select VP10 and send X and Y                                                                              |

| 7    |             | MOVSS 1         | Swap X and Y                                                                                                   |

| 8    |             | CONSO 134,4000  | Is VP10 DONE flag up? If so, skip next instruction.                                                            |

| 9    |             | JRST •-1        | No. Jump back 1.                                                                                               |

| 10   |             | DATAO 134.1     | Yes, select VP10 and send X and Y.                                                                             |

| 11   |             | SOJE 2, SQ      | Subtract 1 from AC 2. Does AC 2 contain all 0s, indicating that the square is half plotted? If so, jump to SQ. |

| 12   |             | MOVSS 1         | No. Swap X and Y.                                                                                              |

| 13   |             | ADDI 1,4        | Add 4 to X in AC 1.                                                                                            |

| 14   |             | JRST SQUARE+3   | Jump back to SQUARE + 3.                                                                                       |

| 15   | SQ/         | MOVEI 2,400     | Load size of square into AC 2.                                                                                 |

| 16   |             | MOVSI 1,1777    | Load 1777 into AC 1 and swap into Y half.                                                                      |

| 17   |             | CONO 134,104200 | Select VP10 and set DONE, HI SPEED and BR01                                                                    |

| 18   | SQ+3/       | CONSO 134,4000  | Is VP10 DONE flag up? If so, skip next instruction.                                                            |

| 19   |             | JRST •-1        | No. Jump back 1.                                                                                               |

| 20   |             | DATAO 134,1     | Yes, select VP10 and send X and Y.                                                                             |

| 21   |             | MOVSS 1         | Swap X and Y.                                                                                                  |

| 22   |             | CONSO 134,4000  | Is VP10 DONE flag up? If so, skip next instruction.                                                            |

Table 3–4 (Cont) Sample Program

| Step | Instruction    | Description                                                                       |  |

|------|----------------|-----------------------------------------------------------------------------------|--|

| 23   | JRST •-1       | No. Jump back 1.                                                                  |  |

| 24   | DATAO 134,1    | Yes. Select VP10 and send X and Y.                                                |  |

| 25   | SOJE 2, SQUARE | Does AC 2 contain all 0s? If so, the square is completed and jump back to SQUARE. |  |

| 26   | MOVSS 1        | No. Swap X and Y.                                                                 |  |

| 27   | ADDI 1,4       | Add 4 to X in AC 1.                                                               |  |

| 28   | JRST SQ+3      | Jump back to SQ + 3.                                                              |  |

Figure 3-4 Sample Program Display

CHAPTER 4

PRINCIPLES OF OPERATION

## 4.1 SCOPE

This chapter presents a discussion of the logical events which take place in the VP10 on receipt of each basic I/O instruction. A discussion of the CROBAR, HI SPEED, TEST MODE, IOBC RESET, and LP STROBE option is also included.

Figure 4-1 is a Timing Diagram showing the various VP10 pulses and levels in the Test Mode. All Display Control functions are asynchronous.

Standard DEC logic (a high is represented by ground and a low by -3V) is used throughout the Display Control, except for the analog outputs to the CRT display, which may vary between between +10V and -15V for the Z input and between 0V and -10V for the X and Y inputs. The oscilloscope X+Y return is -5V.

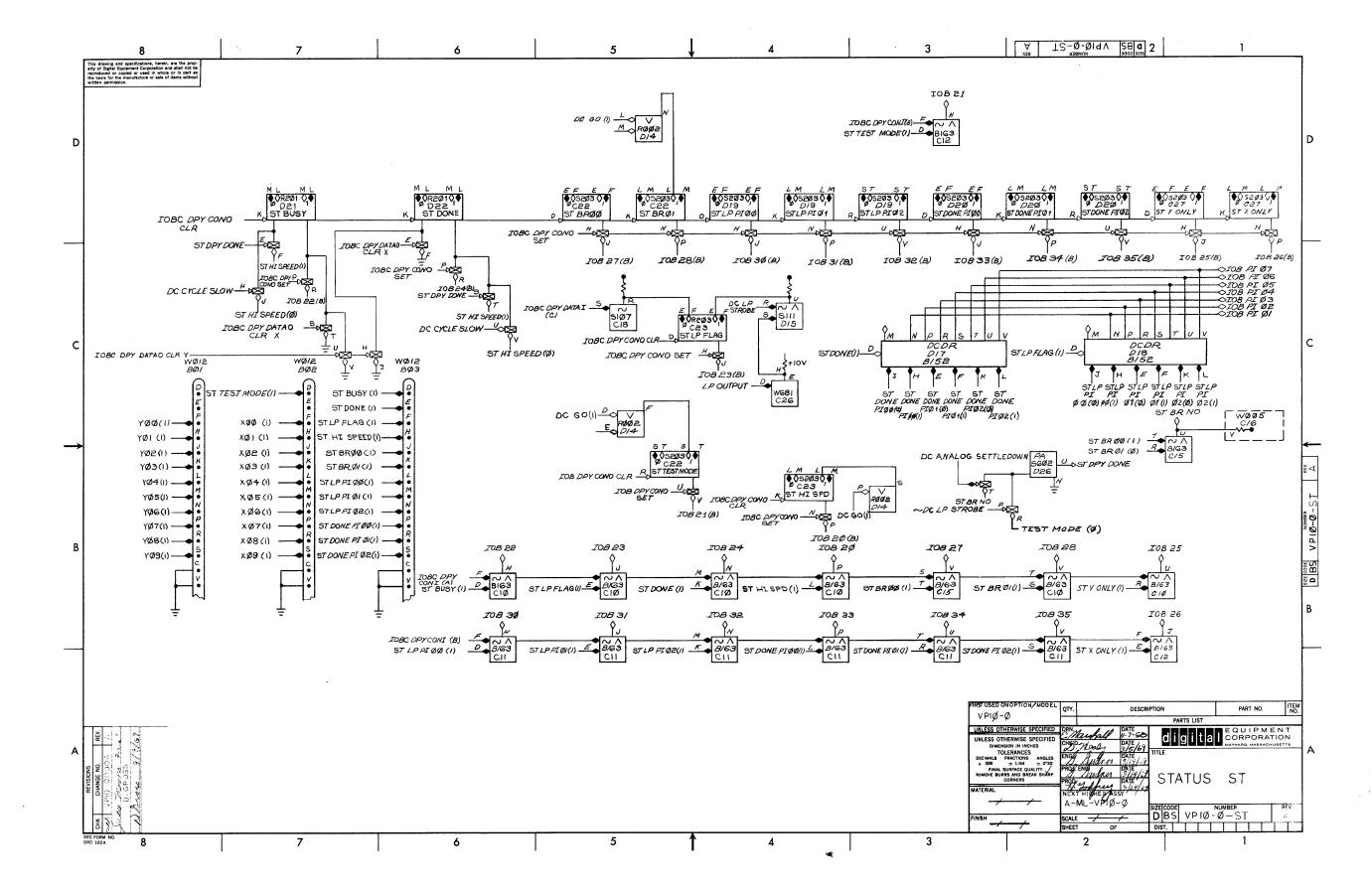

## 4.2 CONDITIONS OUT INSTRUCTION - CONO

IOS 03 through 09 of the I/O Bus are ANDed with ~CROBAR in the I/O Bus Control Logic. If selection bits 03 through 09 contain the VP10 device selection code (134<sub>8</sub>) and ~CROBAR is asserted, the gate is enabled and the IOBC DPY SEL level is produced. This is the basic activating level for all Display Control functions. The performance of all basic instructions are dependent upon the presence of this level. In the following discussions, it will be assumed that the VP10 has been selected by device code 134<sub>8</sub> and that, in all instances, IOBC DPY SEL has been asserted.

When IOB CONO CLR is asserted by the processor, IOBC DPY CONO CLR is produced in the I/O Bus Control Logic and clears the following flip-flops:

ST BUSY

ST DONE PI00-02

ST DONE

ST LP FLAG

ST BR00-01

ST LP PI00-02

ST HI SPEED

DC GO

Figure 4-1 TEST MODE Timing Diagram

The next pulse from the processor, IOB CONO SET, generates IOB DPY CONO SET in the I/O Bus Control Logic. This pulse will cause the contents of IOB bits 20 through 28 and 30 through 35 to be read into the condition flip-flops as follows:

| IOB Bit | Reads Into   |

|---------|--------------|

| 20      | HI SPEED     |

| 21      | ST TEST MODE |

| 22      | ST BUSY      |

| 23      | ST LP FLAG   |

| 24      | ST DONE      |

| 25      | ST Y ONLY    |

| 26      | ST X ONLY    |

| 27      | ST BROO      |

| 28      | ST BRO1      |

| 30      | ST LP PIOO   |

| 31      | ST LP PIO1   |

| 32      | ST LP PIO2   |

| 33      | ST DONE PIOO |

|         | ST DONE PIOT |

| 35      | ST DONE PIO2 |

The program conditions the VP10 during this operation. For example: if IOB bits 20 and 24 are 1s, HI SPEED and ST DONE are set to allow the VP10 to accept data and perform conversions in the HI SPEED mode during the ensuing DATAO instruction. The configuration of IOB bits 27 and 28 and 33 through 35 will determine the display brightness and priority interrupt channel, respectively.

## 4.3 DATA OUT INSTRUCTION - DATAO

IOB DATAO CLR from the processor produces IOBC DPY DATAO CLR X and Y in the I/O Bus Control Logic. These pulses clear the X and Y Registers, respectively, in preparation for the reading-in of a data word from the I/O Bus. IOBC DPY DATAO CLR X also sets ST BUSY, indicating that the VP10 is in operation, and clears ST DONE. The 0 state of ST DONE specifies that the VP10 cannot request another data word until it is again set to its 1 state.

Upon assertion of IOB DATAO SET by the processor, two pulses; IOBC DPY DATAO SET (Y) and (X) are produced by the I/O Bus Control Logic. IOBC DPY DATAO SET (Y) causes the contents of IOBO8(B) through 17(B) to be read into Y00 through 09 in the XY Buffers. In the same manner,

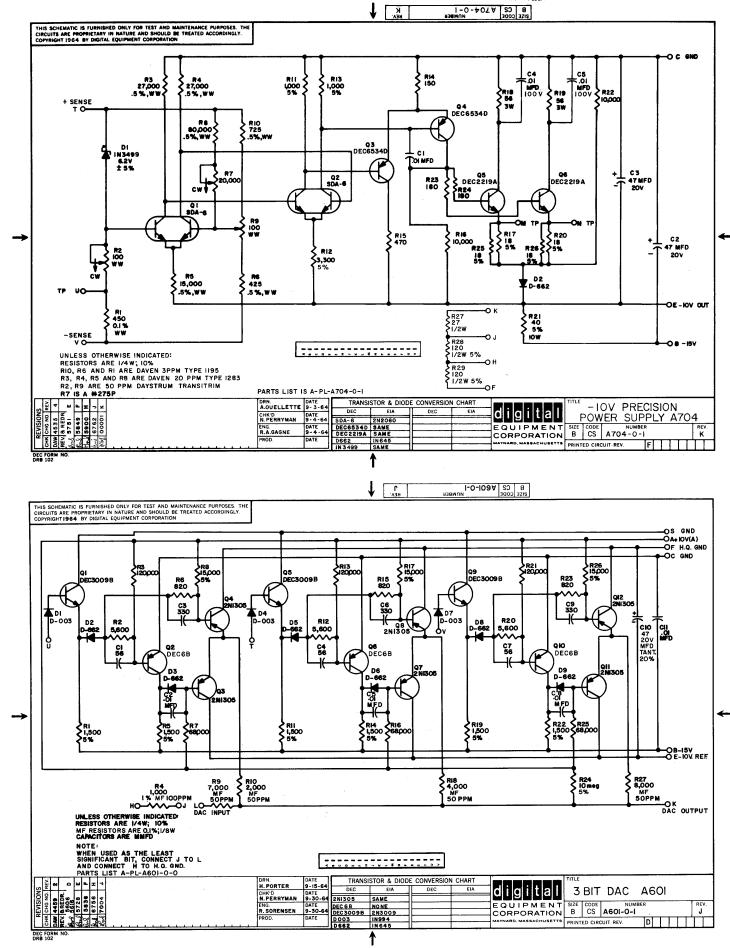

X00 through 09 are loaded from IOB26(B) through 35(B) by the assertion of IOBC DPY DATAO SET (X). The information now contained in the X and Y buffers is in the form of 10-bit non-negative integer binary words which correspond to an X and a Y coordinate. The binary output from each buffer is connected to the binary input of a 10-bit, high-resolution digital-to-analog converter (DAC) composed of DEC Type A601 Modules. Reference potential (-10V) is provided to the DACs by a DEC Type A704 Reference Voltage Supply. Each analog output may vary between 0V and -10V, where the 0V output corresponds to the maximum value binary input to the DAC and the -10V analog output corresponds to the minimum value binary input. The X and Y outputs, which are applied to the horizontal and vertical inputs of the CRT display, are the analog equivalents of the digital inputs to the DACs, and together, determine the relative location of the single spot plotted on the oscilloscope screen.

Bits 27 and 28 of the CONO instruction determine the brightness of this spot by conditioning ST BR00 and ST BR01 in the status logic. IOBC DPY DATAO SET (X), which causes the loading of the X Register, also produces DC ST INT in the Display Control Logic. This pulse, delayed, (DC ANALOG SETTLEDOWN) is the trigger for the DCD gates which enable the three brightness determining delays. The delay associated with DC ANALOG SETTLEDOWN allows the DAC outputs to stabilize, thereby preventing the displayed point from smearing. The outputs of the three brightness delays, DC BR LOW, DC BR MED and DC BR HI, are applied to input pins K, J, and L, respectively of the W681 Scope Intensifier where the duration of assertion of these negative levels determines the duration of the output of the Intensifier. The Intensifier output (+10V or -15V depending on the OR of the inputs) is taken from pin N and applied to the cathode circuit of the CRT via the Z axis input, where longer duration pulses cause brighter displays. Depending on the status of ST BR00 and ST BR01, one of the following four display intensity levels may be obtained:

| ST BROO | ST BRO1 | Level         |

|---------|---------|---------------|

| 1       | 0       | No Brightness |

| 1       | 1       | Low           |

| 0       | 0       | Medium        |

| 0       | 1.      | High          |

The delay associated with DC BR LOW is the shortest of the three and corresponds to the low brightness level. DC BR MED is asserted negatively for a longer period than DC BR LOW but for a shorter time

than DC BR HI. When both ST BR00 and ST BR01 are set, all three levels are asserted; however, only DC BR HI is considered because its delay exceeds the delay of DC BR LOW and DC BR MED and all are triggered simultaneously by DC ANALOG SETTLEDOWN.

## 4.4 CONDITIONS IN INSTRUCTION CONI

The assertion of IOB CONI by the processor produces IOBC DPY CONI (A) and (B) in the I/O Bus Control Logic. IOBC DPY CONI (A) causes the states of the following flip-flops to be tested and read onto the indicated IOB lines:

| Flip-Flop    | IOB Bit |

|--------------|---------|

|              |         |

| ST HI SPEED  | 20      |

| ST TEST MODE | 21      |

| ST BUSY      | 22      |

| ST LP FLAG   | 23      |

| ST DONE      | 24      |

| ST BROO      | 27      |

| ST BR01      | 28      |

Similarly, IOBC DPY CONI (B) tests the status of the following flip-flops, reading their states onto the indicated IOB lines:

| Flip-Flop    | IOB Bit |

|--------------|---------|

| ST LP PIOO   | 30      |

| ST LP PIO1   | 31      |

| ST LP PIO2   | 32      |

| ST DONE PI00 | 33      |

| ST DONE PIOT | 34      |

| ST DONE PIO2 | 35      |

## 4.5 DATA IN INSTRUCTION - DATAI

The assertion of IOB DATAI by the processor produces IOBC DPY DATAI (A) and (B) in the I/O Bus Control Logic. IOBC DPY DATAI(A) causes the contents of Y00 through 09 to be read into IOB08 through 17, while IOBC DPY DATAI(B) causes the contents of X00 through 09 to be read into IOB26 through 35.

These operations result in the contents of the X and Y registers being read into IOB bits 08 through 17 and 26 through 35 and stored in the computer memory in the location specified by the program.

## 4.6 OTHER LOGIC

To preserve the continuity of the previous logic discussion, the logic contained in this section was intentionally omitted. In some instances, the sequence of operations, as previously discussed, were qualified by conditions described in the following.

#### 4.6.1 CROBAR

The CROBAR level is positively asserted for four seconds after power comes up and for four seconds prior to power down. One condition necessary for the generation of IOBC DPY SEL is ~CROBAR; therefore, the VP10 cannot be placed in operation during the period of CROBAR assertion. CROBAR also generates IOBC DPY DATAO CLR X & Y and IOBC DPY CONO CLR in the I/O Bus Control Logic which clears the X and Y registers and all STATUS flip-flops respectively.

## 4.6.2 HI SPEED

In the following discussion all timing is referenced to the RM503 oscilloscope display. Normal settings of the oscilloscope X and Y input sensitivities are 2V/cm. The VP10 has provisions for operating at two speeds designated HI SPEED and ~HI SPEED.IOB bit 20 in a CONO determines the mode. In the HI SPEED mode, the DONE flag is set 19.4 µs following a DATAO (when the high brightness level has been selected), while in the ~HI SPEED mode, DONE is set 100 µs following the DATAO. Assuming that the Central Processor is granting Priority Interrupt requests when they are made, it is therefore possible to plot over 50,000 points per second in HI SPEED and 10,000 points per second in ~HI SPEED.

HI SPEED is set through a DCD gate qualified by IOB 20 (B) (1) and triggered by IOBC DPY CONO SET. The ST DONE Flag is set through a DCD gate qualified by HI SPEED and triggered by ST DPY DONE. The assertion of ST DPY DONE is dependent upon the enabling of a DCD gate qualified by TEST MODE (0)

and triggered by ~DP LP STROBE. The DONE flag is set by the positive going transition of DC LP STROBE 18 µs after the DATAO. The 19.4 µs delay is derived from DC ANALOG SETTLEDOWN (15 µs) and DC BR HI (2 µs) in the Display Control logic.

In the ~HI SPEED mode, HI SPEED is not set due to the IOB 20 (B) (0) condition. The ST DONE flag is set through a DCD gate qualified by ST HI SPEED (0) and triggered by the trailing edge of DC CYCLE SLOW. DC CYCLE SLOW is the combined (100 µs) delay of two 50 µs delays conditioned by ST HI SPEED (0) and triggered by IOBC DPY DATAO SET(X). This sequence results in setting the ST DONE flag 100 µs after each DATAO.

## 4.6.3 TEST MODE

The Test Mode may be entered by: program instruction CONO 134<sub>8</sub> with IOB21(1), or by pushing the TEST MODE switch on the VP10. DC GO is collector-set by depressing the TEST MODE switch. The trailing edge of the DC GO (1) transition causes generation of DC ST INT, initiating the sequence of events described in Section 4.3. Release of the TEST MODE switch, or assertion of IOBC DPY CONO CLR, resets the DC GO flip-flop.

A DCD gate, qualified by ST TEST MODE (1) and triggered by DC DEL START INT, generates DC ST INT and activates the display brightness circuitry. The DC GO (1) level collector-sets ST BR01 to provide the high brightness level, if the TEST MODE switch has been depressed. If under program control, the display brightness is determined by IOB bits 27 and 28 as before.

TEST MODE (1) with DC BR HI asserted, sets Y09 and X09 and causes the sequential setting of X08 through 00 and Y08 through 00, resulting in a diagonal line display on the oscilloscope. Both the X and Y registers are connected as ripple delay counters. The positive-going transition of ~DC BR HI sets X09 and Y09 through DCD gates as shown on the X-Y Buffer Drawing. The next assertion of ~DC BR HI clears X09 and Y09. Connections between the flip-flops are such that when X09 and Y09 change state from 1 to 0, X08 and Y08 are set. Similarly, X07 and Y07 are set and cleared by the positive transitions of X08 and Y08 as they change state from 1 to 0. The operation of the remainder of the counter is identical. X09 and Y09 change states on every assertion of ~DC BR HI; X08 and Y08 on every second assertion; X07 and Y07 on every fourth assertion; etc.

DC DEL ST INT provides a delay between the display of successive points to allow sufficient time for the carries to cease and for the DACS to settle in the new state.

## 4.6.4 IOBC RESET

IOBC RESET is generated by depressing the CLR switch, by IOB RESET from the processor, or by CROBAR. The assertion of IOBC RESET produces IOBC DPY DATAO CLR X & Y in the I/O Bus Control Logic and causes the X and Y registers to be cleared. IOBC RESET also generates IOBC DPY CONO CLR which clears all status flip-flops.

## 4.6.5 LP STROBE

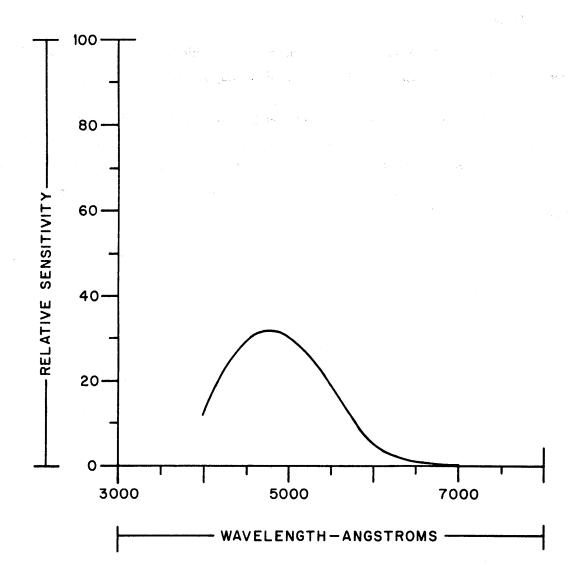

An LP OUTPUT level from the light pen amplifier ANDed with DC LP STROBE collector sets ST LP FLAG. DC LP STROBE causes the light pen to be inactive except while a point is being intensified. ST LP FLAG (1) selects a priority interrupt channel through a binary-to-octal decoder in the status logic. The specific channel (01 through 07) selected depends upon the condition of ST LP PI00 through 02. The decoder output is applied to IOB PI01 through 07.

## 5.1 SCOPE

This Chapter contains maintenance information for the VP10 Point Plot Display Control. Maintenance procedures relevant to the particular oscilloscope or display in use and other system equipment are contained in the equipment maintenance manual. The following test equipment is required for performance of preventive and corrective maintenance procedures in the VP10:

- a. A multimeter with a 20,000 ohms/Vdc Sensitivity.

- b. An oscilloscope with properly calibrated sweep and deflection circuits.

## 5.2 PREVENTIVE MAINTENANCE

Preventive maintenance consists of tasks performed prior to initial operation of the VP10 and periodically thereafter to ensure that the equipment is operating at optimum efficiency and to detect conditions which might lead to subsequent failure of the equipment. Preventive maintenance schedules are primarily based on average usage of the VP10 and down-time limitations.

## 5.2.1 Mechanical Inspection and Cleaning

Mechanical inspection and cleaning consists of periodically cleaning the interior and exterior of the equipment, checking for signs of deterioration, and cleaning the air filters. The exterior of the equipment should be wiped occasionally with a soft cloth to maintain an attractive appearance. The equipment interior should be vacuumed on a regular schedule depending upon environmental conditions. The mechanical inspection of the equipment can be easily conducted while the cleaning tasks are being accomplished. The blower air filters should be checked as often as required to maintain efficient operation of the cooling system. Remove the mesh filters from the blower assemblies. Shake and vacuum thoroughly before reinstalling. If the filters are excessively dirty or clogged, they should be washed in a detergent solution, dried, and sprayed with Filtercoat  $^{\textcircled{R}}$ , before reinstallation.

## 5.2.2 Electrical Inspection

Electrical inspection consists of making measurements of power supply voltages, observing ripple contents to ensure that operation is within the limits specified for the supply in use, and conducting margin checks to aggravate border line conditions within the logic, thereby revealing definite observable faults.

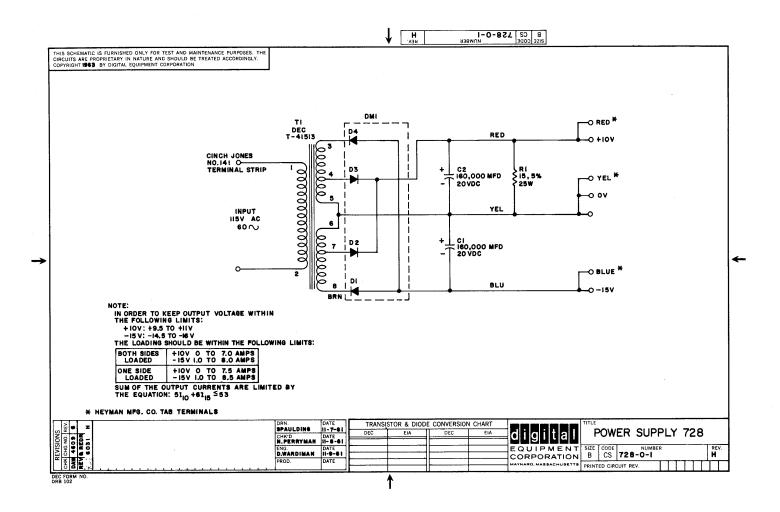

5.2.2.1 DEC Type 728 Power Supply Test Procedures – The +10V and -15V potentials required for operation of the VP10 logic are provided by a single Type 728 Power Supply, mounted on the rear plenum door as shown in Figure 5-1. Both voltages should be read from the terminals at the logic panel end and are not adjustable; therefore, if the voltage and ripple contents are not within the specified limits, the power supply must be either repaired or replaced.

Check the +10V output between the red (+) and black (-) leads. This reading should be between 9.5V and 11V, with less than 700 mV rms ripple. Check the -15V output between the blue (-) and black (+) leads. This reading should be between -14.5V and -16V, with less than 700 mV rms ripple.

Figure 5-1 Plenum Door Layout

5.2.2.2 DEC Type A704 Reference Supply – The DEC Type A704 Reference Supply provides the -10V reference potential to the digital-to-analog converters. This is a double-height module installed in location AB14 of the logic. The output, measured between pins T (-10V) and C (ground) of location A14, should be within  $\pm$  0.1 mV of -10V (from no load to full load) with a ripple content of less than 0.1 mV rms.

5.2.2.3 Margin Checks - VP10 margin checks are accomplished while running the Diagnostic Program, MAINDEC-10-D6Bn\* T0, T1, T2, and Test Mode. The toggle switches located on the left front of the logic panels provide selection of VP10 internal power or power supplied through the margin panel. The checks are performed by manually varying the +10V and -15V logic potentials at the Central Processor Margin Control Panel and observing the effects on VP10 operation. Thus, marginal conditions can be corrected prior to an actual failure. These checks are also useful in locating a faulty component causing intermittent failures. Each rack should be tested separately to allow for more precise fault isolation.

The VP10 margin ranges are:

## 5.3 CORRECTIVE MAINTENANCE

The VP10 is constructed of highly reliable transistorized modules and standard circuits. The reliability of the equipment, combined with proper performance of the preventive maintenance tasks, ensures minimum down-time due to failure. If a malfunction occurs, analyze the fault and correct the condition as outlined in the following paragraphs. Schematic Diagrams of all modules used in the VP10 logic are contained in Chapter 7 of this Manual.

## 5.3.1 Preliminary Investigation

The primary purpose of the preliminary investigation is to simplify and, if possible, isolate the fault. If the fault occurred while in a user program, determine from the user what is expected of the program and the particular error. Two valuable maintenance aids, the diagnostic program and the VP10 Test Mode, are described in the following paragraphs.

<sup>\*</sup>Use latest available program version

## 5.3.2 Diagnostic Program

The diagnostic program which is applicable to VP10 troubleshooting is MAINDEC-10-D6Bn. This program is arranged in three sections designated T0, T1, and T2. In Section T0, all flags are tested. Section T1 allows one of four patterns to be displayed in a dynamic test. Section T2 tests the light pen. A complete description is contained in the write-up which accompanies the program.

If the fault cannot be isolated using the diagnostic program, run the user program that failed, simplifying it with the user's help, if possible.

#### 5.3.3 Test Mode

The Test Mode is initiated by first depressing the CLR and then the TEST MODE switch on the VP10 Switch and Connector Panel. When in the Test Mode, self-contained logic places the VP10 in a loop independent of Central Processor control. The Test Mode display is a high intensity diagonal line as shown in Figure 5–2. Most of the logic contained in the VP10 is used during Test Mode operation. The following logic sections are exercised:

- a. ST BR 01

- b. X and Y Buffers

- c. All DACs

- d. HI SPEED

- e. All the Display Intensity Control logic

Figure 5-2 Test Mode Display

## 5.3.4 Signal Tracing

When a malfunction has been detected and the VP10 is in a loop, either in the Diagnostic Program or while in the Test Mode, use an oscilloscope to trace signal flow through suspected elements. In this manner, the quality of pulse amplitude, duration, rise time, and timing may be observed. If the malfunction occurs intermittently, combine signal tracing with a margin check or other form of aggravation test.

## 5.3.5 Validation Test

After replacement of any electrical component, perform a test to ensure that the malfunction has been corrected and to determine if adjustments are necessary. This test normally consists of the corrective maintenance tasks (i.e., Diagnostic Program and Test Mode, as well as margin checks), or if the problem was not exhibited by these procedures, the user program in which the failure was originally detected. When time permits, it is suggested that the entire preventive maintenance procedure be performed as a validation test.

# 5.3.6 Log Entry

Corrective maintenance procedures are not completed until the action taken has been recorded in the maintenance log. Record all data concerning the symptoms of the malfunction, method of isolation, and any other pertinent information.

# 6.1 SCOPE

This chapter contains a listing of the VP10 logic modules, power supplies and semiconductors. The indicated spare stock quantities are based on percentages of the total quantity of each component installed in the VP10. The actual quantity of spare parts to be stocked depends on down-time tolerance and system reliability requirements.

## 6.2 MODULES

Table 6-1 is a listing of VP10 modules with the total of each type installed and suggested spare quantities.

Table 6-1 VP10 Module Requirements

| DEC Type Number | Quantity in Use | Suggested Spares |

|-----------------|-----------------|------------------|

| A601            | 8               | 1                |

| A704            | 1               | 1                |

| B152            | 2               | 1                |

| B163            | 6               | 1                |

| R002            | 3               | 1                |

| R201            | 2               | 1                |

| R302            | 5               | 1                |

| R613            | 2               | 1                |

| \$107           | 1               | 1                |

| \$111           | 1               | 1                |

| S203            | 2               | 1                |

Table 6-1 (Cont)

VP10 Module Requirements

| DEC Type Number | Quantity in Use | Suggested Spares |

|-----------------|-----------------|------------------|

| S205            | 10              | 1                |

| W005            | 1               | 1                |

| W012            | 3               | 1                |

| W023            | 1               | 1                |

| W107            | 4               | 1                |

| W250            | 3               | 1                |

| W681            | 1               | 1                |

| W851            | 6               | 1                |

| W990            | 4               | ī                |

# 6.2.1 Semiconductors

Table 6-2 is a listing of VP10 semiconductor types with the total number installed and suggested spare quantities.

Table 6-2 VP10 Semiconductor Requirements

| DEC Designation | EIA Designation | Number<br>in Use | Suggested<br>Spares |  |  |  |  |  |

|-----------------|-----------------|------------------|---------------------|--|--|--|--|--|

| 1N3499          | 1N3499          | 1                | 1                   |  |  |  |  |  |

| 2N1305          | 2N1305          | 48               | 5                   |  |  |  |  |  |

| 2N3605          | 2N3605          | 10               | . 1                 |  |  |  |  |  |

| 2N4258          | 2N4258          | 18               | 2                   |  |  |  |  |  |

| D662            | 1N645           | 700              | 10                  |  |  |  |  |  |

| D664            | 1N3606          | 1792             | 20                  |  |  |  |  |  |

| D670            | 1N3653          | 5                | 1                   |  |  |  |  |  |

| DEC2894-2       | None            | 6                | 1                   |  |  |  |  |  |

| DEC2894-3       | None            | 26               | 3                   |  |  |  |  |  |

| DEC2219A        | None            | 2                | 1                   |  |  |  |  |  |

Table 6-2 (Cont)

VP10 Semiconductor Requirements

| DEC Designation | EIA Designation | Number<br>in Use | Suggested<br>Spares |

|-----------------|-----------------|------------------|---------------------|

| DEC3009         | 2N3009          | 26               | 3                   |

| DEC3638B        | 2N3638          | 12               | 1                   |

| DEC3639         | 2N3639          | 42               | 4                   |

| DEC3639B        | 2N3639          | 98               | 10                  |

| DEC3639C        | 2N3639          | 65               | 7                   |

| DEC3639-0       | 2N3639          | 12               | ī                   |

| DEC6534         | None            | 10               | 1                   |

| DEC6534B        | MPS6534         | 40               | 4                   |

| SDA-6           | 2N2060          | 2                | 1                   |

# 6.2.2 Power Supplies

| DEC Type Number     | Number in Use | Suggested Spares |

|---------------------|---------------|------------------|

| 728                 | 1             | 0                |

| 844 (Power Control) | 1             | 0                |

# 6.2.3 Indicator Lamps

| DEC Type Number | Number in Use | Suggested Spares |

|-----------------|---------------|------------------|

| 12-00555        | 34            | 4                |

## 7.1 SCOPE

This chapter contains block schematics, circuit schematics, and other engineering drawings necessary to understand and maintain the VP10. Only those drawings which are essential, and not available in the referenced pertinent documents, are included. If any discrepancy exists between the drawings in this chapter and those supplied with the equipment, assume that the equipment drawings are correct. Appendix A of Volume 1 of the KA10 Central Processor Maintenance Manual contains a discussion of flow diagram and schematic drawing interpretation; chapter 1 of Volume 2 describes the DEC engineering drawing numbering system.

Table 7-1

Engineering Drawing List

| Drawing Number | Title 1                     | Page |

|----------------|-----------------------------|------|

| B-CS-A601-0-1  | 3-Bit DAC                   | 7-3  |

| B-CS-A704-0-1  | -10V Precision Power Supply | 7-3  |

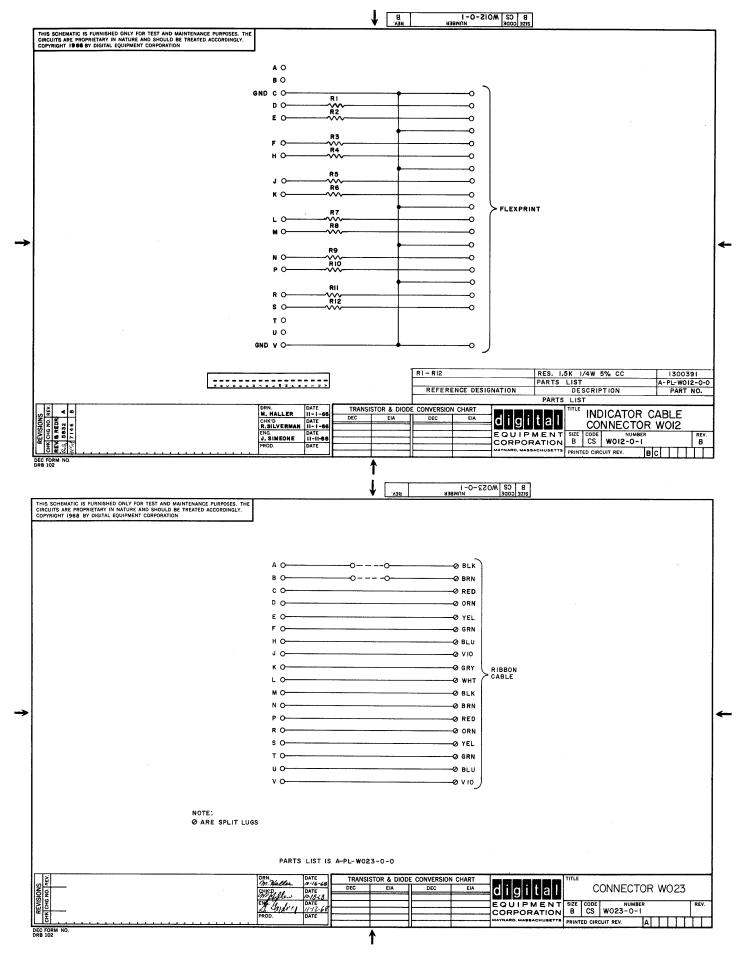

| C-CS-B152-0-1  | Binary to Octal Decoder     | 7-4  |

| B-CS-B163-0-1  | Diode Gate                  | 7-5  |

| B-CS-R002-0-1  | Diode Cluster               | 7-5  |

| B-CS-R201-0-1  | Flip-Flop                   | 7-6  |

| B-CS-R302-0-1  | Delay                       | 7-6  |

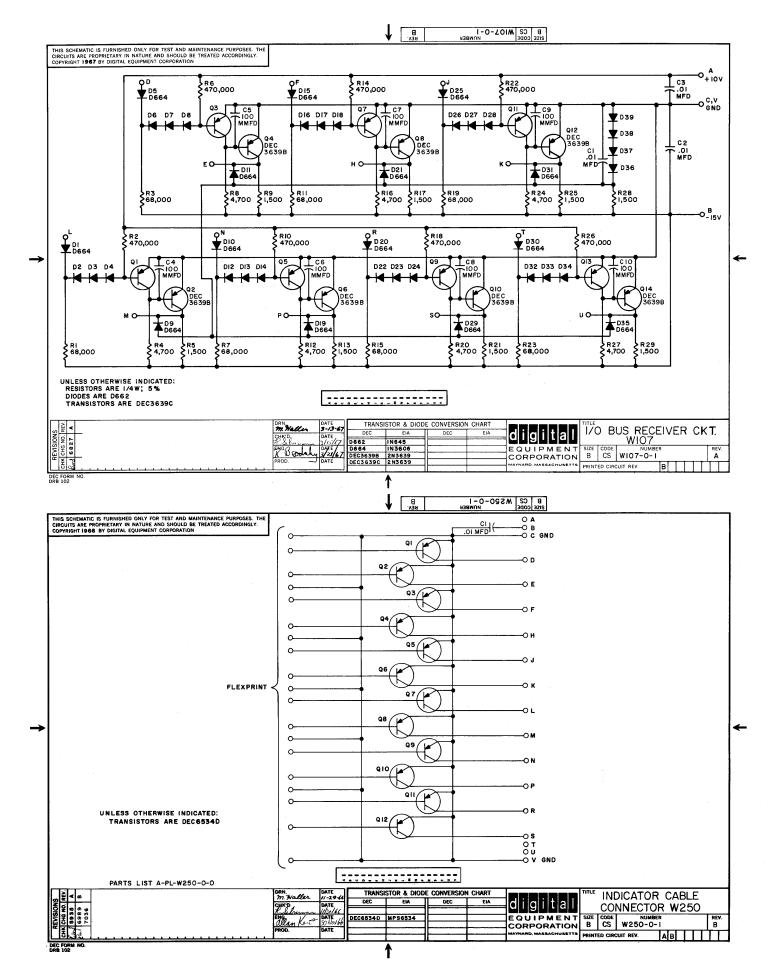

| B-CS-R613-0-1  | Pulse Amplifier             | 7-7  |

| B-CS-S107-0-1  | Inverter                    | 7-7  |

| B-CS-S111-0-1  | Diode Gate                  | 7-8  |

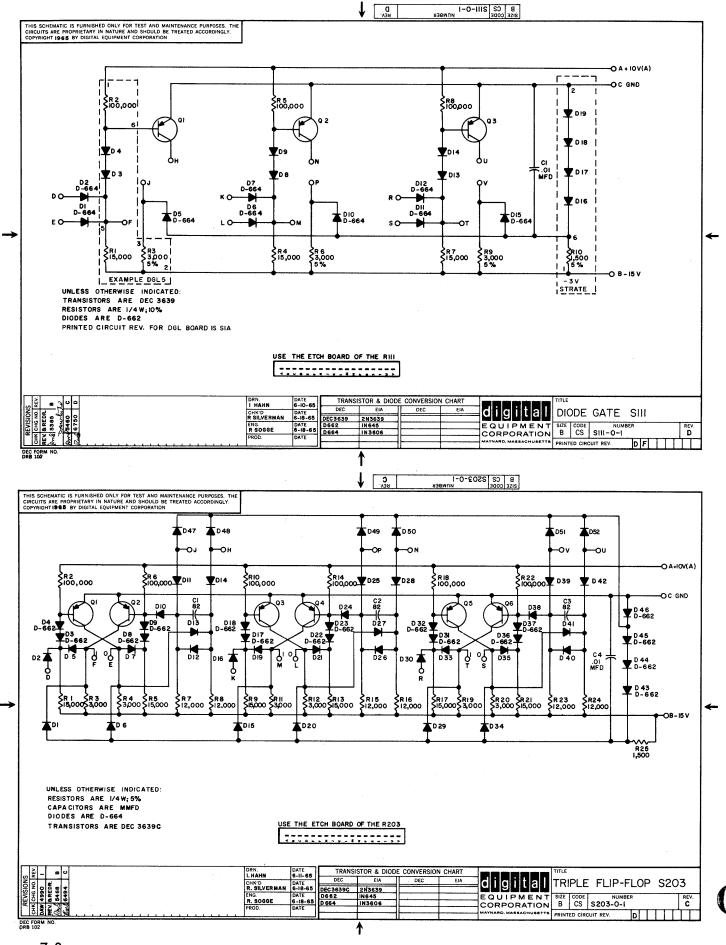

| B-CS-S203-0-*  | Triple Flip-Flop            | 7-8  |

| B-CS-S205-0-1  | Dual Flip–Flop              | 7-9  |

| B-CS-W005-0-1  | Clamped Loads               | 7-9  |

| B-CS-W012-0-1  | Indicator Cable Connector   | 7-10 |

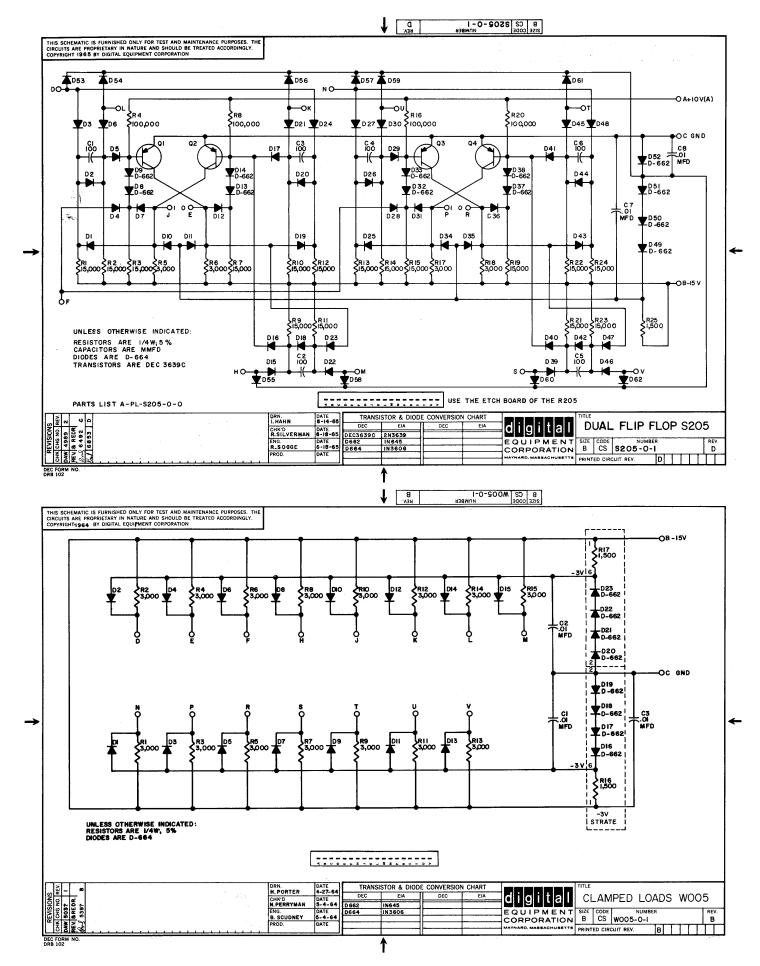

Table 7-1 (Cont) Engineering Drawing List

| Drawing Number   | Title                                   | Page         |

|------------------|-----------------------------------------|--------------|

| B-CS-W023-0-1    | Connector                               | 7-10         |

| B-CS-W107-0-1    | I/O Bus Receiver Ckt.                   | <i>7</i> -11 |

| B-CS-W250-0-1    | Indicator Cable Connector               | <i>7</i> -11 |

| B-CS-W681-0-1    | Scope Intensifier                       | 7-12         |

| C-CS-W851-0-1    | PDP-10 Bus Connector Board              | 7-13         |

| D-BS-VP10-0-DC   | Display Control DC                      | 7-15         |

| D-BS-VP10-0-IOBC | I/O Bus Control Logic                   | 7-17         |

| D-IC-VP10-0-IOBI | I/O Bus Interface IOBI                  | 7-19         |

| D-BS-VP10-0-IOB  | I/O Bus Interface IOB                   | 7-21         |

| D-BS-VP10-0-ST   | Status ST                               | 7-23         |

| D-BS-VP10-0-XYB  | X-Y Buffers XYB                         | 7-25         |

| A-PL-VP10-0-0    | Point Plot Display Interface (3 sheets) | 7-27,28      |

| D-MU-VP10-0-2    | Module Utilization                      | 7-29         |

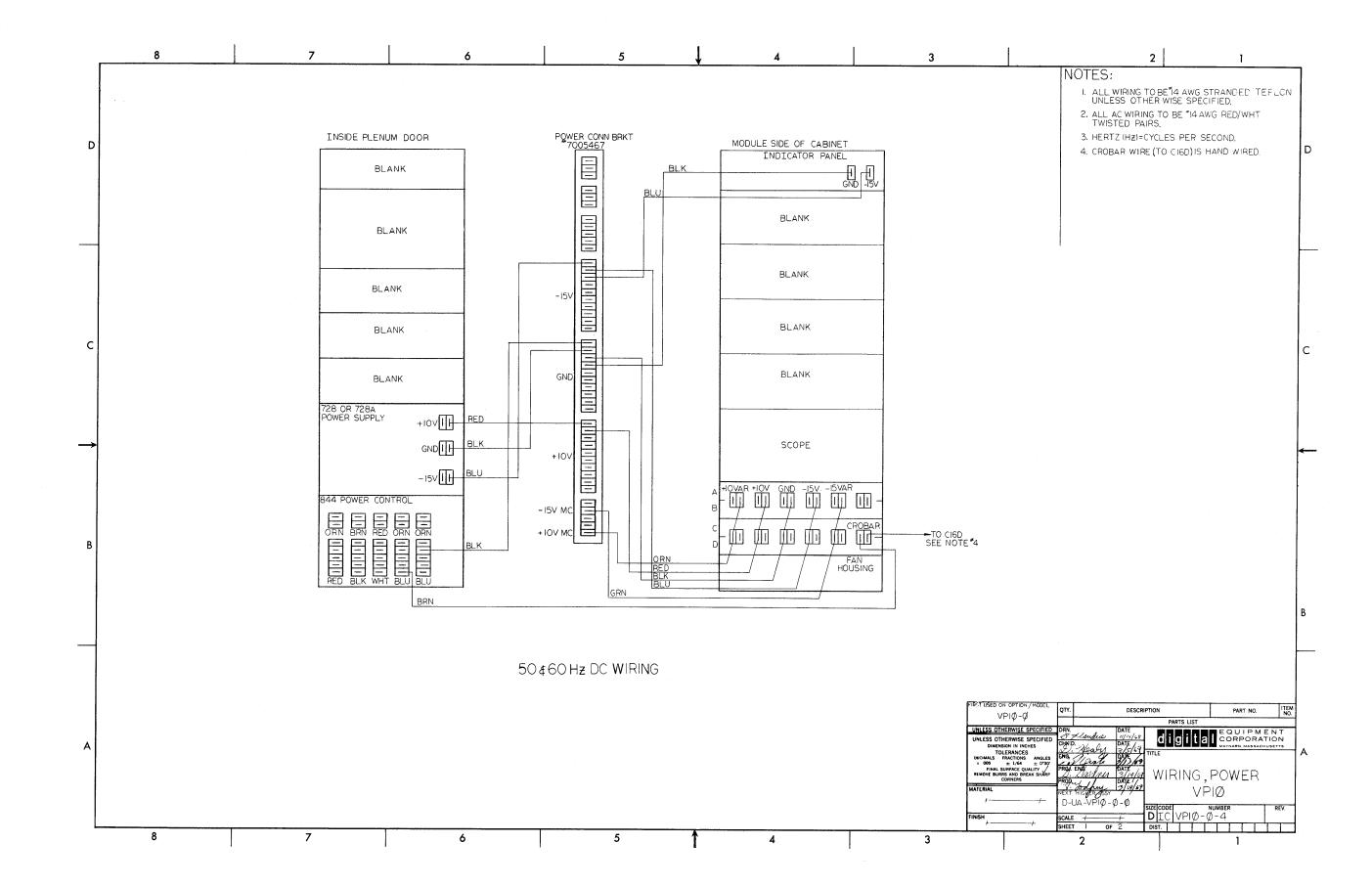

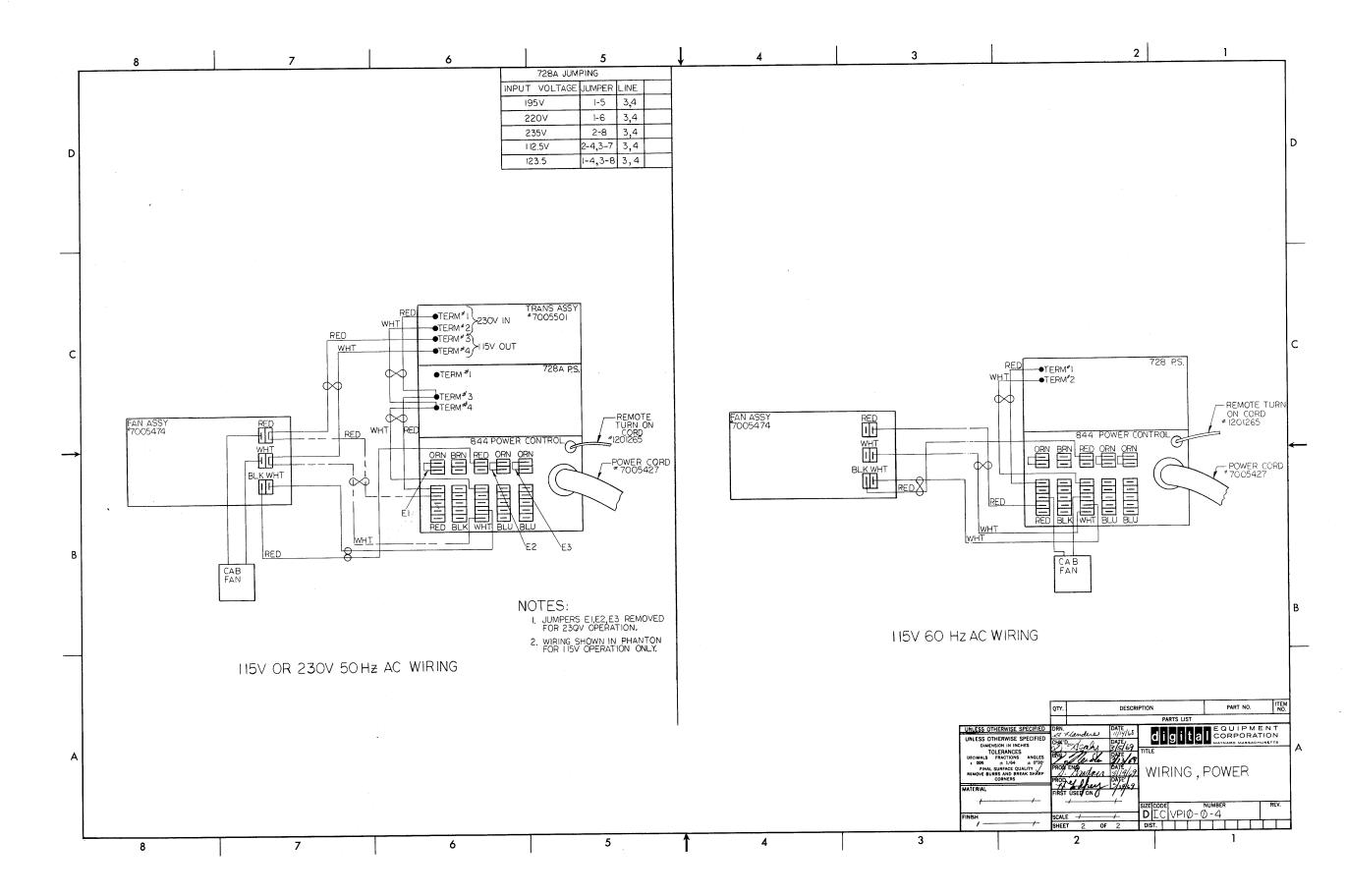

| D-IC-VP10-0-4    | Wiring, Power VP10 (2 sheets)           | 7-31, 33     |

| A-PL-7006041-0-0 | Wired Assembly                          | 7-35         |

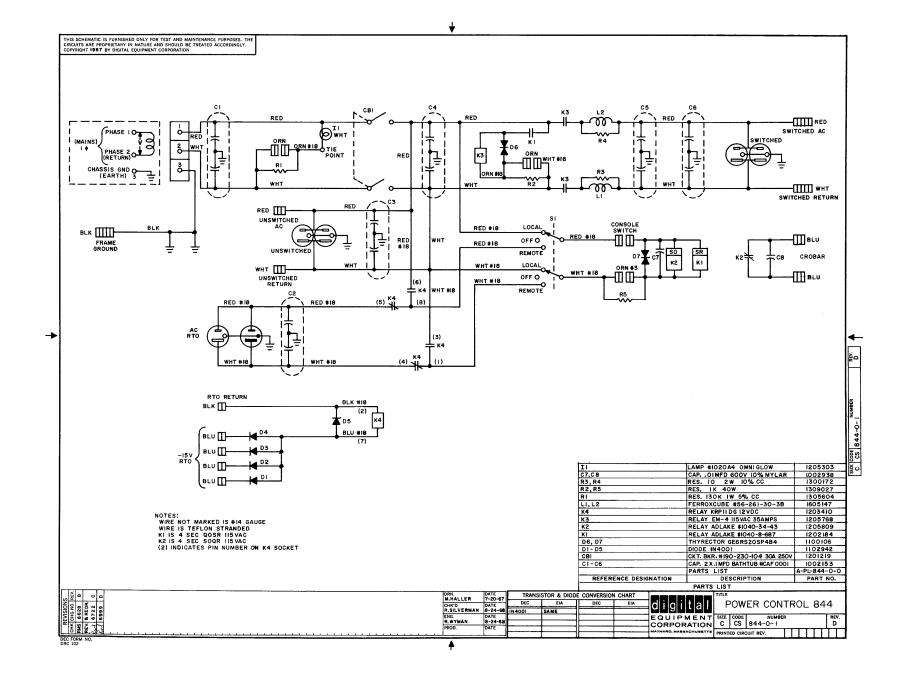

| C-CS-844-0-1     | Power Control 844                       | 7-36         |

| B-CS-728-0-1     | Power Supply 728                        | 7-37         |

7-13

|          | DIGITAL EQ                | UIPMENT CORPORATION                                 | QUANTITY/VARIATION                            |

|----------|---------------------------|-----------------------------------------------------|-----------------------------------------------|

|          | MAYNARD, MASS,<br>PARTS   | PARTS LIST                                          |                                               |

| MADE     | В                         | D. HEALY<br>2/21/69                                 | ZHO                                           |

| ENG DATE | E THE                     | DATE 3/2 4/69 1 ISSUED SECT.                        | S ØT                                          |

| NO.      | DWG NO. / PART NO.        | DESCRIPTION                                         | 1                                             |

| 23       | D-MA-728-0-1              | 728 POWER SUPPLY                                    | 1                                             |

| 24       | D-MA-728A-Ø-1             | 728A POWER SUPPLY                                   |                                               |

| 25       | D-AD-7005358-2-0          | DOOR FULL ASSY                                      | 1 1                                           |

| 26       | 9007620                   | SQ                                                  | 2 2                                           |

| 27       | 9007858                   | WASHER 11/16 O.D. x 3/8 I.D. x 1/16 THK SS          | T2 2                                          |

| 28       | 9006593                   | NUT HEX 3/8-16 SST                                  | 2 2                                           |

| 29       | 9007074                   | CLAMP CAB-L-TITE #261-100 DAKOTA                    | 7 7                                           |

| 30       | 9006075-1                 | SCR PH PAN HD 10-32 c 3/4 LG SST                    | 7 7                                           |

| 31       | B-MD-7406047-0-0          | BLOCK RETAINER                                      | 2 2                                           |

| 32       | 9007799                   | SCR PH HD FIL #8-32 x 1½ LG SST                     | 4 4                                           |

| 33       | D-AD-BC10/A-0/-0/         | BC1ØA CABLE ASSY (LGTH PER ENG.)                    | 2 2                                           |

| 34       | B-IA-BC1ØB-Ø-Ø            | MARGINAL CHK CABLE (LGTH PER ENG.)                  |                                               |