PDP-10 Maintenance Manual

# DC10 DATA LINE SCANNER

# DC10 DATA LINE SCANNER MAINTENANCE MANUAL

1st Edition, November 1967 2nd Printing, April 1968 3rd Printing, May 1969 4th Printing, (Rev) June 1971 5th Printing, June 1973 6th Printing, October 1973

Copyright © 1967, 1968, 1969, 1971, 1973 by Digital Equipment Corporation

The material in this manual is for information purposes and is subject to change without notice.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

FLIP CHIP PDP

# **CONTENTS**

|            |                                                   | Page  |

|------------|---------------------------------------------------|-------|

| CHAPTER 1  | INTRODUCTION                                      |       |

| 1.1        | Scope                                             | 1-1   |

| 1.2        | General Description                               | 1-1   |

| 1.3        | Reference Material                                | 1-2   |

| 1.3.1      | Manuals                                           | 1-2   |

| 1.3.2      | Maintenance Program                               | 1-2   |

| 1.4        | Physical Description                              | 1-2   |

| 1.4.1      | Physical Details                                  | 1-3   |

| CHAPTER 2  | OPERATING INFORMATION AND INSTALLATION            |       |

| 2.1        | Introduction                                      | 2-1   |

| 2.2        | Controls and Indicators                           | 2-1   |

| 2.3        | Operating Notes                                   | 2-3   |

| 2.3.1      | Power Application                                 | 2-4   |

| 2.3.2      | Device Selection                                  | 2-4   |

| 2.3.3      | I/O Instruction                                   | 2-4   |

| 2.4        | Programming Notes                                 | 2-5   |

| 2.4.1      | Introduction                                      | 2-5   |

| 2.4.2      | DC10A Programming                                 | 2-6   |

| 2.4.3      | DC10B Programming                                 | 2-8   |

| 2.4.4      | DC10E Programming                                 | 2-12  |

| 2.4.4.1    | DC 10E Special Application Notes                  | 2-18  |

| 2.4.5      | Maintenance Mode                                  | 2-19  |

| CHAPTER 2A | INSTALLATION                                      |       |

| 2A.1       | Cross Connecting and Cable Terminating Guidelines | 2A-1  |

| 2A.2       | Option Card Adjustments                           | 2A-7  |

| 2A.2.1     | Clock Divider Option Card                         | 2A-7  |

| 2A.2.2     | Device Number Option Cards                        | 2A-9  |

| 2A.2.3     | Clock Line Option Card                            | 2A-11 |

| 2A.2.4     | Half-Duplex Option Cards                          | 2A-11 |

| 2A.2.5     | Teletype Receiver Module                          | 2A-12 |

|            |                                                   |       |

# CONTENTS (Cont)

|           |                                             | Page  |

|-----------|---------------------------------------------|-------|

| 2A.2.6    | Teletype Transmitter Module                 | 2A-15 |

| 2A.2.7    | Telegraph Line Module                       | 2A-16 |

| 2A.3      | I/O Bus Connections                         | 2A-20 |

| 2A.4      | Teletype Information                        | 2A-20 |

| CHAPTER 3 | THEORY OF OPERATION                         |       |

| 3.1       | Block Diagram Analysis                      | 3-1   |

| 3.1.1     | Control Unit DC10A                          | 3-3   |

| 3.1.1.1   | Scanner Operation                           | 3-5   |

| 3.1.1.2   | Baud Rate Clock Operation                   | 3-9   |

| 3.1.1.3   | DLS I/O Control Operation                   | 3-9   |

| 3.1.2     | Eight-Line Group Unit DC10B                 | 3-27  |

| 3.1.3     | Eight-Line Telegraph Relay Assembly DC10C   | 3-32  |

| 3.1.4     | Telegraph Power Supply DC10D                | 3–34  |

| 3.1.5     | Expanded Data-Set Control DC10E             | 3-35  |

| 3.1.5.1   | Data Line Without Automatic Calling         | 3-36  |

| 3.1.5.2   | Data Line With Automatic Calling            | 3-40  |

| 3.2       | Detailed Description                        | 3-43  |

| 3.2.1     | D-FD-DC10A-0-FD                             | 3-43  |

| 3.2.2     | D-BS-DC10A-0-CLKD                           | 3-44  |

| 3.2.3     | D-BS-DC10A-0-CNTR                           | 3-45  |

| 3.2.4     | D-BS-DC10A-0-DAT1 Through D-BS-DC10A-0-DAT4 | 3-46  |

| 3.2.5     | D-BS-DC10A-0-DLS                            | 3-47  |

| 3.2.6     | D-BS-DC10A-0-IND                            | 3-49  |

| 3.2.7     | D-BS-DC10A-0-LSEL                           | 3-50  |

| 3.2.8     | D-BS-DC10A-0-RIO                            | 3-50  |

| 3.2.9     | D-BS-DC10A-0-SCNC                           | 3-51  |

| 3.2.10    | D-BS-DC10A-0-SCNR                           | 3-53  |

| 3.2.11    | D-BS-DC10A-0-WIO                            | 3-54  |

| 3.2.12    | D-MU-DC10A-0-MU                             | 3-55  |

| 3.2.13    | D-BS-DC10B-0-COMM                           | 3-55  |

| 3 2 14    | D-BS-DC10B-0-L01 Through D-BS-DC10B-0-L67   | 3-55  |

# CONTENTS (Cont)

|           |                                                     | Page |

|-----------|-----------------------------------------------------|------|

| CHAPTER 4 | MAINTENANCE                                         |      |

| 4.1       | Scope                                               | 4-1  |

| 4.2       | Equipment Required                                  | 4-1  |

| 4.3       | Preventive Maintenance                              | 4-2  |

| 4.3.1     | Mechanical Checks                                   | 4-2  |

| 4.3.2     | Power Supply Checks                                 | 4-3  |

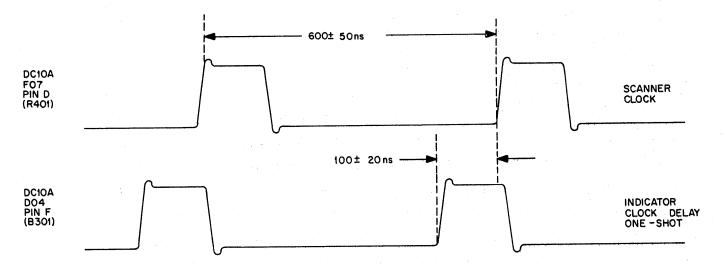

| 4.3.3     | Clock and Delay Adjustments                         | 4-3  |

| 4.3.3.1   | Scanner Clock Check and Adjustment                  | 4-4  |

| 4.3.3.2   | Indicator Clock Delay One-Shot Check and Adjustment | 4-4  |

| 4.3.3.3   | Data Terminal Ready One-Shot Check and Adjustment   | 4-5  |

| 4.3.3.4   | Indicator One-Shot Check and Adjustment             | 4-5  |

| 4.3.3.5   | Telegraph Line Current Check and Adjustment         | 4-5  |

| 4.3.3.6   | Telegraph Line Bias Current Check and Adjustment    | 4-6  |

| 4.3.4     | Margin Checks                                       | 4-6  |

| 4.4       | Corrective Maintenance                              | 4-6  |

| 4.4.1     | Preliminary Investigation                           | 4-7  |

| 4.4.2     | System Troubleshooting                              | 4-7  |

| 4.4.3     | Module Troubleshooting                              | 4-8  |

| 4.4.4     | Repair                                              | 4-9  |

| 4.4.5     | Validation Test                                     | 4-9  |

| 4.4.6     | Log Entry                                           | 4-10 |

| CHAPTER 5 | ENGINEERING DRAWING LIST                            |      |

| 5.1       | Introduction                                        | 5-1  |

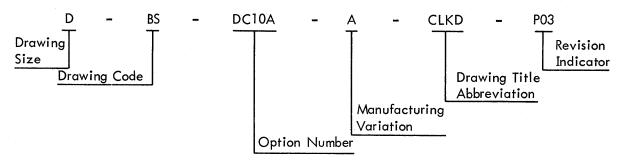

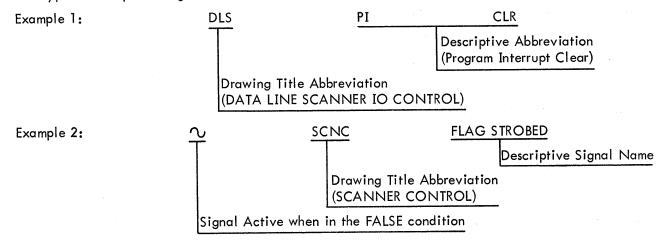

| 5.2       | Drawing Terminology                                 | 5-1  |

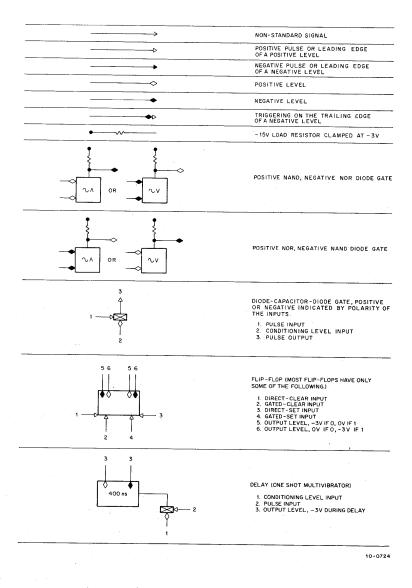

| 5.3       | Logic Symbols                                       | 5-2  |

| 5.4       | Logic Levels                                        | 5-2  |

| 5.5       | FLIP CHIP Pulses                                    | 5-4  |

| 5.6       | Engineering Drawings                                | 5-4  |

# ILLUSTRATIONS

| Figure |                                                                | Page <sup>*</sup> |

|--------|----------------------------------------------------------------|-------------------|

| 1-1    | Data Line Scanner Components                                   | 1-3               |

| 2-1    | Indicator Panel                                                | 2-1               |

| 2-2    | Power Control Panel                                            | 2-3               |

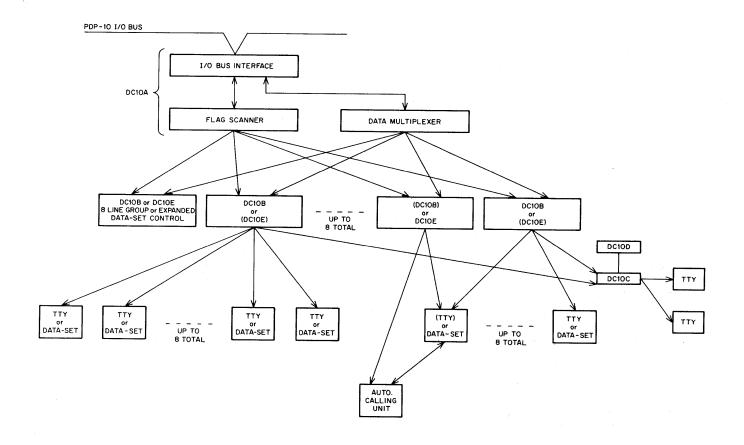

| 2-3    | DC10 Block Diagram                                             | 2-7               |

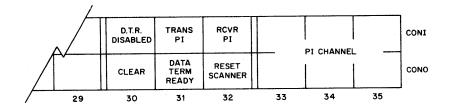

| 2-4    | DC10A Control and Status                                       | 2-8               |

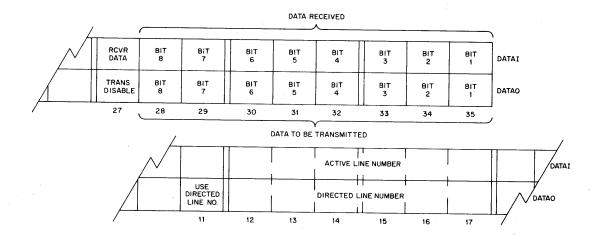

| 2-5    | DC 10B Data                                                    | 2-9               |

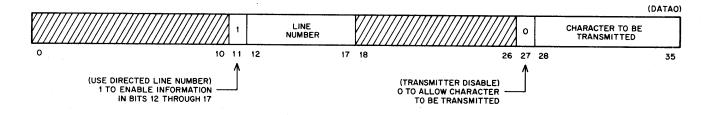

| 2-6    | DC 10E Data                                                    | 2-13              |

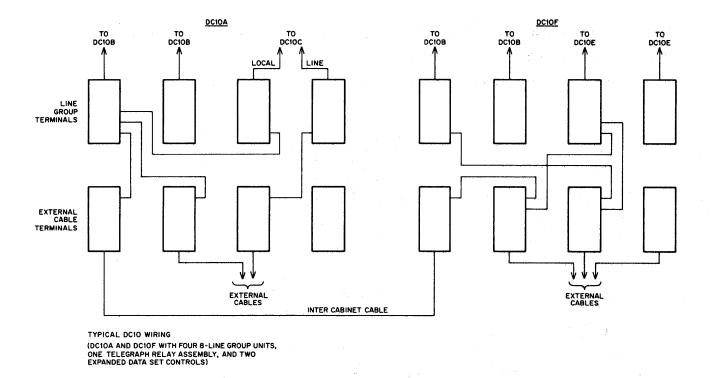

| 2A-1   | Typical DC10 Cabling                                           | 2A-3              |

| 2A-2   | Examples of Crosswiring                                        | 2A-4              |

| 2A-3   | Typical Jumper Configuration                                   | 2A-9              |

| 2A-4   | Device Number Option Cards (DC10A)                             | 2A-10             |

| 2A-5   | Clock Line Option Card (DC10B)                                 | 2A-11             |

| 2A-6   | Half-Duplex Option Card (DC10B)                                | 2A-12             |

| 2A-7   | Teletype Receiver Module W706                                  | 2A-13             |

| 2A-8   | Teletype Transmitter Module W707 (DC10B)                       | 2A-15             |

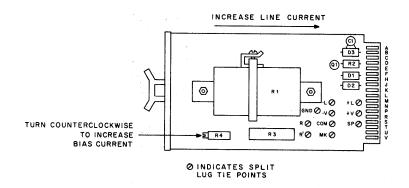

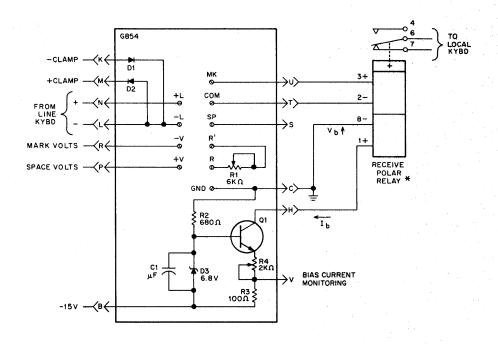

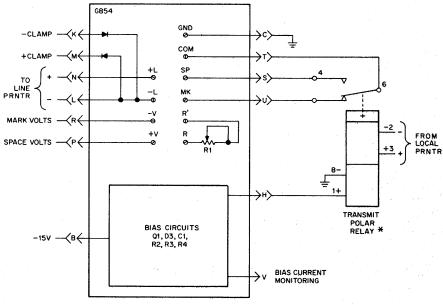

| 2A-9   | Telegraph Line Module G854 (DC10C)                             | 2A-16             |

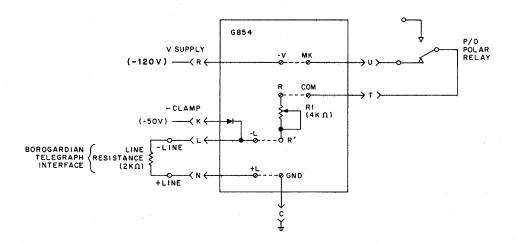

| 2A-10  | G854 Strapping (DC10C)                                         | 2A-18             |

| 2A-11  | Interface for the Borogardian Telecommunication Administration | 2A-19             |

| 2A-12  | Location of DC10A I/O Bus Connections                          | 2A-20             |

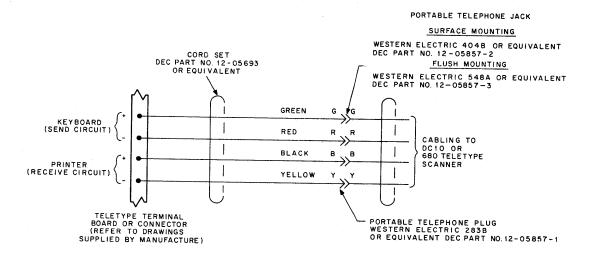

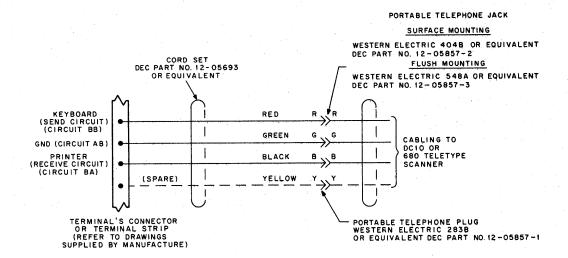

| 2A-13  | 20 mA, Full Duplex Terminals                                   | 2A-21             |

| 2A-14  | EIA Interface Connections                                      | 2A-22             |

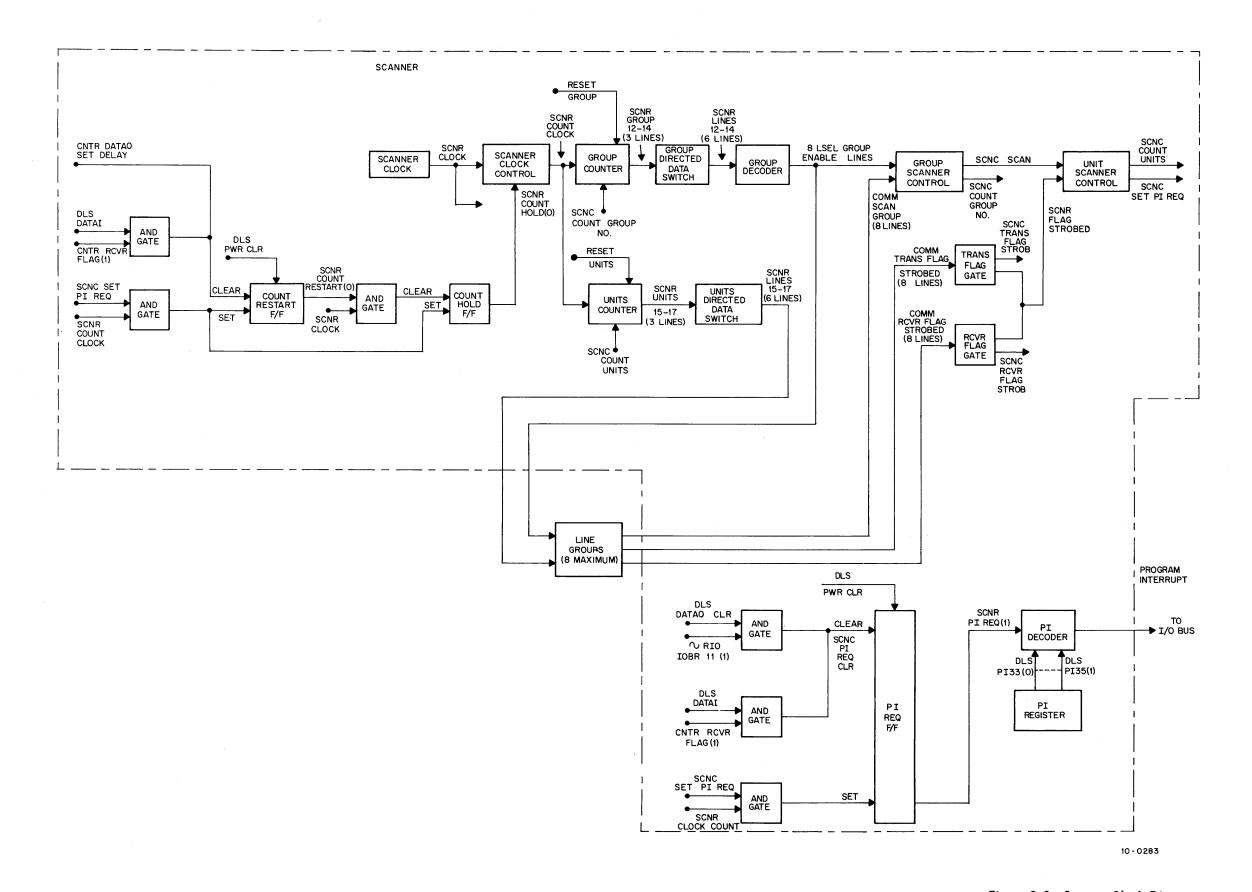

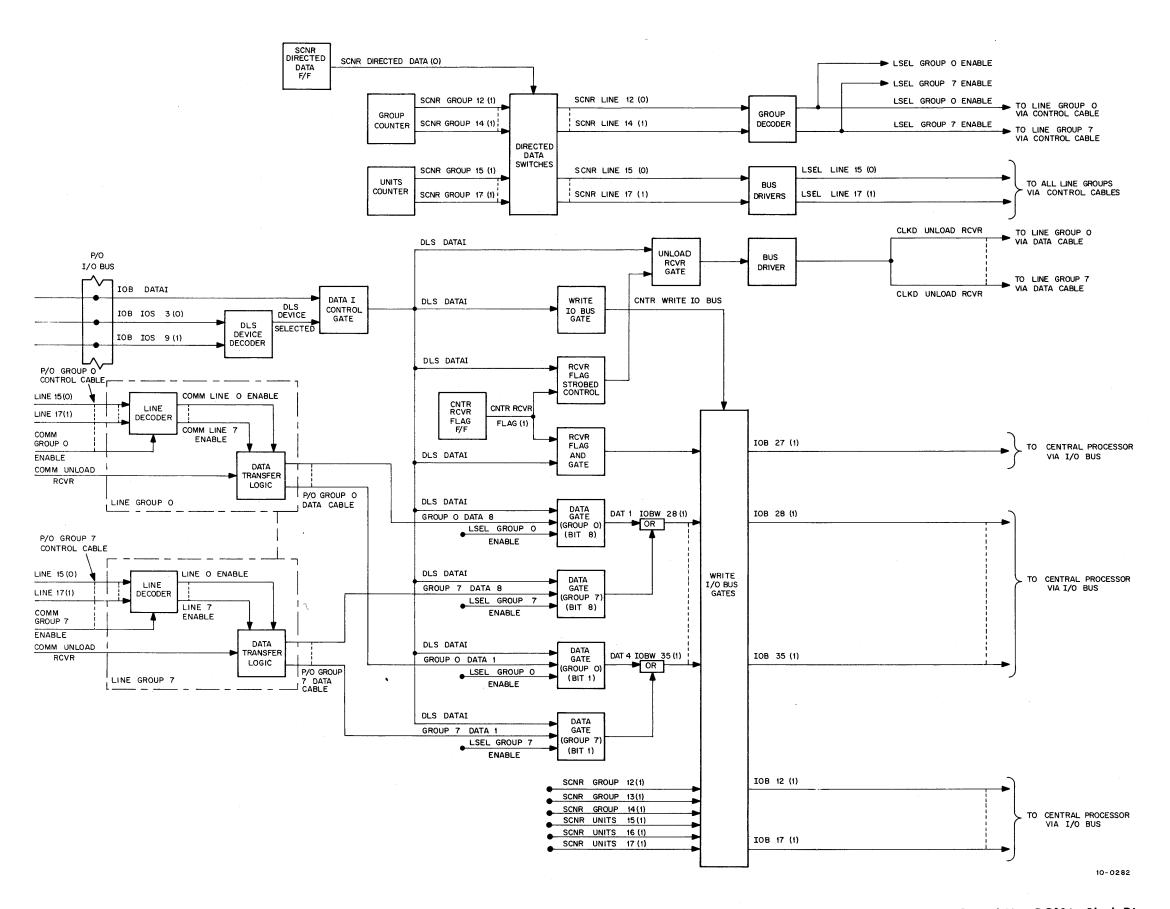

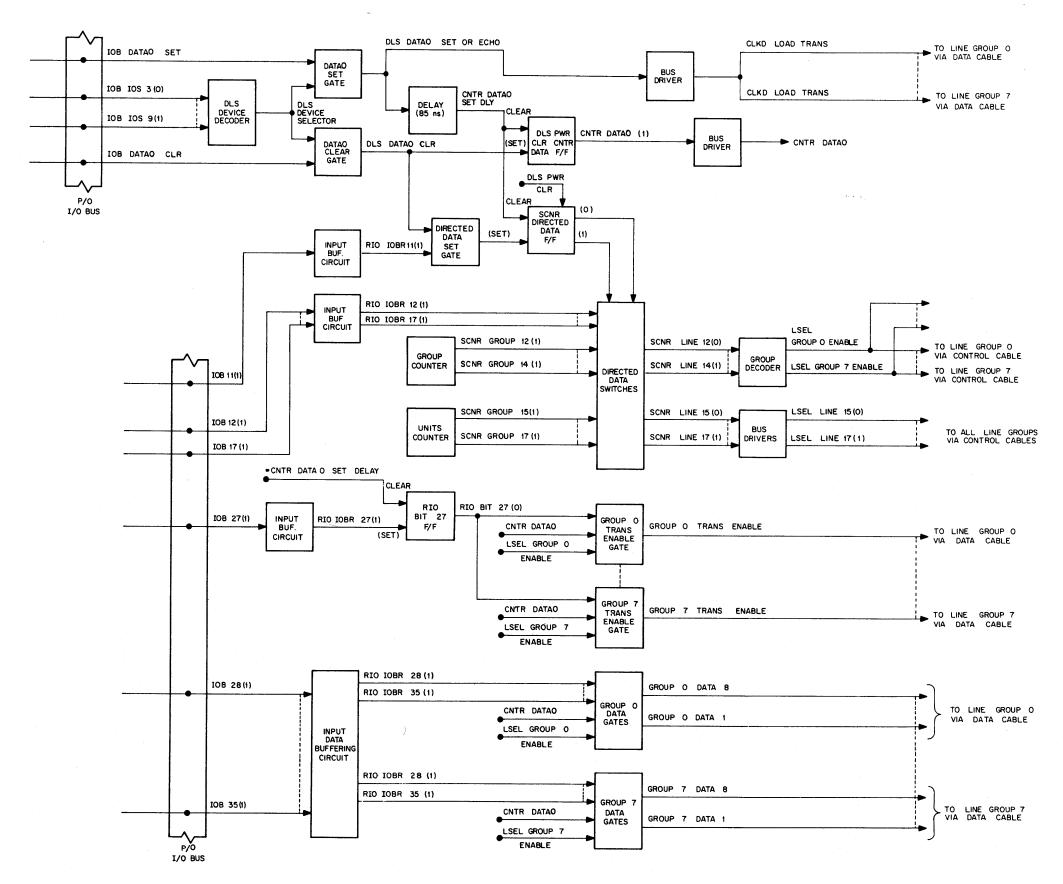

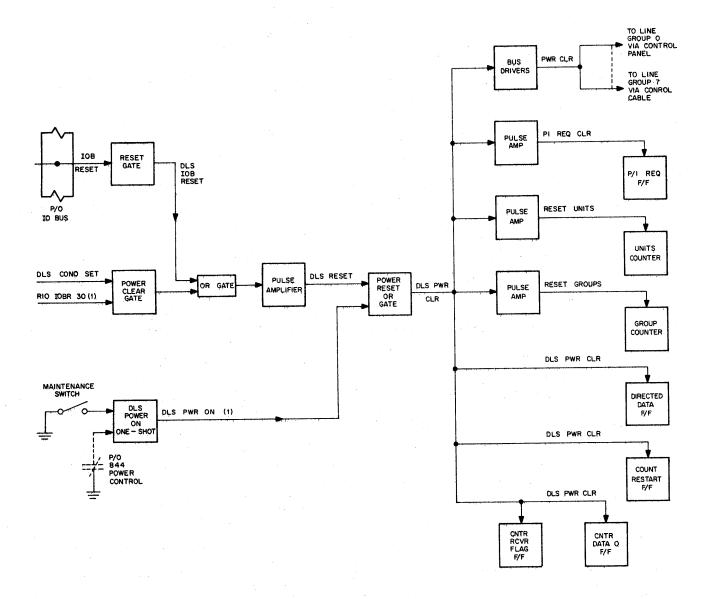

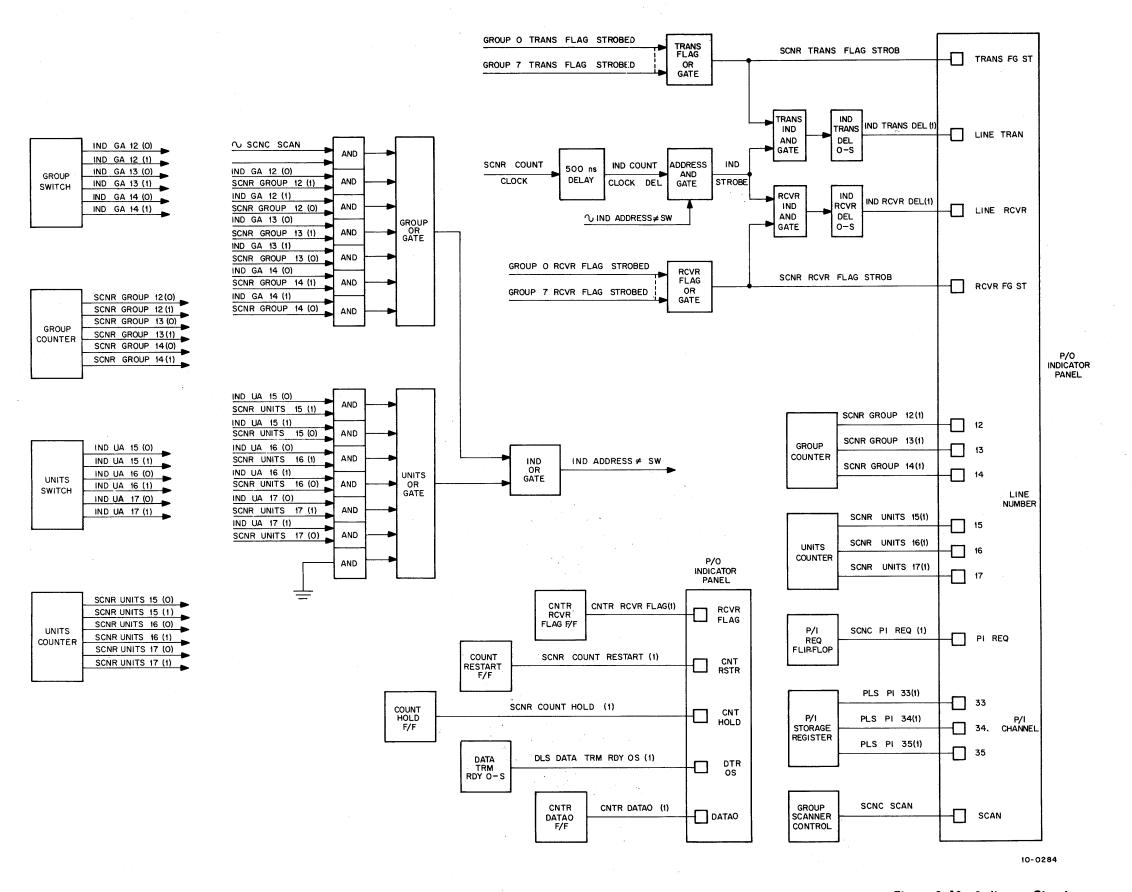

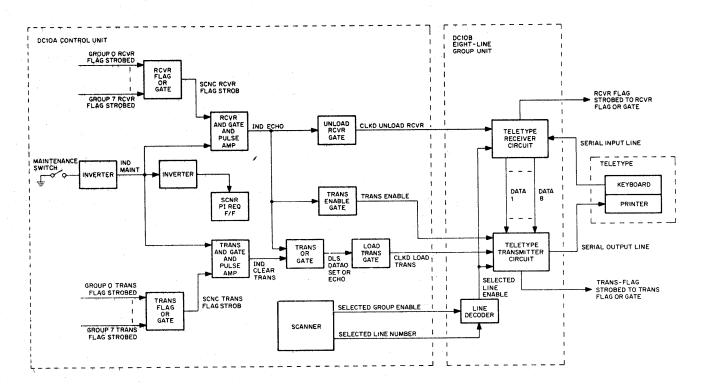

| 3-1    | A Data Line Scanning Block Diagram                             | 3-2               |

| 3-2    | Control Unit DC10A Block Diagram                               | 3-4               |

| 3-3    | Scanner Block Diagram                                          | 3-7               |

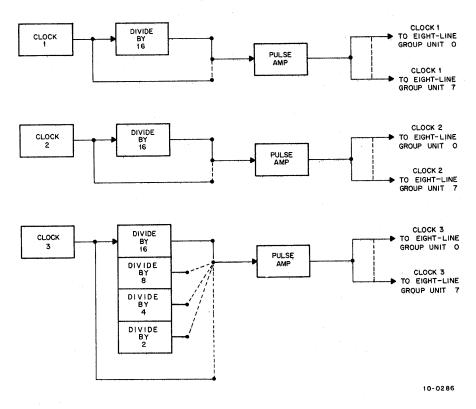

| 3-4    | Baud Rate Clock Block Diagram                                  | 3-10              |

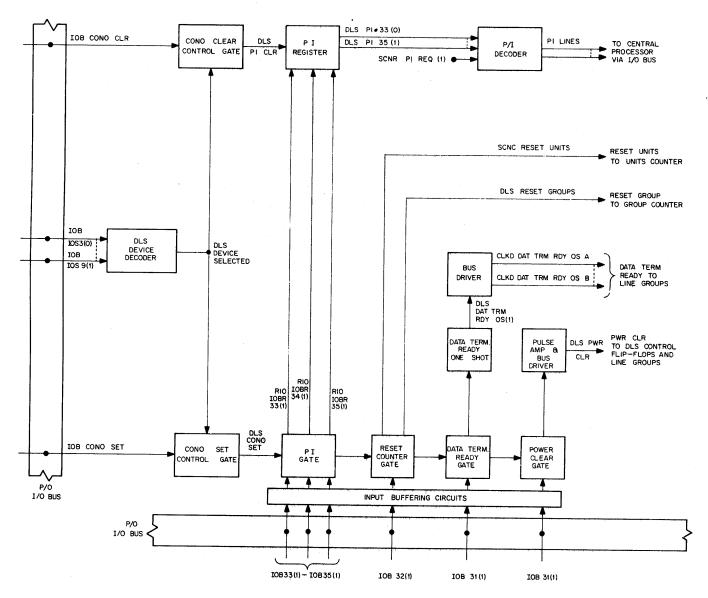

| 3-5    | Control Unit DC10A Block Diagram - CONO Instruction            | 3-11              |

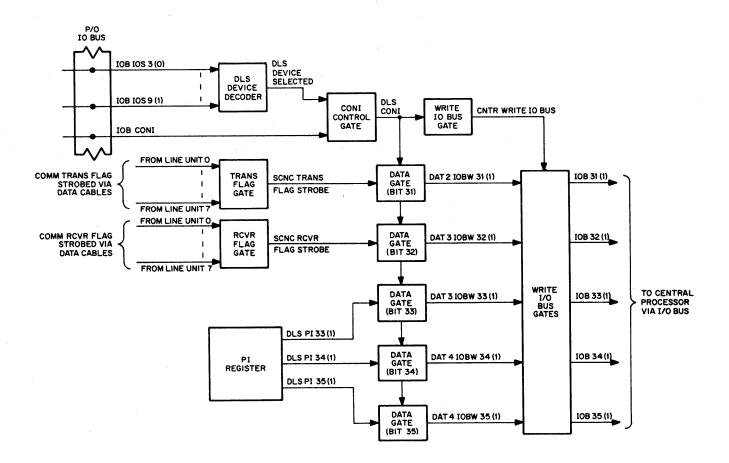

| 3-6    | Control Unit DC10A Block Diagram - CONI Instruction            | 3-12              |

| 3-7    | Control Unit DC10A, Block Diagram DATAI Instruction            | 3-15              |

| 3-8    | Control Unit DC10A, Block Diagram, DATAO Instruction           | 3-19              |

| 3-9    | Data Line Scanner Reset Circuit                                | 3-22              |

| 3-10   | Indicator Circuit                                              | 3-23              |

| 3-11   | Echo Circuit                                                   | 3-26              |

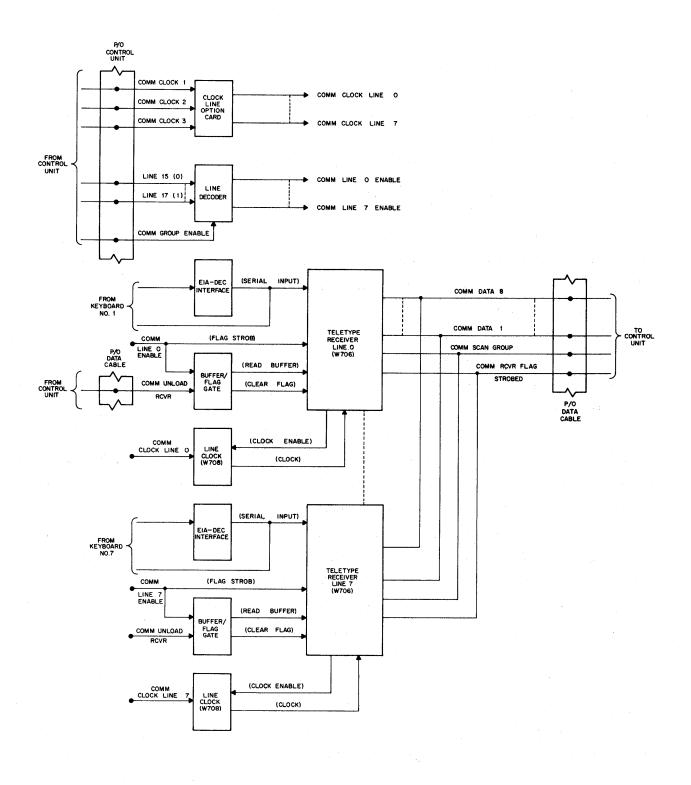

| 3-12   | Eight-Line Group Unit DC10B - Receive Circuit                  | 3-29              |

# ILLUSTRATIONS (Cont)

| Figure |                                                                    | Page |

|--------|--------------------------------------------------------------------|------|

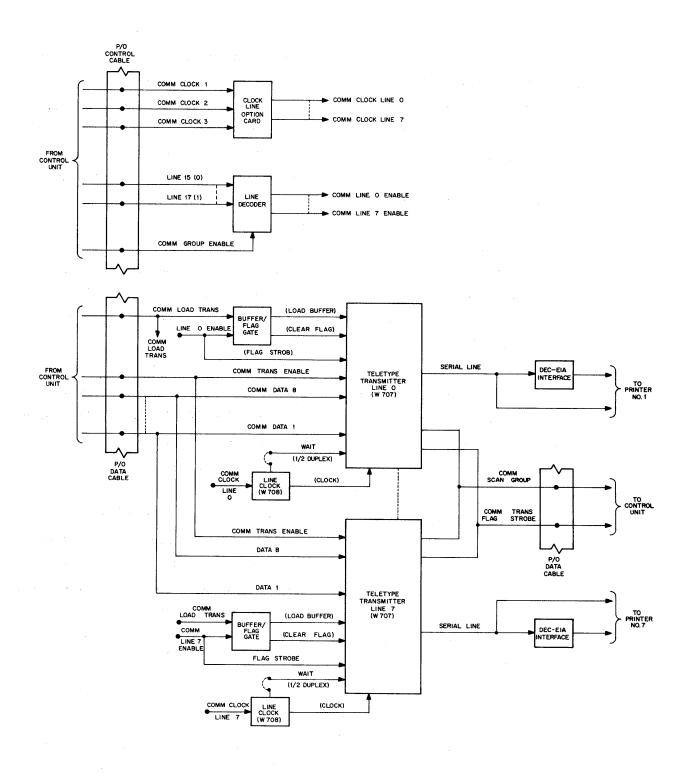

| 3-13   | Eight-Line Group Unit DC10B - Transmit Circuit                     | 3-31 |

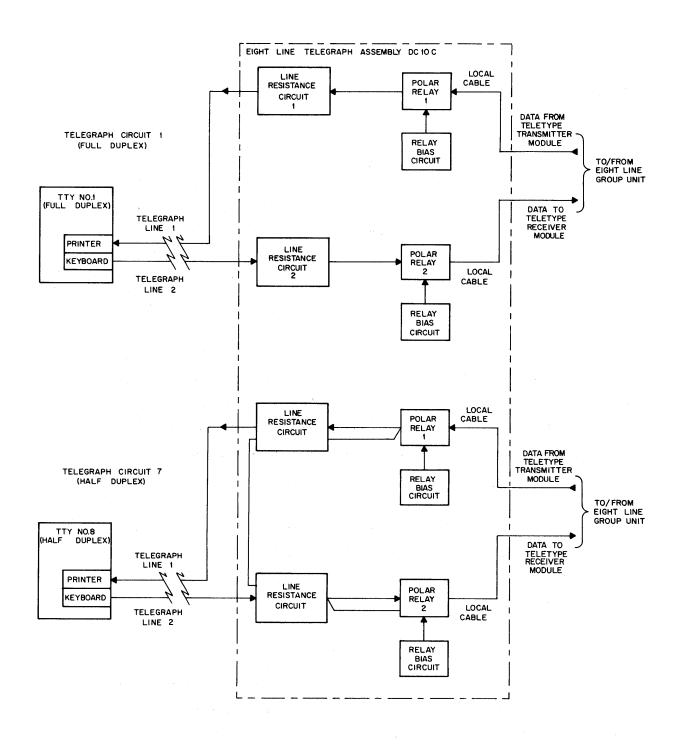

| 3-14   | Eight-Line Telegraph Relay Assembly DC10C - Block Diagram          | 3-33 |

| 3-15   | Telegraph Power Supply Block Diagram                               | 3-35 |

| 3-16   | Expanded Data-Set Control - Typical Line Without Automatic Calling | 3-37 |

| 3-17   | Expanded Data–Set Control – Typical Line With Automatic Calling    | 3-42 |

| 4-1    | Scanner Clock Adjustment                                           | 4-4  |

| 5-1    | DEC Standard Logic Symbols                                         | 5-3  |

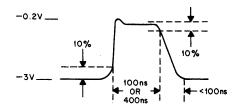

| 5-2    | R-Series Pulse                                                     | 5-4  |

|        | TABLES                                                             |      |

| Table  |                                                                    | Page |

| 1-1    | Physical Characteristics of the Data Line Scanner Options          | 1-4  |

| 2-1    | Indicator Panel Functions                                          | 2-2  |

| 2-2    | Power Control Functions                                            | 2-3  |

| 2A-1   | Wire Color to Line Name Cross Reference Chart                      | 2A-2 |

| 2A-2   | Cable Pairing Guide                                                | 2A-7 |

| 2A-3   | Clock Frequency and Jumper Connections                             | 2A-8 |

| 4-1    | Special Maintenance Equipment                                      | 4 1  |

# CHAPTER 1 INTRODUCTION

# 1.1 SCOPE

This manual contains introductory material, installation and operating information, theory of operation, and maintenance information for the Type DC10 Data Line Scanner. Since this manual is intended to aid maintenance personnel, the equipment is discussed primarily from a maintenance point of view. A general description and physical description is included in the introductory section to provide a brief overall understanding of a data line scanner system. A working knowledge of the central processor and peripheral devices is assumed; but, to aid maintenance personnel in locating reference material, a list of pertinent documents is included in the introductory material. In the installation and operating information, general operating instructions are provided, along with option adjustments that are required by the customer during installation. The theory of operation is divided into three levels of coverage: first, a simplified system block diagram is used to identify the major system components and to describe the basic system operation; next, each of the major components are explained at the block diagrams. In the maintenance section, troubleshooting information and adjustment procedures are provided to aid the maintenance personnel in locating and repairing system malfunctions.

#### 1.2 GENERAL DESCRIPTION

The Type DC10 Data Line Scanner provides a timesharing two-way interface between the PDP-10 central processor and a maximum of 64 teletype-like stations. Any device which uses a 5-level or 8-level serial teletype code can be accommodated at signaling speeds of up to 100 kilobaud. Full-duplex, full-duplex with local copy, and half-duplex data line modes are available on each line serviced. Send-only or receive-only stations are also accommodated. Information is transferred between a device and the central processor on a time-sharing basis and under program control. The data lines to the devices are serviced either on demand or under program control, but servicing of the data lines is controlled by the central processor on a priority interrupt basis. Command signals are routed to the data line scanner via the input/output (I/O) bus and are used to control the I/O instructions. During a CONI or DATAI instruction, data is routed to the central processor from a device via the I/O bus. When a CONO or DATAO instruction is performed, data is routed from the central processor to a device via the I/O bus.

# 1.3 REFERENCE MATERIAL

The following DEC documents contain material which supplements information in this manual. These documents may be obtained from the nearest DEC office or from

Digital Equipment Corporation 146 Main Street Maynard, Massachusetts 01754

## 1.3.1 Manuals

Digital Logic Handbook (C-105) Specifications and descriptions of FLIP

CHIP modules, plus simplified explanation of the selection and use of these modules in numerous applications.

modules in numerous applications

PDP-10 Interface Manual Implementation guidelines and requirements

DEC-10-HIFB-D

for the PDP-10 I/O Bus, memory bus, and

data channel bus.

PDP-10 System Reference Manual

DEC-10-HGAC-D

Programming and operating information for

the computer, including programming information

on the Type DC10 Data Line Scanner.

# 1.3.2 Maintenance Program

DC10 Data Line Scanner Test MAINDEC-10-D2CC-D

## 1.4 PHYSICAL DESCRIPTION

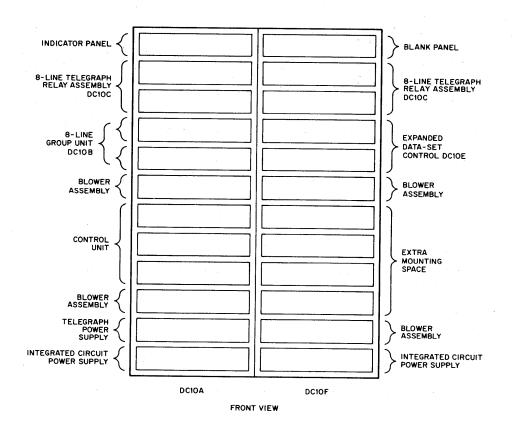

The DC10 Data Line Scanner is designed to fulfill a wide variety of system requirements. System components are purchased as options, thus the hardware configuration of a system depends upon the customer's requirements. The major components of a data line scanner system are identified in Figure 1-1. Table 1-1 lists the physical characteristics and provides a brief functional description for each of the DEC designed and manufactured options.

# 1.4.1 Physical Details

System components are purchased as options and are mounted in standard DEC 19-in. cabinets which are constructed with welded frames and metal sheet covering. Access doors are mounted on the front and rear of the cabinet and are held closed by magnetic latches. The power control, eight standard 25-pair connecting blocks, and the dc power supplies are mounted inside the rear door on a full-width plenum door that is latched by a spring-loaded pin at the top. Module mounting panels are mounted behind the front door with the wiring side facing outward. Blower assemblies mounted between the module mounting panels pass cooling air over the modules; the air is exhausted through an opening at the top of the cabinet.

In each system, the DC10A Control Unit is required. The cabinet supplied with this option contains the control unit, indicator panel, integrated circuit power supply, two blower assemblies, and 21 in. of panel mounting space. When additional panel mounting space is required for a larger system, the cabinet of the DC10F Expander Cabinet option is bolted to the control unit cabinet to form a contiguous unit. The expanded cabinet is similar to the first cabinet except an additional control unit is not required or supplied. Because of this, the cabinet addition provides 42 in. of panel mounting space.

Figure 1-1 Data Line Scanner Components

Table 1–1

Physical Characteristics of the Data Line Scanner Options

| Option                                      | Function                                                                                                                   | Contains                                                                                                                                                                                                                                                  | Weight               | Physical<br>Requirements                                                            | Power 1<br>Requirements |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------|-------------------------|

| DC10A<br>Control Unit                       | Provides the necessary in-<br>terface between the central<br>processor and up to eight<br>line groups.                     | <ul> <li>a. One Control unit</li> <li>b. One cabinet with power supplies</li> <li>c. One set of I/O bus cables</li> <li>d. Four line group connecting blocks</li> <li>e. Four external cable blocks</li> <li>f. 21 in. of panel mounting space</li> </ul> | 500 lb. <sup>1</sup> | Requires 3 ft. in both front and rear for access and maintenance.                   | 1500W.                  |

| DC 10B<br>8-Line Group<br>Unit              | Provides the necessary in-<br>terface between the control<br>unit and eight teletype-like<br>devices.                      | a. One 8-line group b. One set of cables to the control unit.                                                                                                                                                                                             | See DC10A            | Requires 5-1/4 in. of panel<br>mounting space and one<br>equipment connecting block | See DC10A               |

| DC10C<br>8-Line Telegraph<br>Relay Assembly | Provides relay buffering for full or half duplex circuits.                                                                 | <ul><li>a. One telegraph relay assembly</li><li>b. One relay bias panel</li></ul>                                                                                                                                                                         | See DC10A            | Requires 10–1/2 in. of panel mounting space and two equipment connecting blocks     | See DC10A               |

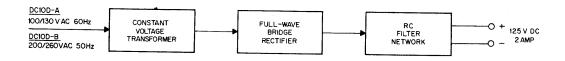

| DC10D<br>Telegraph<br>Power Supply          | Provides the necessary power to operate the telegraph lines associated with approximately four telegraph relay assemblies. | a. One 125 Vdc, 2A<br>power supply                                                                                                                                                                                                                        | See DC10A            | 5–1/4 in. of panel mount-<br>ing space allotted in DC10A<br>cabinet                 | See DC10A               |

| DC 10E<br>Expanded<br>Data–Set<br>Control   | Provides status and operational controls for eight standard data sets, two with automatic calling provisions.              | a. Eight expanded data set controls b. Two automatic call-c. One set of cables to the control unit                                                                                                                                                        | See DC10A            | Requires 10-1/2 in. of panel mounting space and one equipment connecting block      | See DC10A               |

| DC10F<br>Expander<br>Cabinet                | Provides additional panel mounting space for large data line scanner systems.                                              | <ul> <li>a. One cabinet with power supplies</li> <li>b. Four line group connecting blocks</li> <li>c. Four external cable connecting blocks</li> <li>d. 42 in. of panel mounting space</li> </ul>                                                         | 500 lb. <sup>1</sup> | Requires 3 ft. in both front<br>and rear for access and<br>maintenance              | 1500W                   |

<sup>&</sup>lt;sup>1</sup>Typical

Figure 1-1 Data Line Scanner Components (cont)

# CHAPTER 2 OPERATING INFORMATION AND INSTALLATION

#### 2.1 INTRODUCTION

This chapter provides operating and installation information to aid data line scanner maintenance personnel. The contents of this chapter are organized in this manner: first, the control and indicators are identified and their functions are briefly explained; next, general operating instruction and programming notes provide an overall understanding of the data line scanner; then, detailed procedures for setting up various per-line options during installation are provided. To fully understand these procedures, maintenance personnel should read the theory of operation contained in Chapter 3.

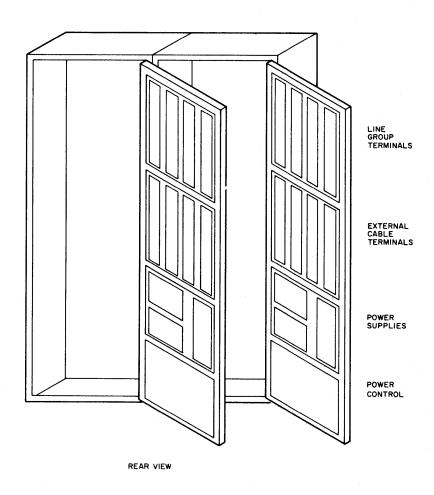

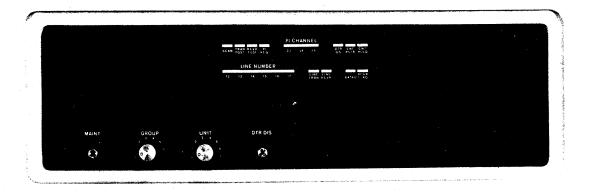

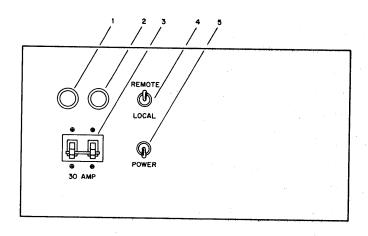

# 2.2 CONTROLS AND INDICATORS

The controls and indicators associated with the data line scanner are identified in Figures 2-1 and 2-2. A thorough understanding of the controls and indicators on the maintenance and indicator panel, Figure 2-1, is a valuable aid to system personnel not only during maintenance mode but also during normal operation. Table 2-1 describes the function of each control or indicator on the panel. The power control panel shown in Figure 2-2 controls the application of the data-line scanner input power. From the power control panel, input power is turned on, the data line scanner power supplies are controlled, and either the local or remote power mode is selected (Table 2-2).

Figure 2-1 Indicator Panel

Table 2–1

Indicator Panel Functions

| Number | Nomenclature   | ltem                        | Function                                                                                              |

|--------|----------------|-----------------------------|-------------------------------------------------------------------------------------------------------|

| 1      | SCAN           | Indicator                   | Indicates that the group selected by the group register has a flag on.                                |

| 2      | tran fg st     | Indicator                   | Indicates when the transmitter flag of the data line selected by the group and units registers is on. |

| 3      | RCVR FG ST     | Indicator                   | Indicates when the receiver flag of the data line selected by the group and units registers is on.    |

| 4      | PI REQ         | Indicator                   | Indicates when the program interrupt flip-flop is set.                                                |

| 5      | PI CHANNEL     | 3 Indicators                | Indicates the octal program-interrupt channel number.                                                 |

| 6      | DTR OS         | Indicator                   | Indicates when the data term ready one-shot is set.                                                   |

| 7      | CNT RSTR       | Indicator                   | Indicates when the count restart flip-flop is set.                                                    |

| 8      | CNT HOLD       | Indicator                   | Indicates when the count hold flip-flop is set.                                                       |

| 9      | RCVR FLAG      | Indicator                   | Indicates when the receiver flag flip-flop is set.                                                    |

| 10     | DATAO          | Indicator                   | Indicates when the DATAO flip-flop is set.                                                            |

| 11     | LINE RCVR      | Indicator                   | Indicates when the receiver flag of the data line selected by the line number switches is on.         |

| 12     | LINE TRAN      | Indicator                   | Indicates when the transmitter flag of the data line selected by the line number switches is on.      |

| 13     | LINE<br>NUMBER | 6 Indicators                | Indicates the data line number selected by the scanner in octal form.                                 |

| 14     | DTR DIS        | Toggle Switch               | When up, holds the data term ready one-shot in the one state.                                         |

| 15     | UNIT           | 8 Position Rotary<br>Switch | Selects a data line within the selected group.                                                        |

| 16     | GROUP          | 8 Position Rotary<br>Switch | Selects the desired group number.                                                                     |

| 17     | MAINT          | Toggle Switch               | When up, selects the maintenance mode.                                                                |

Figure 2-2 Power Control Panel

Table 2–2

Power Control Functions

| Number | Nomenclature     | Item              | Function                                                                                     |

|--------|------------------|-------------------|----------------------------------------------------------------------------------------------|

| 1      |                  | Indicator – White | Illuminated when 115 Vac or 230 Vac line power is applied.                                   |

| 2      |                  | Indicator – Red   | Illuminated when the line power is polarized wrong and when 230 Vac power is applied.        |

| 3      | 30 AMP           | Circuit Breaker   | Controls line power to the convenience outlets and the DC10D option and protects input line. |

| 4      | REMOTE/<br>LOCAL | Toggle Switch     | Selects the local mode or the remote mode.                                                   |

| 5      | POWER            | Toggle Switch     | Controls line power to the power supplies and the data line scanner system.                  |

# 2.3 OPERATING NOTES

In this section, operating notes are supplied to provide both operational and maintenance personnel with an understanding of the data line scanner operation. The information in this section is divided in the following manner: power application procedures during normal and maintenance operations are detailed; device selection for the data line scanner is discussed; and a brief description of the functions performed during the various I/O is provided.

# 2.3.1 Power Application

The application of power is controlled at the central processor's margin control panel when the following switches on the data line scanner power control(s) are placed in the following positions:

- a. The LOCAL/REMOTE switch in the REMOTE position.

- b. The POWER switch in the up position.

- c. The circuit breaker in the up position.

This is the normal placement of the switches.

To control the application of power at the data-line scanner power control during maintenance operation, the LOCAL/REMOTE switch is placed in the LOCAL position and the circuit breaker is left in the up position. Then, the POWER switch may be used to control the application of power, as desired.

### 2.3.2 Device Selection

The data line scanner is selected by the central processor under program control. Seven complementary pairs of signals representing IOS 3 through IOS 9 of the I/O bus are routed to the device selection option card in the DC10A. At the device selection option card, jumpers are normally inserted to provide a device number of 0101000 (240<sub>8</sub>). When this device number is routed to the option card via the I/O bus, the data line scanner is selected. Device number 240<sub>8</sub> is the standard device number for the data line scanner, but of course, it is possible to place the jumpers on the device option card so the data line scanner will respond to any device number. For additional information on device selection, refer to Section 2.5, Installation.

# 2.3.3 I/O Instruction

The data line scanner is designed to respond to the standard I/O instructions under program control. In the following table, each I/O instruction is identified and a brief summary of its functions is provided. The actual function of each instruction is dependent upon programming. Refer to Section 2.4, Programming Notes, for a general reference to data-line scanner programming.

# Instruction

CONO (Conditions Out)

# **Functions**

A transfer of data from the central processor to the data line scanner may perform one or more of the following:

- 1. Clear the data line scanner

- 2. Set the data terminal ready one-shot

- 3. Reset the scanner counters

- 4. Load the PI channel number into the PI storage register.

### Instruction

# CONI (Conditions In)

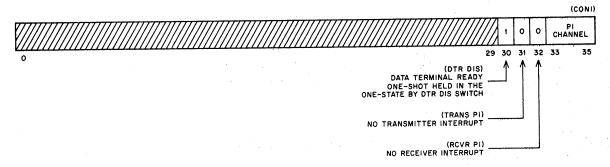

### **Functions**

Transfer of conditions from the data line scanner to the central processor indicates the following:

- 1. The position of the data terminal ready disable (DTR DIS) switch.

- 2. The presence of a transmitter interrupt

- The presence of a receiver interrupt

- 4. The data-line scanner PI channel number

#### DATAO (Data Out)

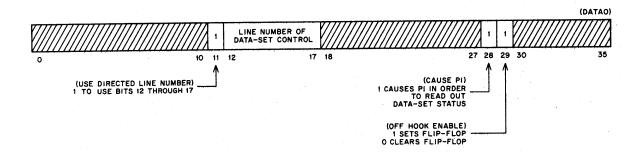

A transfer of data from the central processor to the data line scanner may perform one or more of the following:

- 1. Select a data line number

- 2. Transmit data to an idle data line

- 3. Transmit data to an interrupting data line

- 4. Clear a transmitter flag without sending data

- 5. Cause a program interrupt

- 6. Cause the off-hook enable flip-flop to change states

- 7. Cause a data-set to request a dial tone

- 8. Indicate the presence of a digit

- 9. Identify the digit to be dialed

#### DATAI (Data In)

A transfer of data from the data line scanner to the central processor will transfer the following:

- 1. The interrupting data line number

- The presence of active data

- 3. A 5-bit or 8-bit character transfer or data line status word

# 2.4 PROGRAMMING NOTES

## 2.4.1 Introduction

The DC10 Data Line Scanner interfaces up to 64 teletypewriter-like stations to the PDP-6 or PDP-10 computer. The DC10 Data Line Scanner accommodates any device which uses 5-level or

Programming notes are effective as of September 22, 1967.

8-level, serial start-stop codes at speeds up to 100 kilobaud. Full-duplex, full-duplex with local copy (the usual switched network configuration), and half-duplex data line modes are available on each line serviced. Send-only and receive-only (simplex mode) stations are also accommodated. Each data line serviced can be connected for any of three signalling speeds.

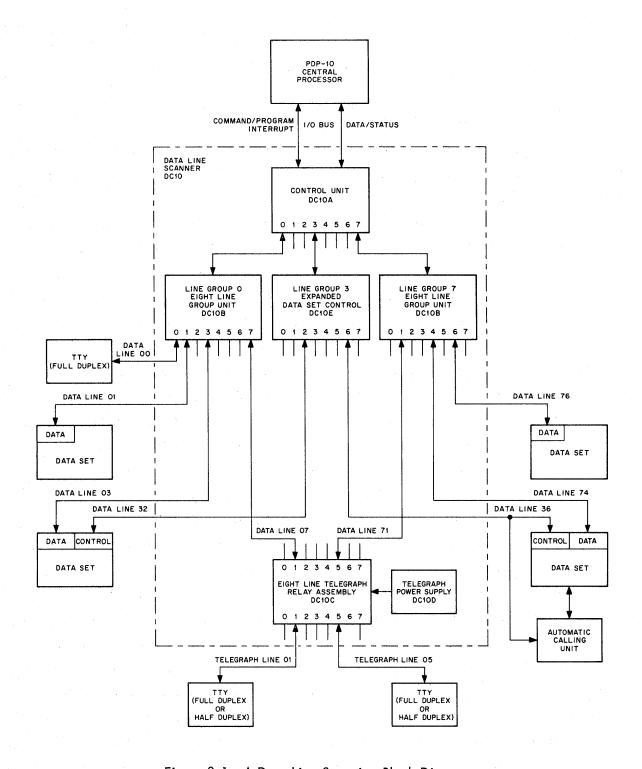

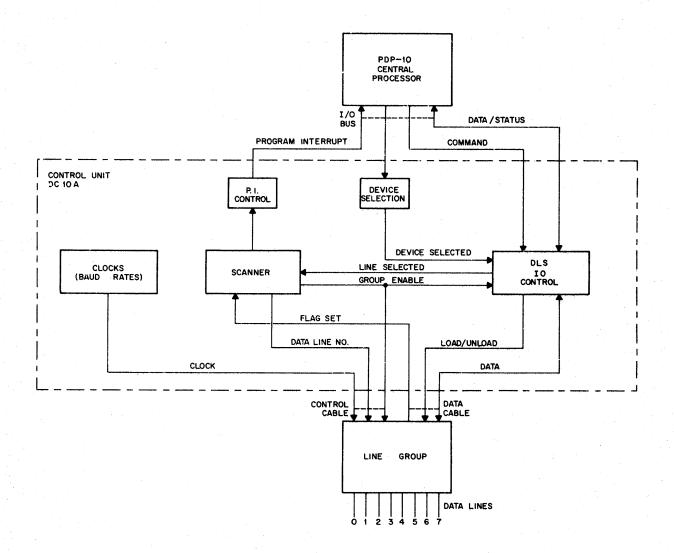

The DC10 Data Line Scanner is constructed "building-block" style out of modularly functional units. Figure 2-3 shows the block diagram of a typical DC10 installation. The DC10A provides a 64-line scanner and the I/O bus interface for the data line scanner and also provides cabinet space and power supplies for the other units of the data line scanner.

The DC10B provides eight lines of serial-parallel conversion and data-line interfaces for both EIA standard RS-232-B<sup>1</sup> signaling and 20 mA full-duplex local loops. The EIA interface is provided for data-sets and Model 37 Teletype machines. The 20 mA local loops are provided for Model 28, 33, and 35 Teletype machines and other compatible equipment.

The DC10C Telegraph Relay Option provides interface conversion for long lines and/or electrically "dirty" environments; half-duplex capability is also provided by this option. The DC10D Telegraph Power Supply is a high voltage power supply used with one or more DC10C options. Both the DC10C and DC10D are invisible to the programmer except that the DC10C provides half-duplex capability for the DC10B.

Data-sets such as those used in the Dataphone, TWX, and Telex systems can be used directly with the DC10B with manual data-set control. The DC10E provides the computer with control over these data-sets. This option allows positive automatic control over the data-sets which is frequently useful in multi-user timesharing systems with switched network access. The DC10E provides control of eight data-sets and two associated automatic calling units.

The DC10F provides the additional cabinet space and power supplies required in expanded systems. It is invisible to the programmer.

The DC10 Data Line Scanner requires one I/O device number (standard: 240<sub>8</sub>; mnemonic: DLS) and provides program interrupts on one PI channel. Although all data, status, and control are passed through the DC10A, the various aspects of programming are described in the various hardware-option oriented sections which follow.

# 2.4.2 DC10A Programming

The scanner in the DC10A continually monitors the eight possible 8-line groups (or expanded data-set controls) until it finds a group or control with a flag that is raised. The scanner then scans through the selected group or control, looking for the data line number (which may represent a data-set's

<sup>&</sup>lt;sup>1</sup> "Interface between Data Processing Terminal Equipment and Data Communication Equipment"

Figure 2-3 DC10 Block Diagram

status bits) which has its flag raised. When the scanner finds a line number requiring attention, it stops and causes a program interrupt on the PI channel assigned to the data line scanner. The maximum time required to find the next flag after having serviced a data line is approximately 20  $\mu$ s.

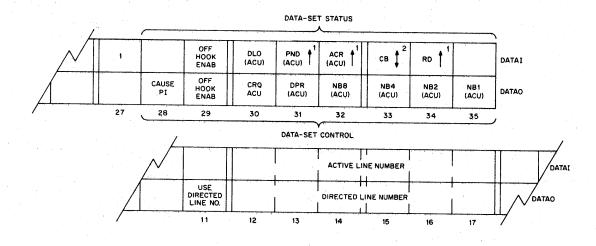

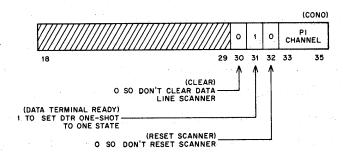

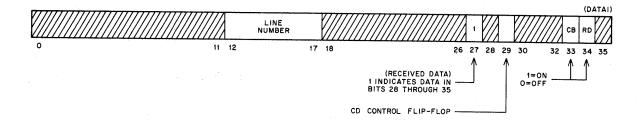

The data line scanner control register is shown in Figure 2-4. A CONO to the data line scanner performs the following functions: bits 33 through 35 are loaded into the PI channel register and are used to determine what channel a PI will occur on; bit 32, when 1, resets the scanner to line number 00, thus providing higher priority for lower numbered lines than for higher numbered ones; bit 31, when 1, sets the data terminal ready one-shot used for data-set control. See Section 2.4.4 for details of data terminal ready operation. Bit 30, when a 1, clears the entire data line scanner system in exactly the same fashion as I/O reset does. It clears the PI channel register, clears the PI flip-flop and initializes all DC10B and DC10E registers, thus clearing all waiting or partially processed characters.

Figure 2-4 DC10A Control and Status

The data line scanner status bits are shown in Figure 2-4. Bits 33 through 35 indicate the setting of the PI channel register; bit 32 = 1, if the scanner is at a line which has its receiver flag raised; bit 31 = 1, if the scanner is at a line which has its transmitter flag raised; bit 30 = 1, if the disable data terminal ready switch is on.

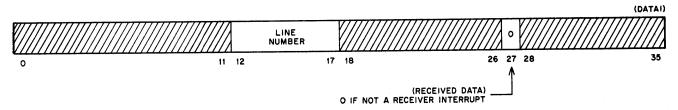

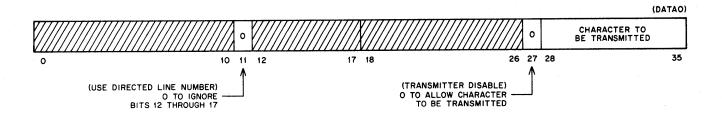

The left-half (bits 11 through 17) of the DATAO and DATAI data contains line number information used in conjunction with the data in the right-half while programming the DC10B and DC10E. See succeeding sections for details.

### 2.4.3 DC10B Programming

Each DC10B provides serial to parallel and parallel to serial conversion for eight serial-data lines. Each line can be connected for one of the three data speeds provided in the DC10A. Each line may be connected for 5-bit or 8-bit asynchronous start-stop code and may be provided with 1 unit, 1-1/2 unit, or 2 unit stop codes and full- or half-duplex options. Each line uses a 20 mA local-loop interface or an EIA interface. The only options which affect programming are the 5-bit or 8-bit option and the half- or full-duplex option. The 8-bit full-duplex option will be treated in detail. The other cases will be treated as variations of this case. The DC10 is designed to minimize the number of central processor instructions required to service it. To achieve this, the data line number and the corresponding data are handled together in the left and right halves of the data words. Figure 2-5 details the bit configurations for DC10B operation. Several different operations are necessary in servicing teletypewriter lines, they are the following.

- a. transmit a character on a presently idle line,

- b. transmit a character on an active line (which is ready for its next character),

- c. deactivate an active transmitter line (turn off its flag without sending another character),

- d. read in a received character.

The heart of the DC10B is the teletype transmitter and teletype receiver modules provided with each line.

Data are loaded into the teletype transmitter module and, if the disable bit is not on, sent out in serial fashion as a proper teletypewriter code. When the transmitter has finished serializing

the data, it turns on its flag for the scanner to see. When the scanner reaches the transmitter's line number, it stops and causes a PI. When additional data is loaded into the transmitter module, its flag is turned off and it starts to send out the serial data. Loading the transmitter module with the disable bit on will clear the transmitter flag without sending out additional data.

Figure 2-5 DC10B Data

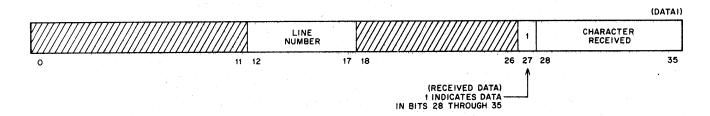

The receiver module gathers serial data until it has received a full character, at that time it raises its flag for the scanner to see. When the scanner reaches the receiver's flag, it stops and causes a PI. Reading the data from the receiver module clears the receiver flag.

To transmit on an idle line, the instruction

DATAO DLS, CHARWD

may be executed, where CHARWD contains

The 1 in bit 11 causes the line number in bits 12 through 17 to be used in place of the scanner register's line number for loading the transmitter module. The scanner is not loaded with bits 12 through 17, instead it continues scanning and resumes looking for lines requiring service after the instruction is finished. If the line specified is not idle, the character transmitted will be garbled.

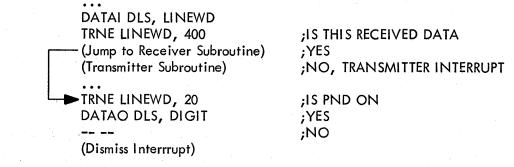

When the transmitter is finished sending a character to the data line (9.5 units after it started), it raises its flag. The scanner stops at the flag and sends a PI request to the central processor. To send another character, the PI may be serviced by

DATAI DLS, LINEWD

TRNE LINEWD, 400

(Jump to Receiver Subroutine)

;DATA INTO AC LINEWD ;IS THIS RECEIVED DATA

;YES

(Look up next character)

;NO, TRANSMITTER INTERRUPT

DATAO DLS, CHAR

;LOAD NEXT CHARACTER INTO TRANSMITTER

(Dismiss interrupt)

LINEWD will contain

#### CHAR should contain

The DATAO will turn off the transmitter's flag (releasing the scanner) and allow the transmitter module to transmit the new character serially.

To maintain maximum speed on a line, the new character must be loaded within  $\mathsf{T}_{_{\mathsf{L}}}$  where

$$T_t = \frac{\text{Number of stop units - } 1/2}{\text{line speed (baud) or units (bits) per second}}$$

seconds

NOTE: A CONI (or CONSO or CONSZ) servicing a PI request will indicate the state of the transmitter and receiver flag. After a PI request is made by the data line scanner, a receiver flag is not allowed to come up, if not already up, until after the PI request is serviced (or I/O reset occurs). This means that if only a transmitter is found with a CONI servicing a PI request, the right halfword data of the DATAI will be 0. If a receiver flag is found with a CONI servicing a PI request, the right halfword data of the DATAI will contain 1 in bit 27 and the character received in bits 28-35. If both a transmitter and receiver flag are on, the receiver flag takes precedence.

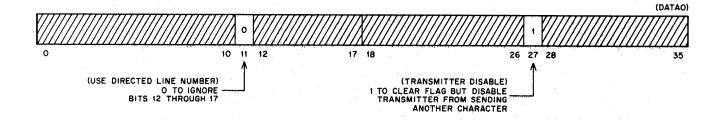

To turn off a transmitter flag, and thus release the scanner, without transmitting another character the DATAO DLS, CHAR should be replaced by DATAO DLS, NOCHAR where NOCHAR contains:

When a receiver module receives a complete character (in the middle of the eighth data bit), it raises its flag. The scanner stops at the flag and sends a PI request to the central processor. The received data is read into the central processor by

DATAI DLS, LINEWD ;DATA INTO AC LINEWD

TRNE LINEWD, 400 ;IS THIS RECEIVED DATA

(Store Character) ;YES

(Transmitter Subroutine) ;NO, TRANSMITTER INTERRUPT

...

(Dismiss Interrupt)

LINEWD will contain

The receiver flag is turned off by this DATAI. To avoid garbling a character, receivers must be serviced within  $T_r$ , where

$$T_r = \frac{\text{Number of stop units} + 1/2}{\text{line speed (band or units (bits) per second)}}$$

seconds

If a data line scanner has many lines, or lines running at different speeds, each PI must be serviced within the  $T_r$  of the highest speed line to avoid "hanging" the scanner and losing data. Even though a PI is not serviced within  $T_r$  and the character is garbled, the DATAI must be done in order to clear the receiver module flag so that the end of the next character can be detected.

Operation of a line with 5-bit teletypewriter codes is identical to that with 8-bit codes except that bits 28 through 30 of DATAI and DATAO data words no longer carry information.

Operation of a line in full-duplex with local copy mode does not effect programming except that the transmitter module will not start transmitting a character until the associated receiver module is idle, in order to avoid garbled copy at the teleprinter. Hence, transmitter PIs may occur less frequently.

Operation of a line in the half-duplex mode is essentially identical to full-duplex operation. (The DC10C Telegraph Relay Option is required, of course.) However, any time a character is transmitted, it will subsequently be received by the receiver module associated with the same line. The received character should be checked by the program to see if it matches the transmitted character. If it does not, either a line error has occurred or the keyboard of the teletypewriter has been struck. This condition is often used to interrupt program output. A line's transmitter and receiver will both cause interrupts at the end of a character. The receiver PI request will occur one unit before the transmitter PI request. If a character is sent to the transmitter of a half-duplex line while its receiver is active, the transmitter will wait until the receiver has finished before starting to transmit. Thus a character may be loaded into the transmitter module at any time without garbling the character presently being received. (It may, however, garble the next character received.)

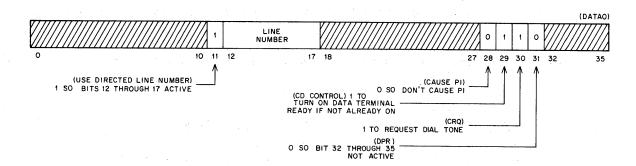

# 2.4.4 DC10E Programming

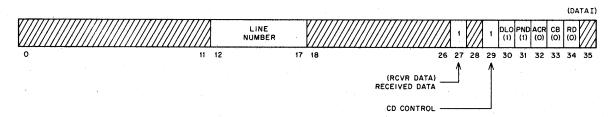

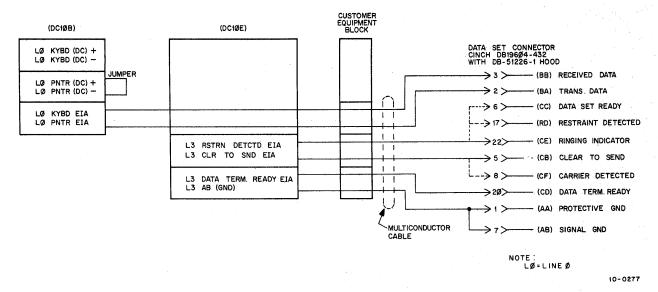

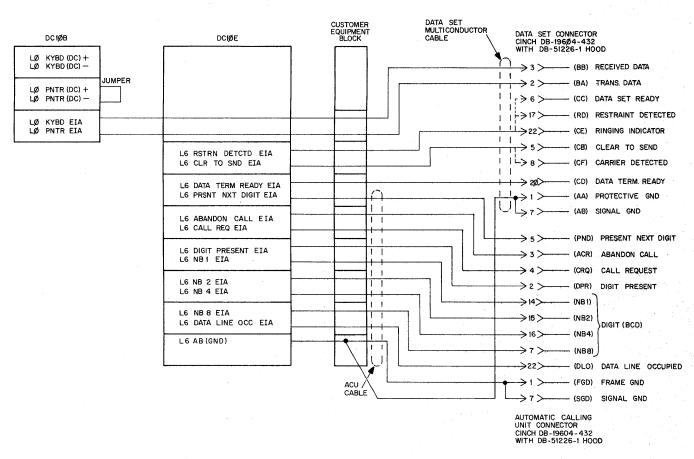

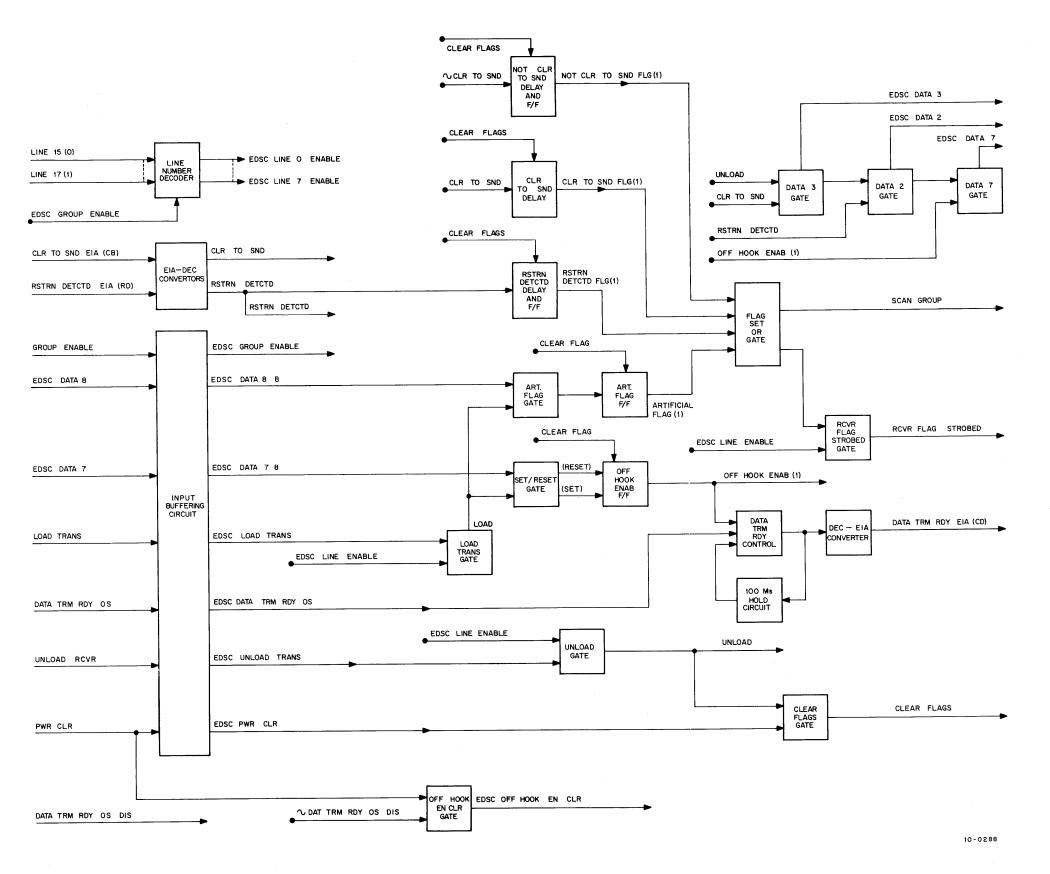

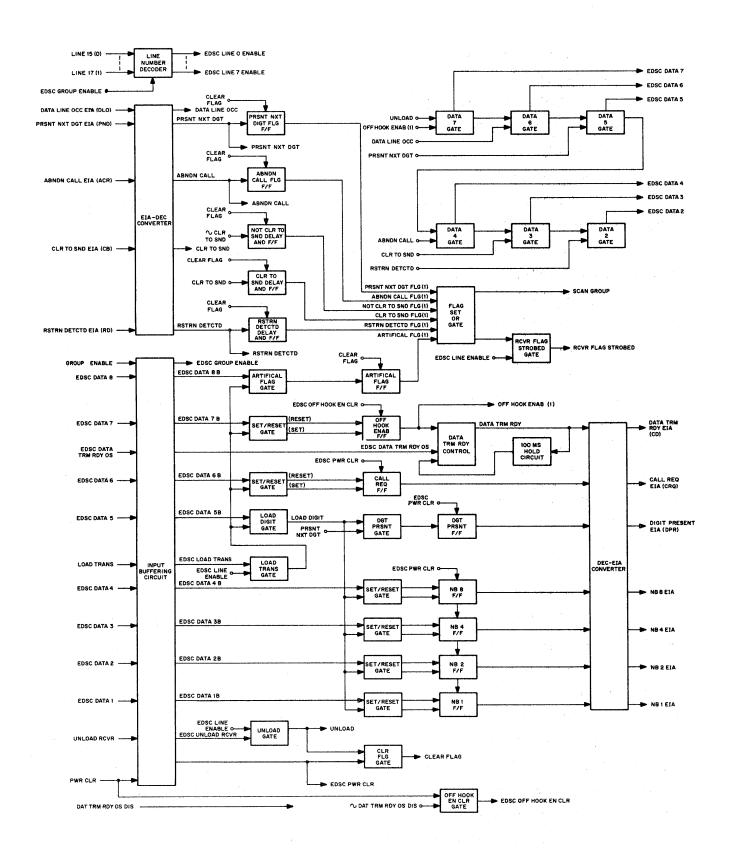

The DC10E Expanded Data-Set Control provides computer supervision of the control functions of the more common types of data-sets. A data set connected to a DC10E then has two line numbers assigned to it: the data line number to the DC10B and the control line number to the DC10E. Provision for two automatic calling units is included in each DC10E. The DC10E uses a control interface which conforms to EIA standard RS-232-B. Data-set status and control bits appear in the same bits of the I/O data words as characters from the DC10B. On the six lines (0 through 5) of the DC10E which are provided with data-set control only, the Clear to Send (CB<sup>1</sup>) and Restrain Detected (RD) signals are provided

Two and three letter abbreviations (CD, RD, DLO etc.) are the signal lead names in the data set technical manuals.

to the data-set. On the two lines provided for control of automatic calling units, Data Line Occupied (DLO), Present Next Digit (PND), and Abandon Call and Retry (ACR) are provided from the automatic calling unit (ACU) in addition to CB and RD from the associated data-set. The signals Call Request (CRQ), Digit Presented (DPR) and NB8, NB4, NB2, and NB1 (binary-coded decimal digit to be dialed) are provided to the automatic calling unit in addition to CD which is provided to the data-set. Figure 2-6 details the bit configuration for the DC10E. As the data-set control information need not be retransmitted periodically, the data-set control never causes a transmitter interrupt. Similarly, the data-set status tends to remain constant for long periods of time. Therefore, only the more meaningful status bit transitions set the data-set status flag (receiver flag). The scanner stops at the data-set status flag and causes a PI request. In order to read out the status of a data-set whose flag is not set, a bit in the data-set control register causes the flag to be set artificially so that the scanner will stop the next time the line is scanned to allow the status to be read out.

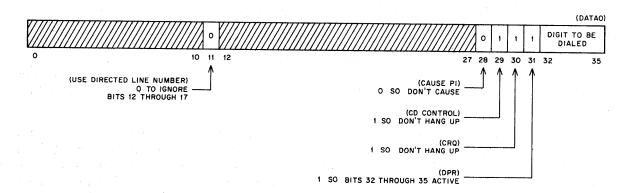

Figure 2-6 DC10E Data

Data sets respond to their CD (data terminal ready) lead, as follows. Whenever the dataterminal ready signal is false, the data set is inactive; if the data terminal ready signal is true, the data-set answers an incoming call or allows an outgoing call to be completed. When data terminal ready goes from true to false, the data-set will break its connection and hang up. Data terminal ready control is provided in the DC10 in two stages. The DC10A contains an integrating one-shot which must

The "ON" transitions set the flag . The "ON" and "OFF" transitions set the flag .

be kept in the 1 state by a CONO instruction every 500 ms. Use the instruction CONO DLS, DTRWD ;SET DATA TERM READY

where DTRWD is as follows:

This feature may be eliminated for software debugging purposes by throwing the DTR DIS switch UP on the indicator panel of the DC10A. The DTR DIS switch holds the data terminal ready one-shot in the one state indefinitely and inhibits clearing of the off hook enable flip-flop by IOB RESET or by a CONO with bit 30 a 1.

The status of the DTR DIS switch can be determined with a CONI:

CONI DLS, CONIWD

where CONIWD will be:

Each data-set line is equipped with an off hook enable flip-flop. When this flip-flop is in the 1 state and the data terminal ready one-shot is in the 1-state, the CD lead to the data set is ON. If the CD lead goes OFF, it is held off for 100 ms to insure that the data set disconnects properly.

A data-set only line is controlled by:

DATAO DLS, DSWD

where DSWD is as follows:

The off hook enable flip-flop may be cleared and set in successive instructions in order to disconnect a call and then allow the data-set to automatically answer another call.

The state of the off hook enable flip-flop can be read out by a DATAI after the data-set flag has been raised. Two other bits of status are also read out. Clear to Send (CB) indicates that the data-set has shaken hands with another data-set and data may be transmitted. In the TWX system, and some other switched network systems, however, the transmission of data should wait until after the receipt of an "answerback" code from the called station if the call was originated at the computer end. If no answerback code appears within a few seconds, the call should probably be disconnected by using the off hook enable flip-flop described previously (switched network only). When answering a call in switched network systems, the computer may be required by the carrier's tariffs to send an answerback code when CB (clear to send) comes ON. When CB goes OFF, the data connection has been broken, either by the distant party disconnecting or by the connection being otherwise broken. Both the ON and OFF transitions of CB (clear to send) raise the data-set control line's receiver flag. Under some conditions the program may have to hang-up the local data-set (see DC10E special application notes below).

In switched network (TWX) service, a 4-row (100 or 150 word per minute) station (such as the computer/data-set conbination) may be connected to a 3-row (60 word per minute) station through an intermediate translator. In these or similar situations, a Restrain Detected (RD) signal informs the computer that the intermediate translator buffer is full and will not receive any more characters. The computer must stop sending until the restrain detected signal goes OFF again, or the translator will disconnect the data circuit. The ON transition of the RD (restrain detected) signal raises the data-set line's receiver flag.

Read the data-set status after a flag has been raised (artificial or other) by

DATAI DLS, LINEWD

TRNE LINEWD, 400

(Jump to receiver rubroutine)

(Transmitter subroutine)

(Transmitter subroutine)

(Must not be a data-set control)

(Dismiss Interrupt)

In switched network operations it is convenient to have the computer originate data calls. The DC10E provides control for two automatic calling (dialing) units (ACU's) in line positions 6 and 7. The automatic calling units are operated as follows. With the CD (data terminal ready) lead ON to the data-set, the CRQ (call request) lead to the automatic calling unit is turned ON. This picks up the telephone line and requests a dial tone. When the dial tone is received, the DLO (data line occupied) and PND (present next digit) lines come ON. Now the first digit of the number to be dialed is set up and transmitted as NB8 through NB1 with DPR (digit present) indicating that NB8 through NB1 are active. Each digit is loaded after PND comes ON. If a data connection is not established within 7 to 40s after the last digit (or if any other step is not completed within this time) (adjustable on the ACU) the ACR (abandon call and retry) line comes ON. The computer should turn OFF the CRQ (call request) line until the DLO (data line occupied) signal goes OFF (several seconds) and then retry the call. ON transitions of PND (present next digit) and ACR (abandon call and retry) raise the data-set line's receiver flag. The CRQ (call request) line may be turned OFF after CB (ready to send) is ON if the data set is strapped properly. All of the above ACU flip-flops are cleared by power clear. Request a dial tone by

#### DATAO DLS, DIALRQ

where DIALRQ contains:

When the data-set line's flag is raised, do:

LINEWD will contain:

The DATAO sends the next digit to the automatic calling unit of the line interrupting. DIGIT should contain:

All of the above assume that the data-set and automatic calling units are equipped with the following options.

Automatic Answer (Data-Set)

Respond to Disconnect (Data-Set)

Long Space Disconnect (Data-Set)

Timer Stops upon Answer (Y Option) (ACU)

Drop CRQ after Answer (Z Option) (ACU)

Transfer to Data Set upon Answer (ACU)

Numerous other options are available and may be required for a particular type of service. For details, see, for example, Bell System Data Communications Technical Reference Manuals -- Station Arrangements to Provide TWX Service for Customer Provided Terminals (Data Auxiliary Set 811B); Data Auxiliary Set 801A (Automatic Calling Unit); Data Auxiliary Set 801C (Automatic Calling Unit); Data Set 103A etc., all Interface Manuals -- Data and Teletypewriter Planning Engineer, American Telephone and Telegraph Company or the equivalent interface manuals for other data-sets contemplated.

2.4.4.1 DC10E Special Application Notes - The exact signal from the data-set which is used by the DC10E is a function of the particular data-set and the circumstances in which the DC10E is used. When the DC10E is used with low speed (less than 300 baud) data sets (Bell System 103A, 811B, etc), the clear-to-send (CB) and carrier detector (CF) signals from the data-set are the same signal and either signal may be used to indicate to the DC10E that a data connection is established. In higher speed (1000-2000 baud) data sets (Bell System 202C, 202D, etc), the clear-to-send (CB) signal provides relatively little information whereas the carrier detected (CF) signal provides a meaningful indication that a data connection has been established.

In the low-speed case, the DC10E lead marked CLR TO SND EIA may be connected to either the CB or CF signal in the data-set. In the higher-speed case, the CLR TO SND EIA lead from the DC10E should be connected to the CF signal in the data set.

The DC10E lead marked RSTRN DETCTD EIA may be used to solve problems in the following three cases.

- a. In 4-row TWX service, it should be connected to the RD lead of the data-set as described in the 811B manual ("Station Arrangements To Provide TWX Service For Customer-Provided Terminals (Data Auxiliary Set 811B) Interface Specifications Preliminary" November 1965) and detailed in DC10E programming.

- b. In normal data-set service, the data-set may fail to hang up when called by a non-data-set telephone subscriber. In this case, either the data-set ready (CC) or ringing indicator (CE) signals may be connected to the RESTRN DETCTD EIA lead to allow the program to hang up the data-set (place it "on-hook") after a period of time with no carrier detected. (See the "Data Set 103A Interface specification," February 1967.) This arrangement is required only when certain types of Bell System equipment are servicing the data set (e.g., some types of dial foreign exchange equipment).

- c. In an installation, it may be desired to have the program "answer the phone" when someone calls a data-set rather than allowing the data-set to answer automatically. In this case, the ringing indicator (CE) signal is connected to the RSTRN DETCTD EIA lead from the DC10E. When this signal becomes true, the program can (selectively, if desired) enable the DATA TERM READY EIA signal and allow the data-set to answer as described in the DC10E programming.

If the ringing indicator (CE) signal is used, features (b) and (c) can both be used. If none of these features using the RSTRN DETCTD EIA signal are desired, the RSTRN DETCTD EIA lead from the DC10E should be connected to a negative voltage of between -3V and -25V to maintain the signal OFF. A source of negative voltage is usually available at pin 10 of the data-set connector.

# 2.4.5 Maintenance Mode

When the MAINT switch is ON (UP), all scanner PI requests are inhibited and all I/O instructions addressed to the data line scanner are ignored. This effectively disconnects the data line scanner from the I/O bus. The only I/O bus function which is active in the MAINT mode is IOB RESET. In the MAINT mode, any character typed in from a teletypewriter will be echoed back to that teletypewriter. This feature serves as a gross check on the operation of the data line scanner and enables the checking of the teletypewriter circuits without the aid of the computer. Data terminal ready is false when the data line scanner is in the MAINT mode.

NOTE: DATAI clears PI only if RCVR interrupt. DATAO clears PI unless IOB 12 (directed data) is 1. If simultaneous RCVR and TRANS interrupt occurs, the PI is cleared by DATAI but reappears within 1.8 µs, due to the TRANS interrupt.

# CHAPTER 2A INSTALLATION

This section contains general information on the DLS installation. Cross-connecting and cable terminating guidelines are provided as an aid to installation and installation planning. Option adjustments are required during installation because the DLS equipment contains a number of optional features. Guidelines for these option adjustments are explained under option card adjustments. Since actual installation procedures vary for each system, the information in this section is written in general terms and is intended as a guide for equipment installation.

# 2A.1 Cross Connecting and Cable Terminating Guidelines

The data lines of the DLS are interfaced at the quick-connect type terminal blocks located on the inside of the rear plenum door of the DC10A and DC10F. In either case, there are two rows of four connecting blocks in each cabinet. The connecting blocks in the upper row are called the line group terminals and are used to terminate the interface lines of the DC10B 8-Line Group Units, the DC10C Telegraph Relay Assembly, or the DC10E Expanded Data Set Control. The connecting blocks in the lower row are called the external cable terminals and are used for terminating external and intercabinet cables. The recommended external cable used to connect teletypes to the DLS is a 25-pair inside telephone cable of either 22 or 24 gage wire. It is terminated at the external cable terminals. When a data line located in one cabinet is connected to a cable terminated in another cabinet, an intercabinet cable is connected between the two cabinets and is terminated at the external cable terminals.

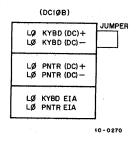

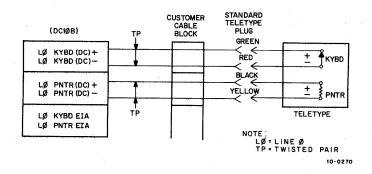

To prevent a DC10B line from receiving continuous space and interrupting with the character NULL  $(0_8)$ , the "running open" condition, a jumper must be installed across the DC10B KYBD (DC) + and KYBD (DC) - terminals when no other wiring is present for a given line. To provide EIA printer signals, it is necessary to jumper the PRNTR (DC) + and PRNTR (DC) - terminals to activate the EIA printer output circuit. These jumpers may be inserted on the appropriate line group terminals. Refer to Table 2A-1 to obtain wire color to line name correspondence.

To connect a data line to a telephone cable, the necessary "cross-wire" pairs are installed between the line group terminals and the external cable terminals. Figure 2A-1 shows examples of typical wiring configurations.

Table 2A-1 Wire Color to Line Name Cross Reference Chart

| Wire<br>Color   | DC1ØA (To DC1ØB)                   | See<br>Note | DC1ØA (DC1ØC-LOCAL)      | DC1ØA (DC1ØC-LINE)       | DCIØA (To DCIØE)                                |

|-----------------|------------------------------------|-------------|--------------------------|--------------------------|-------------------------------------------------|

| White           | LØ KYBD (DC) +                     | 1           | LØ KYBD +                | LØ KYBD +                | LØ RSTRN DETCTD EIA (RD)                        |

| Blue            | LØ KYBD (DC) -                     |             | LØ KYBD -                | LØ KYBD -                | LØ CLR TO SND EIA (CB)                          |

| White           | LØ PRNTR (DC) +                    | 2           | LØ PRNTR +               | LØ PRNTR +               | LØ DATA TRM RDY EIA (CD)                        |

| Orange          | LØ PRNTR (DC) -                    |             | LØ PRNTR -               | LØ PRNTR -               | LØ AB (GND)                                     |

| White           | LØ KYBD EIA                        | -           | N/C                      | N/C                      | L1 RSTRN DETCTD EIA (RD)                        |

| Green           | LØ PRNTR EIA                       |             | N/C                      | N/C                      | L1 CLR TO SND EIA (CB)                          |

| White           | L1 KYBD (DC) +                     | 1           | L1 KYBD +                | L1 KYBD +                | L1 DATA TRM RDY EIA (CD)                        |

| Brown           | L1 KYBD (DC) -                     |             | L1 KYBD -                | L1 KYBD -                | L1 AB (GND)                                     |

| White           | L1 PRNTR (DC) +                    | 2           | LI PRNTR +               | L1 PRNTR +               | L2 RSTRN DETCTD EIA (RD)                        |

| Slate           | L1 PRNTR (DC) -                    |             | LI PRNTR -               | L1 PRNTR -               | L2 CLR TO SND EIA (CB)                          |

| Red             | LI KYBD EIA                        | -           | N/C                      | N/C                      | L2 DATA TRM RDY EIA (CD)                        |

| Blue            | LI PRNTR EIA                       |             | N/C                      | N/C                      | L2 AB (GND)                                     |

| Red             | L2 KYBD (DC) +                     | 1           | L2 KYBD +                | L2 KYBD +                | L3 RSTRN DETCTD EIA (RD)                        |

| Orange          | L2 KYBD (DC) -                     |             | L2 KYBD -                | L2 KYBD -                | L3 CLR TO SND EIA (CB)                          |

| Red             | L2 PRNTR (DC) +                    | 2           | L2 PRNTR +               | L2 PRNTR +               | L3 DATA TRM RDY EIA                             |

| Green           | L2 PRNTR (DC) -                    |             | L2 PRNTR -               | L2 PRNTR -               | L3 AB (GND)                                     |

| Red             | L2 KYBD EIA                        | -           | M/C                      | Z/C                      | L4 RSTRN DETCTD EIA (RD)                        |

| Brown           | L2 PRNTR EIA                       |             | N/C                      | Z/C                      | L4 CLR TO SND EIA (CB)                          |

| Red             | L3 KYBD (DC) +                     | 1           | L3 KYBD +                | L3 KYBD +                | L4 DATA TRM RDY EIA (CB)                        |

| Slate           | L3 KYBD (DC) -                     |             | L3 KYBD -                | L3 KYBD -                | L4 AB (GND)                                     |

| Black           | L3 PRNTR (DC) +                    | 2           | L3 PRNTR +               | L3 PRNTR +               | L5 RSTRN DETCTD EIA (RD)                        |

| Blue            | L3 PRNTR (DC) -                    |             | L3 PRNTR -               | L3 PRNTR -               | L5 CLR TO SND EIA (CB)                          |

| Black           | L3 KYBD EIA                        | -           | N/C                      | N/C                      | L5 DATA TRM RDY EIA (CD)                        |

| Orange          | L3 PRNTR EIA                       |             | N/C                      | N/C                      | L5 AB (GND)                                     |

| Black           | L4 KYBD (DC) +                     | 1           | L4 KYBD +                | L4 KYBD +                | L6 RSTRN DETCTD EIA (RD)                        |

| Green           | L4 KYBD (DC) -                     |             | L4 KYBD -                | L4 KYBD -                | L6 CLR TO SND EIA (CB)                          |

| Black           | L4 PRNTR (DC) +                    | 2           | L4 PRNTR +               | L4 PRNTR +               | L6 DATA TRM RDY EIA (CD)                        |

| Brown           | L4 PRNTR (DC) -                    |             | L4 PRNTR -               | L4 PRNTR -               | L6 PRSNT NXT DGT EIA (PND)                      |

| Black           | L4 KYBD EIA                        | -           | N/C                      | N/C                      | L6 ABNDN CALL EIA (ACR)                         |

| Slate           | L4 PRNTR EIA                       |             | N/C                      | N/C                      | L6 CALL REQ EIA (CRQ)                           |

| Yellow          | L5 KYBD (DC) +                     | 1           | L5 KYBD +                | L5 KYBD +                | L6 DIGIT PRESENT EIA (DPR)                      |

| Blue            | L5 KYBD (DC) -                     |             | L5 KYBD -                | L5 KYBD -                | L6 NB1 EIA                                      |

| Yellow          | L5 PRNTR (DC) +                    | 2           | L5 PRNTR +               | L5 PRNTR +               | L6 NB2 EIA                                      |

| Orange          | L5 PRNTR (DC) -                    |             | L5 PRNTR -               | L5 PRNTR -               | L6 NB4 EIA                                      |

| Yellow          | L5 KYBD EIA                        | -           | N/C                      | N/C                      | L6 NB8 EIA                                      |

| Green           | L5 PRNTR EIA                       |             | N/C                      | N/C                      | L6 DATA LINE OCC EIA (DLO)                      |

| Yellow          | L6 KYBD (DC) +                     | 1           | L6 KYBD +                | L6 KYBD +                | L6 AB (GND)                                     |

| Brown           | L6 KYBD (DC) -                     |             | L6 KYBD -                | L6 KYBD -                | L7 AB (GND)                                     |

| Yellow<br>Slate | L6 PRNTR (DC) +<br>L6 PRNTR (DC) - | 2           | L6 PRNTR +<br>L6 PRNTR - | L6 PRNTR +<br>L6 PRNTR - | L7 RSTRN DETCTD EIA (RD) L7 CLR TO SND EIA (CB) |

| Purple          | L6 KYBD EIA                        |             | N/C                      | N/C                      | L7 DATA TRM RDY EIA (CD)                        |

| Blue            | L6 PRNTR EIA                       |             | N/C                      | N/C                      | L7 PRSNT NXT DGT EIA (PND)                      |

| Purple          | L7 KYBD (DC) +                     | 1           | L7 KYBD +                | L7 KYBD +                | L7 ABNDN CALL EIA (ACR)                         |

| Orange          | L7 KYBD (DC) -                     |             | L7 KYBD -                | L7 KYBD -                | L7 CALL REQ EIA (CRQ)                           |

| Purple          | L7 PRNTR (DC) +                    | 2           | L7 PRNTR +               | L7 PRNTR +               | L7 DIGIT PRESENT EIA (DPR)                      |

| Green           | L7 PRNTR (DC) -                    |             | L7 PRNTR -               | L7 PRNTR -               | L7 NBI EIA                                      |

| Purple          | L7 KYBD EIA                        | -           | N/C                      | N/C                      | L7 NB2 EIA                                      |

| Brown           | L7 PRNTR EIA                       |             | N/C                      | N/C                      | L7 NB4 EIA                                      |

| Purple          | GND                                |             | N/C                      | N/C                      | L7 NB8 EIA                                      |

| Slate           | GND                                |             | N/C                      | N/C                      | L7 DATA LINE DCC EIA (DLO)                      |

#### NOTES:

- Jumper wires together when line is not in use.

Jumper wires together when PRNTR EIA line is in use. N/C Not Connected

Figure 2A-1 Typical DC10 Cabling

Termination of cables and cross-wiring is performed using the 66A or 317B tool supplied with each system. This tool jams the wire onto the terminal and cuts off the excess wire. The wire is automatically stripped by the action of the quick connect terminals so that hand stripping is ordinarily unnecessary. When terminating wires, it is important to orient the tool so that it cuts the excess end of the wire rather than the conductor going to the cable.

The connecting blocks will accommodate unstripped 20- to 26-gage wire which may be removed and the terminal reused an indefinite number of times. Stripped 18-gage wire is also accommodated by the connecting blocks, but this size wire permanently deforms the terminal so that only 18-gage wire can be used on the terminal thereafter. To prevent the inadvertent use of a deformed terminal for smaller wire, all deformed terminals should be marked with a felt tipped pen to identify them.

The recommended cable is a commercial 24 gage, 25-pair inside telephone wiring cables such as that available from Graybar Electric Company or Automatic Electric Company (offices in principal cities of the U.S.A.) or from any large cable or telephone supplies manufacturer.

The standard color code for these cables is that shown in Table 2A-2. When a different color code is to be used, a cable pairing guide should be requested from the manufacturer. The tip and ring conductor notation used in Table 2A-2 comes from telephone switchboard usage. The tip conductor is always the topmost wire of the pair on the connecting block and is ordinarily the positive conductor of

the pair. Since keeping track of line-cable correspondence is a difficult and important job, a line assigner's book is provided with each DLS system.

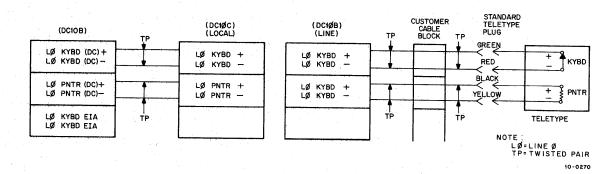

Examples of the most common cases of crosswiring are shown in Figure 2A-2.

A. Line Not in Use

B. Local Line – Current Mode – Full Duplex Model 33 or 35 Teletype

C. Long Line - Current Mode - Full Duplex

Figure 2A-2 Examples of Crosswiring

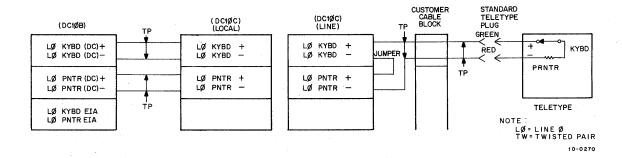

D. Long Line - Current Mode - Half Duplex

E. Local Line EIA - Model 37 Teletype

F. Local Line EIA - Western Electric 103A Data Set

Figure 2A-2 Examples of Crosswiring (Cont)

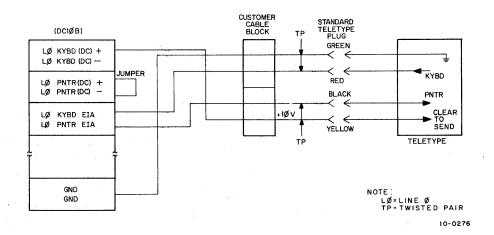

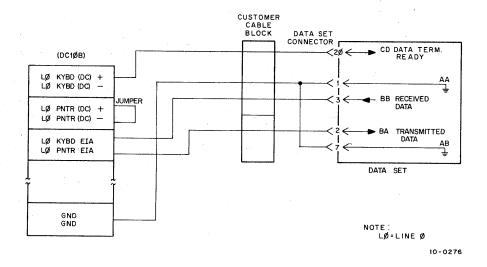

G. Connection to Data Set with DC10E (Bell System 103A, 202C, 202D, 811B, etc.)

10-0274

H. Connection to Data Set and Automatic Calling Unit (Bell System 8Ø1A, etc.)

Figure 2A-2 Examples of Crosswiring (Cont)

# 2A.2 Option Card Adjustments

DLS equipment has been designed with a number of optional features that can be used to adapt the DLS to fulfill varying user requirements. Due to this fact, a number of adjustments may be required at the time of installation or whenever system requirements are changed after installation. To simplify these adjustments, option cards have been inserted at the points where these adjustments are required. The following information explains the function of these cards and explains the adjustment procedure for each.

Table 2A-2

Cable Pairing Guide

| Pair<br>Number | Tip<br>Conductor | Ring<br>Conductor | Pair<br>Number | Tip<br>Conductor | Ring<br>Conductor |

|----------------|------------------|-------------------|----------------|------------------|-------------------|

| 1              | white            | blue              | 14             | black            | brown             |

| 2              | white            | orange            | 15             | black            | slate             |

| 3              | white            | green             | 16             | yellow           | blue              |

| 4              | white            | brown             | 17             | yellow           | orange            |

| 5              | white            | slate             | 18             | yellow           | green             |

| 6              | red              | blue              | 19             | yellow           | brown             |

| 7              | red              | orange            | 20             | yellow           | slate             |

| 8              | red              | green             | 21             | purple           | blue              |

| 9              | red              | brown             | 22             | purple           | orange            |

| 10             | red              | slate             | 23             | purple           | green             |

| 11             | black            | blue              | 24             | purple           | brown             |

| 12             | black            | orange            | 25             | purple           | slate             |

| 13             | black            | green             |                |                  |                   |

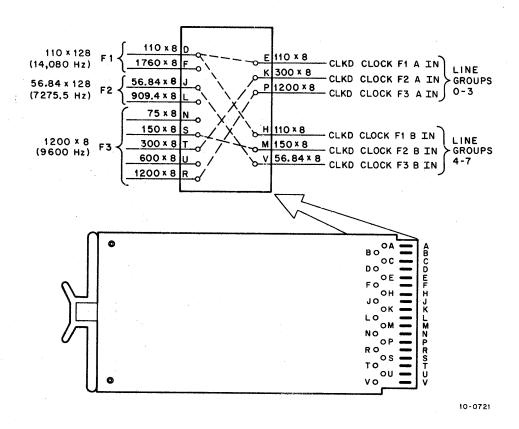

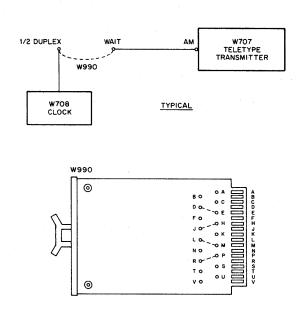

2A.2.1 <u>Clock Divider Option Card</u> - The Clock Divider Option Card (Type W990) is located in card slot D19 of the DC10A (see drawing D-BS-DC10A-0-CLKD). This option card is used to select the baudrate clock frequencies for baud rates between 40 baud and 100 kilobaud by connecting jumpers into various configurations among the input and output pins listed in Table 2A-3. The output clock frequency is eight times the baud rate. For rates of 40 to 999 baud, the required clock frequency is 128 times the baud rate (5.12 kHz to 128 kHz) and the clock frequency is divided by 16 (128 ÷ 16 = 8). When the

desired baud rate is between 1 kilobaud and 100 kilobaud, the clock frequency is divided by one to provide the required clock frequency of eight times the baud rate (8 kHz to 1.6 MHz).

The selection of the crystal frequency of the three clocks (F1, F2, and F3) can be varied by installing the desired value clocks in card slots D10, D11, and D12. When frequencies are not specified by the customer, the DC10A is supplied with clocks for 110 baud (Model 33 and 35 Teletypes), 150 baud (Model 37 Teletype), and 1200 baud (Western Electric Model 202 Data Set or equivalent).

By various jumper configurations, the W990 provides three line speeds common to groups 0-3 (signals CLKD CLOCK F1 A IN through CLKD CLOCK F3 A IN) and three potentially different speeds for groups 4-7 (signals CLKD CLOCK F1 B IN through CLKD CLOCK F3 B IN). In addition, a variety of speeds is made available by using Clock F3 to provide for frequencies based on powers-of-two multiples of the line's required baud rate. For example, if line groups 0-3 require speeds of 110, 300, and 1200 baud and line groups 4-7 require speeds of 110, 150, and 56.84 baud, the jumper connections are as shown in Figure 2A-3.

Table 2A-3

Clock Frequency and Jumper Connections

|       |               | Clock           |           | Jum  | per       |

|-------|---------------|-----------------|-----------|------|-----------|

| Clock | Baud Rate     | Frequency (kHz) | Divide by | From | То        |

| FI    | 40-999        | 5.12-128        | 16        | D    |           |

| (D1Ø) | 1,000-200,000 | 8-1,600         | 1         | F    |           |

| F2    | 40-999        | 5.12-128        | 16        | J    |           |

| (D11) | 1,000-200,000 | 8-1,600         | 1         | L    | See       |

|       | 40-999        | 5.12-128        | 16        | Z    | Note<br>1 |

| F3 [  | 1,000-200,000 | 8-1,600         | 1         | R    |           |

| (D12) | 80-1999       |                 | 8         | S    |           |

|       | 160-3999      | See Note 2      | 4         | T    |           |

|       | 320-7999      |                 | 2         | U    |           |

NOTE 1: The output pins are as follows:

| Groups Ø-3   |       |         | G       | roups 4-7 |         |         |

|--------------|-------|---------|---------|-----------|---------|---------|

| Clock Signal | FIAIN | F2 A IN | F3 A IN | FIBIN     | F2 B IN | F3 B IN |

| Pin          | Е     | К       | Р       | Н         | М       | V       |

NOTE 2: The clock frequency is based on divide-by-one, e.g., if F3 is 1200 baud (9600 Hz at pin R), pin U supplies 600 baud (4800 Hz), pin T supplies 300 baud (2400 Hz), and pin S supplies 150 baud (1200 Hz).

Figure 2A-3 Typical Jumper Configuration

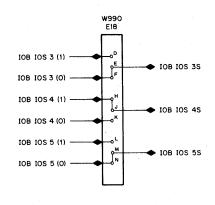

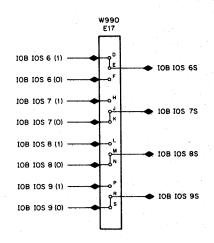

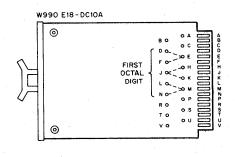

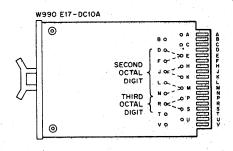

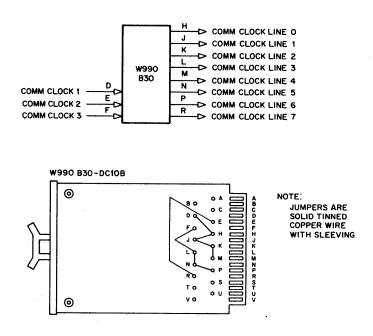

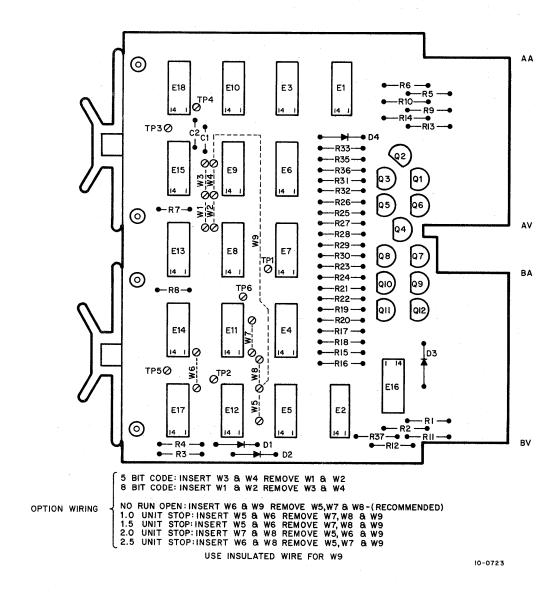

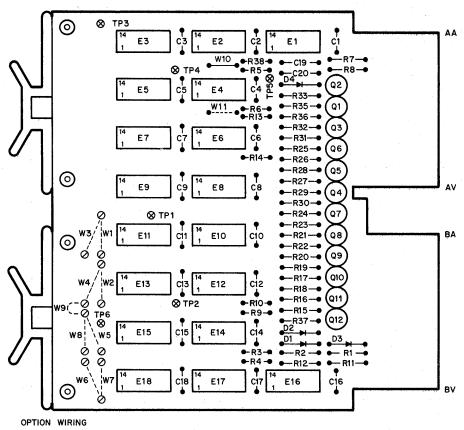

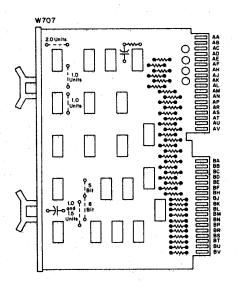

2A.2.2 Device Number Option Cards - The device numbers from the central processor are routed to all devices connected to the I/O bus via the 14 device-selection lines (7 pairs) of the I/O bus. In the DLS, the device selection lines are terminated at the device-number option cards located in slots E17 and E18 of the DC10A. Jumpers located on these option cards can be arranged so the DLS will respond to any device number. If a device number has not been specified by the customer, the jumpers on the device number option cards are connected so that the DLS will respond to the standard device number 240<sub>8</sub>. To prevent the DLS from responding to more than one device number, one jumper of each pair must always be connected.