PDP-11/45, 11/50, and 11/55 system maintenance manual

1st Edition, October 1972 2nd Printing, December 1972 3rd Printing, February 1973 4th Printing (Rev), April 1973 5th Printing, July 1973 2nd Edition, March 1974 7th Printing (Rev), October 1974 8th Printing (Rev), September 1976

Copyright © 1972, 1973, 1974, 1976 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## **CONTENTS**

|           |                                                          | Page       |

|-----------|----------------------------------------------------------|------------|

| CHAPTER 1 | GENERAL DESCRIPTION                                      |            |

| 1.1       | BASIC SYSTEM DESCRIPTION                                 | 1-1        |

| 1.1.1     | Physical Characteristics                                 |            |

| 1.1.2     | General Power Requirements and Electrical Specifications | 1_1        |

| 1.1.2.1   | Internal Option Power Requirements                       |            |

| 1.1.2.2   | Determining Option Power and Line Current Requirements   | 1-10       |

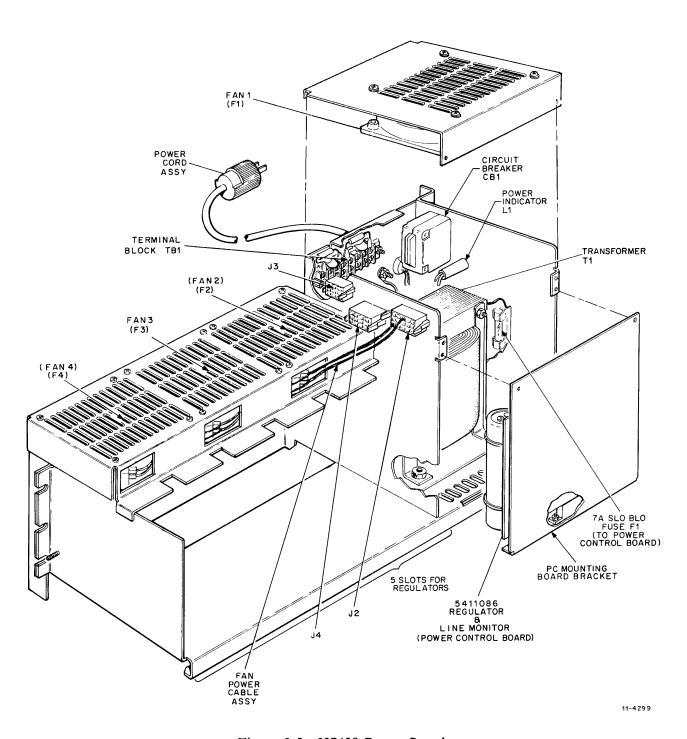

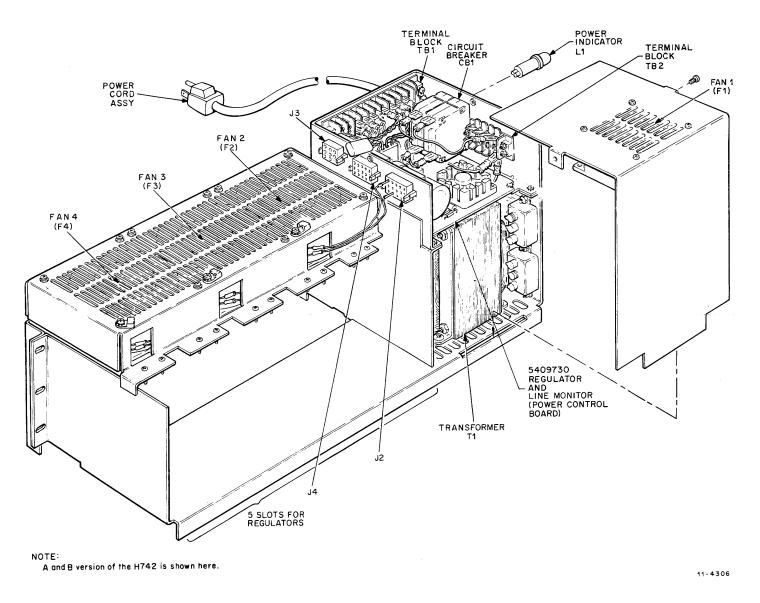

| 1.1.3     | H7420 Power Supply Characteristics                       |            |

| 1.1.4     | H742 Power Supply Characteristics                        | 1-11       |

| 1.1.5     | Voltage Regulator Characteristics                        |            |

| 1.1.6     | Interface Specifications                                 |            |

| 1.1.7     | Environmental Specifications                             |            |

| 1.2       | SYSTEM CONFIGURATIONS AND OPTIONS                        | 1-12       |

| 1.3       | EXPANSION CABINET OPTION                                 | 1-12       |

| 1.4       | REFERENCE DOCUMENTS                                      | 1-12       |

| 1.5       | ENGINEERING DRAWINGS                                     | 1-10       |

| 1.6       | DRAWING CONVENTIONS                                      | 1-23       |

| CHAPTER 2 | SYSTEM INSTALLATION                                      |            |

| 2.1       | GENERAL                                                  | 2-1        |

| 2.2       | SITE PREPARATION                                         |            |

| 2.2.1     | Physical Dimensions                                      |            |

| 2.2.2     | Fire and Safety Precautions                              |            |

| 2.2.3     | Environmental Requirements                               | 2-2<br>2-3 |

| 2.2.3.1   | Humidity and Temperature                                 |            |

| 2.2.3.2   | Air Conditioning                                         |            |

| 2.2.3.3   | Acoustical Damping                                       |            |

| 2.2.3.4   |                                                          |            |

| 2.2.3.5   | Lighting                                                 |            |

| 2.2.3.6   | Static Electricity                                       | 2-3        |

| 2.2.4     | Electrical Requirements                                  | 2-3        |

| 2.3       | INSTALLATION AND INSPECTION                              | 2-3        |

| 2.3.1     |                                                          |            |

| 2.3.2     | Unpacking                                                |            |

| 2.3.3     | Inspection                                               | 2-5        |

| 2.3.4     |                                                          |            |

| 2.3.5     |                                                          |            |

| 2.3.5.1   |                                                          |            |

| 2.3.5.2   | Unibus Connections                                       |            |

| 2.3.5.3   |                                                          |            |

| 2.3.5.4   | Ground Strapping                                         |            |

| 2.3.3.4   | Wire Trough Cabling                                      |            |

| 2.5       | INITIAL POWER TURN-ON                                    |            |

| 2.5.1     | SYSTEM CONFIGURATION TEST PROCEDURES                     | 2-8        |

| 2.5.2     | Special Test Equipment                                   |            |

| 4.3.4     | Preliminary Checks                                       | 2-9        |

|           |                                                  | Page |

|-----------|--------------------------------------------------|------|

| 2.5.3     | Detailed Procedure                               |      |

| 2.5.3.1   | RC Maintenance and Crystal Clock Test            | 2-9  |

| 2.5.3.2   | Microprogram ROM Cycle Test                      | 2-10 |

| 2.5.3.3   | Single Time Start Test                           | 2-10 |

| 2.5.3.4   | Single Time Step Test                            | 2-10 |

| 2.5.3.5   | Switch Register and Display Test                 | 2-11 |

| 2.5.3.6   | Internal Data Transfer Test                      | 2-11 |

| 2.5.3.7   | Register Deposit/Examine Test                    | 2-12 |

| 2.5.3.8   | I/O Data Transfer Test                           |      |

| 2.5.3.9   | Unibus Test                                      |      |

| 2.5.3.10  | Fastbus Test                                     |      |

| 2.5.3.11  | ALU Arithmetic Test                              |      |

| 2.5.3.12  | Unconditional Branch Test                        | 2-15 |

| 2.5.3.13  | Register-to-Register Data Move Test              | 2-16 |

| 2.5.3.14  | Move-Immediate-to-Register Test                  | 2-16 |

| 2.6       | CUSTOMER ACCEPTANCE                              |      |

| CHAPTER 3 | POWER SYSTEM                                     |      |

| 3.1       | OVERALL SYSTEM DESCRIPTION                       | 3-1  |

| 3.2       | 115 Vac AND 230 Vac MODELS                       |      |

| 3.3       | DIFFERENT POWER SYSTEM VERSIONS                  | 3-5  |

| CHAPTER 4 | AC POWER DISTRIBUTION                            |      |

| 4.1       | PRIMARY AC POWER OUTLETS                         | 4-1  |

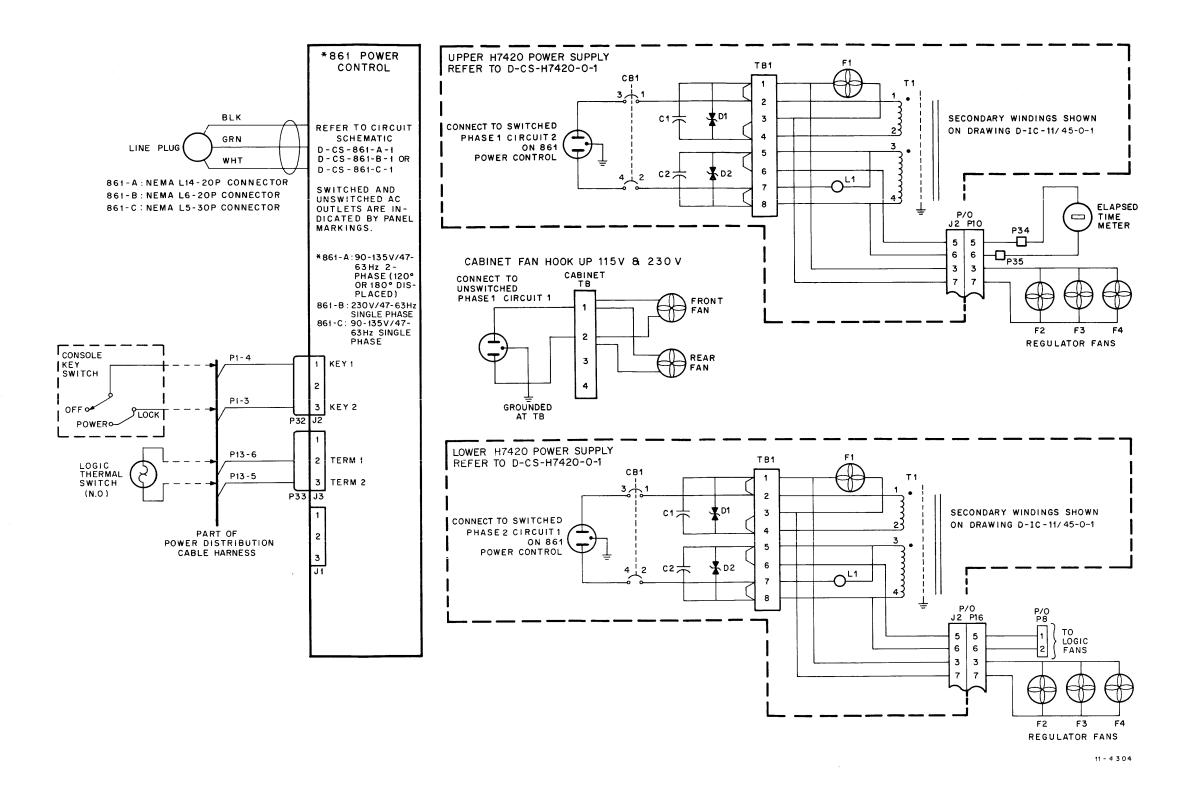

| 4.1.1     | Primary AC Power Outlets, 861 Power Control      |      |

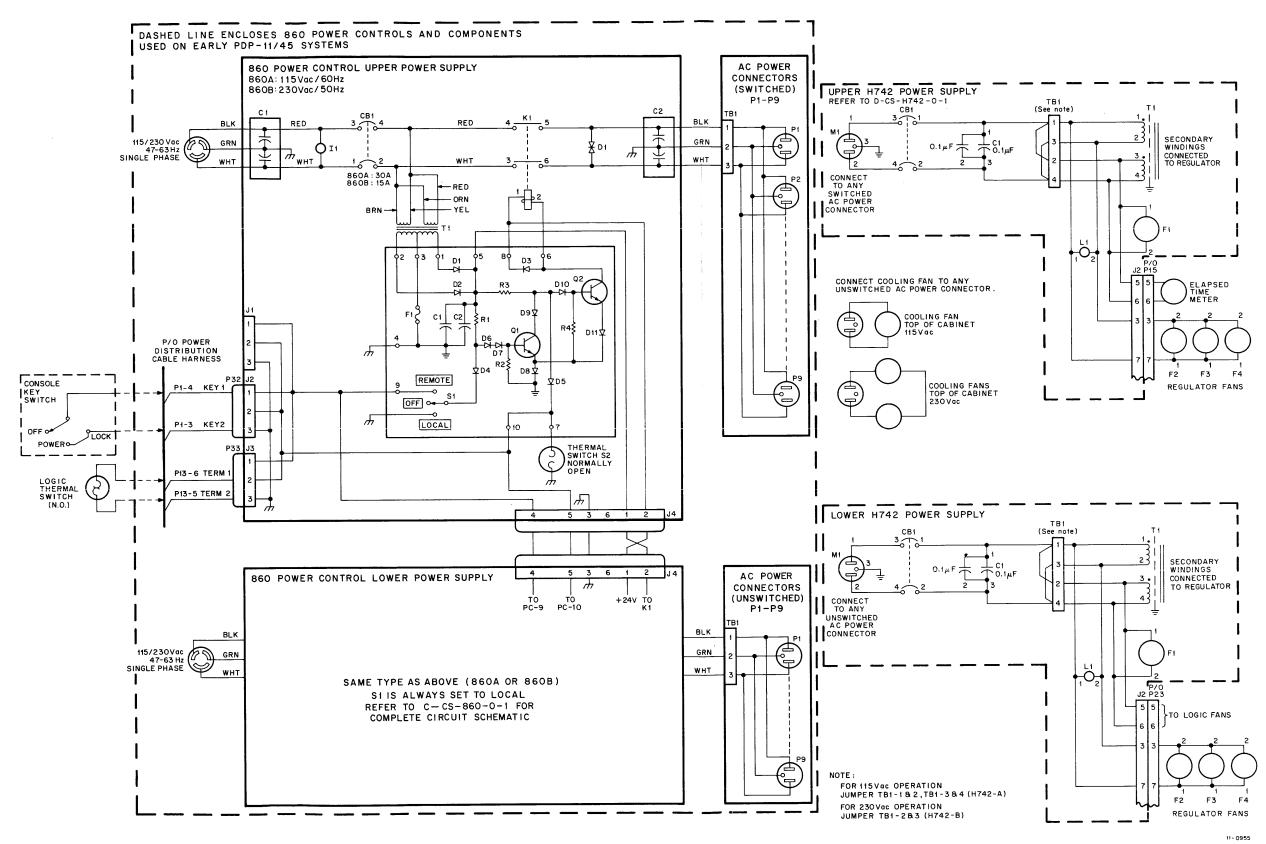

| 4.1.2     | Primary AC Power Outlets, 860 Power Controls     |      |

| 4.2       | AC POWER CONTROL                                 |      |

| 4.2.1     | Remote Power Connections                         |      |

| 4.2.2     | Power Controllers                                |      |

| 4.2.2.1   | 861 Power Controls                               |      |

| 4.2.2.2   | 860 Power Controls                               |      |

| 4.2.2.3   | Switched 860 Power Control                       |      |

| 4.2.2.4   | Unswitched 860 Power Control                     |      |

| 4.3       | BACK-UP AC POWER SOURCE FOR SEMICONDUCTOR MEMORY |      |

| 4.4       | AC POWER DISTRIBUTION                            | 4-11 |

| CHAPTER 5 | DC POWER DISTRIBUTION                            |      |

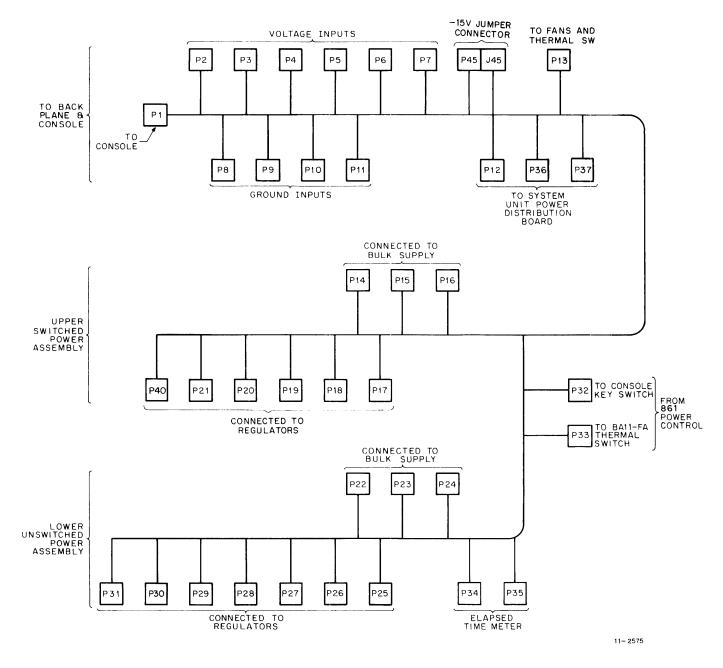

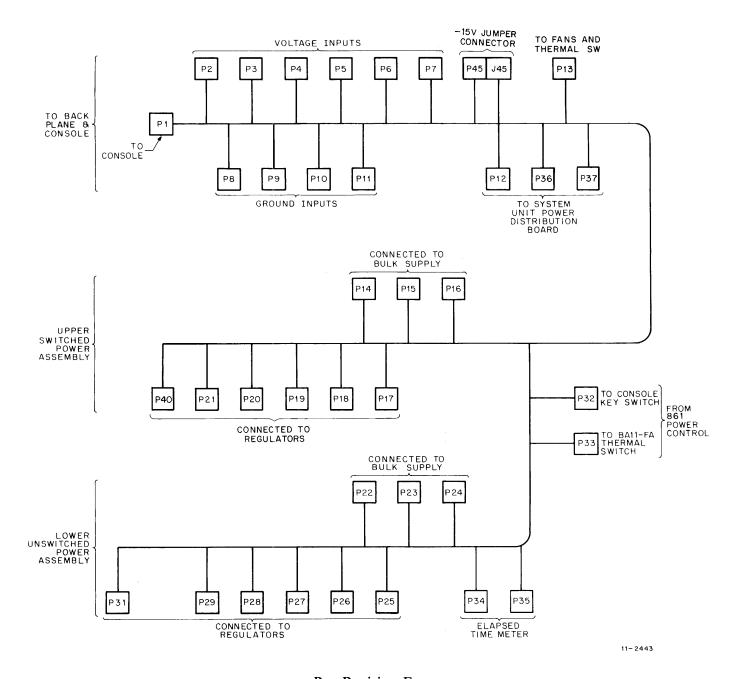

| 5.1       | DC POWER DISTRIBUTION                            | 5-1  |

| 5.1.1     | Power Distribution Cable Harnesses               |      |

| 5.1.2     | Backplane Power Distribution                     |      |

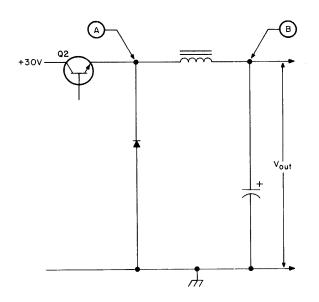

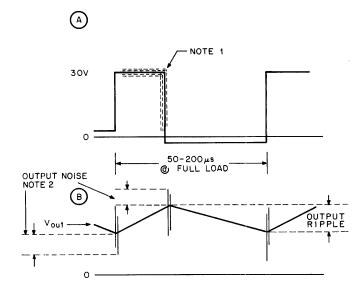

| 5.2       | DC POWER SUPPLIES                                |      |

| 5.2.1     | AC Input/Output                                  |      |

| 5.2.2     | Power Control Boards                             |      |

| J.4.4     | 10wor Control Doutes                             | 0    |

|           |                                                                    | Page   |

|-----------|--------------------------------------------------------------------|--------|

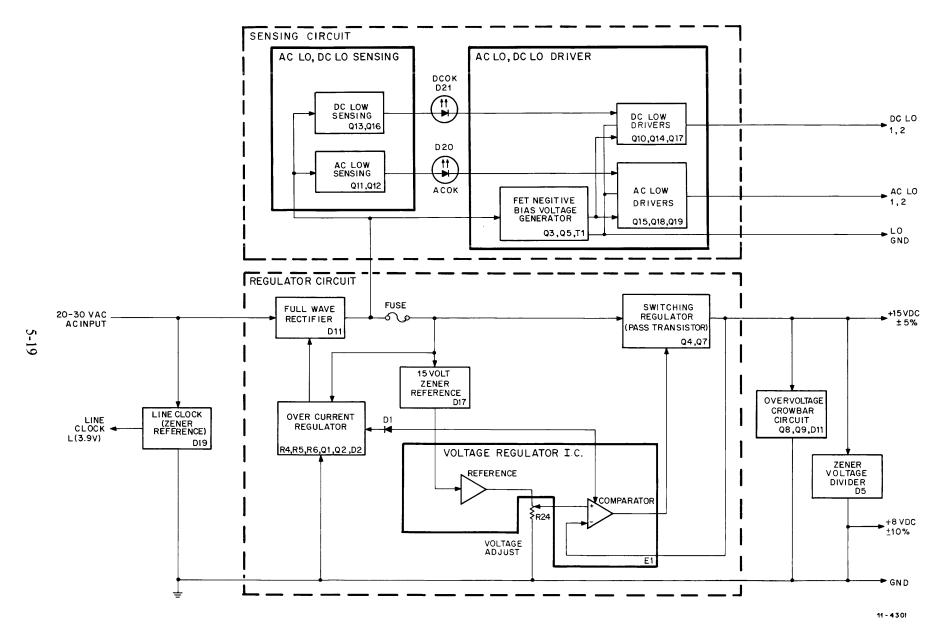

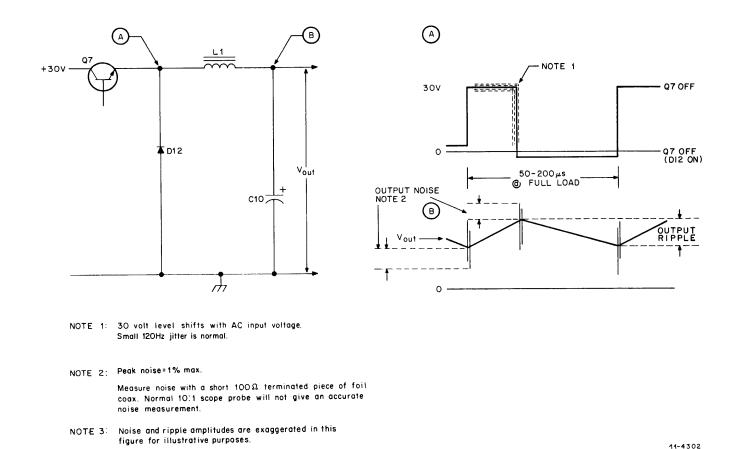

| 5.2.2.1   | 5411086 Power Control Board                                        |        |

| 5.2.2.2   | 5409730 Power Control Board                                        | . 5-22 |

| 5.2.3     | H744 +5 V Regulator                                                | 5-25   |

| 5.2.4     | H745-15 V Regulator                                                | 5-27   |

| 5.2.5     | H746 MOS Regulator                                                 | 5-27   |

| 5.2.6     | H754 +20, -5 V Regulator                                           | . 5-28 |

| CHAPTER 6 | MAINTENANCE                                                        |        |

| 6.1       | MAINTENANCE EQUIPMENT REQUIRED                                     | 6-1    |

| 6.2       | PREVENTIVE MAINTENANCE                                             | 6-1    |

| 6.2.1     | Physical Checks                                                    | 6-2    |

| 6.2.2     | Electrical Checks and Adjustments                                  | 6-3    |

| 6.2.2.1   | Regulator Voltage Checks                                           |        |

| 6.2.2.2   | Power Control                                                      |        |

| 6.2.2.3   | AC Power Connector Receptacles                                     |        |

| 6.2.3     | Timing Margins                                                     |        |

| 6.2.4     | General Diagnostic Testing                                         | 6-4    |

| 6.3       | POWER SYSTEM MAINTENANCE                                           | 6-5    |

| 6.3.1     | Circuit Tracing                                                    |        |

| 6.3.2     | Visual Aids to Troubleshooting                                     | 6-5    |

| 6.3.3     | Voltage Regulator Test Procedures                                  | 6-6    |

| 6.3.3.1   | Initial Tests                                                      |        |

| 6.3.3.2   | Output Short-Circuit Tests                                         |        |

| 6.3.3.3   | Testing a "Dead" Regulator                                         |        |

| 6.3.3.4   | Testing a Voltage Regulator After Repairs                          | 6-7    |

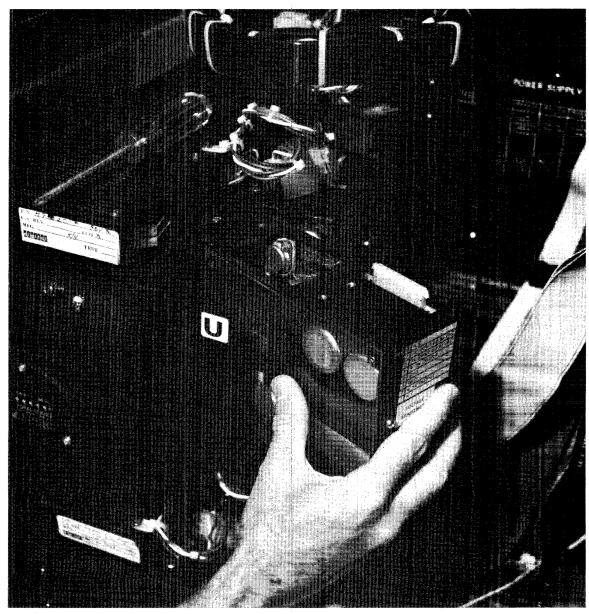

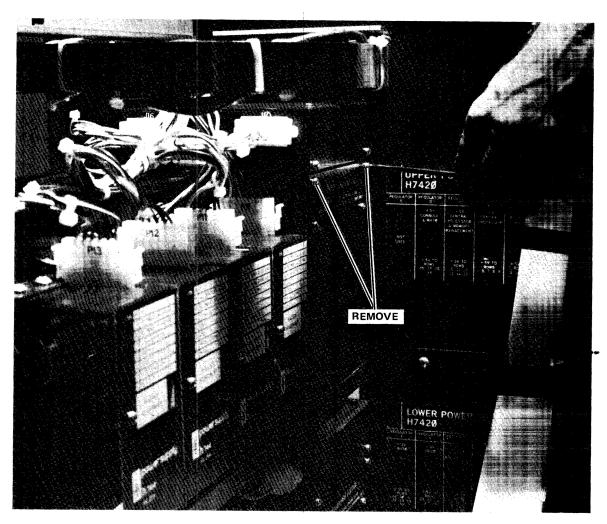

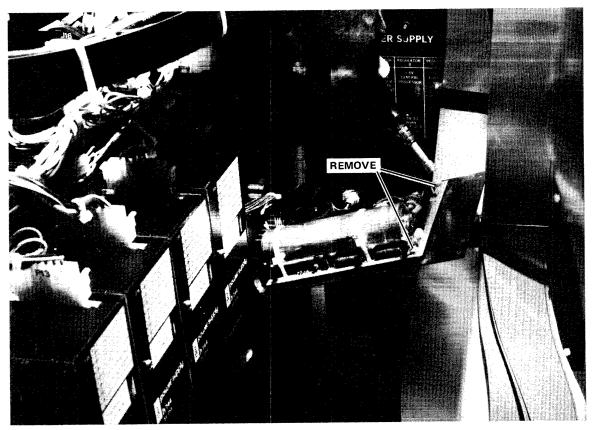

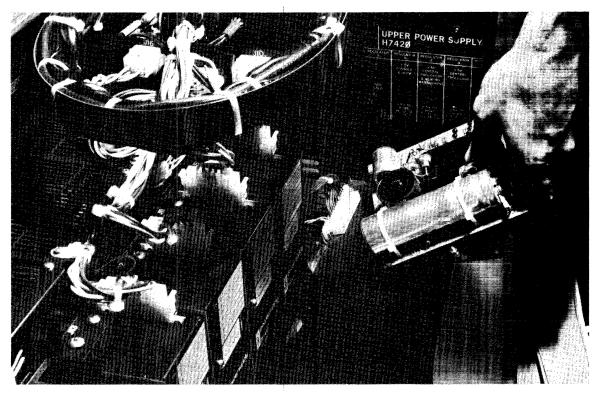

| 6.3.4     | H7420 Power Supply Subassembly Removal and Installation Procedures | 6-9    |

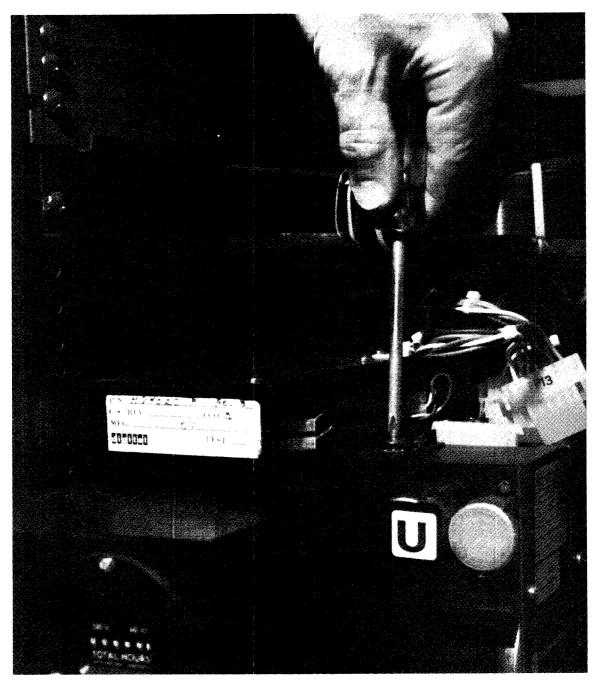

| 6.3.4.1   | Power Supply Access Procedure                                      | 6-9    |

| 6.3.4.2   | H744 Regulator Removal                                             | 6-9    |

| 6.3.4.3   | H744 Regulator Installation                                        | 6-12   |

| 6.3.4.4   | 5411086 15 V Regulator/Power Line Monitor Board Removal            | 6-12   |

| 6.3.4.5   | 5411086 15 V Regulator/Power Line Monitor Board Installation .     | 6-14   |

| 6.4       | CPU MAINTENANCE                                                    | 6-15   |

| 6.4.1     | KB11-A, D CPU Diagnostics                                          |        |

| 6.5       | HOW TO USE MAINTENANCE CARDS                                       | 6-20   |

| 6.5.1     | Clock Selection                                                    |        |

| 6.5.2     | Maintenance Mode Control                                           | 6-23   |

| 6.5.2.1   | Single ROM Cycle                                                   | 6-23   |

| 6.5.2.2   | $\mu 	ext{PB STOP}$                                                |        |

| 6.5.2.3   | Single Step                                                        |        |

| 6.5.3     | Using the Maintenance Card with KB11-A, D                          |        |

| 6.5.3.1   | Deposit Test Instruction                                           |        |

| 6.5.3.2   | $\mu$ PB STOP MODE                                                 |        |

| 6.5.3.3   | Single ROM Cycle Mode                                              |        |

| 6.5.3.4   | SING TP Mode                                                       | 6-26   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                | Page   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------|--------|

| 6.77         MODULE AND ASSEMBLY REMOVAL AND REPLACEMENT         6-72           6.7.1         Module Removal and Replacement         6-27           6.7.2         Console Disassembly         6-27           6.8         REMOVAL AND REPLACEMENT OF ICS         6-28           6.8.1         Location of ICS         6-28           6.8.2         IC Connections         6-29           6.8.3         IC and Component Removal and Replacement         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICS         6-29           6.8.3.2         Removal and Replacement of Ceramic ICS         6-39           6.8.4         Solder Mask Removal         6-40           6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-41           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-43           6.10.3         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7         PLUG-IN CARD OPTIONS         7-1           7.1         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1         FP11-B, C FLOATING POINT PROCESSOR         7-2           7.2.1                                                               | 6.6       | HOW TO USE THE W900 MODULE EXTENDERS           | . 6-27 |

| 6.7.1       Module Removal and Replacement       6-27         6.7.2       Console Disassembly       6-27         6.8       REMOVAL AND REPLACEMENT OF ICS       6-28         6.8.1       Location of ICS       6-28         6.8.2       IC Connections       6-29         6.8.3.1       Removal and Replacement of Plastic Case ICS       6-29         6.8.3.2       Removal and Replacement of Ceramic ICS       6-39         6.8.4       Solder Mask Removal       6-40         6.9       SPECIAL MOS HANDLING PROCEDURES       6-40         6.10       EQUIPMENT CONFIGURATION AND REVISION STATUS       6-41         6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-43         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7       PLUG-IN CARD OPTIONS         7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-2         7.2.2       FP11-B Diagnostics       7-2         7.2.3       Using the Maintenance Card with the FP1-B, C       7-3         7.2.3.1       FPP Test Timing       7-4                                                                                                                                                 |           | MODULE AND ASSEMBLY REMOVAL AND REPLACEMENT    | . 6-27 |

| 6.7.2         Console Disassembly         6-27           6.8         REMOVAL AND REPLACEMENT OF ICS         6-28           6.8.1         Location of ICS         6-28           6.8.2         IC Connections         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICS         6-29           6.8.3.2         Removal and Replacement of Ceramic ICS         6-39           6.8.4         Solder Mask Removal         6-40           6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-41           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-44           6.10.3         Module ECOs         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7         PLUG-IN CARD OPTIONS         7-1           7.1         Installation         7-1           7.2         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1.1         Installation         7-2           7.2.2         FP11-B Diagnostics         7-2           7.2.2.1         FP1 Diagnostics         7-2           7.2.2.3                                                                                                     |           |                                                |        |

| 6.8         REMOVAL AND REPLACEMENT OF ICS         6-28           6.8.1         Location of ICS         6-28           6.8.2         IC Connections         6-29           6.8.3         IC and Component Removal and Replacement         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICS         6-29           6.8.3.2         Removal and Replacement of Ceramic ICS         6-39           6.8.4         Solder Mask Removal         6-40           6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-41           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-43           6.10.4         Module ECOs         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7         PLUG-IN CARD OPTIONS           7.1         Installation         7-1           7.2         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1.1         Installation         7-2           7.2.2         FP11-B Diagnostics         7-2           7.2.2         FP11-B Diagnostics         7-2 <td< td=""><td></td><td>Console Disassembly</td><td>. 6-27</td></td<>                                       |           | Console Disassembly                            | . 6-27 |

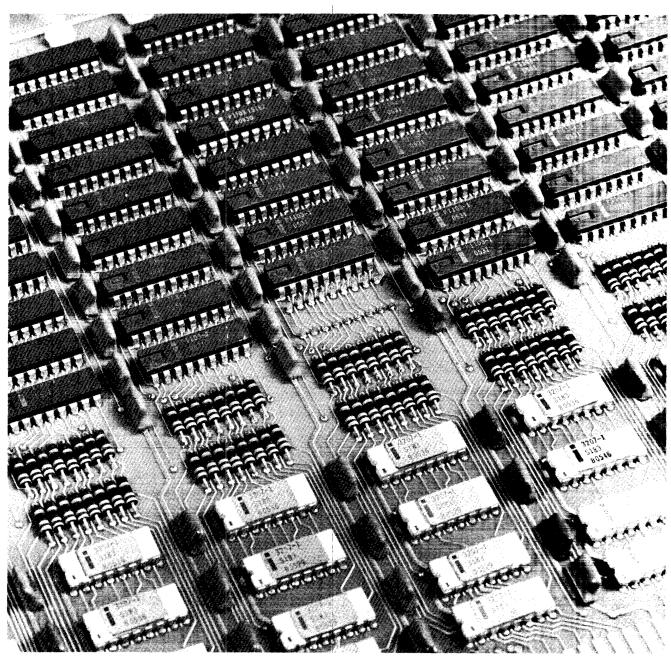

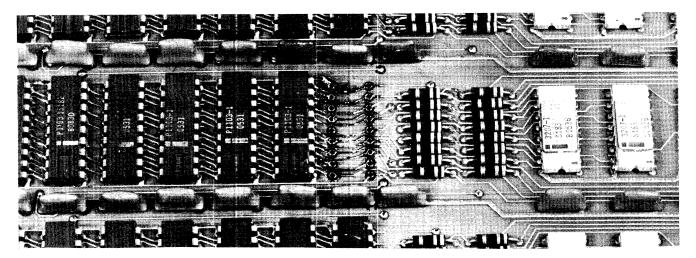

| 6.8.1         Location of ICs         6-28           6.8.2         IC Connections         6-29           6.8.3         IC and Component Removal and Replacement         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICs         6-29           6.8.3.2         Removal and Replacement of Ceramic ICs         6-39           6.8.4         Solder Mask Removal         6-40           6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-41           6.10.1         Mcchanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-43           6.10.3         Module ECOs         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7         PLUG-IN CARD OPTIONS         7-1           7.1         Installation         7-1           7.2         FPI1 DIAGNOSTICS         7-2           7.1.1         Installation         7-1           7.2.2         FPI1-B Diagnostics         7-2           7.2.3         Using the Maintenance Card with the FPI1-B, C         7-3           7.2.4         FPI1-B, C Floating-Point Processor Procedures         7-4 </td <td></td> <td>REMOVAL AND REPLACEMENT OF ICs</td> <td>. 6-28</td> |           | REMOVAL AND REPLACEMENT OF ICs                 | . 6-28 |

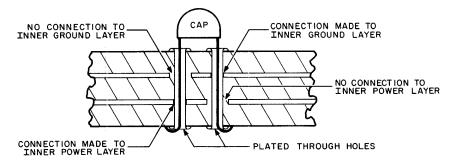

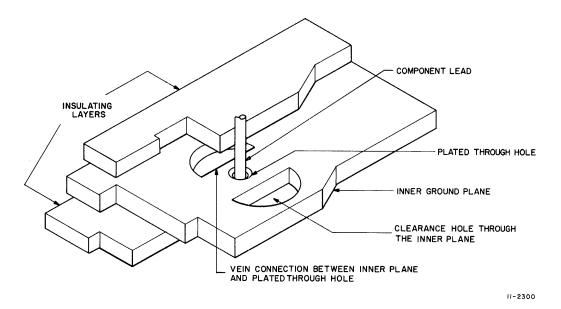

| 6.8.2         IC Connections         6-29           6.8.3         IC and Component Removal and Replacement         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICs         6-29           6.8.3.2         Removal and Replacement of Ceramic ICs         6-39           6.8.4         Solder Mask Removal         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-40           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-41           6.10.3         Module ECOs         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7         PLUG-IN CARD OPTIONS           7.1         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1.1         Installation         7-2           7.2.2         FP11-B Diagnostics         7-2           7.2.2         FP11-B Diagnostics         7-2           7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.3         Using the Maintenance Card with the FP11-B, C         7-4           7.2.4.1         Time Margining of the FP11-B         7-4           7.2.4.2         Time Mar                                                                            |           | Location of ICs                                | . 6-28 |

| 6.8.3.1         IC and Component Removal and Replacement         6-29           6.8.3.1         Removal and Replacement of Plastic Case ICS         6-29           6.8.3.2         Removal and Replacement of Ceramic ICS         6-39           6.8.4         Solder Mask Removal         6-40           6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-41           6.10.3         Module ECOS         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7           PLUG-IN CARD OPTIONS           7.1         Installation         7-1           7.1.1         Installation         7-1           7.2         FP11-B Diagnostics         7-2           7.2.1         FP1-B Diagnostics         7-2           7.2.2         FP1-C Daing-Point Processor         7-3           7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.4         FP1-B-C Floating-Point Processor Procedures         7-4           7.2.4.1         Time Margining of the FP11-B         7-4           7.2.4.2         Time Margining                                                                                              |           | IC Connections                                 | . 6-29 |

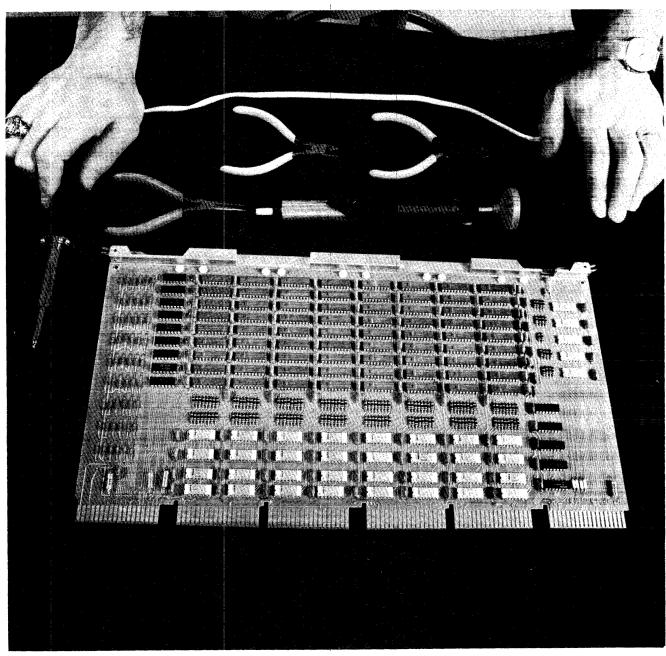

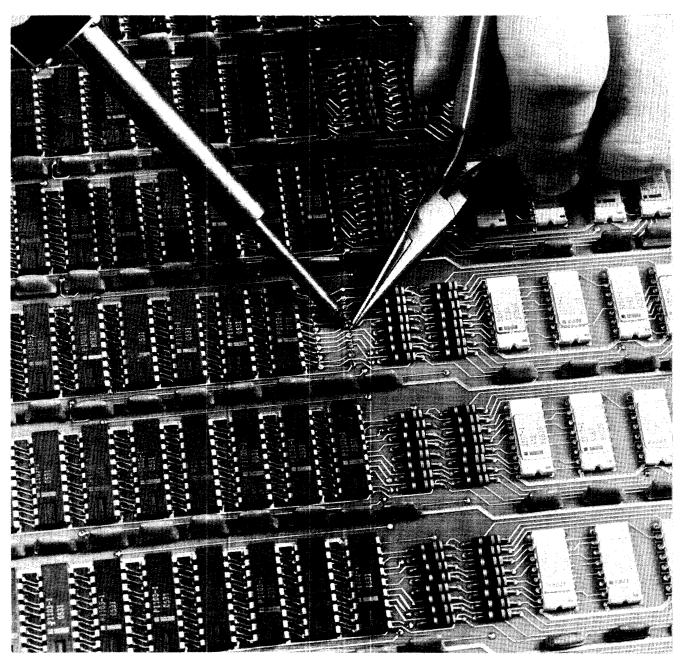

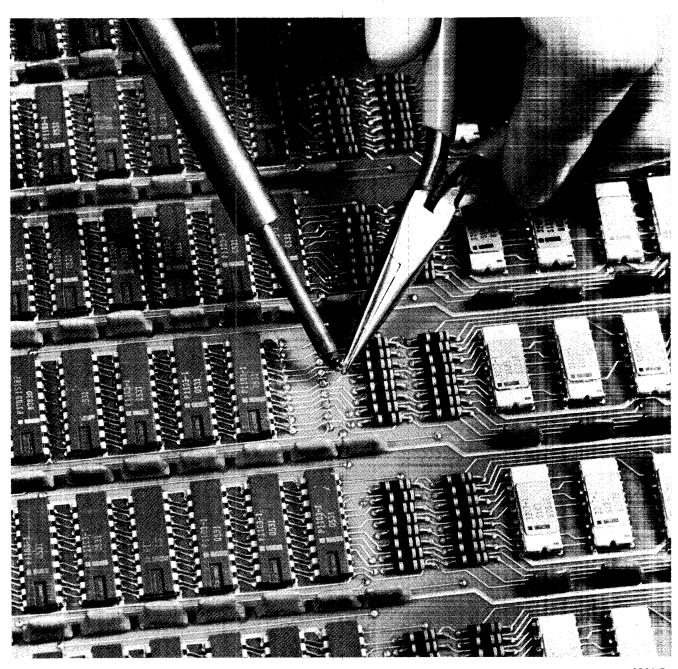

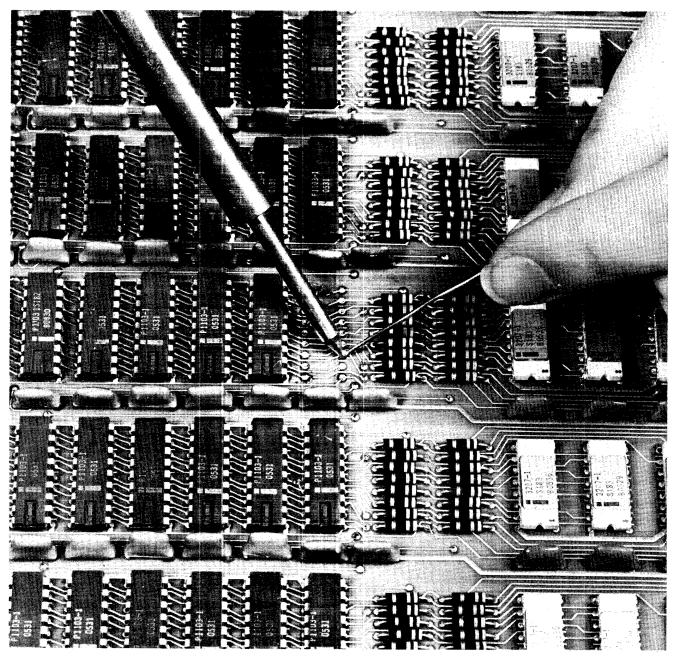

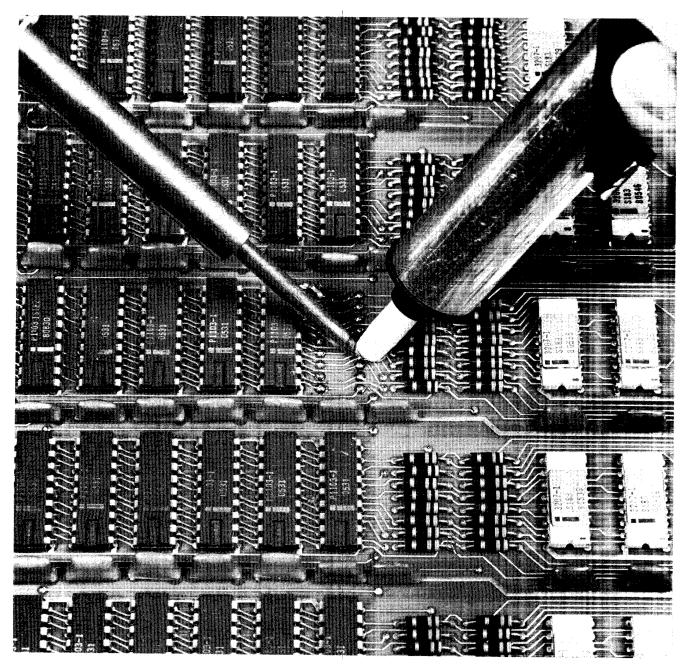

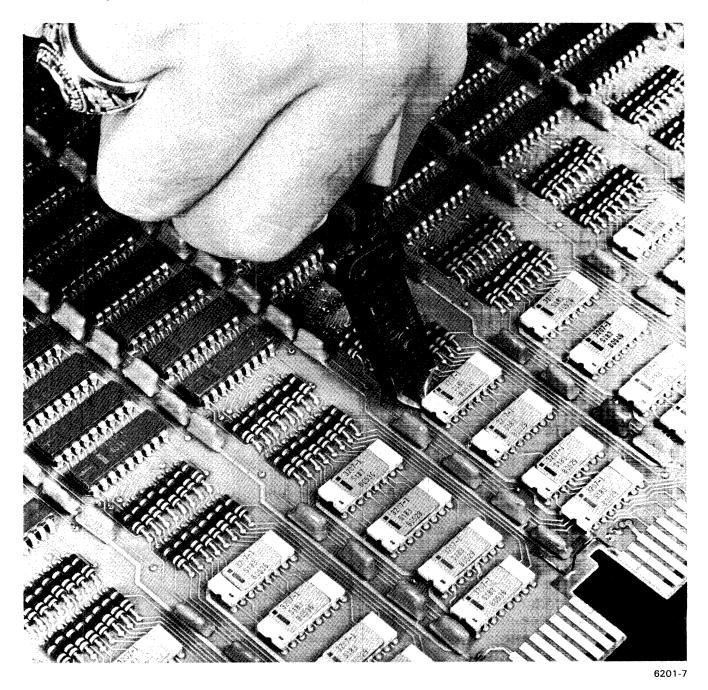

| 6.8.3.1       Removal and Replacement of Plastic Case ICs       6-29         6.8.4       Solder Mask Removal       6-40         6.9       SPECIAL MOS HANDLING PROCEDURES       6-40         6.10       EQUIPMENT CONFIGURATION AND REVISION STATUS       6-41         6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-41         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7         PLUG-IN CARD OPTIONS         7.1       Installation       7-1         7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-B Diagnostics       7-2         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.4.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.5       Time Margining of the FP11-B       7-4         7.2.4.6       Time Margining of the FP11-B       7-4         7.2.4.5       Maintenance Instructions of the FP11-B       7-5         7.2       Maintenance Instructi                                                                                                                                                 |           | IC and Component Removal and Replacement       | . 6-29 |

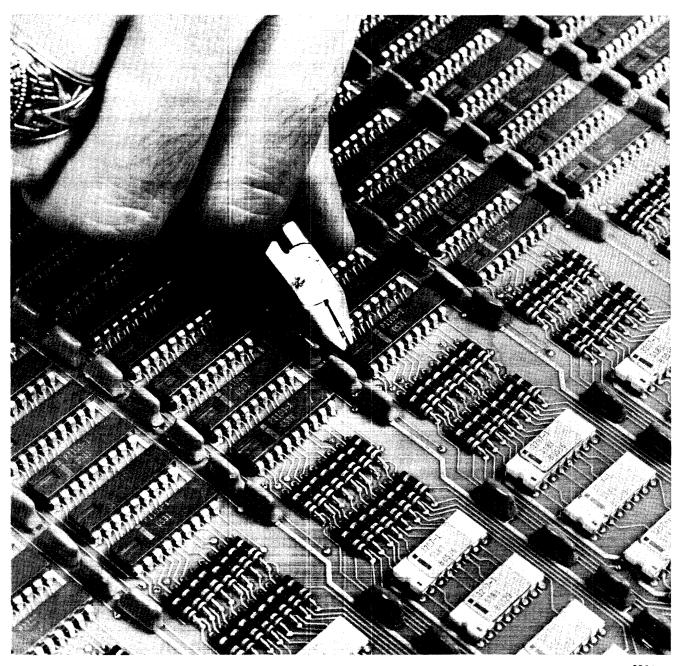

| 6.8.3.2       Removal and Replacement of Ceramic ICs       6-39         6.8.4       Solder Mask Removal       6-40         6.9       SPECIAL MOS HANDLING PROCEDURES       6-40         6.10       EQUIPMENT CONFIGURATION AND REVISION STATUS       6-41         6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-43         6.10.4       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7         PLUG-IN CARD OPTIONS         7.1         FP1-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-1         7.2       FP11-B Diagnostics       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3       Ising the Maintenance Card with the FP11-B, C       7-3         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       FIP1-B, C Floating-Point Processor Procedures       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B                                                                                                                                                        |           | Removal and Replacement of Plastic Case ICs    | . 6-29 |

| 6.8.4       Solder Mask Removal       6-40         6.9       SPECIAL MOS HANDLING PROCEDURES       6-40         6.10       EQUIPMENT CONFIGURATION AND REVISION STATUS       6-41         6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-43         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7       PLUG-IN CARD OPTIONS         7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-5         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6 </td <td></td> <td>Removal and Replacement of Ceramic ICs</td> <td>. 6-39</td>                                                          |           | Removal and Replacement of Ceramic ICs         | . 6-39 |

| 6.9         SPECIAL MOS HANDLING PROCEDURES         6-40           6.10         EQUIPMENT CONFIGURATION AND REVISION STATUS         6-41           6.10.1         Mechanical Status Sticker         6-41           6.10.2         ECO Status Sticker         6-41           6.10.3         Module ECOS         6-43           6.10.4         Module Utilization List (MUL) Sticker         6-43           CHAPTER 7           PLUG-IN CARD OPTIONS           7.1         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1.1         Installation         7-1           7.2         FP11 DIAGNOSTICS         7-2           7.2.1         FP11-B Diagnostics         7-2           7.2.1         FP11-B Diagnostics         7-3           7.2.2         FP11-C Diagnostics         7-3           7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.4         FP11-B, C Floating-Point Processor Procedures         7-4           7.2.4.4         FP11-B, C Floating-Point Processor Procedures         7-4           7.2.4.2         Time Margining of the FP11-B         7-4           7.2.4.3         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.4                                                                                                 |           | Solder Mask Removal                            | . 6-40 |

| 6.10       EQUIPMENT CONFIGURATION AND REVISION STATUS       6-41         6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-41         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7       PLUG-IN CARD OPTIONS         7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-B Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-B       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY M                                                                                                                                |           | SPECIAL MOS HANDLING PROCEDURES                | . 6-40 |

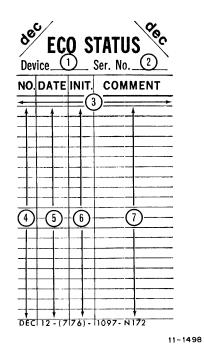

| 6.10.1       Mechanical Status Sticker       6-41         6.10.2       ECO Status Sticker       6-41         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7       PLUG-IN CARD OPTIONS         7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-1         7.2       FP1 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-B Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-B       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-B       7-5         7.2.4.5       Maintenance Instruction Programming Example       7-5         7.2.4.6       Console Display Features       7-5         7.3       KT1-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-12                                                                                                                                     |           | EOUIPMENT CONFIGURATION AND REVISION STATUS    | . 6-41 |

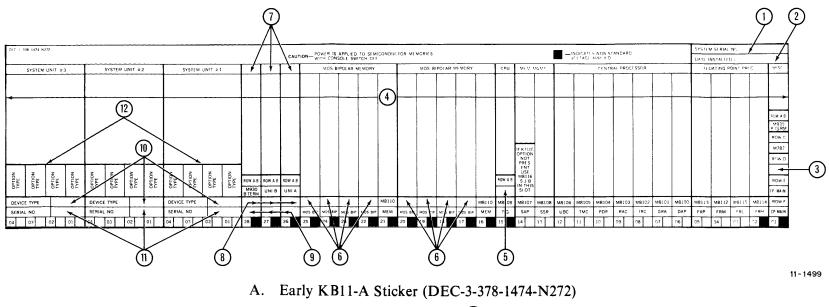

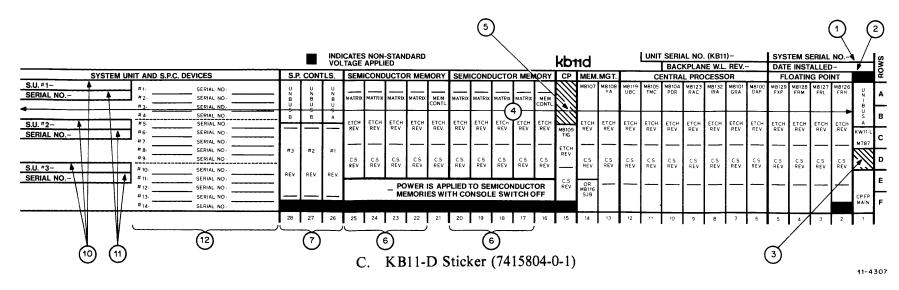

| 6.10.2       ECO Status Sticker       6-41         6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CHAPTER 7       PLUG-IN CARD OPTIONS         7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-B       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.4.1       Installation       7-12                                                                                                                                                 |           | Mechanical Status Sticker                      | . 6-41 |

| 6.10.3       Module ECOs       6-43         6.10.4       Module Utilization List (MUL) Sticker       6-43         CCHAPTER 7       PLUG-IN CARD OPTIONS         7.1       Installation       7-1         7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-B Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-B       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4.1       Installation of MoS Memory (Mos 10                                                                                                                                |           |                                                |        |

| CHAPTER 7         PLUG-IN CARD OPTIONS           7.1         FP11-B, C FLOATING POINT PROCESSOR         7-1           7.1.1         Installation         7-1           7.2         FP11 DIAGNOSTICS         7-2           7.2.1         FP11-B Diagnostics         7-2           7.2.2         FP11-C Diagnostics         7-3           7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.3.1         FPP Test Timing         7-4           7.2.4         FP11-B, C Floating-Point Processor Procedures         7-4           7.2.4.1         Time Margining of the FP11-B         7-4           7.2.4.2         Time Margining of the FP11-C         7-4           7.2.4.3         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.4         Special Maintenance Instructions of the FP11-C         7-6           7.2.4.5         Maintenance Instruction Programming Example         7-7           7.2.4.6         Console Display Features         7-8           7.3         KT11-C, CD MEMORY MANAGEMENT UNIT         7-10           7.3.1         Installation         7-12           7.4.1         Installation         7-12           7.4.1         Semiconductor Memory Jumper Connections                                                                  |           |                                                |        |

| 7.1       FP11-B, C FLOATING POINT PROCESSOR       7-1         7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.4.1       Installation       7-12         7.4.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-12         7.4.1.4       Installa                                                                                                                 | 6.10.4    |                                                |        |

| 7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-12         7.4.1.4       Installation of Both MOS a                                                                                                                 | CHAPTER 7 | PLUG-IN CARD OPTIONS                           |        |

| 7.1.1       Installation       7-1         7.2       FP11 DIAGNOSTICS       7-2         7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-12         7.4.1.4       Installation of Both MOS a                                                                                                                 | 7.1       | EPIL-R C ELOATING POINT PROCESSOR              | . 7-1  |

| 7.2         FP11 DIAGNOSTICS         7-2           7.2.1         FP11-B Diagnostics         7-2           7.2.2         FP11-C Diagnostics         7-3           7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.3.1         FPP Test Timing         7-4           7.2.4         FP11-B, C Floating-Point Processor Procedures         7-4           7.2.4.1         Time Margining of the FP11-B         7-4           7.2.4.2         Time Margining of the FP11-C         7-4           7.2.4.3         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.4         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.5         Maintenance Instruction Programming Example         7-7           7.2.4.5         Maintenance Instruction Programming Example         7-7           7.2.4.6         Console Display Features         7-8           7.3         KT11-C, CD MEMORY MANAGEMENT UNIT         7-10           7.3.1         Installation         7-10           7.3.2         Diagnostics         7-11           7.4.1         Installation         7-12           7.4.1.1         Semiconductor Memory Jumper Connections         7-12           7.4.1.2 <td< td=""><td></td><td>Installation</td><td>. 7-1</td></td<>       |           | Installation                                   | . 7-1  |

| 7.2.1       FP11-B Diagnostics       7-2         7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4.1       Semiconductor MEMORY       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-16         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-16                                                                                                |           |                                                |        |

| 7.2.2       FP11-C Diagnostics       7-3         7.2.3       Using the Maintenance Card with the FP11-B, C       7-3         7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-13         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of Both MOS and Bipolar Memory       7-16         7.4.2       Semiconductor Memory Calibration       7-20                                                                                                       |           |                                                |        |

| 7.2.3         Using the Maintenance Card with the FP11-B, C         7-3           7.2.3.1         FPP Test Timing         7-4           7.2.4         FP11-B, C Floating-Point Processor Procedures         7-4           7.2.4.1         Time Margining of the FP11-B         7-4           7.2.4.2         Time Margining of the FP11-C         7-4           7.2.4.3         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.4         Special Maintenance Instructions of the FP11-C         7-6           7.2.4.5         Maintenance Instruction Programming Example         7-7           7.2.4.6         Console Display Features         7-8           7.3         KT11-C, CD MEMORY MANAGEMENT UNIT         7-10           7.3.1         Installation         7-10           7.3.2         Diagnostics         7-11           7.4         MS11 SEMICONDUCTOR MEMORY         7-12           7.4.1         Installation         7-12           7.4.1.1         Semiconductor Memory Jumper Connections         7-12           7.4.1.2         Installation of Bipolar Memory         7-16           7.4.1.3         Installation of MOS Memory (MS11-B)         7-19           7.4.2         Semiconductor Memory Calibration         7-20                                                      |           |                                                |        |

| 7.2.3.1       FPP Test Timing       7-4         7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of Both MOS and Bipolar Memory       7-15         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                         |           |                                                |        |

| 7.2.4       FP11-B, C Floating-Point Processor Procedures       7-4         7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-16         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-15         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                    |           |                                                |        |

| 7.2.4.1       Time Margining of the FP11-B       7-4         7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-16         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                |           |                                                |        |

| 7.2.4.2       Time Margining of the FP11-C       7-4         7.2.4.3       Special Maintenance Instructions of the FP11-B       7-4         7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-16         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                             |           |                                                |        |

| 7.2.4.3         Special Maintenance Instructions of the FP11-B         7-4           7.2.4.4         Special Maintenance Instructions of the FP11-C         7-6           7.2.4.5         Maintenance Instruction Programming Example         7-7           7.2.4.6         Console Display Features         7-8           7.3         KT11-C, CD MEMORY MANAGEMENT UNIT         7-10           7.3.1         Installation         7-10           7.3.2         Diagnostics         7-11           7.4         MS11 SEMICONDUCTOR MEMORY         7-12           7.4.1         Installation         7-12           7.4.1.1         Semiconductor Memory Jumper Connections         7-12           7.4.1.2         Installation of Bipolar Memory         7-16           7.4.1.3         Installation of MOS Memory (MS11-B)         7-15           7.4.1.4         Installation of Both MOS and Bipolar Memory         7-15           7.4.2         Semiconductor Memory Calibration         7-20           7.4.3         Diagnostics         7-20                                                                                                                                                                                                                                                                                  |           |                                                |        |

| 7.2.4.4       Special Maintenance Instructions of the FP11-C       7-6         7.2.4.5       Maintenance Instruction Programming Example       7-7         7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-16         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                |        |

| 7.2.4.5       Maintenance Instruction Programming Example       7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-7-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | Special Maintenance Instructions of the FP11-C | 7-6    |

| 7.2.4.6       Console Display Features       7-8         7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           | Maintenance Instruction Programming Evennle    | 7-7    |

| 7.3       KT11-C, CD MEMORY MANAGEMENT UNIT       7-10         7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                                |        |

| 7.3.1       Installation       7-10         7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | WT11.C CD MEMORY MANAGEMENT UNIT               |        |

| 7.3.2       Diagnostics       7-11         7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           | Installation                                   | 7-10   |

| 7.4       MS11 SEMICONDUCTOR MEMORY       7-12         7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                                                |        |

| 7.4.1       Installation       7-12         7.4.1.1       Semiconductor Memory Jumper Connections       7-12         7.4.1.2       Installation of Bipolar Memory       7-16         7.4.1.3       Installation of MOS Memory (MS11-B)       7-19         7.4.1.4       Installation of Both MOS and Bipolar Memory       7-19         7.4.2       Semiconductor Memory Calibration       7-20         7.4.3       Diagnostics       7-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                |        |

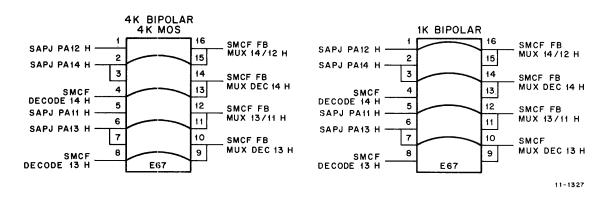

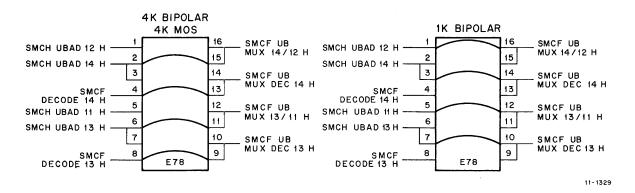

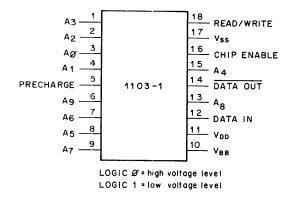

| 7.4.1.1       Semiconductor Memory Jumper Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                                                |        |

| 7.4.1.2       Installation of Bipolar Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                |        |

| 7.4.1.3       Installation of MOS Memory (MS11-B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                |        |

| 7.4.1.4 Installation of Both MOS and Bipolar Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                |        |

| 7.4.2       Semiconductor Memory Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                                                |        |

| 7.4.3 Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                                                |        |

CHAPTER 8 SYSTEM UNIT OPTIONS

8.1

Page

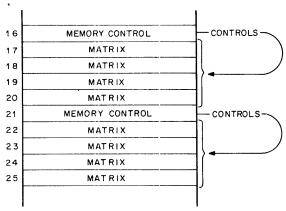

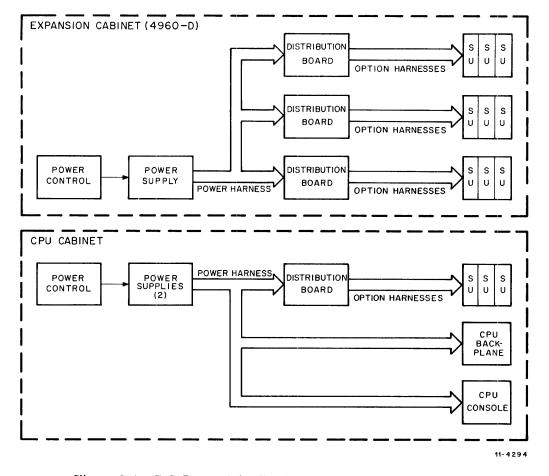

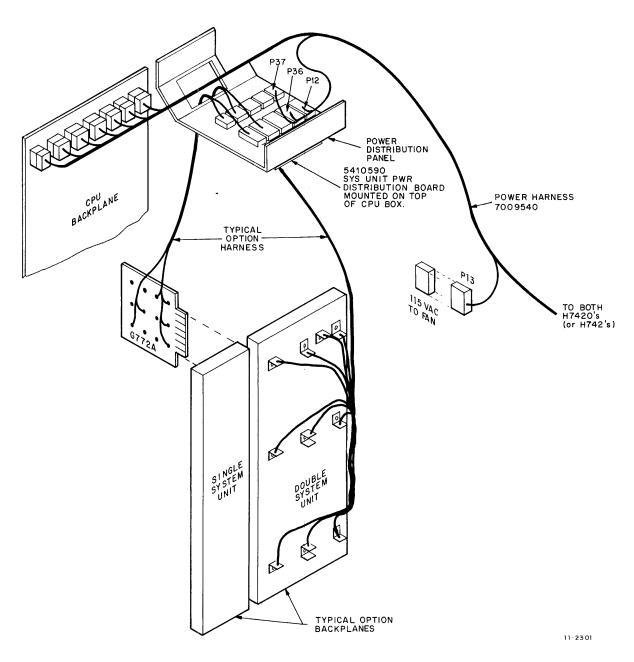

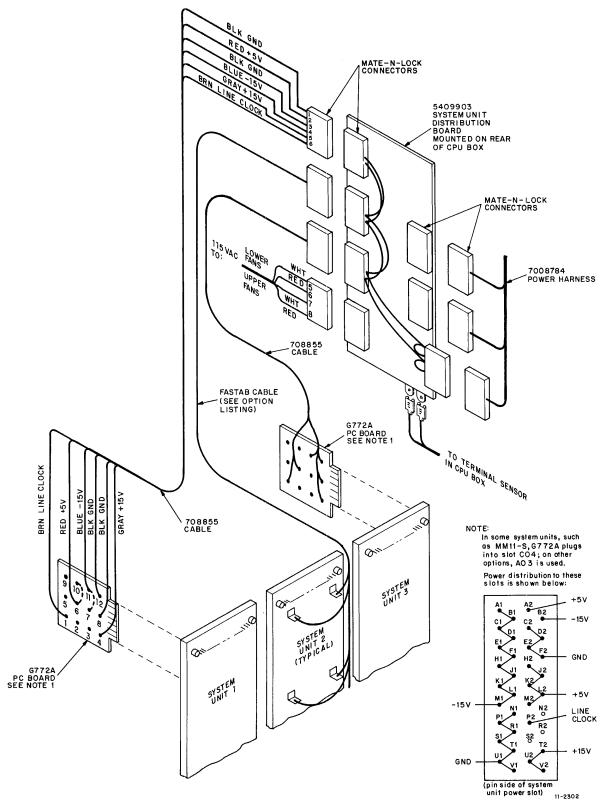

| 8.1<br>8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.4<br>8.5 | SYSTEM UNITS  EXPANSION CABINETS  DC POWER DISTRIBUTION  CPU Cabinet  Expansion Cabinets  MF11 CORE MEMORY INSTALLATION OF SYSTEM UNIT |      |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|

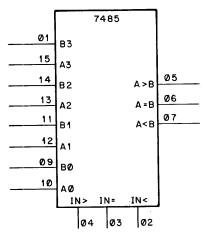

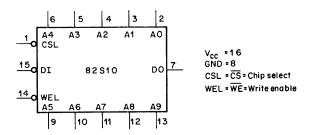

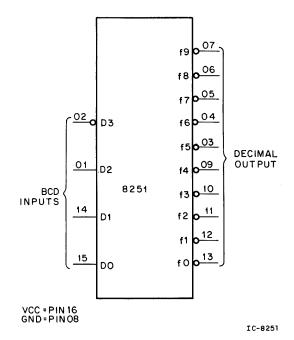

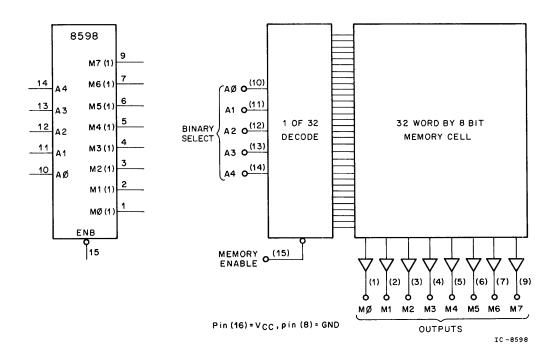

| APPENDIX A                                        | IC DESCRIPTIONS                                                                                                                        |      |

| APPENDIX B                                        | PERIPHERAL PREVENTIVE MAINTENANCE SCHEDULE                                                                                             |      |

| APPENDIX C                                        | SUMMARY OF EQUIPMENT SPECIFICATIONS                                                                                                    |      |

|                                                   | ILLUSTRATIONS                                                                                                                          |      |

| Figure No.                                        | Title                                                                                                                                  | Page |

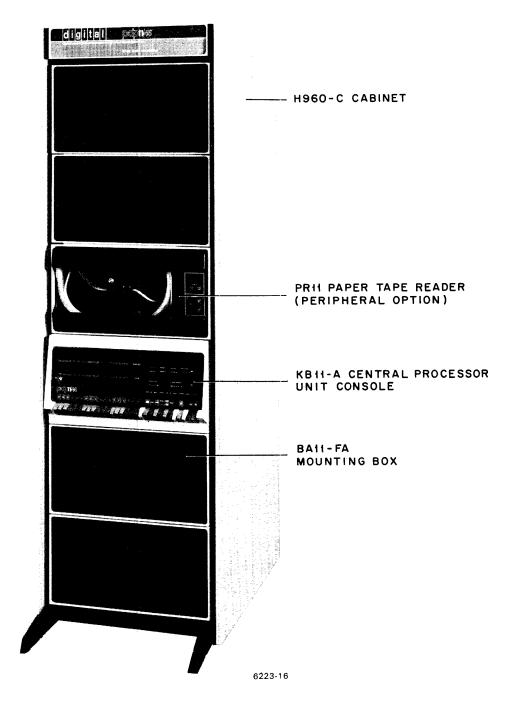

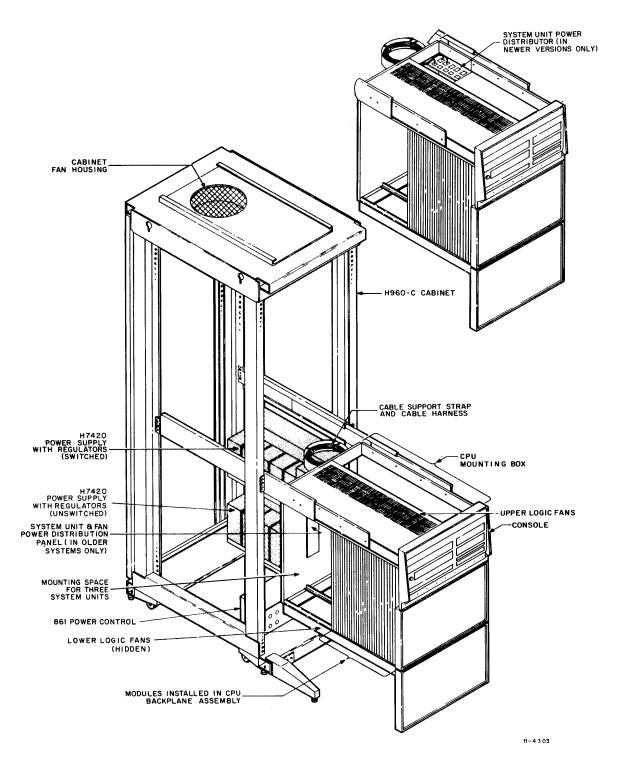

| 1-1                                               | Location of Major Components and Assemblies Showing New Models Using 861 Power Control                                                 | 1-2  |

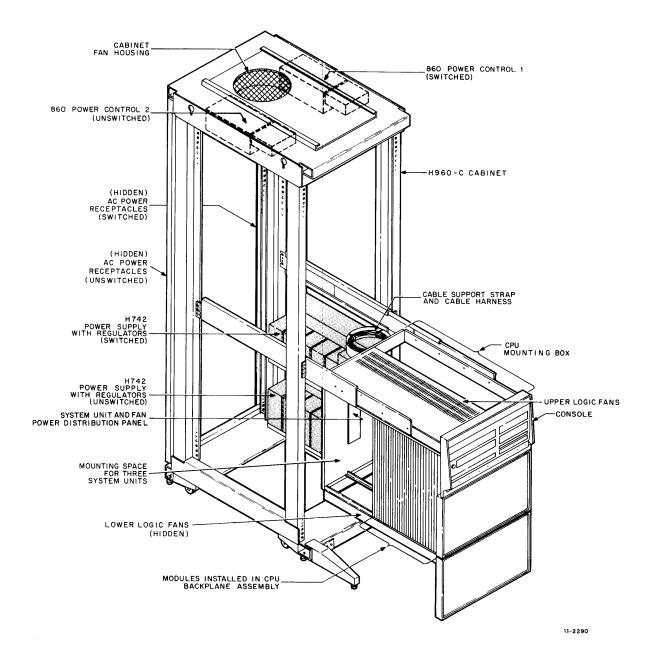

| 1-2                                               | Location of Major Components and Assemblies Showing 860 Power Controls Used on Early Models                                            |      |

| 1-3                                               | Unibus A and B Connectors                                                                                                              |      |

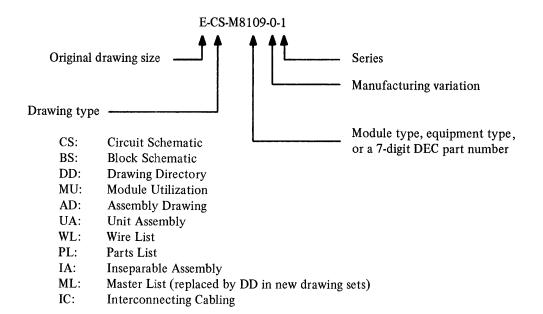

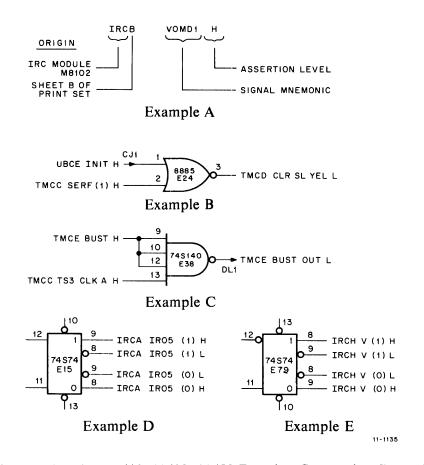

| 1-4                                               | PDP-11/45, 11/50, 11/55 Drawing Convention Examples                                                                                    |      |

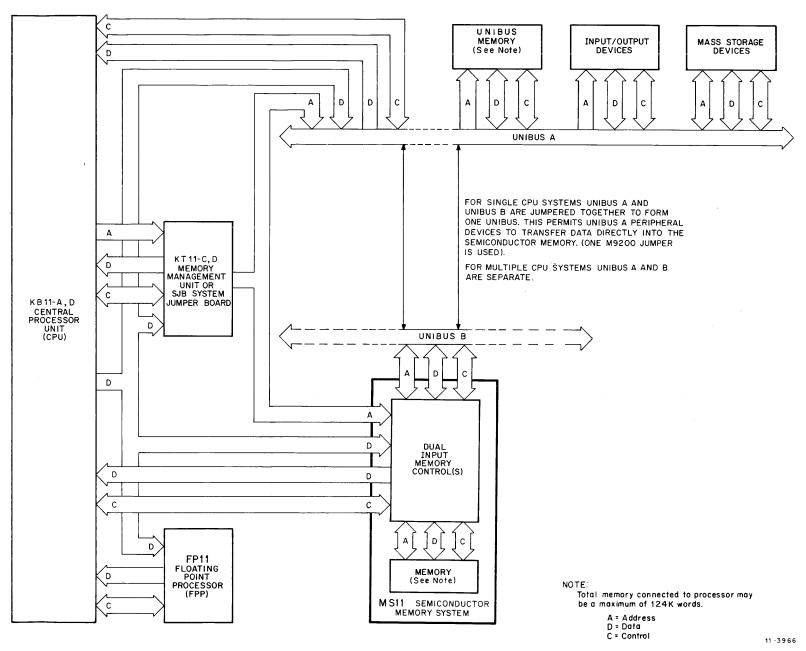

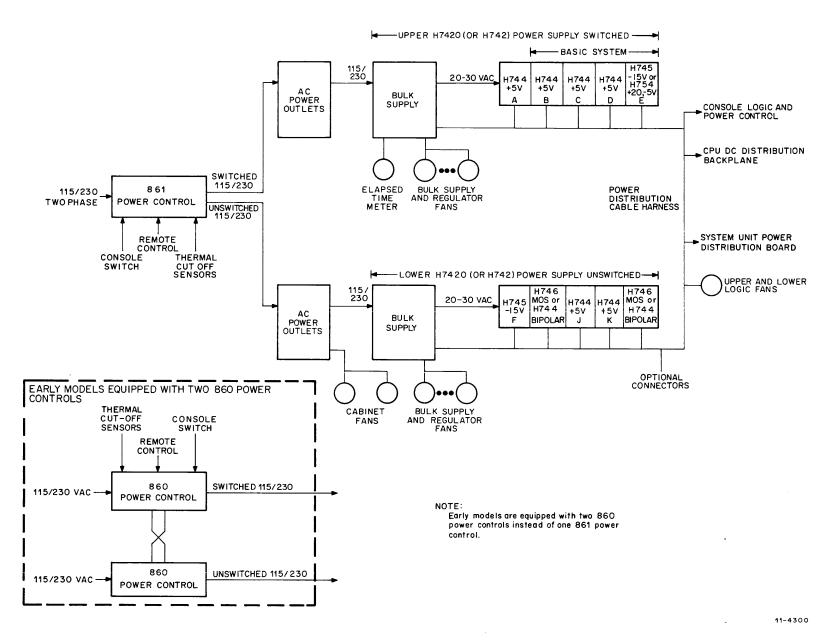

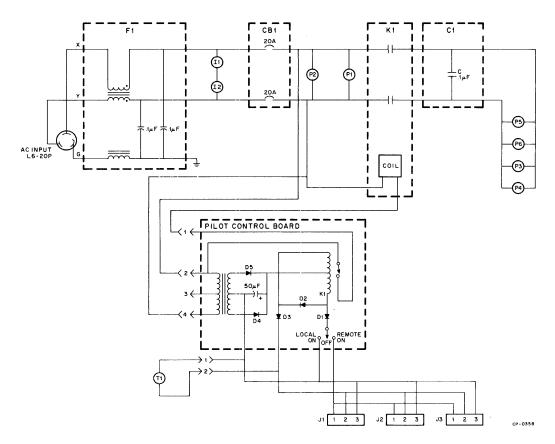

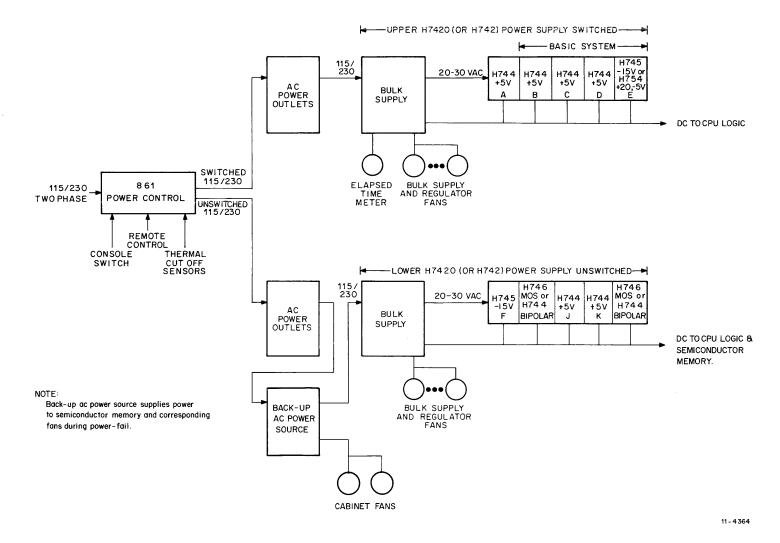

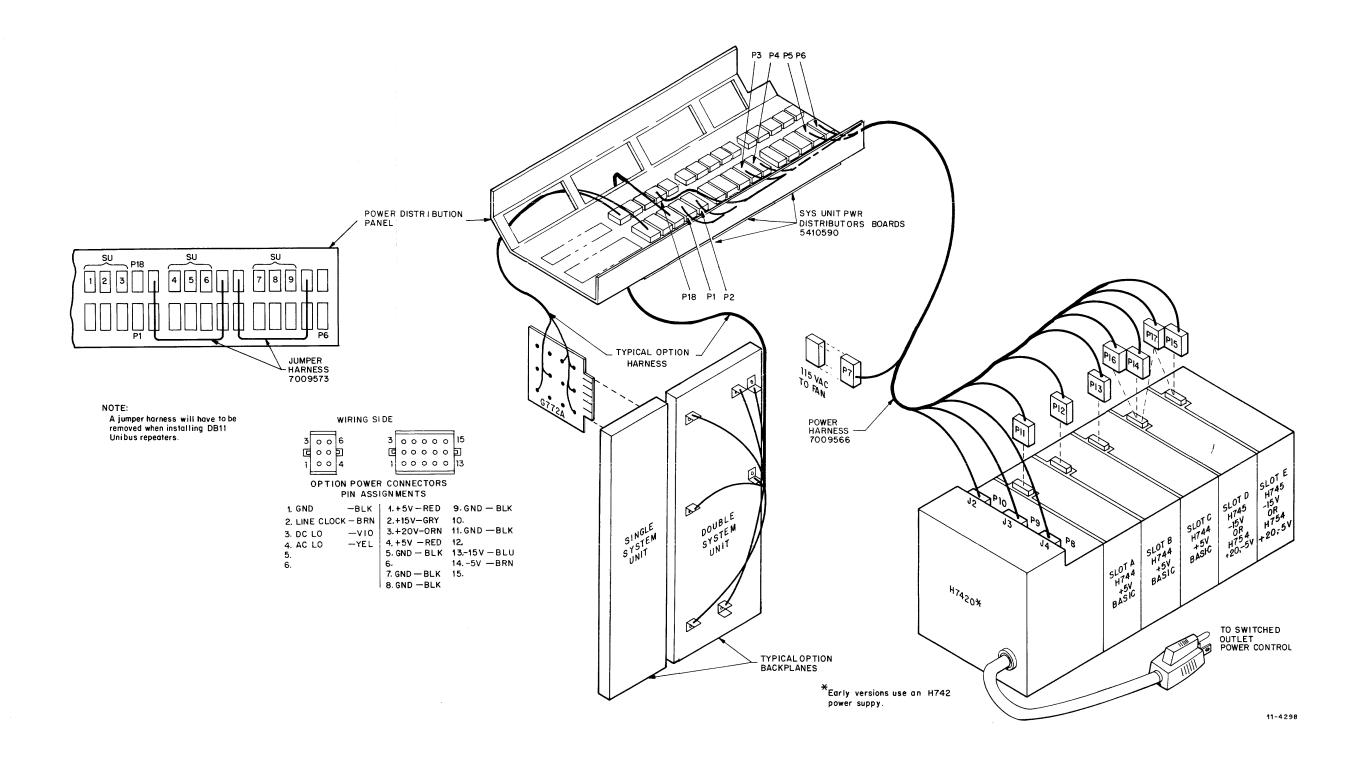

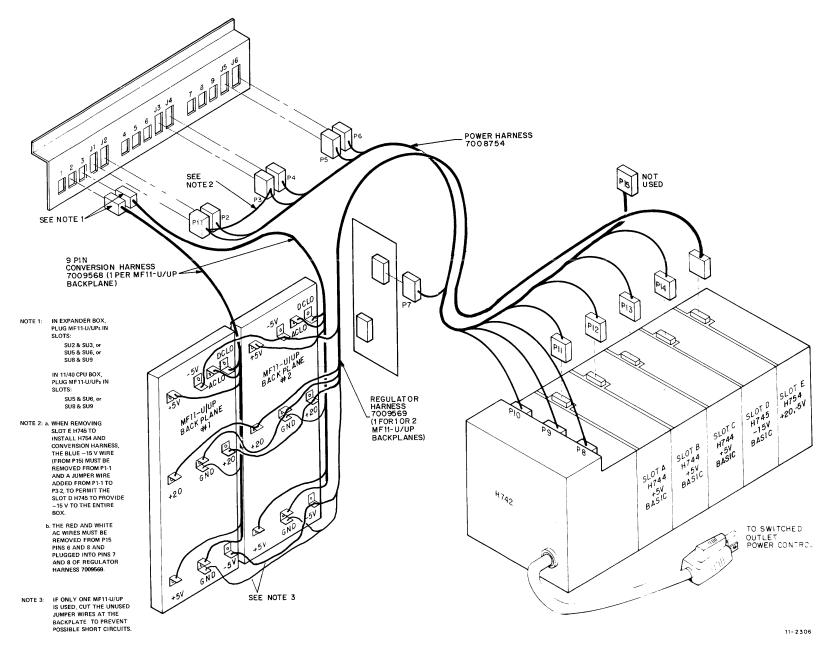

| 3-1                                               | Typical PDP-11/45, 11/50, 11/55 Power System                                                                                           |      |

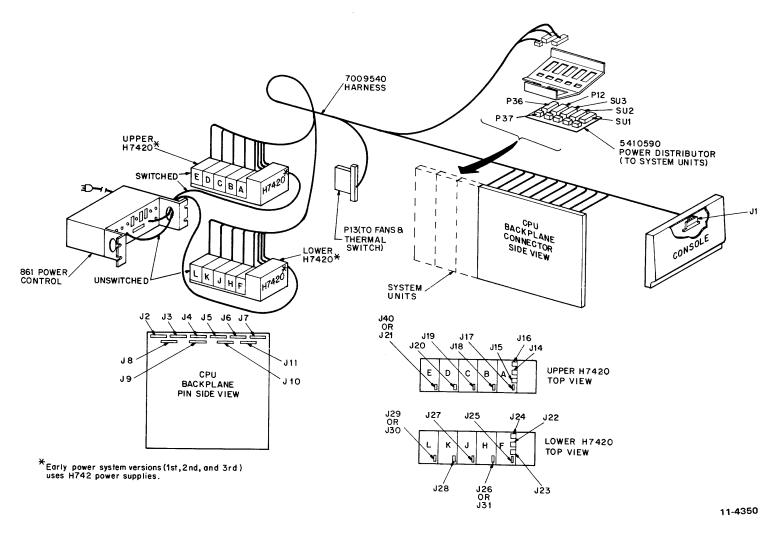

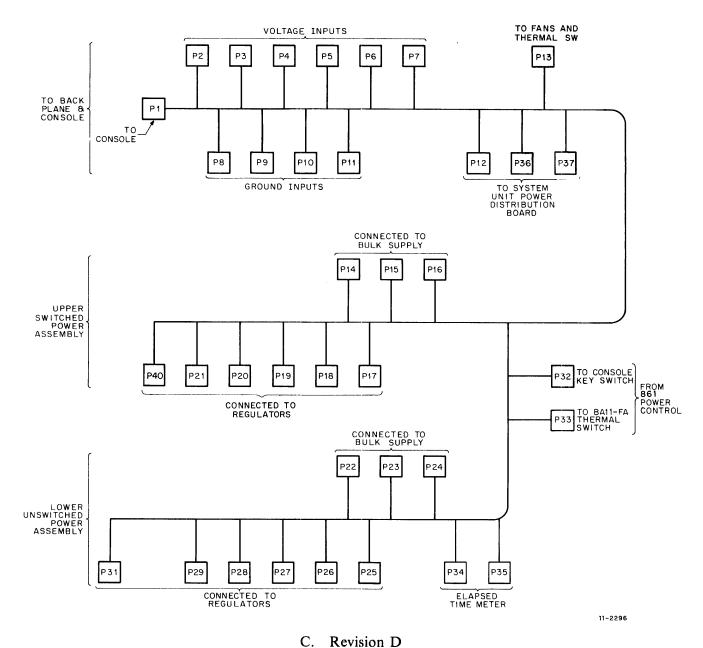

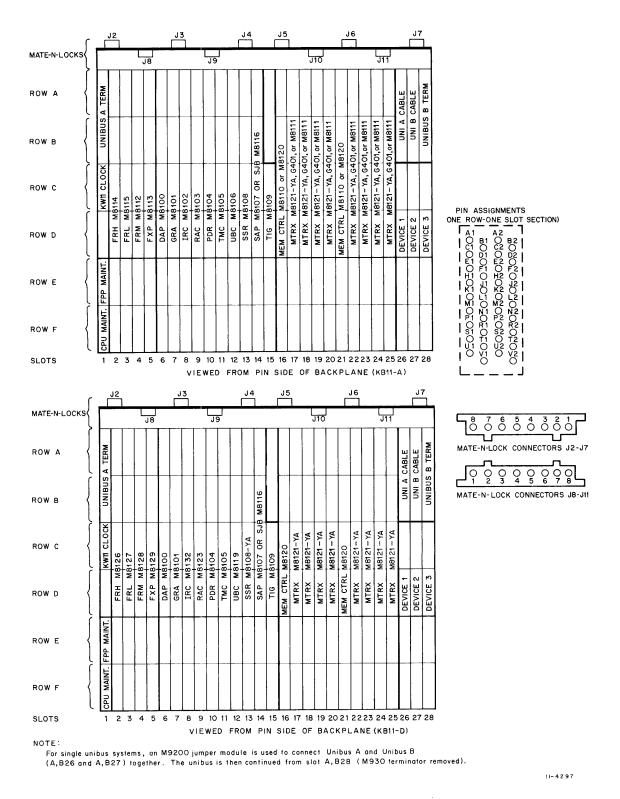

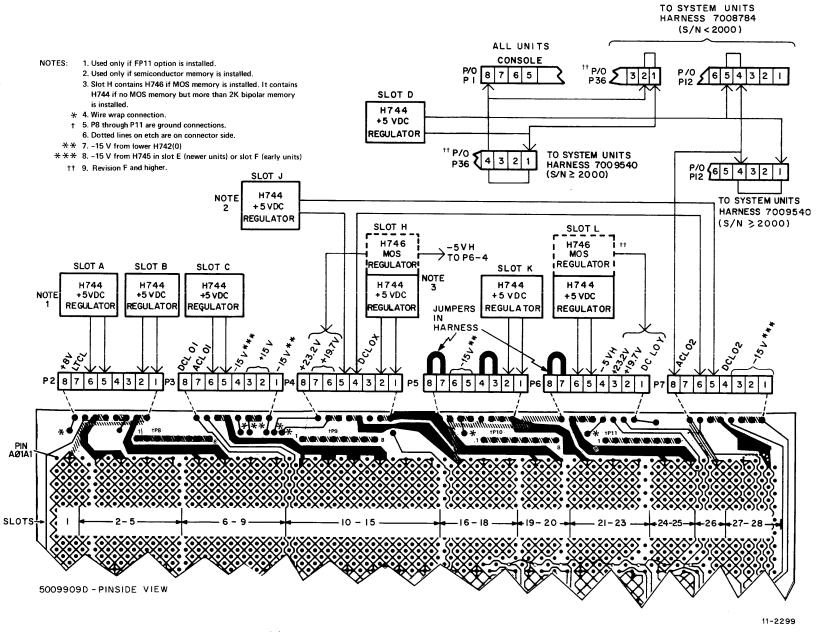

| 3-2                                               | Newer Versions (3rd and 4th) of Power System; CPU Cabinet Serial Numbers 2000 and Higher                                               |      |

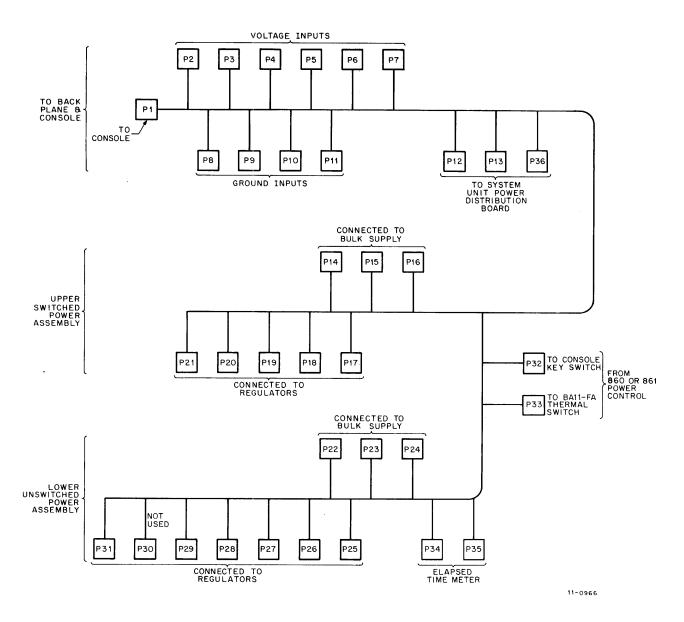

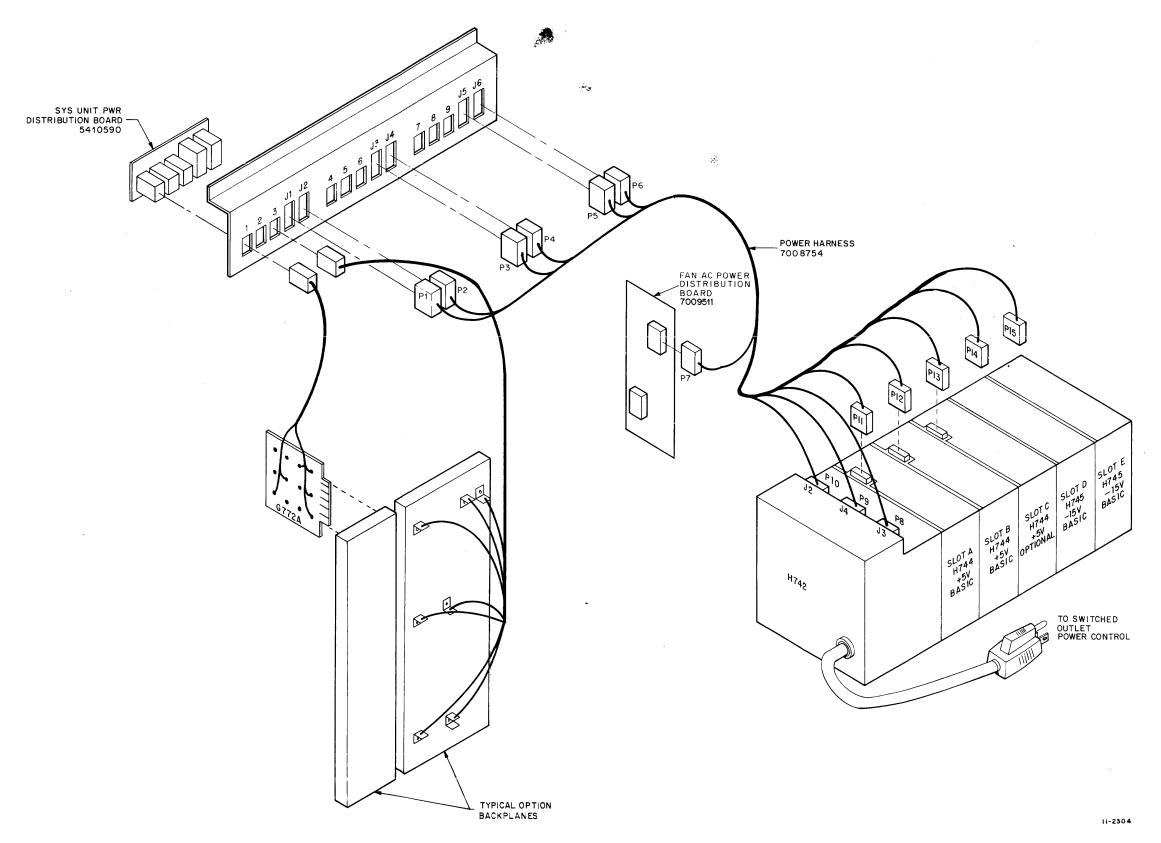

| 3-3                                               | Early Versions (1st and 2nd) of Power System; CPU Cabinet Serial Numbers Less Than 2000                                                | 3-7  |

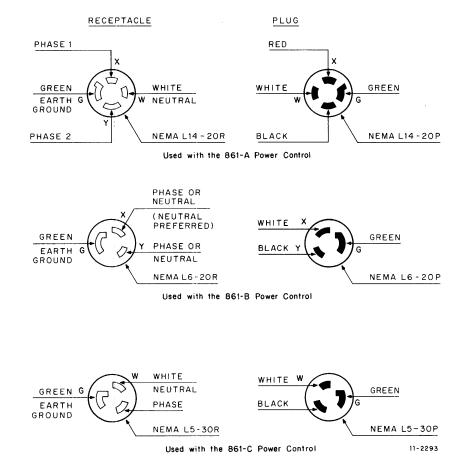

| 4-1                                               | Power Connectors                                                                                                                       | 4-2  |

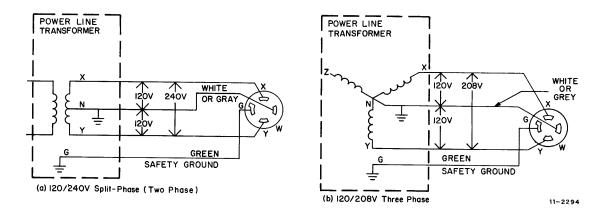

| 4-2                                               | Two-Phase Outlet Connections for Use with 861-A Power Control                                                                          | 4-3  |

| 4-3                                               | Example of Remote Power Control                                                                                                        | 4-4  |

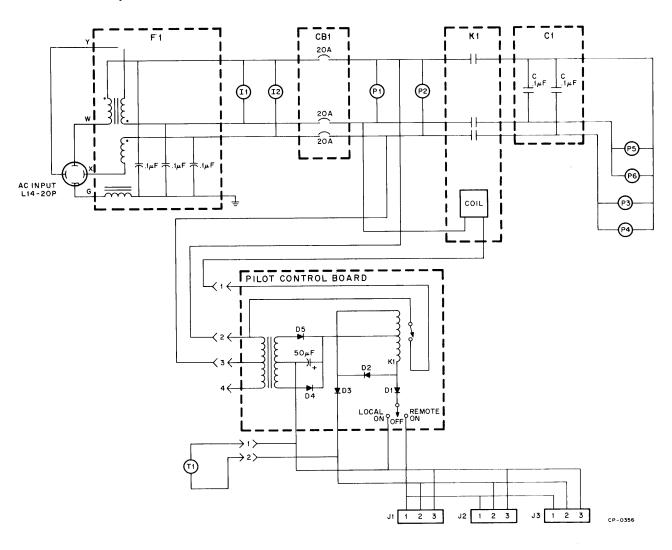

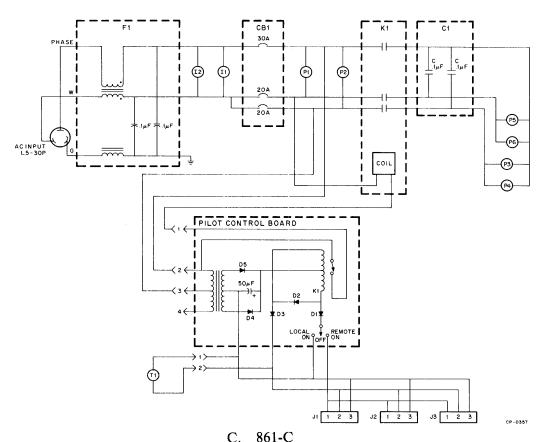

| 4-4                                               | 861 Power Controller Schematic                                                                                                         | 4-5  |

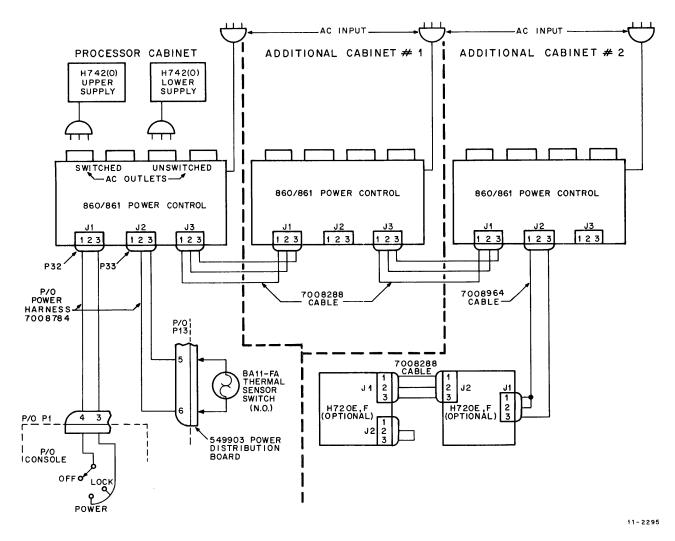

| 4-5                                               | Power System Configuration with Back-Up AC Power Source                                                                                |      |

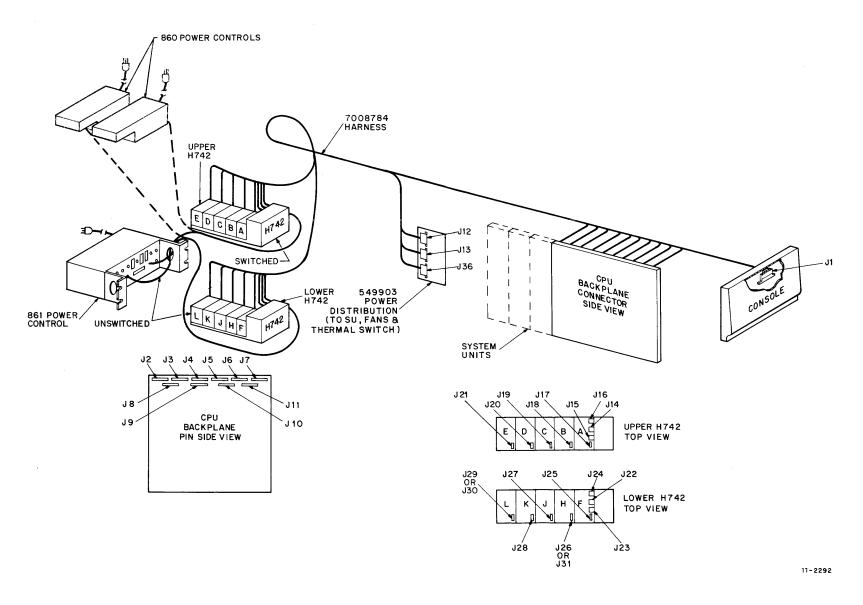

| 4-6                                               | AC Power Interconnections (H7420 and 861)                                                                                              |      |

| 4-7                                               | AC Power Interconnections (H742 and 861)                                                                                               |      |