# KDJ11-D/S CPU Module User's Guide

# KDJ11-D/S CPU Module User's Guide

# First Edition, April 1986 Second Edition, May 1987

Copyright ©1986,1987 by Digital Equipment Corporation.

#### All Rights Reserved.

Printed in U.S.A.

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

Using Digital's networked computer services, this book was produced electronically by the Educational Services Development and Publishing department in Reading, England.

The following are trademarks of Digital Equipment Corporation:

digital

DEC DECmate DECUS DECwriter DIBOL MASSBUS

PDP P/OS Professional Rainbow RSTS RSX RT UNIBUS VAX VMS VT

Work Processor

# Contents

| Pre | face    |       |                                     | х    |

|-----|---------|-------|-------------------------------------|------|

| Chá | apter 1 | Α     | RCHITECTURE                         |      |

| 1.1 | FEATUI  | RES . |                                     | 1–2  |

|     | 1.1.1   |       | rures Not Supported                 |      |

|     | 1.1.2   |       | isters                              |      |

| 1.2 | SYSTEM  | л CC  | NTROL REGISTERS                     | 1–7  |

|     | 1.2.1   |       | ressor Status Word                  |      |

|     | 1.2.2   |       | gram Interrupt Request              |      |

|     | 1.2.3   | CPU   | J Error Register                    | 1–10 |

|     | 1.2.4   |       | ntenance Register                   |      |

|     | 1.2.5   | Line  | Time Clock Register                 | 1–12 |

|     | 1.2.6   | Nat   | ve Register                         | 1–13 |

|     | 1.2.7   |       | ART Registers                       |      |

|     | 1.2     | .7.1  | Receiver Control/Status Register    | 1–14 |

|     | 1.2     | .7.2  | Receiver Data Buffer                | 1–15 |

|     | 1.2     | .7.3  | Transmitter Control/Status Register | 1–16 |

|     | 1.2     | .7.4  | Transmitter Data Buffer             | 1–17 |

| 1.3 | GENER A | AL P  | JRPOSE REGISTERS                    | 1–17 |

|     | 1.3.1   |       | k Pointer                           |      |

|     | 1.3.2   | Prog  | ram Counter                         | 1–19 |

| 1.4 | INTERR  | UPTS  | 6                                   | 1–19 |

|     | 1.4.1   | Halt  | Line                                | 1–21 |

|     | 1.4.2   | HAI   | T Instruction                       | 1–21 |

| 1.5 | MEMOR   | RY M  | ANAGEMENT                           | 1–22 |

|     | 1.5.1   | Phys  | ical Address Space                  | 1–22 |

|     | 1.5     | .1.1  | I/O Page                            | 1–23 |

|     | 1.5     | .1.2  | Self-test ROM                       | 1–24 |

|     | 1.5.    | .1.3  | Bootstrap                           | 1–25 |

|     |         |       |                                     |      |

|     | 1.5.2 Virt | ual Memory Mapping                                     |

|-----|------------|--------------------------------------------------------|

|     | 1.5.2.1    | 16-bit Mapping                                         |

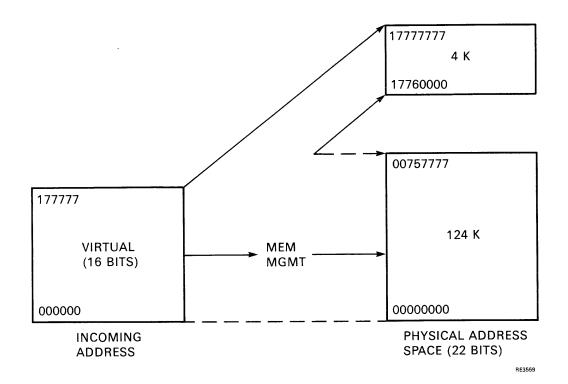

|     | 1.5.2.2    | 18-bit Mapping                                         |

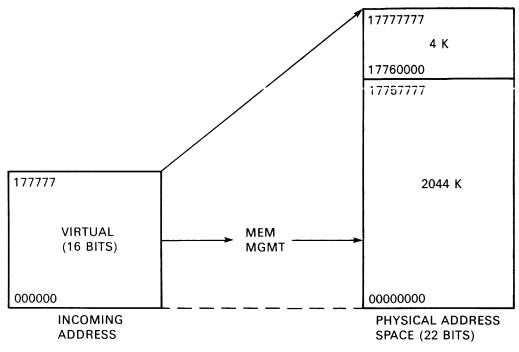

|     | 1.5.2.3    | 22-bit Mapping                                         |

|     | 1.5.3 Cor  | npatibility                                            |

|     | 1.5.4 Virt | ual Addressing                                         |

|     | 1.5.5 Inte | rrupts Under Memory Management Control                 |

|     | 1.5.6 Buil | lding a Physical Address                               |

|     | 1.5.7 Mai  | nagement Registers (PARs and PDRs)                     |

|     | 1.5.7.1    | Page Address Register                                  |

|     | 1.5.7.2    | Page Descriptor Register                               |

|     | 1.5.8 Fau  | lt Recovery Registers                                  |

|     | 1.5.8.1    | Memory Management Register 0                           |

|     | 1.5.8.2    | Memory Management Register 1                           |

|     | 1.5.8.3    | Memory Management Register 2                           |

|     | 1.5.8.4    | Memory Management Register 3                           |

|     | 1.5.8.5    | Instruction Back-up/Restart Recovery                   |

|     | 1.5.8.6    | Clearing Status Registers After an Abort               |

|     | 1.5.8.7    | Multiple Faults                                        |

|     | 1.5.9 Typ  | oical Usage                                            |

|     | 1.5.9.1    | Typical Memory Page1–40                                |

|     | 1.5.9.2    | Non-consecutive Memory Pages                           |

|     | 1.5.9.3    | Stack Memory Pages                                     |

| 1.6 | MEMORY S   | YSTEM REGISTERS                                        |

|     | 1.6.1 Me   | mory Error Register                                    |

| 1.7 | FLOATING-  | POINT                                                  |

|     | 1.7.1 Flo  | ating Point Registers                                  |

|     | 1.7.1.1    | Floating-point Status Register                         |

|     | 1.7.1.2    | Floating-point Exception Registers                     |

|     | 1.7.1.3    | Floating-point Accumulators                            |

|     |            |                                                        |

| Cha | apter 2 IN | ISTALLATION                                            |

|     |            |                                                        |

| 2.1 |            | AHON                                                   |

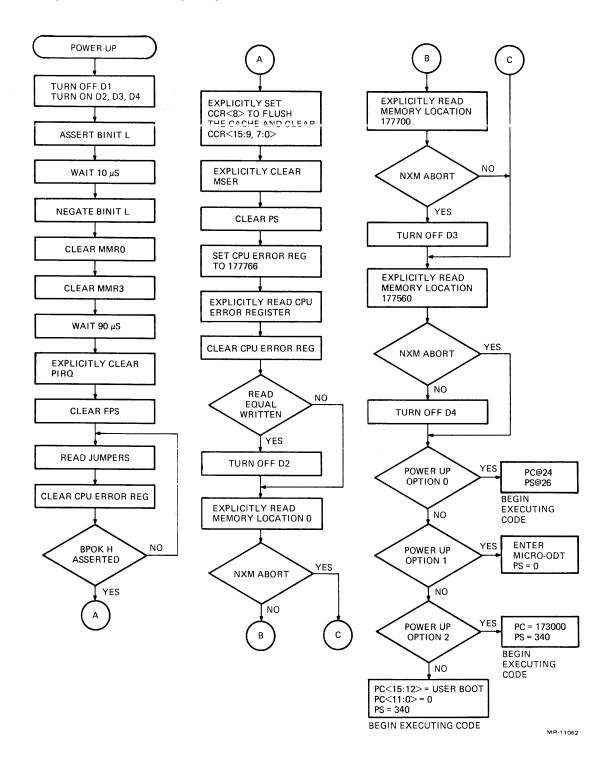

|     |            | ver-up Options                                         |

|     | 2.1.1.1    | Power-down Sequence 2–5                                |

|     | 2.1.1.2    | Tower-down Sequence                                    |

|     |            | otstrap options 1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1.1. |

|     |            | El Option                                              |

| 2.2 |            | ctory Configuration                                    |

| 2.2 |            | TIC LEDS                                               |

| 23  | MODULE E   | DGE CONNECTOR PINS                                     |

| 2.4  | HARDWARE OPTIONS                        |

|------|-----------------------------------------|

|      | 2.4.1 Restricted LSI-11 Options         |

| 2.5  | KDJ11-D/S INSTALLATION                  |

|      | 2.5.1 Pre-installation Considerations   |

|      | 2.5.2 System Differences                |

|      | 2.5.3 Installation Procedure            |

| 2.6  | SPECIFICATIONS                          |

|      |                                         |

| Cha  | apter 3 FUNCTIONAL DESCRIPTION          |

| 3.1  | INTRODUCTION                            |

| 3.2  | DCJ11 MICROPROCESSOR                    |

|      | 3.2.1 DCJ11 Cycles                      |

|      | 3.2.1.1 NIO                             |

|      | 3.2.1.2 Bus Read                        |

|      | 3.2.1.3 Bus Write                       |

|      | 3.2.1.4 GP Read                         |

|      | 3.2.1.5 GP Write                        |

|      | 3.2.1.6 IAK                             |

| 3.3  | AIO DECODER                             |

| 3.4  | GP DECODER                              |

| 3.5  | MEMORY DECODER                          |

| 3.6  | I/O DECODER                             |

| 3.7  | CYCLE DECODER                           |

| 3.8  | I/O READ/WRITE LOGIC3-20                |

| 3.9  | IAK DECODER AND VECTOR GENERATION LOGIC |

| 3.10 | MEMORY STATE MACHINE                    |

| 3.11 | BUS STATE MACHINE3-26                   |

| 3.12 | SACKTIMEUP, NXM, BBS7, BTWT3-26         |

|      | 3.12.1 SACKTIMEUP and NXM               |

|      | 3.12.2 BBS7 and BWTBT                   |

| 3.13 | PARITY AND ABORT3-29                    |

| 3.14 | REGISTERS                               |

|      | 3.14.1 Memory Error Register            |

|      | 3.14.2 Maintenance Register             |

|      | 3.14.3 Native Register                  |

|      | 3.14.4 Line Time Clock Register         |

| 3.15 | RAM ADDRESSING3-32                      |

|      | 3.15.1 Refresh                          |

| 3.16 | DLARTS                                  |

|      | 3 16 1 DLART Registers 2 25             |

# Chapter 4 BOOT AND DIAGNOSTIC ROM

| 4.1 | INTROL  | DUCTION 4-1                               |

|-----|---------|-------------------------------------------|

|     | 4.1.1   | Terminal Requirements                     |

| 4.2 | BOOT S  | SELECT                                    |

|     | 4.2.1   | Automatic-boot Mode                       |

|     | 4.2.2   | Console Mode                              |

|     | 4.2     | .2.1 Manual Start                         |

|     | 4.2.3   | ROM Part and Version Numbers              |

|     | 4.2.4   | Message Formats                           |

| 4.3 | CONSC   | DLE MODE                                  |

|     | 4.3.1   | Entering Console Mode Commands            |

|     | 4.3.2   | HELP Command                              |

|     | 4.3.3   | BOOT Command                              |

|     | 4.3.4   | LIST Command                              |

|     | 4.3.5   | MAP Command                               |

|     | 4.3.6   | TEST Command                              |

|     | 4.3.7   | WRAP Command                              |

| 4.4 | TEST RI | ESULTS                                    |

|     | 4.4.1   | Test 1 Errors                             |

|     | 4.4.2   | Test 2 Errors                             |

|     | 4.4.3   | Tests 3 through 6 Errors                  |

|     | 4.4     | .3.1 Test 3 Through 6 Error Messages      |

|     | 4.4     | .3.2 Commands to Override Errors          |

| 4.5 | AUTOM   | 1ATIC-BOOT MODE                           |

|     | 4.5.1   | Boot Code                                 |

|     | 4.5.2   | Automatic-boot Sequence (Autoboot)        |

|     | 4.5.3   | Bootstrap Error Messages                  |

|     | 4.5.4   | Disk and Tape Autoboot (Except TU58)      |

|     | 4.5.5   | DPV11, DUV11, DLV11-E/F and TU58 Autoboot |

|     | 4.5.6   | DEONA Autoboot                            |

|     | 4.5.7   | Bootable Media                            |

| 4.6 |         | VAGE SELECTION                            |

| 4.7 |         | LESHOOTING                                |

|     |         |                                           |

|     |         |                                           |

# Index

# Examples

|           | 4-1                          | Typical Automatic-boot Message                                                         |

|-----------|------------------------------|----------------------------------------------------------------------------------------|

|           | 4-2                          | Typical Power-up to Console Mode Message                                               |

|           | 4-3                          | Console Mode Prompt                                                                    |

|           | 4-4                          | Invalid Entry Message 4–9                                                              |

|           | 4-5                          | HELP Command                                                                           |

|           | 4-6                          | BOOT Command Argument Prompt                                                           |

|           | 4-7                          | BOOT Command Using DL2                                                                 |

|           | 4-8                          | LIST Command                                                                           |

|           | 4-9                          | MAP Command                                                                            |

|           | 4-10                         | TEST Command                                                                           |

|           | 4-11                         | WRAP Command Without Switch                                                            |

|           | 4-12                         | WRAP Command With Switch                                                               |

|           | 4-13                         | On-board RAM Test Error Message                                                        |

|           | 4-14                         | Q22-bus RAM Test Error Message                                                         |

|           | 4-15                         | J11 Unexpected Trap Error Message                                                      |

|           | 4-16                         | Language Inquiry and Error Prompt                                                      |

|           | 4-17                         | Unsuccessful Automatic-boot Message                                                    |

|           | 4-18                         | Console Mode Boot Error Message (1 of 2)                                               |

|           | 4-19                         | Console Mode Boot Error Message (2 of 2)                                               |

|           | 4-20                         | Language Inquiry                                                                       |

| <b></b> . |                              |                                                                                        |

| Figi      | ures                         |                                                                                        |

|           | 1-1                          | Registers                                                                              |

|           | 1-2                          | PSW (Processor Status Word) Register                                                   |

|           | 1-3                          | PIRQ (Program Interrupt Request) Register                                              |

|           | 1-4                          | CPU Error Register                                                                     |

|           | 1-5                          | Maintenance Register                                                                   |

|           | 1-6                          | LTC (Line Time Clock) Register (BEVNT)                                                 |

|           | 1-7                          | Native Register                                                                        |

|           | 1-8                          | Receiver Control/Status Register (RCSR)1–14                                            |

|           | 1-9                          | Receiver Data Buffer (RBUF)                                                            |

|           | 1-10                         | Transmitter Control/Status Register (XCSR)                                             |

|           | 1-11                         |                                                                                        |

|           |                              | Transmitter Data Buffer (XBUF)1–17                                                     |

|           | 1–12                         | Transmitter Data Buffer (XBUF)                                                         |

|           |                              | Physical Address Space                                                                 |

|           | 1–12                         | Physical Address Space                                                                 |

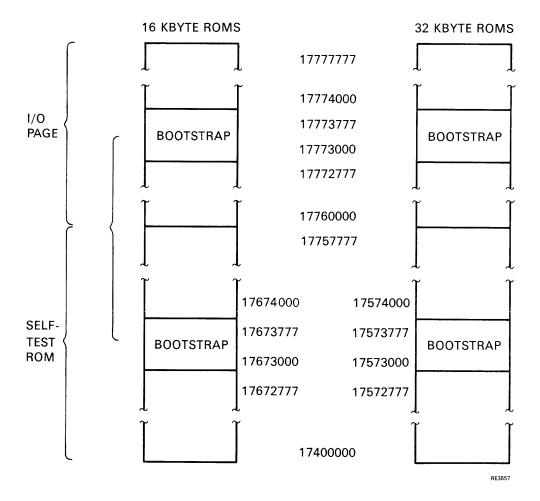

|           | 1–12<br>1–13                 | Physical Address Space1–23Self-test ROM Space1–24Bootstrap Space1–25                   |

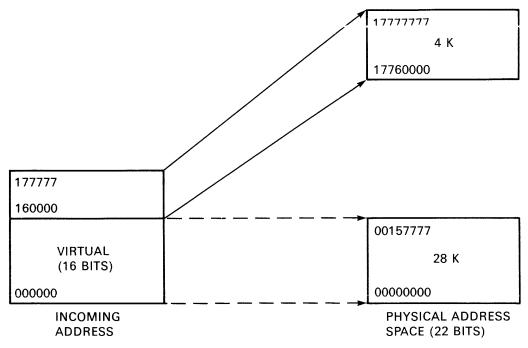

|           | 1–12<br>1–13<br>1–14         | Physical Address Space1–23Self-test ROM Space1–24Bootstrap Space1–2516-bit Mapping1–26 |

|           | 1-12<br>1-13<br>1-14<br>1-15 | Physical Address Space1–23Self-test ROM Space1–24Bootstrap Space1–25                   |

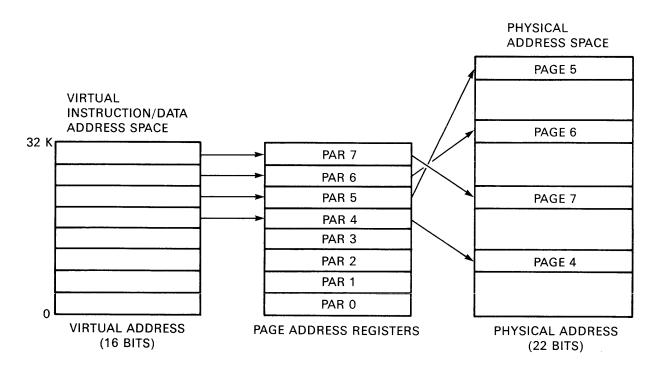

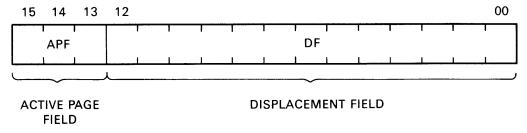

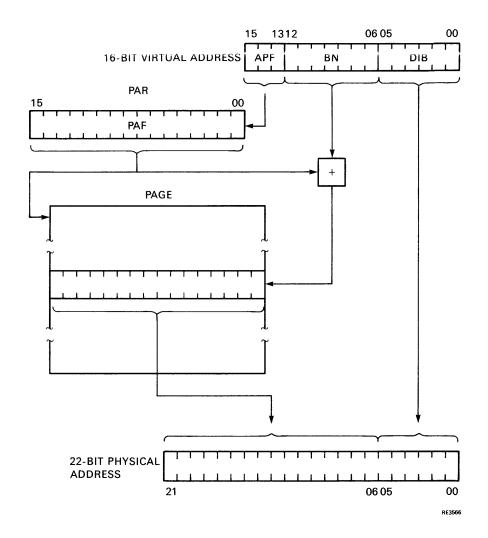

| 1-19 | Virtual Address Fields                   | l <b>–</b> 30 |

|------|------------------------------------------|---------------|

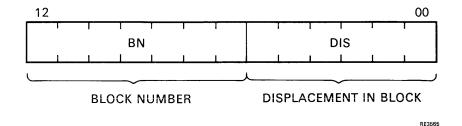

| 1-20 | Virtual Address Displacement Field       |               |

| 1-21 | Physical Address Assembly                | 1–32          |

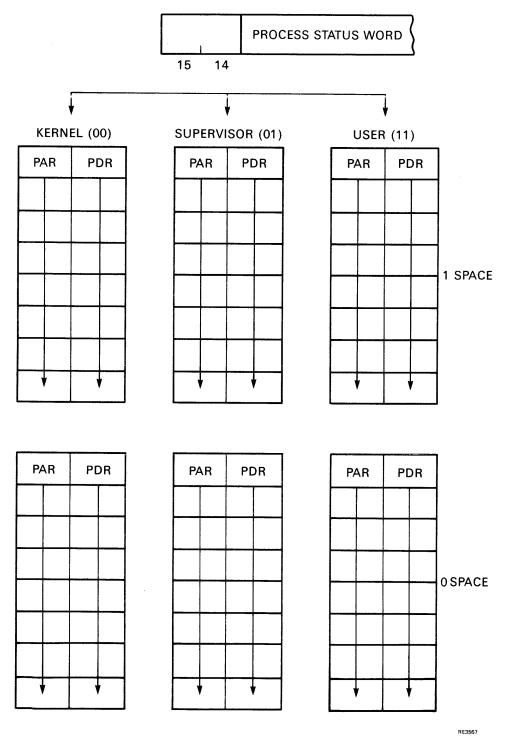

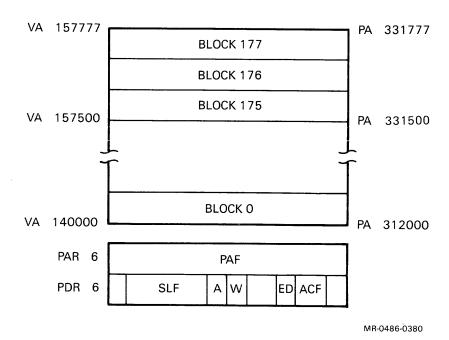

| 1-22 | Management Registers (PARs and PDRs)     |               |

| 1-23 | Page Address Register (PAR)              | 1–35          |

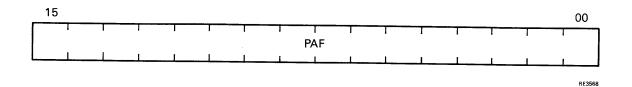

| 1-24 | Page Descriptor Register (PDR)           | 1–35          |

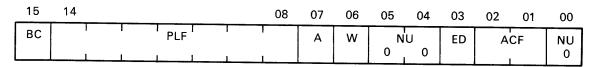

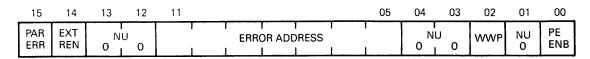

| 1-25 | Memory Management Register 0 (MMR0)      | 1–37          |

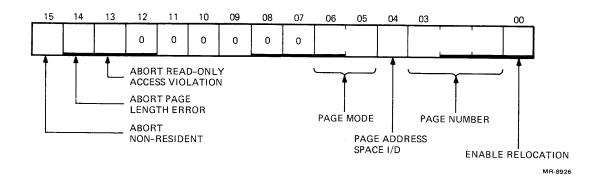

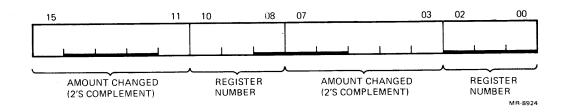

| 1-26 | Memory Management Register 1 (MMR1)      | 1–38          |

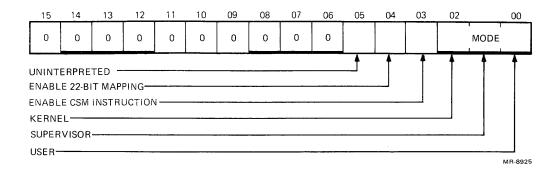

| 1-27 | Memory Management Register 3 (MMR3)      | 1–39          |

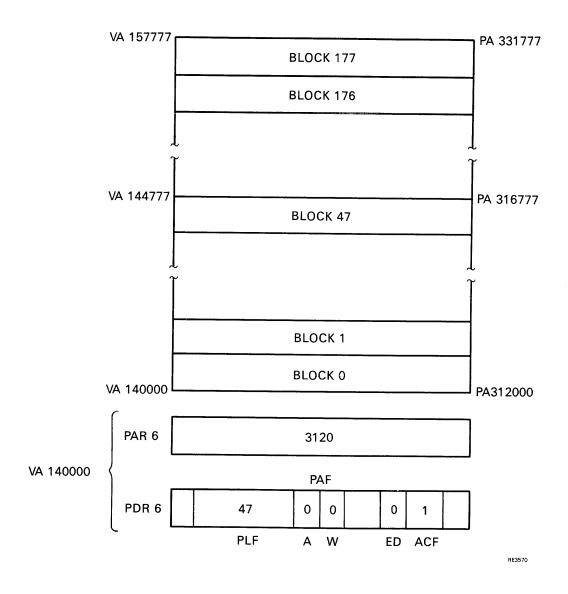

| 1-28 | Typical Memory Page                      | 1-41          |

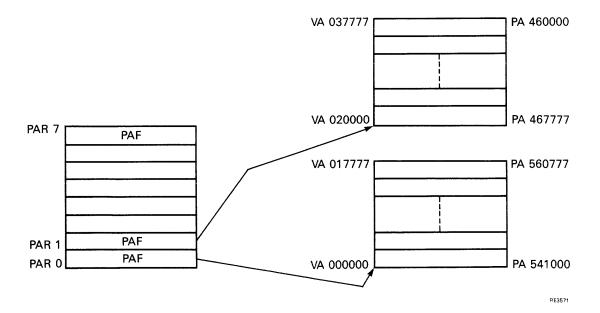

| 1-29 | Non-consecutive Memory Pages             |               |

| 1-30 | Typical Stack Memory Page                | 1-43          |

| 1-31 | Memory Error Register (MER)              |               |

| 1-32 | Floating-point Status Register (FPS)     |               |

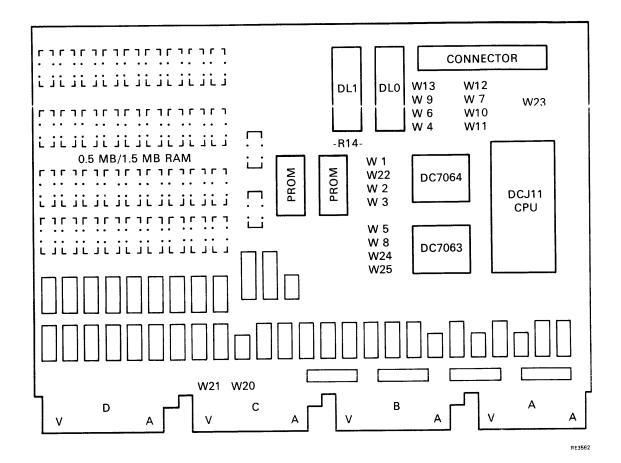

| 2-1  | KDJ11-D/S Module (M7554)                 | 2–2           |

| 2-2  | KDJ11-D/S Module - Early version (M7554) | 2–3           |

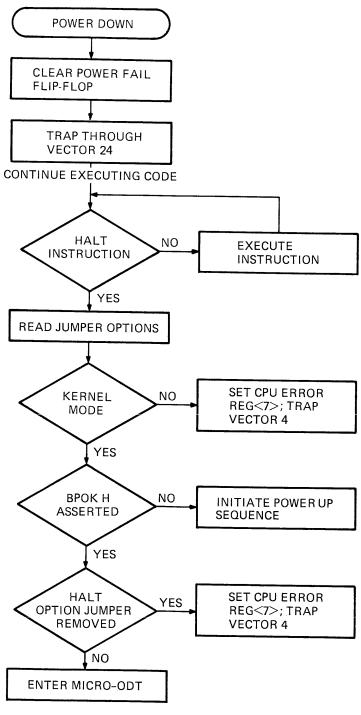

| 2–3  | Power-up Sequence                        |               |

| 2-4  | Power-down Sequence                      |               |

| 2-5  | Console ODT Exit Sequence                |               |

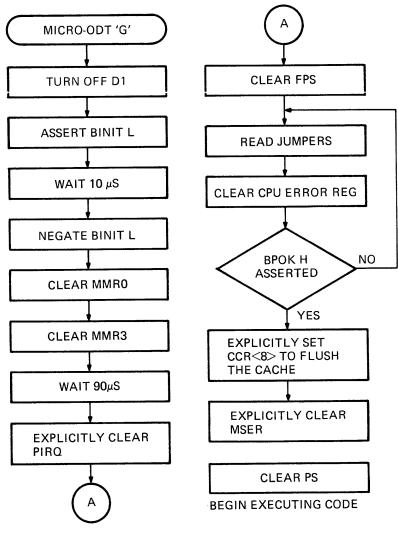

| 2-6  | Module Edge Connectors                   | 2–17          |

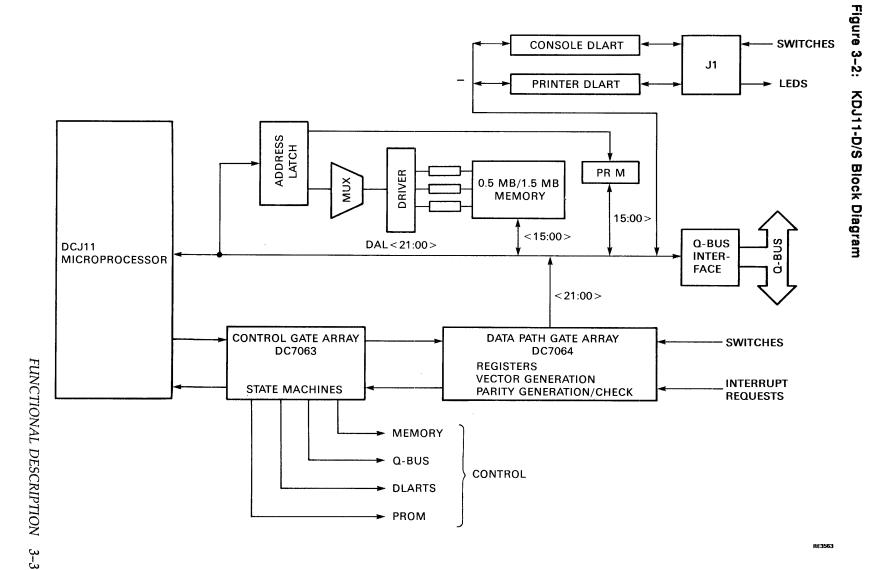

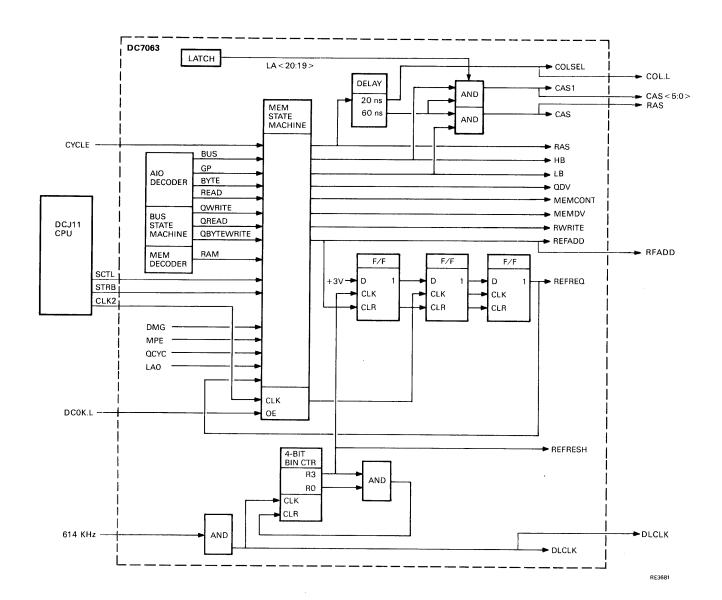

| 3–1  | KDJ11-DA Block Diagram                   |               |

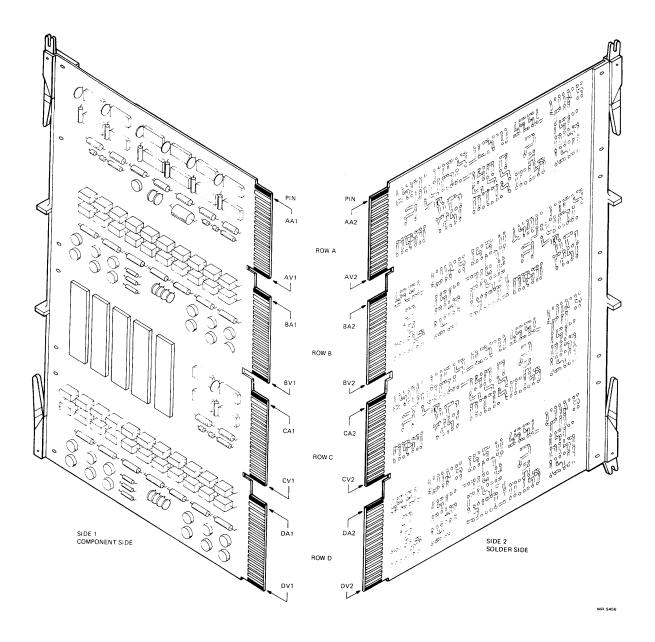

| 3-2  | KDJ11-D/S Block Diagram                  |               |

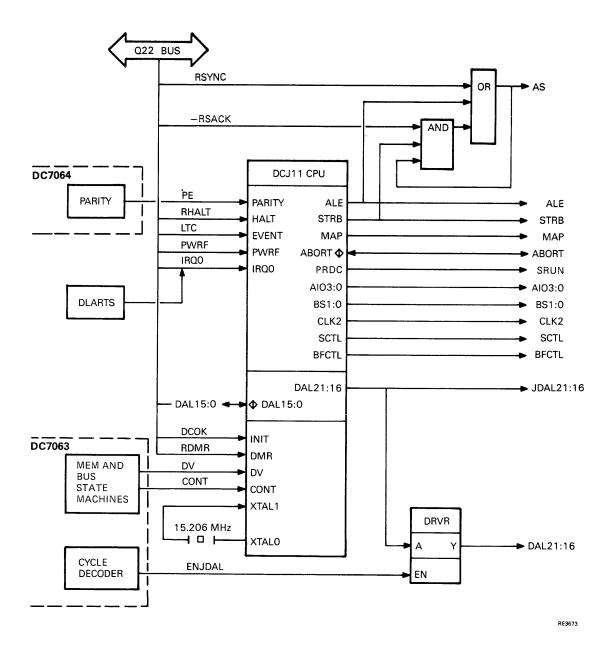

| 3–3  | DCJ11 CPU                                |               |

| 3–4  | AIO Decoder                              |               |

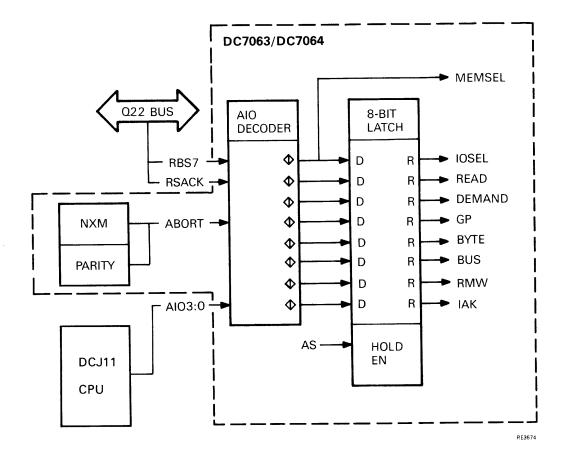

| 3-5  | GP Decoder                               |               |

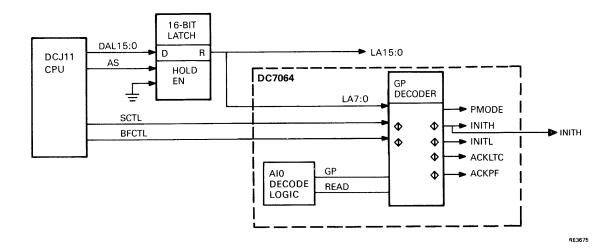

| 3-6  | Memory Decoder                           |               |

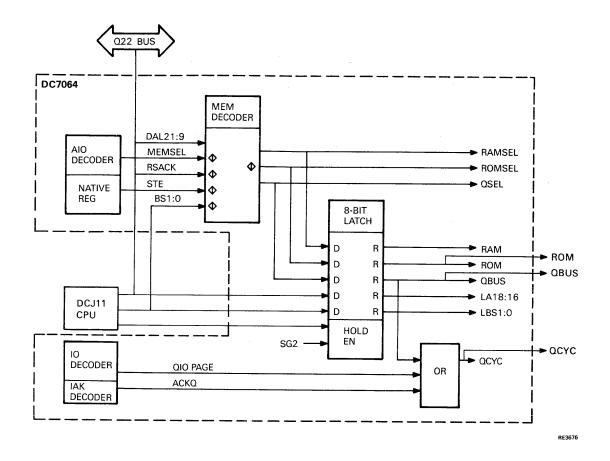

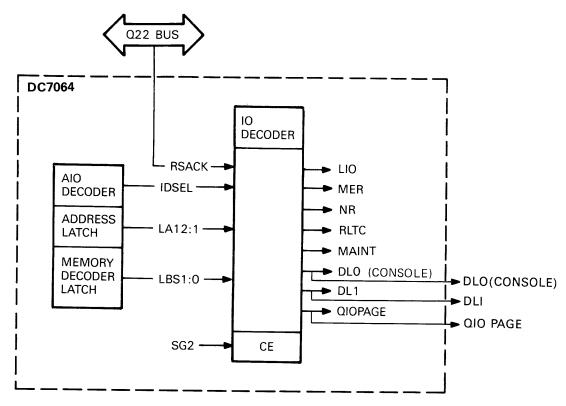

| 3–7  | I/O Decoder                              |               |

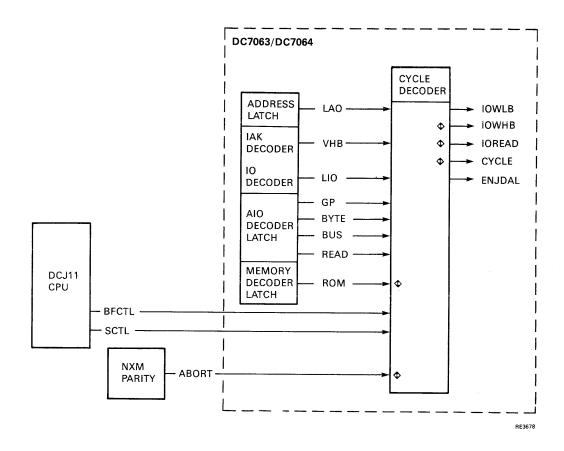

| 3-8  | Cycle Decoder                            |               |

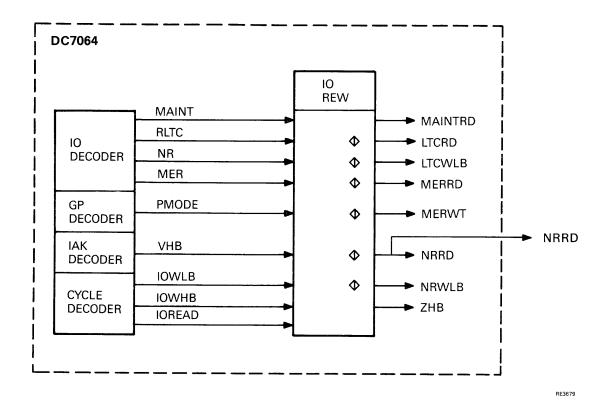

| 3-9  | I/O Read/Write logic                     |               |

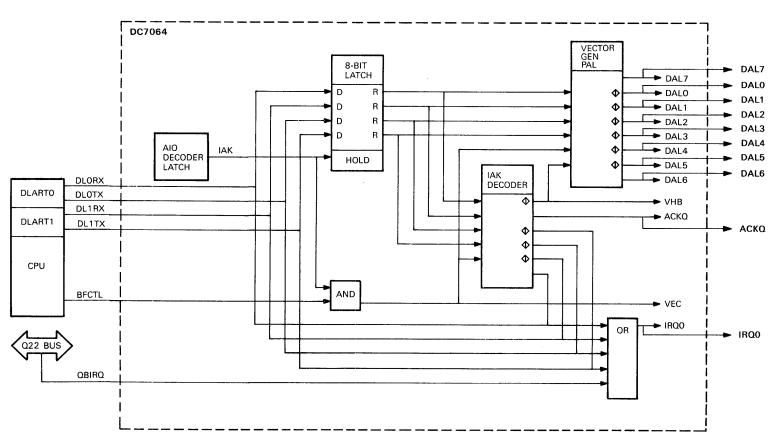

| 3–10 | IAK Decoder and Vector Generation Logic  |               |

| 3–11 | Memory State Machine                     |               |

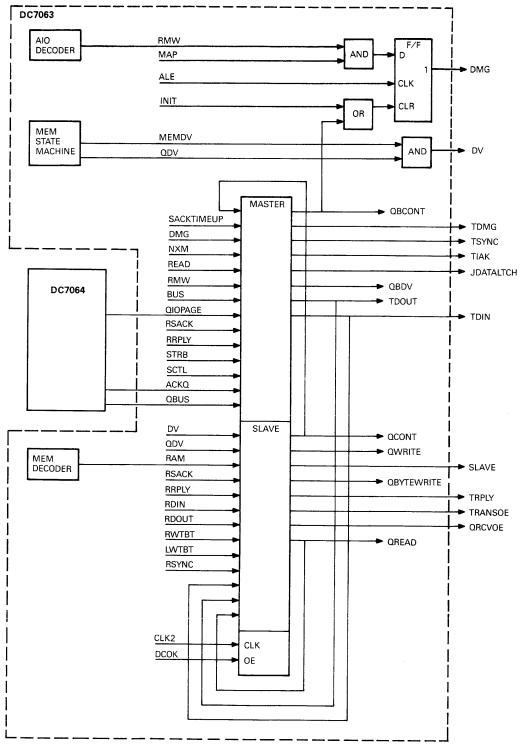

| 3–12 | Bus State Machine                        |               |

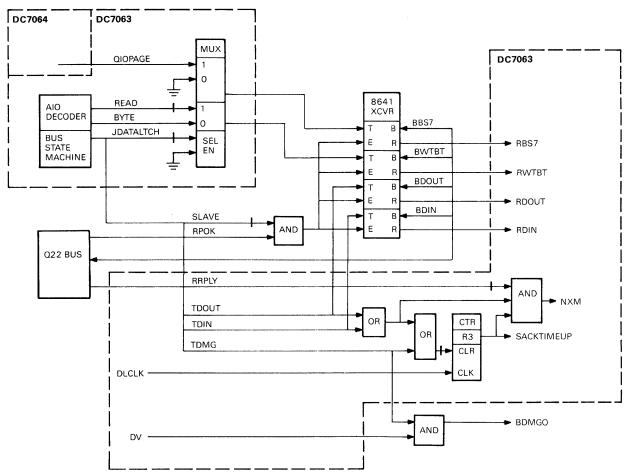

| 3–13 | SACKTIMEUP, NXM, BBS7, and BWTBT         |               |

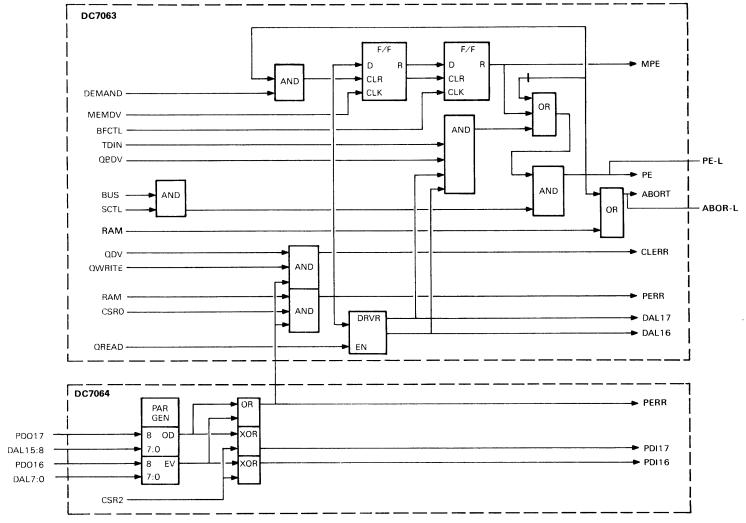

| 3–14 | Parity Error and Abort                   |               |

| 3–15 | Memory Error Register Access             |               |

| 3-16 | Maintenance Register Access              |               |

| 3-17 | Native Register Access                   |               |

| 3-18 | LTC Register Access                      |               |

| 3-19 | Memory Address Multiplexer               |               |

| 2 20 | DI APTo                                  | 3-37          |

# Tables

| <br> |                                                 |

|------|-------------------------------------------------|

| 1-1  | KDJ11 versions                                  |

| 1-2  | Address Map                                     |

| 1–3  | PSW (Processor Status Word) Bits                |

| 1-4  | PIRQ (Program Interrupt Request) Bits           |

| 1-5  | CPU Error Register Bits                         |

| 1-6  | Maintenance Register Bits                       |

| 1-7  | LTC (Line Time Clock) Register Bits             |

| 1-8  | Native Register Bits                            |

| 1-9  | Receiver Control/Status Register (RCSR) Bits    |

| 1-10 | Receiver Data Buffer (RBUF) Bits                |

| 1-11 | Transmitter Control/Status Register (XCSR) Bits |

| 1-12 | Transmitter Data Buffer (XBUF) Bits             |

| 1-13 | General Purpose Registers                       |

| 1-14 | Stack Pointer Selection                         |

| 1-15 | Asynchronous Interrupts                         |

| 1-16 | Synchronous Interrupts                          |

| 1-17 | Interrupt Priorities                            |

| 1-18 | KDJ11-D/S Compatibility                         |

| 1-19 | Virtual Address Description                     |

| 1-20 | Displacement Field Description                  |

| 1-21 | Page Descriptor Register (PDR) Bits             |

| 1-22 | Memory Management Register 0 (MMR0) Bits        |

| 1-23 | Memory Management Register 3 (MMR3) Bits        |

| 1-24 | Memory Error Register (MER) Bits                |

| 1-25 | Floating-point Status (FPS) Bits                |

| 2-1  | Jumpers                                         |

| 2-2  | Boot Select Options                             |

| 2-3  | Self-test ROM Display Codes                     |

| 2-4  | J1 Pin Assignments                              |

| 2-5  | Module Edge Connector Pin Assignments           |

| 2-6  | Restricted or Non-compatible LSI-11 Options     |

| 2-7  | KDJ11-D/S Specifications                        |

| 3-1  | DCJ11 Input and Output Signals                  |

| 3–2  | AIO<3:0> Codes                                  |

| 3-3  | BS<1:0> Codes                                   |

| 3-4  | GP Codes                                        |

| 3-5  | AIO Decoder Outputs                             |

| 3-6  | GP Decoder Outputs                              |

| 3-7  | Memory Decoder Outputs                          |

| 3-8  | I/O Decoder Outputs 3–17                        |

| 3-9  | Cycle Decoder Outputs                      |

|------|--------------------------------------------|

| 3-10 | I/O Read/Write Logic Outputs               |

| 3-11 | IAK Decoder Outputs                        |

| 3-12 | Vector Generation logic Outputs            |

| 4-1  | Terminal Requirements                      |

| 4-2  | Native Register Boot Select Codes          |

| 4-3  | ROM Status Codes 4-4                       |

| 4-4  | Manual Restart Addresses                   |

| 4-5  | Console Mode Commands                      |

| 4-6  | BOOT Command Interpretation                |

| 4-7  | Error Override commands                    |

| 4-8  | Q22-bus Boot Devices                       |

| 4-9  | Boot Device Errors                         |

| 4-10 | Disk and Tape Boot List                    |

| 4-11 | DPV, DUV, DLV, TU58 and RK05 Autoboot List |

# **Preface**

#### INTRODUCTION

The KDJ11-D/S CPU module is a low-cost quad-height processor module for use in extended LSI-11 bus (Q22-bus) systems. It is based on the DCJ11 microprocessor, and executes the PDP11/73 instruction set.

#### **PURPOSE**

This user's guide provides first-time and sophisticated users of the KDJ11-D/S CPU Module with the information to install, test, operate, and troubleshoot the module.

#### INTENDED AUDIENCE

This user's guide is written for end users, COEMs, TOEMs, and Field Service.

#### **REVISION NOTES**

This manual has been revised to reflect the re-engineered KDJ11-DA. The re-engineered version is referred to in this manual as the KDJ11-D/S. Where differences occur, both the new and the previous version will be described.

#### **GUIDE CONTENT**

This user's guide contains four chapters and an index. The following list describes the primary content of each chapter.

#### 1. Architecture

Describes KDJ11-D/S features, registers, interrupt scheme, and memory management.

#### 2. Installation

Describes module configuration, options, power-up/down sequences, specifications, backplane pin-out, and installation.

#### 3. Functional Description

Briefly describes the functional operation of the major module components.

# 4. Boot ROMs and Diagnostics

Describes boot ROM routines and micro-diagnostics.

#### **RELATED INFORMATION**

This guide does not replicate generic PDP-11 information often found in other MicroPDP-11 CPU User's Guides. Such related information and its source documents are listed below.

- PDP-11 Architecture Handbook, EB-23657-18

- Addressing modes

- Instruction set.

- Floating-point instructions set.

- Programming techniques.

- Extended LSI-11 bus description.

- PDP-11 UNIBUS Processor Handbook, EB-26077-41

- Console ODT (On-line Debugging Technique) command descriptions and examples.

#### **ASSOCIATED DOCUMENTS**

| Order       |                                   |

|-------------|-----------------------------------|

| EB-26077-41 | PDP-11 UNIBUS Processor Handbook  |

| EB-23657-18 | PDP-11 Architecture Handbook      |

| EK-DCJ11-UG | DCJ11 Microprocessor User's Guide |

## **CONVENTIONS**

The notational conventions used in this guide are described in the following table.

| Convention               | Meaning                                                                                                                                                                                                    |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NOTE                     | Contains general information.                                                                                                                                                                              |  |  |  |

| CAUTION                  | Contains information to prevent damage to equipment.                                                                                                                                                       |  |  |  |

| <mm:nn></mm:nn>          | Read as ''mm through nn.'' This use of angle brackets and the colon indicates a bit field, or a set of lines or signals. For example, $A < 17:00 >$ is the mnemonic for address lines ''A17 through A00.'' |  |  |  |

| Addresses                | Unless otherwise noted, all addresses in this guide are in octal notation.                                                                                                                                 |  |  |  |

| k, M                     | Abbreviations for kilo, Mega. When used with bytes and words, k and M represent the actual decimal value of quantities. For example:                                                                       |  |  |  |

|                          | 8 kbytes = 8192 bytes not 8000 bytes                                                                                                                                                                       |  |  |  |

|                          | 32 kwords = 32768 words not 32000 words                                                                                                                                                                    |  |  |  |

|                          | 512 kbytes = 524288 bytes not 512000 bytes                                                                                                                                                                 |  |  |  |

|                          | 4 Mbytes = 4194304 bytes not 4000000 bytes                                                                                                                                                                 |  |  |  |

| <ctrl n=""> or în</ctrl> | Control sequence. Press the <ctrl> key and the appropriate typing key at the same time.</ctrl>                                                                                                             |  |  |  |

| Abbreviations            | Abbreviations are in accordance with DEC STD 015, 3 February 1983.                                                                                                                                         |  |  |  |

# Chapter 1

# ARCHITECTURE

This chapter describes features of the KDJ11-D/S module, its registers, interrupt scheme, and memory management.

The range of three modules has been expanded to four modules, as shown in the following table.

Table 1-1: KDJ11 versions

| Old version |                     | New version | Comments             |  |

|-------------|---------------------|-------------|----------------------|--|

| KDJ11-DA    | Q-bus 0.5 Mb 15 MHz | KDJ11-DA    | Re-engineered        |  |

|             |                     | KDJ11-DB    | Q-bus 1.5 Mb 15 MHz  |  |

| KDJ11-SA    | BA200 0.5Mb 15 MHz  |             | Replaced by KDJ11-SC |  |

| KDJ11-SB    | BA200 0.5Mb 18 MHz  |             | Replaced by KDJ11-SD |  |

|             |                     | KDJ11-SC    | BA200 1.5 Mb 15 MHz  |  |

|             |                     | KDJ11-SD    | BA200 1.5 Mb 18 MHz  |  |

The are three main differences between the previous versions and the new versions of the boards. All the PALs and most of the discrete logic has been replaced by two gate arrays. This has made room on board for an optional increase in on-board memory from 0.5 Mb to 1.5 Mb. As a result of the change in physical layout, the position of the jumpers has been changed, although the previous numbers have been retained. Details of the jumpers will be covered in Chapter 2

# 1.1 FEATURES

The KDJ11-D/S CPU module (part number M7554) is a low-cost quad-height single board computer for use in extended LSI-11 bus (Q22-bus) systems. It is based on the DCJ11 microprocessor chip, and executes the PDP11/73 instruction set. The module includes the CPU, memory management, local memory, and I/O.

The CPU executes the full PDP11 integer instruction set. Floating point instructions are standard on the KDJ11-D/S; however, the FPA (Floating-point Accelerator) is not an option. Full 22-bit memory management is provided for both instruction and data references in three protection modes: kernel, supervisor, and user. (These are also called operating modes.)

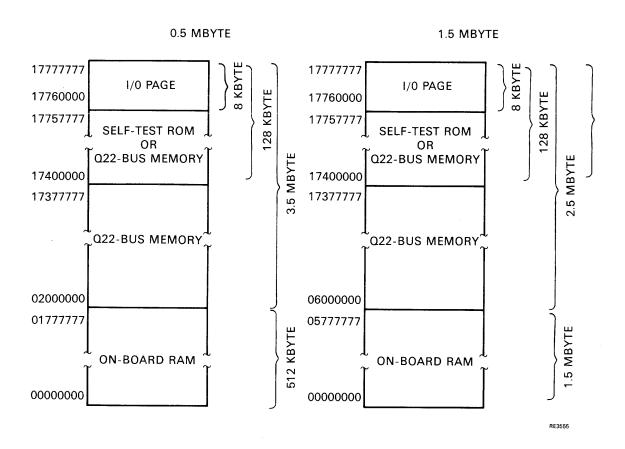

The KDJ11-D/S can address up to 4 Mbytes of memory. The module includes 0.5 Mbytes or 1.5 Mbytes of local memory, as shown below:

- KDJ11-DA 0.5 Mbytes

- KDJ11-DB 1.5 Mbytes

- KDJ11-SA 0.5 Mbytes

- KDJ11-SC 1.5 Mbytes

- KDJ11-SD 1.5 Mbytes (BA200 only)

An additional 3.5 Mbytes/2.5 Mbytes of memory can be addressed over the Q22-bus interface. Local (on-board) memory is 0.5 Mbytes/1.5 Mbytes of dynamic RAM with no battery back-up. Its starting address is fixed at 0.

All Q22-bus transaction types are supported. The KDJ11-D/S is the Q22-bus arbiter, and services only level 4 interrupts. Interrupt requests on levels 5, 6, or 7 are serviced at level 4 (BIRQ<5:7> are terminated and not connected to on-board logic).

The CPU supports power-up mode 2, bootstrap on power-up. The bootstrap starting address is fixed at 17773000 in the I/O page. Bootstrap and self-test routines are included in the on-board ROM. The ROMs can be either 32 kbytes (two 16-kbyte ROMs) or 64 kbytes (two 32-kbyte ROMs). Bootstrap options are selectable with on-board jumpers or through a remote switch. Seven indicator signal lines are provided to drive remote indicators for diagnostic purposes.

The HALT/trap option is supported with an on-board jumper. With the jumper removed, the CPU will trap through location 4 when a HALT instruction is executed in kernel mode. If the jumper is installed, the CPU will enter console ODT mode.

The module includes two DLARTs (DL-style UARTs (Universal Asynchronous Receiver/Transmitter)) for console and printer SLUs (Serial Line Units). DLART baud rate is selectable with on-board jumpers or remote switch. Halt on BREAK is jumper selectable in the console DLART.

# 1.1.1 Features Not Supported

The KDJ11-D/S CPU module does not have a cache memory. The FPA (Floating-point Accelerator) is not an option. Power-up modes 0 (power-fail), 1 (ODT), and 3 (user-defined starting address) are not supported.

## 1.1.2 Registers

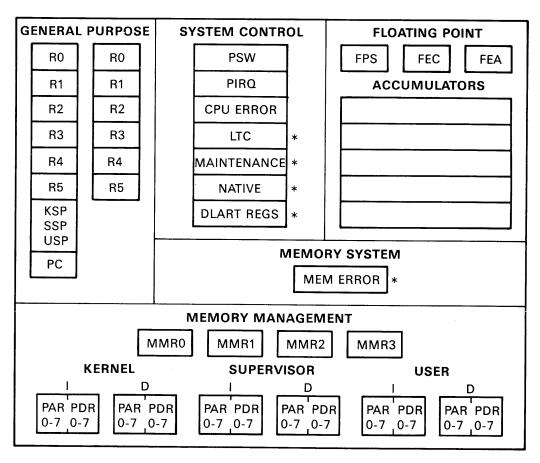

User-visible registers are shown in Figure 1–1. They are classified as: System Control, General Purpose, Memory System, Memory Management, and Floating Point registers. The addresses for the memory-addressable registers are listed in Table 1–2. These are user-visible registers which can be accessed with a 22-bit physical address. The other user-visible registers are referenced with the instruction set. Table 1-2 is an address map and lists the addresses and vectors for registers and other system devices.

Figure 1-1: Registers

\* EXTERNAL TO THE DCJ11

RE3547

Table 1-2: Address Map

| Register/Device                                                |                                                                      | Address                                                                                      | Vector                                                      |

|----------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| FPP (Floating Point Processor)                                 | )                                                                    | _                                                                                            | 244                                                         |

| PSW (Processor Status Word)                                    |                                                                      | 17777776                                                                                     | -                                                           |

| PIRQ (Program Interrupt Req                                    | uest)                                                                | 17777772                                                                                     | 240                                                         |

| CPU Error                                                      |                                                                      | 17777766                                                                                     | -                                                           |

| Maintenance                                                    |                                                                      | 17777750                                                                                     | -                                                           |

| Memory Error                                                   |                                                                      | 17772100                                                                                     | -                                                           |

| MMU (Memory Management                                         | Unit)                                                                |                                                                                              |                                                             |

| User Data                                                      | PAR 7<br>PAR 6<br>PAR 5<br>PAR 4<br>PAR 3<br>PAR 2<br>PAR 1<br>PAR 0 | 17777676<br>17777674<br>17777672<br>17777670<br>17777666<br>17777664<br>17777662<br>17777660 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250<br>250 |

| User Instruction                                               | PAR 7<br>PAR 6<br>PAR 5<br>PAR 4<br>PAR 3<br>PAR 2<br>PAR 1<br>PAR 0 | 17777656<br>17777654<br>17777652<br>17777650<br>17777646<br>17777644<br>17777642<br>17777640 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250<br>250 |

| User Data                                                      | PDR 7<br>PDR 6<br>PDR 5<br>PDR 4<br>PDR 3<br>PDR 2<br>PDR 1<br>PDR 0 | 17777636<br>17777634<br>17777632<br>17777630<br>17777626<br>17777624<br>17777622<br>17777620 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250<br>250 |

| User Instruction                                               | PDR 7<br>PDR 6<br>PDR 5<br>PDR 4<br>PDR 3<br>PDR 2<br>PDR 1<br>PDR 0 | 17777616<br>17777614<br>17777612<br>17777610<br>17777606<br>17777604<br>17777602<br>17777600 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250        |

| MMR2 (MMU Status 2<br>MMR1 (MMU Status 1<br>MMR0 (MMU Status 0 | ĺ)                                                                   | 17777576<br>17777574<br>17777572                                                             | 250<br><br>250                                              |

SLU 0 (Console Serial Line Unit 0)

Table 1-2 (Cont.): Address Map

| Register/Device                                                          |                                                                      | Address                                                                                      | Vector                                                      |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| Transmitter Buffer<br>Transmitter CSR<br>Receiver Buffer<br>Receiver CSR |                                                                      | 17777566<br>17777564<br>17777562<br>17777560                                                 | 64<br>64<br>60<br>60                                        |  |

| LTC (line time clock)                                                    |                                                                      | 17777546                                                                                     | 100                                                         |  |

| KDJ11-D/S Native Register                                                |                                                                      | 17777520                                                                                     | _                                                           |  |

| SLU 1 (General Purpose Seria                                             | l Line Unit 1)                                                       |                                                                                              |                                                             |  |

| Transmitter Buffer<br>Transmitter CSR<br>Receiver Buffer<br>Receiver CSR |                                                                      | 17776506<br>17776504<br>17776502<br>17776500                                                 | 304<br>304<br>300<br>300                                    |  |

| Bootstrap (512 bytes)                                                    |                                                                      | 17773776<br>through<br>17773000                                                              |                                                             |  |

| MMU (Memory Management                                                   | Unit)                                                                |                                                                                              |                                                             |  |

| MMR3 (MMU Status 3                                                       | )                                                                    | 17772516                                                                                     | 250                                                         |  |

| Kernel Data                                                              | PAR 7<br>PAR 6<br>PAR 5<br>PAR 4<br>PAR 3<br>PAR 2<br>PAR 1<br>PAR 0 | 17772376<br>17772374<br>17772372<br>17772370<br>17772366<br>17772364<br>17772362<br>17772360 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250        |  |

| Kernel Instruction                                                       | PAR 7<br>PAR 6<br>PAR 5<br>PAR 4<br>PAR 3<br>PAR 2<br>PAR 1<br>PAR 0 | 17772356<br>17772354<br>17772352<br>17772350<br>17772346<br>17772344<br>17772342<br>17772340 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250        |  |

| Kernel Data                                                              | PDR 7 PDR 6 PDR 5 PDR 4 PDR 3 PDR 2 PDR 1 PDR 0                      | 17772336<br>17772334<br>17772332<br>17772330<br>17772326<br>17772324<br>17772322<br>17772320 | 250<br>250<br>250<br>250<br>250<br>250<br>250<br>250<br>250 |  |

Table 1-2 (Cont.): Address Map

| ter/Device             |       | Address  | Vector |  |

|------------------------|-------|----------|--------|--|

| Kernel Instruction     | PDR 7 | 17772316 | 250    |  |

| retrie. met de de de   | PDR 6 | 17772314 | 250    |  |

|                        | PDR 5 | 17772312 | 250    |  |

|                        | PDR 4 | 17772310 | 250    |  |

|                        | PDR 3 | 17772306 | 250    |  |

|                        | PDR 2 | 17772304 | 250    |  |

|                        | PDR 1 | 17772302 | 250    |  |

|                        | PDR 0 | 17772300 | 250    |  |

|                        | PDRU  | 17772300 | 250    |  |

| Supervisor Data        | PAR 7 | 17772276 | 250    |  |

| •                      | PAR 6 | 17772274 | 250    |  |

|                        | PAR 5 | 17772272 | 250    |  |

|                        | PAR 4 | 17772270 | 250    |  |

|                        | PAR 3 | 17772266 | 250    |  |

|                        | PAR 2 | 17772264 | 250    |  |

|                        | PAR 1 | 17772262 | 250    |  |

|                        | PAR 0 | 17772260 | 250    |  |

|                        |       |          |        |  |

| Supervisor Instruction | PAR 7 | 17772256 | 250    |  |

| _                      | PAR 6 | 17772254 | 250    |  |

|                        | PAR 5 | 17772252 | 250    |  |

|                        | PAR 4 | 17772250 | 250    |  |

|                        | PAR 3 | 17772246 | 250    |  |

|                        | PAR 2 | 17772244 | 250    |  |

|                        | PAR 1 | 17772242 | 250    |  |

|                        | PAR 0 | 17772240 | 250    |  |

| Supervisor Data        | PDR 7 | 17772236 | 250    |  |

| Supervisor Data        | PDR 6 | 17772234 | 250    |  |

|                        | PDR 5 | 17772232 | 250    |  |

|                        | PDR 4 | 17772230 | 250    |  |

|                        | PDR 3 | 17772226 | 250    |  |

|                        | PDR 2 | 17772224 | 250    |  |

|                        |       | •        | 250    |  |

|                        | PDR 1 | 17772222 |        |  |

|                        | PDR 0 | 17772220 | 250    |  |

| Supervisor Instruction | PDR 7 | 17772216 | 250    |  |

| 1                      | PDR 6 | 17772214 | 250    |  |

|                        | PDR 5 | 17772212 | 250    |  |

|                        | PDR 4 | 17772210 | 250    |  |

|                        | PDR 3 | 17772206 | 250    |  |

|                        | PDR 2 | 17772204 | 250    |  |

|                        | PDR 1 | 17772202 | 250    |  |

|                        | PDR 0 | 17772200 | 250    |  |

Table 1-2 (Cont.): Address Map

| Register/Device            | Address                         | Vector |

|----------------------------|---------------------------------|--------|

| Self Test ROM (120 kbytes) | 17400000<br>through<br>17757777 |        |

| User RAM (0.5 Mbytes)      | 00000000<br>through<br>01777777 |        |

| User RAM (1.5 Mbytes)      | 00000000<br>through<br>05777777 |        |

# 1.2 SYSTEM CONTROL REGISTERS

These registers, shown in Figure 1–1, control system functions.

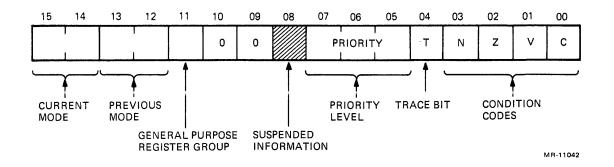

# 1.2.1 Processor Status Word

Address: 17777776

The PSW (Processor Status Word) Register contains:

- Current and previous operating mode

- General purpose register group in use

- Current priority level

- Condition code status

- Trace/trap bit for debugging

The PSW is initialized at power-up and cleared with a console start. See Figure 1-2 and Table 1-3.

Figure 1-2: PSW (Processor Status Word) Register

Table 1-3: PSW (Processor Status Word) Bits

| Bit     | Access | Description                                                                                |                                                                 |  |  |

|---------|--------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| <15:14> | R/W    | Current Mo                                                                                 | ode—Indicate the current operating mode as follows:             |  |  |

|         |        | Bit                                                                                        | Mode                                                            |  |  |

|         |        | 15 14<br>0 0<br>0 1<br>1 0<br>1 1                                                          | Kernel<br>Supervisor<br>Illegal<br>User                         |  |  |

| <13:12> | R/W    | Previous Mode—Indicate the previous operating mode, and are coded the sam as bits <15:14>. |                                                                 |  |  |

| <11>    | R/W    | Register Se                                                                                | —Selects the current general purpose register set, as follows:  |  |  |

|         |        | Bit < 11 >                                                                                 | Register Set                                                    |  |  |

|         |        | 0<br>1                                                                                     | R0 through R5<br>R0' through R5'                                |  |  |

| <10:09> | R      | not used                                                                                   |                                                                 |  |  |

| < 08>   |        | Suspended                                                                                  | Information—reserved                                            |  |  |

| <07:05> | R/W    | Priority Lev                                                                               | el—Indicate the processor's current priority level, as follows: |  |  |

Table 1-3 (Cont.): PSW (Processor Status Word) Bits

| Bit  | Access | Description                                                                                                                                                                                                                                                             |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |        | Bit Level                                                                                                                                                                                                                                                               |

|      |        | 07 06 05                                                                                                                                                                                                                                                                |

|      |        | 1 1 1 7                                                                                                                                                                                                                                                                 |

|      |        | 1 1 0 6                                                                                                                                                                                                                                                                 |

|      |        | 1 0 1 5                                                                                                                                                                                                                                                                 |

|      |        | 1 0 0 4                                                                                                                                                                                                                                                                 |

|      |        | 0 1 1 3<br>0 1 0 2                                                                                                                                                                                                                                                      |

|      |        | 0 0 1 1 1                                                                                                                                                                                                                                                               |

|      |        | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                   |

| <04> | R/W    | Trap—Inactive when cleared. When set, the processor traps to location 14 at the end of the current instruction. Used for debugging and setting breakpoints, this bit cannot be explicitly set by writing the PSW; it can be changed only with the RTI/RTT instructions. |

| <03> | R/W    | Condition code N—Set when the result of the previous operation is negative.                                                                                                                                                                                             |

| <02> | R/W    | Condition code Z—Set when the result of the previous operation is zero.                                                                                                                                                                                                 |

| <01> | R/W    | Condition code V—Set when the previous operation resulted in an overflow.                                                                                                                                                                                               |

| <00> | R/W    | Condition code C—Set when the previous operation caused a carry-out.                                                                                                                                                                                                    |

# 1.2.2 Program Interrupt Request

Address: 17777772

The PIRQ (Program Interrupt Request) Register implements software interrupts. Setting one of bits <15:09> corresponds to a request on one of the priority levels 7:1. See Figure 1–3 and Table 1–4. Hardware sets bits <07:05> and <03:01> to the encoded value of the highest priority request pending. When the interrupt is acknowledged, the processor vectors to location 240 for the service routine. (The service routine must clear the interrupt request.) The PIRQ Register is cleared by power-up, console start, or the RESET instruction.

Figure 1-3: PIRQ (Program Interrupt Request) Register

| 15       | 14       | 13       | 12       | 11       | 10       | 09       | 80      | 07           | 05 | 04      | 03 | 01    | 00      |

|----------|----------|----------|----------|----------|----------|----------|---------|--------------|----|---------|----|-------|---------|

| PIR<br>7 | PIR<br>6 | PIR<br>5 | PIR<br>4 | PIR<br>3 | PIR<br>2 | PIR<br>1 | NU<br>O | ENC(<br>VALU |    | NU<br>O |    | CODED | NU<br>O |

MR-9013

Table 1-4: PIRQ (Program Interrupt Request) Bits

| Bit     | Access | Description                                                            |  |  |  |

|---------|--------|------------------------------------------------------------------------|--|--|--|

| <15>    | R/W    | Priority Level 7—When set, requests an interrupt on level 7.           |  |  |  |

| <14>    | R/W    | Priority Level 6—When set, requests an interrupt on level 6.           |  |  |  |

| <13>    | R/W    | Priority Level 5—When set, requests an interrupt on level 5.           |  |  |  |

| <12>    | R/W    | Priority Level 4—When set, requests an interrupt on level 4.           |  |  |  |

| <11>    | R/W    | Priority Level 4—When set, requests an interrupt on level 3.           |  |  |  |

| <10>    | R/W    | Priority Level 2—When set, requests an interrupt on level 2.           |  |  |  |

| <09>    | R/W    | Priority Level 1—When set, requests an interrupt on level 1.           |  |  |  |

| <08>    |        | not used                                                               |  |  |  |

| <07:05> | R      | Encoded Value—Indicate the highest priority level set in bits <15:09>. |  |  |  |

| <04>    |        | not used                                                               |  |  |  |

| <03:01> | R      | Encoded Value—Same as bits < 07:05 > .                                 |  |  |  |

| <00>    |        | not used                                                               |  |  |  |

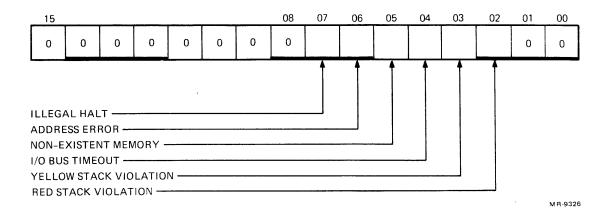

# 1.2.3 CPU Error Register

Address: 17777766

The CPU Error Register indicates the source of any trap or error condition that caused a trap through location 4. See Figure 1-4 and Table 1-5. The register is cleared by any write reference, power-up, or console start. It is not changed by the RESET instruction.

Figure 1-4: CPU Error Register

Table 1-5: CPU Error Register Bits

| Bit     | Access | Description                                                                                                                                               |  |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <15:08> |        | not used                                                                                                                                                  |  |

| <07>    | R      | Illegal HALT—Set when an attempt is made to execute a HALT instruction in user or supervisor mode. (See Maintenance Register $< 0.3 > 0.3$ ), Table 1–6.) |  |

| <06>    | R      | Address Error—Set when an attempt is made to either word-access an odd byte-address or to fetch an instruction from an internal register.                 |  |

| <05>    | R      | Non-existent Memory—Set when a reference to main memory times-out.                                                                                        |  |

| <04>    | R      | I/O Bus Time-out—Set when a reference to the I/O page times-out.                                                                                          |  |

| <03>    | R      | Yellow Stack Violation—Set on a yellow-zone stack-overflow trap (kernel mod stack reference less than 4008).                                              |  |

| <02>    | R      | Red Stack Violation—Set on a red stack-trap (a kernel stack-push abort durin an interrupt, abort, or stack sequence).                                     |  |

| <01:00> |        | not used                                                                                                                                                  |  |

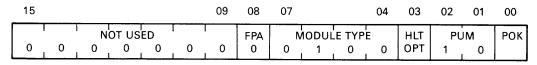

# 1.2.4 Maintenance Register

Address: 17777750

The Maintenance Register allows software to determine which power-up options are selected and if an FPA (floating point accelerator) is installed. See Figure 1–5 and Table 1–6.

Figure 1-5: Maintenance Register

RE3548

Table 1-6: Maintenance Register Bits

| Bit     | Access | Description                                                                                                                                                                                                                                                                                                                                             |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:09> | R      | not used—always read zero                                                                                                                                                                                                                                                                                                                               |

| < 08 >  | R      | FPA Here—Always reads zero. The FPA is not a KDJ11-D/S option.                                                                                                                                                                                                                                                                                          |

| <07:04> | R      | Module Type Number—Encoded value indicating the module type number. The KDJ11-D/S is module type four $(0100_2)$ .                                                                                                                                                                                                                                      |

| <03>    | R      | Halt Option—Indicates how a HALT instruction will execute in kernel mode. If jumper W1 is not installed the bit is set; when a HALT is executed, the KDJ11-D/S traps through location 4, and sets CPU Error Register < 07 > (Table 1–5). If jumper W1 is installed, the bit is cleared; when a HALT is executed, the KDJ11-D/S enters console ODT mode. |

| <02:01> | R      | Power-up Mode Option—Indicates the selected power-up mode option. The KDJ11-D/S supports only power-up mode 2 ( $10_2$ ), bootstrap at starting address 17773000.                                                                                                                                                                                       |

| <00>    | R      | Power OK—When set, indicates that Q22-bus signal BPOK is asserted H (system power is within tolerance and stable).                                                                                                                                                                                                                                      |

# 1.2.5 Line Time Clock Register

Address: 17777546

The LTC (Line Time Clock) Register controls recognition of the Q22-bus signal, BEVNT. See Figure 1-6 and Table 1-7.

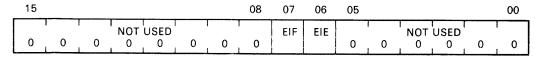

Figure 1-6: LTC (Line Time Clock) Register (BEVNT)

RE3549

Table 1-7: LTC (Line Time Clock) Register Bits

| Bit     | Access | Description                                                                                                                                                                                                                                                                      |  |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <15:08> | R      | not used—always read zero                                                                                                                                                                                                                                                        |  |

| <07>    | R      | Event Interrupt Flag—Indicates the state of the Q22-bus BEVNT signal when bit <06> is not set. If set when <06> is set, causes an interrupt through vector 100, at priority level 6. Must be deasserted and asserted (BEVNT asserted and deasserted) to cause another interrupt. |  |

| <06>    | R/W    | Event Interrupt Enable—When set, enables level 6 interrupts through ve 100. Cleared by power-up, reboot, or the RESEΓ instruction.                                                                                                                                               |  |

| <05:00> | R      | not used—always read zero                                                                                                                                                                                                                                                        |  |

# 1.2.6 Native Register

Address: 17777520

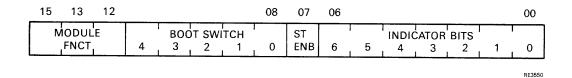

The Native Register (Figure 1–7) provides the test and boot functions described in Table 1–8.

Figure 1-7: Native Register

Table 1-8: Native Register Bits

| Bit     | Access | Description                      |                                                                                                                             |

|---------|--------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| <15:13> | R      | 15 = 1                           |                                                                                                                             |

|         |        | $ 14 = 0 \\ 14 = 1 $             | 0.5 Mbyte memory (on board) 1.5 Mbyte memory (on board).                                                                    |

|         |        | Bit 14 reflects<br>0.5 Mbytes of | the setting of jumper W25. The jumper is installed when there is memory, and is removed when there is 1.5 Mbytes of memory. |

|         |        | 13 = 0 $13 = 1$                  | Normal<br>For special applications.                                                                                         |

|         |        | Bit 13 reflects                  | the setting of jumper W4.                                                                                                   |

|         |        | Bits <15:13>                     | are always zero on early versions.                                                                                          |

Table 1-8 (Cont.): Native Register Bits

| Bit     | Access | Description                                                                                                                                                                                                                                                                                                                                |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <12:08> | R      | Boot Switch <4:0>—Binary coded value read by firmware to direct self-test and bootstrap program execution. Up to 32 routines can be selected, either with on-board jumpers W22, W2, W3, W5, and W8 (bits <12:08>, respectively), or with W22 (bit <12>) and a remote 16-position switch (bits <11:08>). See Table 2–2.                     |

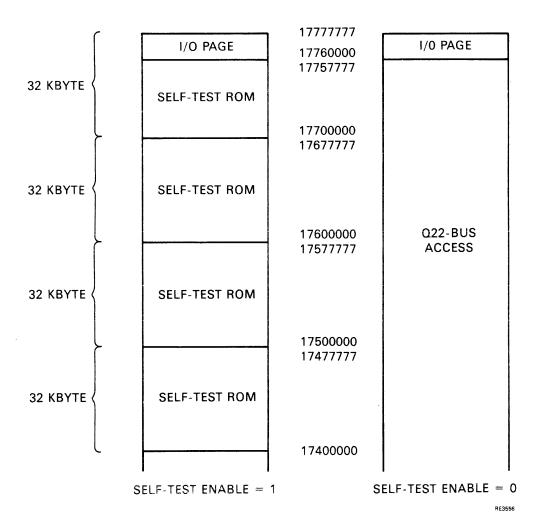

| <07>    | R/W    | Self-test Enable—When set, enables the Self-test ROM; that is, physical addresses 17400000 through 17757777 access Self-test ROM space. When cleared, disables the Self-test ROM; that is, physical addresses 17400000 through 17757777 access Q22-bus memory space. Cleared by power-up or reboot; not affected by the RESET instruction. |

| <06:00> | R/W    | Indicator $<6:0>$ —Indicate the state of lines IND $<6:0>$ . Cleared on power-up or reboot; not affected by the RESET instruction. The lines are connected to J1, to drive remote LEDs. The Self-test program reports its progress on IND $<3:0>$ . See Table 2–3.                                                                         |

## 1.2.7 DLART Registers

Each DLART contains the following registers.

RCSR (Receiver Control/Status Register)

RBUF (Receiver Data Buffer)

XCSR (Transmitter Control/Status Register)

XBUF (Transmitter Data Buffer)

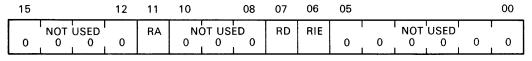

#### 1.2.7.1 Receiver Control/Status Register

Address: 17777560 (SLU 0), 17776500 (SLU 1)

Figure 1-8: Receiver Control/Status Register (RCSR)

RE3551

Table 1-9: Receiver Control/Status Register (RCSR) Bits

| Bit     | Access | Description                                                                                                                            |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------|

| <15:12> | R      | not used—always read 0                                                                                                                 |

| <11>    | R      | Receiver Active—When set, indicates that a start bit has been detected. Cleared when a stop bit is detected, or on power-up or reboot. |

Table 1-9 (Cont.): Receiver Control/Status Register (RCSR) Bits

| Bit Access |     | Description                                                                                                                                                                                              |  |  |  |  |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <10:08>    | R   | not used—always read 0                                                                                                                                                                                   |  |  |  |  |

| <07>       | R   | Receiver Done—When set, indicates that the serial interface has received a character; and requests an interrupt if $<06>$ is set. Cleared by reading the receiver data buffer, or on power-up or reboot. |  |  |  |  |

| <06>       | R/W | Receiver Interrupt Enable—When set, receiver interrupts are enabled (see <07>). When cleared, receiver interrupts are disabled. Cleared by power-up, reboot, or the RESET instruction.                   |  |  |  |  |

| <05:00>    | R   | not used—always read 0                                                                                                                                                                                   |  |  |  |  |

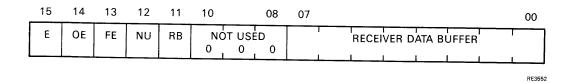

# 1.2.7.2 Receiver Data Buffer

Address: 17777562 (SLU 0), 17776502 (SLU 1)

Figure 1-9: Receiver Data Buffer (RBUF)

Table 1-10: Receiver Data Buffer (RBUF) Bits

| Bit     | Access | Description                                                                                                                                                                                                                                                                                            |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15>    | R      | Error—Set when $<14>$ or $<13>$ is set. Cleared when the error condition is cleared.                                                                                                                                                                                                                   |

| <14>    | R      | Overrun Error—When set, indicates that a new character was received before an old character was read. Will be set if Receiver Done (RCSR $<$ 07 $>$ ) was not cleared when a character was received. Cleared when a character is received and RCSR $<$ 07 $>$ = 0 (cleared), or on power-up or reboot. |

| <13>    | R      | Framing Error—When set, indicates that a received character did not have a valid stop bit. Cleared when a character with a valid stop bit is received, or on power-up or reboot.                                                                                                                       |

| <12>    | R      | not used—always read 0                                                                                                                                                                                                                                                                                 |

| <11>    | R      | Received Break—When set, indicates that the received signal has gone from a MARK to a SPACE, and stayed in the SPACE condition for 11 bit-times. Cleared when the received signal returns to a MARK, or on power-up or reboot.                                                                         |

| <10:08> | R      | not used—always read 0                                                                                                                                                                                                                                                                                 |

Table 1-10 (Cont.): Receiver Data Buffer (RBUF) Bits

| Bit     | Access | Description                                                                                                   |

|---------|--------|---------------------------------------------------------------------------------------------------------------|

| <07:00> | R      | Receiver Data Buffer—Set to the value of the most recently received character. Cleared by power-up or reboot. |

## 1.2.7.3 Transmitter Control/Status Register

Address: 17777564 (SLU 0), 17776504 (SLU 1)

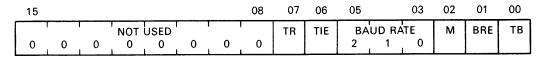

Figure 1-10: Transmitter Control/Status Register (XCSR)

RE3553

Table 1-11: Transmitter Control/Status Register (XCSR) Bits

| Bit     | Access | Description                                                                                                                                                                                                                                      |  |  |  |  |  |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <15:08> | R      | not used—always read 0                                                                                                                                                                                                                           |  |  |  |  |  |

| < 07 >  | R      | Transmitter Ready—When set, indicates that the Transmitter Buffer is empty and can accept a new character for transmission; and requests an interrupt if <06> is set. Set on power-up or reboot. Cleared by writing into the Transmitter Buffer. |  |  |  |  |  |

| <06>    | R/W    | Transmitter Interrupt Enable—Set to enable transmitter interrupts (see $<07>$ ). Cleared to disable transmitter interrupts. Cleared by power-up, reboot, or the RESET instruction.                                                               |  |  |  |  |  |

| <05:03> | R/W    | Baud Rate Select—In the KDJ11-D/S, these bits are ALWAYS CLEARED (see <01>).                                                                                                                                                                     |  |  |  |  |  |

|         |        | (In other applications, if $<01>$ is set, these bits determine the transmit/receive baud rate under program control, and are cleared when $<01>$ is cleared, on power-up, or on reboot.)                                                         |  |  |  |  |  |

| <02>    | R/W    | Maintenance—When set, the external receiver input is disconnected and the transmitter output is connected to the receiver input. Cleared by power-up, reboot, or the RESET instruction.                                                          |  |  |  |  |  |

Table 1-11 (Cont.): Transmitter Control/Status Register (XCSR) Bits

| Bit  | Access | Description                                                                                                                                                                                                                                                                                                                      |

|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <01> | R/W    | Baud Rate Enable—In the KDJ11-D/S, this bit is ALWAYS CLEARED. The baud rate is selected by remote switch or on-board jumpers W4, W6, and W9 for DLART0 and W10, W7, and W12 for DLART1 (baud rate select BRS2, BRS1, and BRS0, respectively).                                                                                   |

|      |        | (In other applications, if this bit is set, $<05:03>$ can select the baud rate under program control. When $<01>$ is cleared, the baud rate is selected by remote switch or on-board jumpers. Cleared on power-up or reboot.)                                                                                                    |

| <00> | R/W    | Transmit Break—When set, causes the output signal to go to a SPACE condition. A SPACE longer than a character-time causes a framing error, and is interpreted as a break. Transmit Ready and Transmit Interrupt continue to operate, allowing software to time the break. Cleared by power-up, reboot, or the RESET instruction. |

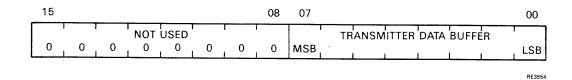

#### 1.2.7.4 Transmitter Data Buffer

Address: 17777566 (SLU 0), 17776506 (SLU 1)

Figure 1-11: Transmitter Data Buffer (XBUF)

Table 1-12: Transmitter Data Buffer (XBUF) Bits

| Bit     | Access | Description                                                                                                                                                                                                                                                                                                                               |

|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <15:08> | R      | not used—always read 0                                                                                                                                                                                                                                                                                                                    |

| <07:00> | R/W    | Transmitter Data Buffer—When a byte is written into this buffer, the Transmitter Ready bit (XCSR<07>) is cleared. This byte is copied into the transmitter serial output register when it is empty and XCSR<07> is cleared. Copying the byte into the serial output register sets XCSR<07>. These bits are cleared on power-up or reboot. |

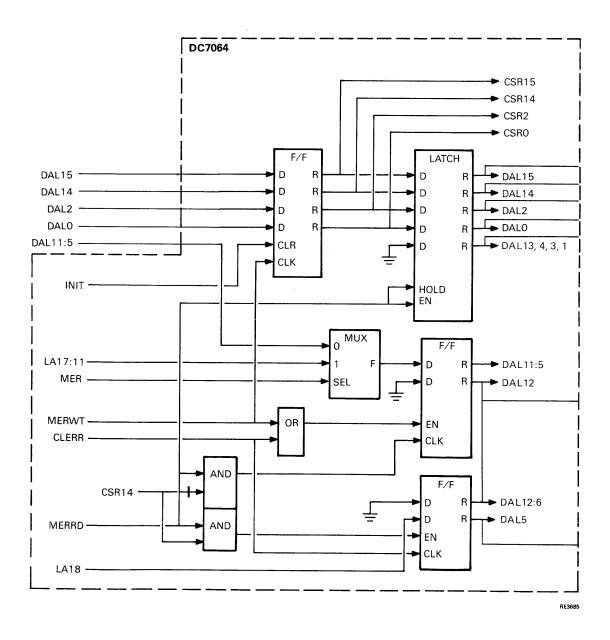

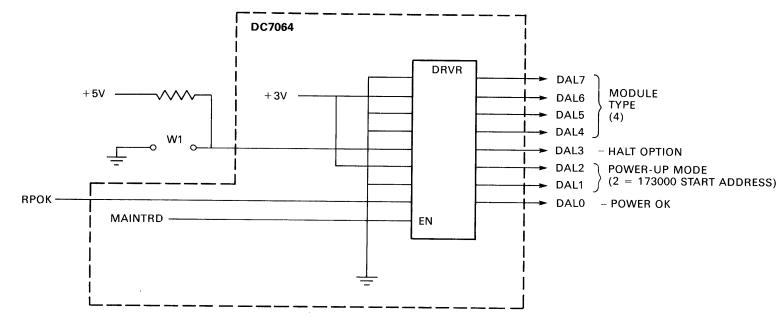

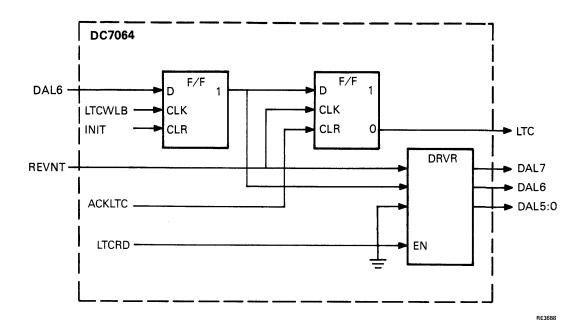

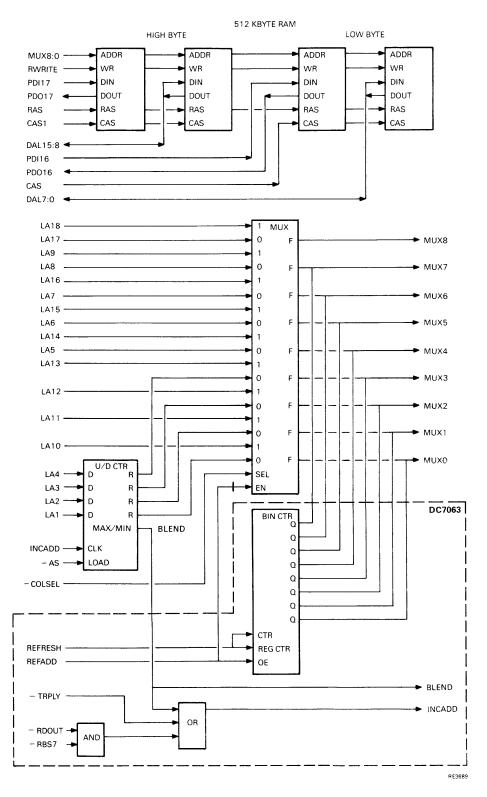

# 1.3 GENERAL PURPOSE REGISTERS