EK-70MP-TM-PRE

#### PRELIMINARY

PDP-11/70 MULTIPROCESSOR TECHNICAL MANUAL (PRELIMINARY)

PRELIMINARY

Copyright © 1975, 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

DEC DECtape PDP

DECCOMM DECUS RSTS

DECsystem-10 DIGITAL TYPESET-8

DECSYSTEM-20 MASSBUS TYPESET-11

UNIBUS

## CONTENTS

|       |                                                              | Page           |

|-------|--------------------------------------------------------------|----------------|

| CHAPT | ER 1 INTRODUCTION                                            |                |

| 1.1   | PDP-11/70 MULTIPROCESSOR SYSTEM                              | 1-1            |

| 1.2   | APPLICATIONS                                                 | 1-4            |

| 1.3   | MULTIPROCESSOR PACKAGING                                     | 1-5            |

| 1.4   | BRIEF FUNCTIONAL DESCRIPTION OF BASIC COMPONENTS             | 1-11           |

|       | 1.4.1 Modified KB11-C Processor                              | 1-11           |

|       | 1.4.2 MKAll-Memory                                           | 1-12           |

|       | 1.4.3 Interporcessor Interrupt and Sanity Timer (IIST) Sub   | system<br>1-13 |

|       | 1.4.4 IIST Interface Module (M8717)                          | 1-13           |

|       | 1.4.5 Massbus Controllers and Devices                        | 1-14           |

|       | 1.4.6 Single Accessed Devices on Shared Bus                  | 1-14           |

|       | 1.4.7 DB11-A Bus Repeater                                    | 1-15           |

| 1.5   | FIELD TEST SYSTEM CONFIGURATION                              |                |

| 1.6   | RECOMMENDED MINIMUM, PDP-11/70 MULTIPROCESSOR CONFIGURATION  |                |

| 1.7   | MKA11 MEMORY OPTIONS                                         | 4 1 1 1        |

| CHAPT | ER 2SYSTEM TECHNICAL DESCRIPTION                             |                |

| 2.1   | SCOPE AND PRUPOSE                                            | 2-1            |

| 2.2   | MULTIPROCESSOR CONCEPTS                                      | 2-1            |

| 2.3   | TYPICAL PDP-11/74 MULTIPROCESSOR SYSTEM (2-PROCESSOR CONFIGU |                |

| 2.4   | SIMPLIFIED OVERVIEW OF MULTIPROCESSOR OPERATION (NON-CACHED) | 2-2            |

| 2.5   | SIMPLIFIED OVERVIEW OF MULTIPROCESSOR OPERATION (WITH CACHE) | 2-5            |

| 2.6   | INTERPROCESSOR INTERRUPT AND SANITY TIMER (IIST) SYSTEM      | 2-7            |

|       | 2.6.1 Major Purpose                                          | 2-9            |

|       | 2.6.2 BOOT/IIST Panel Switch and Logic Boards                | 2-9            |

|       | 2.6.3 IIST Interface Subsystem                               | 2-10           |

|       | 2.6.4 Summary of Major Functions                             | 2-10           |

| 2.6.5  | Program-Ge              | nerated Inter              | rupts and/or Bo             | oots                            | 2-12          |

|--------|-------------------------|----------------------------|-----------------------------|---------------------------------|---------------|

| 2.6.6  | Sanity-Tim<br>Processor |                            | Interrupts and,             | or Boots and                    | 2-15          |

| 2.6.7  | Processor               | Identification             | n Switches                  |                                 | 2-16          |

| 2.6.8  | Masking of              | Processors A               | gainst Interrup             | pts and/or Boot                 | s2-16         |

| 2.6.9  | DCLO/Disco              | nnect Detection            | on                          |                                 | 2-17          |

| 2.6.10 | Error Dete              | ction                      |                             |                                 | 2-17          |

| 2.6.11 | ON/OFF Lin              | e Maintenance              | Capability                  |                                 | 2-17          |

| 2.6.12 | IIST Inter              | faces                      |                             |                                 | 2-18          |

|        | 2.6.12.1                | IIST to Unib               | ıs                          |                                 | 2-18          |

|        | 2.6.12.2                | Program-Generato Processor |                             | t Transmission                  | (IIST<br>2-19 |

|        | 2.6.12.3                | IIST to IIST               | Interface                   |                                 | 2-21          |

|        |                         | 2.6.12.3.1                 | Program-Genera<br>Operation | ated Interrupt/                 | Boot<br>2-24  |

|        |                         | 2,6.12,3.2                 | Sanity Timer (              | Operation                       | 2-24          |

| 2.6.13 | BOOT/IIST               | Switch Panel a             | and Associated              | Logic                           | 2-29          |

|        | 2.6.13.1                | CPU Status I               | ndications                  |                                 | 2-30          |

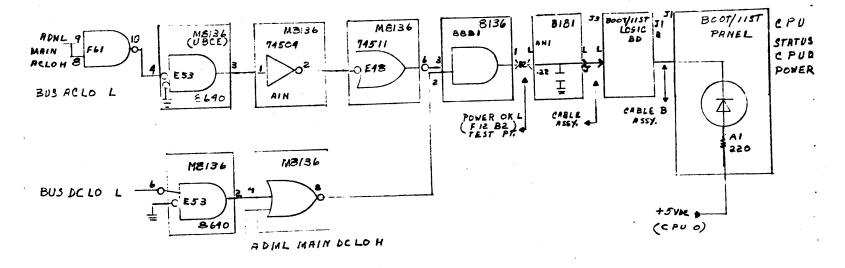

|        |                         | 2.6.13.1.1                 | Power Indicate              | ors                             | 2-30          |

|        |                         | 2.6.13.1.2                 | Run Indicators              | 5                               | 2-30          |

|        |                         | 2.6.13.1.3                 | Sanity Timer I              | Halt Indicators                 | and<br>2-32   |

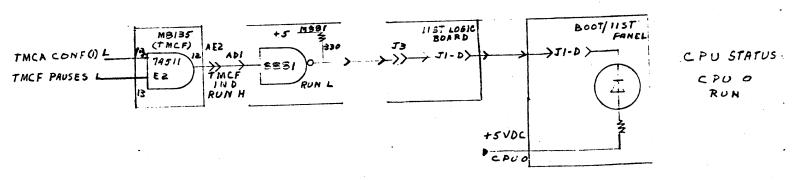

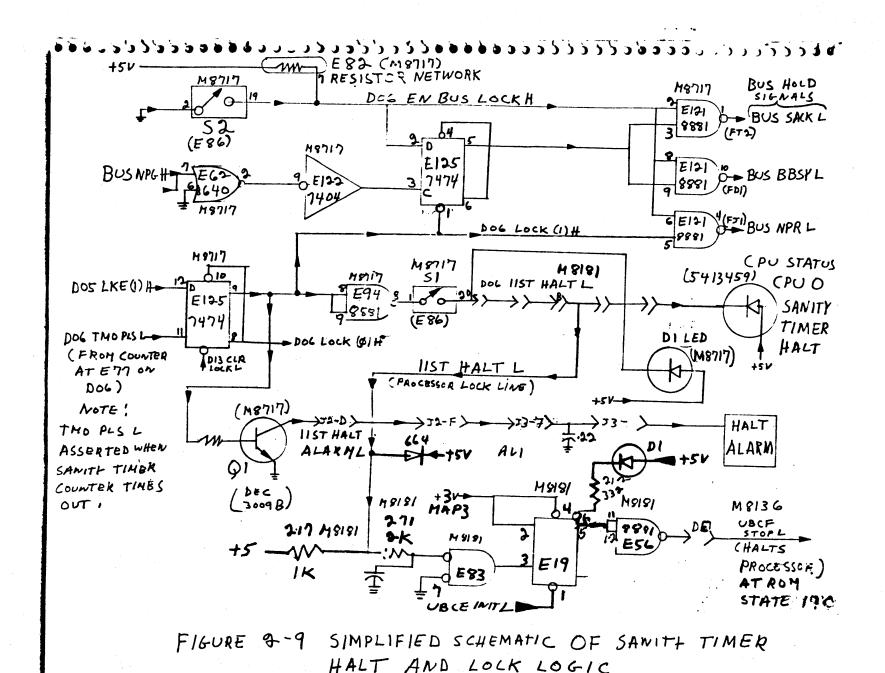

|        |                         |                            | 2.6.13.1.3.1                | Detailed Halt<br>Lock Signal Fl |               |

|        |                         |                            | 2.6.13.1.3.2                | NPR Bus Hold                    | 2-36          |

|        |                         |                            | 2.6.13.1.3.3                | Direct Sanity<br>Halt Lock to P | rocessor      |

|        |                         |                            | 2.6.13.1.3.4                | Halt Alarm                      | 2-38<br>2-39  |

|        | 2.6.13.2                | System Boot                | from Boot/IIST              | Switch Panel                    | 2-39          |

|        | 2,6,13,3                | CPU Power-Up               | Action                      |                                 | 2-42          |

|        |                         | 2.6.13.3.1                 | Automatic Boot              | t on Power-Up                   | 2-43          |

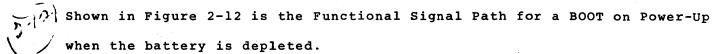

|        |                         | 2.6.13.3.2                 | Run or Boot On<br>Depleted  | nly if Battery                  | 2-45          |

|                                        |                                          |            | 2.6.13.3.3 Run or Halt (if Battery Deplet   | ed)          |

|----------------------------------------|------------------------------------------|------------|---------------------------------------------|--------------|

|                                        | •                                        | 2,6,13,4   |                                             | 2-47<br>2-47 |

|                                        |                                          | 2.6.13.5   | IIST Enable ON LINE/OFF LINE Switches       | 2-49         |

|                                        |                                          | 2.6.13.6   | IIST Configuration Switches                 | 2-51         |

|                                        | 2.6.14                                   | IIST Inter | face Module Registers                       | 2-55         |

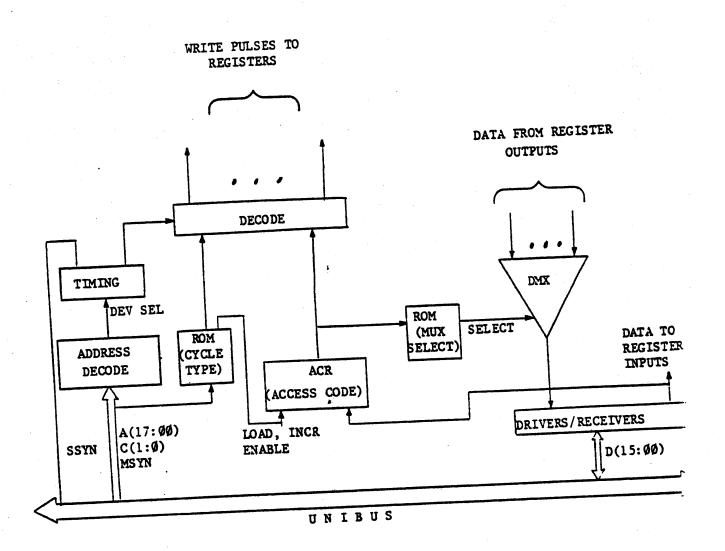

|                                        |                                          | 2,6,14.1   | Access-Path Register Descriptions           | 2-57         |

| -                                      |                                          | 2.6.14.2   | ACR (Access Control Register)               | 2-58         |

|                                        |                                          | 2.6.14.3   | ADR (Access Data Register)                  | 2-59         |

|                                        |                                          | 2.6.14.4   | Device Register Descriptions                | 2-60         |

|                                        |                                          | 2.6.14.5   | Register Access Path                        | 2-60         |

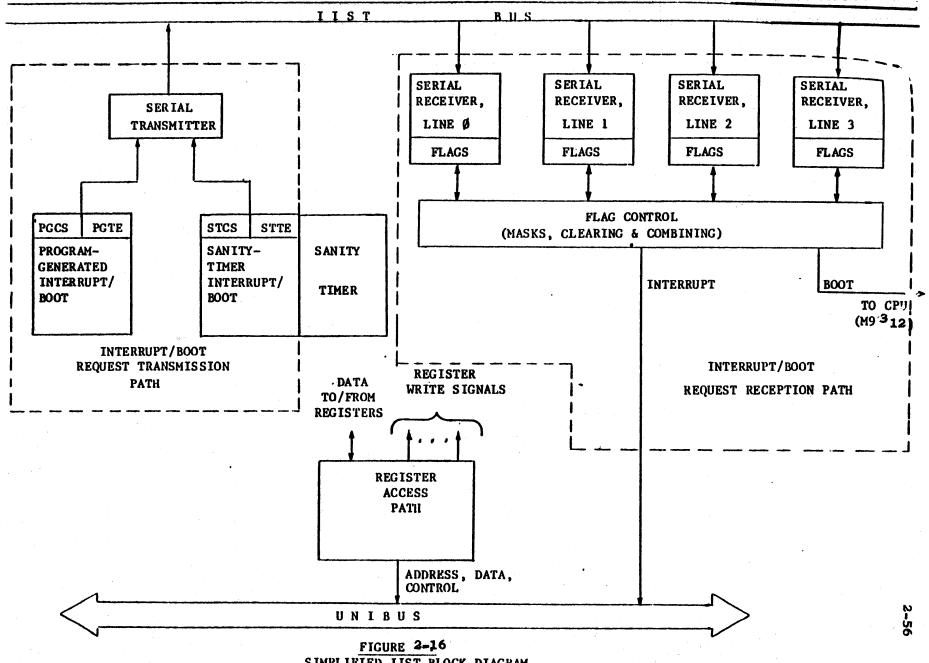

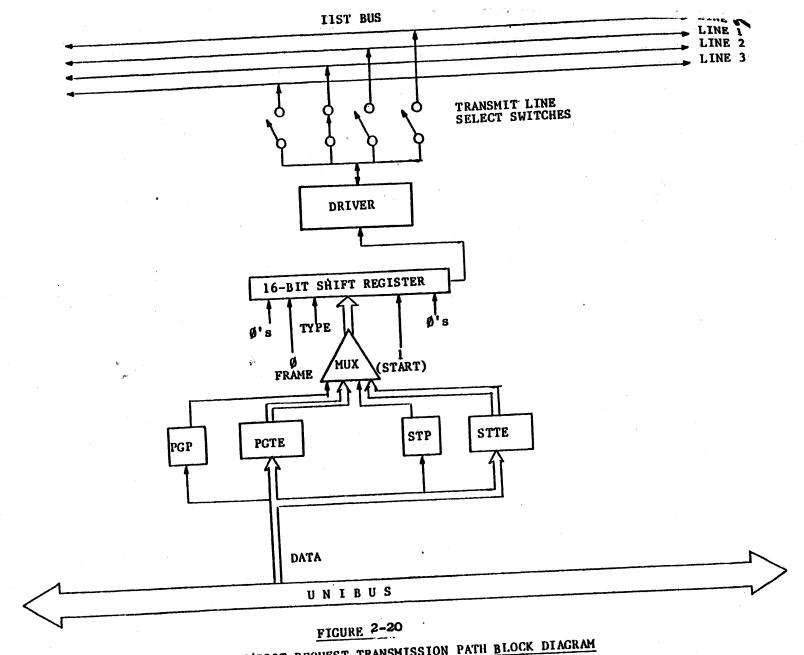

|                                        |                                          | 2.6.14.6   | Interrupt/Boot Transmission Path            | 2-71         |

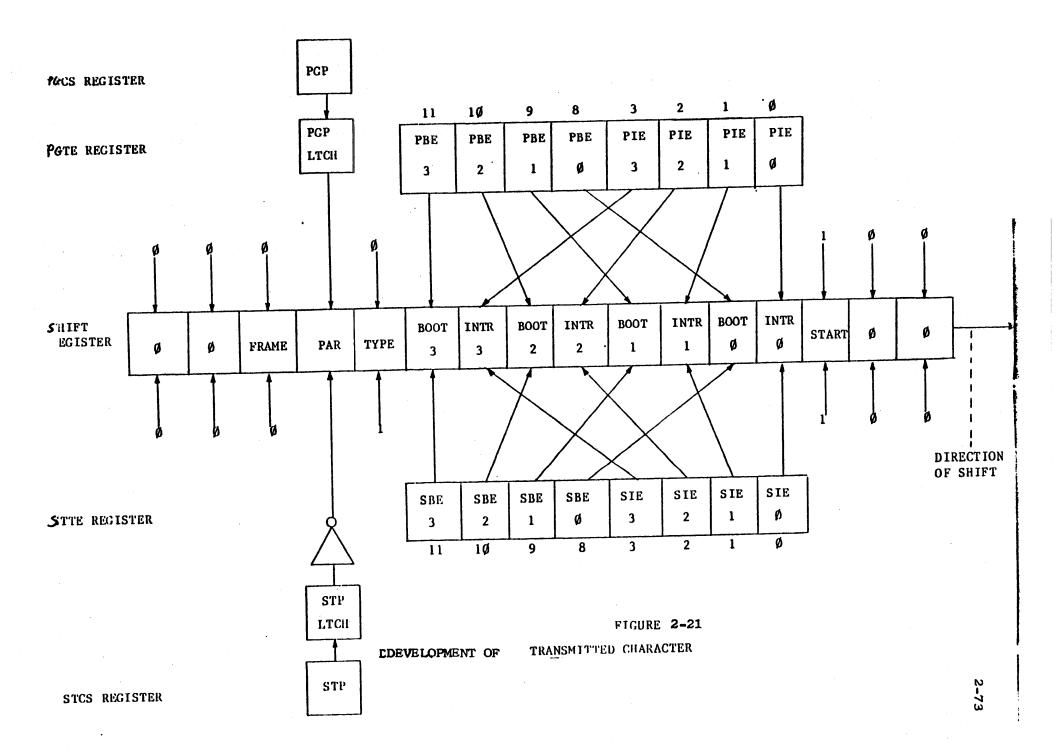

|                                        |                                          | 2.6.14.7   | Development of Transmitted Character        | 2-71         |

|                                        | . A. | 2.6.14.8   | Program-Generated Interrupt/Boot Transmissi | ion<br>2-71  |

| ************************************** |                                          | 2.6.14.9   | Interrupt/Boot Request Path                 | 2-76         |

|                                        |                                          | 2.6.10.10  | Serial Line Receivers                       | 2-76         |

|                                        |                                          |            | 2.6.10.1 Basic Receiver Functions           | 2-76         |

|                                        |                                          |            | 2.6.14.10.2 Summary of Receiver Operation   | 2-79         |

| 2.7                                    | кв11-С                                   | PROCESSOR  |                                             | 2-81         |

|                                        | 2.7.1                                    | Relationsh | nip of Processors to Shared Memory          | 2-82         |

|                                        | 2.7.2                                    | Cache Oper | ation (Cache Bypass not Generated)          | 2-84         |

|                                        |                                          | 2.7.2.1    | Read Hit                                    | 2-85         |

|                                        |                                          | 2.7.2.2    | Read Miss                                   | 2-86         |

|                                        |                                          | 2.7.2.3    | Write Hit                                   | 2-86         |

|                                        |                                          | 2.7.2.4    | Write Miss                                  | 2-87         |

|                                        |                                          | 2.7.2.5    | Cache Flush                                 | 2-87         |

|                                        |                                          |            | 2.7.2.5.1 Purpose                           | 2-87         |

|                                        |                                          |            | 2.7.2.5.2 Typical Cache Flush Operation     | 2-88         |

|                                        |                                          | 2.7.2.6    | Cache Bypass                                | 2-9]         |

|        | •          | 2.7.2.6.1    | Cache Bypass All                                     | 2-92          |

|--------|------------|--------------|------------------------------------------------------|---------------|

|        | <b>.</b>   | 2.7.2.6.2    | Bypass Only on a Virtual Page                        | 2-92          |

|        | ,          | 2.7.2.6.3    | Bypass Only on a Unibus Map Pa                       | ge2-93        |

| 2.7.3  | Use of AS  | RB to Test a | nd Set Memory Lock (if Unlocked                      | 1) 2-96       |

|        | 2.7.3.1    | Purpose      |                                                      | 2-96          |

|        | 2.7.3.2    | Detailed Di  | scussion                                             | 2-96          |

| •      |            | 2.7.3.2.1    | Simplified View of ASRB Test a<br>Set of Memory Lock | nd<br>2-97    |

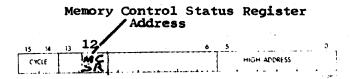

| 2.7.4  | Accessing  | Main Memory  | Control Status Registers (CSR                        | s)2-102       |

| 2.7.5  | Main Memo: | ry Timeouts  |                                                      | 2-104         |

| 2.7.6  | Cancelled  |              |                                                      |               |

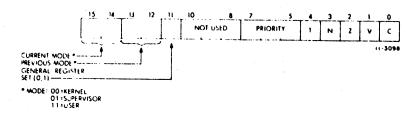

| 2.7.7  | Processor  | Registers    |                                                      | 2-106         |

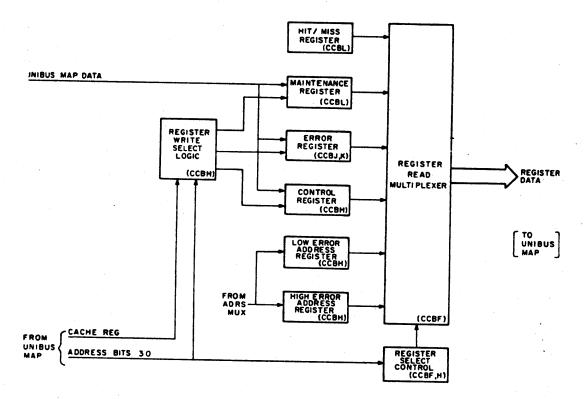

| 2.7.8  | Cache Reg  | isters       |                                                      | 2-113         |

|        | 2.7.8.1    | Low Error A  | idress Register                                      | 2-115         |

|        | 2.7.8.2    | High Error   | Address Register                                     | 2-116         |

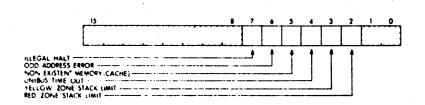

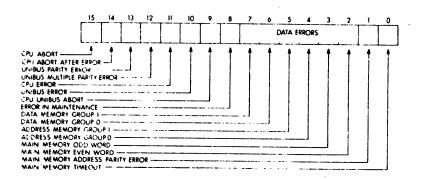

|        | 2.7.8.3    | Memory Syste | em Error Register                                    | 2-119         |

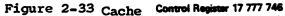

|        | 2.7.8.4    | Control Reg  | ister                                                | 2-121         |

|        |            | 2.7.8.4.1    | Summary of Cache Control Regis<br>Bit Functions      | ter<br>2-123  |

|        |            | 2.7.8.4.2    | Disable Trapping with Bits 1 a                       | nd 0<br>2-123 |

|        | · .        | 2.7.8.4.3    | Use of Control Register in Tro                       |               |

|        | 2.7.8.5    | Maintenance  | Register                                             | 2-128         |

|        | 2.7.8.6    | Hit/Miss Re  | gister                                               | 2-131         |

| •      | 2.7.8.7    | Use of Cache | e Registers                                          | 2-132         |

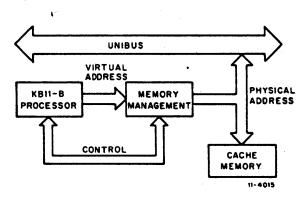

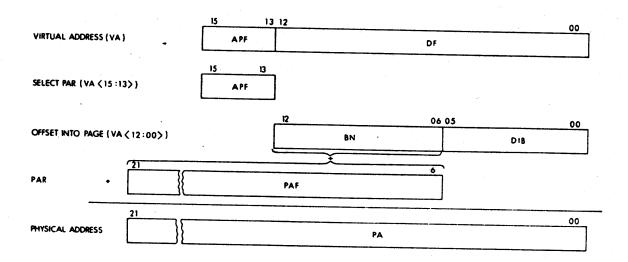

| 2.7.9  | Memory Ma  | nagement     |                                                      | 2-134         |

|        | 2.7.8.1    | Purpose      |                                                      | 2-135         |

|        | 2.7.8.2    | Memory Mana  | gement Registers                                     | 2-140         |

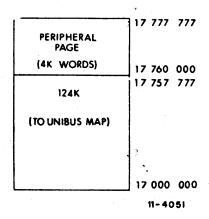

| 2.7.10 | Unibus Ma  | D            |                                                      | 2-152         |

|      |            | 2,7.10.1   | Purpose                          | Ź-152  |

|------|------------|------------|----------------------------------|--------|

| ••   | <u>.</u> : | 2.7.10.2   | Relocation Disabled              | 2-153  |

|      |            | 2.7.10.3   | Relocation Enabled               | 2-153  |

|      |            | 2.7.10.4   | Unibus Map Registers             | 2-154  |

|      |            | •          | 2.7.10.4.1 15 Bypass Cache (BYP) | 2-156  |

|      |            |            | 2.7.10.4.2 Register Access       | 2-156  |

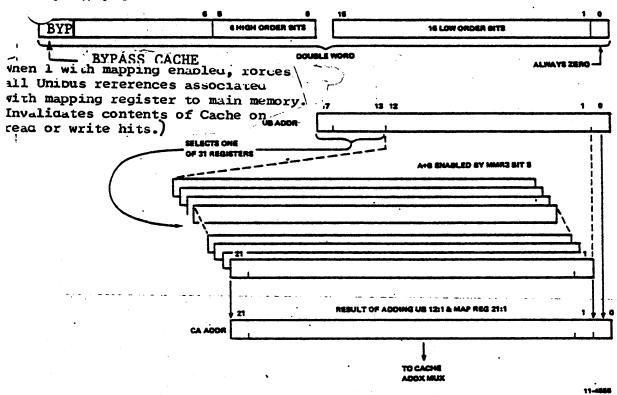

| 2.8  | MKAll M    | JLTIPORTED | MEMORY                           | 2-158  |

|      | 2.8.1      | Addressing | g and Data Transfers             | 2-160  |

|      | 2.8.2      | Major Com  | ponents                          | 2-162  |

|      |            | 2.8.2.1    | Memory Frame                     | 2-162  |

|      |            | 2.8.2.2    | Port Controllers                 | 2-162  |

|      |            | 2.8.2.3    | Power Supply and Power Control   | 2-162  |

|      |            | 2.8.2.4    | Battery Back-Up Unit             | 2-1621 |

|      |            | 2.8.2.5    | Main Memory Busses               | 2-1620 |

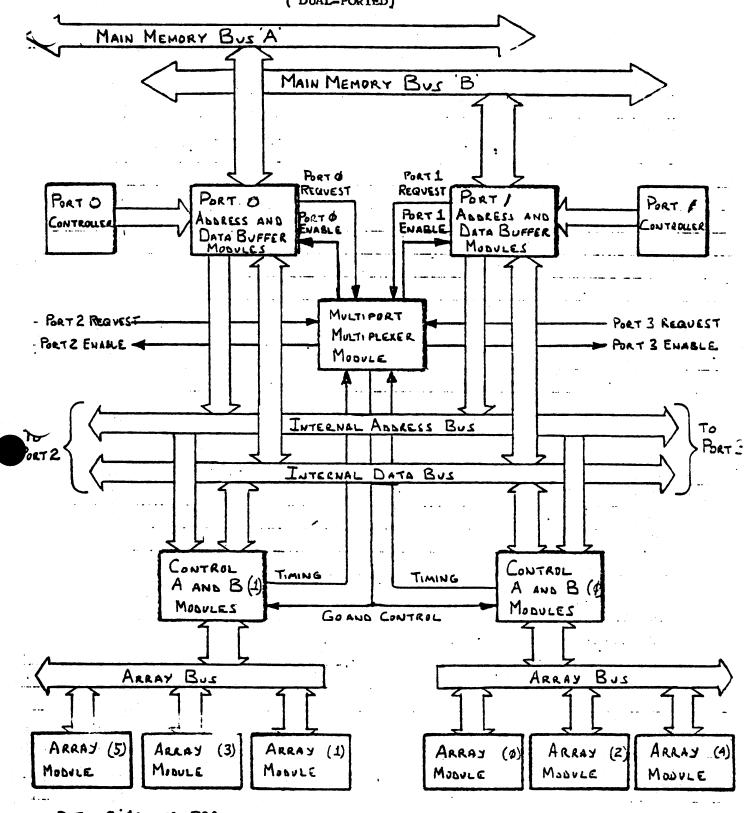

| 2.9  | MASSBUS    | OPERATION  |                                  | 2-163  |

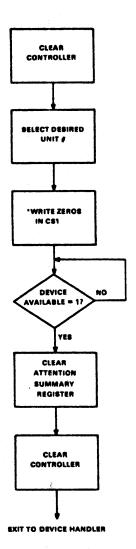

|      | 2.9.1      | RHOl Mass  | bus Dual-Port Adapter            | 2-164  |

|      |            | 2.9.1.1    | Purpose                          | 2-164  |

|      | 1          | 2.9.1.2    | Operation                        | 2-165  |

|      |            | 2.9.1.3    | System Considerations            | 2-166  |

|      |            | 2.9.1.4    | RH01 Electronic Switches         | 2-167  |

|      |            | 2.9.1.5    | Attention Summary Register       | 2-167  |

|      |            | •          |                                  |        |

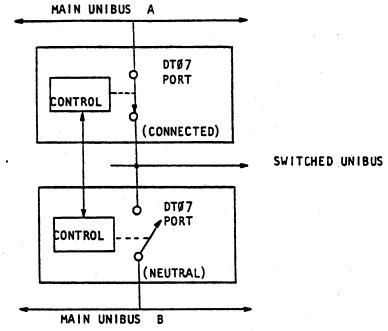

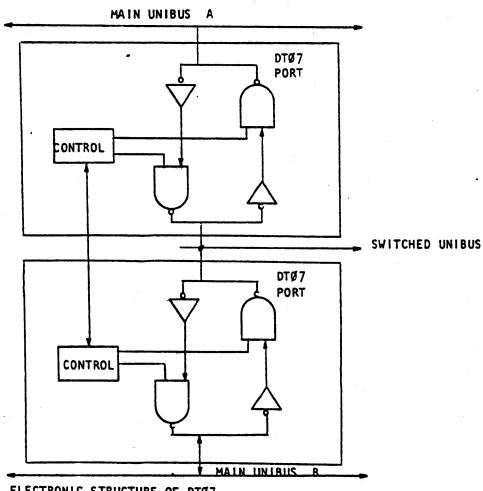

| 2.10 | DT07 SH    | ARED UNIBU | S SWITCH                         | 2-169  |

|      | 2.10.1     | Purpose    |                                  | 2-169  |

|      | 2.10.2     | Operation  |                                  | 2-171  |

|      |            | 2.10.2.1   | Basic Switch Functions           | 2-171  |

|      | •          | 2.10.2.2   | Control                          | 2-173  |

| CHAPI | TER 3OPERATING CONTROLS AND INDICATORS                     | 3-1          |

|-------|------------------------------------------------------------|--------------|

| 3,1   | SCOPE                                                      | 3-1          |

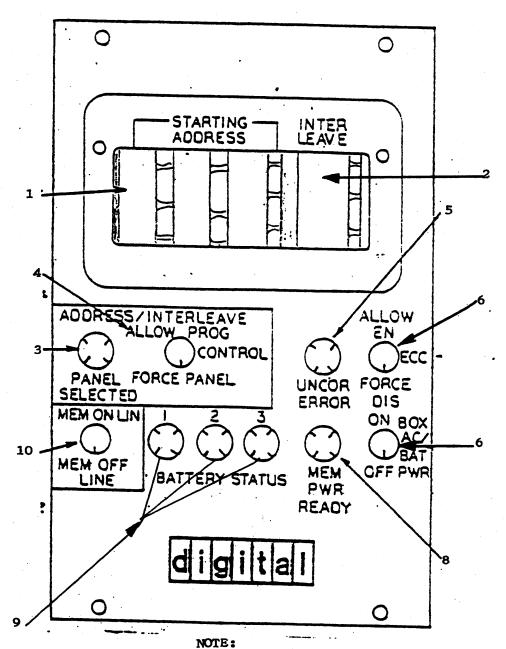

| 3.2   | BOOT/IIST SWITCH PANEL SWITCHES AND INDICATORS             | 3-1          |

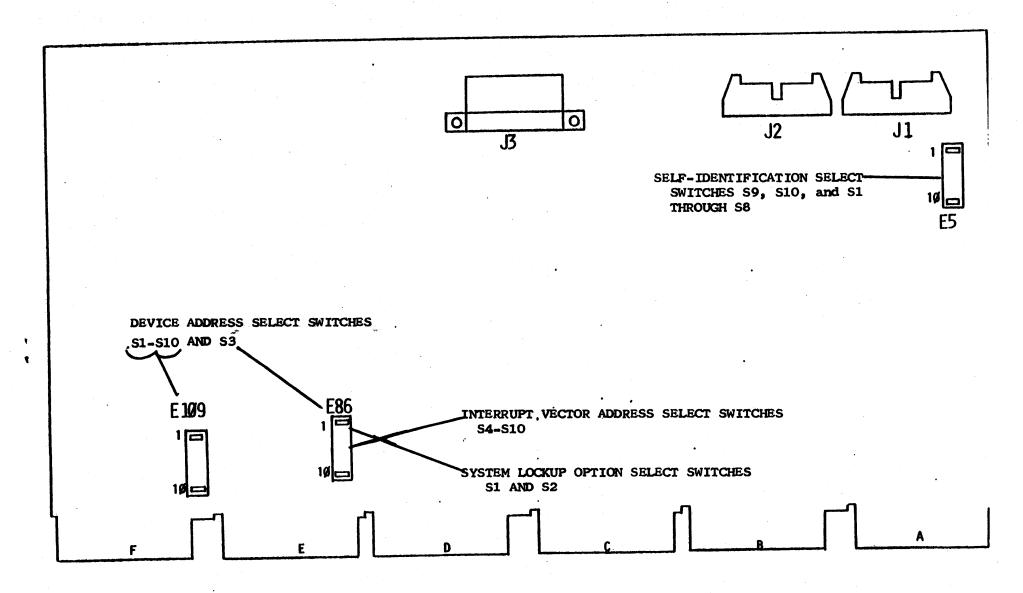

| 3.3   | IIST INTERFACE MODULE (M8717) SWITCHES                     | 3-9          |

|       | 3.3.1 Device Address Select Switches                       | 3-9          |

|       | 3.3.2 Interrupt Vector Address Select Switches             | 3-9          |

|       | 3.3.3 Self-Identification Select Switches                  | 3-15         |

|       | 3.3.4 System Lockup Option Select Switches                 | 3-15         |

|       |                                                            |              |

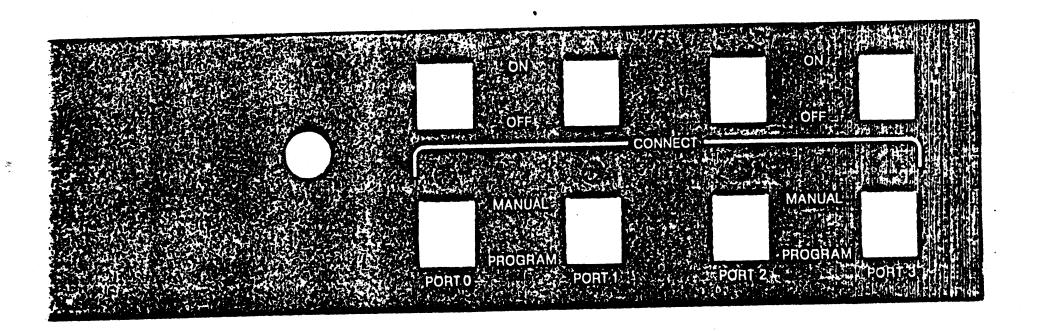

| 3.4   | FRONT PANEL SWITCHES AND INDICATORS OF MEMORY PORT CONTROL | LER 3-16     |

| 3.5   | RHOL DUAL-ACCESS ADAPTER                                   | 3-16         |

|       | 3.5.1 Switches and Indicators                              | 3-16         |

|       | 3.5.2 Manual Mode of Operation                             | 3-25         |

|       | 3.5.3 Dual Access Mode of Operation                        | 3-25         |

|       | 3.5.3,1 Unseized State                                     | 3-25         |

|       | 3.5.3.2 Seized State                                       | 3-25         |

|       | 3.5.4 Hardware Registers                                   | 3-27         |

|       | 3.5.4.1 Attention Summary Register                         | 3-27         |

|       | 3.5.4.2 Control/Status 1 Register (CSI)                    | 3-28         |

|       | 3.5.4.2.1 Reading the Control/Status R                     |              |

|       | 3.5.4.2.2 Programming                                      | 3-29<br>3-29 |

|       | 3.5.4.2.3 Programming Example                              | 3-30         |

| 3.6   | DT07 BUS SWITCH                                            | 3-33         |

| 3.7   | PDP-11/70 SWITCH CONSOLE                                   | 3-45         |

| 3.8   | REMOTE SERIAL DIAGNOSTIC CONSOLE (Optional)                | 3-45         |

|       | 3.8.1 Serial Console Control Panel Switches and Indicato   | rs 3-45      |

|       | 2 ° 2 Consolo Commande                                     | 3-45         |

CHAPTER 1

INTRODUCTION

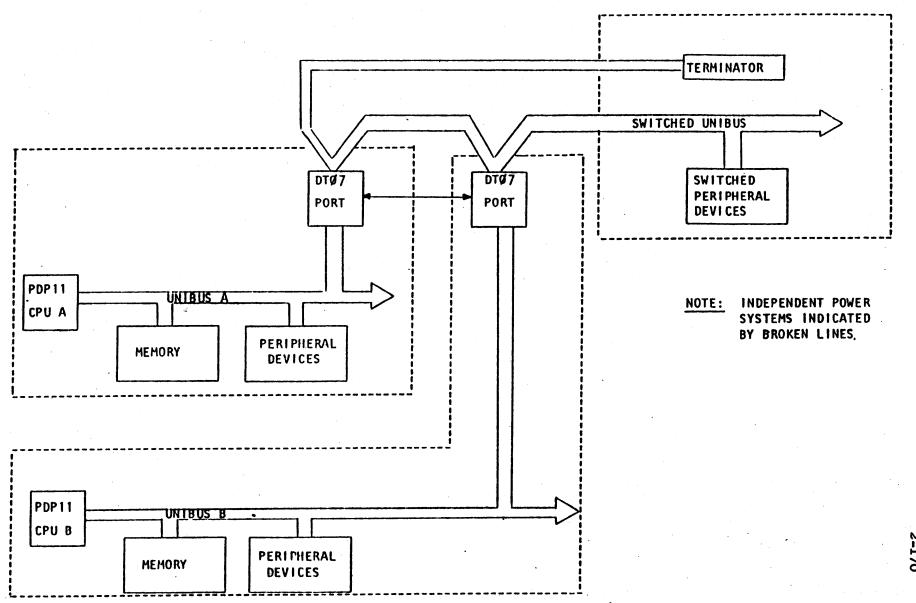

#### 1.1 PDP-11/70 MULTIPROCESSOR SYSTEM

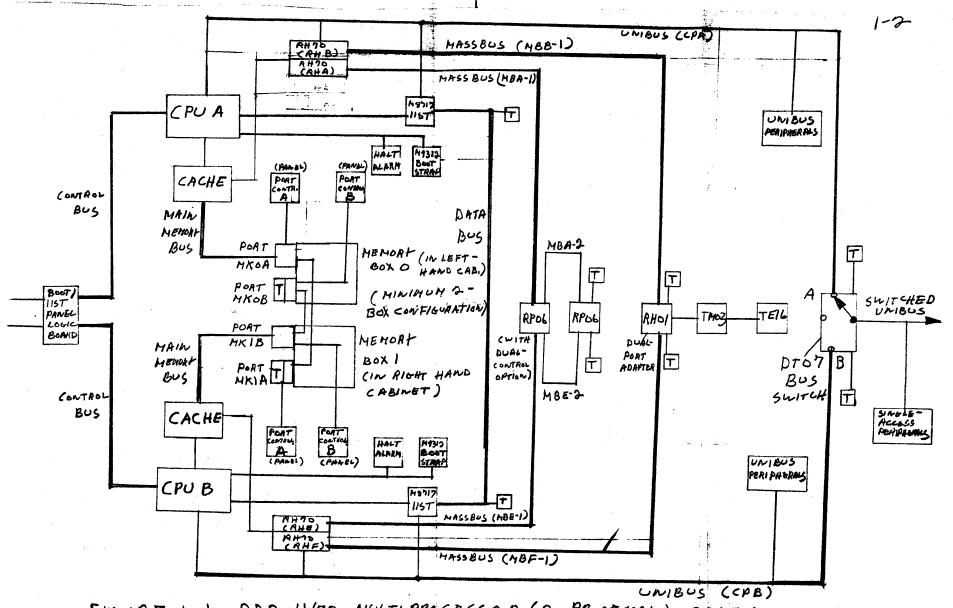

The PDP-11/70 Multiprocessor System shown in Figure 1-1 consists of two modified KB11-C PDP-11/70 main processors (the PDP-11/74 Multiprocessor can have up to four KB11-E main processors), each one of which has independent access to a multi-ported common (tight-ly-coupled) MOS memory. Both processors are controlled by a single operating system, the RSX-11M+ that provides interaction between the processors, the programs they are executing and the I/O devices. The processors are all functionally equal with the ability to perform any task and function either as slave or master during program operations. Each processor has its own independent Unibus with peripheral devices connected to it.

Connected to each processor via its Unibus is an Interprocessor Interrupt Sanity Timer (IIST) Interface Module. The IIST modules are also connected to each other by the IIST independent Interrupt/Boot request Bus which passes Interrupt and Boot requests between them. The IIST sub-system is used by the RSX-llMP Executive to interrupt processors for the purpose of re-scheduling system activity. The IIST sub-system allows the operating program in one processor to send interrupts and boot requests via the IIST Bus and modules to any and all processors in the system. Execution of a task running on a processor can be pre-empted by the system software by means of the IIST sub-system whenever access to a device via that CPU is required.

Only the interrupt or boot request is sent over the IIST Bus. The

FIGURE 1-1 PDP-11/70 MULTIPROCESSOR (2-PROCESSOR) SASTEM

actual interrupt handling service sequence involving the Interrupt signal and the interrupt vector address is accomplished via the Unibus as a normal interrupt service handling routine between the concerned processor and the IIST Interface Module receiving the Interrupt request.

Thus a task running on one CPU can request I/O service on any device regardless of where that device is located.\* The IIST also provides a Sanity Timer that must be periodically refreshed by the program. If a timeout should occur before the timer has been refreshed, an interrupt and/or boot request can be transmitted to any or all of the processors (depending upon how the Sanity-Timer Transmission Enables Register is set) and the faulty processor is halted and its Unibus will be frozen or locked by the IIST asserting BBSY (Bus Busy), thereby, limiting the effect of a possibly faulty processor.

Both single ported and dual ported devices can be used. When required, single-ported devices can be replicated on different busses. Dual access massbus devices can be accessed by Massbus controllers on different massbuses. Dual port adapters and options are used to dual-port these devices.

In addition, single ported devices can be used on a shared bus and (optionally) switched for use with one processor or another on different Unibuses by means of the DT07 Bus Switch.

<sup>\*</sup>Of course, requests for I/O and the servicing of interrupts must be performed by the processor to which the device controller is connected.

#### 1.2 APPLICATIONS

The PDP-11/70 Multiprocessor supplies to the customer an increase in the capability of his system to perform its critical application (enhanced availability) by means of redundant functional units, and a system fault recovery capability that allows the operator to reconfigure around a failed element or system in order to recover the critical application part of his system.

It provides to customers significantly improved performance and functions in the areas of Commercial Data Processing. When coupled with properly designed applications, multiprocessors can provide a significant reduction in cost penalties resulting from critical downtime combined with substantial throughput improvements. It will improve customer's system performance providing the ability to execute tasks simultaneously and by efficient use of added resources (various configurations of multiprocessors and standalone processors can be used without interference of one with the other) during peak load handling.

Basically the multiprocessor system will provide the following capabilities:

- 1. Symmetrical multiprocessing

- 2. Use of Multiported memory

- 3. Use of dual-ported access massbus devices

- 4. Use of DT07 Bus Switch for use with shared Bus (optional)

- 5. Program-assisted reconfiguration of most units under operator control to allow powered-up fault isolation and maintenance

- 6. Improved Error Logging capability

- 7. Use of System Crash Analyzer

- 8. Ability to reconfigure system into independent systems

- 9. Ability to load stand-alone diagnostics into an off-line system from a Files-11 volume.

- 10. Ability to allow on-line processor diagnostics to be run by binding a task to a particular CPU (task-CPU affinity).

- 11. Ability to allow the operating system to be bootstrapped from any Files-11 device.

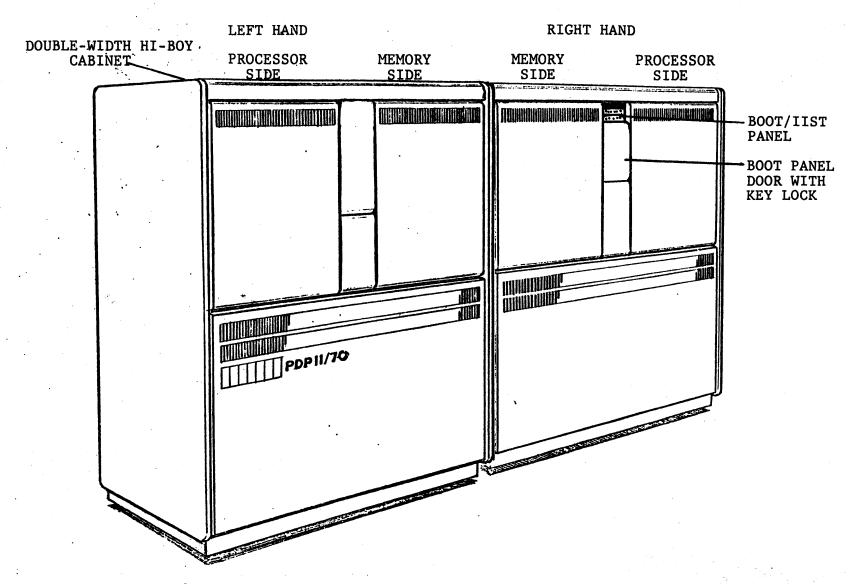

# 1.3 MULTI-PROCESSOR PACKAGING

The PDP-11/70 Multiprocessor System is packaged in Double-Width High-Boy Cabinets and in Single-Width High-Boy Expander Cabinets. Each individual processor and memory are contained in a Double-Width High-Boy (DWHB) cabinet which has two bays: the processor bay and the memory bay. Two of these DWHB cabinets (shown in Figure 1-2) are bolted together during installation. One is the left-hand processor, the other the right-hand processor. The left-hand processor has a left- x mounted modified KB11-C and the right, a right-mounted modified KB11-C.

Figure 1-2 PDP-11/70 Multiprocessor (2-Processor) System

each processor. The right processor is a mirror image of the left one in that the location of components is reversed; left bay components to the right bay and right bay components to the left bay which puts the memory system bays of the different processors adjacent to each other when the DWHB cabinets are bolted together.

In addition, the PDP-11/70 multiprocessor system requires at least two single width-high boys Expander Cabinets, A and B, in which BAll-P boxes are mounted. Contained in each of the Expander Cabinets are the DIP11-A IIST interface module (M8717), the DD11-F system mounting unit (9-slots), and the various communication devices and switches (DZ11's, BSM-11, CSS-11, etc.). Expander Cabinet A is dedicated to CPU A, and Expander Cabinet B to CPU B.

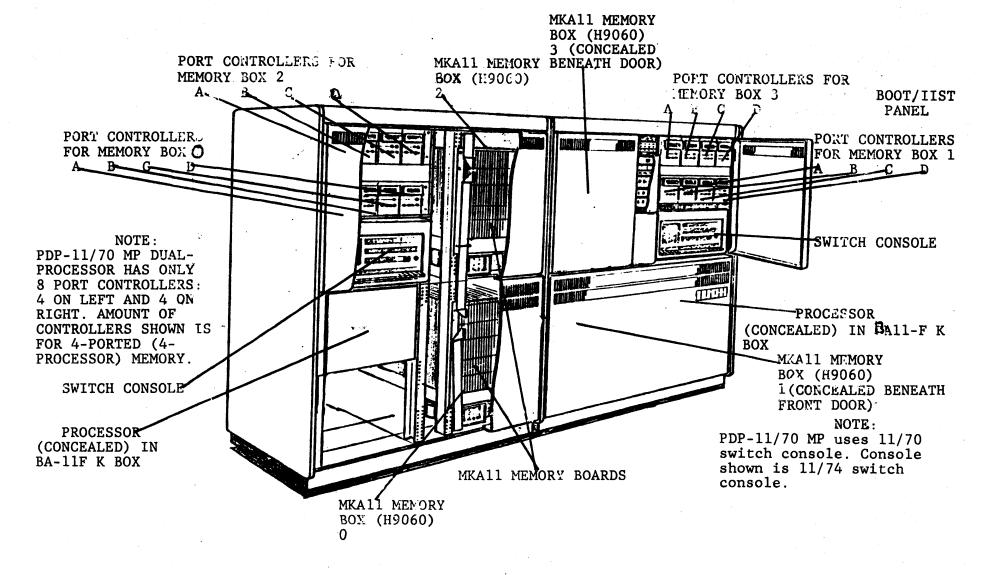

Location of the major components contained in the DWHB cabinets is shown in Figure 1-3. Memory Port Controllers are located in the upper left portion on the processor side of the DWHB cabinet of the left-hand processor and in the upper right of the right-hand processor. There is one port controller for each port of the MKAll memory. For the PDP-11/70 multiprocessor, up to four port controllers can be mounted on the processor side of each DWHB (assuming that two boxes of memory are contained on the memory side). Unused mounting locations on the panel are covered with blank panels. In the lower portion on the processor side of the DWHB cabinet are contained the CPU switch console or remote diagnostic console (optional), and in the DAll-F CPU mounting box which can be pulled out for easy board access are the modified KBll-C processor, the DLll-W Console Interface, the M9312 Bootstrap/Terminator Module, and the M9014 or M9302 Unibus terminators.

Figure 1-3 Major Components of Multiprocessor System (Front View--Sheet 1 of 2)

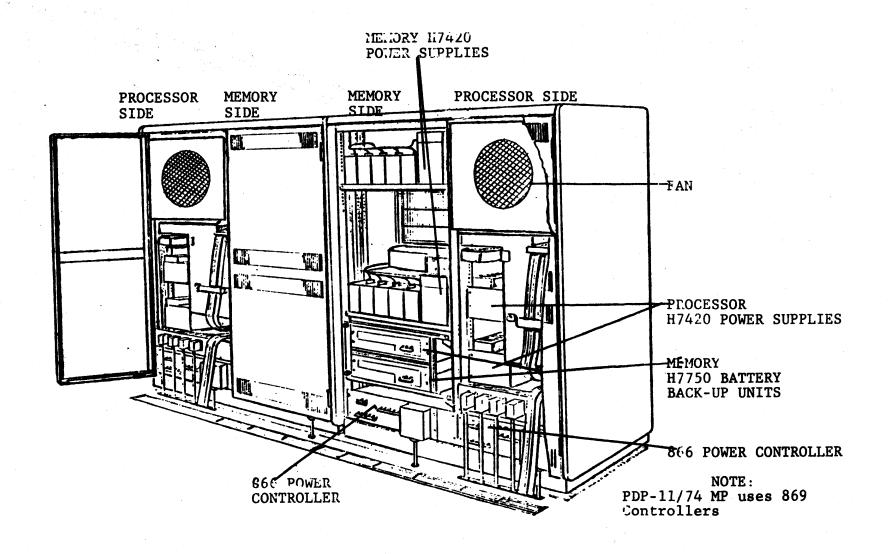

Figure 1-8 Major Components of Multiprocessor System (Rear View--Sheet 2 of 2)

NOTE: The M9302 will be installed in slot 44 during systems Manufacturing, and the DIP11-A will be in slot No. 42 during FA&T. At the customer site the M9014 will be installed in slot No. 44 and the DIP11-A (M8717) Interface Modules will be located in Expander Cabinets A and B.

Also located on the processor side of each DWHB are two processor H7420 power supplies and at the very bottom of the cabinet an 866D or E power controller.

The right bay or memory side of each DWHB can contain up to two H9060 memory boxes. One H9060 card cage contains the memory systems buffer, multiplexor, control, and storage array modules. These boards slide into the card cage on guides and plug into the memory backplane. Also contained on the memory side of each DWHB cabinet are the H7420 power supplies, the H7750, battery back-up units, and the 870 remote power control. Each memory box must have at least one H7420 power supply, one battery back-up unit H7750, and one 870 A or B power control. The 870 power control is connected to an 866 D or E Power Controller located on the memory side at the very bottom of each DWHB cabinet.

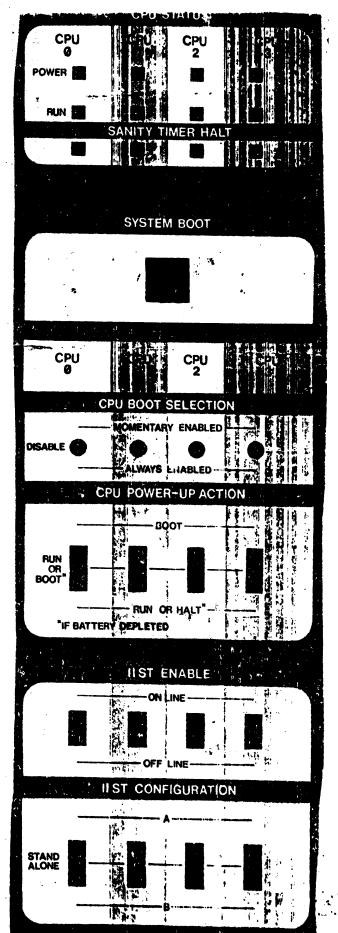

The BOOT/IIST Panel Switch Board (mounted behind a panel) and the BOOT/IIST Panel are located on the right-hand processor. (There is only one BOOT/IIST Panel and Panel Logic Board for each multiprocessor system.)

#### 1.4 BRIEF FUNCTIONAL DESCRIPTION OF BASIC COMPONENTS

#### 1.4.1 Modified KBll-C Processor

The basic KBll-C processor has been modified for use as the basic processor in a Multiprocessor System. Each modified processor's cache is connected via an independent main memory bus cable to an individual port on the MKAll multiported shared memory. The operation of the modified KBll-C is identical to the KBll-C except for those functions required specifically for Multiprocessor operation:

- Cache Flush (invalidates all the data in the cache when cache data no longer reflects the data in main memory.

- 2. Cache Bypass (Occurs when the cache is bypassed and all references are forced directly to main memory. Bypasses can occur under three different conditions and for different durations. The Bypass can occur continuously for short durations, or only at those locations associated with a particular Virtual page, or for locations mapped specifically by the Unibus Mapping Registers.

- 3. Ability to access Control Status Registers (CSR's) on main memory bus.

- 4. Memory timeouts are of longer duration in a modified KBll-C processor than in an unmodified one.

- 5. Use of ASRB instruction to implement a lock on shared

# data locations in memory

### 1.4.2 MKAll-MEMORY

The MKAll memory is a multiport MOS common main memory that can be shared by two, three or four CPU's.

NOTE: The PDP-11/70 and processor uses only 2 ports of the MKAll memory. The PDP-11/74 multiprocessor can use up to four ports of the MKAll memory.

Each processor's cache interfaces to one of the memory's four ports. via independent main memory bus cables.

Each MKAll memory has a storage capacity of 64K to 512 K 16-bit words. Larger main memory capacities are obtained by adding additional MKAll memories to the system and daisy chaining the memory's ports on the main memory busses. Up to four memories can be daisy-chained in this fashion, expanding the shared main memory space to the maximum addressable 2M words.

Access to main memory is achieved through the memory ports with a multiplexor board that arbitrates within each memory box among contending CUP's and devices for access to memory.

All ports have equal priority. When one or more processors makes a request to a port, and the memory is ready to accept requests, an arbitration cycle is initiated. At the conclusion of the arbitration cycle, the requesting ports are serviced round-robin in sequence, starting with the port immediately after the last port to have accom-

plished a memory cycle.

The multiplexor permits instruction execution to be symmetrical and processor-independent. Concurrent access by different processors to the Executive shared data structure in memory is inhibited by a software locking mechanism.

Each memory box has its own independent power supply with power supply regulators. Every box also has a battery back-up unit that can provide up to five minutes of standby power for retaining memory integrity during loss of power or power down sequences.

1.4.3 INTERPROCESSOR INTERRUPT AND SANITY TIMER (IIST) SUBSYSTEM

The BOOT/IIST Panel Switch Board contains indicators that display

the operating status of each processor, and switches that allow the

operator to select and boot the various processors and the type of

boot action that will or will not occur during power-up sequences.

Switches on this panel also permit the operator to configure the

processors to run as dual, tri, or quad multiprocessors in System

A or B groupings or as standalone processors or any various combination of multiprocessor and standalone that the program requires.

They also permit the operator, to select any processor for ON or OFF

LINE operation.

The BOOT/IIST Panel Switch Logic Board contains all the switch logic (controlled by the IIST CONFIGURATION Switches) for enabling or disabling the various drivers and receivers of the IIST Interface Modules of each processor so they can receive and transmit to other or to themselves when they are grouped properly in System A, System B, or

Standalone by the IIST Configuration switches.

# 1.4.4 IIST INTERFACE MODULE (M8717)

Each processor has an IIST Interface Module that is connected to all the other IIST Interface Modules by means of a Data Bus. Each module has its own data and clock line over which it transmits to the other modules (processors) any request for a boot or interrupt that it has received from its processor via the Unibus. It allows the operating program in one processor to send interrupt and/or Boot requests to any or all of the other processors in the system for the purpose of rescheduling activity on the various processors. For example, the RSX11MP Executive treats the different processors on different Unibuses as resource devices that it can use as it sees fit to perform all the various tasks required. There is also a Sanity Timer in the IIST Interface Module which must be refreshed periodically otherwise it will time out indicating a possible faulty processor.

#### 1.4.5 MASSBUS CONTROLLERS AND DEVICES

Up to four RH70 Massbus controllers can be used with each CPU in the multiprocessor system. Only two controllers are shown with each CPU in Figure 1-1. Massbus devices used in a multiprocessor system are dual accessed by means of dual-access options or adapters. Dual access to the TE16 drive is accomplished by means of the RH01 dual port adapter which is used with the TM03 Formatter.

# 1.4.6 SINGLE ACCESSED DEVICES ON SHARED BUS Single accessed devices can be connected to an optional switched Unibus by means of the DT07 Bus switch. Devices on the shared Bus

therefore can be accessed by two different processors at different times. In the event of a CPU failure, the Bus with its devices can be switched over to the other processor.

#### 1.4.7 DB11-A BUS REPEATER

The PDP-11 Unibus is capable of handling 18 unit loads (including a DB11-A). The DB11-A Bus Repeater allows the Unibus to be extended beyond 20 Unit loads. And additional 18 unit loads can be attached to the Unibus using the bus repeater. The bus repeater does not affect the bus cycle time (it adds zero time) of any device before the DB11, and it adds a maximum of 375 ns to the cycle time of devices addressed beyond the bus repeater. It is a non-programmable device that interfaces two buses (left and right) in four sections:

- 1. Bus Repeater Control

- 2. Bus D (data) Lines

- 3. Bus A (address) Lines

- 4. Bus Unidirectional Lines.

#### 1.5 FIELD TEST SYSTEM CONFIGURATION

Listed in Table 1-1 are the units making up the dual-processor multiprocessor (enhanced availability) Field Test System.

1.6 RECOMMENDED MINIMUM PDP-11/70 MULTIPROCESSOR CONFIGURATION

(ENHANCED AVAILABILITY)

Table 1-2 lists the recommended components making up a minimum dualprocessor system.

Table 1-1 Field Test System Dual-Processor Configuration

| Quantity | Item                 | Description                  |

|----------|----------------------|------------------------------|

| 1        | PDP-11/70 Dual Proc- | consisting of:               |

|          | essor System         |                              |

| 2        | KB11-C               | KBll-C Processor modified    |

|          | (Modified)           | for multiprocessor operation |

| 1        | 870 Power Control    | Remote power controller      |

|          |                      | used in memory power supply  |

|          |                      | system.                      |

| 2        | MKA11-BA             | Dualported multiprocessor    |

|          |                      | MOS memory with Error Cor-   |

|          |                      | rection Coding and 256KB     |

|          |                      | capacity per box             |

|          |                      | (512KB total). Includes      |

|          |                      | the following:               |

|          |                      | 1) H9060 memory box          |

|          |                      | 2) two sets of Port Buffer   |

|          |                      | modules (M8158 and M8159)    |

|          | <b>4</b><br>1        | 3) two sets of Control Mod-  |

|          |                      | ules (M8161 and M8160)       |

|          |                      | 4) two Port Controllers      |

|          |                      | 5) one Multiport Multiplexor |

|          |                      | (M8162)                      |

|          |                      | 6) four 64KB MOS storage     |

|          |                      | arrays                       |

up Unit

9) Cable set

7) one H7420 power supply

8) one H7750 Battery Back-

Table 1-1 Field Test System Dual-Processor Configuration

| Quantity | Item         | Description                  |

|----------|--------------|------------------------------|

| 2        | H7420        | Processor Power supplies     |

| 1        | DIP11-C      | BOOT/IIST Panel and Logic    |

|          |              | Board                        |

| 2        | M9312        | Bootstrap Loader and         |

|          |              | Terminator                   |

| 2        | 70-142211-24 | Ruggedized Unibus Cables     |

| 2        |              | Double-width Hi-boy Cabinets |

|          |              | with 866A/E Controllers      |

| 2        | LA36-HE      | LA36CE and LAX-LG(EIA)       |

| 2        | DL11-WC      | DL11W with EIA Cable         |

| 1        | RWP04-BA     | 2 RH70-A and RP04-BA (dual   |

|          |              | access-60 HZ)                |

| 1        | RP04-BA      | 88MByte Disk pack and        |

|          |              | drive (dual access)          |

| 2        | DIP11-A      | IIST (M8717)                 |

| 2        | TWE16-AA     | Magtape                      |

| 2        | BS11A-40     | Remote Mag tape cable kit    |

| 2        | BC037-25     | Null Modern Cable            |

| 2        | •            | Single-width Hi-Boy expander |

|          |              | cabinet                      |

| <b>2</b> | BAll-P       | Expander Box (used in the    |

|          |              | SWHB Expander Cabinet)       |

| 16       | DZ11         |                              |

| 1        | M7258        | Printer Control              |

| 1        | DB11-A       | Bus Repeater                 |

| 2        | DD11-DF      | Peripheral Mounting Panel    |

|          |              | (9-slot)                     |

Table 1-2 Minimum PDP-11/70 Multiprocessor Configuration (Enhanced Availability)

| Quantity | Item             | Description                              |

|----------|------------------|------------------------------------------|

| 1        | PDP-11/70        | Dual-processor consisting of:            |

|          |                  | Double-Width Hi-boy Cabinets with        |

|          |                  | 866A/D Controllers                       |

| 2        | H9602 BA         | Expansion Cabinet (SWHB) with 866A/D     |

|          | ·<br>·           | controller                               |

| 2        | CPU Mounting Box | Installed in Double-width Hi-boy         |

|          |                  | cabinets. Houses modified KBll-C         |

|          |                  | processor, DL11-W, and M9312MP Boot-     |

|          |                  | strap/Terminator for Module. It is       |

|          |                  | also prewired for four RH70 control-     |

|          |                  | lers, and floating point processor.      |

| 2        | Modified KBll-C  | Processor modified for multiproc-        |

|          |                  | essor operation. Consists of the         |

|          |                  | following:                               |

|          | M8130 DAP Module | Data Paths (slot)                        |

|          | M8131 GRA Module | General Registers and ALU control (slot) |

|          | M8132 IRC Module | IR Decode and Condition Codes            |

|          |                  | specially modified (slot 8)              |

|          | M8123 RAC Module | ROM and ROM Control (slot 9)             |

|          | M8134 PDR Module | Processor Data and Unibus Registers      |

|          | ₩<br>•           | (slot 10)                                |

|          | M8135 TMC Module | Trap and Miscellaneous Control (slot 11) |

|          | M8136 UBC Module | Unibus and Console Control specially     |

|          |                  | modified (slot 12)                       |

|          | M8177 SAP Module | System Address Paths specially modi-     |

|          |                  | fied (slot 14)                           |

# Table 1-2 Minimum PDP-11/70 Multiprocessor Configuration (Enhanced Availability)

| Quantity | Item               | Description                           |

|----------|--------------------|---------------------------------------|

|          | M8138 YA SSR Mo    |                                       |

|          | Module             | System Status Registers (slot 15)     |

|          | M8139 TIG Module   | Timing Generator (slot 13)            |

|          | M8140 SCC Module   | System Descriptor/Console Cables      |

|          |                    | (slot 16)                             |

|          | M8181 MAP Module   | Unibus Map (slot 22)                  |

|          | M8182 CCB Module   | Cache Control (slot 17)               |

|          | M8143 ADM Module   | Address Memory (slot 18)              |

|          | M8144 DTM Module   | Data Memory (slot 20)                 |

|          | M8145 DCP Module   | Cache Data Paths (slot 21)            |

|          | 5411294 KNL Module | Console                               |

| 2        | MKA11-BA           | Dual-ported MOS memory with Error     |

|          |                    | Correction Coding. Consists of:       |

|          |                    | H9060 Memory Box (with two pairs of   |

|          |                    | Port Buffers, Multi-port Multiplexor, |

|          |                    | two pairs of Control Modules, and     |

|          |                    | four 32K word MOS storage Arrays),    |

|          |                    | and a H7420 Power Supply H7750 Bat-   |

|          |                    | tery Back-up Unit, and two Port Con-  |

|          |                    | trollers. Port Controller contains    |

|          |                    | control switches and indicators. One  |

|          |                    | Port Controller controls one port on  |

|          |                    | memory.                               |

| 2        | DL11W              | Asynchronous Serial Line Interface    |

|          |                    | with LA36                             |

| 2        | LA36 (or LA120)    | DECWRITER 11 (300 baud printer        |

|          |                    | terminal)                             |

|          |                    |                                       |

Table 1-2 Minimum PDP-11/70 Multiprocessor Configuration (Enhanced Availability)

|             |                    | Section 1                               |

|-------------|--------------------|-----------------------------------------|

| Quantity    | Item               | Description                             |

| 2           | M9312              | Bootstrap/Terminator Module with        |

| N. Carlotte |                    | special MP ROM Code                     |

| 4           | RH70               | Massbus High-Speed I/O Controller.      |

|             |                    | Up to four RH70 Massbus controllers     |

|             |                    | can be installed in prewired slots      |

|             |                    | in individual CPU's backplane.          |

|             |                    | Controller A in slots 24-27             |

|             |                    | Controller B in slots 28-31             |

|             |                    | Controller C in slots 32-35             |

|             |                    | Controller D in slots 36-39             |

|             | Each controller co | on-                                     |

|             | sists of the follo | ) <b>W</b> -                            |

|             | ing:               |                                         |

|             | M5904 MBS Module   | Massbus transceivers (3 required)       |

|             |                    | (slots 25-27, 29-31, 33-35 or 37-39,    |

|             |                    | rows A-F).                              |

|             | M8151 CST Module   | Control and status (slots 25,29,33      |

|             |                    | or 37, rows C-F).                       |

|             | M8152 AWR Module   | Word Count and address (slots 26,30,    |

|             |                    | 34 or 38, rows C-F).                    |

|             | M8153 BCT Module   | Unibus and register logic (slots 27,    |

|             |                    | 31, 35 or 39, rows C-F).                |

|             |                    | Each RH70 can control up to eight       |

|             |                    | devices which must be of the same type. |

| 2           | RP05/6             | Disk Drives (with dual-port option)     |

Table 1-2 Minimum PDP-11/70 Multiprocessor Configuration (Enhanced Availability)

| Quantity | Item             | Description                          |

|----------|------------------|--------------------------------------|

| 1        | RH01*            | Dual-port adapter. Used for dual-    |

| •        |                  | porting TE16.                        |

| 1        | TM03*            | Tape controller (Used with TE16 and  |

|          |                  | RH01)                                |

| 2        | TE16             | Tape Transport                       |

| 2        | DIP11-A          | Interprocessor Interrupt and Sanity  |

|          |                  | Timer Interface Module (M8717)       |

| 1        | DIP11-C          | Consists of Boot/IIST Panel Switch   |

|          |                  | Board (Only one per multiprocessor   |

|          |                  | system) and Boot/IIST Panel Logic    |

|          |                  | Board (Only one per multiprocessor   |

|          |                  | system)                              |

| 2        | DD11 C or D      | Peripheral Mounting Panel (System    |

|          |                  | Unit)                                |

| 2        | H7420 Power Sup- | Refer to Figure 1-1. Two H7420s con- |

|          | plies            | tain the dc power regulators for the |

|          |                  | CPU mounting box.                    |

| 14       | H7441+5 Regu-    | Eight H7441+5 Vdc regulators supply  |

|          | lators           | dc power. An additional H7441 is     |

|          |                  | required if floating point processor |

|          |                  | is installed.                        |

| 2        | 5411086 Modules  | Each H7420 contains one 5411086 mod- |

|          |                  | ule which monitors the ac input      |

|          |                  | voltage in addition to its function  |

|          |                  | as a 15 Vdc regulator.               |

<sup>\*</sup>Optional

# Table 1-2 Minimum PDP-11/70 Multiporcessor Configuration (Enhanced Availability)

Quantity

Item

Description

866D (115 V) or Controls ac power input.

866E (230V)

Power Control

#### Table 1-3 MKAll Memory Options

Designator

MKA11-AA

(For 115 Vac)

MKA11-AB

(For 230 Vac)

MKA11-AC

(For 115 Vac/50 Hz)

MKA11-AD

MKAll-AY

MKA11-BA

Description

Single Port Memory, 128K words Includes:

H9060 Memory Box with one pair of Port

Buffers, Single Port Jumper Card, two

pair of Control Modules, and four 32K

word MOS Storage Arrays, a Power Supply,

Battery Back-up Unit, Port Controller,

and Cable Set

Single Port Memory, 128K words same as MKAll-AA, except for 230 Volt or 60 Hz operation

Single Port Memory, 128K words same as MKAll-AA, except for 115 volt 50 Hz operation

Single Port Memory, 128K words same as MKAll-AA, except for 230 Volt 50 Hz operation

Single Port Memory Box, 64K words

Includes: H9060 Memory Box with one

pair of Port Buffers, Single Port.

Jumper Card, two pair of Control Modules, and two 32K word MOS Storage Arrays

Dual Port Memory, 128K words

Includes: H9060 Memory Box with two

pair of Port Buffers, Multiport Multiplexor, two pair of Control Modules, and

four 32K word MOS Storage Arrays; a power

#### Table 1-3 (cont) MKAll Memory Options

Designator

Description

Supply, Battery Back-up Unit, two Port

Controllers, and Cable Set

MKAll-BB Dual Port Memory, 128K words. Same as

MK11-BA, except for 230 volt 60HZ opera-

tion.

MKA11-BC

(For 230 VAC)

(For 115 VAC/50HZ)

Dual port memory, 128K words, same as

MK11-BA, except for 115 volt 50HZ

operation

MKAll-BD

(For 230 VAC/50HZ)

Dual port memory, 128K words, same as

MK11-BA, except for 230 volt 50HZ

operation.

MKAll-BY

MKAll-UA

Dual port memory box, 64K words,

Includes: H9060 memory box with two

pairs of port buffers, Multiport multi-

plexor, two pair of control modules,

and two 32K word MOS storage arrays.

Single port upgrade Kit, upgrades

single port memory (MKAll-AA through-AD)

to dual port memory. Includes: one

pair port buffers and one multiport

multiplexor.

MKA11-UB

Multiport upgrade kit, adds another port

to existing dual-port memory (MKAll-BA

through BD) or triport memory. Includes:

one pair of port buffers.

# Table 1-3 (cont) MKAll Memory Options

| Designator | Description                          |

|------------|--------------------------------------|

| MS11-KE    | 32 word Storage Array Module, imple- |

|            | mented with 4K MOS RAM chips         |

| M8158      | Port Address Buffer Module           |

| M8159      | Port Data Buffer Module              |

| M8160      | Control A Module                     |

| M8161      | Control B Module                     |

| M8162      | Multiport Multiplexer Module         |

| M8163      | Single Port Jumper Card              |

CHAPTER 2

#### SYSTEM TECHNICAL DESCRIPTION

#### 2.1 SCOPE AND PURPOSE

This section describes the system theory of operation of the PDP-11/70 Multiprocessor System. Its purpose is to give the reader an understanding of the operation of the Multiprocessor System at the system-level by means of a system functional overview and description in order to assist him in installation, maintenance, and troubleshooting. More detailed information concerning the operation of each one of the components making up the Multiprocessor System can be found in the appropriate field maintenance component manuals listed in Appendix C, a List of Related Documents.

#### 2.2 PDP-11/70 MULTIPROCESSOR CONCEPTS

Multiprocessors have from two to four central processors (the PDP-11/70 MP has two processors, the PDP-11/74 can have up to four processors). The Multiprocessor system uses a common (tightly-coupled) multiported memory. Each processor has access to the memory by means of an individual port. The memory has four ports and, therefore, can be connected to four different processors via these ports. All the processors are controlled by a single operating system, the RSX-11 MP that provides interaction between the processors, the programs they are executing, and the I/O devices.

connected through the Boot LIST Panel logic board to the Unibus Map Board of each processor. The Unibus Map Board is connected to the Halt Alarm of each processor, the M9312 Bootstrap Terminator Module, and to the IIST Interface Module on the IIST BUS. The IIST Interface Modules of all processors are all connected to each other by means of the IIST Bus.

2.4 SIMPLIFIED OVERVIEW OF MULTIPROCESSOR OPERATION (NON-CACHED)

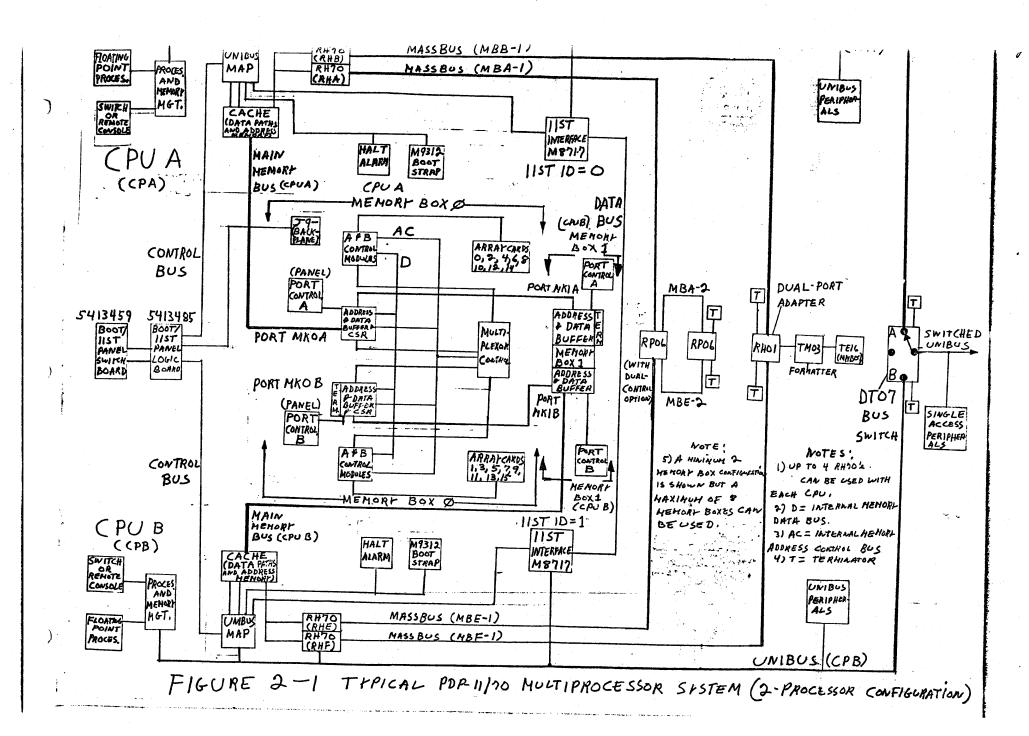

Assume that one task is currently active on each processor shown in

Figure 2-1: Task A on Processor CPU A and Task B on Processor CPU B

(to simplify this initial explanation the effect of the cache has been ommitted). When Task A issues a non-I/O directive, the EMT (Emulator Trap) occurs on processor CPU A. CPU A enters kernel state and is vectored to the Executive code that handles synchronous traps. Since no I/O is performed, the Executive carries out the directive and returns control of the processor to Task A. Execution of Task B on Processor CPU B is uninterrupted.

When Task A issues a request for I/O, processor CPU A enters the kernel state and is vectored to the Executive code that handles synchronous traps. If the device can be accessed from CPU A, i.e., it is located on CPU A's Unibus, the driver is called immediately to perform I/O.

Task A can suspend execution until I/O completes thus freeing CPU A for use by another task.

If the device resides on the Unibus of Processor CPU B then the Executive transfers control to CPU B by generating program interrupt request via the Unibus to CPU A's Interprocessor Interrupt and Sanity Timer

(IIIST) module where it is loaded into a shift register and then clocked out over the serial data lines of the IIST Bus to be received by CPU B's IIST Interface Module. From there, it is sent via CPU B's Unibus to the CPU B Processor (the vector address that is sent to the CPU B Processor along with the Interrupt signal is determined by Vector Address Selection Switches on its IIST Interface Module. The Executive has now transferred control to CPU B and released CPU A for use by another task. The Executive, now running on Processor CPU B calls the driver to initiate the I/O transfer with the device located on CPU B's Unibus. As in the single processor system, the allocation of CPU's to tasks is interrupt driven. When the I/O operation is completed, the Executive will scan the list of active tasks, searching for the highest priority tasks that can run (including the null task). On each scan of the list, the Executive will start unblocked tasks until all processors are busy.

When different processors are attempting to access the Executive at the same time, the contention is resolved by a single software lock that blocks access to the Executive by all but one CPU. Other processors will assert lock requests until the owning processor opens the lock and returns to user state. Contention involving the Executive is, therefore avoided by forcing all CPU's to accessthe Executive data base in serial fashion.

2.5 SIMPLIFIED OVERVIEW OF MULTIPROCESSOR OPERATION (WITH CACHE)

In the Multiprocessor System the cache of each processor is independent and unsynchronized and is connected by means of independent main memory bus cables to an individual port on the multiported MKAll common memory. Multiple copies of the data are not always maintained

in all the caches. To avoid, therefore, the problem of using data in a processor's cache that does not reflect the current data in main memory, cache flush and cache bypass operations have been added to the modified KBllC Processor. These functions permit the contents of the cache to be invalidated or the cache to be bypassed for certain accesses when the cache at that moment no longer reflects accurately the data in main memory. In a cache flush the entire contents of a Processor's cache is invalidated; during a Cache Bypass the Cache is bypassed and all references are forced to main memory.

In addition to the functions listed above a software locking convention has been added to the processor by adding an uninterruptible read-modify-write (DATIP-DATO) memory cycle to the MKAll memory and modifying the ASRBinstruction to bypass the cache, initiate the DATIP-DATO memory cycle, and implement a lock by the use of the Carry (C) bit which is used to determine and reflect the condition of the lock byte at the shared data location. During potential cached operations, Cache Bypass can be performed at different times in the Multiprocessor System. Bypass of the Cache can be uninterrupted, i.e. quickly turned on and then off for short sections of code. Uninterrupted cache bypass is required when short segments of code, such as interrupt service routines must have guaranteed access to main memory.

Cache Bypass is also, of course, required when two or more parallel processes are accessing a common data base. In this case the effect on system performance caused by bypassing the cache is reduced by confined ing the virtual address space over which cache bypass occurs to the region containing shared data.

When a process is allowed to run serially on all CPU's, total cache invalidation is necessary by means of a cache flush. Because all con-

teXt switching is performed by the Executive, the cache flush occurs without task intervention. A system-initiated cache invalidation procedure occurs as follows:

- 1. Read location X on CPU A.

- 2. Flush the CPU A Cache.

- 3. Write location X on CPU B.

- 4. Flush the CPU B Cache.

- 5. Read location X on CPU A.

The flush of CPU A's cache performed during the initial transition from CPU A to CPU B ensures that the next reference to location X from processor CPU A will correctly access main memory.

Invalidation of the cache's contents by means of a cache flush will also occur if a match should occur between an I/O memory address and a cache tag address when I/O traffic is being sent to main memory.

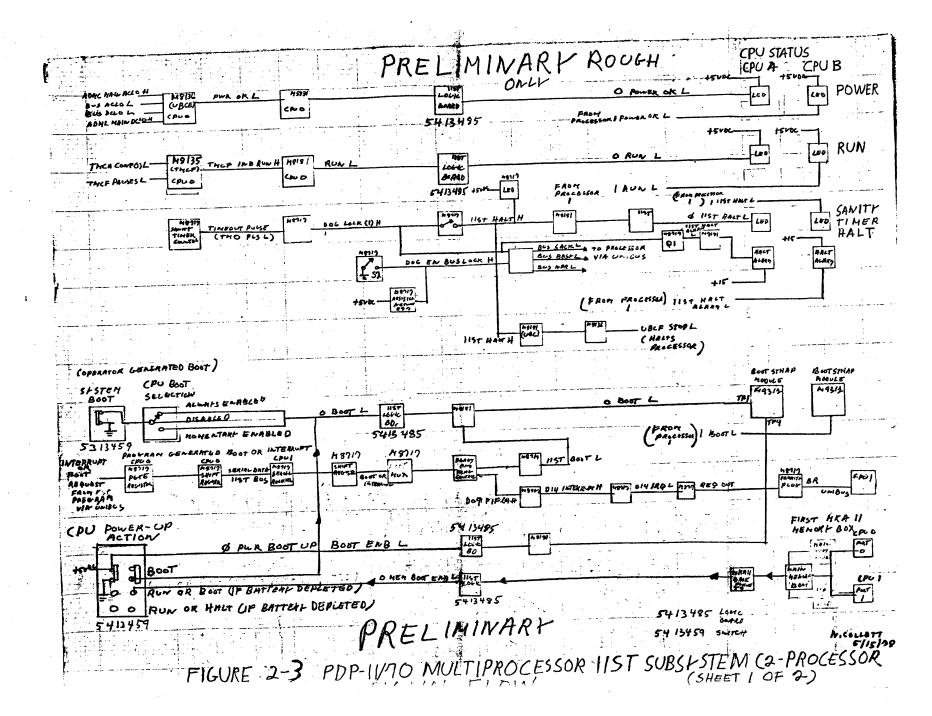

- 2.6 INTERPROCESSOR INTERRUPT AND SANITY (IIST) SYSTEM

The IIST Multiprocessor System consists of the following:

- 1. IIST Interface Module (Each processor has its own M8717).

- 2. BOOT/IIST Panel Switch Board (Each Multiprocessor System has only one.)

- BOOT/LIST Panel Logic Board (Each Multiprocessor has only one.)

- 4. Unibus Map Board (Part of each CPU System, but interfaces with the IIST Interface Module).

- 5. Cable Assemblies

- 5A. IIST Bus Cable (Connects all IIST Interface modules.

Each multiprocessor has one.)

- 5B. BOOT/LOCK/CONTROL 20-conductor ribbon Cable. One for each processor. Connects between M8717 and M8181.)

- 5C. BOOT/HALT Alarm 8-conductor ribbon Cable (Connects between M8181, the Halt Alarm and the M9312. One for each processor.)

- 5D. BOOT/IIST Panel Switch Cable<sup>S</sup>(Connect between the BOOT/IIST Panel Switch Board and the BOOT/IIST Panel Logic Board. Each Multiprocessor has two.)

- 5E. BOOT/IIST Panel Logic Board Cable (Connects between the IIST Panel Logic Board and the Unibus Map Board of each processor. (Each processor has one.)

- 5F. Memory Boot Cable (Connects between the BOOT/IIST Panel Logic Board and the J9 connector on the backplane of the first box of memory on the system or memory 0).

## 2.6.1 Major Purpose

The major purpose of the IIST subsystem (IIST Interface Module M8717 and the IIST Bus) is to allow the operating program in one processor to send interrupt and boot requests to any or all of the other processors, in the system by means of the IIST Interface Module and the IIST Bus for the purpose of rescheduling activity on the various processors.

(The actual Interrupt signal and vector address is sent via the Unibus to the selected Processor by the IIST Interface Module that received the request over its IIST Bus.) In addition a Sanity Timer is included in the IIST Interface Module which, if not refreshed periodically by the operating program within a programmable timout period will cause a Sanity Timer generated Interrupt or Boot request to be transmitted to any or all of the processors in the system, thereby notifying them of a possible faulty processor.

2.6.2 BOOT/IIST Panel Switch and Logic Boards

The BOOT/IIST Panel Switch (together with the BOOT/IIST Panel Logic

Board) is used to perform the following functions:

## (Displays

- 1. Power and operating Status of each of the processors (POWER, RUN, OR HALT)

- 2. Allows operator to manually boot any of the processors.

- 3. Allows operator to select type of BOOT action occurring on CPU POWER-UP action sequence (Boot, Run or Boot if battery depleted, or Run and halt if battery depleted)

- 4. Permits operator to partition the processors for operation as

dual, tri or quad multiprocessors in A or B groupings or as Standalones.

5. Permits the operator to place any Processor in ON or OFF line mode by disabling or enabling its IIST Interface Module.

## 2.6.3 IIST Interface Subsystem

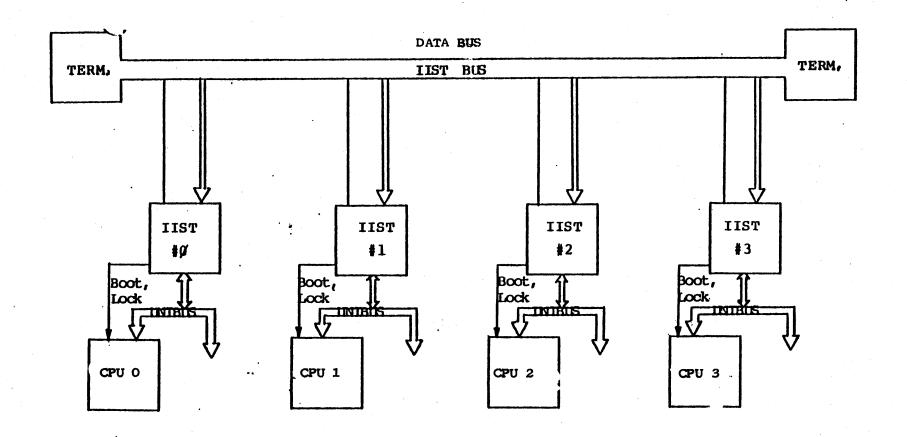

The IIST Interface subsystem consists of from two to four IIST Interface modules (M8717) depending upon the number of main processors, connected to each other by means of the IIST Bus cable. (Refer to Figure 2-2, which shows a simplified block diagram of the IIST Interface Subsystem using a four-processor configuration).

Each IIST Interface module is a hex-height module that plugs into a small peripheral Controller (SPC) slot in a DD11-C or equivalent backplane. Each module is connected to the Unibus through the backplane. The configuration of the IIST interconnecting Bus Cable depends upon the number of IIST Interface Modules (number of processors) present in the system and the distance between them. One IIST Interface Module is required for each Processor.

- 2.6.4 Summary of Major Functions

The IIST Interface Subsystem performs or provides the following functions:

- a. Allows the operating program in one processor to send interrupt and Boot requests to any or all processors.

- b. Provides a Sanity Timer that can time out and generate

FIGURE 2-2

IIST INTERFACE SUBSYSTEM BLOCK

DIAGRAM

interrupt or boot requests to any or all processors

- c. Provides for locking up or preserving the state of a faulty processor when its Sanity Timer times out

- d. Contains Processor (IIST Interface Module) identification switches

- Allows a processor to accept or ignore interrupt and/or boot requests

- f. Contains a DCLO/Disconnect detection circuit

- g. Provides for Error detection by means of parity bits

- h. Includes On and Off line maintenance capabilities

Further details of these major functions are contained in the following paragraphs.

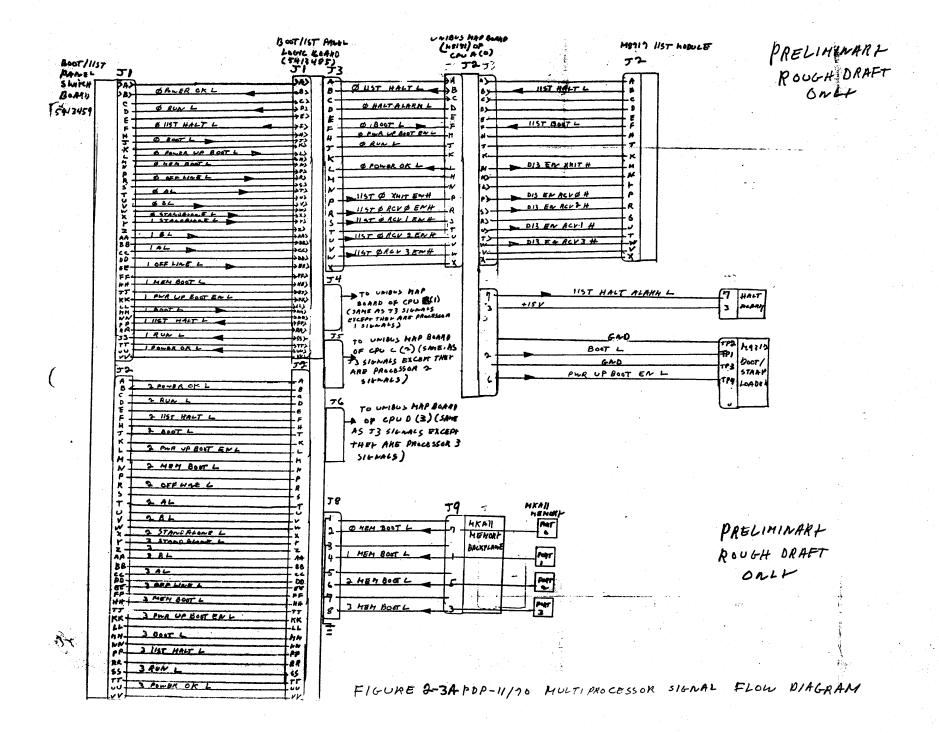

Shown in Figure 2-3 is a Multiprocessor IIST subsystem signal flow block diagram using a two processor configuration.

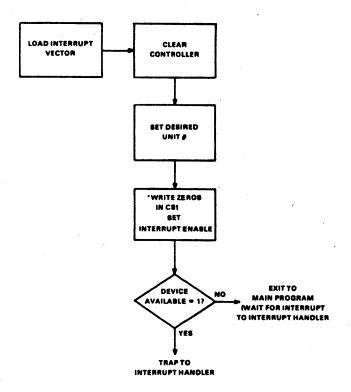

2.6.5 Program-Generated Interrupts and/or Boots

An operating Program in one processor causes interrupt and/or

boot requests to be sent to other processors in the system by first

setting transmit enable bits in an IIST Interface Module internal

device register specifying which processors are to receive an interrupt

and/or boot request and then setting a GO bit which starts transmission

of a serial character on the IIST Bus to the selected IIST Interface

4-.

Module. This is the primary function of the IIST sybsystem and is used by the operating system to re-schedule system activity on the various processors. Pre-empting task execution on a processor for I/O service is an example of rescheduling system activity.

A boot request properly received and enabled boots the receiving CPU by triggering its M9312 bootstrap module. (The M9312 is electrically connected through the Unibus Map Board to the IIST Interface Module by means of the Boot/Lock/Control Cable.) This boot function is used by the multiprocessor system boot code to permit the first CPU that has been booted to bring up the other CPU's in the system.

There are eight enable bits; four to specify processors selected to receive interrupt requests, and four to specify processors selected to receive boot requests. Therefore, in a single operation any or all processors may be interrup ted and/or booted. One processor can selectively ignore interrupt or boot requests from another processor by setting mask bits in the IIST interval device masking registers.

# 2.6.6 S Sanity-Timer Generated Interruptsand/or Boots and Processor Lock-Up

Under normal operation the Sanity Timer contained in the IIST Interface Module will be periodically refreshed by the Executive software if, however, the refresh commands to not occur within the programmed period, the IIST will issue an interprocessor interrupt to inform the other processors in the On-Line system of the faulty processor operations.

In addition a system lockup will be generated so that the state of

the processor can be frozen upon expiration of the sanity Timer thereby preserving the processor state and limiting the effect of a faulty

processor. The Lockup conditions held until an interrupt or boot

request is received by the IIST Interface Module. The method of

lockup can vary since it is switch selectable and will depend upon

the settings of the two switches on the IIST Interface Module. The

Lockup can be accomplished by holding the Unibus of the faculty Processor or by directly halting the processor itself through a lock line.

## 2.6.7 Processor Identification Switches

The processor identification switches (IIST Interface Module) contain ed on the IIST Interface Module can be read by the operating program to facilitate CPU-specific operations and to facilitate fault isolation during troubleshooting and maintenance. They also provide unique identification of the source and destination of all interrupt and boot requests. They, therefore, can be thought of as the CPU number, even though they are switches on the IIST Interface Module and determine the identification of the IIST Interface Module.

2.6.8 Masking of Processors Against Interrupts and/or Boots

Mask Registers in the IIST Interface Module can be programmed so that

a processor can selectively accept or ignore interrupt and/or boot

requests from other processors in the system. This capability is used

by the reconfiguration software to isolate one (or more) of the

processors that have been established as an independent or standalone

system.

For example, a tri-processor multiprocessor system could be masked by use of the mask registers into an off-line thread for troubleshooting purposes with one processor while leaving the other two processors grouped together on-line and running as a dual-processor multiprocessor. (Of course the same division could be manually accomplished by the operator at the BOOT/IIST Control Switch Panel by use of the IIST CONFIGURATION switches.)

## 2.6.9 DCLO/Disconnect Detection

A DCLO/Disconnect detection circuit in the IIST Interface Module is used to notify a processor when other IIST Interface Modules in the ed system are either powered down or disconnect from the IIST interconnecting Bus. The interconnecting IIST Bus is T-connected to permit an IIST Interface Module to be disconnected or powered down without disturbing the remaining IIST Interface Modules on the IIST (Data) Bus.

#### 2.6.10 Error Detection

The IIST Interface subsystem provides error detection by means of parity bits transmitted along with interrupt and boot requests on the IIST interconnecting Bus. If an error is detected, an error bit identifying the transmitting IIST Interface Module is set but no normal interrupt or boot action is taken.

## 2.6.11 ON/OFF Line Maintenance Capability

ON or OFF Line maintenance and checkout is accomplished by first running the single-interface portion of the IIST diagnostic program, YM-Z095A with the other processors halted and initialized, and then the Multi-interface Exerciser portion of it on all processors in the

system simultaneously for at least fifteen minutes. The results of the diagnostics must be completely error-free to indicate that the IIST Interface Subsystem is operating properly.

## 2.6.12 IIST Interfaces

#### 2.5.12.1 IIST to Unibus

The Unibus provides the interface between a PDP-11/70 Processor and its IIST Interface Module. All data transfers to or from the IIST to the processor are accomplished under program control through IIST device registers residing in the Unibus peripheral address space. The Unibus also provides the path by which the IIST may interrupt and send the Vector Address to the processor.

The IIST Interface Module functions as any standard device on the Unibus. Addresses, data, and control information are sent along the standard lines of the Unibus. Communication between the processor and the IIST Interface Module is like any two standard devices on the Bus and takes the form of a master-slave relationship with the IIST capable of being either masteror slave. Priority of a particular IIST Interface Module is established by a priority plug in the IIST Interface Module. The IIST can have a priority level of anywhere from BR4 - BR7 or when generating a Sanity Timer Halt it can generate an NPR to hold the Bus, if certain option switches have been, enabled. Horizontal priority is established, like any standard Unibus device, by its location on the Bus.

Two 16-bit Unibus registers are employed to interface the IIST to the PDP-11/70 Processor. These registers act as an access path to the ten

internal device registers of the IIST Interface Module which may be read and loaded under program control to monitor IIST status and to control operation

2.6.12.2 Program-Generated Interrupt Transmission (IIST to Processor via Unibus)

(4-1)

Shown in Figure 2-4 is the Interrupt Handling sequence that occurs between the IIST and the processor.

When the IIST Interface Module receives an interrupt request and the Interrupt Enable (INTR ENB) signal is set, then an interrupt request is asserted. As a result of the presence of the interrupt request and the INTR ENB signal, a Bus Request (BR) is asserted on the Unibus to the processor by the IIST Interface Module. The priority level of the BR is determined by a priority plug in the IIST Interface Module.

The processor responds with a Bus Grant (BG). Since an interrupt is being requested by the IIST Interface Module, the BG is blocked and Bus Sack is asserted by the IIST. The processor then clears BG, BBSY, and MSYN (froma previous operation). When the IIST sees that BG, Bus BBSY, ane MSYN are all cleared, it becomes bus master, aserting the BBSY signal. This signal causes the INTR signal to be asserted (SACK is now cleared after INTR but prior to start of last bus cycle) and the Interrupt Vector Address (selected by switches on the IIST Interface Module) to be driven onto the Unibus Data lines. When the Processor sees the assertion of Bus INTR, it waits a short time and then strobes the data lines, and issues Bus SSYN. When the IIST sees the assertion of Bus SSYN,

The processors are all functionally equal with the ability to perform any task and function either as slave or master during program operation. The common memory contains a single copy of the Executive and its data base. Each processor is connected to each memory port and all physical memory is addressable from each CPU.

The system is fully symmetrical, i.e., any task can run on any processor and any processor can service a non-I/O Executive request. Of course, requests for I/O and the servicing of interrupts must be performed by the processor to which the device controller is attached. Each processor is connected by an Interprocessor Interrupt and Sanity Timer Bus (IIST) in order to permit the shared Executive to interrupt processors for the purpose of re-scheduling system activity. The Executive, in effect, treats the processors as if they were additional resource devices available for use whenever program activity demands it, and can schedule tasks to run on the various processors whenever it is required.

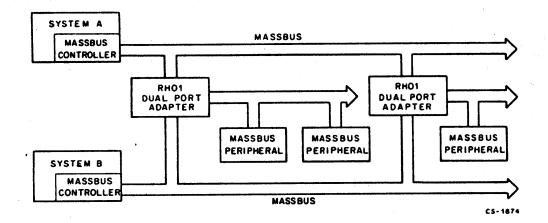

2.3 TYPICAL PDP-11/70 MULTIPROCESSOR SYSTEM (2-PROCESSOR CONFIGURATION)

Shown in Figure 2-1 is a simplified block diagram of a typical PDP-11/70

Multiprocessor System using two main processors. The cache of each

processor is connected by means of independent main memory Bus cables to

a separate port on a box of the MKall multiported common memory;

CPUA to port MKOA and CPUB to port MKIB. The memory boxes are connected

to each other with a minimum of two boxes required and a possible maximum of up to form memory boxes Every port on every memory box is

connected to a memory Controller panel which controls the operation

of the memory port to which it is connected. There is one Boot

processor Interrupt and Sanity Timer Panel (IIST) switchboard that is

TO BE SUPPLIED

it drops control of the Unibus by clearing the INTR signal, the vector address and the Bus BBSY signal. The Processor then clears SSYN and asserts BBSY making the CPU the bus master and completing the cycle.

#### NOTE

The logic circuits in the IIST Interface

Module that generate SACK AND BBSY signals

when the Sanity Timer times out in order

to freeze or lock the Bus are not the same

circuits used to generate these signals

during a normal communication exchange

between the IIST Interface Module and the

Processor.

## 2.6.12.3 IIIST to IIST Interface

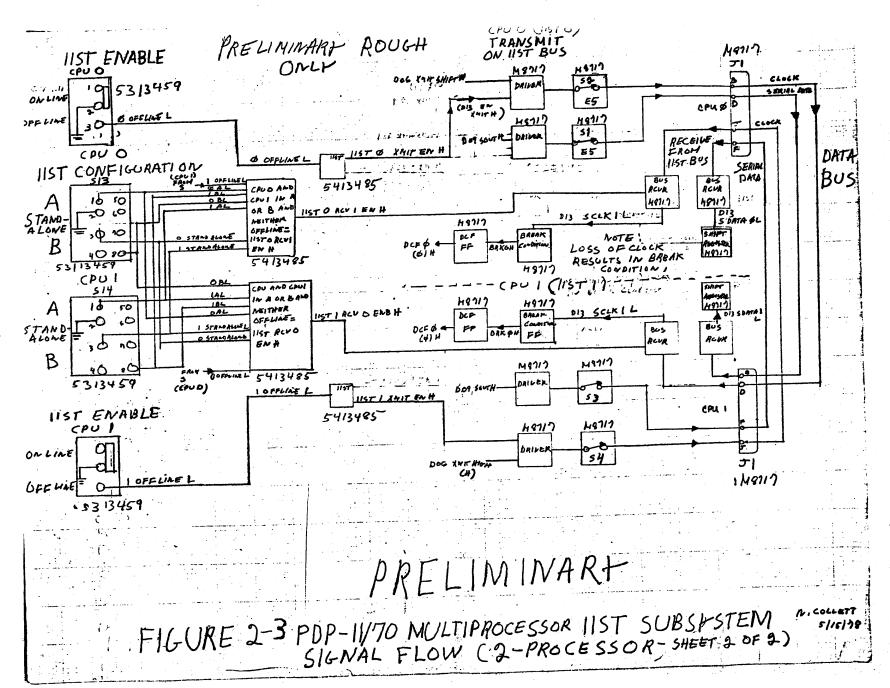

All IIST Interface Modules in the system are interconnected by means of the IIST Bus, composed of four signal pairs. This bus carries interrupt and boot requests between the interfaces.

(Refer to Figure 2-5.)

7 h

Interrupt and boot commands are transmitted serially on the bus. Each IIST drives one pair of signal lines on the bus: one line of the pair is for data, the other for a clocking signal. The pair of lines to be used for transmission is selected by the Self-Indentification switches within the IIST. Each IIST must have a unique Self-ID. Therefore, each signal pair on the bus has at most one driver, eliminating any requirement for a bus arbitration scheme.

TO BE SUPPLIED

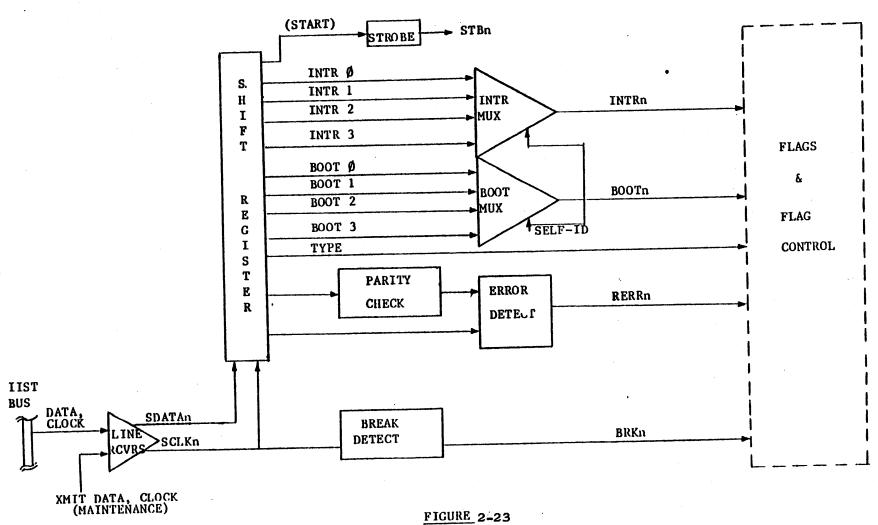

Each list interface receives all four serial signal pairs. The line from which an interrupt or boot request is received therefore identifies the source of that request.

Upon transmission, the IIST interface sending interrupt and/or boot requests specifies within a single serial character one or more destination interfaces. The character format is shown on Figure 2-5. There are four pairs of Interrupt/Boot destination fields, one Type bit (specifying whether the Interrupt/Boot requests are programor sanity-timer generated), one parity bit (provided by the program), and a Framebit (which must be 0). Each receiving interface connected to the particular transmission line receives and assembles the entire character, checks for parity and framing errors, and, assuming no errors are detected, responds to a particular 2-bit field, selected by its Self-ID switches.

Absence of the clocking signal on a transmission line is detected by the receiving interfaces as a powerdown or disconnect condition.

The bus is structured such that there are no serially-threaded paths through any interface. Also, the driving circuits are chosen such that only passive terminations to ground are required at the ends of the cable; these terminators are part of the cable assembly. Furthermore, the receiving circuits always present high impedance to the cable, whether the interface is powered on or off. Therefore, any IIST interface may be powered down or disconnected without affecting the other interfaces.

2.6.12.3.1 Program-Generated Interrupt/Boot Operation

The program causes interrupt and/or boot requests to be sent to other processors in the system by first setting "transmit enable" bits, specifying which processors are to receive an interrupt and/or boot request, and then setting a GO bit, which starts transmission of a serial character on the IIST bus. There are eight enable bits: four to specify processors destined to receive interrupt requests, and four to specify processors destined to receive boot requests. Therefore, in a single operation, any or all processors may be interrupted and/or booted. One processor can selectively ignore requests from another processor by setting a mask bit.

## 2.6.12.3.2 Sanity Timer Operation

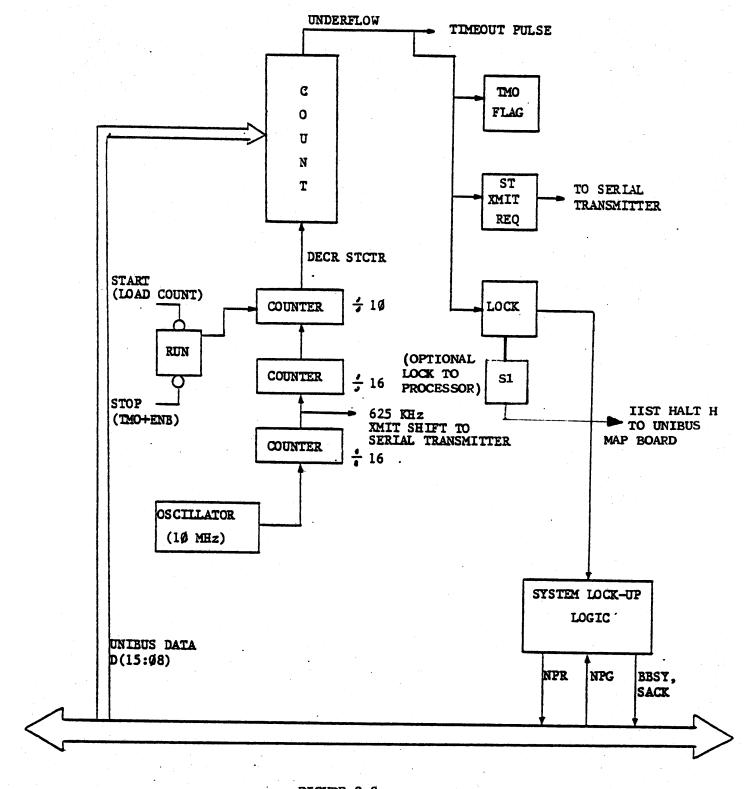

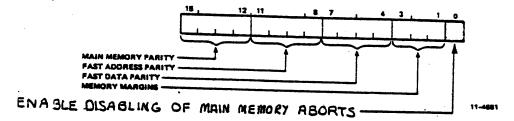

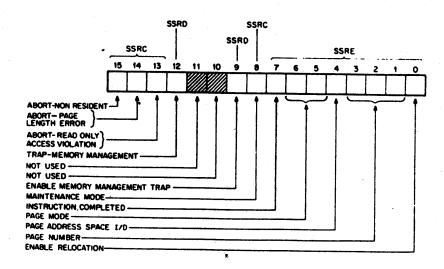

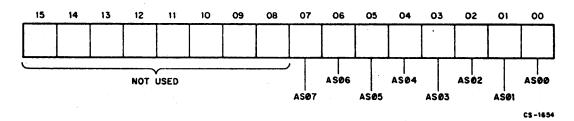

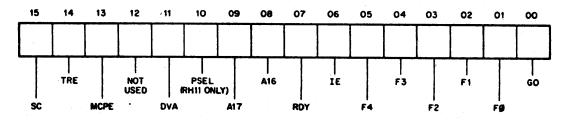

The Sanity Timer portion of the IIST consists of a clock and an 8-bit counter. To start the timer, the program loads the counter with a number specifying the desired timer duration. The clock then decrements the counter once every 256 uS. If the counter underflows from 0 to -1, a timeout is said to have occurred. In a properly running processor, the program will reload the counter before it times out, thereby continually preventing a timeout condition.