# PDP-11/84 System

Technical and

**Reference Manual**

# PDP-11/84 System

Technical and

**Reference Manual**

### December 1987

The information in this document is subject to change without notice and should not be construed as a commitment by Digital Equipment Corporation. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license and may be used or copied only in accordance with the terms of such license.

No responsibility is assumed for the use or reliability of software on equipment that is not supplied by Digital Equipment Corporation or its affiliated companies.

Copyright ©1987 by Digital Equipment Corporation

All Rights Reserved. Printed in U.S.A.

The following are trademarks of Digital Equipment Corporation:

**RSTS** Micro/RSX DEC **RSX** MicroVAX **DECmate** RT PDP **DECnet** ULTRIX PDP-11 **DECUS UNIBUS** PDP-11/84 DECwriter VAX P/OS DIBOL **VAXstation** Professional J-11 VMS Q-bus MASSBUS VT Q22-bus Micro/PDP-11 Work Processor Rainbow Micro/RSTS

| About TI       | his Manual                             | v            |

|----------------|----------------------------------------|--------------|

| Chapter        | 1 System Overview                      |              |

| 1.1            | Introduction                           | 1-1          |

| 1.2            | System Components                      | 1-1          |

| 1.2.1          | KDJ11-BF CPU Module                    | 1-1          |

| 1.2.2          | KTJ11-B UNIBUS Adapter Module          | 1-2          |

| 1.2.3          | MSV11-JD/JE Memory Module              | 1-2          |

| 1.3            | Related Documents                      | 1-2          |

| 1.3.1          | Digital Personnel Ordering Information | 1-3          |

| 1.3.2          | Customer Ordering Information          | 1-3          |

| Chapter        | 2 Functional Description               |              |

| 2.1            | -                                      |              |

|                | Introduction                           | 2–1          |

| 2.2            | PMI Bus Description                    | 2-2          |

| 2.2.1<br>2.2.2 | PMA Representation                     | 2-5          |

| 2.2.2          | DMA Requests                           | 2-6          |

| 2.2.4          | UNIBUS Device Interrupt Requests       | 2-9<br>2-11  |

| 2.2.5          | PMI Data Transfer Protocol             | 2-11         |

| 2.2.6          | PMI Data in Cycles (DATI and DATIP)    | 2-13         |

| 2.2.7          | PMI Block Mode Data In Cycles          | 2-14         |

| 2.2.8          | PMI Data Out Cycles                    | 2-16         |

| 2.3            | Memory Management                      | 2-17         |

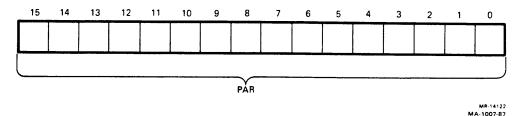

| 2.3.1          | Page Address Registers                 | 2-19         |

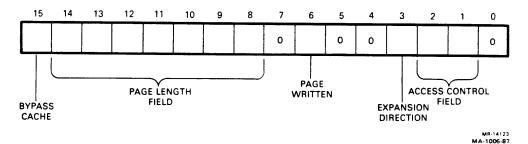

| 2.3.2          | Page Descriptor Registers              | 2-19         |

| 2.3.3          | Memory Management Register 0           | 2-20         |

| 2.3.4<br>2.3.5 | Memory Management Register 1           | 2-22         |

| 2.3.6          | Memory Management Register 2           | 2-22         |

| 2.3.7          | Memory Management Register 3           | 2-22<br>2-23 |

| 2.3.8          | Memory Relocation                      | 2-23         |

| 2.4            | KDJ11-BF Cache                         | 2-24         |

| 2.4.1          | KDJ11-BF Cache Operations              | 2-24         |

| 2.4.2          | KDJ11-BF Cache Organization            | 2-26         |

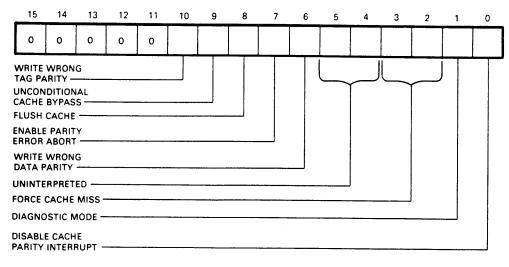

| 2.4.3          | Cache Control Register                 | 2-28         |

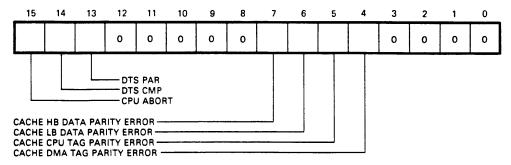

| 2.4.4          | Memory System Error Register           | 2-31         |

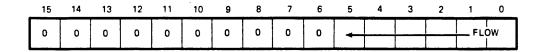

| 2.4.5          | Hit/Miss Register                      | 2-33         |

| 2.5            | Additional CPU Register Descriptions   | 2-33         |

| 2.5.1          | Processor Status Word                  | 2 22         |

| 2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7<br>2.5.8 | CPU Error Register                        | 2-35<br>2-35<br>2-36<br>2-38<br>2-39<br>2-42<br>2-43 |

|-------------------------------------------------------------|-------------------------------------------|------------------------------------------------------|

| 2.6                                                         | Stack Limit Protection                    | 2-44                                                 |

| 2.7                                                         | Kernel Protection                         | 2-45                                                 |

| 2.8                                                         | Trap and Interrupt Service Priorities     | 2-45                                                 |

| 2.9<br>2.9.1<br>2.9.2<br>2.9.3<br>2.9.4<br>2.9.5            | Console Serial Line Unit                  | 2-46<br>2-47<br>2-48<br>2-49<br>2-49<br>2-50         |

| 2.10                                                        | Kernel/Supervisor/User Mode Descriptions  | 2-50                                                 |

| 2.11                                                        | PMG Counter                               | 2-51                                                 |

| 2.12<br>2.12.2<br>2.12.3<br>2.12.3<br>2.12.4                | DMA Cache Enable/Disable                  | 2-52<br>2-52<br>2-54<br>2-54<br>2-55                 |

| 2.13<br>2.13.<br>2.13.<br>2.13.                             | 2 Optional UNIBUS Memory                  | 2-55<br>2-56<br>2-58<br>2-62                         |

| 2.14<br>2.14.<br>2.14.<br>2.14.<br>2.14.                    | Diagnostic Data Register                  | 2-65<br>2-66<br>2-67<br>2-69<br>2-69                 |

| Chapter                                                     | 3 Bootstrap and Diagnostic ROM Programmin | g                                                    |

| 3.1                                                         | Introduction                              | 3-1                                                  |

| 3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6   | Boot Command                              | 3-3<br>3-5<br>3-6<br>3-8<br>3-9<br>3-11              |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3                              | Setup Command 2                           | 3-12<br>3-13<br>3-13<br>3-19<br>3-21                 |

| 3.3.6            | Setup Command 6                                              | 3-23         |

|------------------|--------------------------------------------------------------|--------------|

| 3.3.7            | Setup Command 7                                              | 3-23<br>3-24 |

| 3.3.8            | Setup Command 8                                              | 3-25         |

| 3.3.9            | Setup Command 9                                              | 3-25         |

| 3.3.10           | Setup Command 10                                             | 3-26         |

| 3.3.11           | Setup Command 11                                             | 3-26         |

| 3.3.12           | Setup Command 12                                             | 3-27         |

| 3.3.13<br>3.3.14 | Setup Command 14                                             | 3-27         |

| 3.3.15           | Setup Command 14                                             | 3-29<br>3-29 |

| 3.4              | Diagnostic Error Messages                                    | 3-31         |

|                  | Bootstrap Programs                                           | 3-31         |

| 3.5.1            | Bootstrap List                                               | 3-33         |

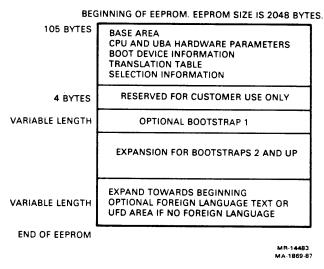

| 3.5.2            | EEPROM Format                                                | 3-35         |

| 3.5.3            | General Rules for EEPROM User Boots                          | 3–36         |

|                  | Boot ROM Facility (M9312 compatible)                         | 3-38         |

| 3.6.1            | Boot ROM Installation                                        | 3-38         |

| 3.6.2<br>3.6.3   | ROM Addresses 17773000—17773776                              | 3-38<br>3-38 |

| 3.6.4            | Single ROM Programs                                          | 3-30         |

| 3.6.5            | Multiple ROM Programs                                        | 3-39         |

| 3.6.6            | Program Header                                               | 3-39         |

| 3.6.7            | ROM Data Organization                                        | 3-40         |

|                  | J-11 Micro ODT                                               | 3-40         |

| 3.7.1            | / (ASCII 057) Slash                                          | 3-41         |

| 3.7.2            | Return (ASCII 015)                                           | 3-42         |

| 3.7.3            | Line Feed (ASCII 012)                                        | 3-42         |

| 3.7.4<br>3.7.5   | \$ (ASCII 044) or R (ASCII 122) Internal Register Designator | 3-42         |

| 3.7.6            | G (ASCII 107) Go                                             | 3-43<br>3-43 |

| 3.7.7            | S Ctri Snift S Binary Dump                                   | 3-43         |

| Appendix         | A CPU Instruction Timing                                     | -            |

| A.1              | Introduction                                                 | A-1          |

| A.2              | Source and Destination Table Notes                           | A-19         |

| Appendix         | B PDP-11/84 Hardware/Software Differences                    |              |

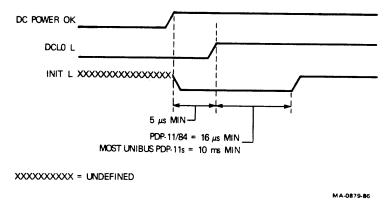

| B.1              | UNIBUS Power-up Protocol Differences                         | B-1          |

| B.2              | PDP-11/84 and PDP-11/44 Hardware Differences                 | B-2          |

| B.3              | PDP-11/84 and PDP-11/70 Hardware Differences                 | B-4          |

| B.4              | Software Differences                                         | B-7          |

|                  |                                                              |              |

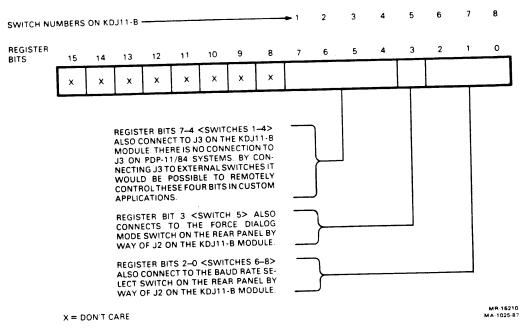

| Appendix C | Configuration Register Modification                           |             |

|------------|---------------------------------------------------------------|-------------|

| C.1        | Introduction                                                  | C-1         |

| C.2        | ROM Code Interpretation                                       | C-1         |

| Appendix D | Floating-Point Instruction Timing                             |             |

| Appendix E | ROM Code Differences                                          |             |

| E.1        | General                                                       | E-1         |

| E.2        | V6.0 and V7.0 Differences                                     | E-1         |

| E.2.1      | Boot Support for Tape MSCP Devices (TK50/TU81)                | E-1         |

| E.2.2      | Disk MSCP Automatic Boot Routine                              | E-1         |

| E.2.3      | Dialog Mode Boot Command for Disk MSCP Boot                   | E-2         |

| E.2.4      | Disk MSCP Boot (DU)                                           | E-2         |

| E.2.5      | 8-Unit Restriction for MSCP Automatic Boot                    | E-2         |

| E.2.6      | Irregular Monitoring of Keyboard During Automatic Boot        |             |

| 1.2.0      | Sequence                                                      | E-3         |

| E.2.7      | Addition of Single-Letter Mnemonic in Automatic Boot List     | E-3         |

| E.2.8      | Setup Mode Disable                                            | E-3         |

| E.2.9      | Disable All Testing Parameter                                 | E-4         |

| E.2.10     | Edit/Create Command                                           | E-4         |

| E.2.11     | Initialize Command for the PMG Counter                        | E-4         |

| E.2.12     | PMG Parameter Warning                                         | E-5         |

| E.2.13     | Setup Command 4 Printout                                      | E-5         |

| E.2.14     | MU (TK50/TU81) Device                                         | E-5         |

| E.2.15     | Setup Command 5                                               | E-6         |

| E.2.16     | Memory Initialization at Power-Up                             | E-6         |

| E.2.17     | Power-Up Option Set to 3 with Battery Backed Up Memory        | E-6         |

| E.2.18     | Halt-on-Break                                                 | E-6         |

| E.2.19     | Local Language Support                                        | E-7         |

| E.2.20     | Addition of Map Command Feature                               | E-7         |

| E.2.21     | EEPROM Load Error Before Dialog Mode                          | <u>E</u> -7 |

| E.2.22     | Test Command Decimal Numbers                                  | E-7         |

| E.2.23     | Test Command Execution of a Single Test                       | E-8         |

| E.2.24     | Test Errors in Tests 72 to 75                                 | E-8         |

| E.2.25     | Bypass Errors for Test Failures                               | E-8         |

| E.2.26     | Test 76 and 75 Error Messages                                 | E-8         |

| E.2.27     | Starting Automatic Boot Sequence Message                      | E-8         |

| E.2.28     | Device Name and Number After Message                          | E-9         |

| E.2.29     | Incorrect Message for Invalid Unit Number                     | E-9         |

| E.2.30     | Dialog Mode Header Message                                    | E-9         |

| E.2.31     | Map Command Message                                           | E-9         |

| E.2.32     | List Device Descriptions                                      | E-9         |

| E.2.33     | Loss of the First Line in a List Header                       | E-10        |

| E.2.34     | CTRL R and CTRL U Echo                                        | E-10        |

| E.2.35     | Power-Up or Restart Mode Set to 3 (LSI Bus Only)              | E-10        |

| E.2.36     | Automatic Boot Misleading Error Message (LSI Bus Only)        | E-11        |

| E.2.37     | APT Halt-on-Break Detect (LSI Bus Only)                       | E-11        |

| E.2.38     | B Mnemonic for ROM Boots (UNIBUS Only)                        | E-11        |

| E.2.39     | Error in List Command When Unknown ROM is Found (UNIBUS Only) | E-11        |

| E.2.40     | Power-Up or Restart Mode Set to 3 (UNIBUS Only)               | E-11        |

| E.2.41     | Saving KMCR Bits <5:0> in the EEPROM (UNIBUS Only)            | E-12        |

| E.3             | V7.0 and V8.0 Differences                          | E-12 |

|-----------------|----------------------------------------------------|------|

| E.3.1           | M9312 MultiROM Bootstrap Support (PDP-11/84 Only)  | E-12 |

| E.3.2           | RAnn Disk Spinup Time Delay for Automatic Boot     | E-12 |

| E.3.3           | Addition of RESET Instruction at Beginning of Code | E-13 |

| E.3.4           | Addition of New Setup Command 5                    | E-13 |

| E.3.5           | Memory Test Coverage Problem                       | E-13 |

| E.3.6           | List Command Device Descriptions                   | E-14 |

| E.3.7           | Manufacturing Test Loop Problem                    | E-14 |

| <b>Appendix</b> |                                                    |      |

| F.1             | Introduction                                       | F-1  |

| F.2             | Transfer Control Program                           | F-1  |

| F.3             | EEPROM Load Example                                | F-2  |

|                 | · •                                                |      |

| Examples        |                                                    |      |

| 3–1             | Ambamatia Daul Mada                                |      |

| 3-1<br>3-2      | Automatic Boot Mode                                | 3-2  |

| 3-2<br>3-3      | System Power-Up in Dialog Mode                     | 3-3  |

|                 | Dialog Mode Commands                               | 3-3  |

| 3-4             | Ctrl U Executed                                    | 3-4  |

| 3–5             | Ctrl R Executed                                    | 3-4  |

| 3–6             | Ctrl U Equivalent                                  | 3-4  |

| 3-7             | Invalid Entry                                      | 3-5  |

| 3–8             | Help Command Display                               | 3-5  |

| 3–9             | DL2 BOOT                                           | 3-8  |

| 3–10            | List Command                                       | 3-9  |

| 3–11            | Map Command                                        | 3-10 |

| 3–12            | Test Command                                       | 3-11 |

| 3–13            | Loop-On-Test                                       | 3-11 |

| 3-14            | Setup Mode Command Descriptions                    | 3-12 |

| 3–15            | Short Command Message                              | 3-13 |

| 3-16            | Setup Command 2                                    | 3-14 |

| 3–17            | Setup Command 3                                    | 3-19 |

| 3–18            | Two-Entry Translation Table                        | 3-21 |

| 3–19            | Unit Number Translation                            | 3-21 |

| 3-20            | Setup Command 4                                    | 3-22 |

| 3–21            | Setup Command 6                                    | 3-24 |

| 3–22            | Setup Command 8                                    | 3-25 |

| 3–23            | Setup Command 9                                    | 3-26 |

| 3-24            | Setup Command 10                                   | 3-26 |

| 3–25            | Setup Command 11                                   | 3-27 |

| 3-26            | Setup Command 12                                   | 3-27 |

| 3-27            | Setup Command 13                                   | 3-28 |

| 3-28            | Setup Command 14                                   | 3-29 |

| 3-29            | Setup Command 14 with No Changes                   | 3-29 |

| 3-30            | Setup Command 15                                   | 3-30 |

| E-1             | Program for Continuous Loop                        | E-4  |

| E-2             | Single-Letter Description for Command 4            | E-5  |

| E 2             | Automatic Root Coguence Massace                    | EO   |

|      | T 4  | V6.0 Incorrect Message                            | E-9          |

|------|------|---------------------------------------------------|--------------|

|      | E-4  | V7.0 Correct Error Message                        | E-9          |

|      | E-5  | V6.0 List Header Error                            | E-10         |

|      | E-6  | V7.0 Correct List Header                          | E-10         |

|      | E-7  | EEPROM Load                                       | F-2          |

|      | F-1  | EEPROM LOAD                                       |              |

| Figu | res  |                                                   |              |

|      | 1-1  | PDP-11/84 System Block Diagram                    | 1-1          |

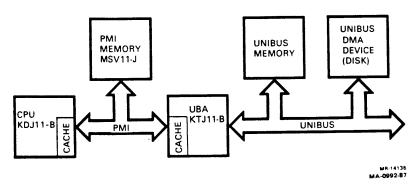

|      | 2-1  | PDP-11/84 Functional Block Diagram                | 2-1          |

|      | 2-2  | Page Address Register Format                      | 2-19         |

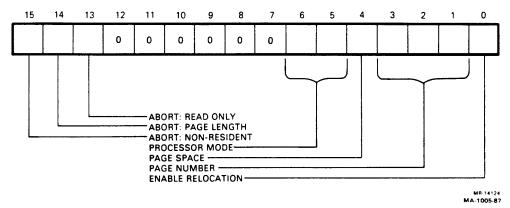

|      | 2-3  | Page Descriptor Register Format                   | 2-19         |

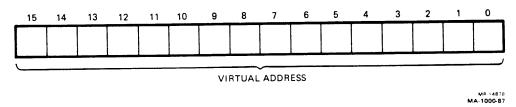

|      | 2-4  | Memory Management Register 0 Format               | 2-21         |

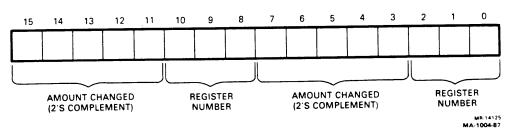

|      | 2-5  | Memory Management Register 1 Format               | 2-22         |

|      | 2-6  | Memory Management Register 2 Format               | 2-22         |

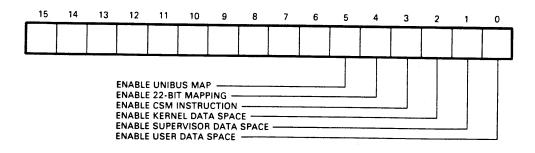

|      | 2-7  | Memory Management Register 3 Format               | 2-23         |

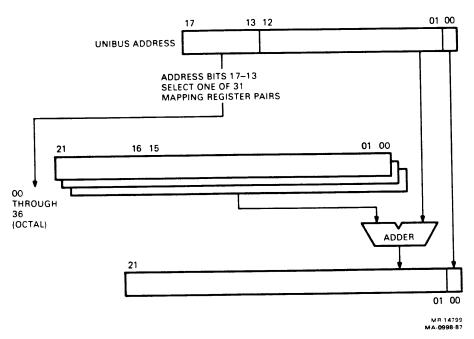

|      | 2-8  | Physical Address Interpretation                   | 2-24         |

|      | 2-9  | Cache Response Matrix                             | 2-25         |

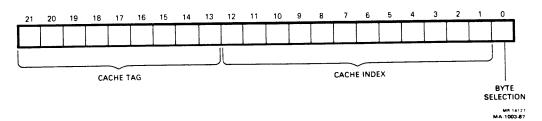

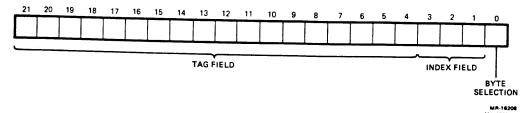

|      | 2-10 | CPU/DMA Physical Address Interpretation Register  | 2-26         |

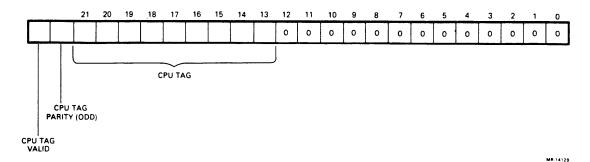

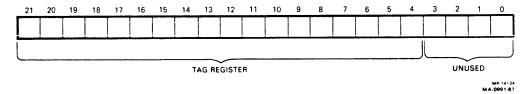

|      | 2-11 | CPU Cache Tag Register Format                     | 2-27         |

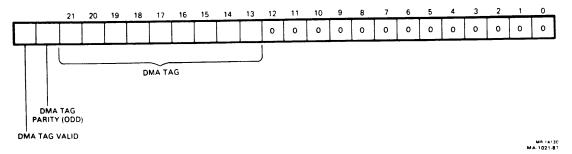

|      | 2-12 | DMA Tag Register Format                           | 2-28         |

|      | 2-13 | CPU Cache Data Organization                       | 2-28         |

|      | 2-14 | Cache Control Register Format                     | 2-29         |

|      | 2-15 | Memory System Error Register Format               | 2-31         |

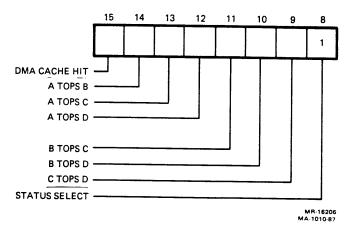

|      | 2-16 | Hit/Miss Register Format                          | 2-33         |

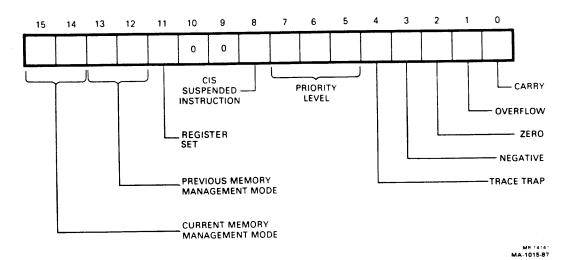

|      | 2-17 | Processor Status Word Register                    | 2-34         |

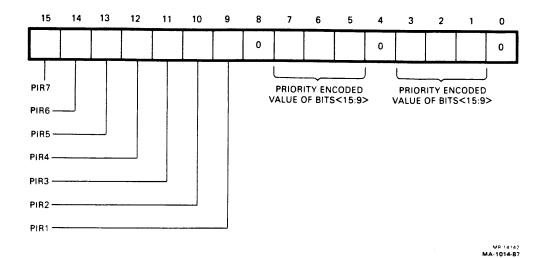

|      | 2-18 | Program Interrupt Request Register                | 2-35         |

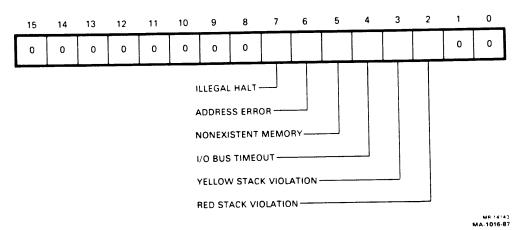

|      | 2-19 | CPU Error Register Format                         | 2-36         |

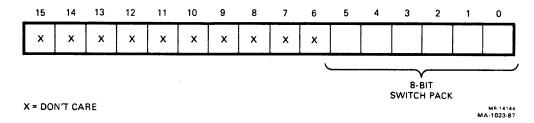

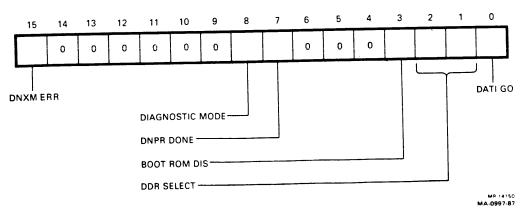

|      | 2-20 | Boot and Diagnostic Configuration Register Format | 2-37<br>2-37 |

|      | 2-21 | Display Register                                  |              |

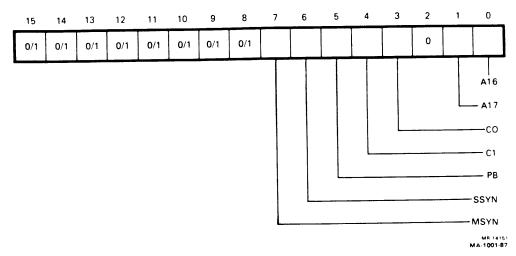

|      | 2-22 | Maintenance Register Format                       | 2-38         |

|      | 2-23 | Boot and Diagnostic Controller Register Format    | 2-40         |

|      | 2-24 | Page Control Register Format                      | 2-42         |

|      | 2-25 | Clock Status Register Format                      | 2-43         |

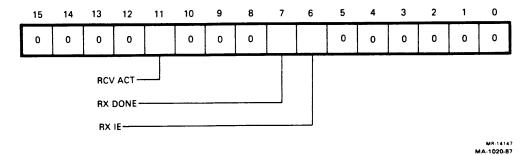

|      | 2-26 | Receiver Status Register Format                   | - 40         |

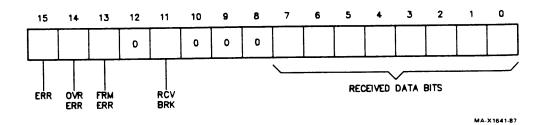

|      | 2-27 | Received Data Buffer Register Format              | 2-48<br>2-49 |

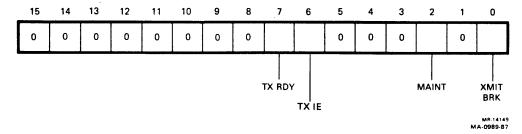

|      | 2-28 | Transmitter Status Register Format                |              |

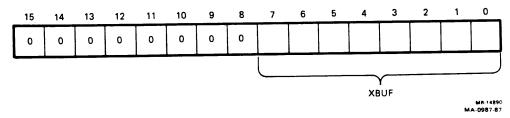

|      | 2-29 | Transmitter Data Buffer Register Format           | 2-30         |

|      | 2-30 | Valid Bit and Tag Register Format (One of Four)   |              |

|      | 2-31 | Physical Address Interpretation                   |              |

|      | 2-32 | PDP-11/84 Cache Diagram                           | 2-34         |

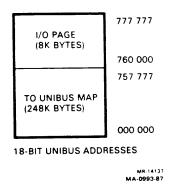

|      | 2-33 | UNIBUS Address Space                              |              |

|      | 2-34 | High-Address Register Format                      | . 2-30       |

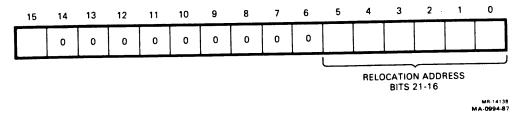

|      | 2-35 | Low-Address Register Format                       | . 2-57       |

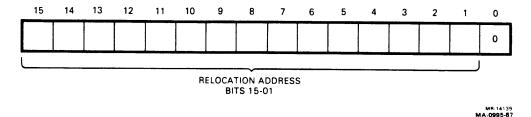

|      | 2-36 | Memory Configuration Register (KMCR)              | . 2-02       |

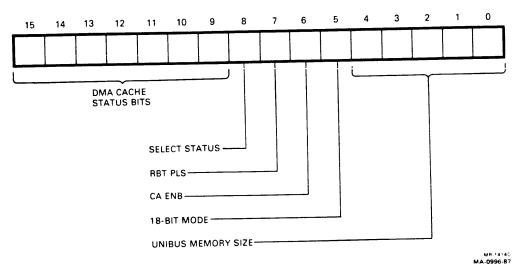

|      | 2-37 | Status Select = 0 Field Format                    | . 2-03       |

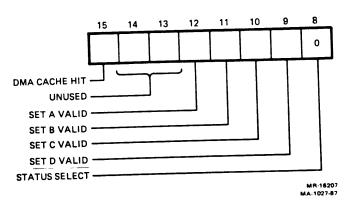

|      | 2-38 | Status Select = 1 Field Format                    |              |

|      | 2-39 | Diagnostic Controller Status Register Format      |              |

|      | 2-40 |                                                   | . 4-07       |

| 3.     | 1 EEPROM Layout 3-3                             | 35 |

|--------|-------------------------------------------------|----|

| В      |                                                 |    |

| C      |                                                 |    |

|        |                                                 |    |

| Tables |                                                 |    |

| 1-     | Related Documents                               | -3 |

| 2-     |                                                 |    |

| 2-     |                                                 |    |

| 2-     |                                                 |    |

| 2-     |                                                 | 23 |

| 2-     |                                                 | 27 |

| 2-     |                                                 | 29 |

| 2-     |                                                 | 30 |

| 2-     |                                                 | 30 |

| 2-     |                                                 | 31 |

| 2-     | 10 Hit/Miss Register Bit Descriptions 2-3       | 3  |

| 2-     | Processor Status Word Bit Descriptions          | 34 |

| 2-     | Program Interrupt Register Bit Descriptions 2-3 | 35 |

| 2-     |                                                 | 36 |

| 2-     |                                                 | 38 |

| 2-     | 0 1                                             | 19 |

| 2-     | 0 I I I I I I I I I I I I I I I I I I I         | 10 |

|        | Page Control Register Bit Descriptions 2-4      | 13 |

| 2-     | 0                                               | 4  |

| 2-     | 6 · · · · · · · · · · · · · · · · · · ·         | 17 |

| 2-     | 1                                               | 8  |

| 2-     |                                                 | 19 |

| 2-     |                                                 | 60 |

| 2-     |                                                 | 51 |

| 2-     | 0                                               |    |

| 2-     |                                                 |    |

| 2-     | 1 0                                             |    |

| 2-     |                                                 |    |

| 2-     | j b                                             |    |

| 2-     |                                                 |    |

| 2-     |                                                 |    |

| 2-     | 0                                               |    |

| 2-     | 6                                               |    |

| 3-     | •                                               |    |

| 3-     |                                                 |    |

| 3-     | •                                               |    |

| 3-     | -Jr                                             |    |

| 3-     | <b>6</b>                                        |    |

| 3-     |                                                 |    |

| 3-     | 8                                               |    |

| 3-     |                                                 |    |

| Α      | 0 1                                             |    |

| Α      | 2 Double Operand Instructions                   | .4 |

| \_3         | Branch Instructions                                      | A-5        |

|-------------|----------------------------------------------------------|------------|

|             | Jump and Subroutine                                      | A-6        |

| \_4         | Trap and Interrupt Instructions                          | A-7        |

| A-5         | Condition Code Operators                                 | A-7        |

| A-6         | Miscellaneous Instructions                               | A-8        |

| <b>1</b> -7 | Floating-Point Instructions                              | A-9        |

| A-8         | Source Address Times: All Double Operand                 | A-11       |

| <b>A</b> -9 | Destination Address: Read-Only Single Operand            | A-12       |

| A-10        | Destination Address: Read-Only Single Operand            | A-12       |

| 4-11        | Destination Address Times: Write-Only                    | A-13       |

| A-12        | Destination Address Times: Write-Only                    | A-13       |

| A-13        | Destination Address Times: Read Modify Write             | A-14       |

| A-14        | Destination Address Times: JMP                           | A-14       |

| A-15        | Destination Address Times: JSR                           | A-15       |

| A-16        | Floating Source 1-7                                      | A-16       |

| A-17        | Floating Destination Modes 1-7                           | A-17       |

| A-18        | Floating Read-Modify-Write Modes 1-7                     | A-17       |

| A-19        | Integer Source Modes 1-7                                 | A-19       |

| A-20        | Integer Destination Modes 1-7                            | B-3        |

| B-1         | Hardware Differences Between the PDP-11/84 and PDP-11/44 | B-5<br>B-5 |

| B-2         | Hardware Differences Between the PDP-11/84 and PDP-11/70 |            |

| B-3         | Programming Difference for PDP-11 Family Processors      | B-7        |

| C-1         | Rand Rate Selection                                      | C-4        |

| C-2         | KDI11-B Switch Selection $(1 = OFF, 0 = ON)$             | C-4        |

| D-1         | Address Calculation Times                                | D-3        |

| D-2         | FPI11 Instruction Times                                  | D-4        |

| E-1         | ROM Part Numbers                                         | E-1        |

| E-2         | Setup Command 4 Automatic Boot Lists                     | E-6        |

| E-3         | ROM Code Test Selections                                 | E-7        |

| E-4         | New List Command Device Descriptions                     | E-14       |

# **About This Manual**

This manual provides a detailed functional description of the standard PDP-11/84 system.

The manual consists of the following chapters and appendices.

Chapter 1, System Overview – Includes a general description of the PDP-11/84 system and its components and a list of related documents.

**Chapter 2, Functional Description** – Describes each of the major logic elements of the PDP-11/84 system.

Chapter 3, Bootstrap and Diagnostic ROM Programming - Describes the commands for the ROM and EEPROM codes.

**Appendix A, CPU Instruction Timing** – Describes the method of calculating the execution time for CPU instructions.

**Appendix B, Hardware/Software Differences** – Describes the differences between the UNIBUS power-up protocol for the PDP-11/84 and other PDP-11 systems.

Appendix C, Configuration Register Modification – Describes the format of the boot and diagnostic configuration register (BCR).

Appendix D, Floating-Point Instruction Timing - Contains information necessary to calculate the floating-point instruction timing.

**Appendix E, ROM Code Differences** – Explains the differences between versions 6.0, 7.0, and 8.0 of the ROM code used in the KDJ11-BF CPU module.

Appendix F, Multiboot ROM Control Transfer - Describes the program used to transfer control to any UBA ROM or M9312 ROM boot.

#### **Conventions Used in This Manual**

Warnings, cautions, and notes appear throughout this guide. They serve the following functions.

Warning Provides information to prevent personal injury.

Caution Provides information to prevent damage to equipment or software.

Note Provides general information about the current topic.

Other conventions used in this manual are as follows.

- Bits are usually shown in angle brackets. Two numbers separated by a colon indicate a set of bits, or bit field. For example, <15:08> stands for bits 15 through 8.

- Keyboard function keys are enclosed in a box. For example, the carriage return key is specified as Return.

- In the examples of screen display, the text the user enters is in bold type.

Some functions may be labeled differently on different keyboards. See the user's manual for your terminal if you have a question.

# 1

# **System Overview**

# 1.1 Introduction

The PDP-11/84 system is a high performance computer containing a J-11 microprocessor with a floating-point processor. The CPU executes the PDP-11 instruction set. The system operates on Digital Equipment Corporation's 18-bit UNIBUS with a 22-bit memory addressing capability.

# 1.2 System Components

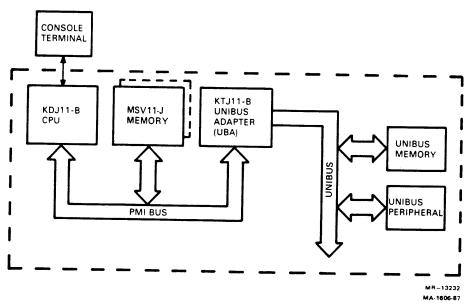

Figure 1-1 shows the system block diagram. The kernel system consists of:

- KDJ11-BF CPU module

- One MSV11-JD 1 Mbyte ECC memory module, one MSV11-JE 2 Mbyte ECC memory module, or two MSV11-JE 2 Mbyte ECC memory modules

- KTJ11-B UNIBUS adapter (UBA) module

Figure 1-1 PDP-11/84 System Block Diagram

The modules communicate through the high-speed private memory interconnect (PMI) bus using 22-bit address and 16-bit data lines.

A console serial line unit supporting the EIA RS232 communication standard allows you to connect a console terminal to the KDJ11-BF CPU module.

The KTJ11-B UBA module interfaces to the PMI bus and the UNIBUS. The UBA module supports all address and data communications between the processor memory and all UNIBUS peripherals. In addition, the UBA module serves as a terminator for the CPU end of the UNIBUS.

#### 1.2.1 KDJ11-BF CPU Module

The KDJ11-BF (M8190-AE) is a quad CPU module with the complete functionality of a PDP-11 processor. The KTJ11-B UNIBUS adapter module allows the CPU to interface with Digital's UNIBUS.

The module features a J-11 microprocessor, a floating-point processor, 22-bit memory management, an 8 Kbyte cache memory, a programmable line frequency clock, a console serial line unit, a configuration electrically erasable programmable read only memory (EEPROM), and boot and diagnostic ROMs.

In addition, the KDJ11-BF has six red LED indicators for displaying diagnostic information during power-up and bootstrapping. A single green LED indicates dc power to the module.

# 1.2.2 KTJ11-B UNIBUS Adapter Module

The KTJ11-B UNIBUS adapter (M8191) is a hex module that interfaces with the KDJ11-BF processor and memory through the PMI. The module contains the PMI adapter logic, UNIBUS mapping, four M9312 compatible boot ROM sockets, and a DMA cache.

# 1.2.3 MSV11-JD/JE Memory Module

The quad memory module is available in two versions:

- MSV11-JD (M8637-DA) with a 1 Mbyte capacity

- MSV11-JE (M8637-EA) with a 2 Mbyte capacity

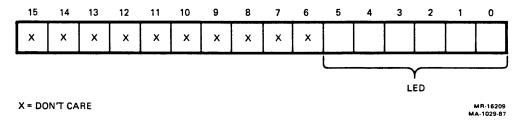

The modules provide error correcting code (ECC) and support write byte/word, double word read, and block mode read operations over the PMI bus. A red LED indicates the occurrence of an uncorrectable error. A green LED indicates the presence of +5.1 VB power.

### 1.3 Related Documents

Table 1-1 lists some documents that contain information related to the PDP-11/84 or its operating systems.

Table 1-1 Related Documents

| Title                                    | Order Number |  |

|------------------------------------------|--------------|--|

| PDP-11/84-D User's and Maintenance Guide | EK-1184D-UG  |  |

| PDP-11/84-E User's and Maintenance Guide | EK-1184E-UG  |  |

| PDP-11/84-D Field Maintenance Print Set  | MP-02536-01  |  |

| PDP-11/84-E Field Maintenance Print Set  | MP-01955-01  |  |

| PDP-11/84-D Illustrated Parts Breakdown  | EK-1184D-IP  |  |

| PDP-11/84-E Illustrated Parts Breakdown  | EK-1184E-IP  |  |

| PDP-11 UNIBUS Processor Handbook         | EB-26077-41  |  |

| PDP-11 Architecture Handbook             | EB-23657-18  |  |

| KDJ11-B CPU User Guide                   | EK-KDJ1B-UG  |  |

| MSV11-J Memory User Guide                | EK-MSV1J-UG  |  |

| DCJ11 Microprocessor User Guide          | EK-DCJ11-UG  |  |

| Supermicrosystems Handbook               | EB-27713-41  |  |

| Chipkit Handbook                         | EK-01387-92  |  |

| Communications Handbook                  | EB-30066-42  |  |

| Terminals and Printers Handbook          | EB-23909-54  |  |

| PDP-11 Software Handbook                 | EB-25398-41  |  |

| RSX-11 Handbook                          | EB-25742-41  |  |

| RSTS/E Handbook                          | EJ-23534-18  |  |

| ULTRIX Software Guidebook                | EJ-26153-20  |  |

### 1.3.1 Digital Personnel Ordering Information

Additional copies of this document and printed copies of the documents listed may be obtained from:

Digital Equipment Corporation 10 Forbes Road Northboro, MA 01532

ATTN: Printing and Circulation Services (NRO3/A5)

**Customer Services**

# 1.3.2 Customer Ordering Information

Purchase orders for supplies and accessories should be sent to:

Digital Equipment Corporation P.O. Box CS2008 Nashua, NH 03061

# **Functional Description**

#### 2.1 Introduction

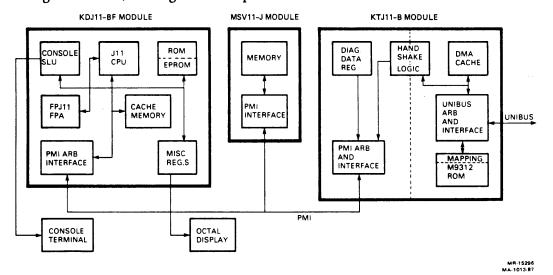

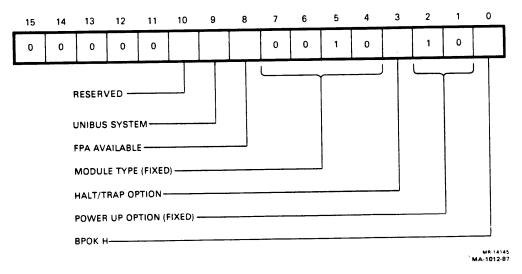

The PDP-11/84 functional block diagram is shown in Figure 2-1. The three modules are the KDJ11-BF CPU, MSV11-JD/JE ECC memory, and KTJ11-B UNIBUS adapter (UBA). The KDJ11-BF module has a J-11 microprocessor with an integral floating-point processor, an 8 Kbyte cache memory, private memory interconnect (PMI) arbitration logic, memory management registers, EEPROM/ROM, configuration registers, a serial line unit (SLU), six red diagnostic LEDs, and a green +5 V power LED.

Figure 2-1 PDP-11/84 Functional Block Diagram

The KTJ11-B UNIBUS adapter module is divided into a PMI section and a UNIBUS section. The handshake logic enables data transfers to occur between PMI and UNIBUS devices. The PMI section has diagnostic registers and PMI arbitration/interface logic. The UNIBUS section has a 32-word DMA cache, UNIBUS mapping logic, sockets for M9312-type user ROMs, and UNIBUS arbitration and interface logic.

The MSV11-JD memory module has a 1 Mbyte capacity, while the MSV11-JE has a 2 Mbyte capacity. A maximum of two memory modules are allowed in the system configuration.

The modules transfer data using the PMI. Data transfers between the PMI and UNIBUS devices use the handshaking logic on the KTJ11-B module. PMI read operations (DATI, DATIP, and DATBI) can be word or block mode. PMI write operations (DATO, DATOB) can be word or byte mode.

#### NOTE

The PDP-11/84 UNIBUS power-up protocol is slightly different from most PDP-11 systems. See Appendix B for a protocol description.

All communications between UNIBUS devices and the UBA occur through standard UNIBUS protocol. No Q-bus devices may be configured on the system.

# 2.2 PMI Bus Description

The PMI bus provides a high-performance communication path between the KDJ11-BF CPU, the MSV11-JD/JE memory, and the KTJ11-B UBA. The PMI consists of 14 signals that are unique to PMI protocol. The signal lines are described in Table 2–1.

The KDJ11-BF CPU module is also used in systems that contain Q-bus devices. Some of the signals, therefore, retain their Q-bus names. The functionality of these signals changes, however, when a KTJ11-B UBA is part of the system. Data and address information is multiplexed and uses the same data/address lines as Q-bus protocol.

Table 2-1 PMI Signal Line Descriptions

| Signal Line  | Description                                                                                                                                                                                                                                                                                |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BDAL <21:00> | 22 Multiplexed Bidirectional Data/Address Lines.                                                                                                                                                                                                                                           |  |  |

|              | During the address phase of a data transfer cycle, the PMI master gates address information onto these lines. During the data phase of the cycle, the slave (DATI) or the master (DATO) gates data onto BDAL <15:00 > and parity error/control information onto BDAL <17:16 >.             |  |  |

| BBS7         | Bank 7 Select (I/O Page Select).                                                                                                                                                                                                                                                           |  |  |

|              | When the PMI master gates an address onto BDAL <21:00>, it asserts BBS7 to reference the I/O page (including the I/O page addresses reserved a nonexistent memory). When BBS7 is asserted, BDAL <12:00> specifies the I/O page address; Negation of BBS7 selects the memory address space. |  |  |

| BRPLY        | Reply                                                                                                                                                                                                                                                                                      |  |  |

|              | This signal is asserted by the UBA as a slave response during the PMI DATO(B) cycle and during the interrupt vector DATI cycle.                                                                                                                                                            |  |  |

| BDIN         | Data Input                                                                                                                                                                                                                                                                                 |  |  |

|              | This signal is used by PMI protocol during UNIBUS interrupt grant cycles. The CPU asserts BDIN after gating the interrupt priority onto BDAL $< 03$ : $00>$ . The UBA latches the interrupt priority on the leading edge of BDIN.                                                          |  |  |

| BIACKI       | Interrupt Acknowledge                                                                                                                                                                                                                                                                      |  |  |

Table 2-1 (Cont.) PMI Signal Line Descriptions

| Signal Line             | Descripti                                                                                                                                                                                                                                                                                                                                                                                                                                   | on                        |                                                                                                                                                            |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                         | When the                                                                                                                                                                                                                                                                                                                                                                                                                                    | UBA recei                 | y PMI protocol during UNIBUS interrupt grant cycles. ves the assertion of BIACK (from the CPU), it asserts grant (BGn) signals.                            |  |

| врок                    | Power OK                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                                                                                                                                                            |  |

|                         | the UNIBL                                                                                                                                                                                                                                                                                                                                                                                                                                   | JS followii<br>evices and | d and negated by the UBA in response to AC LO on ng standard UNIBUS power-up/power-down protocol.  I/or PMI memory may, during power-up, prolong the BPOK. |  |

| The following signals a | re asserted (                                                                                                                                                                                                                                                                                                                                                                                                                               | low) and i                | negated (high) by the PMI master:                                                                                                                          |  |

| PBCYC                   | PMI Bus C                                                                                                                                                                                                                                                                                                                                                                                                                                   | ycle                      |                                                                                                                                                            |  |

|                         | The PMI m                                                                                                                                                                                                                                                                                                                                                                                                                                   | naster asse<br>at the end | rts this signal at the start of a PMI cycle and negates of that cycle.                                                                                     |  |

| PBYT BWTBT              | PMI Byte a                                                                                                                                                                                                                                                                                                                                                                                                                                  | nd Write                  | Indication                                                                                                                                                 |  |

|                         | When the PMI master gates an address onto BDAL <21:00>, it asserts or negates these signals to indicate what type of data transfer will occur during the next bus cycle:                                                                                                                                                                                                                                                                    |                           |                                                                                                                                                            |  |

|                         | вштвт                                                                                                                                                                                                                                                                                                                                                                                                                                       | PBYT                      | Bus Cycle Type                                                                                                                                             |  |

|                         | Н                                                                                                                                                                                                                                                                                                                                                                                                                                           | Н                         | DATI or DATBI                                                                                                                                              |  |

|                         | Н                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                         | DATIP                                                                                                                                                      |  |

|                         | L                                                                                                                                                                                                                                                                                                                                                                                                                                           | Н                         | DATO                                                                                                                                                       |  |

|                         | L                                                                                                                                                                                                                                                                                                                                                                                                                                           | L                         | DATOB                                                                                                                                                      |  |

| PBLKM                   | PMI Block                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mode                      |                                                                                                                                                            |  |

|                         | When a PMI master wants to read more than two words of data, it uses both PBCYC and PBLKM to control the timing of the block mode data in (DATBI) cycle. It asserts both PBCYC and PBLKM at the start of the DATBI cycle. It negates PBLKM after reading two data words and then reasserts PBLKM (unless the next two words will end the cycle). After reading the last two words, the PMI master negates PBCYC (PBLKM is already negated). |                           |                                                                                                                                                            |  |

| PWTSTB                  | PMI Write                                                                                                                                                                                                                                                                                                                                                                                                                                   | Strobe                    |                                                                                                                                                            |  |

|                         | The PMI m<br>The PMI slathe<br>the PWTST                                                                                                                                                                                                                                                                                                                                                                                                    | ave latche:               | rts this signal after gating data onto BDAL <15:00>. s the data into its write buffer on the leading edge of                                               |  |

| QSACK                   | The UBA asserts this signal on the PMI in response to SACK from the UNIBUS.                                                                                                                                                                                                                                                                                                                                                                 |                           |                                                                                                                                                            |  |

| DMR                     | The UBA asserts this signal on the PMI in response to NPR from the UNIBUS or when the UBA is performing a DMA cycle in its own behalf.                                                                                                                                                                                                                                                                                                      |                           |                                                                                                                                                            |  |

Table 2-1 (Cont.) PMI Signal Line Descriptions

| Signal Line        | Description                                                                                                                                                                                                                                                                                    |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DMG                | The CPU asserts this signal when PMI master status has been granted to the UBA in response to a DMG.                                                                                                                                                                                           |  |  |

| QBR7-4             | The UBA asserts one of these signals in response to one of the BR7-4 lines being asserted on the UNIBUS during interrupt request cycles.                                                                                                                                                       |  |  |

| The following sign | nals are asserted and negated by the PMI slave:                                                                                                                                                                                                                                                |  |  |

| PSSEL              | PMI Slave Selected                                                                                                                                                                                                                                                                             |  |  |

|                    | The PMI slave (CPU or memory only) asserts this signal whenever it decodes a valid address on BDAL $<21:00>$ .                                                                                                                                                                                 |  |  |

|                    | NOTE When PUBMEM is asserted, the PMI slave does not respond to PMI control signals. PUBMEM is asserted by the UBA to indicate that UNIBUS memory space is being addressed. The UBA does not assert PSSEL. The CPU ignores the assertion of PSSEL if PUBMEM is asserted.                       |  |  |

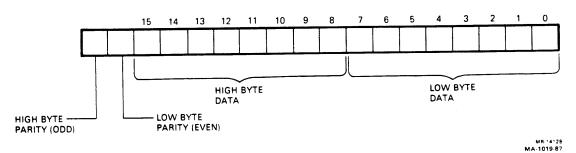

| PHBPAR             | PMI High Byte Data Parity                                                                                                                                                                                                                                                                      |  |  |

|                    | This signal is generated by PMI memory during DATI and DATBI cycles an provides odd parity for the high byte data (on BDAL <15:08>).                                                                                                                                                           |  |  |

| PLBPAR             | PMI Low Byte Data Parity                                                                                                                                                                                                                                                                       |  |  |

|                    | This signal is generated by PMI memory during DATI and DATBI cycles are provides even parity for the low byte data (on BDAL <07:00>).                                                                                                                                                          |  |  |

| PRDSTB             | PMI Read Strobe                                                                                                                                                                                                                                                                                |  |  |

|                    | The PMI slave asserts and negates this line to control data transfers during DATI and DATBI cycles. The PMI master latches the first word of the received data on the negating edge of this signal. The PMI master latches the second data word a specified time after this signal is negated. |  |  |

| PSBFUL             | PMI Slave Buffer Full                                                                                                                                                                                                                                                                          |  |  |

|                    | A PMI slave asserts PSBFUL during a write cycle, indicating that its write buffer is full and that it cannot respond to another cycle request. The ne PMI master may gate an address onto BDAL <21:00> while PSBFUL is asserted, but it must not assert PBCYC until PSBFUL is negated.         |  |  |

|                    | CDII and the INIBIIS adapter P                                                                                                                                                                                                                                                                 |  |  |

The following signals are used for communication between the CPU and the UNIBUS adapter. PMI memory modules do not use these signals.

PMAPE PMI UNIBUS Map Enable

The CPU module asserts this signal if memory management register 3 (MMR3) bit <5> is set and negates this signal if MMR <05> is clear. The UBA module enables the UNIBUS map if PMAPE is asserted and disables the UNIBUS map if PMAPE is negated.

Table 2-1 (Cont.) PMI Signal Line Descriptions

| Signal Line | Description                                                                                                                                                                                                                       |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUBSYS      | PMI UNIBUS System                                                                                                                                                                                                                 |

|             | This signal is a static signal that indicates whether the system is a UNIBUS system or a Q-bus system and is asserted by the UBA. The CPU follows PMI protocol for data transfers whether PSSEL is asserted or not.               |

| PUBMEM      | PMI UNIBUS Memory                                                                                                                                                                                                                 |

|             | This signal line is asserted by the UBA to indicate that the UNIBUS memory space is being addressed. The UBA asserts PUBMEM during the assertion of PBCYC.                                                                        |

|             | NOTE When PUBMEM is asserted, the PMI slave does not respond to PMI control signals. PSSEL is asserted by PMI memory when addressed. The CPU ignores the assertion of PSSEL if PUBMEM is asserted. The UBA does not assert PSSEL. |

| PUBTMO      | PMI UNIBUS Timeout                                                                                                                                                                                                                |

|             | This signal is asserted by the UBA in response to any of the following conditions:                                                                                                                                                |

|             | <ul> <li>A nonexistent memory timeout occurs when the UBA sends an address<br/>out on the UNIBUS.</li> </ul>                                                                                                                      |

| -           | <ul> <li>A SACK timeout occurs during an interrupt cycle.</li> </ul>                                                                                                                                                              |

|             | <ul> <li>An interrupting UNIBUS device has been granted UNIBUS master<br/>status but does not execute an interrupt transaction.</li> </ul>                                                                                        |

| PBSY        | PMI Busy                                                                                                                                                                                                                          |

|             | This signal is asserted by the PMI master (CPU or UBA) when it gains PMI master status and is negated by the PMI master when it relinquishes PMI master status. The CPU is the PMI master on power-up.                            |

### 2.2.1 PMI Bus Acquisition

In the PDP-11/84 system, the CPU is the default PMI bus master; the UBA is the default UNIBUS master. This is always the condition at power-up. When the UBA is not requesting the PMI bus, the CPU arbitrates to become PMI master and holds PBUSY asserted.

Unlike previous PDP-11 systems, when no device on the UNIBUS is requesting use of the bus, the UBA arbitrates to become UNIBUS master and holds BBSY asserted.

The CPU relinquishes PMI master status when responding to a DMA request or an interrupt cycle from the UBA. Once the CPU has relinquished control of the PMI, it can regain PMI master status only when the following conditions are met.

- QSACK has been negated for 75 ns minimum.

- PBSY has been negated for 0 ns minimum.

When the CPU, as PMI master, references a memory or I/O page address on the UNIBUS, the UBA responds as the slave on the PMI. The UBA continues to control the UNIBUS side of the data transfer as bus master.

The UBA becomes PMI master when the CPU issues a DMA grant (DMG) or performs an interrupt cycle. The UBA may accept the DMG or interrupt grant, thus becoming both PMI and UNIBUS master at the same time. Alternatively, the UBA may pass the DMG or interrupt grant on to a requesting UNIBUS device, which would then become UNIBUS master.

Master status of the UNIBUS and/or PMI bus is requested as follows:

- A UNIBUS device can become UNIBUS master through an NPR request and control

data transfers over the UNIBUS. During these data transfers, the UBA is PMI master

and responds as UNIBUS slave if the UNIBUS device accesses a PMI memory

location, a PMI I/O page location, or a UBA I/O page location.

- A UNIBUS device can become UNIBUS master through a BR7-4 request. As UNIBUS master, the device can control data and/or interrupt vector transfers. In both cases the UBA will respond as UNIBUS slave. The device may perform an interrupt vector cycle or access a PMI memory location, a PMI I/O page location, or a UBA I/O page location.

- The UBA can become both PMI and UNIBUS master at the same time through DMG and interrupt requests. As PMI and UNIBUS master, the UBA has direct access to the PMI.

# 2.2.2 DMA Requests

Unlike previous PDP-11 system CPUs, the PDP-11/84 CPU does not necessarily give unconditional priority to DMA requests. It can be programmed (see Section 3.3 on setup mode) to give itself priority over DMA requests after waiting for this programmed length of time to perform a memory transfer or to honor an interrupt request.

Through an NPR request to the UBA, a UNIBUS DMA device can perform UNIBUS DATI, DATIP, DATO, and DATOB cycles. The UBA controls the PMI portion of the data transfer.

When placed in diagnostic test mode, the UBA can perform DMA transfers without a requesting UNIBUS device. In this case, the UBA itself is the requesting device. When the UBA performs a DMA cycle, it becomes master of the PMI and the UNIBUS simultaneously, and has complete control of the PMI.

The following PMI protocol flow is observed by the CPU and UBA when arbitrating a nonprocessor request from a UNIBUS device.

| PMI Bus | UNIBUS |  |

|---------|--------|--|

|         |        |  |

- 1. The UNIBUS device asserts NPR.

- If the UBA is UNIBUS master, it negates BBSY after removing address, data, and control information from the bus.

- 3. The UBA asserts DMA request (DMR) on the PMI bus.

- The CPU bus arbitration logic asserts DMG on the PMI after receiving DMR and 75 ns minimum after the negation of QSACK from a previous PMI bus transaction.

- 5. The UBA receives the assertion of DMG.

- 6. The UBA asserts nonprocessor grant (NPG).

- 7. The requesting device with the highest priority asserts SACK and negates nonprocessor request (NPR).

- 8. The UBA asserts QSACK on the PMI.

NOTE The UBA asserts PUBTMO instead of QSACK (indicating no SACK timeout) if SACK is not received within 10  $\mu$ s after it asserts BGn on the UNIBUS. The CPU then cancels the DMA cycle and resumes arbitration.

The CPU arbitration logic receives QSACK and negates DMG. PMI Bus UNIBUS

#### NOTE

Because the UBA provides the No SACK Timeout function on the PMI, the CPU always asserts DMG until it receives QSACK or UBTMO.

- 10. The UBA negates NPG on the UNIBUS.

- 11. The UBA asserts PBSY after receiving the negation of PBSY from the previous PMI cycle, and becomes PMI master.

- 12. After receiving the negation of BBSY from the previous bus master, the UNIBUS device asserts BBSY and negates SACK.

When a UNIBUS DMA device becomes UNIBUS master through an NPR request, it can perform UNIBUS DATI, DATIP, DATO, and DATOB cycles. If the device accesses a PMI memory location, a PMI I/O Page location, or a UNIBUS I/O page location, on the UBA, the UBA responds as the UNIBUS slave. For PMI memory and PMI I/O page accesses, the UBA—as the PMI master—controls the PMI portion of the data transfer.

Data transfer cycles are described in Section 2.2.5.

- 13. The UBA negates QSACK.

- 14. The CPU resumes arbitration 75 ns minimum after receiving the negation of QSACK.

- 15. The UNIBUS device removes address, data, and control information from the bus and negates BBUSY.

- After the PMI slave or the UBA has removed all data and control information from the bus, the UBA negates PBSY.

# 2.2.3 UNIBUS Device Interrupt Requests

The CPU and UBA observe the following protocol flow when arbitrating interrupt requests.

PMI Bus

**UNIBUS**

1. The UNIBUS device asserts the appropriate interrupt request line BR7-4.

- The CPU receives the appropriate request level on QBR7-4.

- 3. The CPU arbitration logic asserts one of the four lines, DAL <03:00>, to indicate the level of the granted interrupt.

- 4. The CPU asserts BDIN 150 ns minimum after gating DAL <03:00> onto the bus.

- The CPU asserts BIAK 225 ns minimum after it asserts BDIN.

- 6. The UBA latches DAL <03:00> on the asserting edge of BDIN.

- The CPU receives the assertion of IACK on the PMI.

#### **NOTE**

The UBA compares the interrupt level being granted with its own interrupt level and can block the grant. In this case, the UBA performs an interrupt or data transfer cycle and has complete control of the PMI and the UNIBUS simultaneously. In this case, the BGn line would not be asserted on the UNIBUS.

| PMI Bus | UNIBUS |

|---------|--------|

|         |        |

- 8. The UBA asserts the selected UNIBUS grant (BGn) line. DAL <03> = BG7, DAL <02> = BG6, etc.

- If the UBA was the UNIBUS master, it removes address, data, and control information from the bus and negates BBSY.

- The highest priority-requesting device receives the assertion of BGn and asserts SACK.

- 11. The device negates its BRn.

12. The UBA asserts QSACK.

#### NOTE

The UBA asserts PUBTMO (indicating No SACK Timeout) if SACK is not received on the UNIBUS within 10  $\mu$ s after it asserts BGn. When the CPU receives the assertion of PUBTMO, it cancels the interrupt cycle and resumes arbitration.

- 13. The UBA negates BGn.

- After receiving the negation of BBSY from the previous bus master, the UNIBUS device asserts BBSY and negates SACK.

- 15. After the UBA receives the negation of PBSY from the previous PMI cycle, the UBA asserts PBSY and negates QSACK.

- 16. The UBA now has control of the PMI bus and may initiate a PMI data transfer cycle(s) and/or an interrupt cycle.

#### NOTE

The CPU resumes NPR arbitration 75 ns after the negation of QSACK but does not resume BR arbitration until it has updated the PC and PSW to complete the interrupt cycle or has aborted the interrupt request.

#### PMI Bus UNIBUS

When a UNIBUS device becomes UNIBUS master through an interrupt request, it can perform interrupt vector cycles or UNIBUS DATI, DATIP, DATO, and DATOB cycles. If the device accesses a PMI memory location, a PMI I/O page location, or a UNIBUS I/O page location, the UBA responds as UNIBUS slave. For PMI memory and PMI I/O page accesses, the UBA, as the PMI master, controls the PMI portion of the data transfer. BDIN and BIACK being asserted does not effect the data transfer.

Data transfer cycles are described in Section 2.2.5.

The following sequence describes the interrupt transfer cycle:

- The interrupting device, as bus master, gates its vector onto the data lines and asserts INTR.

- 18. The UBA, as PMI master, asserts BRPLY on the PMI.

- 19. The UBA as slave receives the assertion of INTR and latches the interrupt vector.

- 20. The UBA asserts SSYN.

- 21. The UBA gates the vector onto the DAL lines.

- 22. The CPU latches the interrupt vector 200 ns minimum after receiving BRPLY.

- 23. The CPU negates BDIN and BIAK.

- 24. The UBA receives the negation of BIACK and negates BRPLY.

- After receiving SSYN, the device removes its vector from the data lines and negates INTR and BBSY.

26. The UBA negates PBSY.

# 2.2.4 PMI Data Transfer Address Cycle

The addressing phase of the PMI cycle starts immediately after the CPU or UBA has gained PMI master status and has asserted PBSY on the PMI.

#### **Functional Description**

The PMI bus acquisition phase is described in Section 2.2.1.

| PMI Master | PMI Slave |

|------------|-----------|

|            |           |

1. The address is gated out on BDAL <21:00>, and BS7 is asserted if the address is in the I/O page. The signal lines BWTBT and PBYT are asserted to indicate the cycle to be performed:

| BWTBT | PBYT | Bus Cycle Type |

|-------|------|----------------|

| Н     | Н    | DATI or DATB   |

| Н     | L    | DATIP          |

| L     | Н    | DATO           |

| L     | L    | DATOB          |

- 2. When a valid address is decoded by a slave, it responds as follows:

- The UBA asserts PUBMEM if the address is UNIBUS memory or UNIBUS I/O page.

- b. PMI memory and the CPU assert PSSEL.

- 3. PBCYC is asserted.

- 4. How the cycle proceeds is dependent on whether the CPU or UBA is master, and on what the response was from the slave as follows.

- a. When the CPU is PMI master:

If PSSEL is asserted and PUBMEM is negated, the CPU proceeds with a PMI memory cycle.

If PSSEL is negated, the CPU performs a PMI cycle with the UBA responding as the PMI slave.

b. When the UBA is PMI master:

If PSSEL is negated, then the UBA aborts the PMI cycle and does not respond as the UNIBUS slave.

#### 2.2.5 PMI Data Transfer Protocol

Following the data transfer address cycle, the data transfer cycle begins. The transfer of data on the PMI can be grouped into three general types of PMI data transfer cycles:

- The data in (DATI) and data in pause (DATIP) cycles. These are used to read one or two words.

- The block data in (DATBI) cycle. This is used to read up to 16 words.

- The data out (DATO) and data out byte (DATOB). These cycles are used to write a single word or byte.

The following sections describe each of the data transfer cycles.

## 2.2.6 PMI Data in Cycles (DATI and DATIP)

When accessing the PMI memory address space, a PMI master uses the DATI(P) cycle to read either one or two words of data. When accessing either I/O page or UNIBUS memory, a PMI master reads single words only.

The PMI DATIP cycle is identical to the DATI cycle with one exception: PBYT is asserted with the address to indicate that the next cycle (immediately following the current cycle) will be a DATO cycle to the same address.

The following flow is a description of a DATI(P) data transfer cycle.

| PMI Master | PMI Slave    |

|------------|--------------|

|            | 1 1111 01446 |

PBCYC is asserted during the addressing phase of the cycle (described in Section 2.2.4).

- 1. Data from the specified address is gated onto the bus.

- If the slave is PMI memory, PHBPAR and PLBPAR are generated and gated onto the bus.

#### NOTE

These parity bits are generated only for memory locations that are cached on the CPU (that is, PMI memory).

- 3. PRDSTB is asserted.

- 4. PRDSTB is negated.

| PMI Master | PMI Slave |

|------------|-----------|

|            |           |

5. The first data word, with PHBPAR and PLBAR, is latched on the negating edge of PRDSTB. If only one word is to be read, PBCYC is negated and the cycle ends. If two words are to be read, PBCYC remains asserted. If a read-modify-write (DATIP) is being performed, a DATO cycle will take place here. The DATO(B) cycle is described in Section 2.2.8.