# PDP-11 Systems Handbook

Featuring: MicroPDP-11/83 MicroPDP-11/73 MicroPDP-11/53 PDP-11/84

Digital Equipment Corporation makes no representation that the interconnection of its products in the manner described herein will not infringe on existing or future patent rights, nor do the descriptions contained herein imply the granting of license to make, use, or sell equipment constructed in accordance with this description.

Digital believes the information in this publication is accurate as of its publication date; such information is subject to change without notice. Digital is not responsible for any inadvertent errors. The following are trademarks of Digital Equipment Corporation: All-IN-1, COMPACTape, Correspondent, CTS-300, DATATRIEVE, DATATRIEVE-11, DDCMP, DEC, DECdataway, DECform, DECgraph, DECmail-11, DECmailer, DECmate, DECmate II, DECmate III, DECnet, DECnet/E, DECservice, DECUS, DELNI, DIBOL-83, the Digital logo, DMS-300, FMS, FMS-11, IAS, Internet, J-11, LA100, LA12, LA120, LA210, LA50, Letterprinter, Letterwriter, LN03, LQP03, MASSBUS, MicroPDP-11, MicroPower/Pascal, MicroPower/Pascal-RSX, MicroPower/Pascal-VMS, Micro/RSTS, Micro/RSX, MicroVAX, MicroVMS, Packetnet, PDP-11, P/OS, Professional, Q-bus, Rainbow, ReGIS, RSTS, RSTS/E, RSX-11M, RSX-11M-PLUS, RSX-11S, RT-11, RTEM-11, ULTRIX, ULTRIX-11, ULTRIX-32m, UNIBUS, VAX, VAX/VMS, VTX, VMS, VT100, VT200, VT240, VT241, VT52, and WPS-8.

Ada is a registered trademark of the United States government.

Apple is a trademark of Apple Computer, Inc.

IBM is a registered trademark of International Business Machines Corporation.

Macintosh trademark is licensed to Apple Computer, Inc.

MUMPS is a registered trademark of Massachusetts General Hospital.

Tektronix is a registered trademark of Tektronix, Inc.

UNIX is a registered trademark of American Telephone and Telegraph Company.

Copyright © 1987 Digital Equipment Corporation. All Rights Reserved.

# Contents

| Preface                                                                  |

|--------------------------------------------------------------------------|

| Chapter 1 • Introduction to the PDP-11 Family                            |

| The PDP-11 Tradition Continues                                           |

| Powerful, High-Performagnce Systems Offer Fast, Reliable Response 1-1    |

| PDP-11 Buses Built for Reliable Performance                              |

| PDP-11s—Your Best Business Choice                                        |

| Digital's Networking Strategy Integrates Your Computer Resources 1-4     |

| Software Compatibility Keeps Investment Costs Down 1-4                   |

| Maximum Packaging Flexibility Allows the Latest in Peripheral Tech . 1-5 |

| Digital's Attention to Detail Saves You Time and Money 1-6               |

| Digital's Quality and ServiceAn Ongoing Commitment 1-6                   |

| PDP-11 Systems Grow With You1-7                                          |

| MicroPDP-11/531-7                                                        |

| MicroPDP-11/73                                                           |

| MicroPDP-11/83                                                           |

| PDP-11/84                                                                |

| PDP-11 System Comparison Chart                                           |

|                                                                          |

| Classica 2 - Mina DDD 11/02 Career                                       |

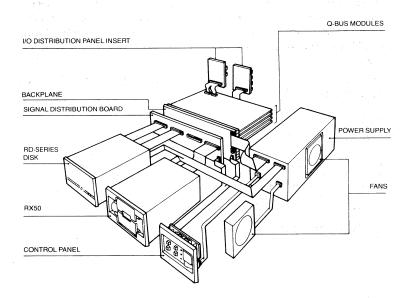

| Chapter 2 • MicroPDP-11/83 System                                        |

| Introduction                                                             |

| MicroPDP-11/83 System Features                                           |

| KDJ11-BF CPU Module2-3                                                   |

| MSV11-J Memory Module2-4                                                 |

| MicroPDP-11/83 Configurations                                            |

| Standard System                                                          |

| System Building Blocks                                                   |

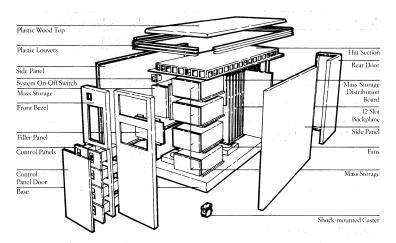

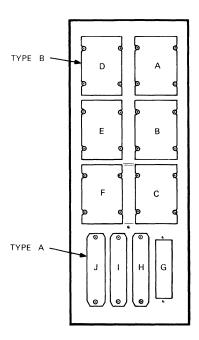

| Enclosures                                                               |

| Mass Storage                                                             |

| MicroPDP-11 Specifications2-7                                            |

| Backplane Assemblies2-7                                                  |

| Power Supplies                                                           |

| Control Panels                                                           |

| I/O Distribution Panels                                                  |

| Fans                                                                     |

| and Weight                                                               |

| equirements                                                              |

| vironment2-11                                                            |

|                                                                          |

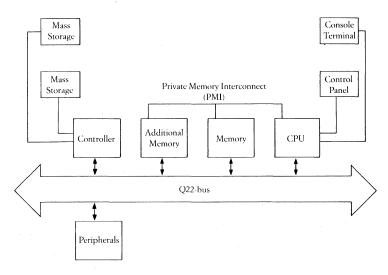

| MicroPDP-11 Architecture Summary2-                         | 11      |

|------------------------------------------------------------|---------|

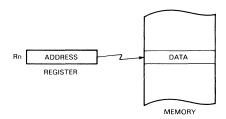

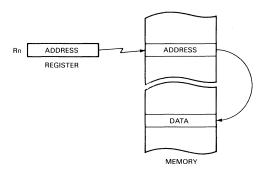

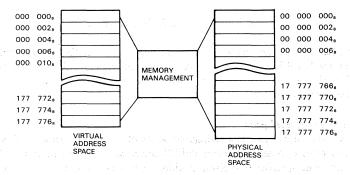

| Address Space and Memory                                   |         |

| Physical-address Space2-                                   | 13      |

| Virtual-address Space                                      |         |

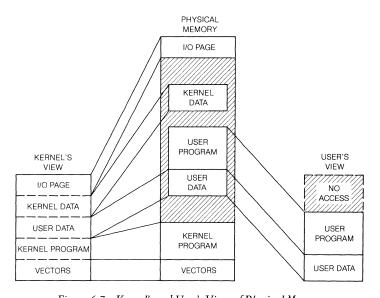

| Memory Management2-                                        | 14      |

| Memory Protection2-                                        | 15      |

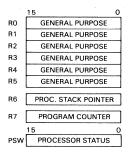

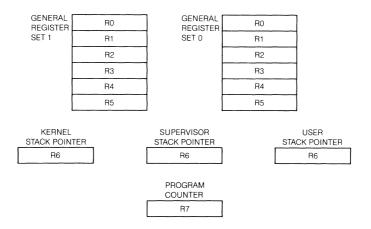

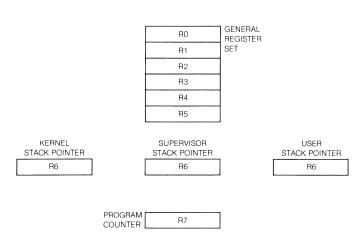

| Registers and Stacks2-                                     | 15      |

| MicroPDP-11 Registers2-                                    |         |

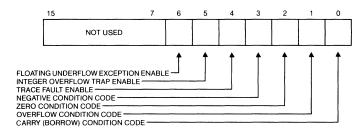

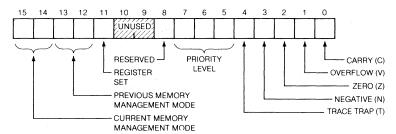

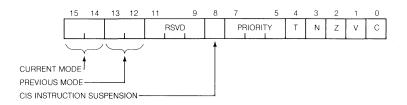

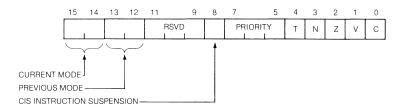

| Processor Status Word                                      |         |

| Addressing Modes2-                                         |         |

| Exceptions and Interrupts2-                                |         |

| Exception and Interrupt Vectors2-                          |         |

| Processor-priority Levels2-                                |         |

| Context Switching2-                                        |         |

| MicroPDP-11 Processor Operating Modes                      |         |

| Data Types2-                                               |         |

| Instruction Set                                            |         |

| Additional Documentation2-                                 | 31      |

|                                                            |         |

| Chapter 3 • MicroPDP-11/73 System                          |         |

| Introduction                                               | 3-1     |

| MicroPDP-11/73 System Features                             |         |

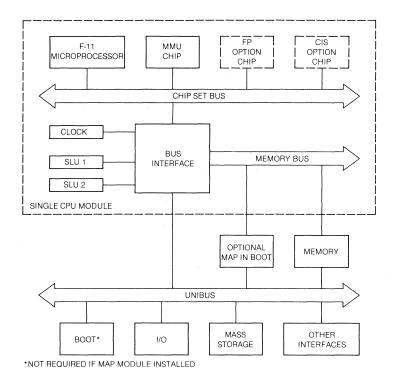

| KDJ11-BB CPU Module                                        |         |

| MSV11-Q Memory Module                                      |         |

| MicroPDP-11/73 Configurations                              |         |

| Standard Systems                                           |         |

| System Building Blocks                                     |         |

| Enclosures                                                 |         |

| Mass Storage                                               | 3-4     |

| Additional Information                                     | 3-4     |

|                                                            |         |

| Chapter 4 • MicroPDP-11/53 and MicroPDP-11/53 PLUS Systems |         |

| Introduction                                               | <br>4_1 |

| MicroPDP-11/53 and MicroPDP-11/53 PLUS Features            |         |

| KDJ11-DA and KDJ11-DB CPU Modules                          |         |

| MSV11-Q Memory Module                                      |         |

| MicroPDP-11/53 and MicroPDP-11/53 PLUS Configurations      |         |

| Standard Systems                                           |         |

| Enclosures                                                 |         |

| Mass Storage                                               |         |

| Additional Information                                     |         |

| Chapter 5 • Q-Bus Technical Description |

|-----------------------------------------|

| Introduction                            |

| Bus Communications                      |

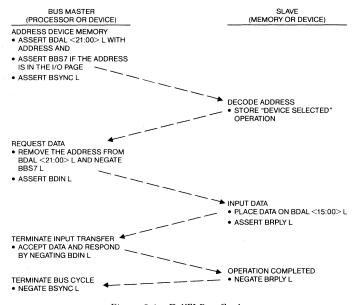

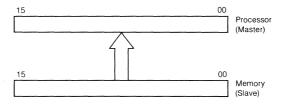

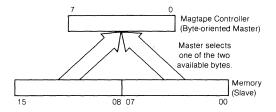

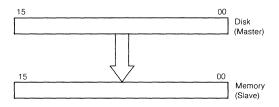

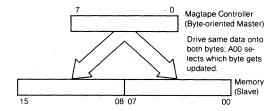

| Master/Slave Relationship5-2            |

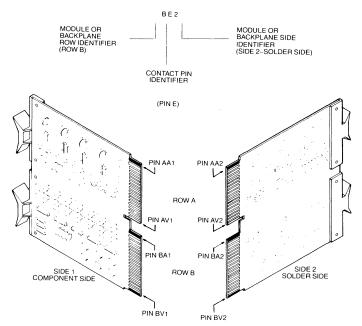

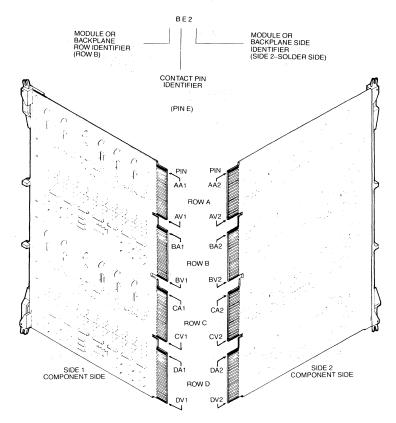

| Bus Signals and Pin Assignments         |

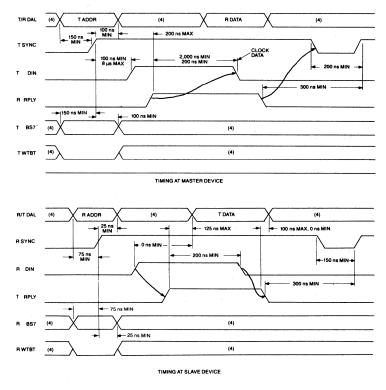

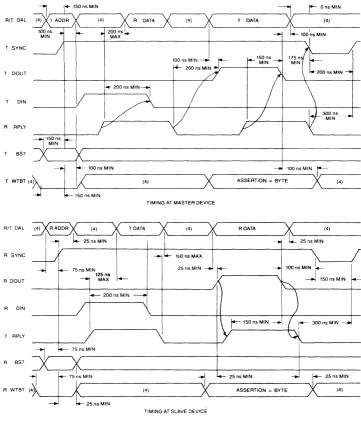

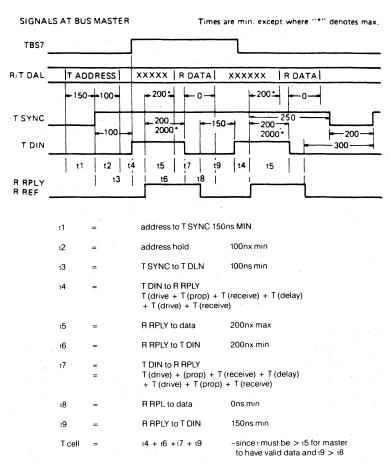

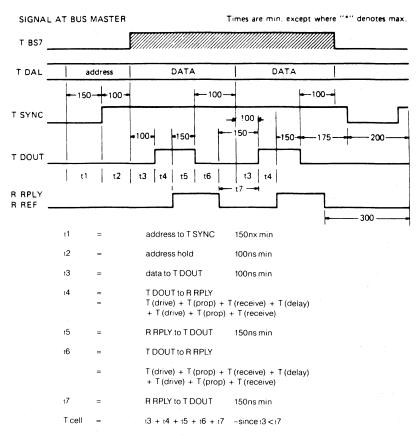

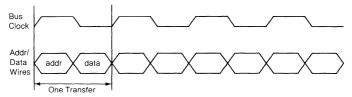

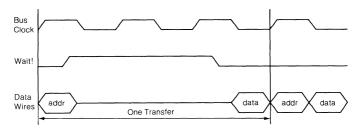

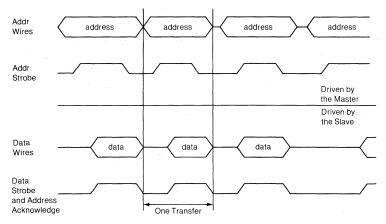

| Data Transfer Bus Cycles5-5             |

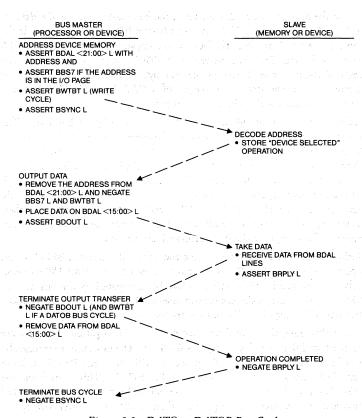

| Bus-cycle Protocol                      |

| Device Addressing5-7                    |

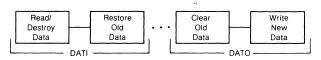

| DATI Bus Cycle                          |

| DATO(B) Bus Cycle                       |

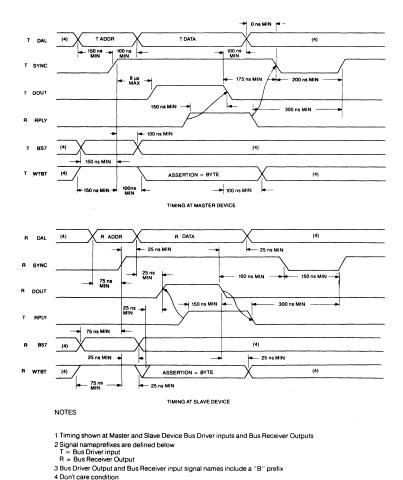

| DATIO(B) Bus Cycle5-13                  |

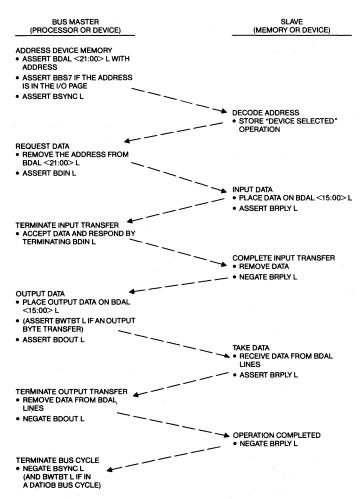

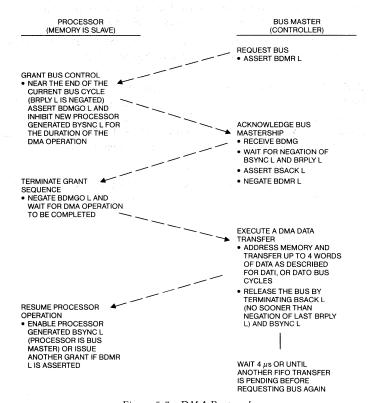

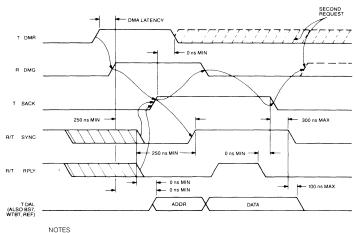

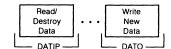

| Direct Memory Access 5-16               |

| DMA Protocol                            |

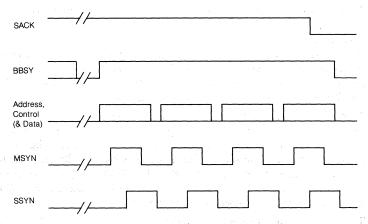

| Block Mode                              |

| DATBI Bus Cycle                         |

| DATBO Bus Cycle                         |

| DMA Guidelines5-23                      |

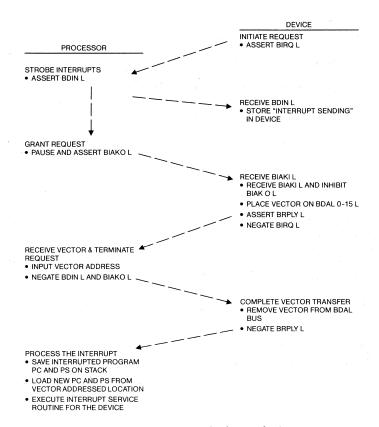

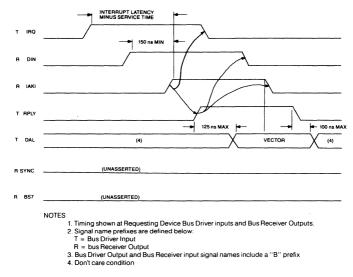

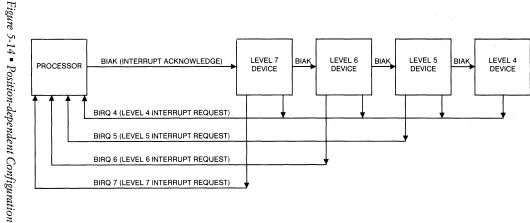

| Interrupts 5-23                         |

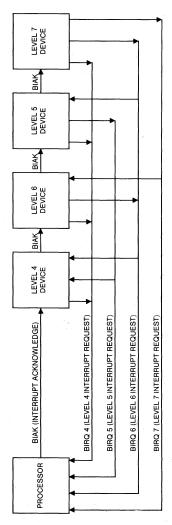

| Device Priority                         |

| Interrupt Protocol                      |

| Four-level Interrupt Configurations     |

| Control Functions                       |

| BREF                                    |

| Halt 5-33                               |

| Initialization 5-33                     |

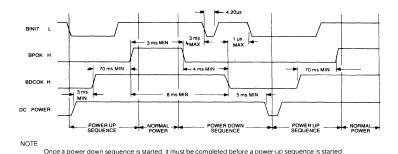

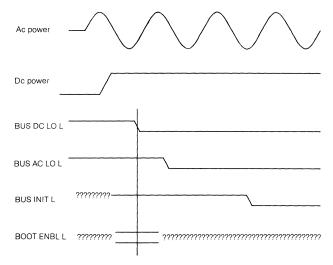

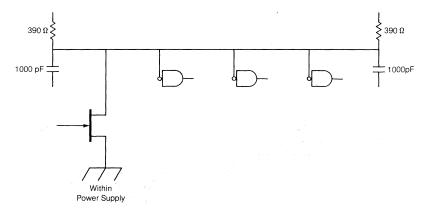

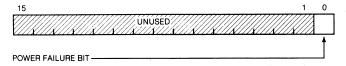

| Power Status                            |

| Powerup/Powerdown Protocol              |

| Bus Electrical Characteristics          |

| Load Definition                         |

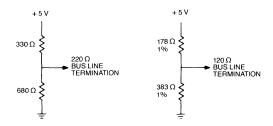

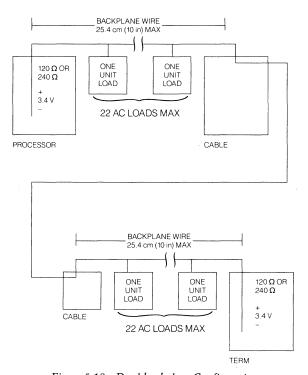

| 120-Ohm Bus5-35                         |

| Bus Drivers                             |

| Bus Receivers                           |

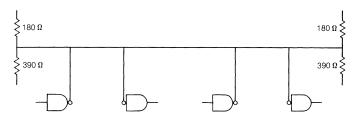

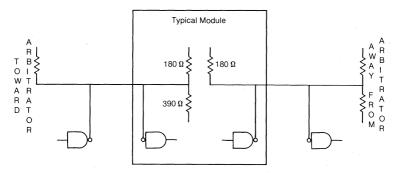

| Bus Termination                         |

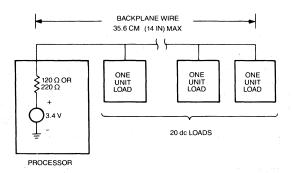

| Bus Interconnect Wiring                 |

| Backplane Wiring                        |

| Intrabackplane Wiring                   |

| Power and Ground5-38                    |

| A | Dual-backplane Configurations Power Supply Loading Module Connector Pin Identification Additional Information |

|---|---------------------------------------------------------------------------------------------------------------|

| A | Module Connector Pin Identification                                                                           |

| A |                                                                                                               |

| P | Additional Information                                                                                        |

|   |                                                                                                               |

| - |                                                                                                               |

| _ | Chapter 6 • PDP-11/84                                                                                         |

|   | ntroduction                                                                                                   |

|   | PDP-11/84 Hardware Features                                                                                   |

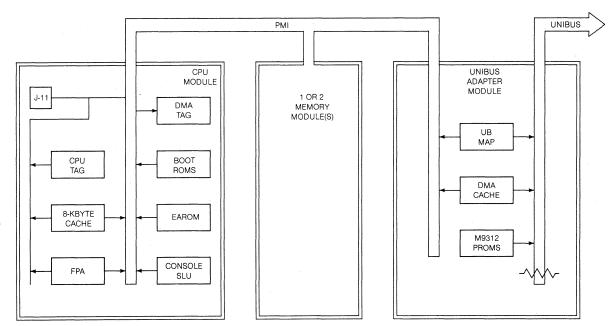

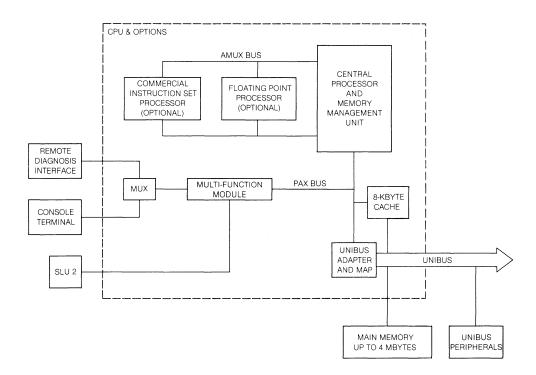

|   | System Architecture                                                                                           |

| ( | Central Processor                                                                                             |

|   | General Registers                                                                                             |

|   | Processor Status Word                                                                                         |

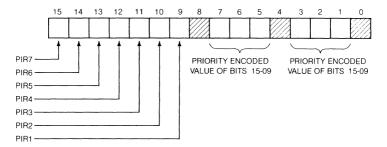

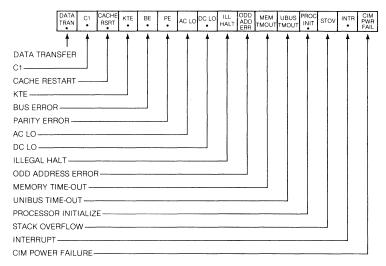

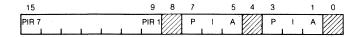

|   | Program Interrupt Request Register                                                                            |

|   | Pipeline Processing                                                                                           |

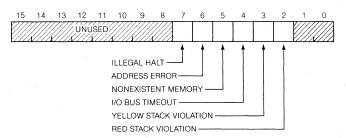

|   | CPU Error Register                                                                                            |

|   | Stack Limit Protection                                                                                        |

|   | Kernel Protection                                                                                             |

|   | Trap and Interrupt Service Priorities                                                                         |

|   | Hardware Detected Errors                                                                                      |

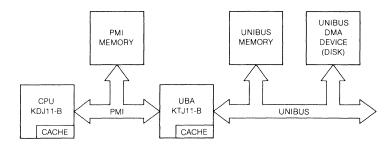

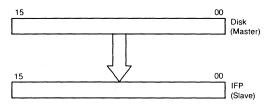

|   | Private Memory Interconnect                                                                                   |

| Ν | Memory System                                                                                                 |

|   | Memory Management                                                                                             |

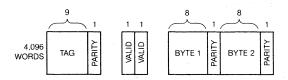

|   | Error Correction Code                                                                                         |

|   | Battery Backup Unit                                                                                           |

|   | UNIBUS Adapter                                                                                                |

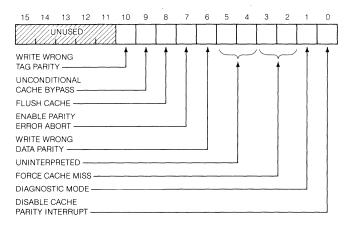

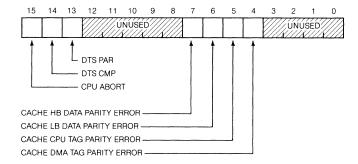

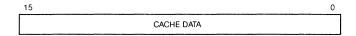

| _ | Cache Memory                                                                                                  |

|   | Backplane                                                                                                     |

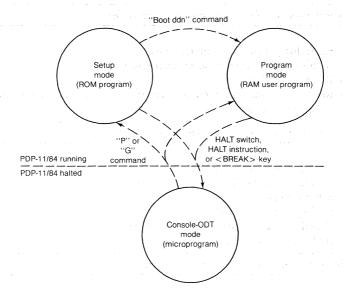

| ( | Console Functions                                                                                             |

| _ | Console Serial-line Unit                                                                                      |

| 1 | Line-time Clock                                                                                               |

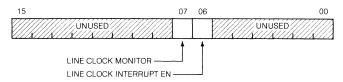

|   | Clock Status Register                                                                                         |

| ( | Console                                                                                                       |

|   | Setup Mode Functions                                                                                          |

|   | Program Mode Functions                                                                                        |

|   | Console ODT                                                                                                   |

| S | Specifications                                                                                                |

|   | Packaging                                                                                                     |

|   | Standard Equipment                                                                                            |

| Other Specifications                     |

|------------------------------------------|

| ac Power 6-41                            |

| Physical Characteristics                 |

| Weight 6-41                              |

| Operating Environment                    |

| Nonoperating Environment                 |

|                                          |

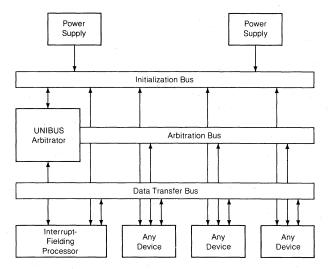

| Chapter 7 • UNIBUS Technical Description |

| Characteristics of the UNIBUS            |

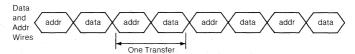

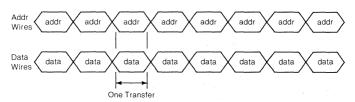

| Nonmultiplexed Bus                       |

| Strict Master/Slave Relationship         |

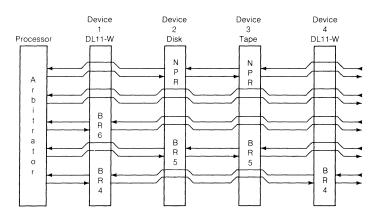

| Partially Distributed Arbitration        |

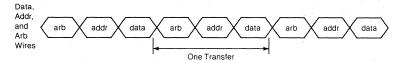

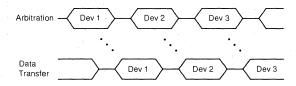

| Overlapped Arbitration and Data Transfer |

| Asynchronous Operation                   |

| 18 Address Bits                          |

| Word or Byte Operations                  |

| Parity Error Information from Slaves     |

| UNIBUS Block Diagram7-7                  |

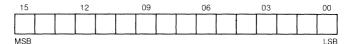

| UNIBUS Data and Address Organization     |

| Addresses                                |

| Data                                     |

| Types of UNIBUS Data Transfers           |

| Read Word                                |

| Write Word                               |

| Write Byte                               |

| Read Word with Write Intent              |

| Write Vector                             |

| UNIBUS Signal Details                    |

| Initialization and Shutdown Signals      |

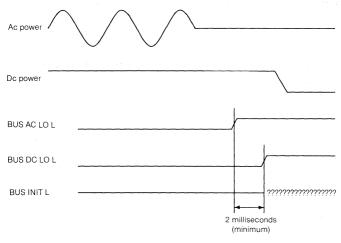

| Powerup Timing                           |

| Powerdown Timing                         |

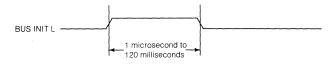

| Initialization Timing                    |

| Arbitration Signals                      |

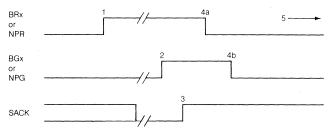

| UNIBUS Arbitration Timing                |

| Abnormal Cycles                          |

| Data Transfer Signals                    |

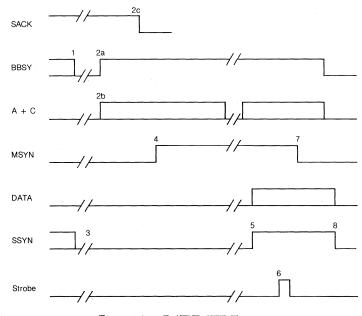

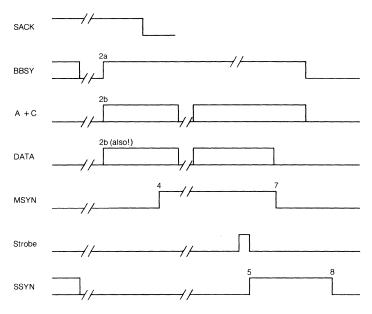

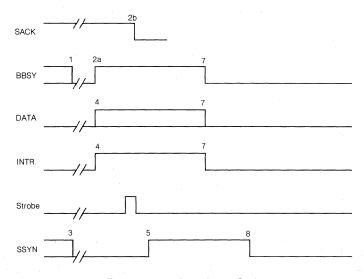

| DATI Timing                              |

| DATIP                                    |

| DATO/DATOB                               |

| Write Vector Timing                      |

|                                                  | 7-36<br>7-37<br>7-37<br>7-38<br>7-39<br>7-40<br>7-41<br>7-41<br>7-42<br>7-43<br>7-43 |

|--------------------------------------------------|--------------------------------------------------------------------------------------|

| Chapter 8 • System Software and Layered Products |                                                                                      |

| Introduction                                     | 8-1                                                                                  |

| PDP-11 Operating and Development Systems         |                                                                                      |

| RSX-11 Family                                    | 8-1                                                                                  |

| RSTS Family                                      | 8-4                                                                                  |

| MicroPower/Pascal Development Toolkit            |                                                                                      |

| ULTRIX-11 Operating System                       |                                                                                      |

| RT-11 and CTS-300 Operating Systems              |                                                                                      |

| DSM-11                                           |                                                                                      |

| High-level Languages                             |                                                                                      |

| BASIC                                            |                                                                                      |

| C                                                |                                                                                      |

| COBOL-81                                         |                                                                                      |

| CORAL-66                                         |                                                                                      |

| DIBOL-83                                         |                                                                                      |

| FORTRAN                                          |                                                                                      |

| MUMPS                                            | 8-16                                                                                 |

| PDP-11 Pascal/RSX                                |                                                                                      |

| Information Management Software                  |                                                                                      |

| DATATRIEVE-11                                    |                                                                                      |

| DECgraph-11                                      |                                                                                      |

| DECmail-11                                       |                                                                                      |

| FMS-11                                           |                                                                                      |

| INDENT                                           |                                                                                      |

| RMS                                              |                                                                                      |

| Programmer Productivity Tools                    |                                                                                      |

| ADE                                              | 8-20                                                                                 |

| MENU-11                                          |                                                                                      |

|                                                  |                                                                                      |

| Communications                       |

|--------------------------------------|

| Business Applications                |

| Additional Documentation 8-21        |

|                                      |

| Chapter 9 • System Options           |

|                                      |

| Q-bus Memory Options                 |

| Q-bus Storage Options                |

| Q-bus Communications Options         |

| Q-bus Asynchronous Interfaces        |

| Q-bus Synchronous Interfaces         |

| Q-bus Realtime Interfaces            |

| UNIBUS System Options                |

| UNIBUS Memory Options                |

| UNIBUS Storage Options               |

| UNIBUS Communications Options        |

| UNIBUS Realtime Interfaces           |

| Terminals, Printers, and Modems 9-14 |

| Videoterminals 9-14                  |

| Printers and Printing Terminals      |

|                                      |

| Modems                               |

| Additional Options                   |

| Additional Documentation             |

|                                      |

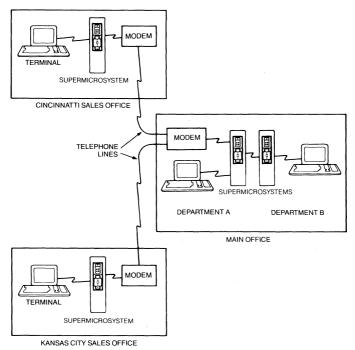

| Chapter 10 • Networks                |

| Introduction                         |

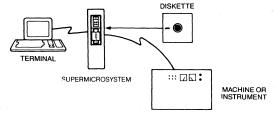

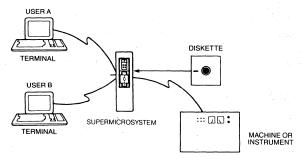

| Types of Systems                     |

| Stand-alone Systems                  |

| Network-connected Systems            |

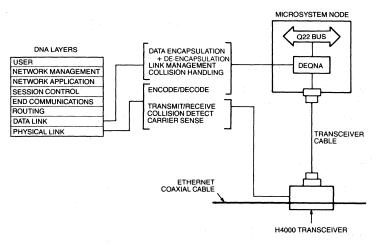

| Digital Network Architecture         |

| DNA Structures                       |

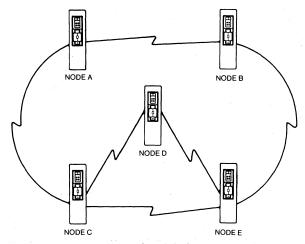

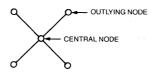

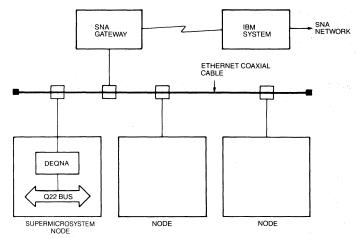

| Typical Network Configurations       |

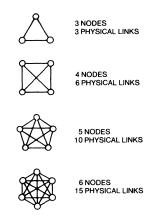

| Types of Links                       |

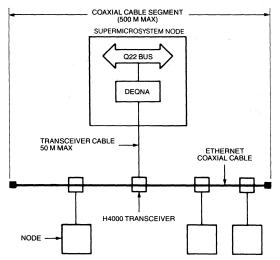

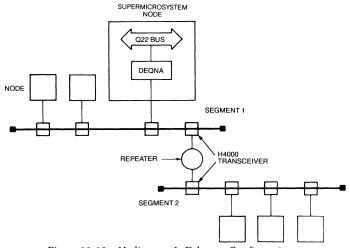

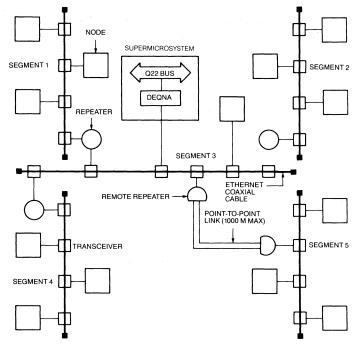

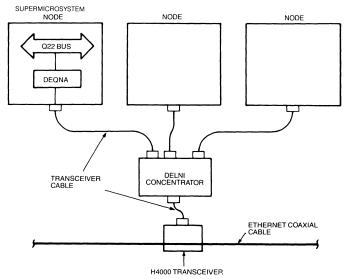

| Ethernet and ThinWire Ethernet Links |

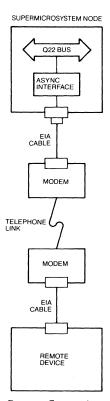

| Asynchronous Links                   |

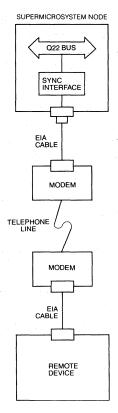

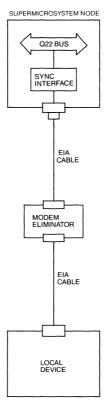

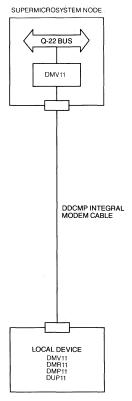

| Synchronous Links                    |

| Network Software                     |

| DECnet Communications                |

| Internet Communications              |

| Packetnet System Interface           |

| Additional Documentation 10-24  Chapter 11 * Services and Documentation  Field Service 11-1 The OEM Portfolio 11-1 Onsite Services 11-2 Offsite Services 11-5 Computer Services 11-5 Computer Services 11-5 Professional Services 11-5 Professional Services 11-5 Professional Services 11-6 Educational Services 11-6 Educational Services 11-7 Training Centers 11-10 Documentation 11-12  Appendices  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Digital PC Connection                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 11 * Services and Documentation  Field Service                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Additional Documentation                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| The OEM Portfolio Onsite Services Offsite Services 11-3 Offsite Services 11-4 Software Services 11-5 Computer Services 11-5 Professional Services 11-6 Network Management Services 11-7 Educational Services 11-8 Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences Appendix B Console ODT Command Languages Appendix C Instruction Timing Appendix C Instruction Timing Appendix D MicroPDP-11/23 System Upgrades Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapter 11 • Services and Documentation                             | on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| The OEM Portfolio Onsite Services Offsite Services 11-3 Offsite Services 11-4 Software Services 11-5 Computer Services 11-5 Professional Services 11-6 Network Management Services 11-7 Educational Services 11-8 Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences Appendix B Console ODT Command Languages Appendix C Instruction Timing Appendix C Instruction Timing Appendix D MicroPDP-11/23 System Upgrades Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Field Service                                                       | 11-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Offsite Services 11-5 Software Services 11-5 Computer Services 11-5 Professional Services 11-6 Network Management Services 11-8 Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The OEM Portfolio                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Software Services 11-5 Computer Services 11-5 Professional Services 11-6 Network Management Services 11-8 Educational Services 11-5 Training Centers 11-10 Documentation 11-12  Appendices  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary  Software Services 11-5 Computer Services 11-6 Network Management Services 11-6 Net | Onsite Services                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Computer Services 11-5 Professional Services 11-6 Network Management Services 11-8 Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Offsite Services                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Professional Services 11-6 Network Management Services 11-8 Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Software Services                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Network Management Services  Educational Services  Training Centers  11-10  Documentation  11-12  Appendices  Appendix A PDP-11 Family Differences  Appendix B Console ODT Command Languages  Appendix C Instruction Timing  C-Appendix D MicroPDP-11/23 System Upgrades  Appendix E PDP-11/24 and PDP-11/44 Systems  Glossary  C-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary  Educational Services 11-9  Training Centers 11-10  Appendices  A-Appendices A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/24 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Educational Services 11-9 Training Centers 11-10 Documentation 11-12  Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary  Educational Services 11-9  Training Centers 11-10  Appendices  A-Appendices A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/24 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Network Management Services                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Appendices  Appendix A PDP-11 Family Differences A-Appendix B Console ODT Command Languages B-Appendix C Instruction Timing C-Appendix D MicroPDP-11/23 System Upgrades D-Appendix E PDP-11/24 and PDP-11/44 Systems E-Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |